J-11

# DATA CHIP SPECIFICATION 21-17677-00

Rev. 3.03 (July 1, 1982)

#### COMPANY CONFIDENTIAL

Copyright (c) 1979, 1980, 1981, 1982 by Digital Equipment Corporation.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may occur in this document.

This specification does not describe any program or product which is currently available from Digital Equipment Corporation. Nor does Digital Equipment Corporation commit to implement this specification in any program or product. Digital Equipment Corporation makes no commitment that this document accurately describes any product it might ever make.

ι,

## RESERVED ISSUES

The following issues are reserved for the implementation effort and have no impact on contractual status or delivery. When these issues are resolved, the chip specifications will be updated accordingly.

Data Chip - EU register file codes. Harris may assign extra register select codes to ensure that all codes actually select a register.

Freeze point: Data chip logic design review

Status: Closed December, 1980

2. Data Chip - MMU register file codes. Harris may reassign register select codes to minimize internal logic.

Freeze point: End June, 1980

Status: Closed December, 1980

3. Data Chip - Opcodes. Within guidelines to be provided by DEC by end April 1980, Harris may assign currently unassigned opcodes to minimize internal logic.

Freeze point: End June, 1980

Status: Closed December, 1980

4. Control Chip - AIO codes. DEC may reassign AIO codes to minimize external logic.

Freeze point: End April, 1980

Status: Closed - no change to specification

5. Data Chip - NOP status flags. This is a don't care. NOP must have an opcode of 177 and must not alter the EU register file.

Freeze point: End June, 1980

Status: Closed December, 1980

6. Control and Data Chips - AC characteristics. By mutual agreement, Harris and DEC can adjust all non-critical parameters to minimize internal and external logic, within the following limits:

. .

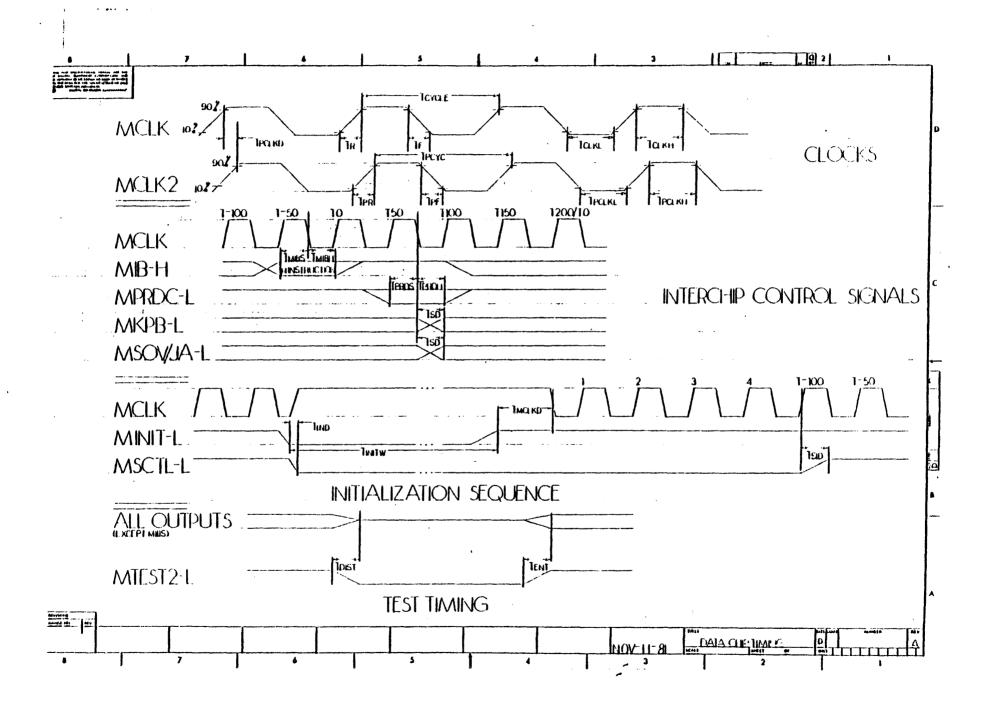

## Control Chip AC Constraints

tpd + tps (MPRDC-L valid delay + setup)  $\leq$  75 ns

tseld + tsels (MCSEL-L active delay + setup)  $\leq$  75 ns

tmibs + tmibd (MIB-H valid delay + setup) < 75 ns

## Interchip AC Constraints

tscs + tsid (MSCTL-L setup + inactive delay)  $\leq$  50 ns tmibs + tmibd (Data Chip + Control Chip)  $\leq$  75 ns tpd + tprds (MPRDC-L valid delay + setup)  $\leq$  75 ns

MKPB-L, MSOV/JA-L must be valid by T100 and held to T150

Freeze point: End of pass 3 of Control Chip Status: Open

7. Data Chip - I/O multiplexor. Within the functional and timing constraints of the Data Chip Specification, Harris can implement the I/O multiplexor as it chooses to minimize layout area and/or logic.

Freeze point: Data Chip logic design review Status: Closed December, 1980

8. Data Chip - UMULS, SMULS, DIVS microinstructions. These microinstructions are shown as implemented for all operand lengths. Should a subset implementation save logic in the Data Chip, only the following lengths need be implemented:

UMULS - longword SMULS - word DIVS - word, longword

In particular, support of byte length operands need not be implemented.

Freeze point: Data chip logic design review

Status: Closed - byte length not implemented

9. Data Chip - Crystal input parameters. The crystal input AC parameters and test conditions will be specified when DEC selects an input crystal for the chip set.

Freeze point: End April, 1980

Status: Open, extended until December, 1982

10. Control and Data Chips - DC characteristics. The TTL input parameters ( $V_{\rm LHT}$  and  $V_{\rm LLT}$ ) are goals and are subject to change as simulation results become available. Harris and DEC can adjust these parameters by mutual agreement.

Freeze point: End April, 1980

Status: Open, extended until December, 1982

11. Data Chip - Clock outputs. Input test conditions are tbs.

Freeze point: End June, 1980

Status: Open, extended until December, 1982

12. Data Chip - MDAL turnaround. The test specification is for an isolated chip. In a real system, the Data Chip will be fighting with another driver. By mutual agreement, Harris and DEC can adjust the test specification on MDAL turnaround to more accurately reflect actual operating conditions.

Freeze point: End April, 1980

Status: Closed - no change to test specification

## REVISION HISTORY

| REV  | DATE    | REASON                                                                                                                                                                                                          |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.03 | 7/1/82  | Incorporated spcification changes 1b, 63, 105, 111-112, 114, 118-121, 124-125, 128-130 of Rev 13 of the specification change list dated June 22, 1982.                                                          |

| 3.02 | 2/9/81  | Incorporated specification changes 1b, 30, 34, 36-57, 59-62, 64-81, and 83-104 of Rev 9 of the Specification Change list dated February 9, 1981.                                                                |

| 3.01 | 8/4/80  | Incorporated specification changes 1, 2, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 20, 21, 23, 28, 31, 32, 33, 35, 40, 41, 42, 43, and 44 of Rev 5 of the Specification Change list dated Aug 4, 1980. |

| 3.00 | 4/16/80 | Incorporated specification number.                                                                                                                                                                              |

| 2.00 | 1/80    | Major revision. Reorganized to reflect proposed layout. Removed virtual cache structure.                                                                                                                        |

| 1.01 | 10/79   | Changed microcode format and prefetch mechanism to reflect virtual cache structure. Moved PS to dual ported register file. Defined shifting functions. Further enhanced English explanations. General clean up. |

| 1.0  | 7/79    | Preliminary.                                                                                                                                                                                                    |

## TABLE OF CONTENTS

| 1.0 | INTRODUCTION 1.1 Scope 1.2 Applicable Documents 1.3 Data Chip Description 1.4 Internal Busses                                                                                                                                                   | 1-10<br>1-10<br>1-10                                 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|     | 1.5 Major States                                                                                                                                                                                                                                | 1-11<br>1-12                                         |

| 2.0 | EXECUTION UNIT 2.1 Register File 2.1.1 Physical Organization 2.1.1.1 32-Bit Scratch Registers 2.1.1.2 PDP-11 General Registerns (Rn,Rn') 2.1.1.3 Stack Pointers (SP) 2.1.1.4 Program Counter (PC) 2.1.1.5 Memory Management Register 2 (MMR2)   | 2-1<br>2-1<br>2-1<br>2-3<br>2-4<br>2-4               |

|     | 2.1.1.6 Processor Status Register (PS) 2.1.1.6.1 Register Format 2.1.1.6.2 PS Protection Logic 2.1.1.7 PDP-11 Instruction Register (IR) 2.1.1.7.1 Instruction Register 2.1.1.7.2 Shadow Instruction Register (SIR) 2.1.1.7.3 IR Field Extractor | 2 - 5<br>2 - 5<br>2 - 6<br>2 - 8                     |

|     | 2.1.2 Decode and Access 2.1.2.1 Microcode Access 2.1.2.2 Explicit Access 2.1.3 Register Read Operations 2.1.4 Register Write Operations 2.2 Special B-Bus Logic                                                                                 | 2-9<br>2-9<br>2-11<br>2-11<br>2-11                   |

|     | 2.2.1 Literal Generation Logic 2.2.2 Decimal Adjust Logic 2.2.3 Sign Extension Logic 2.3 EU Data Path Components 2.3.1 EU Data Path Functions 2.3.1.1 Operations                                                                                | 2-12<br>2-13<br>2-14<br>2-15<br>2-15                 |

|     | 2.3.1.2 Data Flow 2.3.1.3 Status Flags 2.3.1.4 Extended Status Testing 2.3.2 Arithmetic-Logical Unit (ALU) 2.3.3 Bit Shifter and Byte Swapper 2.3.4 Shift Register (SR) 2.4 Branch/Jump Logic                                                   | 2-15<br>2-15<br>2-17<br>2-13<br>2-13<br>2-19<br>2-25 |

|     | 2.4.1 Macro-Branch Logic 2.4.2 Conditional Jump Testing Logic 2.5 EU/MDAL Interface 2.5.1 I/O Multiplexor 2.5.2 Input Latch (IL[1:0]<15:0>)                                                                                                     | 2-25<br>2-25<br>2-27<br>2-27                         |

|     | 2.5.3 Output Latch (OL<21:0>) 2.6 Microinstruction Register (MIR<21:0>) 2.7 State Sequencer                                                                                                                                                     | 2-23<br>2-28<br>2-28<br>2-28                         |

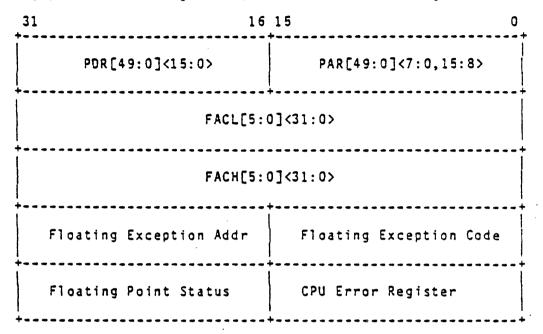

| 3.1.1 Physical Organization 3.1.1.1 Floating Point Registers 3.1.1.2 CPU Error Register 3.1.1.3 Relocation Registers 3.1.1.3.1 Page Address Registers (PARs) 3.1.1.3.2 Page Descriptor Registers (PDRs) 3.1.2 MMU Register Access     | 3-7                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 3.2.1 Adder Input Multiplexor/Latch 3.2.2 Address Adder                                                                                                                                                                               | 3-13<br>3-13<br>3-13<br>3-14<br>3-14<br>3-14<br>3-15<br>3-16<br>3-16 |

| 3.2.4 Memory Management Abort Logic 3.2.5 Address Error Logic 3.2.6 Address Adjust and Detect Logic 3.2.7 Usage of Results 3.3 MMU Special Registers 3.3.1 MMRO 3.3.2 MMR1 3.3.3 MMR3 3.3.3.1 Register Format 3.3.3.2 I/O Space Logic | 3-18<br>3-10<br>3-19<br>3-21<br>3-22<br>3-25<br>3-25<br>3-26         |

| 3.3.5.1 Register Format 3.3.5.2 Cache Control Logic 3.3.6 Hit/Miss Register 3.4 Stack Limit Logic  4.0 PREFETCH MECHANISM 4.1 Prefetch Operation 4.1.1 Normal Operating State                                                         | 3-26<br>3-27<br>3-27<br>3-28<br>3-28<br>3-28<br>4-1<br>4-2<br>4-2    |

|     | 4 2   | Prefetch Microinstructions                                                 | 4 - 4                        |

|-----|-------|----------------------------------------------------------------------------|------------------------------|

|     | * • • | 4.2.1 Operate Prefetch                                                     | 4-4                          |

|     |       | 4.2.2 Read Instruction Stream (RDI)                                        | 4-5                          |

|     |       | 4.2.3 Read Demand Prefetch (RDF)                                           | 4-6                          |

|     |       | 4.2.4 Resynchronization (RSYNC)                                            | 4-6                          |

|     |       | 4.2.4 Resynchronization (RSYNC) 4.2.5 Resynchronization Sequences          | 4 - 7                        |

|     | 4.3   | Parallel Decode Operation                                                  | 4 - 8                        |

| 5.0 | MIC   | ROINSTRUCTIONS                                                             | 5-1                          |

|     | 5.1   | Operate Microinstructions                                                  | 5 - 2                        |

|     |       | 5.1.1 Format                                                               | 5 - 2                        |

|     |       | 5.1.1.1 Operand Length                                                     | 5 - 3                        |

|     |       | 5.1.1.2 PS Condition Code Update                                           | 5 - 3                        |

|     |       | 5.1.1.3 Counter Control 5.1.1.4 Prefetch Control Field                     | 5 <b>-</b> 3<br>5 <b>-</b> 4 |

|     |       | 5.1.2 Special Assembly Syntax                                              | 5 - 4                        |

|     |       | 5.1.3 Mnemonics                                                            | 5-4                          |

|     | 5.2   | Literal Microinstructions                                                  | 5-10                         |

|     | •••   | 5.2.1 Format                                                               | 5-10                         |

|     |       | 5.2.2 Mnemonics                                                            | 5-10                         |

|     |       | 5.2.2.1 Load Counter (LCNTR)                                               | 5-12                         |

|     |       | 5.2.2.2 Load Microstack (LMSTK)                                            | 5-12                         |

|     | 5.3   | Address Microinstructions                                                  | 5-13<br>5-13                 |

|     |       | 5.3.1 Format                                                               | 5-13                         |

|     | 5 A   | 5.3.2 Mnemonics                                                            | 5-13<br>5-15                 |

|     | 3.4   | Internal Input/Output Microinstructions 5.4.1 Format                       | 5-15                         |

|     |       | 5.4.2 Mnemonics                                                            | 5-15                         |

|     |       | 5.4.2.1 Read Data from MMU Register (INPR)                                 | 5-16                         |

|     |       | 5.4.2.2 Write Data to MMU Register (OUTR)                                  | 5-16                         |

|     |       | 5.4.2.3 Write Control Chip Status (OUTS)                                   | 5-17                         |

|     |       | 5.4.2.4 Write Control Chip Control (OUTC)                                  | 2-12                         |

|     | 5.5   | External Input/Output Microinstructions                                    | 5-19                         |

|     |       | 5.5.1 Format                                                               | 5-19                         |

|     |       | 5.5.2 Mnemonics                                                            | 5-19                         |

|     |       | 5.5.2.1 Read Data (RD)                                                     | 5-20<br>5-20                 |

|     |       | 5.5.2.2 Read-Modify-Write Data (RMW)<br>5.5.2.3 Read General Purpose (RDG) | 5-21                         |

|     |       | 5.5.2.4 Read Interrupt Vector (RDINTR)                                     | 5-21                         |

|     |       | 5.5.2.5 Read Instruction Stream (RDI)                                      | 5-21<br>5-21                 |

|     |       | 5.5.2.5 Read Prefetch Data (RDF)                                           | 5-22<br>5-22                 |

|     | 5.6   | Jumps                                                                      | 5 - 2 2                      |

|     |       | 5.6.1 Format                                                               | 5-22                         |

|     |       | 5.6.2 Mnemonics                                                            | 5-22                         |

|     |       | 5.6.3 Pipelined Jumping                                                    | 5-23                         |

|     | 5.7   | Microinstruction Format Summary                                            | 5-24                         |

| 6.0  |       | TERFACE                                           | 6-1   |

|------|-------|---------------------------------------------------|-------|

|      | 6.1   | Inputs                                            | 6-1   |

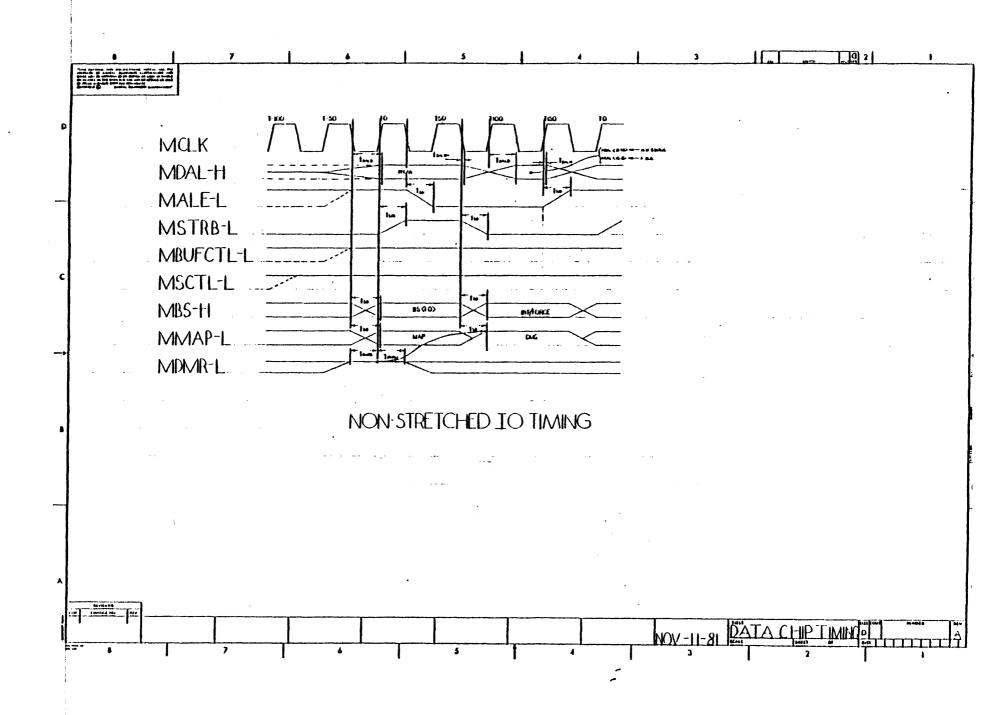

|      |       | 6.1.1 Micro Data and Address Lines (MDAL-H<15:0>) | 6-1   |

|      |       | 6.1.2 Microinstruction Bus (MIB-H<21:0>)          | 6-1   |

|      |       | 6.1.3 Crystal Inputs (XTALI, XTALO)               | 6-1   |

|      |       | 6.1.4 Data Valid (MDV-L)                          | 6-1   |

|      |       | 6.1.5 Cache Miss (MMISS-L)                        | 6-1   |

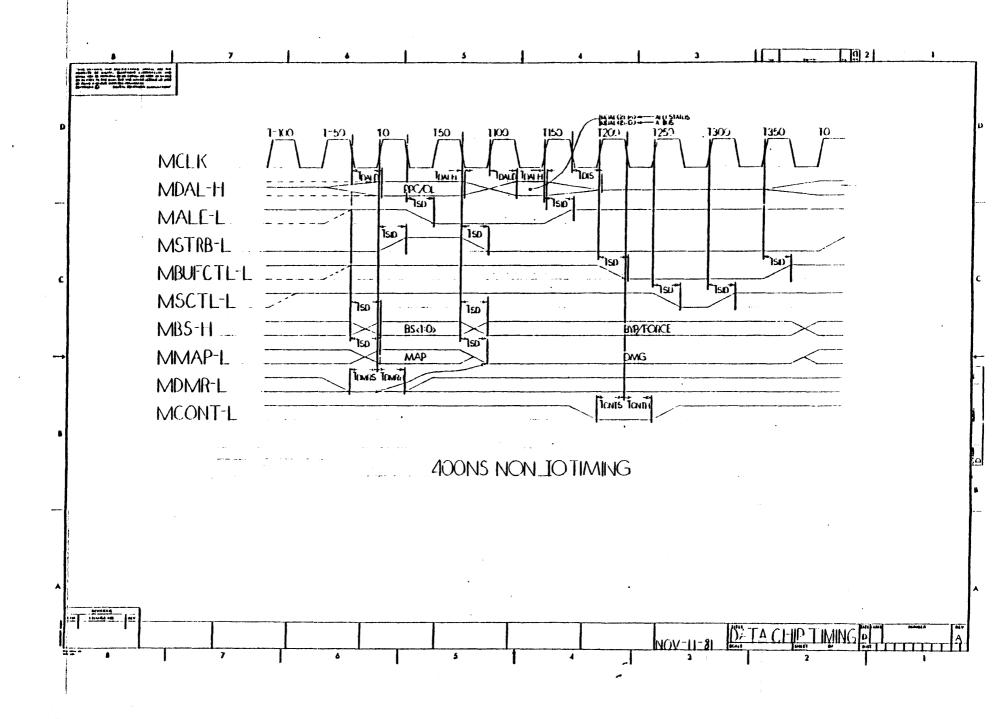

|      |       | 6.1.6 Continue (MCONT-L)                          | 6-1   |

|      |       | 6.1.7 DMA Request (MDMR-L)                        | 6 - 2 |

|      |       | 6.1.8 Abort (MABORT-L)                            | 6-2   |

|      |       | 6.1.9 Predecode (MPRDC-L)                         | 6 - 2 |

|      |       | 6.1.10 Initialize (MINIT-L)                       | 6-2   |

|      |       | 6.1.11 Test Mode (TEST1-L)                        | 6 - 2 |

|      |       | 6.1.12 Chip Disable (TEST2-L)                     | 6-2   |

|      | 6.2   | Outputs                                           | 6 - 3 |

|      |       | 6.2.1 Micro Data and Address Lines (MDAL-H<21:0>) | 6-3   |

|      |       | 6.2.2 Microinstruction Bus (MIB-H<21:0>)          | 5-3   |

|      |       | 6.2.3 Clock (MCLK)                                | 6 - 3 |

|      |       | 6.2.4 Phase Clock (MCLK2)                         | 6 - 3 |

|      |       | 6.2.5 Address Latch Enable (MALE-L)               | 6-3   |

|      |       | 6.2.6 Buffer Control (MBUFCTL-L)                  | 6 - 3 |

|      |       | 6.2.7 Stretch Control (MSCTL-L)                   | 6-4   |

|      |       | 6.2.8 Stack Overflow and Jump Allow (MSOV/JA-L)   | 6 - 4 |

|      |       | 6.2.9 Abort (MABORT-L)                            | 6 - 4 |

|      |       | 6.2.10 Kill Prefetch Buffer (MKPB-L)              | 6-4   |

|      |       | 6.2.11 Strobe (MSTRB-L)                           | 6-4   |

|      |       | 6.2.12 Bank Select (MBS-H<1:0>)                   | 6 - 5 |

|      |       | 6.2.13 I/O Map Enable (MMAP-L)                    | 6 - 5 |

|      | 5.3   | Signal Summary                                    | 6 - 6 |

| 7.0  | DC    | CHARACTERISTICS                                   | 6-7   |

|      |       |                                                   |       |

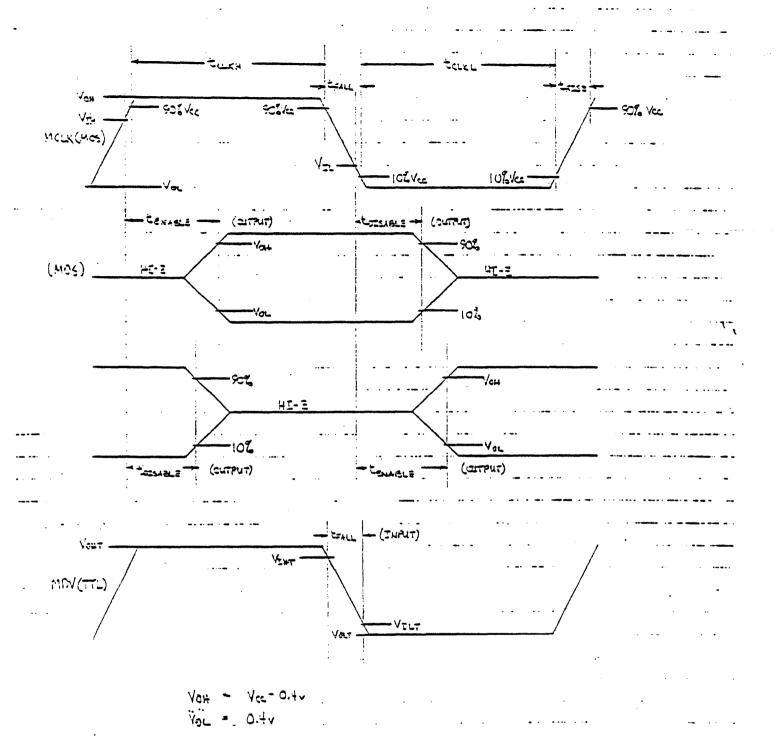

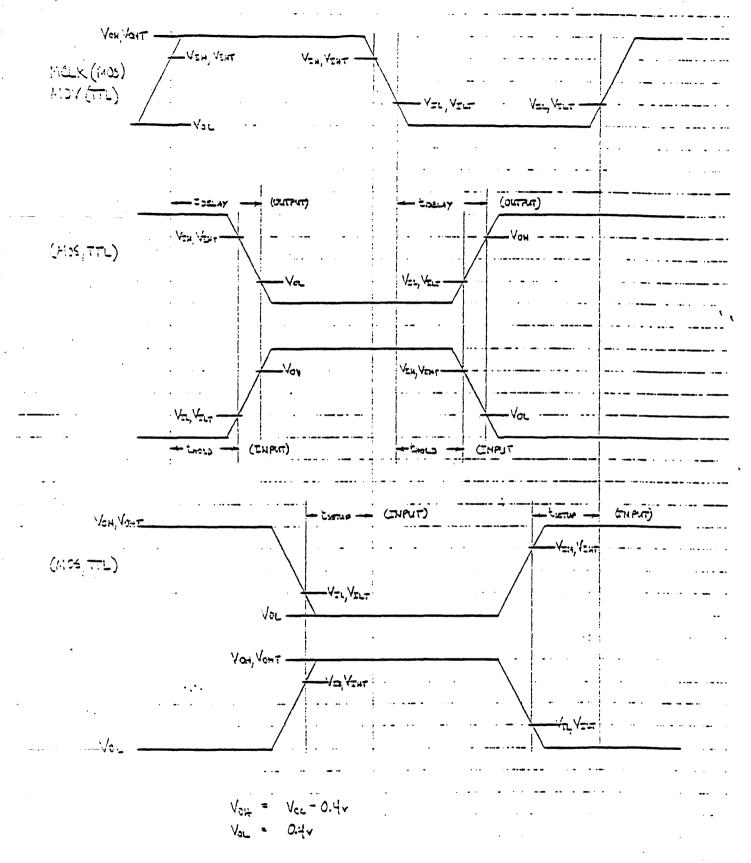

| 8.0  | AC    | CHARACTERISTICS                                   | 8-1   |

| Аррі | end i | x A - Multiply/Divide Microinstructions           | A-1   |

| Anne | and i | x B - Condition Code Equations                    | B-1   |

#### 1.0 INTRODUCTION

#### 1.1 Scope

This document specifies the design of a MOS/LSI chip which is part of a chip set that implements a high performance PDP-11 processor with Memory Management, FP-11 Floating Point, and CIS Commercial Instructions. This specification describes the internal organization of the Data chip. It does not describe the operation of the PDP-11 or other chips in the chip set. For further information, the applicable documents should be consulted.

#### 1.2 Applicable Documents

PDP-11/70 Processor Handbook

J-11 Chip System Specification

J-11 Programmer's Reference

J-11 Control Chip Specification

J-11 Microprogrammer's Reference

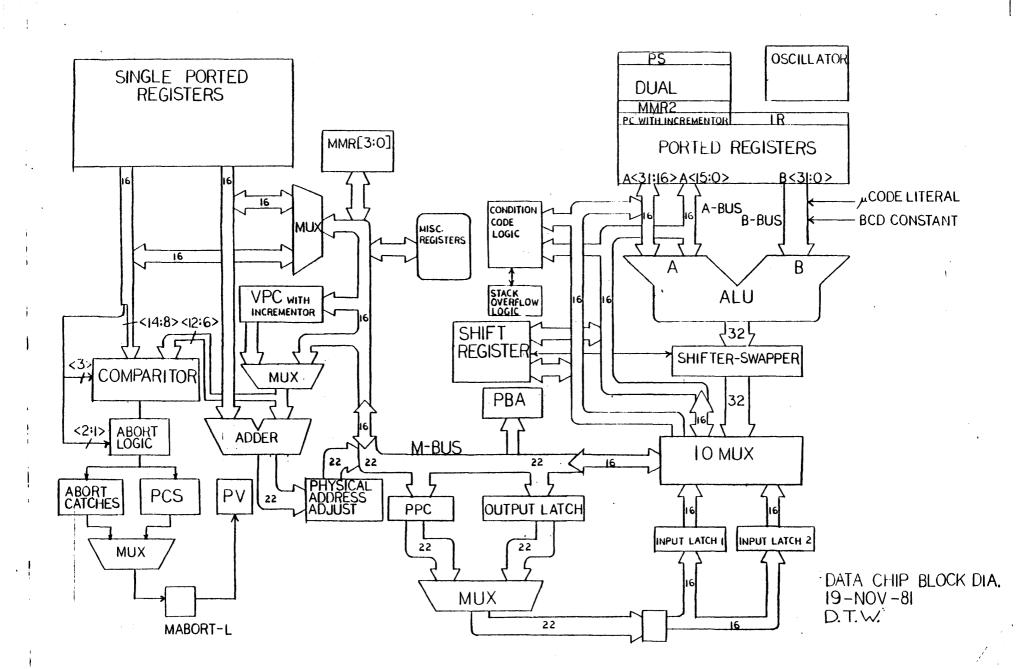

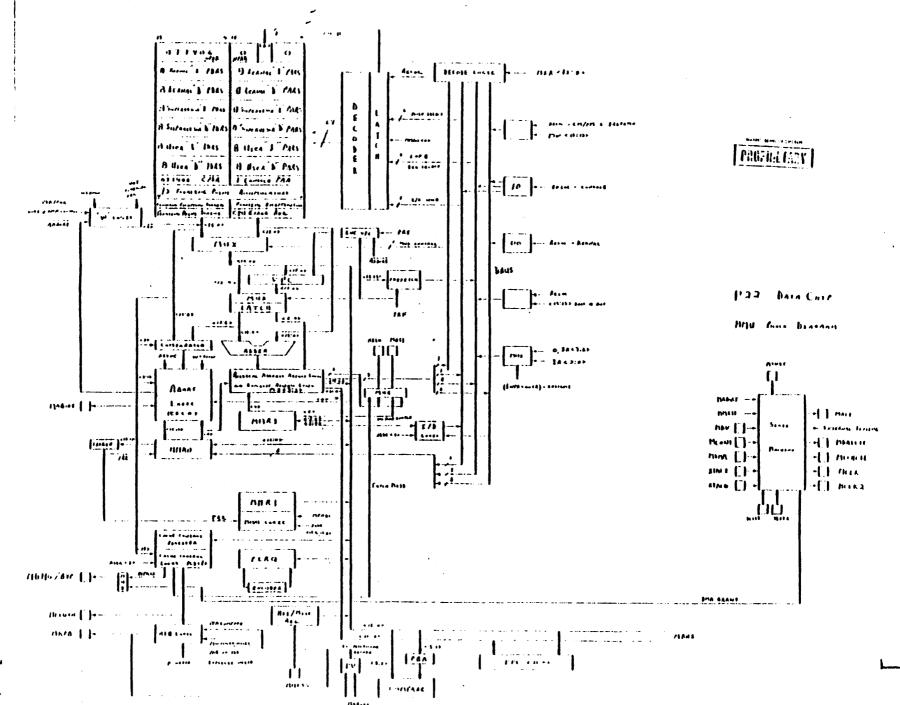

## 1.3 Data Chip Description

The Data chip is composed of three major pieces: an Execution Unit (EU), a Memory Management Unit (MMU), and a Prefetch Mechanism. The Execution Unit contains the PDP-11 general purpose registers, eight scratch registers, the ALU, a shifter/swapper and shift register, and necessary word/byte multiplexors. The Memory Management Unit contains the relocation registers, FP-11 floating point accumulators, the relocation logic, and the error status registers. The Prefetch Mechanism contains a virtual program counter (VPC), a relocated version of the PC, a prefetch buffer, and various status flags. The Data chip performs all arithmetic and logic functions, handles all data and address transfers including relocation, and operates most of the signals used for interchip communications and system timing.

The Data chip is designed to work with a cached or cacheless memory system. A cached memory system will yield the highest performance  $J\!-\!11$  system; a cacheless memory system will result in the lowest cost  $J\!-\!11$  system.

The Data chip receives microinstructions from the Control chips over the bidirectional Microinstruction Bus (MIB-H).

Note: The equations in this specification are meant to be interpreted as logic, irrespective of polarity, and not as levels.

#### 1.4 Internal Busses

The Data chip is organized around the following internal busses:

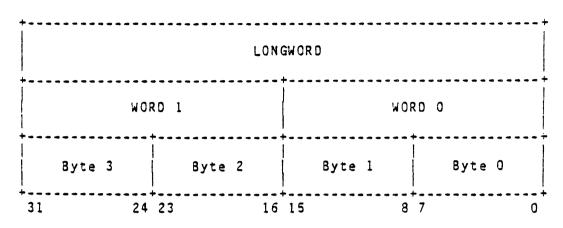

- The A-bus (A<31:0>) interconnects the A-port of the EU register file, the A-input of the ALU, the shift register (SR), and the I/O multiplexor. Data flows both into and out of the EU register file on the A-bus; hence, the A-bus is bidirectional. Most microinstructions place EU register file data on the A-bus during the first part of the microcycle. This supplies the A-input to the ALU or, for address microinstructions, a virtual address to the I/O multiplexor. The output of the I/O multiplexor is driven onto the A-bus during the second part of the microcycle. This supplies the write data to the EU register file.

- The B-bus (B<31:0>) interconnects the B-port of the EU register file, the decimal adjust logic, the literal generation logic, the sign extension logic, and the B-input of the ALU. The ALU B-input is, always the B-bus destination; hence, the B-bus is unidirectional. Most microinstructions place EU register file data on the B-bus during the first part of the microcycle. Decimal adjust microinstructions place a decimal constant on the B-bus; literal microinstructions, a byte wide literal.

- The S-bus (S<31:0>) connects the output of the ALU to the input of the shifter/swapper.

- The F-bus (F $\langle 31:0 \rangle$ ) connects the output of the shifter/swapper to the input of the I/O multiplexor.

- The MMU data bus (M<21:0>) connects the I/O multiplexor to the MMU. The MMU register file, the adder input latch, the address adjust logic, the special MMU registers, the virtual program counter (VPC), the physical program counter (PPC), the output latch, and other MMU logic functions all connect to the M-bus. The M-bus is used for internal data transfers between the MMU and EU register files, for address relocation operations, and for explicit MMU register access.

- The MMU decode bus (D<7:0>) drives the MMU register file decoder. The D-bus is driven directly from the microinstruction during microcode access, from the explicit address logic during explicit access, and from the microinstruction and the incoming virtual address during relocation access.

- The fast A-bus (FA<15:13>) is a high-speed connection between A<15:13> and D<2:0>. This time-critical path is needed to meet the access budget of the MMU register file during data stream relocation. The bus data is always the high-order three bits of a virtual address.

## 1.5 Major States

At its maximum operation frequency (20 Mhz), the Data chip can potentially enter a new state every 25 nsec. The major states in a microcycle are as follows:

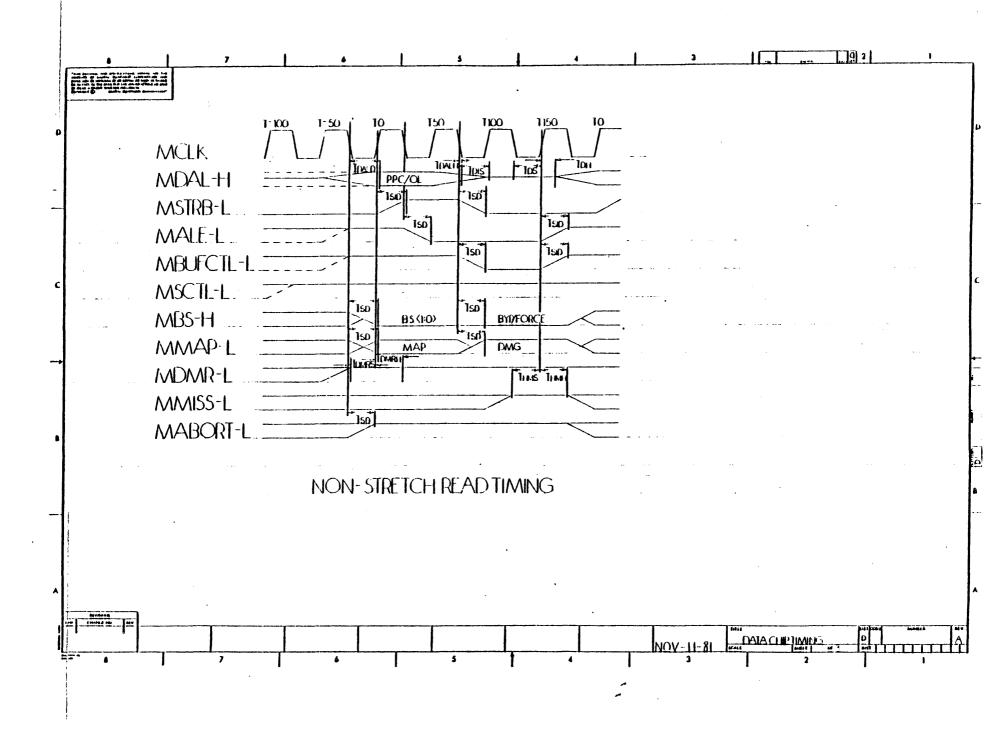

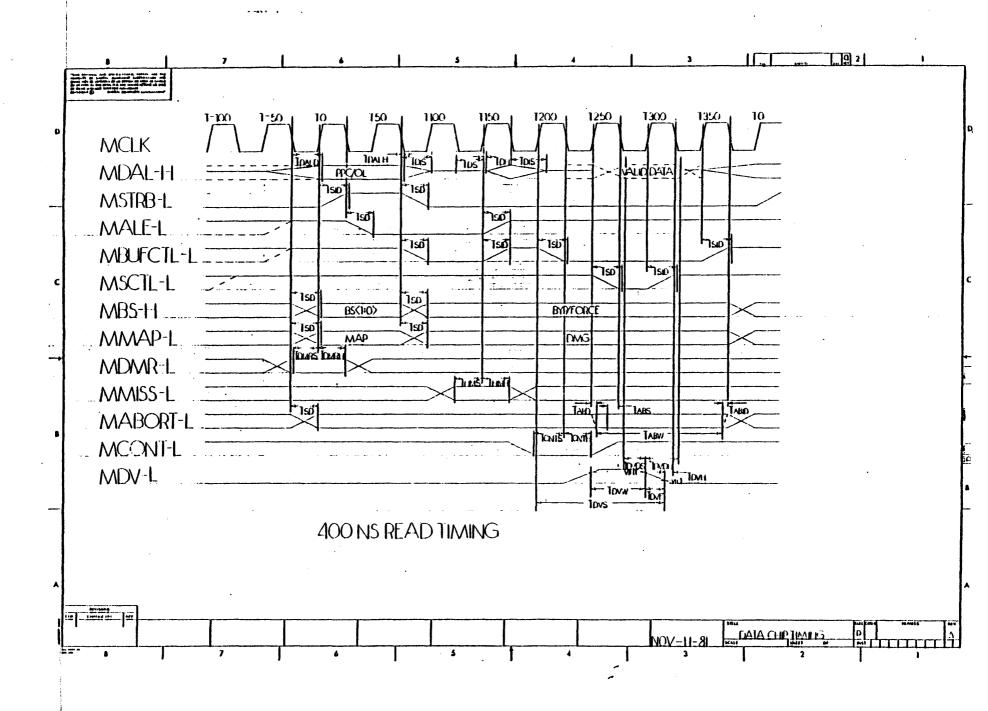

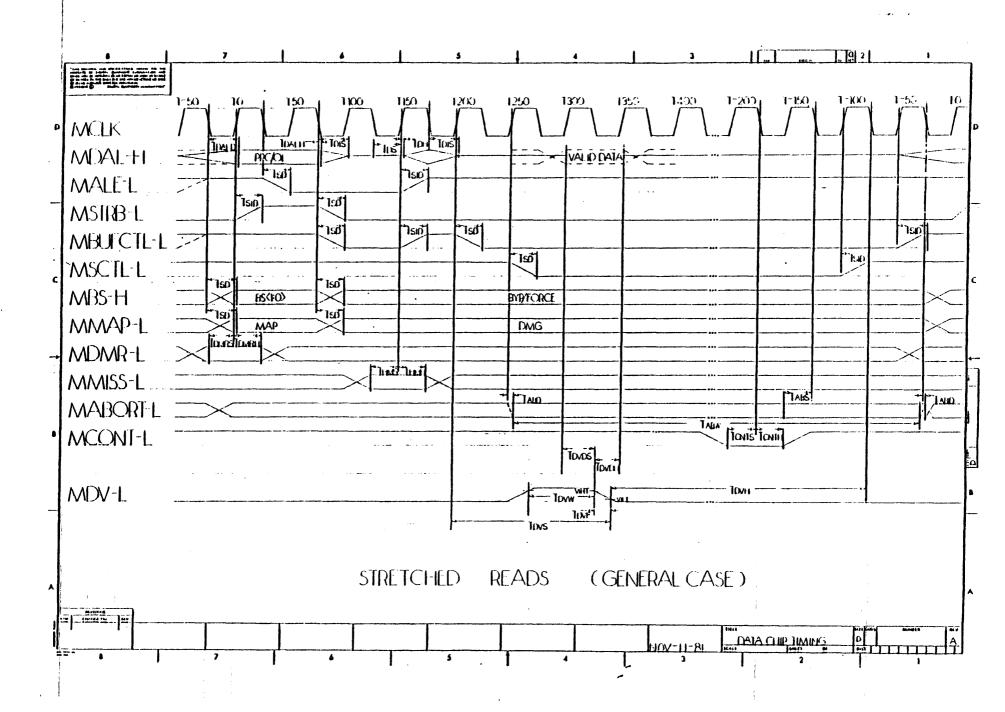

| State | Time     | Applicable<br>Cycles                           | Action                                                                                                                                                                                                                                                                    |

|-------|----------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТО    | O msec   | all                                            | Precharge EU and MMU register files Clock MDMR-L synchronizer                                                                                                                                                                                                             |

| T25   | 25 nsec  | all                                            | Start EU register file access<br>Assert MALE-L                                                                                                                                                                                                                            |

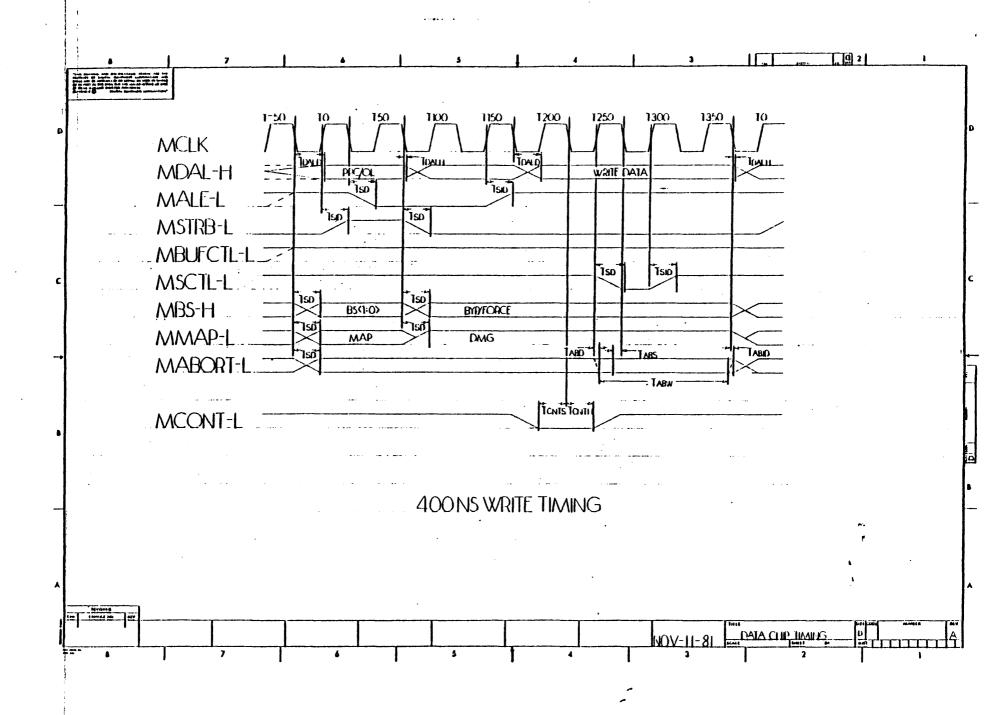

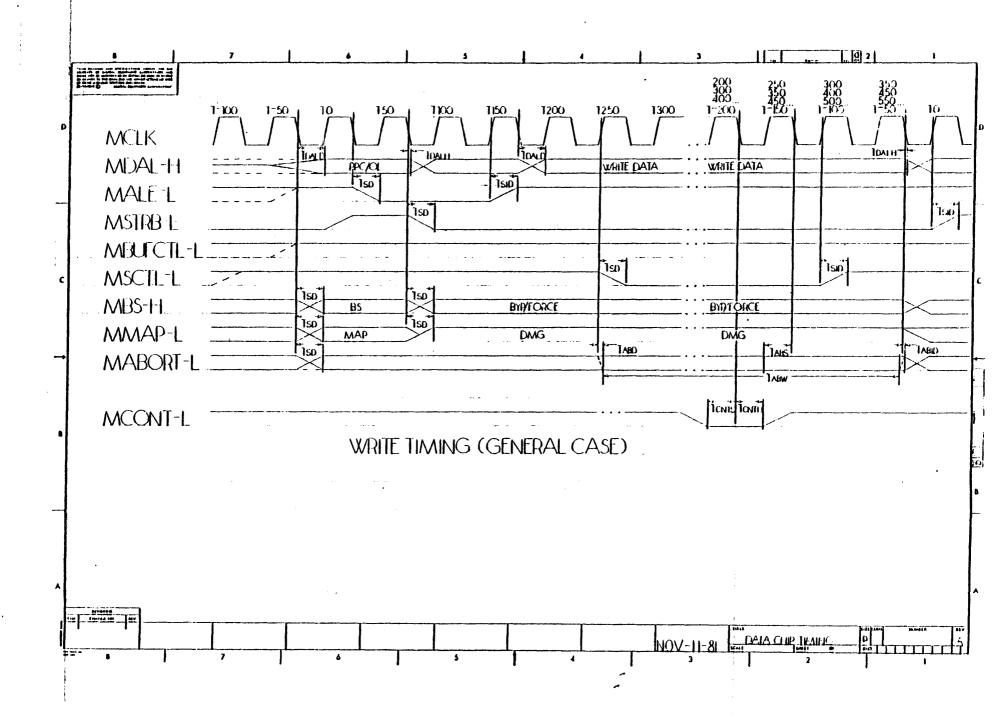

| T75   | 75 nsec  | all all read relocation or expl access all all | Start ALU operation Strobe MPRDC-L Assert MSTRB-L Assert MBUFCTL-L Start MMU register file access Drive MBS-H<1:0> from cache bypass status and CCR<3> + CCR<2> Drive MMAP-L with DMA grant derived from output of MDMR-L synchronzier  Drive ALU status onto MDAL<21:16> |

| T125  | 125 nsec | relocation                                     | Start relocation add/compare                                                                                                                                                                                                                                              |

| T150  | 150 nsec | read all read mem I/0                          | Latch selected input latch<br>from MDAL-H<15:0><br>Deassert MALE-L<br>Deassert MBUFCTL-L<br>Strobe MMISS-L                                                                                                                                                                |

| T175  | 175 nsec | prefetch<br>other relocation<br>or output      | Latch PPC<br>Latch output latch                                                                                                                                                                                                                                           |

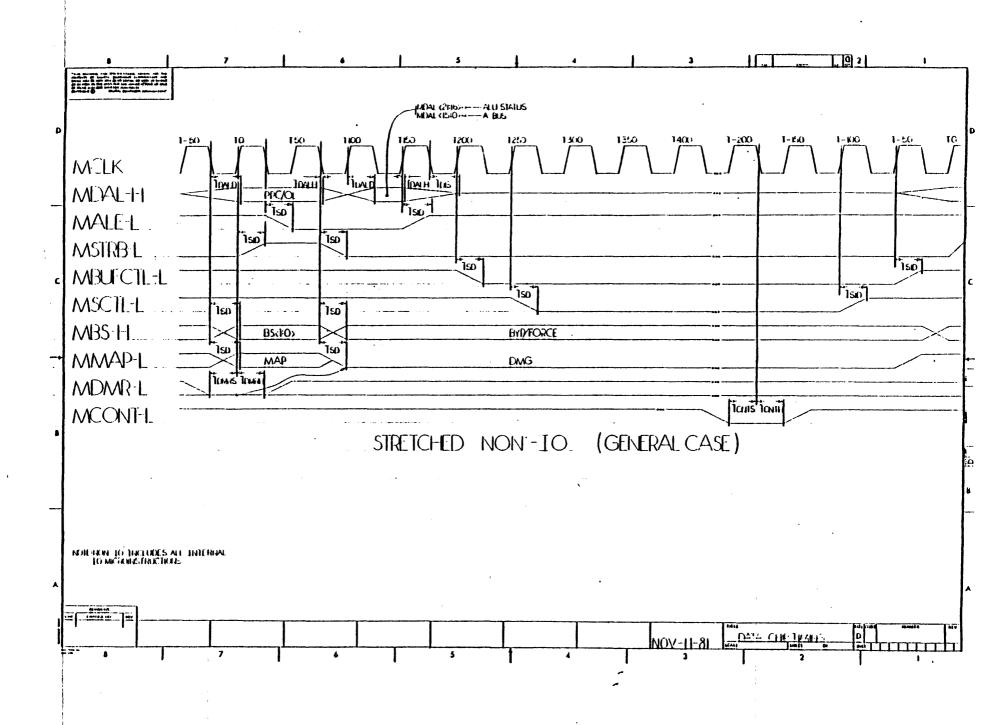

If the microcycle is not extended, T175 coincides with T-25. If the microcycle is extended, operations proceed as follows:

| microc       | yole is extended,                         | operations proceed     | as tollows:                                                                                                                                 |

|--------------|-------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| <u>State</u> | Time                                      | Applicable<br>Cycles   | Action                                                                                                                                      |

| T200         | 200 ns                                    | extended<br>non-writes | Assert MBUFCTL-L                                                                                                                            |

| Tx25         | 225, 325, ms                              | all extended           | Clock MCONT-L synchronizer flip-flop                                                                                                        |

| T250         | 250 ns                                    | all extended           | Assert MSCTL-L                                                                                                                              |

| Tx50         | 250, 350, ns                              | all extended           |                                                                                                                                             |

| Tx75         | 275, 375, ns                              | all extended           | Clock MCONT-L holding flip-flop                                                                                                             |

| Tx00         | 300, 400, ns                              | all extended           |                                                                                                                                             |

| All mi       | crocycles conclud                         | e as follows:          |                                                                                                                                             |

| <u>State</u> | Time                                      | Applicable<br>Cycles   | Action                                                                                                                                      |

| T-100        | 300,.400, ns                              | all extended           | Deassert MSCTL-L                                                                                                                            |

| T-50         | 350, 450, ns                              | extended non-writes    | Deassert MBUFCTL-L                                                                                                                          |

| T-25         | 175 ns if not extended, else 375, 475, ns |                        | Latch MIR from MIB-H<21:0> Write EU register file Drive MDAL-H<21:0> from PPC or output latch Drive MBS-H<1:0> from PCS<3:2> or bank select |

TEND 200 ns if not all

extended, else 400, 500, ... ns

Deassert MSTR8-L

Drive MMAP-L from MMR3<5> Drive MABORT-L from PCS<0> or abort latch

latches

#### 2.0 EXECUTION UNIT (EU)

The Execution Unit contains the main register file, special 8-bus logic, the data path proper, branch/jump logic, the interface to the external MDAL bus, the Microinstruction Register, and the state sequencer.

#### 2.1 Register File

#### 2.1.1 Physical Organization

The EU register file is organized in two sections. The first section is 18 registers deep by 16 bits wide. The second section is 9 registers deep by 32 bits wide. The 18 by 16 section contains two sets of PDP-11 general registers (RO-R5, RO'-R5'), three stack pointers (KSP, SSP, USP), the Processor Status Register (PS), the Program Counter (PC), and Memory Management Register 2 (MMR2). The 9 by 32 section contains the Instruction Register (IR) and its field extractor, and eight scratch registers for microcode use.

The registers in the EU file (except for MMR2 and the IR) are dual ported. In any microcycle, an EU register can be accessed through both the A-port (which is read/write) and the B-port (which is read only). The A-port connects to the A-bus and thence to the data path, the B-port to the B-bus. The A-port of the register file is also connected to the I/O multiplexor which interfaces the EU to the external MDAL bus. Thus the contents of the EU registers can be modified from or written out to the external system bus.

Note that MMR2 is read only and can be accessed only through the B-port.

The 18 by 16 register area is organized as follows:

| User S | stack Pointer (USP) |

|--------|---------------------|

| R5'    | 3                   |

| R4'    |                     |

| R3'    |                     |

| R2'    |                     |

| R1'    |                     |

| RO'    |                     |

| R 5    |                     |

| R 4    |                     |

| R3     |                     |

| R2     |                     |

| R1     |                     |

| RO     |                     |

1.

| The | 9 | bv | 32 | register | area | is | organized | as | follows: |

|-----|---|----|----|----------|------|----|-----------|----|----------|

|-----|---|----|----|----------|------|----|-----------|----|----------|

| 31          | 16 | 15<br>+           | . 0 |

|-------------|----|-------------------|-----|

| Instruction |    | IR Field Extracto | r   |

| Scratch RF  |    |                   |     |

| Scratch RE  |    |                   |     |

| Scratch RD  |    |                   |     |

| Scratch RC  |    |                   |     |

| Scratch RB  |    |                   |     |

| Scratch RA  |    |                   |     |

| Scratch R9  |    |                   |     |

| Scratch R8  |    |                   |     |

The Instruction Register (IR) connects to bits  $\langle 31:16 \rangle$  of the A-port and, through the field extractor, to bits  $\langle 15:0 \rangle$  of the B-port.

## 2.1.1.1 32-bit Scratch Registers

The scratch registers are accessible only from the microcode. Their state at power up is  ${\tt UNDEFINED}.$

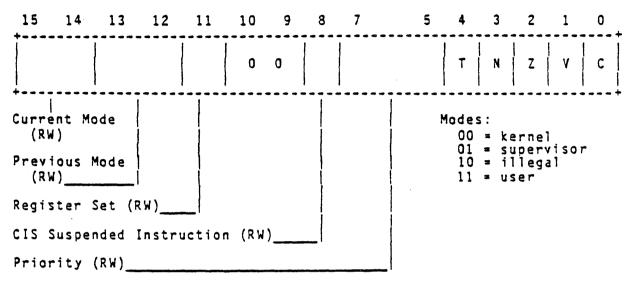

## 2.1.1.2 PDP-11 General Registers (Rn, Rn')

There are two sets of general registers in the register file. The register set information in the PS (bit<11>) defines which set is selected. PS<11> = 0 selects RO - R5; PS<11> = 1 selects RO' - R5'. The microcode can access only the selected register set.

The state of the PDP-11 general registers at power up is UNDEFINED.

#### 2.1.1.3 Stack Pointers (SP)

There are three stack pointer registers in the register file to support the three processor modes (kernel, supervisor, user). The User Stack Pointer (USP) is used for stack references in user mode. The Supervisor Stack Pointer (SSP) is used for stack references in supervisor mode. The Kernel Stack Pointer (KSP) is used for kernel mode stack operations. The current mode field in the PS (bits(15:14>) selects the stack pointer, to be used for the execution of all microinstructions except MOVPM. This microinstruction uses the previous mode field of the PS (bits(13:12>) to select the stack pointer. The microcode can access only the selected stack pointer.

If the mode field used to access the stack pointer specifies the illegal mode (= 10), the USP is selected.

The state of the stack pointers at power up is UNDEFINED.

### 2.1.1.4 Program Counter (PC)

The Program Counter is useable as a general purpose register in macro code (R7). It can also be incremented by 2 independently of the EU data path. This operation automatically happens during an RDI microinstruction or when a predecode (MPRDC-L) signal is received from the Control chip.

The state of the program counter at power up is UNDEFINED.

#### 2.1.1.5 Memory Management Register 2 (MMR2)

MMR2 is a read-only register used to recover from memory management errors. If MMRO $\langle 15:13\rangle$  = 000 and if either the predecode signal (MPRDC-L) is received or the current microinstruction is RDF, the Data chip loads the unincremented contents of the PC into MMR2.

MMR2 can be read as an explicit memory location (17777576/7). It can also be read by microcode as an entry in the EU register file.

The state of MMR2 at power up is UNDEFINED.

2.1.1.6 Processor Status Register (PS)

#### 2.1.1.6.1 Register Format

The PS has dedicated fields which are independently accessed in complex ways:

The PS can be accessed as an explicit location (17777776/7). It can also be accessed by microcode as an entry in the EU register file. The current mode (PS<15:14>) and previous mode (PS<13:12>) fields, as well as the register set select (PS<11>), are used by the EU and MMU register decoders in register access and relocation operations. Furthermore, the PS condition codes (N, Z, V, C) can be set by the microcode and reflect the results of an ALU operation. If the PS is written both explicitly (i.e., as a memory location) and implicitly (i.e., update condition codes) in the same microcycle, the PS condition codes (bits<3:0>) are set from the memory data, rather than from the EU status flags. Explicit and microcode PS references do not always completely overwrite the register. Table 2-1 summarizes the protection of the PS in various modes:

Table 2-1 PS PROTECTION

| Access Method | Protection Mechanism | Protection                                                                                |

|---------------|----------------------|-------------------------------------------------------------------------------------------|

| vector read   | PS protection logic  | PS<13:12> set from PS<15:14>                                                              |

| RTI/RTT read  | PS protection logic  | In supervisor or user mode, PS<15:11> are ORed with new value; PS<7:5> can not be altered |

٠,

explicit write PS protection logic PS<4> can not be altered

MTPS microcode In supervisor or user mode,

PS<7:5> cannot be altered; PS<15:8.4> can not be altered

console write microcode PS<4> can not be altered

power up microcode PS set to predefined value

#### 2.1.1.6.2 PS Protection Logic

The PS protection logic handles protection of the PS. There are three distinct functions:

- Vector-to-PS protection

- RTI/RTT-to-PS protection

- Explicit write protection

Vector-to-PS protection is activated by a RD or RMW microinstruction with control bit $\langle 10 \rangle$  = 0. RTI/RTT-to-PS protection is activated by a RD or RMW microinstruction with control bit $\langle 9 \rangle$  = 0. In both cases, the destination register (Ra) should be PS. Explicit write protection is activated by an external write to the explicit PS address (17777776/7).

If vector-to-PS protection is specified, bits<15:14,11,8:0> of the input data are directly transferred to Ra. Bits<13:12> of the input, however, are suppressed, and the old contents of Ra<15:14> are transferred to Ra<13:12>. The microcode must guarantee that Ra=PS to protect the PS.

If RTI/RTT-to-PS protection is selected, the action taken depends on the current memory management mode. If the current mode is kernel, bits  $\langle 15:11,8:0\rangle$  of the input data are directly transferred to Ra. If the current mode is supervisor or user, only bits  $\langle 8,4:0\rangle$  of the input are directly transferred to Ra. Of the remaining bits, Ra  $\langle 7:5\rangle$  are not modified. Input bits  $\langle 15:11\rangle$  are first ORed with the old value of Ra  $\langle 15:11\rangle$  and then are written into Ra. The microcode must guarantee that Ra=PS to protect the PS.

Finally, on an explicit write to PS, bits<15:11,8:5,3:0> of the input are directly transferred to PS. PS<4> is not modified. Register Ra is also written with the same data. An explicit write may write only a byte of the PS.

A summary of the PS protection logic is given in Table 2-2.

Table 2-2 PS PROTECTION LOGIC

| PS Write<br>Data            | Yector-<br>to-PS | RTI/RTT<br>User/Super        | RTI/RTT<br>Kernel | Explicit<br>Write |

|-----------------------------|------------------|------------------------------|-------------------|-------------------|

| Cond.<br>Codes<br>(3:0)     | input<3:0>       | input<3:0>                   | input<3:0>        | input<3:0>        |

| Trap <4>                    | input<4>         | input<4>                     | input<4>          | PS <4>            |

| Priority <7:5>              | input<7:5>       | Ra<7:5>                      | input<7:5>        | input<7:5>        |

| Instr.<br>Suspen.<br><8>    | input<8>         | input<8>                     | input<8>          | input<8>          |

| Register<br>Set <11>        | input<11>        | input<11><br>OR Ra<11>       | input<11>         | input<11>         |

| Previous<br>Mode<br><13:12> | Ra<15:14>        | input<13:12><br>OR Ra<13:12> | input<13:12>      | input<13:12>      |

| Current<br>mode<br><15:14>  | input<15:14>     | input<15:14><br>OR Ra<15:14> | input<15:14>      | input<15:14>      |

#### 2.1.1.7 PDP-11 Instruction Register (IR)

#### 2.1.1.7.1 Instruction Register

The Instruction Register (IR) is automatically loaded from the prefetch buffer at the end of a microcycle in which the predecode signal (MPRDC-L) is asserted. It can be accessed through the B-port using the IR field extractor (see below), or through the A-port as a high-word scratch register. The extractor is activated by any microinstruction which specifies the IR as the B-port operand. Its action is controlled by the microinstruction. AOBC and SOBC extract a subfield of the IR. All other microinstructions access the entire IR.

The IR serves several purposes in the Data chip. Bits<7:0> contain the PC offset for all macro-branch instructions. Bits<5:0> hold data for the SOB and MARK macroinstructions. The PC offset, SOB offset, and MARK data are accessed through the IR field extractor.

## 2.1.1.7.2 Shadow Instruction Register (SIR)

The Shadow Instruction Register copies bits<15,10:6,2:0> from the prefetch buffer on a predecode. It is also loadable by microcode with an OUTR microinstruction with control code 207 from register Ra. The SIR serves several purposes in the Data chip. Bits<8:6> and <2:0> are used to indirectly address PDP-11 general registers in the EU register file. Bits<7:6> and <2:0> are used to indirectly address floating point accumulators in the MMU register file. Bits<15,10:8> are used to interrogate the condition codes in the PS for the PDP-11 macro-branch instructions.

#### 2.1.1.7.3 IR Field Extractor

The IR field extractor connects the IR to the B-port of the EU register file. The field extractor is activated by any microinstruction which specifies the IR as the B-port operand. The action of the field extractor is controlled by the microinstruction. Table 2-3 summarizes the actions performed by the IR field extractor.

1.1

|       | Table   | 2-3 |        |

|-------|---------|-----|--------|

| FIELD | EXTRACT | OR  | ACTION |

| MACRO CODE                                                                         | MICROINSTRUCTION | B-BUS RESULT                                    |

|------------------------------------------------------------------------------------|------------------|-------------------------------------------------|

| BR, BNE, BEQ, BGE,<br>BLT, BGT, BLE, BPL,<br>BMI, BHI, BLOS, BVC,<br>BVS, BCC, BCS | AOB C            | B<8:1> < IR<7:0><br>B<0> < 0<br>B<15:9> < IR<7> |

| MARK, SOB                                                                          | SOBC             | B<6:1> < IR<5:0><br>B<0> < 0<br>B<15:7> < 0     |

| all others                                                                         | all others       | 8<15:0> < IR<15:0>                              |

#### 2.1.2 Decode and Access

All the registers in the EU can be accessed from the microcode. In addition, MMR2 and PS can be accessed explicitly as memory locations.

#### 2.1.2.1 Microcode Access

The microcode can always access the 32-bit scratch registers, PC, MMR2, and PS, but can only access the selected stack pointers and general register set. Selection of the stack pointer is determined by the current processor mode (PS<15:14>, except for MOVPM); of the general register set, by the register set select (PS<11>).

Except for MMR2 and the IR, the EU registers are dual ported. Access to the EU registers through the A-port and the B-port is controlled by bits(4:0) and bits(9:5), respectively, of the microinstruction. The codes in these register select fields provide for direct addressing of all the selected EU registers and indirect addressing of the selected general register set, selected stack pointer, and PC by the two register designator fields of the PDP-11 instruction. Register select information is latched and held constant for the duration of the cycle to prevent incoming information for the next microcycle from altering register selection. The register select codes are given in Table 2-4. Note that A- and B-port select codes are not equivalent. Note also that the IR field extractor is single ported since it is not accessible on the A-port.

When sixteen-bit registers are accessed on the B-bus, B-bus bits<31:16> are forced to zero; when read out on the A-bus, A-bus bits<31:16> contain the IR.

Table 2-4

EU REGISTER ACCESS CODES

| Access<br>code                                                       | Rb<31:16>                                                                                   | selects<br><u>Rb&lt;15:0&gt;</u>                                                                             | Ra<31:16>                                                             | Ra<15:0>                                                        | Notes                                     |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------|

|                                                                      | Rb<31:16>  0 0 0 0 RE RF 0 0 R8 R9 RA RB RC RD RE                                           | Rb<15:0>  PS IR field extractor MMR2 RS OR 1 RE RF Rd RS R8 R9 RA RB RC RD RE RF R0 R1                       | Ra<31:16>  IR IR IR IR IR IR IR RE IR IR R8 R9 RA RB RC RD RE RF IR   | Ra<15:0> PS PS PS RSE RC RS | 1 2 3 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 |

| 21<br>22<br>23<br>24<br>25<br>26<br>27<br>31<br>33<br>33<br>35<br>37 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | R 2<br>R 3<br>R 4<br>R 5<br>R 6<br>R 7<br>R 8<br>R 8<br>R C<br>R C<br>R C<br>R C<br>R C<br>R C<br>R C<br>R C | IR<br>IR<br>IR<br>IR<br>IR<br>IR<br>IR<br>R9<br>R8<br>RCD<br>RF<br>RF | R R R R R R R R R R R R R R R R R R R                           |                                           |

Note 1 - Rs OR 1 - select Rn, n = (SIR < 8:6 > OR 1).

Note 2 - Rd - select Rn, n = SIR(2:0).

Note 3 - Rs - select Rn, n = SIR <8:6>.

Note 4 - Affects operation of ALU, I/O mux, write amplifiers, otherwise same as 30-37.

#### 2.1.2.2 Explicit Access

MMR2 and PS can be explicitly accessed, byte or word, as memory locations. Table 2-5 lists the explicit addresses of these registers:

## Table 2-5 EXPLICITLY ADDRESSABLE EU REGISTERS

| Name | Address    | Special Requirements                 |

|------|------------|--------------------------------------|

| PS   | 17777776/7 | PS<4> not modified by explicit write |

| MMR2 | 17777576/7 | Read only                            |

Selection of these registers is detected by the MMU address adjust and detect logic.

## 2.1.3 Register Read Operations

The EU register file places data on both the A-bus and the B-bus during a microinstruction. Some microinstructions, however, substitute other information on the B-bus or modify the B-bus data:

- Execution of a literal microinstruction places a literal generated from bits<12:5> of the microinstruction on the B-bus (see section 2.2.1).

- Execution of a decimal adjust microinstruction places data from the decimal adjust logic on the B-bus (see section 2.2.2).

- Execution of a MOVS microinstruction sign extends bit<7> of the B-bus through bits<31:8> (see section 2.2.3).

#### 2.1.4 Register Write Operations

The EU register file is written by four sets of write amplifiers (one set per byte) through the A-port only. Since file writing is only permitted for certain microinstructions, and even then sometimes on a per word or per byte basis only, the write amplifier sets can selectively write any of the four bytes of the destination register. When some of the write amplifer sets are disabled, the associated byte or bytes in the destination register are not altered.

11

Operation of the write amplifier sets is controlled by the microinstruction decode and, for references to the 32-bit scratch registers, by the A-port register select code. The microinstruction decode detects if the EU data path output is to be written back to the A-port, the operand length, and any special conditions which control the action of the write amplifier sets. The A-port select code controls which half of a 32-bit register is overwritten. This is illustrated below:

Table 2-6 OPERATION OF WRITE AMPLIFIERS

| Microinstruction<br>Length Field | A-port Select<br>Code <4:0>                      | Microinstruction | Bits Written                          |

|----------------------------------|--------------------------------------------------|------------------|---------------------------------------|

| byte .                           | 00XXX + 1XXXX<br>00XXX + 1XXXX<br>01XXX<br>01XXX | SWAB.B + LLSW.B  | <7:0><br><15:8><br><23:16><br><31:24> |

| word                             | OOXXX + 1XXXX<br>O1XXX                           | any<br>any       | <15:0><br><31:16>                     |

| longword                         | any                                              | any              | <31:0>                                |

On both MMU and bus read aborts, the original contents of the registers are preserved.

Note that if MPROC-L is asserted, the write amplifiers for bits<31:16> are automatically enabled to write the IR, irrespective of the microinstruction.

#### 2.2 Special B-bus Logic

Normally, the EU data path inputs are the A-port and B-port outputs of the EU register file. However, certain microinstructions place different information on or modify the B-bus input.

#### 2.2.1 Literal Generation Logic

During execution of any literal microinstruction, this logic disconnects the B-port of the EU register file from the B-bus and generates a 32-bit operand for the B-bus from the 8-bit literal field in the microinstruction. The 8-bit literal (bits<12:5> of the microinstruction) is copied to bits<7:0> of the B-bus. Bits<31:8> of the B-bus are zeroed.

#### 2.2.2 Decimal Adjust Logic

A decimal adjustment is required before and after a BCD operation because only binary arithmetic can be performed in the EU data path. Prior to any BCD addition, 6 is added to each of the nibbles in one of the operands. This is accomplished with a PDAD microinstruction. PDAD disconnects the B-port of the EU register file from the B-input of the EU data path, inserts the constant 666666666 (hexidecimal) on the B-input, and adds it to the A-port operand, forming the preadjusted result. Prior to any BCD subtraction, the subtrahend is one's complemented. This is accomplished with a normal COM microinstruction.

After preadjustment, the BCD operation is performed as a binary addition and the carry-out from each nibble is saved. A post-adjustment (invoked by a DADP microinstruction) is then executed to recover the final BCD answer. Specifically, a BCD correction constant is formed - nibble by nibble - on the B-input and is added (with a carry-in to the least significant bit of the addition operation) to the intermediate BCD result yielding the corrected BCD result. Each nibble BCD correction constant is either a 9 or F (hexidecimal) and is selected by the state of its saved carry-out from the binary add. If there was a carry-out, the constant F is used. Conversely, no carry-out results in the constant 9. The following example demonstrates the BCD capabilities of the Data chip:

Example: BCD Addition Capability

Operand A: 0 0 0 1 9 3 4 6

Operand 8: 0 0 1 2 4 6 8 0

NOTE: All numbers are hexidecimal nibbles.

Step 1: Preadjust Operand (PDAD)

0 0 0 1 9 3 4 6

6 6 6 6 6 6 6

6 6 6 7 F 9 A C Preadjusted result

Step 2: Binary Addition and Save Carries (Add)

6 6 6 7 F 9 A C

0 0 1 2 4 6 8 0

6 6 7 A 4 0 2 C Intermediate result

0 0 0 0 1 1 1 0 Saved carry out

٠,

## Step 3: Post-adjustment (DADP)

## 2.2.3 Sign Extension Logic

The sign extension logic modifies the data on the B-bus by sign extending the low order byte to 32 bits. The MOVS microinstruction sign extends the low order byte.

#### 2.3 EU Data Path Components

The EU data path performs the arithmetic and logical operations in the Data chip. It consists of an arithmetic and logic unit (ALU), a combination bit shifter and byte swapper, and a shift extension register. The inputs to the ALU are the A-bus (A<31:0>) and B-bus (B<31:0>), which are usually driven by the A-port and B-port, respectively, of the EU register file. The output of the ALU connects to the shifter/swapper over the S-bus (S<31:0>). The output of the shifter/swapper connects to the I/O multiplexor over the F-bus (F<31:0>).

The operation of the EU data path is determined by the current microinstruction.

## 2.3.1 EU Data Path Functions

## 2.3.1.1 Operations

The EU data path is capable of the following operations:

- logical operations on two operands

- binary addition, with optional carry in

- binary subtraction, with optional borrow in

- left shift one bit, with optional carry in

- right shift one bit, with optional carry in

- byte swap within words

- byte shift left or right one bit followed by byte swap (low order word only)

- conditional add/subtract/negate

- combined conditional add/subtract and shift

- decimal adjustment

For further details, see section 5.0, Microinstructions.

#### 2.3.1.2 Data Flow

Data flow within the EU data path depends on the microinstruction being executed, the length (byte/word/longword) of the operation being performed, and, for operations on the 32-bit scratch registers, the A-port and B-port register select codes. For the microinstructions which do not have a B-port register select field, the EU data flow behaves as if the B-port code is OOXXX + IXXXX. This is summarized in Table 2-7.

Table 2-7 EU DATA FLOW

| Length field | B-port<br>code <9:5>                         | A-port<br>code <4:0>                         | Micro-<br>instruction              | Effective operands                     | Store<br>in                            |

|--------------|----------------------------------------------|----------------------------------------------|------------------------------------|----------------------------------------|----------------------------------------|

| byte         | 00XXX+1XXXX                                  | 00XXX+1XXXX                                  | -(SWAB.B+LLSW.B)<br>SWAB.B+LLSW.B  | <7:0><br><7:0>                         | <7:0><br><15:8>                        |

|              | 00XXX+1XXXX                                  | Olxxx                                        | -(SWAB.B+LLSW.B)<br>SWAB.B+LLSW.B  | <7:0><br><7:0><br><7:0>                | <23:16><br><31:24>                     |

|              | Olxxx                                        | 00XXX+1XXXX                                  | - (SWAB.B+LLSW.B)<br>SWAB.B+LLSW.B | <23:16><br><23:16>                     | <7:0><br><15:8>                        |

|              | Olxxx                                        | OIXXX                                        | - (SWAB.8+LLSW.B)<br>SWAB.B+LLSW.B | <23:16><br><23:16>                     | <23:16><br><31:24>                     |

| word         | 00XXX+1XXXX<br>00XXX+1XXXX<br>01XXX<br>01XXX | 00XXX+1XXXX<br>01XXX<br>00XXX+1XXXX<br>01XXX | any<br>any<br>any<br>any           | <15:0><br><15:0><br><31:16><br><31:16> | <15:0><br><31:16><br><15:0><br><31:16> |

| longword     | an'y                                         | any                                          | any                                | <31:0>                                 | <31:0>                                 |

#### 2.3.1.3 Status Flags

AN, AV, AZ, and AC are the local EU data path status flags. They are updated at the conclusion of an EU data path operation. Depending on instruction type, they may be set or cleared unconditionally, or affected conditionally to give additional information about the operation just completed. In the latter case, they generally have the following meaning:

AN=1: result is negative

=0: otherwise

AZ=1: result is zero

=0: otherwise

AV=1: operation results in an arithmetic overflow

=0: otherwise

AC=1: non-subtract operation results in a carry;

subtract-type operation does not result in a carry

=0: otherwise

The derivation of the status flags depends on the microinstruction being executed, the length of the operation being performed, and, for operations on the 32-bit scratch registers, the A-port register select code. This is detailed in Appendix 8 (Condition Code Equations) and summarized in Table 2-8.

Table 2-8

STATUS FLAGS DERIVATION

| Microinstruction length field | A-port select code <4:0> | Microinstruction                                                               | Normally<br>AN,AZ<br>from A            | derive<br>AV,AC<br>from Cin/out |

|-------------------------------|--------------------------|--------------------------------------------------------------------------------|----------------------------------------|---------------------------------|

| byte                          | OOXXX + 1XXXX<br>O1XXX   | -(SWAB.B + LLSW.B)<br>SWAB.B + LLSW.B<br>-(SWAB.B + LLSW.B)<br>SWAB.B + LLSW.B | <7:0><br><15:8><br><23:16><br><31:24>  | <7> na <7> na                   |

| word.                         | OOXXX + 1XXXX<br>O1XXX   | -(SWAB.W + LLSW.W) SWAB.W + LLSW.W) -(SWAB.W + LLSW.W) SWAB.W + LLSW.W         | <15:0><br><15:8><br><31:16><br><31:24> | <15><br>na<br><15><br>na        |

| longword                      | any                      | any                                                                            | <31:0>                                 | <31>                            |

Note that the AV status flag can reflect multi-bit left shift operations, and the AZ flag can be used for multi-word zero testing. Section 2.3.1.4 details multi-bit shifting and multi-word zero testing.

The four local status flags are conditionally written under microprogram control into the PS condition codes at the end of the microcycle.

#### 2.3.1.4 Extended Status Testing

The EU data path supports multi-word zero testing. The multi-word microinstructions ADDC, SUBC, and NEGC affect the local AZ status flag as follows:

AZ = 0 if result not equal to 0 = Z otherwise

That is, AZ is cleared if the result is non-zero; otherwise it is copied from the PS Z flag.

The EU data path also supports multi-bit shift overflow testing. The data path includes an extra flag called the sticky V flip-flop. This flip-flop is cleared by predecode (MPRDC-L asserted). It is set by any ASL microinstruction which sets AV. It is also an OR input into AV. Thus, once AV is set by an ASL microinstruction, it remains set during subsequent ASL microinstructions until predecode is recognized. If predecode is recognized during an ASL microinstruction, AV is evaluated with the sticky overflow flip-flop (SVFF) before it is cleared.

The EU data path also supports double-precision divide. The data path includes two extra flags called the extended carry flag ( $\rm XC$ ) and the extended rotate flag ( $\rm XR$ ). During an XLDIVS microinstruction, XC captures the carry out of the ALU, and XR the carry out of the shifter. During an XHDIVS, XC supplies the carry into the ALU, and XR the carry into the shifter.

٠,

#### 2.3.2 Arithmetic-Logical Unit (ALU)

The ALU performs the arithmetic, logical, and selected left shift operations in the EU data path. The inputs to the ALU are the A-bus and B-bus; its output is the S-bus. The ALU function is determined by decoding the current microinstruction.

The input operands are fed to the P and G logic to generate the propagate and generate terms for the desired ALU function. The propagate and generate terms are used by the carry logic to derive the carry terms. The carry and propagate terms are XOR'd to yield the result. (Some of the carry terms are also used to control the decimal adjust logic, section 2.2.2.) The low order eight bits of this result are fed to a multiplexor which operates as follows:

| microinstruction         | multiplexor action                                                                                             |   |  |  |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|

| -(ASR.B + ROR.B + LSR.B) | S<7:0> < ALU result<7:0                                                                                        | > |  |  |  |  |  |

| ASR.B                    | S<7> < ALU result<7> S<6:0> < ALU result<7:1: carry out < ALU result<0>                                        | > |  |  |  |  |  |

| ROR.8                    | S<7> < C<br>S<6:0> < ALU result<7:1:<br>carry out < ALU result<0>                                              | > |  |  |  |  |  |

| LSR.B                    | <pre>S&lt;7&gt;      &lt; 0 S&lt;6:0&gt;      &lt; ALU result&lt;7:1: carry out &lt; ALU result&lt;0&gt;</pre> | > |  |  |  |  |  |

The output of the ALU and this multiplexor connect to the shifter/swapper over the S-bus.

#### 2.3.3 Bit Shifter and Byte Swapper

The shifter/swapper receives its input from the S-bus (S<31:0>). It can shift data left or right one bit, and can be used in conjunction with a special shift register (SR) to perform relatively high speed multiplies, divides, and multi-word shifts. It can also swap the bytes within the low word and high word outputs from the ALU. The function performed by the shifter/swapper is determined by the current microinstruction. Note that a byte write to an odd address automatically invokes the byte swap function. Ra<15:8> will get written with the data, not Ra<7:0>.

The inputs to the shifter/swapper consist of the 32-bit ALU result (S<31:0>) and a shift-in signal; the outputs consist of a 32-bit result (F<31:0>) and a shift-out signal. The shifter works with 8, 16, or 32 bit values. This is accomplished by selecting where the shift-out and shift-in are connected to the shifter and SR. Table 2-9 details the functions performed by the shifter/swapper.

Note that the ROL.B and ASL.B microinstructions use an ALU shift to perform the left shift, while the ROR.B, ASR.B, and LSR.B microinstructions use an ALU shift to perform the right shift. This enables a bit shift and byte swap operation during the same microinstruction.

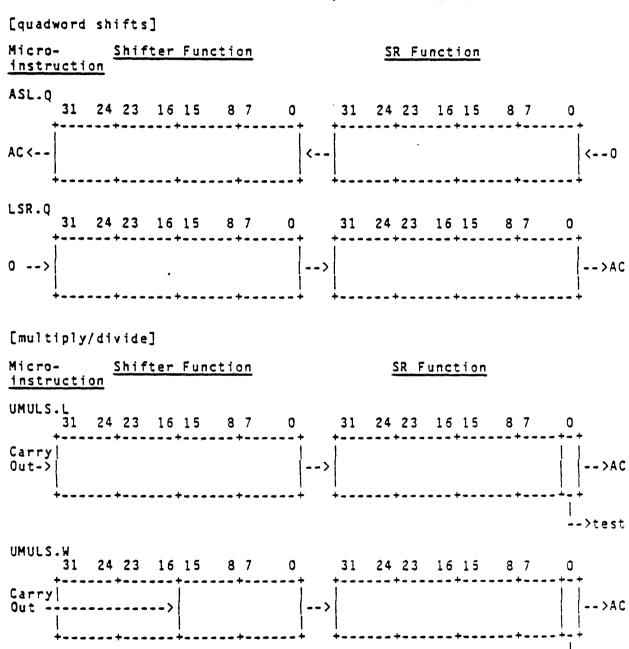

## 2.3.4 Shift Register (SR)

The shift register is a special purpose register used in conjunction with the shifter/swapper. It is addressable via an INPR or OUTR microinstruction with control code 206. This is encoded within the single port select codes shown in Table 3-3. The SR register accelerates the PDP-11 Extended Instruction Set (EIS). In particular, this hardware enables the inner multiply and divide loops to execute at the rate of one microcycle per bit.

The SR is a bidirectional shift register. It can provide the shift-in data to the shifter/swapper and can collect the shift-out data from the shifter/swapper. Furthermore, the EU data path can examine the low order bit in the SR and conditionally execute based on the result.

The SR connects to the A-bus. When written via any length OUTR, all 32 bits are modified according to the following table.

| OUTR.x | [SR,Ra.H] | SR < 0     |             |          |

|--------|-----------|------------|-------------|----------|

| OUTR.B | [SR,Ra.x] | undefined  |             |          |

| OUTR.L | [SR.Ra.L] | SR < Ra    |             |          |

| OUTR.W | [SR.Ra.L] | SR <31:16> | <           | 0        |

|        | • .       | SR <15:0>  | <b>&lt;</b> | Ra<15:0> |

When read via INPR, all 32 bits are read out, although the microinstruction length field controls how many bits are written into the destination (Ra) register.

In summary, the SR is a parallel loaded and read register which is shifted in parallel with the shifter/swapper, can be tested, and is 32 bits wide. Table 2-9 enumerates the operation of the shifter/swapper and the SR.

Table 2-9

DATA CHIP SHIFT/SWAP CAPABILITIES

## [ALU shifts]

| <u>Microinstruction</u> |      |    | ALU   | Shift Fun | ction |      |    |

|-------------------------|------|----|-------|-----------|-------|------|----|

|                         |      | 31 | 24 23 | 16 15     | 8 7   | 0    |    |

| ASL.B                   | AC < |    |       |           |       | < 0  |    |

|                         |      | +  | +     | +         | +     | +    |    |

|                         |      | 31 | 24 23 | 16 15     | 8 7   | 0    |    |

| ROL.B                   | AC < |    |       |           |       | < c  | ι, |

|                         |      | +  | +     | +         | +     | +    |    |

|                         |      | 31 | 24 23 | 16 15     | 8 7   | 0    |    |

| ASR.B                   |      |    |       |           | >     | > AC |    |

|                         |      | +  | +     | +         | +-+   | +    |    |

|                         |      |    |       |           |       |      |    |

|                         |      | 31 | 24 23 | 16 15     | 8 7   | 0    |    |

| ROR.B                   | C    |    |       |           | >     | > AC |    |

|                         |      | ļ  | +     | +         | +     | +    |    |

|                         |      | 31 | 24 23 | 16 15     | 8 7   | o .  |    |

| LSR.B                   | 0    |    |       |           |       | > AC |    |

| L3K • D                 |      | 1  |       |           | /     | / // |    |

Table 2-9 (continued)

DATA CHIP SHIFT/SWAP CAPABILITIES

## [simple shifter/swapper functions]

| Microinstruction | Shifter Function |               |       |         |    |           |          |   |        |    |

|------------------|------------------|---------------|-------|---------|----|-----------|----------|---|--------|----|

|                  |                  | 3             | 1 24  | 23      | 16 | 15        | 8 7      | 0 | _      |    |

| ASL.L            | AC ·             | <             |       | +       |    |           |          |   | <      | 0  |

|                  |                  | 3             | 11 24 | 23      | 16 | 15        | 8 7      | 0 | +      |    |

| ASL.W            | AC ·             | <             |       |         |    |           |          |   | <      | 0  |

|                  |                  | · +-          | 31 24 | 23      | 16 | 15        | 8 7<br>+ | 0 | +<br>+ |    |

| ROL.L            | AC ·             | <             |       |         |    |           |          |   | <      | С  |

|                  |                  | *·            | 31 24 | 23      | 16 | 15        | 8 7      | 0 | +      |    |

| ROL.W            | AC               | <             | ••••• |         |    |           |          |   | <      | С  |

|                  |                  | +-<br>;<br>+- | 31 24 | 23      | 16 | 15        | 8 7<br>+ | 0 | +      |    |

| ASR.L            |                  | >             |       | +       |    |           | +        |   | >      | AC |

|                  |                  |               | •     |         |    |           |          |   |        |    |

|                  |                  | <b>+</b> .    | 31 24 | 23<br>+ | 16 | 15<br>+-+ | 8 7<br>+ | 0 | +      |    |

| ASR.W            |                  |               |       | *       | >  |           | +        |   | >      | AC |

|                  |                  | **            |       | , =     |    |           |          |   |        |    |

Table 2-9 (continued)

DATA CHIP SHIFT/SWAP CAPABILITIES

| Microinstruction  | Shifter Function |          |         |         |          |      |            |   |              |                                       |         |              |    |

|-------------------|------------------|----------|---------|---------|----------|------|------------|---|--------------|---------------------------------------|---------|--------------|----|

|                   |                  |          | 31      | 24      | 23       | 16   | 15         |   | 3 7          |                                       | 0       | L            |    |

| LSR.L             | 0 -              | >        |         |         | <b>+</b> |      | <b>.</b>   |   |              |                                       |         | >            | AC |

|                   |                  | •        | 31      | 24      | 23<br>+  | 16   | 15         |   | 3 7<br>-+-   |                                       | 0       | •            |    |

| LSR.W             | 0 -              | <u> </u> |         | ••••    |          | >    |            |   | - <b>4</b> - |                                       |         | >            | AC |

|                   |                  |          | 31      | 24      | 23       | 16   | 15         |   | 3 7<br>-+-   |                                       | 0       | •            |    |

| ROR.L             | c ·              | >        |         |         | <b></b>  |      | <b>.</b>   |   | - 4 -        |                                       |         | >            | AC |

|                   |                  |          | 31      | 24      | 23       | 16   | 15         |   | 3 7<br>•+-   |                                       | 0       | •            |    |

| ROR.W             | с.               |          |         |         |          | >    |            |   |              |                                       |         | >            | AC |

|                   |                  | ·        | T ·     |         |          |      | T          |   |              |                                       |         |              |    |

|                   |                  |          | 31<br>+ | 24      | 23<br>+  | v 16 | 15<br>+    |   | 8 7<br>-+-   | , , , , , , , , , , , , , , , , , , , | 0<br>:  | <del>+</del> |    |

| SW AB . (L)(W)(B) |                  |          |         |         |          |      |            |   |              |                                       |         |              |    |

|                   |                  |          | T       | 0       |          |      | <b>+</b>   | 0 |              |                                       |         | •            |    |

|                   |                  |          | 31      | 24      | 23       | 16   | 15         |   | 8 7          | •                                     | 0       |              |    |

| XLDIVS            | XR               | <        |         | • • • • | +        |      | <b>+</b> - |   | • <b>+</b> • |                                       | • • • • | <b></b>      | 0  |

|                   |                  |          | T       |         | 7        |      | ~          |   |              |                                       |         | т            |    |

-->test

## Table 2-9 (continued) DATA CHIP SHIFT/SWAP CAPABILITIES

Table 2-9 (continued)

DATA CHIP SHIFT/SWAP CAPABILITIES

# Table 2-9 (continued) DATA CHIP SHIFT/SWAP CAPABILITIES

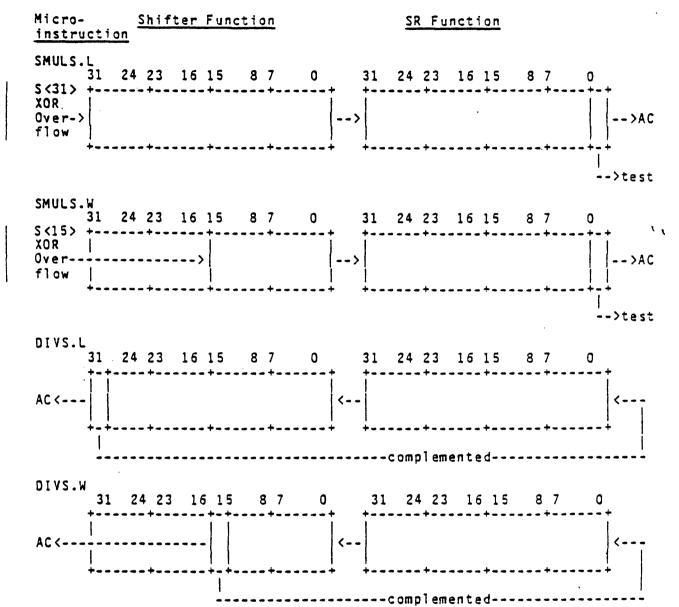

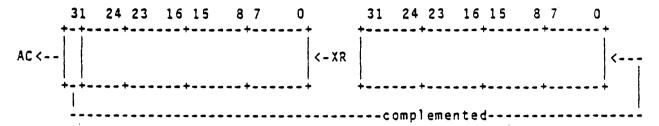

Micro- Shifter Function SR Function instruction

XHDIVS

# 2.4 Branch/Jump Logic

This logic implements both the macro-branch microinstructions (AOBC, SOBC) and the micro-jump microinstructions.

# 2.4.1 Macro-branch Logic

The PS condition codes (N, Z, V, C) govern execution of PDP-11 conditional branches. Conditional branches are implemented using two microinstructions, Add On Branch Condition (AOBC) and Subtract On Branch Condition (SOBC).

AOBC conditionally performs an add operation based on conditions specified by bits<15,10:8> of the PDP-11 instruction in the SIR (see Table 2-10). If the stated branch condition is satisfied, the add operation is performed. Otherwise, the operands are left unchanged.

SOBC conditionally performs a subtract operation based on the local status flags set during the previous microinstruction (see Table 2-10). If the local status flags satisfy the branch condition, -AZ, the subtraction is performed. Otherwise, the operands are left unchanged.

In both AOBC and SOBC, the suppression of the arithmetic operation is implemented by inhibiting the write-back to the A-port. That is, the operation always takes place, and suppression of the output is realized by disabling the write amplifiers. If the write-back is not suppressed (branch taken) and the destination register is the PC, the Data chip clears the prefetch buffer valid flag (PV) and asserts the kill prefetch buffer signal (MKPB-L).

Table 2-10 AOBC BRANCH CONDITIONS

| SIR<br>Bits: | <15>                                    | <10>                                    | <b>&lt;9&gt;</b>                                    | <b>&lt;8&gt;</b>                               | SPECIFIED BRANCH CONDITION                                                                                    | CORRESPONDING PDP-11 INSTR.                                      |

|--------------|-----------------------------------------|-----------------------------------------|-----------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

|              | 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | don't care unconditional -Z Z -(N XOR V) N XOR V -(Z + (N XOR V)) Z + (N XOR V) -N N -(Z + C) Z + C -V V -C C | none BR BNE BEQ BGE BLT BGT BLE BPL BMI BHI BLOS BVC BVS BCC BCS |

#### SOBC BRANCH CONDITION

| <br> |   |   |   | ·<br>+ | -+  |

|------|---|---|---|--------|-----|

| X    | X | X | X | l -AZ  | SOB |

#### 2.4.2 Conditional Jump Testing Logic

The conditional jump logic tests various status flags in the Data chip (see Table 2-11). Both the local EU status flags (AN, AV, AZ, AC) and the processor status flags (N, V, Z, C) can be tested. It is also possible to test if the current mode (PS<15:14>) is kernel mode. If the stated condition is satisfied, the Data chip asserts the Jump Allow signal (MSOV/JA-L). This signals the Control chip to execute the jump. Note that the execution of a conditional jump is effectively delayed one microcycle, during which the microcode can specify a NOP instruction or, if possible, perform some useful operation.

Table 2-11 CONDITIONAL JUMP INSTRUCTIONS

| Microinstruction | Condition Tested |

|------------------|------------------|

| JC               | C = 1            |

| JÝ               | V = 1            |

| JZ               | Z = 1            |

| JN               | N = 1            |

| JAC              | AC = 1           |

| JAV              | AV = 1           |

| JAZ              | AZ = 1           |

| JAN              | AN = 1           |

| JKM              | PS < 15:14 > = 0 |

#### 2.5 EU/MDAL Interface

The interface between the EU and the external MDAL bus consists of an I/O multiplexor, two input latches, and an output latch.

# 2.5.1 I/O Multiplexor

The I/O multiplexor provides a complex set of interconnects among the A-bus (A<31:0>), the output of the shifter/swapper (F<31:0>), the MMU data bus (M<15:0>), the input latches (IL[1:0]<15:0>), and the output latch (OL<15:0>). All connections are word width (16 bits); multiple paths may be enabled simultaneously to implement 32-bit transfers. The specific paths within the I/O multiplexor are as follows:

| 1-  | F<31:16>>      | A<31:16> |

|-----|----------------|----------|

| 2 - | F<15:0>>       | A<31:16> |

| 3 - | M<15:0>>       | A<31:16> |

| 4 - | IL[1:0]<15:0>> | A<31:16> |

| 5-  | F<15:0>>       | A<15:0>  |

| 6 – | F<31:16>>      | A<15:0>  |

| 7-  | M<15:0>>       | A<15:0>  |

| 8 - | IL[1:0]<15:0>> | A<15:0>  |

| 9-  | M<7:0,15:8>>   | A<15:0>  |

| 10- | IL[1:0]<15:8>> | A<7:0>   |

| 11- | A<15:0>>       | M<15:0>  |

| 12- | F<31:16>>      | M<15:0>  |

| 13- | F<15:0>>       | M<15:0>  |

| 14- | F<7:0,15:8>>   | M<15:0>  |

|     | <u> </u>       |          |

#### Note that:

- Paths 1,2,3,4 are mutually exclusive.

- Paths 5,6,7,8 are mutually exclusive.

- Paths 9,10 are mutually exclusive.

- Paths 11,12,13,14 are mutually exclusive.

- Paths 5 to 8 and 9 to 10 are mutually exclusive.

- Simultaneous use of paths 2 and 6 is not supported.

The upper 16 bits of both the A-bus and the B-bus can not be

- used during a predecode microcycle.

Other than F<31:0> --> A<31:0>, only 16 bits of the A bus can be driven with data at one time. The other 16 bits are zeroes.

# 2.5.2 Input Latch (IL[1:0]<15:0>)

The dual input latches (IL[1:0]<15:0>) latch incoming data from MDAL-H<15:0>. The latches are used on an alternating basis for instruction stream and data stream information. Operation of these latches is explained in detail in section 4.

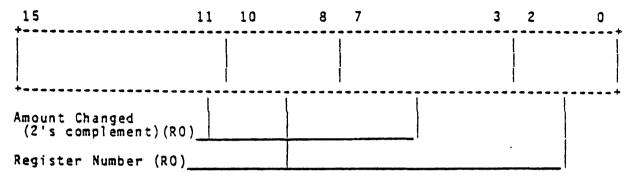

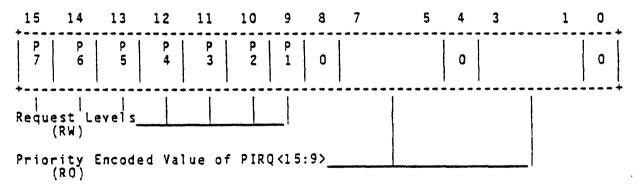

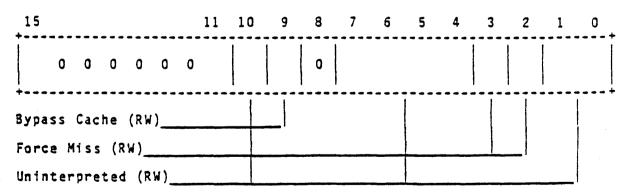

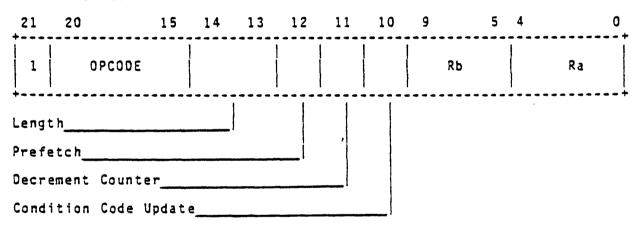

# 2.5.3 Output Latch (OL<21:0>)