digital

MK11 MOS memory technical manual

#### Copyright © 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10     | MASSBUS |

|---------|------------------|---------|

| DEC     | DECSYSTEM-20     | OMNIBUS |

| PDP     | DIBOL            | OS/8    |

| DECUS   | <b>EDUSYSTEM</b> | RSTS    |

| UNIBUS  | VAX              | RSX     |

|         | VMS              | IAS     |

# **CONTENTS**

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CHAPTER 1 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 1.1       | MEMORY SYSTEM OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-1  |

| 1.1.1     | General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-1  |

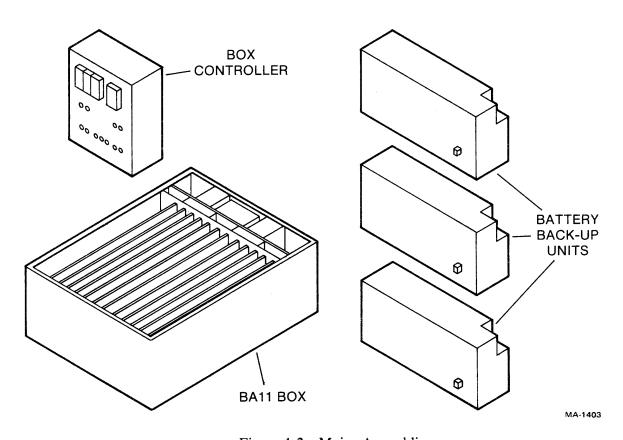

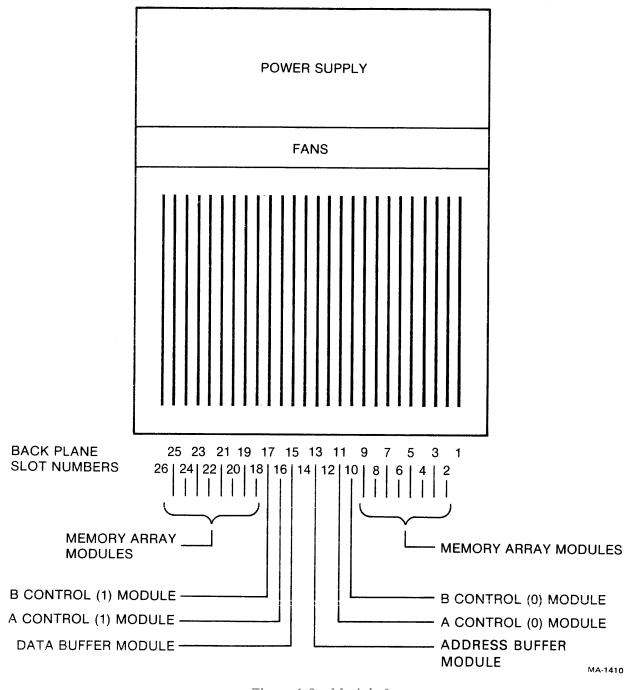

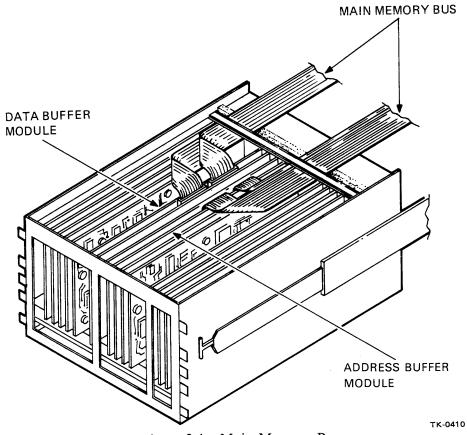

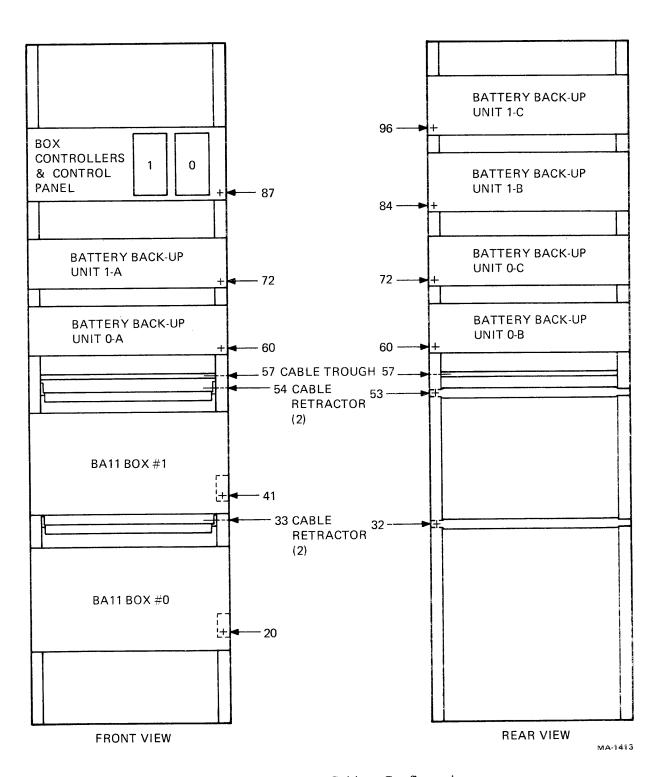

| 1.1.2     | Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-3  |

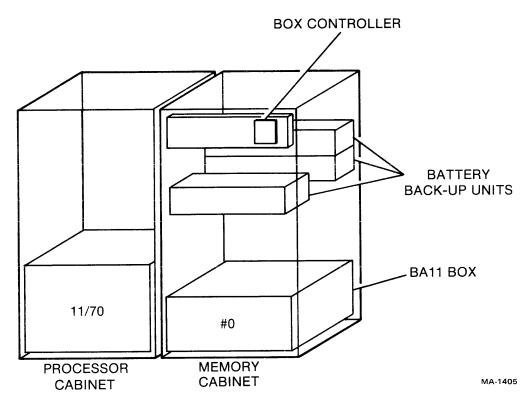

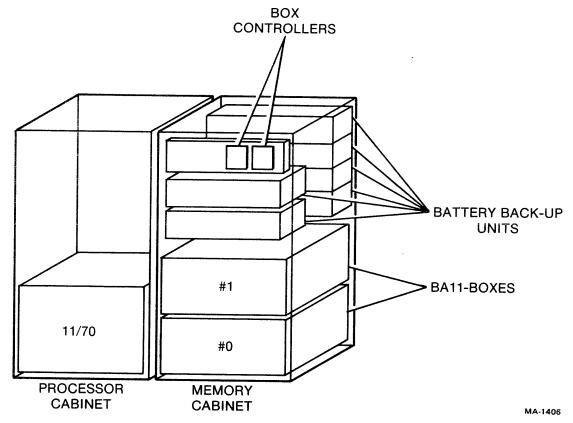

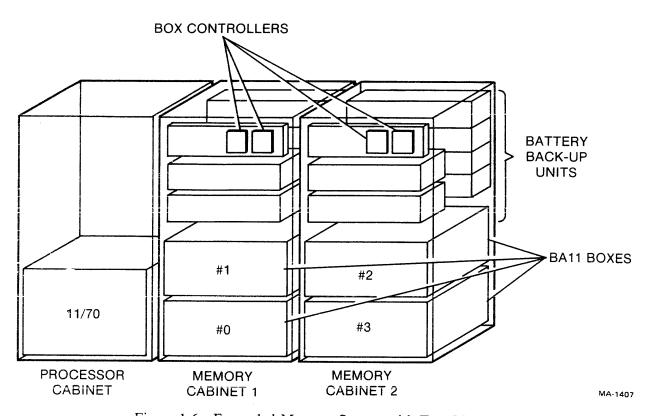

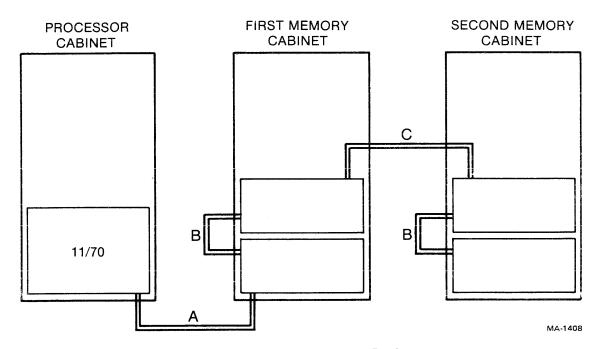

| 1.1.3     | Memory System Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-4  |

| 1.1.4     | Options MEMORY SYSTEM ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-5  |

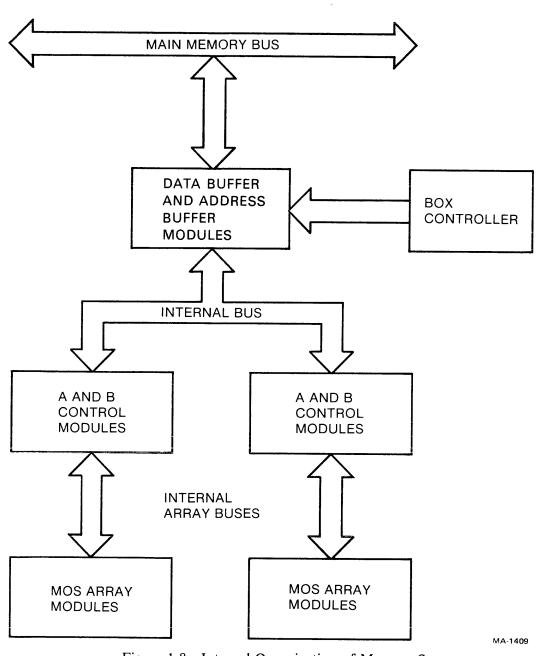

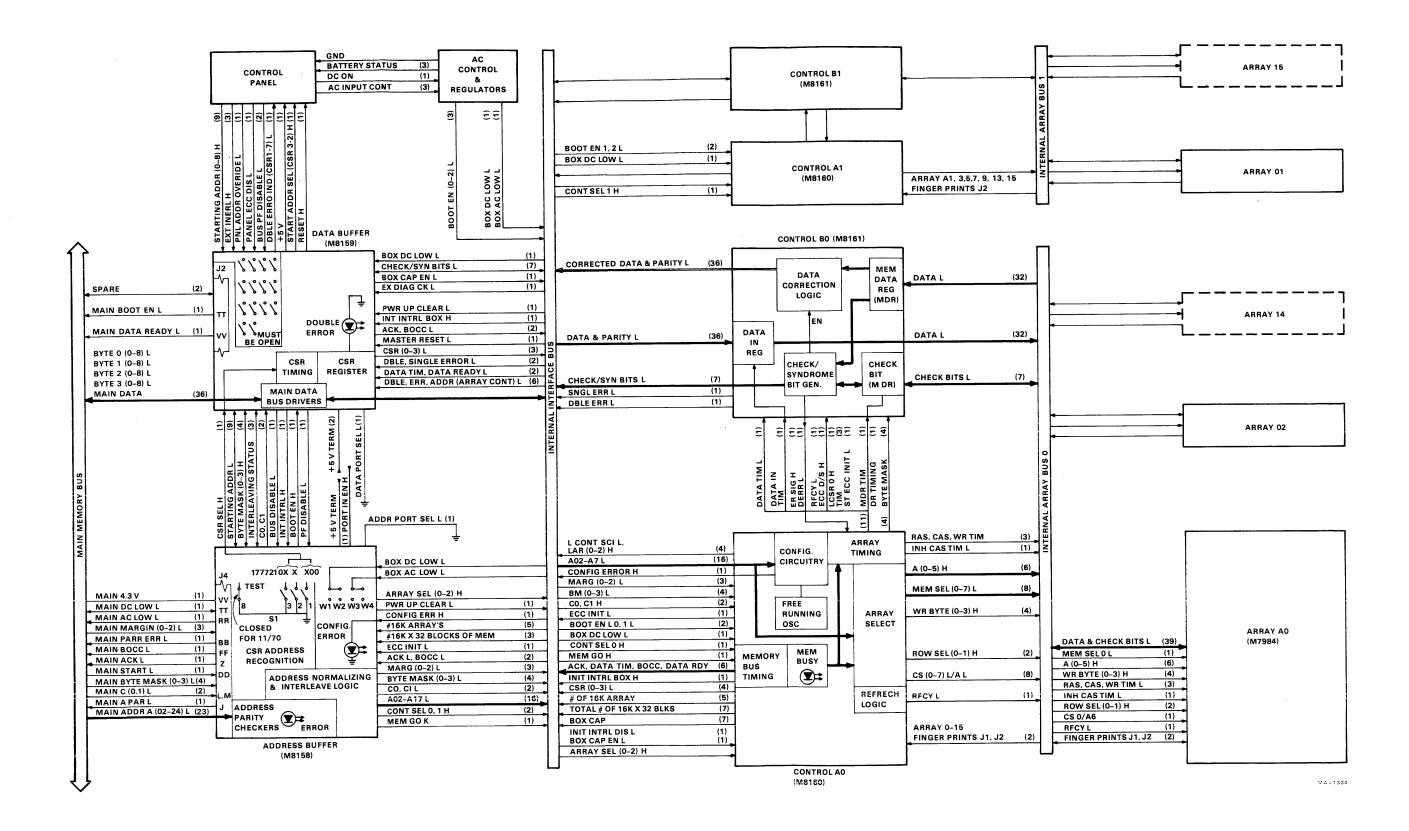

| 1.2       | MEMORY SYSTEM ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-8  |

| 1.2.1     | Main Memory Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-9  |

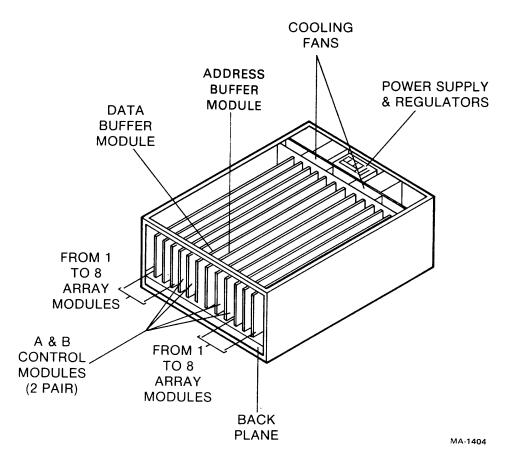

| 1.2.2     | Address Buffer Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-9  |

| 1.2.3     | Data Buffer Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-9  |

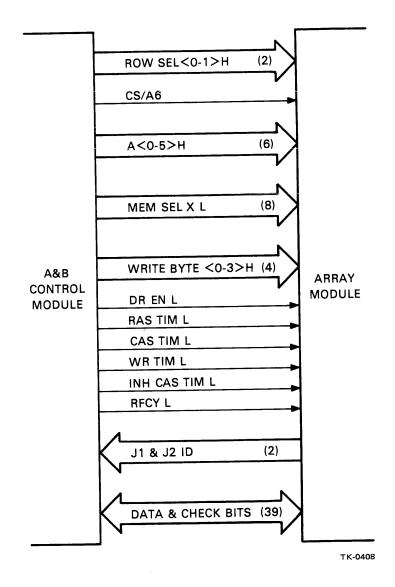

| 1.2.4     | Control A and B Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-9  |

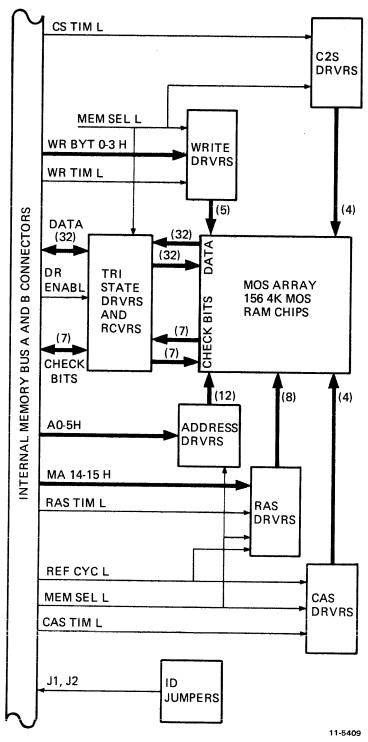

| 1.2.5     | MOS Memory Array Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-9  |

| 1.3       | RELATED HARDWARE MANUALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-11 |

| 1.5       | RELITED THING WITH STATE |      |

| CHAPTER 2 | MAIN MEMORY BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 2.1       | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-1  |

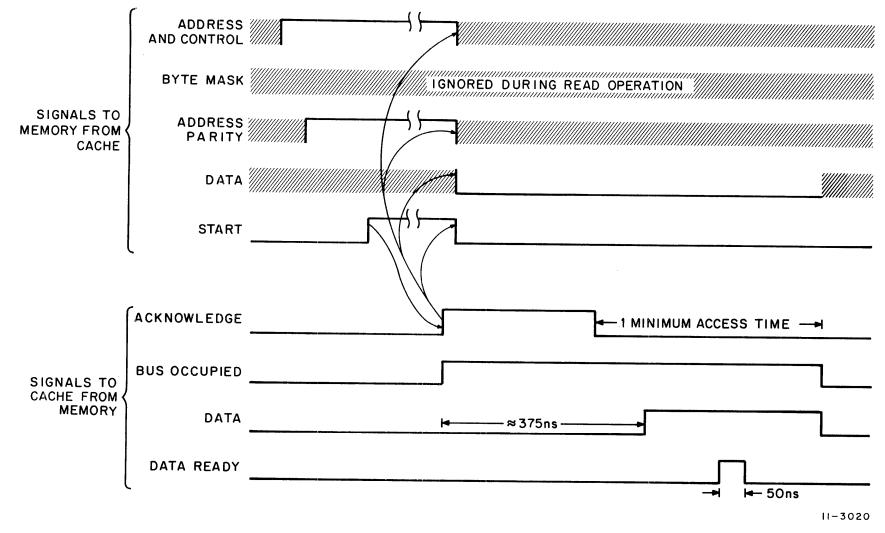

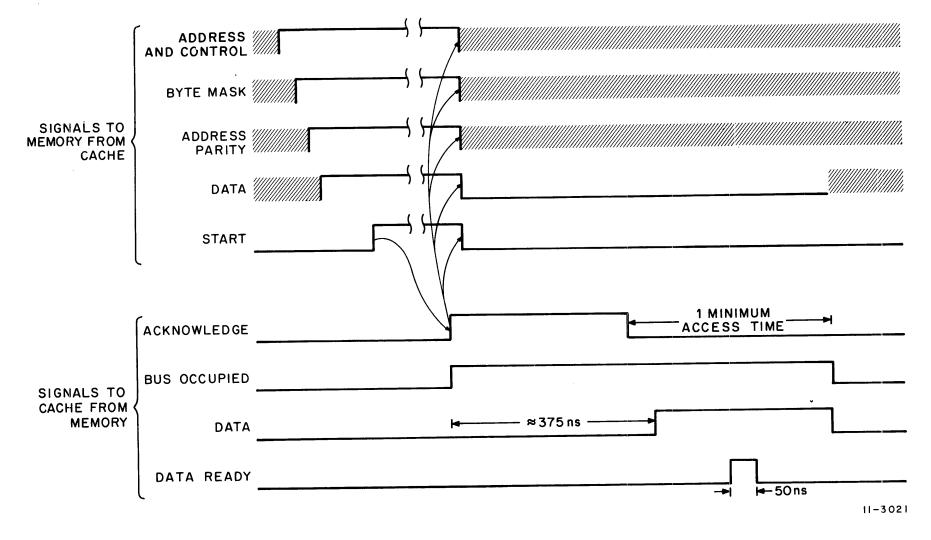

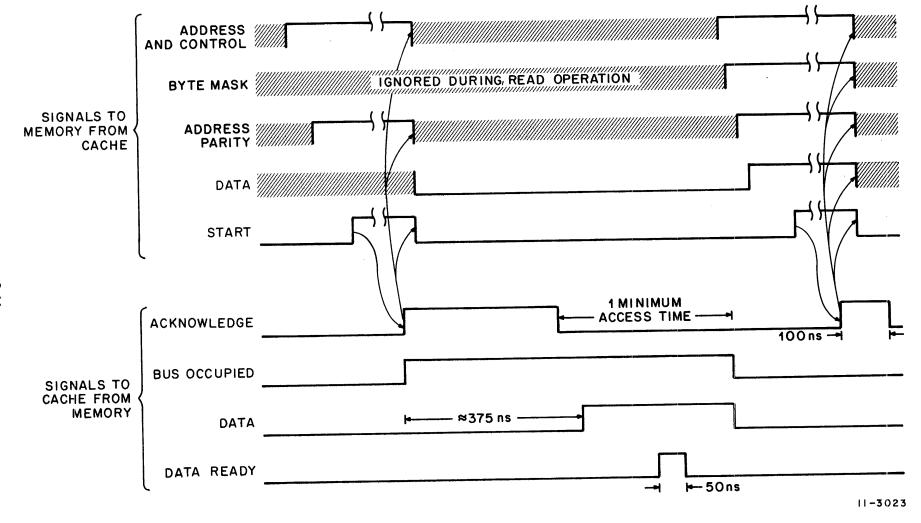

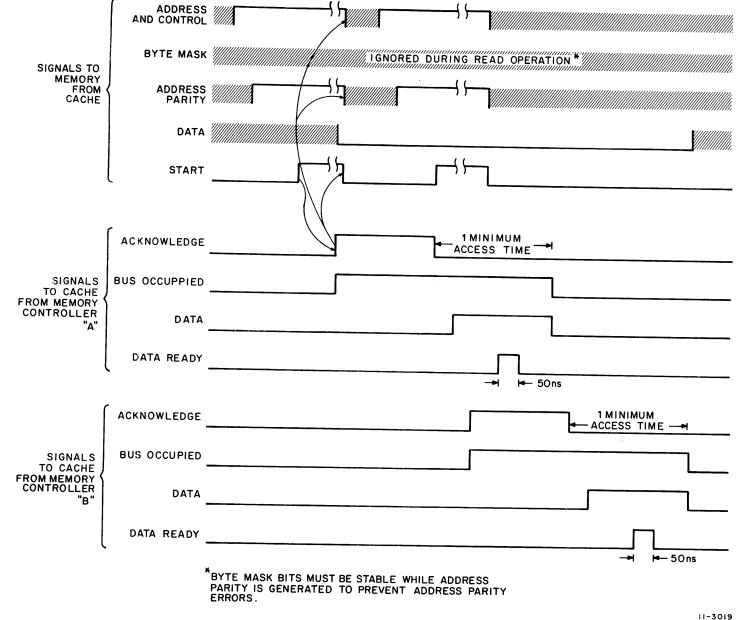

| 2.2       | PROTOCOL AND TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-6  |

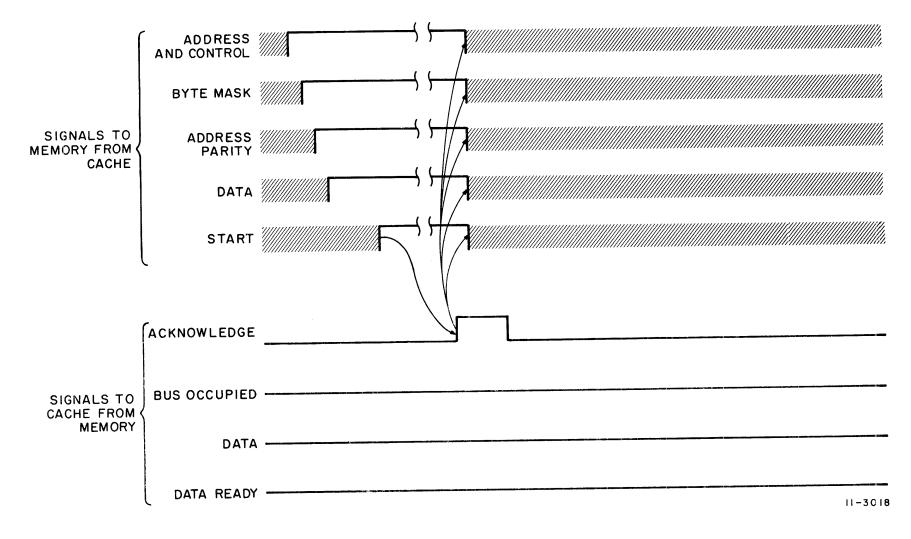

| 2.2.1     | Initiation of a Memory Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-6  |

| 2.2.2     | Response of the Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-6  |

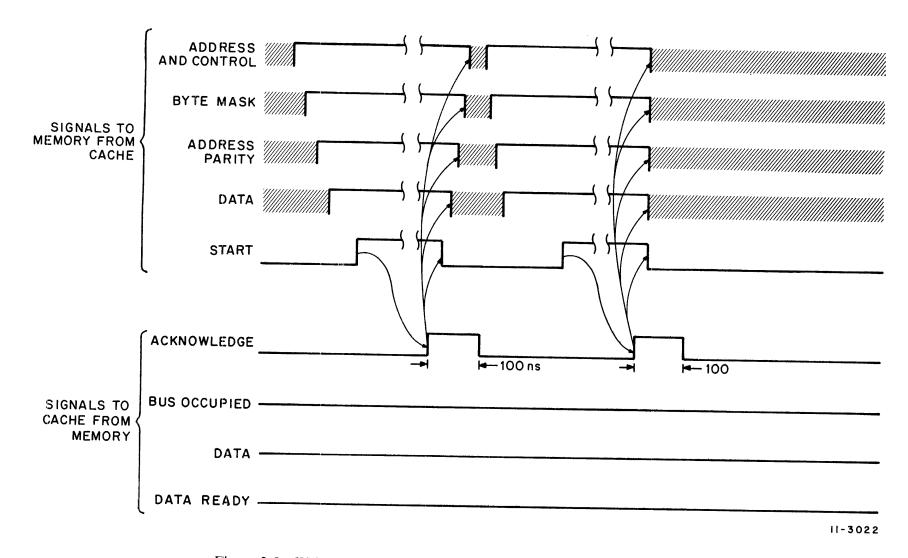

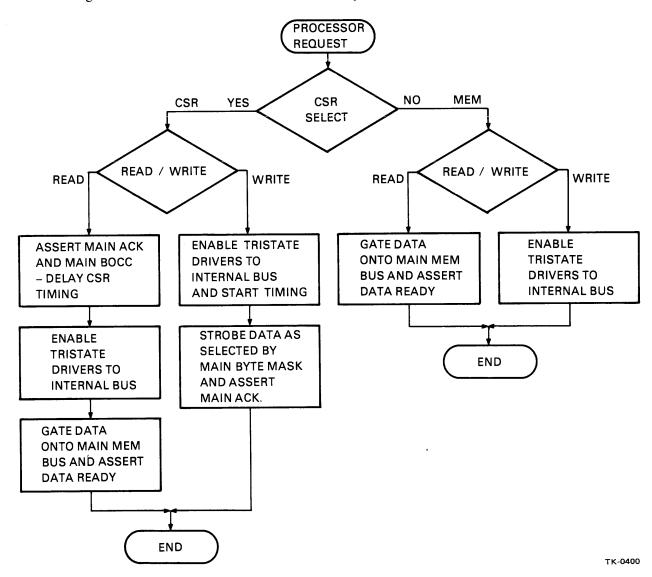

| 2.2.3     | CSR Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-13 |

| 2.2.4     | Initiation of "Overlapped" Memory Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-13 |

| 2.2.7     | initiation of Overlapped Monory Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| CHAPTER 3 | BOX CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 3.1       | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-1  |

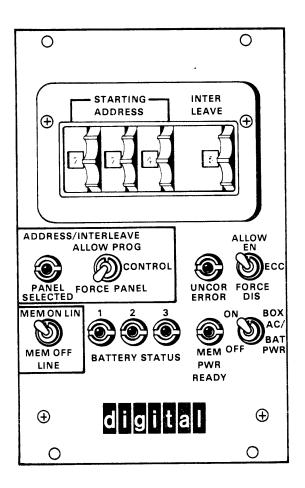

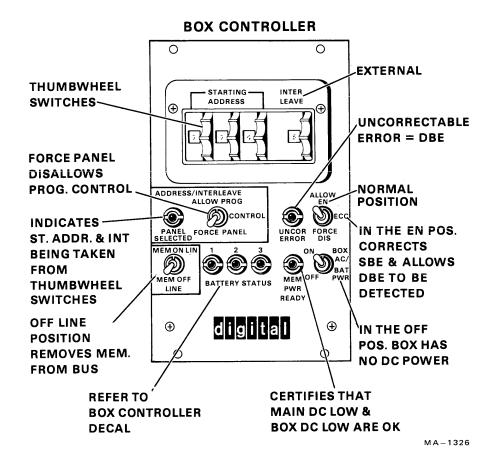

| 3.2       | CONTROL SWITCHES AND INDICATORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-2  |

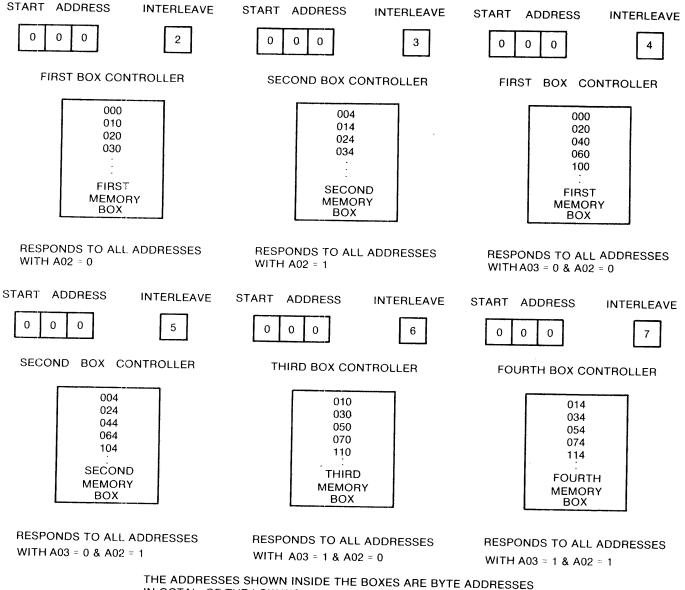

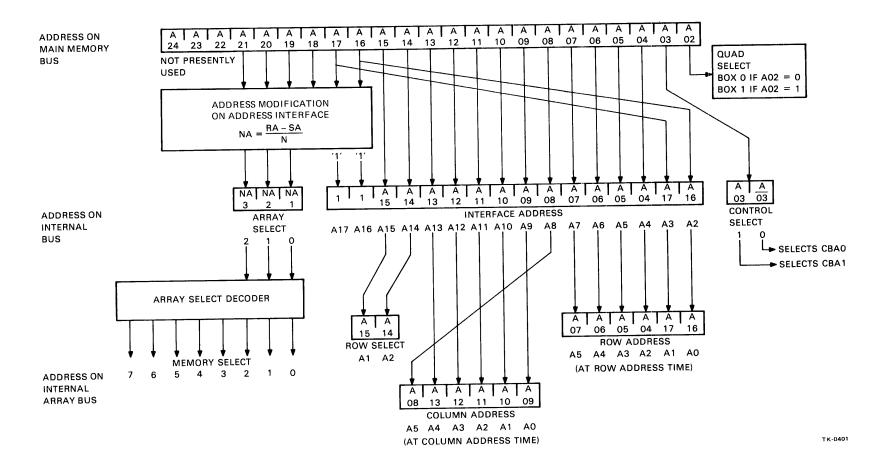

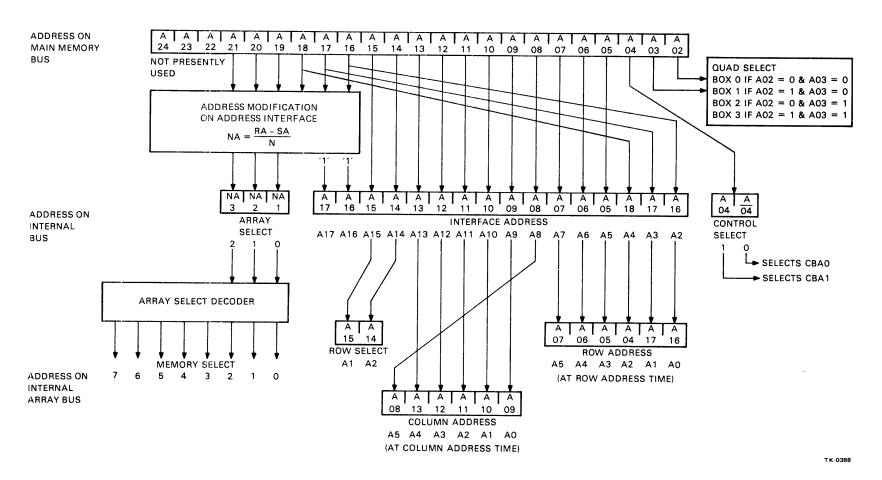

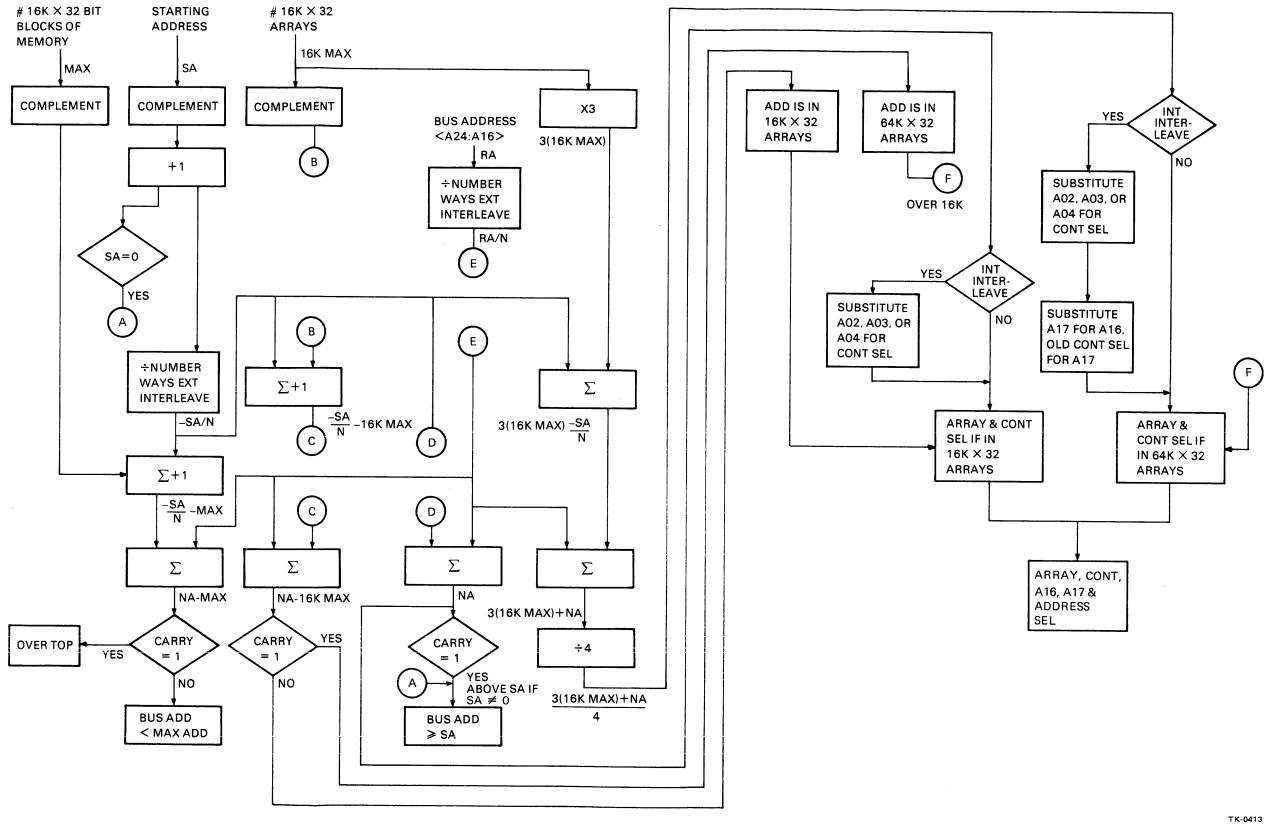

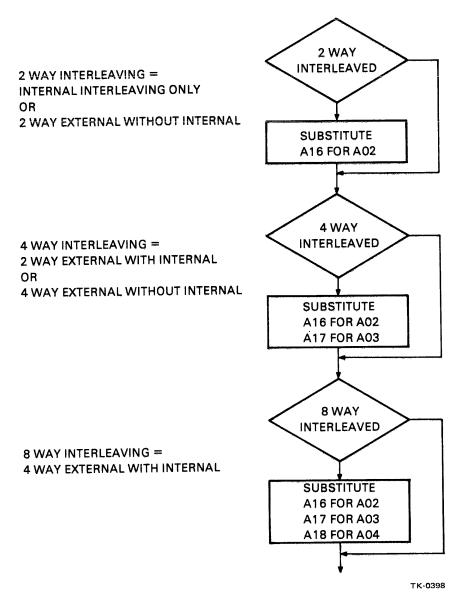

| 3.3       | STARTING ADDRESS AND EXTERNAL INTERLEAVING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-3  |

| 3.4       | DISABLING ERROR CORRECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-3  |

| CHAPTER 4 | MS11-KE MOS ARRAY MODULES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

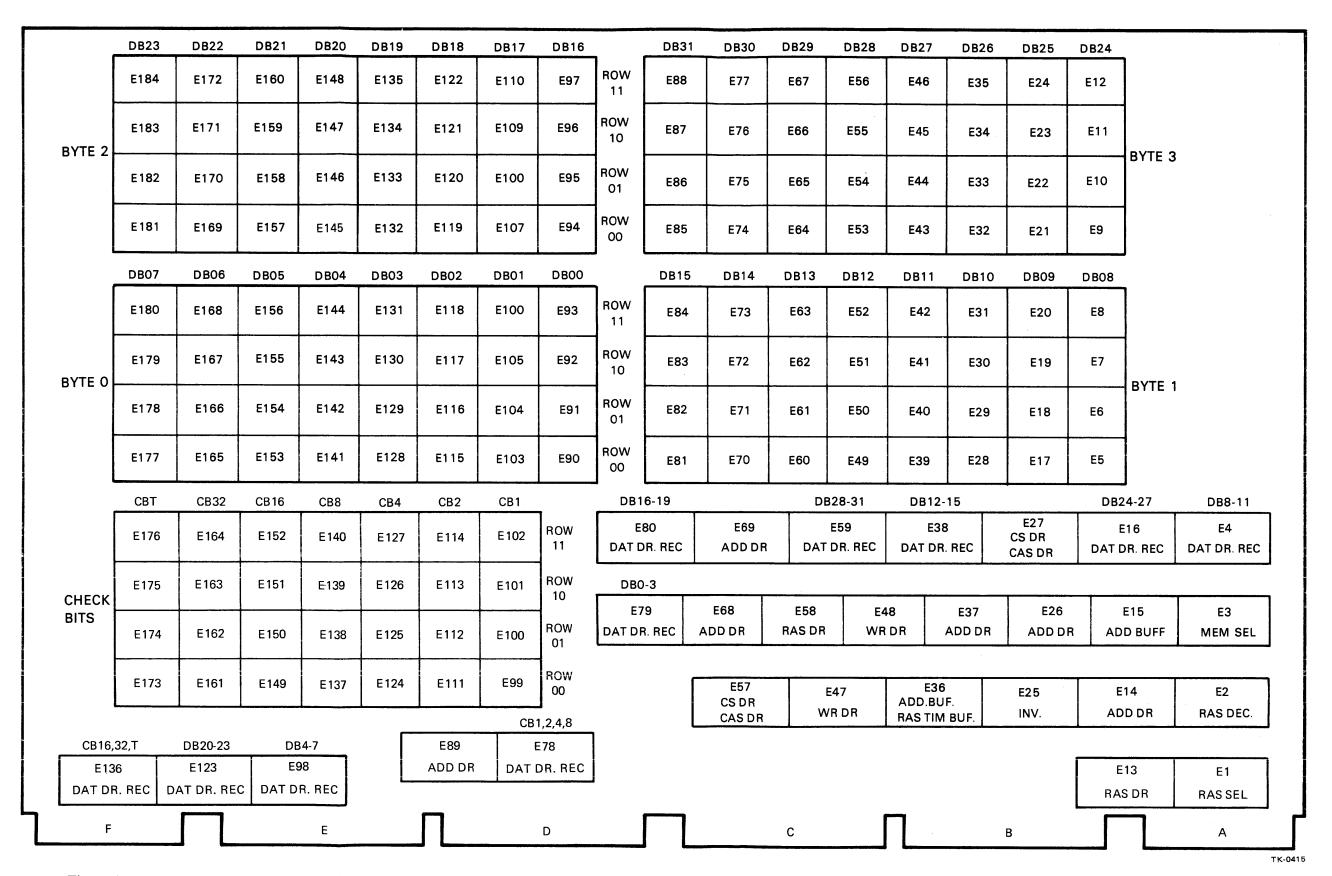

| 4.1       | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-1  |

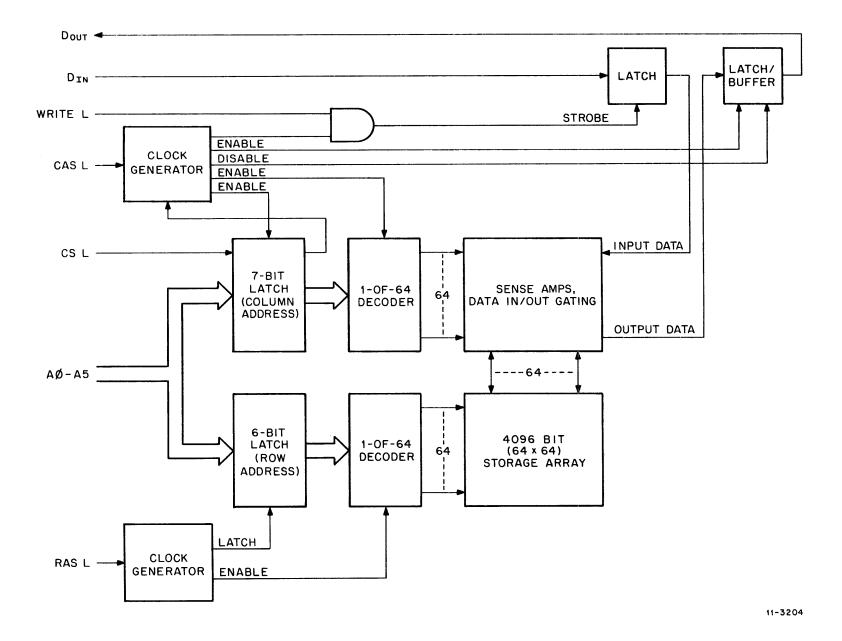

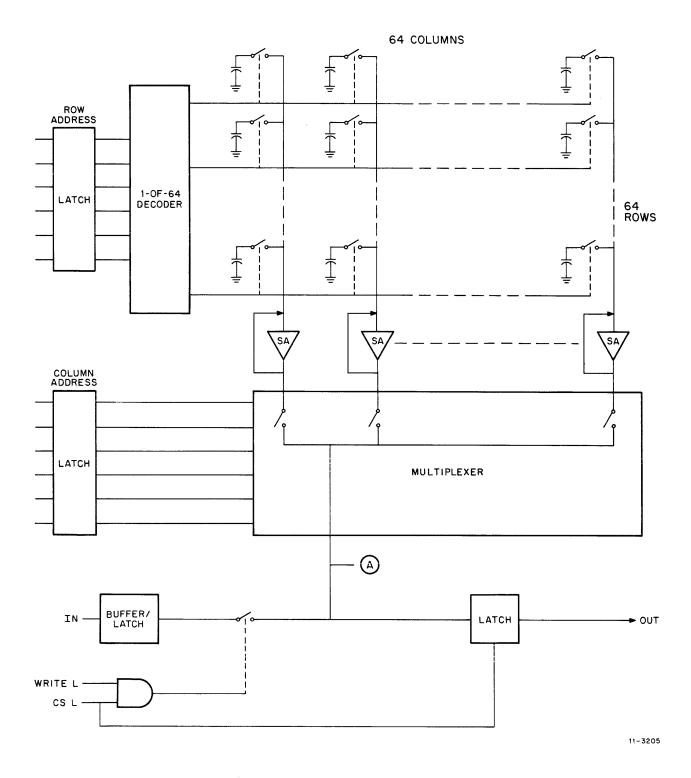

| 4.2       | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-1  |

| 4.2.1     | Data Receivers and Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-1  |

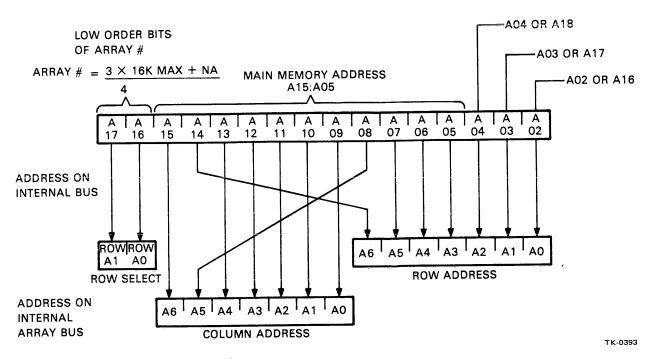

| 4.2.2     | Addressing and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-1  |

| ·         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •    |

# CONTENTS (Cont)

|           |                                                                                      | Page                   |

|-----------|--------------------------------------------------------------------------------------|------------------------|

| CHAPTER 5 | CONTROL MODULES                                                                      |                        |

| 5.1       | GENERAL DESCRIPTION                                                                  | 5-1                    |

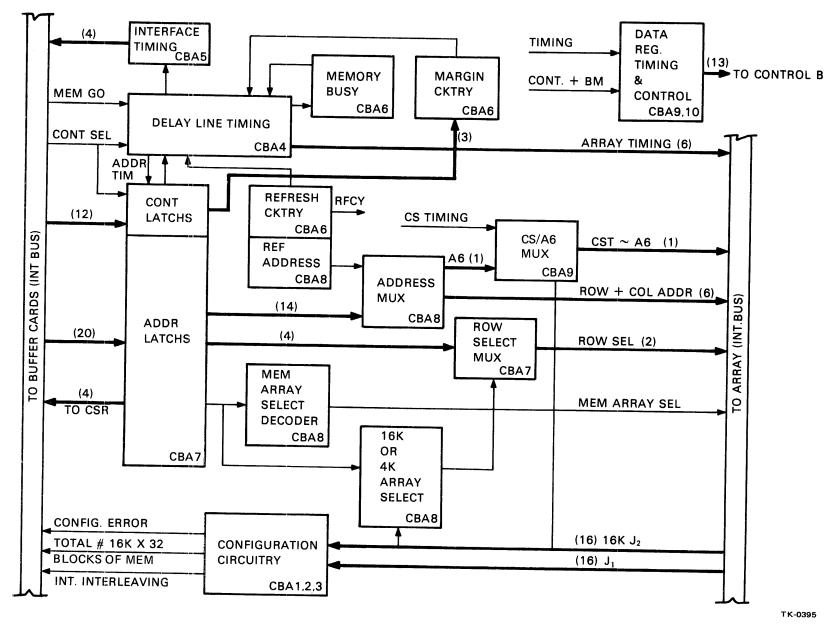

| 5.1.1     | Control A Module                                                                     | 5_1                    |

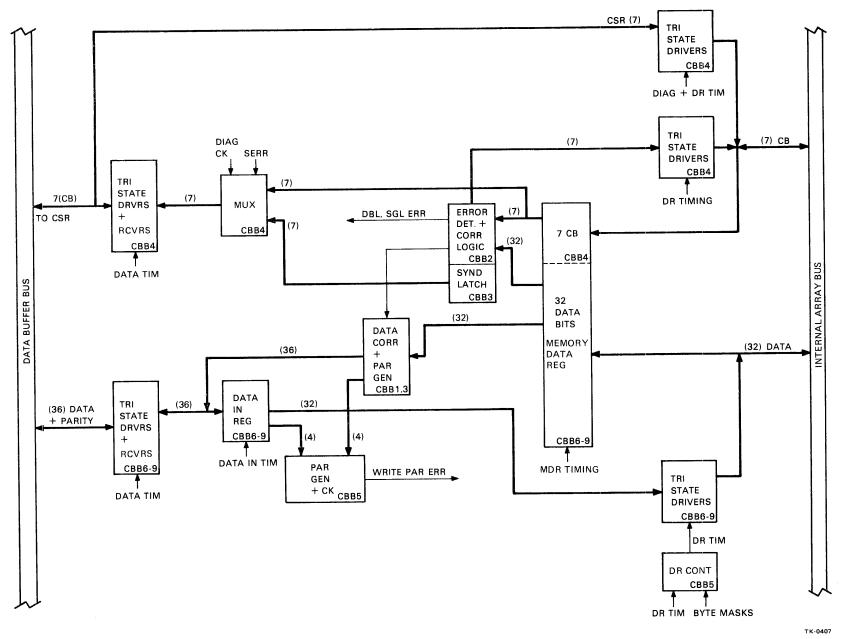

| 5.1.2     | Control B Module                                                                     | 5-1                    |

| 5.2       | FUNCTIONAL DESCRIPTION                                                               | 5-1<br>5_1             |

| 5.2.1     | Timing                                                                               | 5-4                    |

| 5.2.2     | Address and Control                                                                  | 5_4                    |

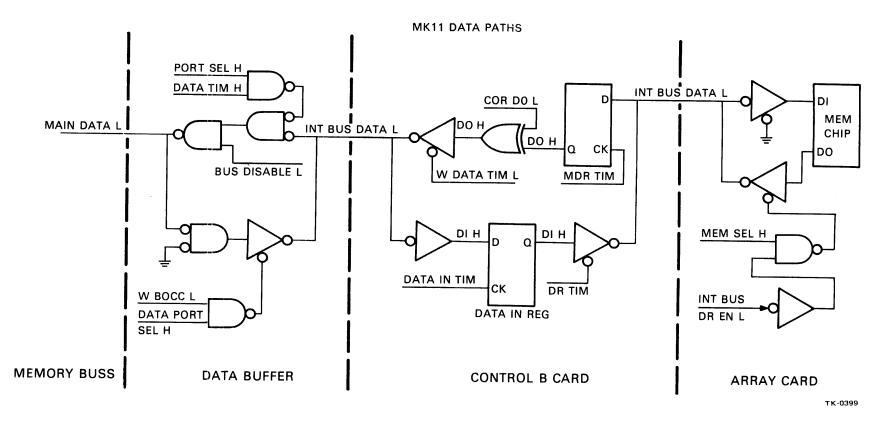

| 5.2.3     | Data Paths                                                                           | 5- <del>4</del><br>5-7 |

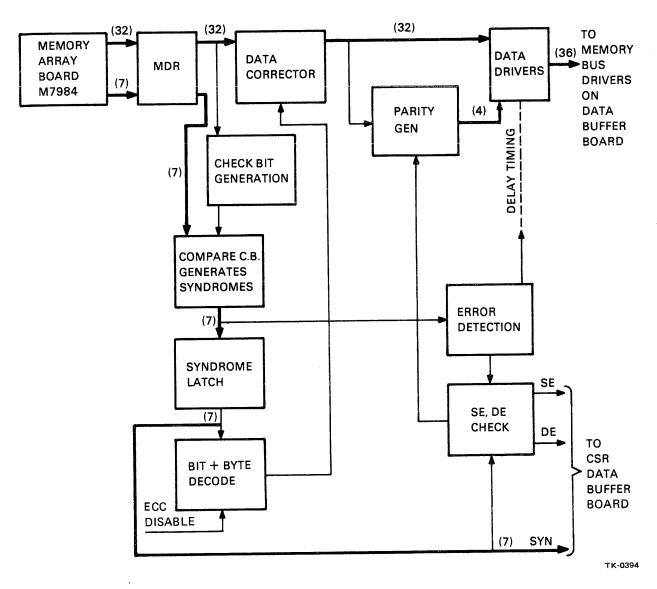

| 5.2.4     | Error Detection and Correction                                                       | <i>5-7</i>             |

| 5.3       | MEMORY CYCLES                                                                        | 5_12                   |

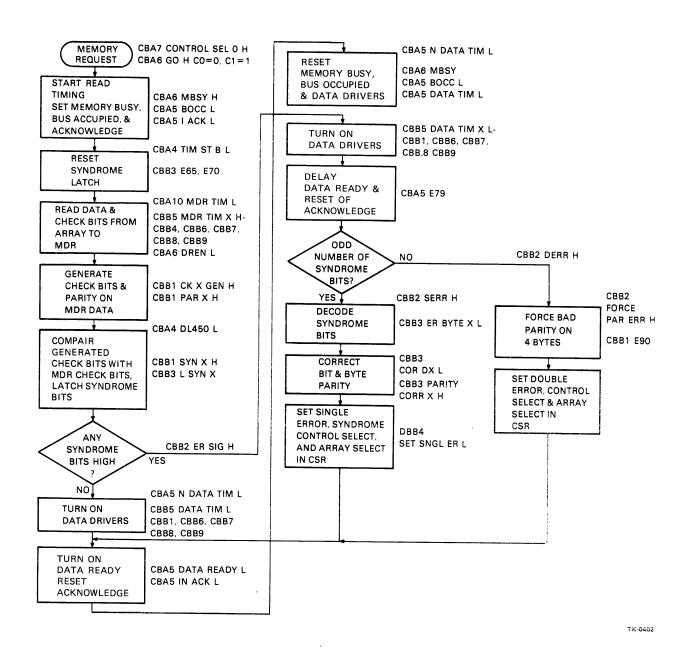

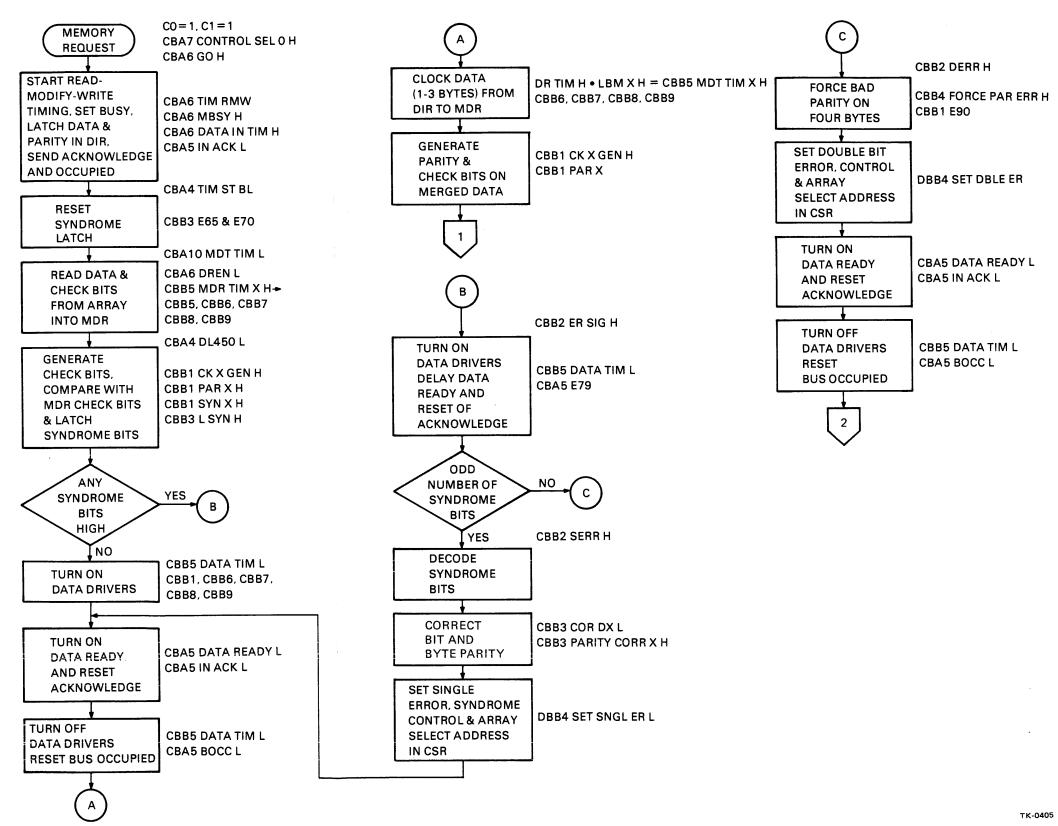

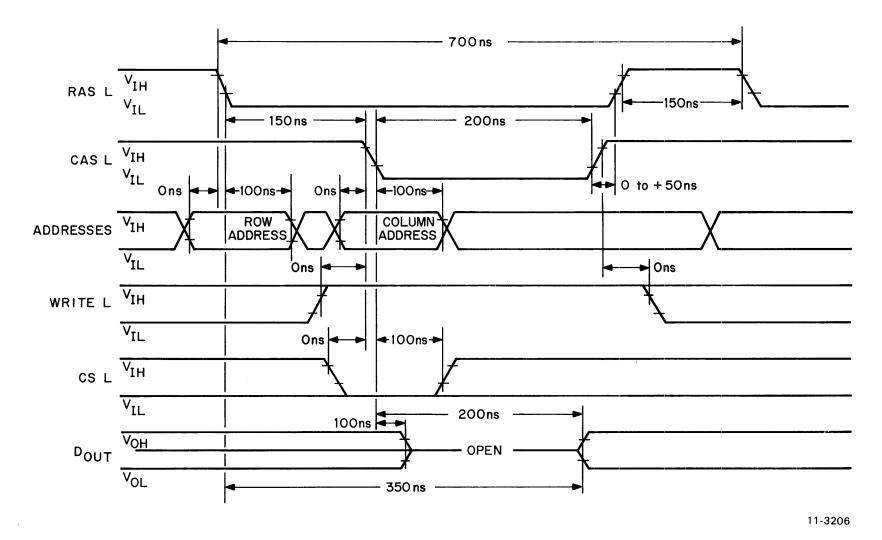

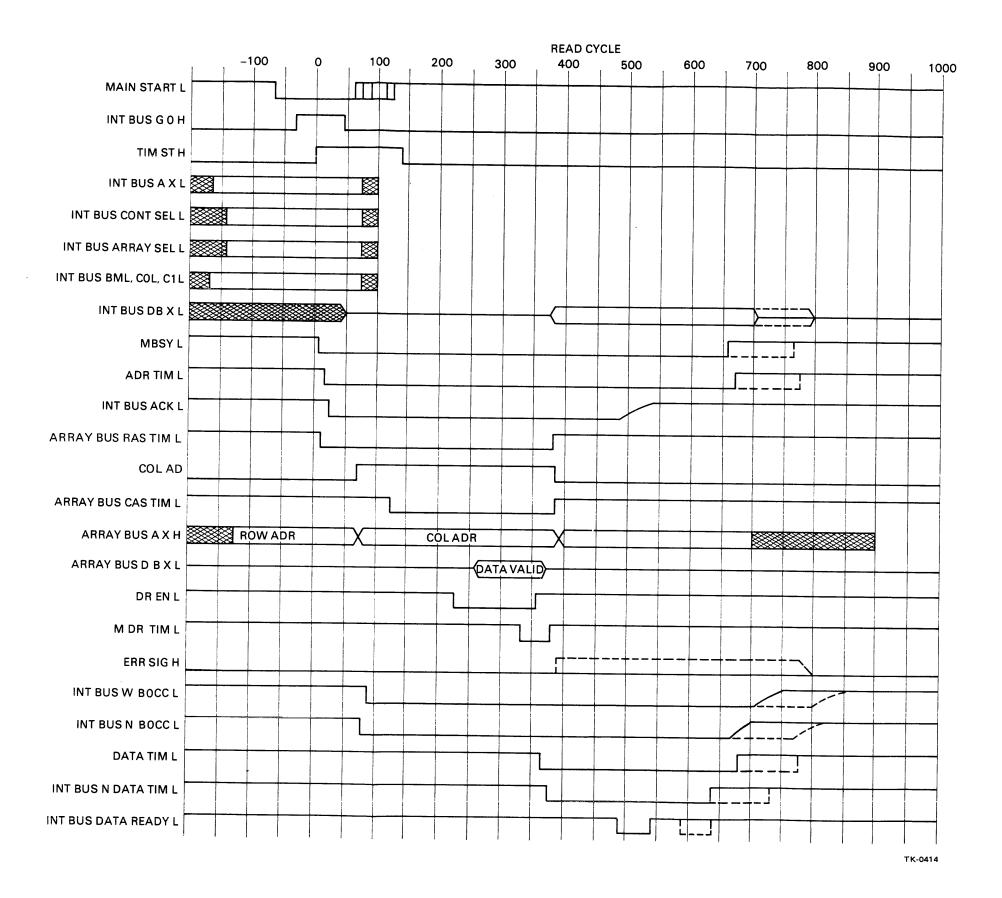

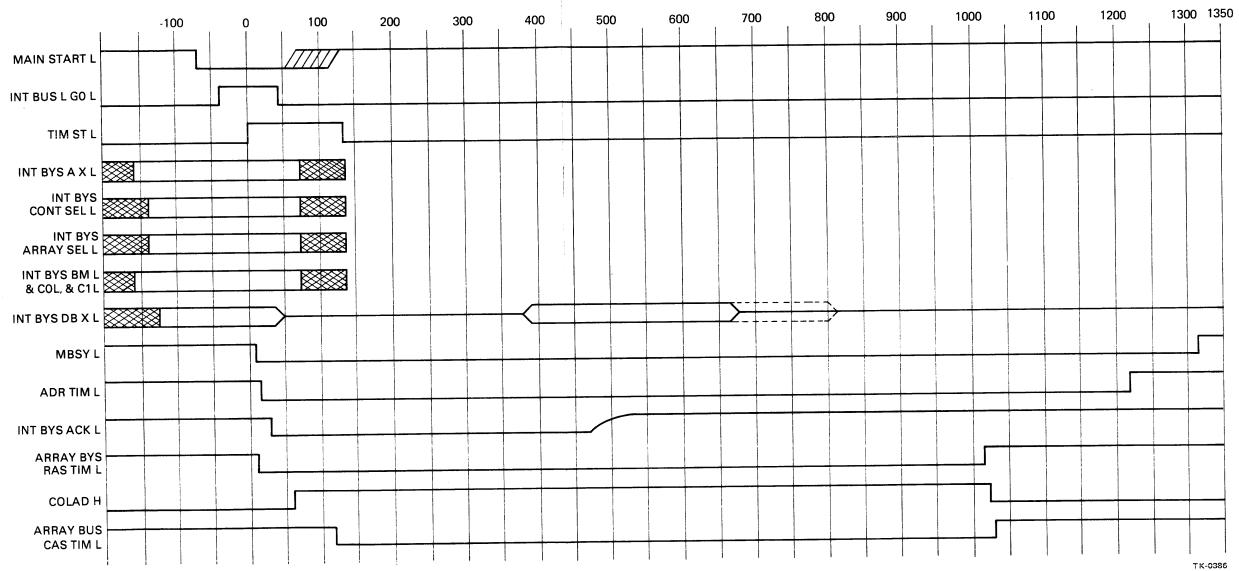

| 5.3.1     | Read                                                                                 | 5_12                   |

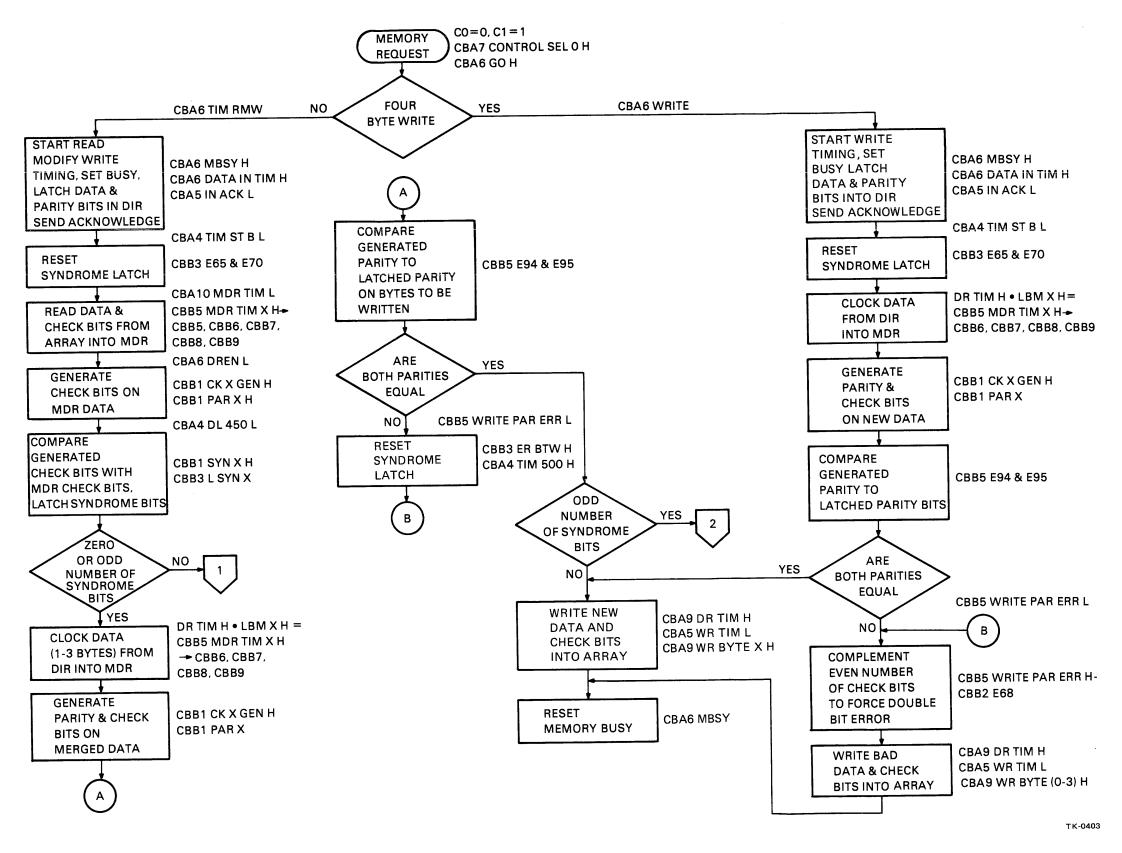

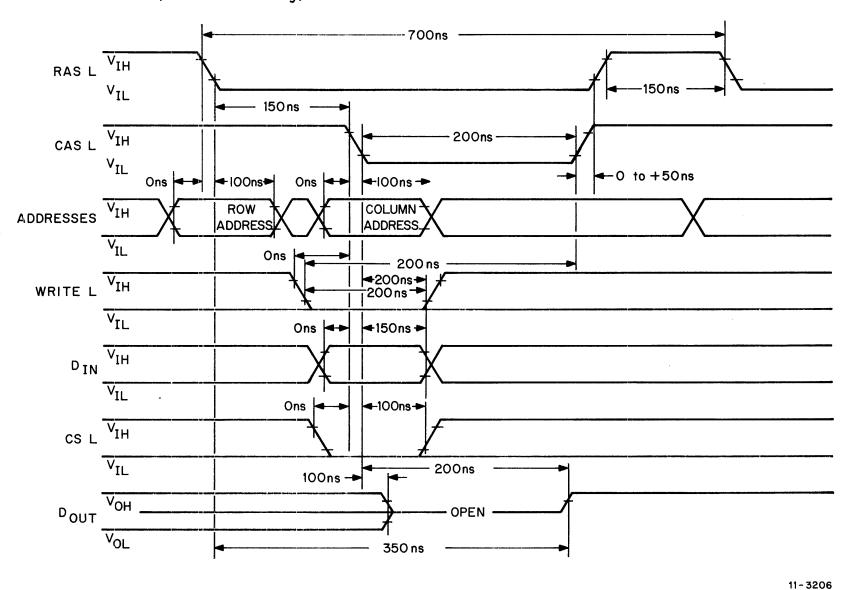

| 5.3.2     | Write                                                                                | 5-15                   |

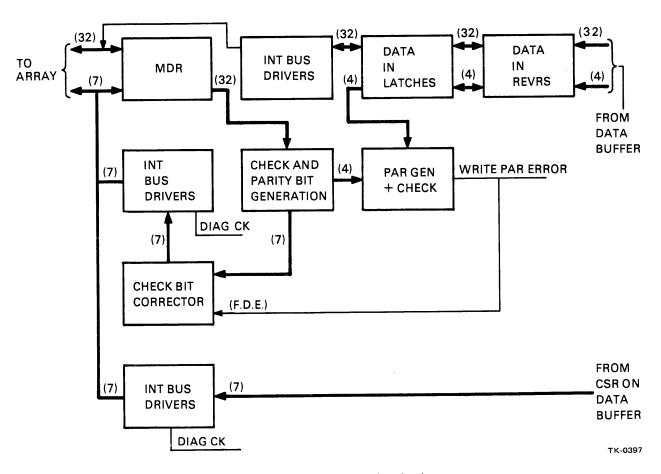

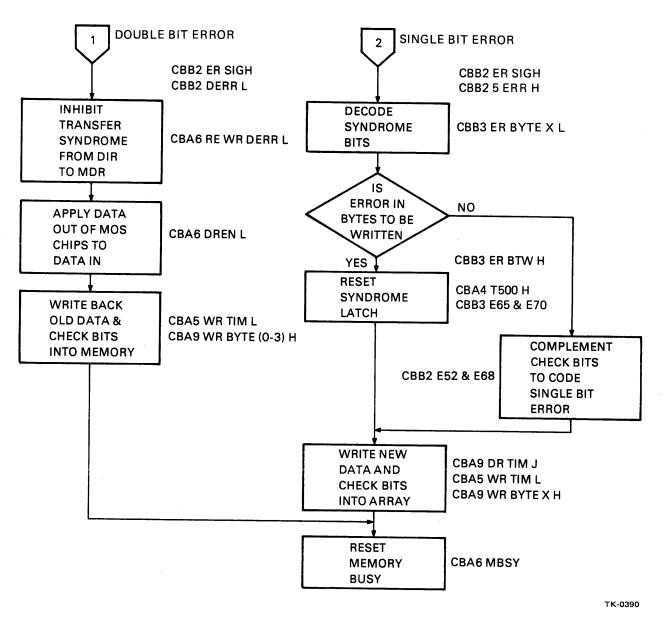

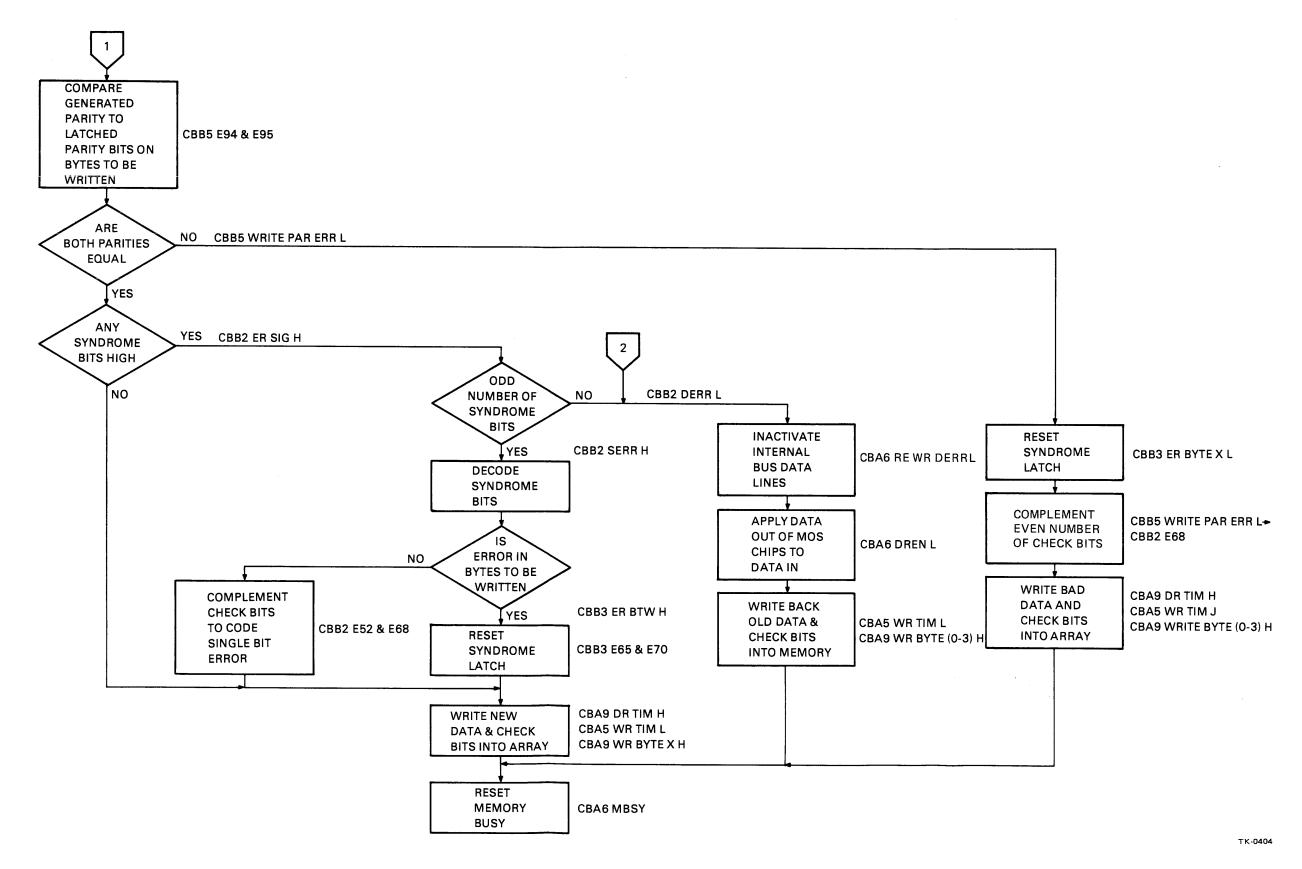

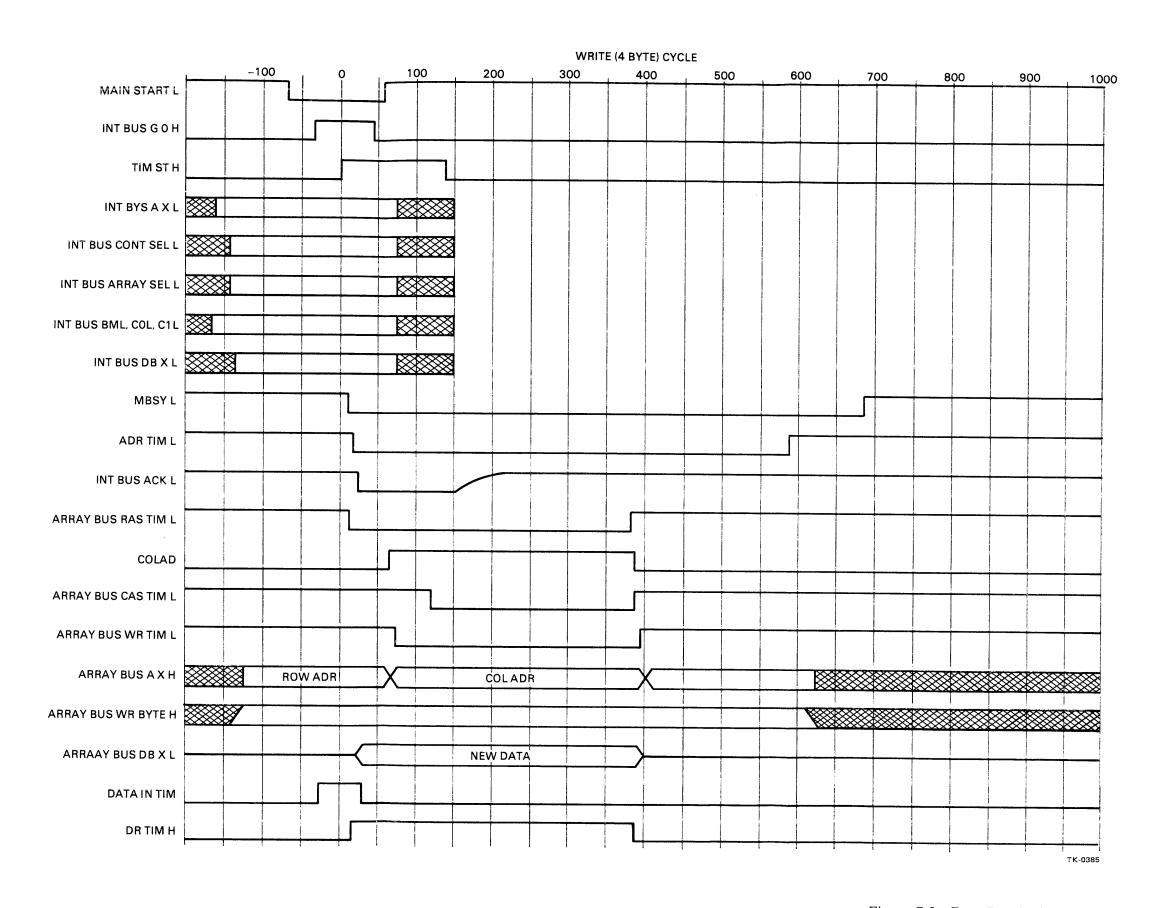

| 5.3.2.1   | Four-Byte Write                                                                      | 5-19                   |

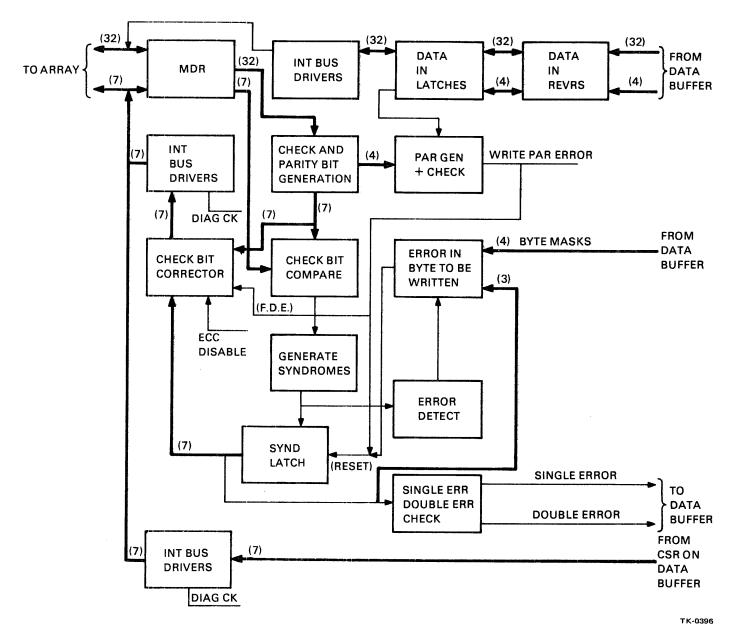

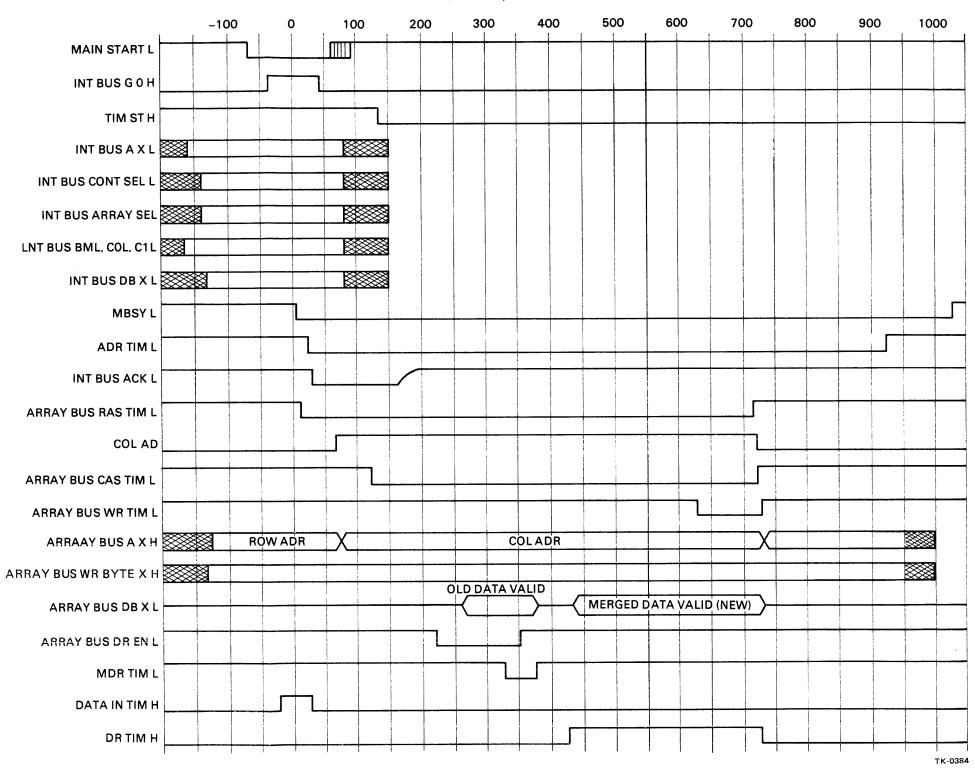

| 5.3.2.2   | Internal Read-Modify-Write                                                           | 5.10                   |

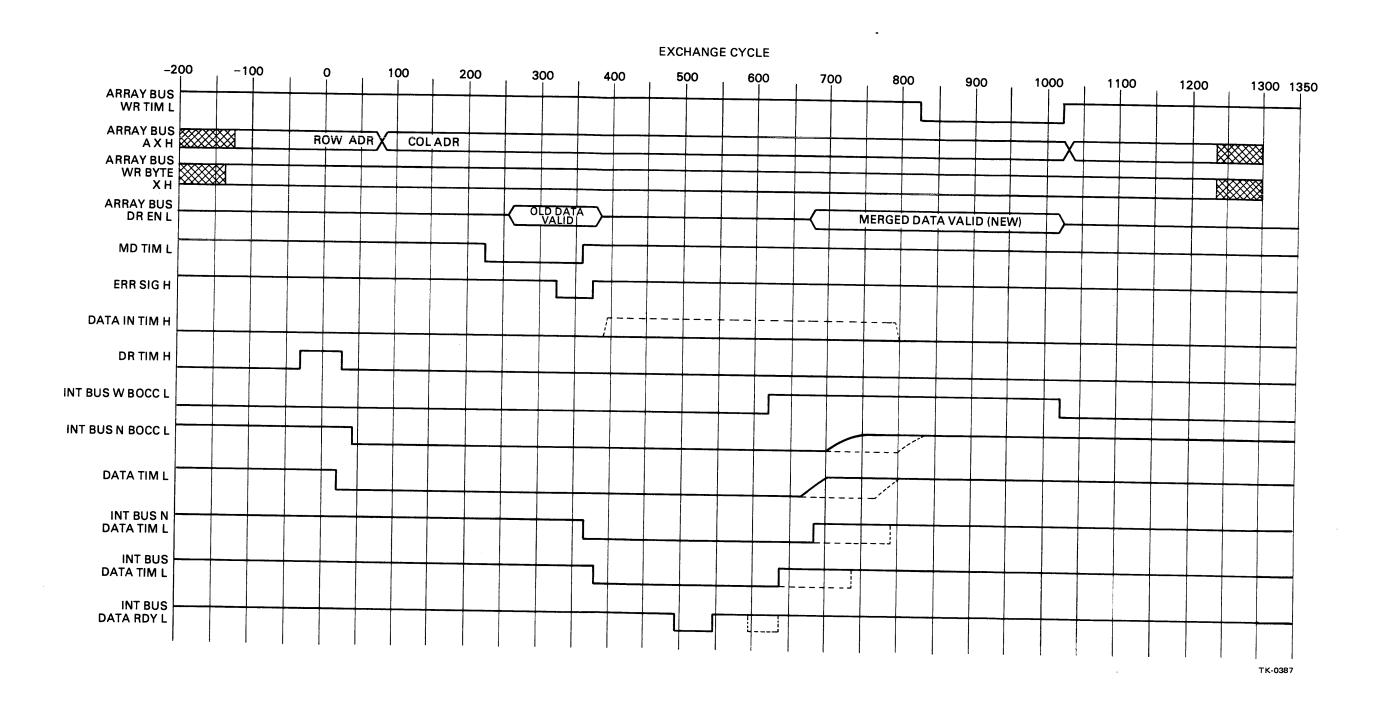

| 5.3.3     | Exchange Cycle                                                                       | 5 71                   |

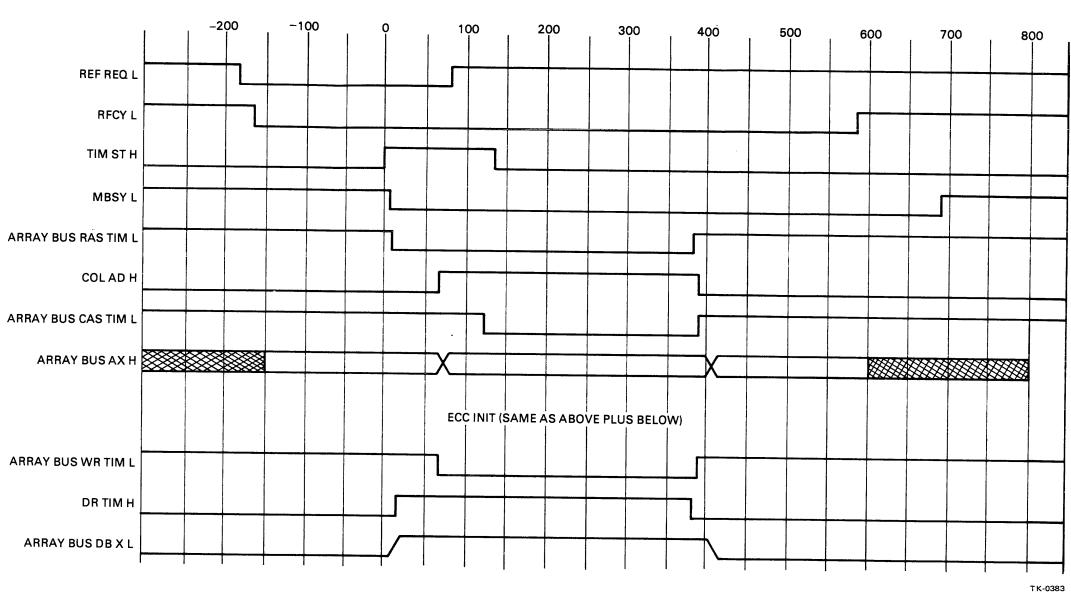

| 5.3.4     | Refresh                                                                              | 5 24                   |

| 5.3.5     | ECC Initialization                                                                   | 5 24                   |

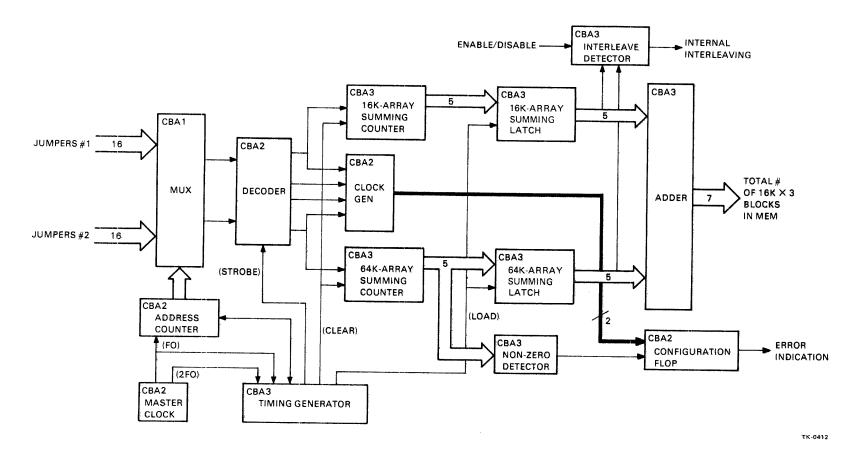

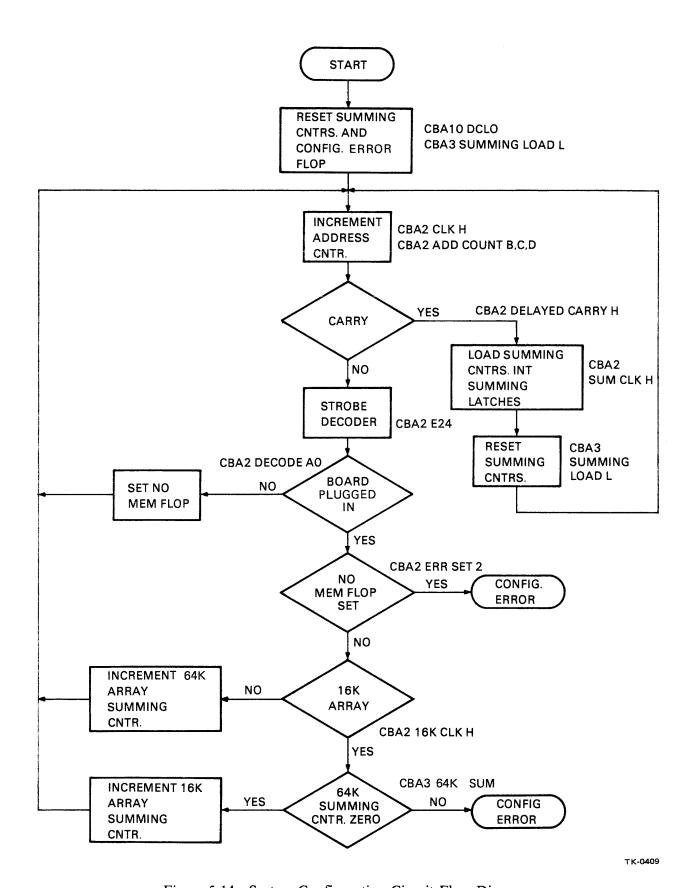

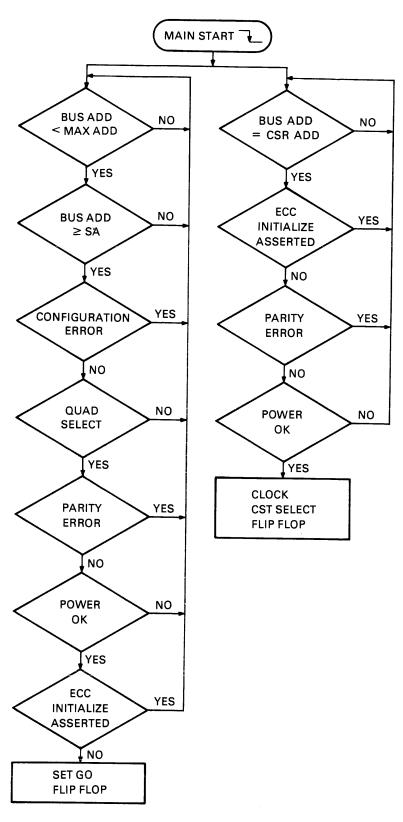

| 5.3.6     | Configuration Circuitry                                                              | 5 25                   |

|           | Configuration Circuity                                                               | .3-23                  |

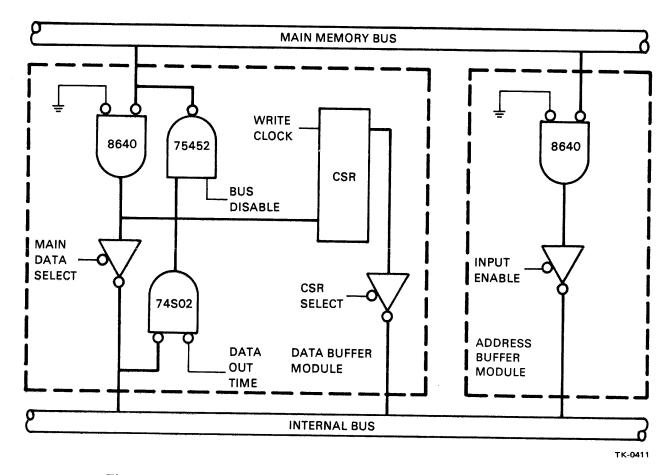

| CHAPTER 6 | ADDRESS BUFFER AND DATA BUFFER MODULES                                               |                        |

| 6.1       | GENERAL DESCRIPTION                                                                  | <b>6</b> 1             |

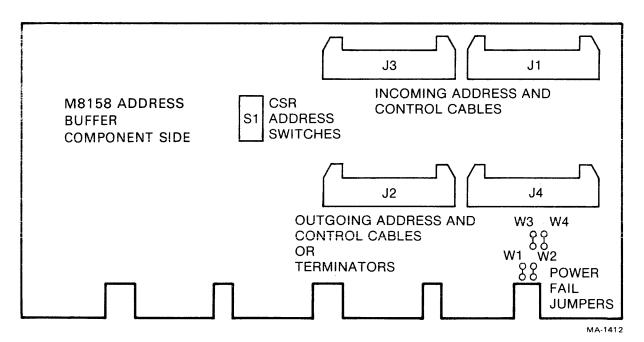

| 6.2       | ADDRESS BUFFER MODULE (M8158)                                                        | 0-1                    |

| 6.2.1     | Main Memory Bus Interface                                                            | 0-1                    |

| 6.2.2     | Address Parity Checking                                                              | 0-1                    |

| 6.2.3     | Address Modification                                                                 | 0-1                    |

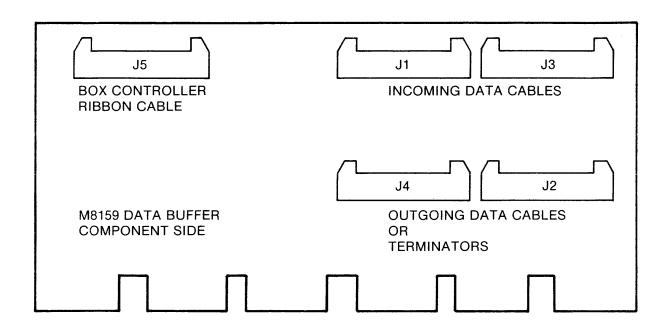

| 6.3       | DATA BUFFER MODULE (M8159)                                                           | 0-2                    |

| 6.3.1     | Main Memory Rus Interface                                                            | 0-/                    |

| 6.3.2     | Main Memory Bus Interface                                                            | 6-/                    |

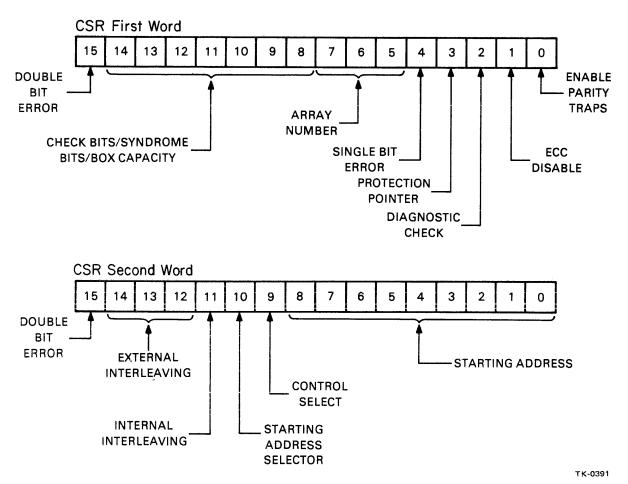

| 6.3.3     | Control and Status Register Control and Status Bit Allocation                        | 6-8                    |

| 6.3.4     | CSP Addressing                                                                       | 6-9                    |

| 0.5.4     | CSR Addressing                                                                       | .6-11                  |

| CHAPTER 7 | POWER SUPPLY AND DISTRIBUTION                                                        |                        |

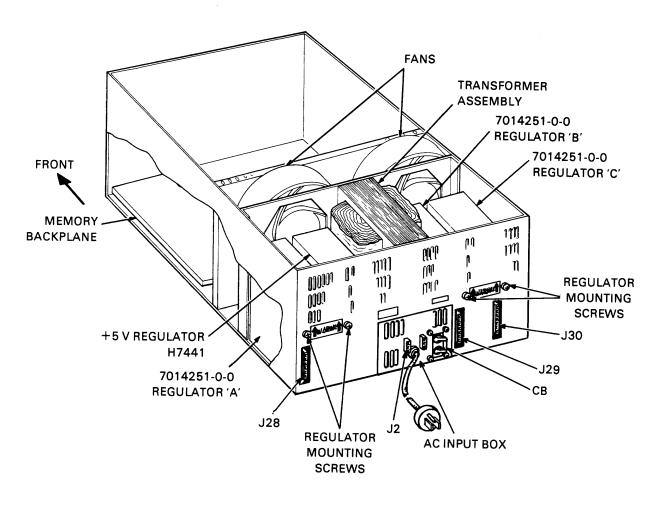

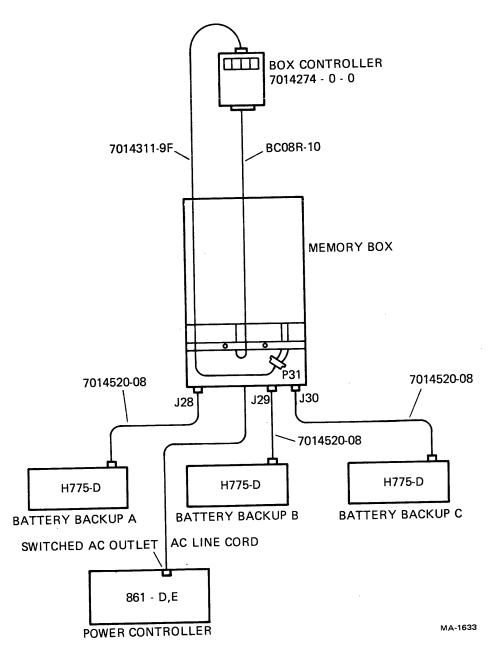

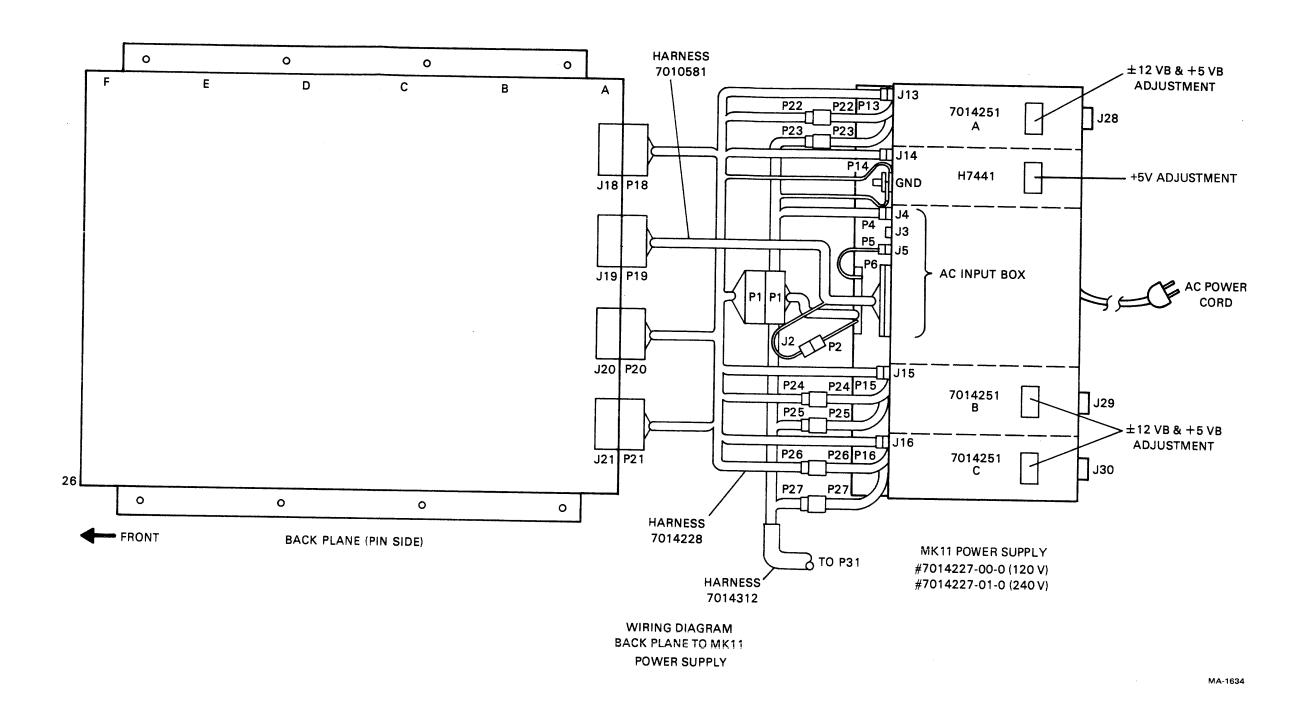

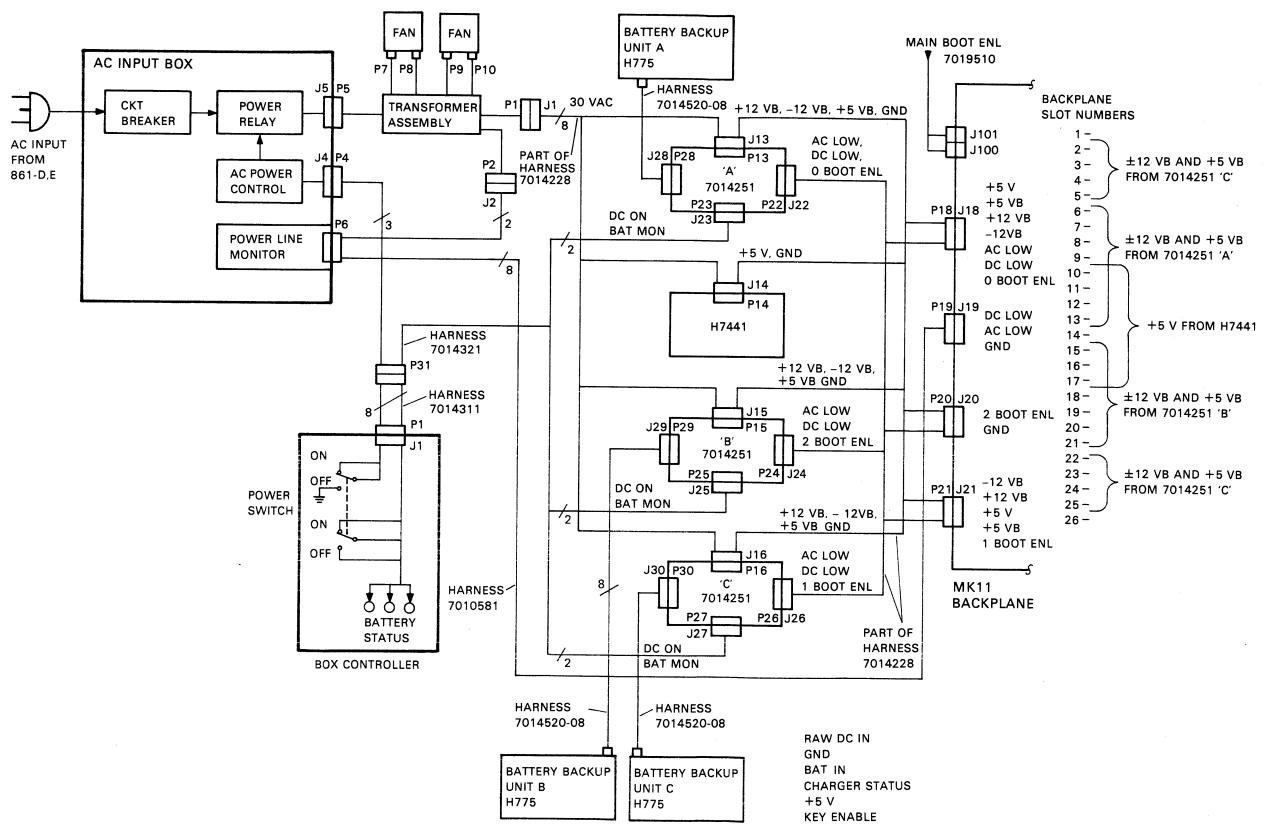

| 7.1       | GENERAL DESCRIPTION                                                                  | 7 i                    |

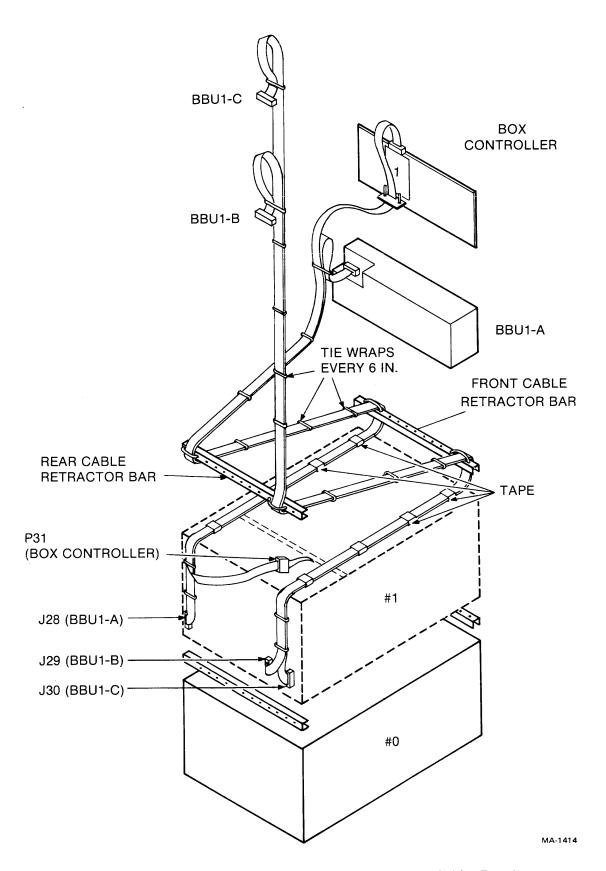

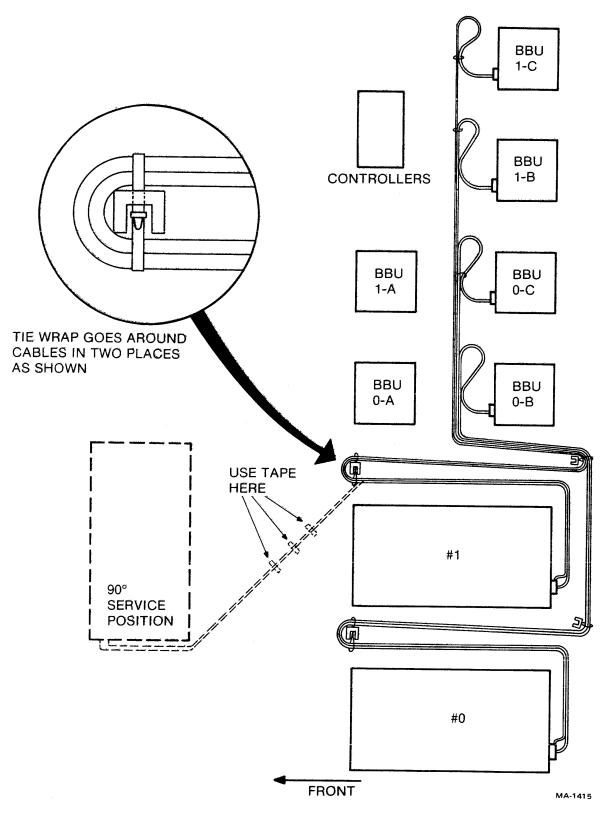

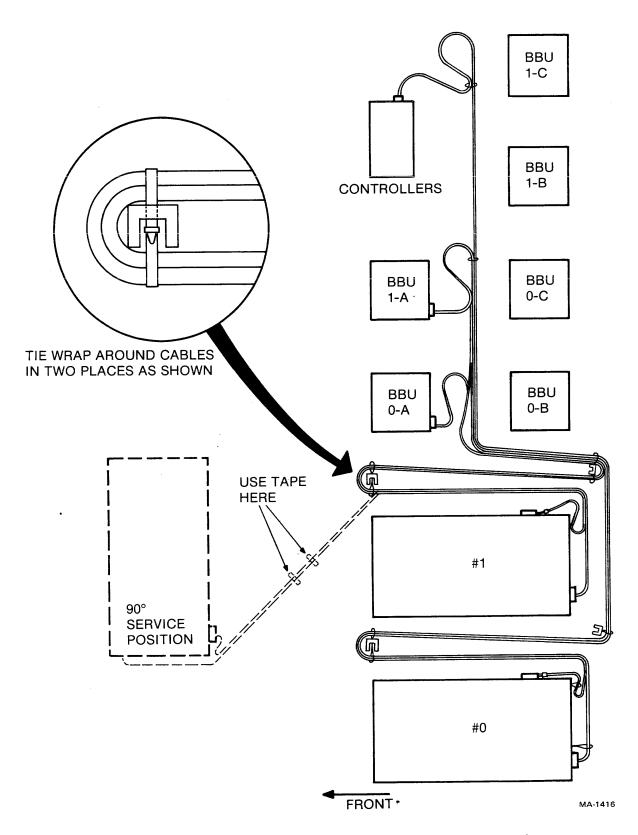

| 7.2       | POWER SUPPLY CABLES                                                                  | 7 1                    |

| 7.2.1     | External Power Cables                                                                | 7 1                    |

| 7.2.2     | Internal Power Harnesses                                                             | /-l                    |

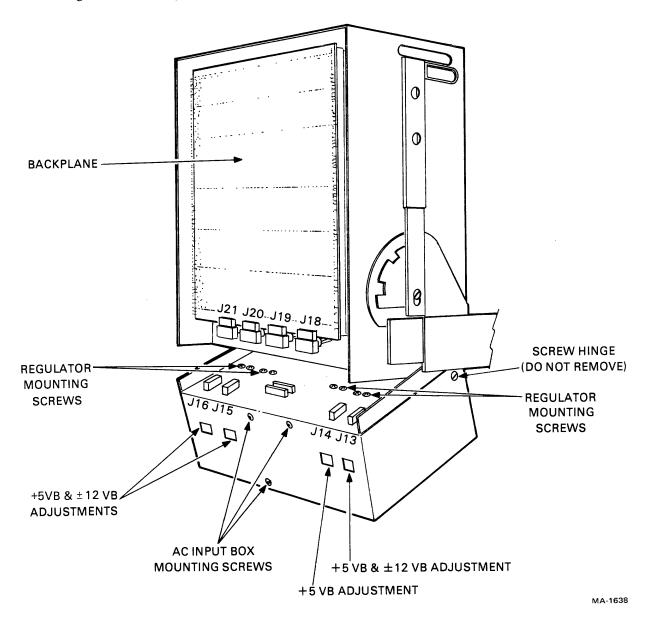

| 7.3       | POWER SUPPLY MAJOR ASSEMBLIES                                                        | /-1                    |

| 7.3.1     | Power Controller (861-D, E)                                                          | /-3                    |

| 7.3.2     | AC Input Box (7009811-1, 2)                                                          | /-5                    |

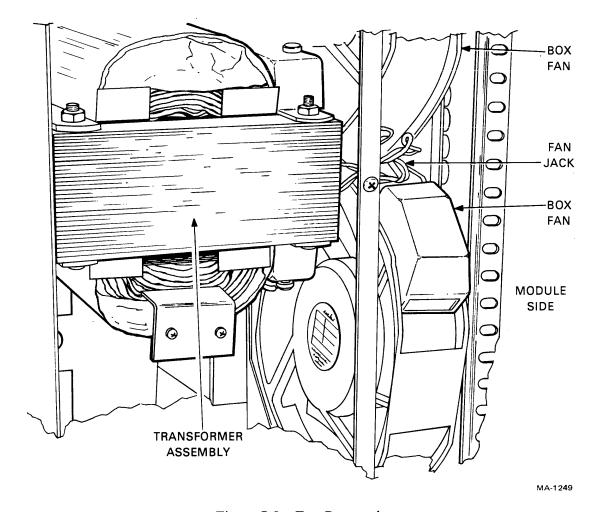

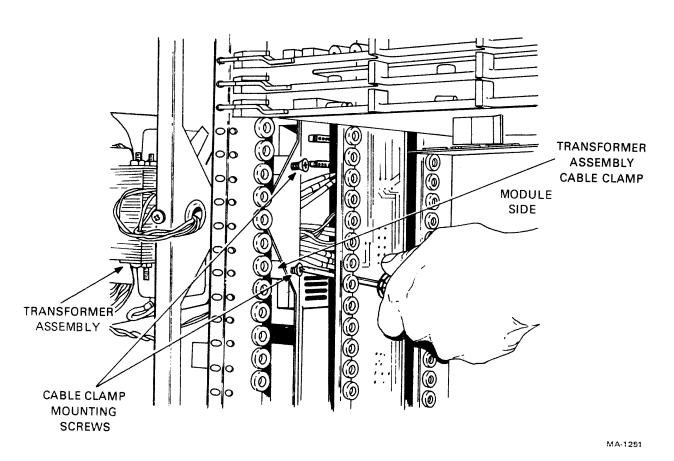

| 7.3.3     | Transformer Assembly (7011486)                                                       | /->                    |

| 7.3.4     | +5 Vdc Regulator (H7M1)                                                              | /-5                    |

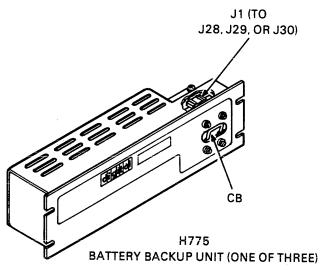

| 7.3.5     | +5 Vdc Regulator (H7441)<br>±12 VB and +5 VB Battery Backup Regulators (7014251) and | /-5                    |

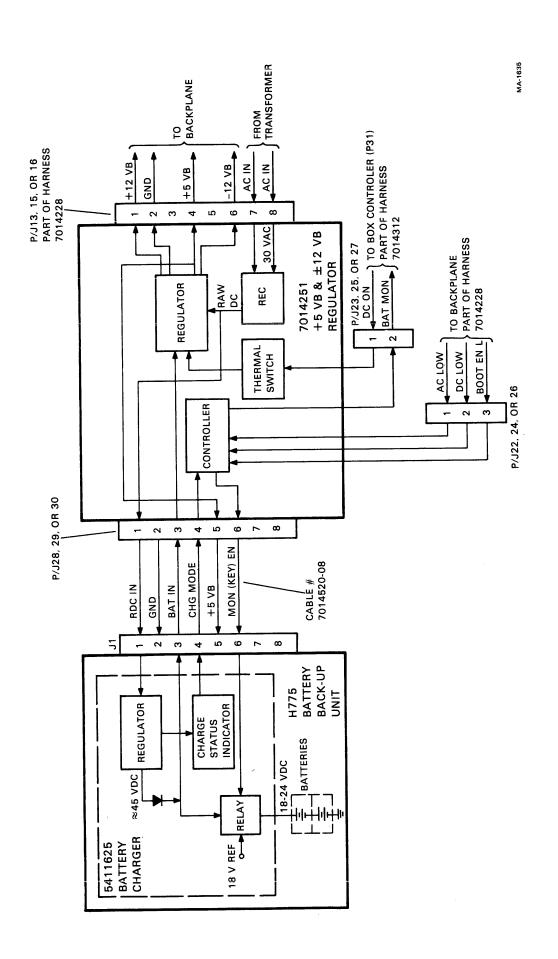

|           | Battery Backup Units (H775D)                                                         | 7 /                    |

|           | Buttery Backup Onits (11/13D)                                                        | /-6                    |

# CONTENTS (Cont)

|                        |                                                                  | Page   |

|------------------------|------------------------------------------------------------------|--------|

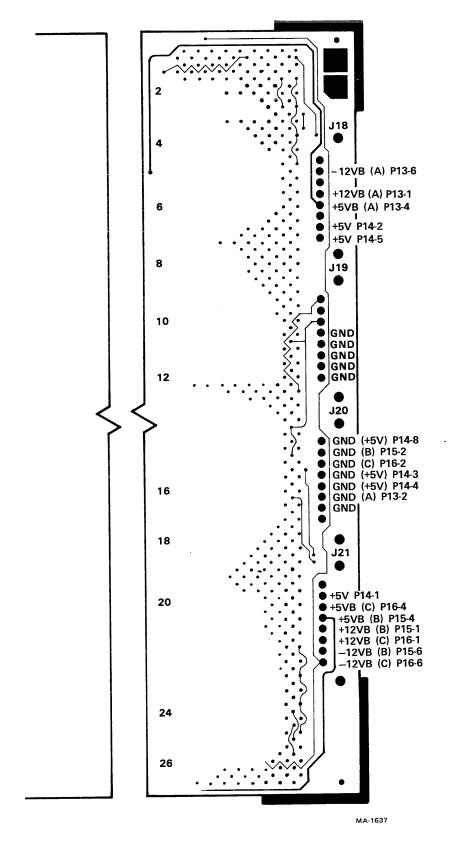

| 7.4                    | POWER DISTRIBUTION                                               | 7-6    |