ENGINEERING SPECIFICATIONS

NUMBER: ES:0001

DATE: 28 March 1968

BASIC PDP-11/30 DESCRIPTION

INSTRUCTION SET

Originated by: H. McFarland

Approved by:

Project Manager

This document is COMPANY CONSIDENT and is for internal company use only. Copying is expressly prohibited.

## **ABSTRACT**

Brief description of organization and concept of PDP-11 system and detailed discussion of the basic instruction set for the PDP-11/30 processor; includes basic Assembler Syntax.

Sample programs

Multiple precision (44bit) integer auth (add & subtract)

These specifications are for the instruction set implemented in the PDP-11/30 system. This initial system will contain a 4K word memory and have an average cycle time of 2.2us.

THESE SPECIFICATIONS ARE FOR INTERNAL DIGITAL USE ONLY AND ARE NOT TO BE RELEASED TO ANYONE OUTSIDE OF THE PDP-11 PROJECT WITHOUT APPROVAL OF PDP-11 ENGINEERING.

Future PDP-11 Engineering Specifications will deal with definition of expansion instructions for extended arithmetic, double precision, floating point, exec/user operations, memory relocation and protect, and other larger system features.

# This document is COMPANY CONFIDENTIAL

and is for internal use only by Digital Equipment Corp. employees. Copying is expressly prohibited.

#### PDP-11 DESCRIPTION AND INSTRUCTION SET

The PDP-11 is a two's-complement arithmetic, stored-program computer with a basic 16 bit instruction word. It is a two-address machine with a very powerful multi-accumulator/general register configuration, and is capable of doing memory-to-memory arithmetic operations. Most instructions can specify either byte or word data, enabling use as an 8- or 16-bit processor. When the byte mode is used, the accumulators operate as true 8-bit registers on two's-complement numbers. The memory is byte addressable with instructions that occupy 2 bytes.

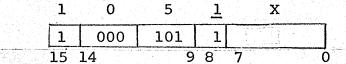

The basic instruction organization for binary two address operations is

|                | В        | OP |    |    | SOURCE |   |   | DESTINATION |  |

|----------------|----------|----|----|----|--------|---|---|-------------|--|

| 49<br>49<br>49 | <u> </u> | 14 | 12 | 11 |        | 6 | 5 | 0           |  |

where:

B indicates byte or word operation (except for multiply/divide instructions).

OP designates the operation to be performed.

SOURCE defines the location of source data.

DESTINATION defines the location of the destination data

SOURCE and DESTINATION are configured identically.

|     |                              | Several control of the |                                            |                                      |

|-----|------------------------------|------------------------|--------------------------------------------|--------------------------------------|

|     |                              |                        | REG                                        | [ 백기 ] - 전통 등이라는 전 경찰에 쓰는 사람이 되고 있다. |

|     |                              |                        |                                            | 나는 아일에서 가는 그 가능이 보이고 말하는 것은 일 같아!    |

|     |                              | <del></del>            |                                            | 병교 이 경험적으로 가장 그는 이 경우를 받았다.          |

|     | 77 70 0                      |                        |                                            | COTTDOTT                             |

|     | TT TO 9                      | 8                      | 6                                          | SOURCE                               |

|     | 보고 그 가장 시간을 다 되고 그리고 하는 것이다. |                        | 5.5 등이 없었습니다 하다 그                          | 그리트리는 사람들이 모스를 모르게 가다.               |

|     | 5 4 3                        | 2                      | Ω                                          | DESTINATION                          |

| 100 |                              |                        | All the second of the second of the second | DED T THE T T OT                     |

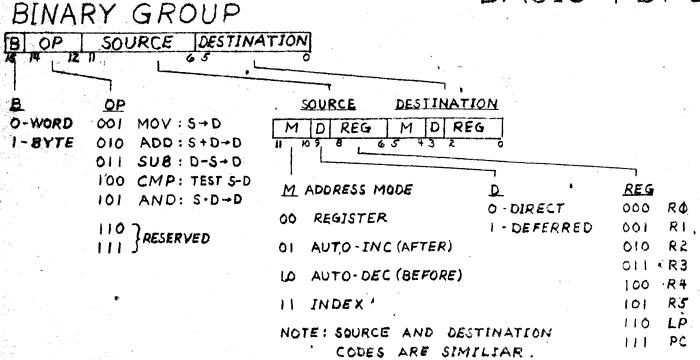

M is the mode

00 The register (bits 8-6 or 2-0) itself

- 01 Autoincrement using the register specified

- 10 Autodecrement using the register specified

- 11 Register specified is indexed by the following word.

Das register Ø moder?

D is the defer bit

REG is the register

| 000 RØ |                                                                                                                                     |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| 001 Rl | (1997년 1월 1일 1997년)<br>1982년 - 1일 - 1984년 - 1984년 - 1884년 - 1884년 |

| 010 R2 | general hardware                                                                                                                    |

| 011 R3 | register/accumulators                                                                                                               |

| 100 R4 |                                                                                                                                     |

| 101 R5 |                                                                                                                                     |

| 110 LP | Linkage Pointer                                                                                                                     |

| 111 PC | Program Counter                                                                                                                     |

There are three classes of instruction format:

Single word:

B OP SOURCE DESTINATION

15 0

Double word:

B OP SOURCE DESTINATION

15 0

immediate address or data

15 0

The second word can be used by either the source or destination field of the first word.

Triple word:

B OP SOURCE DESTINATION

15 0

immediate source address or data

15 0

immediate destination address or data

15 0

The second word is used by the source field of the first word, the third word is used by the destination field of the first word.

In addition, there is a hardware register that contains a STATUS word

| PRIORITY              | I  | N  | Z  | v   | С | UNDEFINED |  |

|-----------------------|----|----|----|-----|---|-----------|--|

| <b>1</b> 5 <b>1</b> 3 | 12 | 11 | 10 | 9 { | 8 | 7 0       |  |

where: PRIORITY

The operating program priority 000 - 111 which determines the major priority level of interrupts allowed.

|                            | Makka 1991 sangga sangga ngga sangga kangga kangga ngga ngga sangga sangga sangga sangga ng mga sangga sangga s                                                                           |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| , I                        | Reserved for INSTRUCTION set expansion (Not                                                                                                                                               |

|                            | implemented in basic set.)                                                                                                                                                                |

| N                          | A condition code indicating last result was <a href="NEGATIVE"><u>N</u>EGATIVE</a> .                                                                                                      |

| Z                          | A condition code indicating the last result was ZERO.                                                                                                                                     |

| <b>V</b>                   | A condition code indicating that the last arithmetic operation had a true arithmetic OVERFLOW (a change in sign when quantities of like sign are added).                                  |

| C<br>,                     | A condition code indicating that the last arithmetic operation had a <u>C</u> ARRY out from bit 15 (bit 7 if byte). Unchanged on unary instructions: Increment (INC) and Decrement (DEC). |

|                            | ne PDP-11 Assembler is as follows (Numbers are cified otherwise):                                                                                                                         |

| #L                         | designates a literal L (literal data is analogous to immediate instruction)                                                                                                               |

|                            | (#100 is the quantity 100)                                                                                                                                                                |

| Α                          | designates the absolute address of a location A                                                                                                                                           |

|                            | (A∢100 is the memory location 100)                                                                                                                                                        |

| @                          | designates a level of deferral                                                                                                                                                            |

|                            | (@100 is the contents of location 100)                                                                                                                                                    |

|                            | designates current location                                                                                                                                                               |

|                            | <pre>(•+10 is the memory location 10 bytes<br/>beyond the present instruction)</pre>                                                                                                      |

| <b>A.</b>                  | designates a value which is the octal equivalent of an ASCII A                                                                                                                            |

|                            | (#'A is the quantity 101)                                                                                                                                                                 |

| "AB                        | designates a value which is the octal equiva-<br>lent of an ASCII pair AB.                                                                                                                |

|                            | (#"AB is the quantity 102 101 = 041102)                                                                                                                                                   |

| 골 교교를 위대결합하다면 하다 가게 되었습니다. | 용상인 경험을 본통 성과 제가 전투는 경영화 중요한 등에 가지고 있다. 그는 말 보고 하지 않면 그렇게 했다. 이렇게 되었는데 하게 다니 아니다.                                                                                                         |

must IIIIII ABODEFG?

%m designates a register m, where m can be an expression that has a value in the range 0-7 (corresponding to registers RØ-R5, LP, PC). (m) +designates using register m (as defined above) in an autoincrement mode. (Increment is after use.) -(m)designates using register m (as defined above) in an autodecrement mode. (Decrement is before use.) who? For stacks, A (m) designates using register m (as defined above) in an indexed mode (A is added to the register in computing address). designates that a comment field follows; must be repeated on continuation lines. equates symbol to the value specified (K1=07123) defines the absolute address of a symbolically expressed location.

The symbology for description of the instruction operations is defined as:

(PC)+1 → (RØ) The contents of the register named PC are incremented and become the new contents of the register named RØ. The contents of PC do not change.

(PC)→((RØ)) The contents of the register named PC become the contents of the memory cell whose address is the contents of the register named RØ.

The contents of PC and RØ do not change.

(PC)+n This is symbolic of the program counter pointing to the next instruction. If there is no immediate data or address PC is incremented by 2. If there is an immediate byte or word data, or word address, the PC is incremented by 4. If there are 2 immediate references, the PC is incremented by 6.

E Effective Address

SE Source Effective Address

DE Destination Effective Address

Refer to Appendix B for a complete discussion of address modes.

Because of the nature of the possible stack operations in the PDP-11 instructions, stacks usually are built to expand towards zero; a push is an autodecrement and a pop is an autoincrement.

MOV A,  $-(R\emptyset)$  /Push A onto RØ stack

MOV (RØ)+, A /Pop A from RØ stack

The linkage pointer stack (pointed to by LP) must be built to expand towards zero since the interrupt stacking process decrements LP during the push operation and increments LP during the pop operation.

Note because of this:

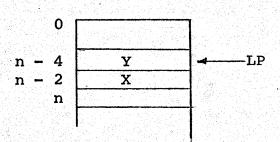

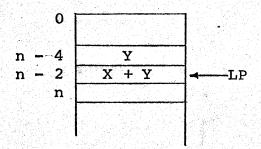

- 1: MOV #X,  $-(R\emptyset)$  /Push X onto stack

- 2: MOV #Y, -(RØ) /Push Y onto stack

- 3: ADD (RØ)+, @%RØ /Pop last on stack and

/add to former next to last, leave

/result in top of

/stack

Stack After 2:

Stack After 3:

Both instruction and data words are constrained to even address boundaries. Bytes (except a byte immediate reference) may be on even or odd address boundaries. This is a hardware restriction. It will result in faster and uniform execution times.

The following assumptions are common to all instructions, unless otherwise noted:

- 1. The B bit determines that the operand is a 16-bit word (B = 0) or an 8-bit byte (B = 1). Condition codes are set accordingly.

- 2. Two's complement arithmetic.

- 3. Condition codes are unchanged.

BINARY GROUP

MOV

| MO'        | V           | A      | В           |

|------------|-------------|--------|-------------|

| В          | 001         | SOURCE | DESTINATION |

| <b>1</b> 5 | 14 12       | 11 6   | 5 0         |

| (SE        | ) → (DE)    |        |             |

| (PC        | )+n -> (PC) |        |             |

Condition code operation same as in ADD, noted below.

There is no carry or overflow, however, as a MOV is an ADD to zero.

ADD

(SE) + (DE)

$$\longrightarrow$$

(DE)

(PC) +n  $\longrightarrow$  PC

If result negative  $1 \rightarrow N$ , otherwise  $\emptyset \rightarrow N$

If zero  $1 \rightarrow Z$ , otherwise  $\emptyset \rightarrow Z$

If carry  $1 \rightarrow C$ , otherwise  $\emptyset \rightarrow C$ .

If overflow  $1 \rightarrow V$ , otherwise  $\emptyset \rightarrow V$ .

SUBTRACT

mat transitive op.

| SUB |       | A      | and the second of the second |

|-----|-------|--------|------------------------------|

| В   | 011   | SOURCE | DESTINATION                  |

| 15  | 14 12 | 11 6   | . <b>5</b>                   |

(DE) - (SE)

$$\longrightarrow$$

(DE) (PC) +n  $\longrightarrow$  PC

Condition codes N, Z, and V operate as in ADD. If carry  $0 \rightarrow C$ , otherwise  $1 \rightarrow C$ .

COMPARE

| CM | P    | A      |             |

|----|------|--------|-------------|

| В  | 100  | SOURCE | DESTINATION |

| 15 | 14 1 | 2 11 6 | 5           |

(SE) - (DE), Set Condition Codes (PC)+n → (PC)

Condition codes operate as in SUB.

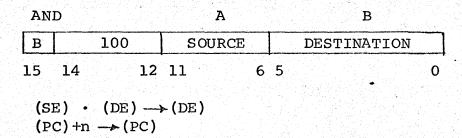

AND

Condition codes operate as in ADD. No carry or overflow results.

MULTIPLY, DIVIDE, ETC. (OP Codes 1100 - 1111)

Not fully defined at this time; not implemented in basic machine.

## GOTO (Unconditional Jump)

GOTO

| 0  | 001   | 0  | SOURCE | ØØØ111 | • |

|----|-------|----|--------|--------|---|

| 15 | 14 12 | 11 | . 6    | 5 0    |   |

This is a special case of the MOV instruction (move source word to PC).

The source field is the location to which the jump is desired.

GOTO  $A \equiv MOV \#A$ , %PC

This assembles as a two-word instruction unless A is held in a register:

if

$$(R\emptyset) = A$$

then GOTO @%RØ

assembles as MOV %RØ, %PC

Condition codes operate as in ADD.

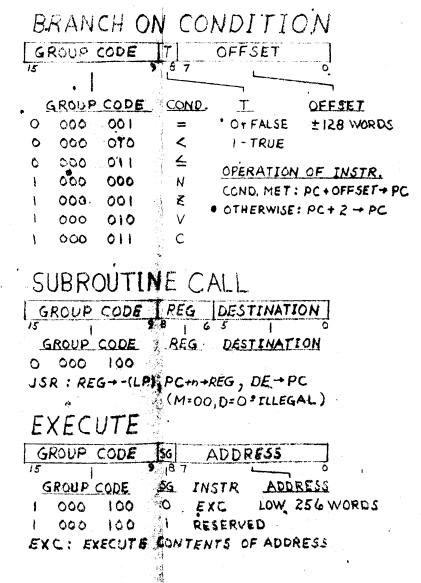

BRANCH

B-

X 0000 Y T OFFSET

15 14 11 10 9 8 7 0

Test condition and, if met, branch to a location which is from +127 to -128 words from location of Branch instruction. Condition codes are not changed. If condition met: (PC) + OFFSET  $\longrightarrow$  (PC), where OFFSET is an 8-bit 2's complement quantity. If condition not met: (PC)  $+2 \longrightarrow$  (PC)

| x | Y   | CONDITION*              | MNEMO<br>T=1 | DNICS<br>T=0 |                                                                   |

|---|-----|-------------------------|--------------|--------------|-------------------------------------------------------------------|

| 0 | 01  | $=(z\cdot\overline{v})$ | BEQ          | BNE          |                                                                   |

| 0 | .10 | <b>⟨</b> ,(N⊕V)         | BLT          | BGE          | Arithmetic Results Tests                                          |

| ó | 11  | <b>∠,</b> (z •V+N⊕V)    | BLE          | BGT          |                                                                   |

| 1 | øø  | N                       | BNS          | BNC          |                                                                   |

| 1 | Ø1  |                         | BZS          | BZC          | 하는 것이 되었다. 사람들이 가장 휴가를 다는 것을 받는다.<br>그림 사람들은 것이 하는 동료를 하는 것이 되었다. |

| 1 | 10  |                         | BVS          | BVC          | Condition Code Flag Tests                                         |

| 1 | 11  |                         | BCS          | BCC          |                                                                   |

<sup>\*</sup> If T is set the branch takes place if stated condition is met.

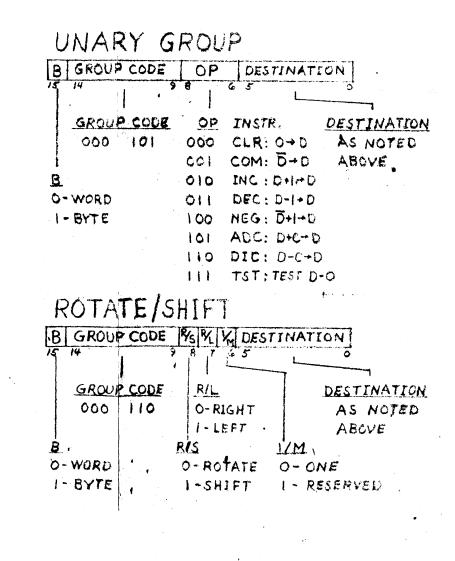

## UNARY GROUP

| В  | 000101 | OP  | DESTINATION |

|----|--------|-----|-------------|

| 15 | 14 9   | 8 6 | 5 0         |

Eight byte-word instructions which perform operations on the operand as designated by DESTINATION. Byte, word and DESTINATION operation same as noted before. Condition codes are set as noted.

CLEAR CLR A

OP =

$$\emptyset \emptyset \emptyset$$

$\emptyset \longrightarrow (DE)$

(PC) +n  $\longrightarrow (PC)$

Condition codes operate as in ADD.

COMPLEMENT

COM A

$OP = \emptyset \emptyset 1$

l's complement of (DE) → (DE)

(PC)+n → (PC)

Condition codes operate as in SUB.

INCREMENT

INC A

$OP = \emptyset 1\emptyset$

(DE) +

$$1 \rightarrow (DE)$$

$(PC) + n \longrightarrow (PC)$

Condition codes Z, N, V operate as in ADD; C is not changed.

DECREMENT .

DEC

$OP = \emptyset 11$

(DE)

$$-1 \rightarrow (DE)$$

$(PC)+n \rightarrow (PC)$

Condition codes Z, N, V operate as in ADD; C is not changed.

NEGATE

NEG Z

OP = 100

2's complement of (DE)  $\rightarrow$  (DE) (PC)+n  $\rightarrow$  (PC)

Condition codes operate as in SUB.

ADD CARRY

ADC

OP = 101

$$(DE) + (C) \rightarrow (DE)$$

$(PC)+n \longrightarrow (PC)$

Condition codes operate as in ADD.

DECREMENT IF CARRY DIC

$OP = 11\emptyset$

$$(DE) - (C) \rightarrow (DE)$$

$(PC)+n \rightarrow (PC)$

Condition codes operate as in SUB.

TEST

TST A

OP = 111

(PC)+n → (PC)

Condition codes operate as in ADD.

## ROTATE/SHIFT

| В  | 000110 | OP  | DESTINATION |

|----|--------|-----|-------------|

| 15 | 14 9   | 8 6 | 5 0         |

Rotates include carry to expand register to 9 or 17 bits.

Shift left fills bit  $\emptyset$  with  $\emptyset$ Shift right fills left bits with sign (arithmetic shift)

Condition codes N and Z operate as in ADD.

Condition code C receives the bit shifted or rotated out.

Condition code V is set if C changes, cleared otherwise.

| $\cup$ : |         |   | Operation | Mnemonics                                        |      |

|----------|---------|---|-----------|--------------------------------------------------|------|

| OP:      | Bit 8 = | 0 | Rotate    | ROT                                              |      |

|          | 8 =     | 1 | Shift     | SHF                                              |      |

|          | Bit 7 = | 0 | Right     |                                                  |      |

|          | 7 =     | 1 | Left      |                                                  |      |

|          | Bit 9 = | 0 | Once      | 20 12 1 원호 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 |      |

|          | 9 =     | 1 | Multiple  | (unimplemen                                      |      |

|          |         |   |           | basic machi                                      | ine) |

Example: ROT+1 (Rotate right once) =  $\emptyset\emptyset\emptyset$  (DE) Rotated right once  $\longrightarrow$  (DE) (PC)+n  $\longrightarrow$  (PC)

R

SUBROUTINE CALL

0 000 100 REG DESTINATION

15 9 8 6 5 0

JSR, Jump and Store Return

JSR

$$(LP)-2 \longrightarrow (LP)$$

$(REG) \longrightarrow ((LP))$

$(PC)+n \longrightarrow (REG)$

$DE \longrightarrow (PC)$

Α

DE cannot be REG undeferred. This is illegal and will trap to location 0.

EXECUTE

| EXC       |   | Α       |

|-----------|---|---------|

| 1 000 100 | 0 | ADDRESS |

| 15 9      | 8 | 7 0     |

EXC BEANCH

The instruction at ADDRESS of the low 256 memory words is executed. For all but subroutine linkage the effective PC becomes ADDRESS; for JSR the PC is that of the EXC instruction. Condition codes are a function of the executed instruction.

TRAP

| 1 000 | 100 | l | A DD | RESS |

|-------|-----|---|------|------|

| 15    | 9   | 8 | 7    | 0    |

Trap to ADDRESS of low 256 memory words is undefined and unimplemented in basic machine.

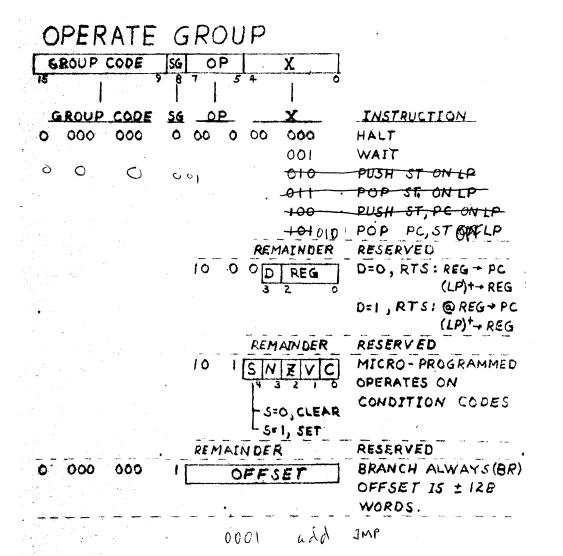

#### OPERATE GROUP

| 0 000 000 | SG  | OP  | Х   |

|-----------|-----|-----|-----|

| 15        | 8 6 | 7 5 | 4 0 |

Combinations of SG, OP and X provide the miscellaneous instructions noted:

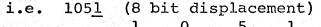

### BRANCH ALWAYS

where OFFSET is an 8-bit, 2's complement quantity allowing a +127, -128 word relative branch.

### CONDITION CODES OPERATES

$$OP = 101, SG = 0$$

| i<br>Si | 0 000 | 000 | 0 | 101        | s   | n Z | V  | C |

|---------|-------|-----|---|------------|-----|-----|----|---|

|         | 15    | 9   | 8 | <b>7</b> 5 | 4 3 | 3 2 | 1. | 0 |

Micro-coding of the X, bits 4 - 0, allows a variety of instructions:

| Bit | 4 | = | 0 | Clear codes noted          |

|-----|---|---|---|----------------------------|

| Bit | 4 | = | 1 | Set codes noted            |

| Bit | 3 | = | 0 | N code unaffected by bit 4 |

| Bit | 3 | = | 1 | N code affected by bit 4   |

| Bit | 2 | = | 0 | Z code unaffected by bit 4 |

| Bit | 2 | = | 1 | Z code affected by bit 4   |

| Bit | 1 | = | 0 | V code unaffected by bit 4 |

| Bit | 1 | = | 1 | V code affected by bit 4   |

| Bit | 0 | = | 0 | C code unaffected by bit 4 |

| Bit | 0 | = | 1 | C code affected by bit 4   |

## RETURN

$$OP = 100, SG = 0$$

|   | RTS       | 5 |     |   |   | Α   |          |

|---|-----------|---|-----|---|---|-----|----------|

|   | 0 000 000 | 0 | 100 | 0 | D | REG | 1        |

| 1 | L5 9      | 8 | 7 5 | 4 | 3 | 2 ( | <b>3</b> |

Return from subroutine either direct or indirect on register noted.

For D = 0: (REG)

$$\rightarrow$$

(PC), ((LP))  $\rightarrow$  (REG), (LP)+2  $\rightarrow$  (LP)

For D = 1: ((REG))  $\rightarrow$  (PC), ((LP))  $\rightarrow$  (REG), (LP)+2  $\rightarrow$  (LP)

Reminder of this OP unimplemented on basic machine.

## PUSH/POP

$$OP = 000, SG = 0$$

|    | 0 000 | 000 | 0 | 000 | X   |

|----|-------|-----|---|-----|-----|

| ٠. |       |     |   |     |     |

| ं  | L5 .  | 9   | 8 | 7 5 | 4 0 |

Direct coding of X provides the Halt, Wait and basic Push/Pop instructions. The remainder of this OP is unimplemented on the basic machine.

| MNEMONIC | X      | OPERATION                                                  |

|----------|--------|------------------------------------------------------------|

| HALT     | 00 000 | (PC)+2 → (PC), Halt                                        |

| WAIT     | 00 001 | (PC)+2 → (PC), Pause and stop cycling, wait for interrupt. |

| PUS      | 00 010 | Push ST on Linkage Pointer Stack                           |

| POS      | 00 011 | Pop ST off Linkage Pointer Stack                           |

| PUSP     | 00 100 | Push ST, PC on Linkage Pointer Stack                       |

| RTI      | 00 101 | Pop PC, ST off Linkage Pointer Stack                       |

RTI instruction is used for return from interrupt.

Typical operation: RTI

$$((LP)) \longrightarrow (PC)$$

$(LP) + 2 \longrightarrow (LP)$

$((LP)) \longrightarrow (ST)$

$(LS) + 2 \longrightarrow (LP)$

The remainder of OPERATE GROUP, SG = 0, is unimplemented on the basic machine.

The group code (bits 14-9) 000111 is unimplemented on the basic machine.

Traps on the Basic Machine:

While no specific trap instruction is provided on the basic machine, two trap locations exist. These are: location Ø for time-out and illegal instructions; and location 4 for unimplemented instructions. The trap results in ST and PC being pushed on the Linkage Pointer Stack and a new PC and ST obtained from the trap locations.

## APPENDIX A: Instruction Summary (Basic Set)

NOTE: All instruction numbers in octal representation except where digit is underlined it is a single binary digit. (First digit is always single digit and underline is implied.)

#### 2 octal digits 2 octal digits 6 bits 6 bits Binary 01 (Source) (Destination) MOV A, B 11 MOVB A, B 02 ADD A, B ADDB A, B 12 SUB A, B 03 13 SUBB A, B 04 CMP A, B 14 CMPB A, B 05 AND A, B 15 ANDB A, B Branch

|     | [1일 : 1 : 1 : 1 : 1 : 1 : 1 : 1 : 1 : 1 :                                                                      | 골목 보기를 되고 있는데 있는데 보니 보다는 보다는데 보다 보다 있다. 나는  |

|-----|----------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| BEQ |                                                                                                                | $001\underline{1}$ (Q = 8 bit displacement) |

| BNE |                                                                                                                | 10 001 <u>0</u>                             |

| BLT | Q                                                                                                              | $002\overline{1}$                           |

| BGE | Q                                                                                                              | 002 <u>0</u>                                |

| BLE | Q                                                                                                              | 003 <u>1</u>                                |

| BGT | Q diametric de la light de | 003 <u>0</u>                                |

| BCS | Q                                                                                                              | 103 <u>1</u>                                |

| BCC | Q                                                                                                              | 103 <u>0</u>                                |

| BVS | Q                                                                                                              | 102 <u>1</u>                                |

| BVC | Q                                                                                                              | 102 <u>0</u>                                |

| BZS | Q                                                                                                              | 101 <u>1</u>                                |

| BZC | Q                                                                                                              | 101 <u>0</u>                                |

| BNS | Q                                                                                                              | . 100 <u>1</u>                              |

| BNC | Q                                                                                                              | 1000                                        |

| BR  | Q                                                                                                              | 000 <u>1</u>                                |

|     |                                                                                                                | 네티어 보고 말하다면 보다 보는 하는 생님이 없는데 그렇게 되었다.       |

#### Execute

EXC A  $104\underline{0}$  (8 bit address of 256)

| Unary Group                                                        | 마이 보다 이번 이 경기를 통해되었습니다.<br>Hat Pin 이 이 아래의 이 등을 하는데 |                          | 6 bits          |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------|-----------------|

|                                                                    | CLR A                                                                                   | 0050                     | (Destination)   |

|                                                                    | CLRB A                                                                                  | 1050                     |                 |

|                                                                    | COM A                                                                                   | 0051                     |                 |

|                                                                    | COMB A                                                                                  | 1051                     |                 |

| 성당하는 그리 경찰과                                                        | INC A                                                                                   | 0052                     |                 |

|                                                                    | INCB A                                                                                  | 1052                     |                 |

|                                                                    | DEC A                                                                                   | 0053                     |                 |

|                                                                    | DECB A                                                                                  | 1053                     |                 |

|                                                                    | NEG A                                                                                   | 0054                     |                 |

|                                                                    | NEGB A                                                                                  | 1054                     |                 |

|                                                                    | ADC A<br>ADCB A                                                                         | 0055                     |                 |

|                                                                    | DIC A                                                                                   | 1055<br>0056             |                 |

|                                                                    | DIC A DICB A                                                                            | 1056                     |                 |

|                                                                    | TST A                                                                                   | 0057                     |                 |

|                                                                    | TSTB A                                                                                  | 1057                     |                 |

|                                                                    |                                                                                         |                          |                 |

| Rotate/Shift                                                       |                                                                                         |                          | 6 bits          |

|                                                                    | ROT+l A                                                                                 | 0060                     | (Destination)   |

|                                                                    | ROTB+1 A                                                                                | 1060                     |                 |

|                                                                    | ROT-1 A                                                                                 | 0062                     |                 |

|                                                                    | ROTB-1 A                                                                                | 1062                     |                 |

|                                                                    | SHF+1 A                                                                                 | 0064                     |                 |

| (1) 후 1 1일이 한 19 1년 1일<br>1일 1일 1 | SHFB+1 A<br>SHF-1 A                                                                     | 1064<br>0066             |                 |

|                                                                    | SHFB-1 A                                                                                | 1066                     |                 |

|                                                                    |                                                                                         | n un STAR<br>Resultation |                 |

| Subroutine Cal                                                     |                                                                                         |                          | 3 bits 6 k      |

| Franklika atau                                                     | JSR A, A                                                                                | 004 (1                   | Reg.) (Destinat |

| Subroutine Ret                                                     | urn                                                                                     |                          |                 |

|                                                                    |                                                                                         |                          | 3 bits          |

|                                                                    | RTS R                                                                                   | 00020                    | (Reg.)          |

|                                                                    | RTS R                                                                                   | 00021                    | (Reg.)          |

| Operate Group,                                                     | Condition Codes                                                                         |                          |                 |

|                                                                    | CLC                                                                                     | 000241                   |                 |

|                                                                    | SEC                                                                                     | 000251                   |                 |

|                                                                    | CLV                                                                                     | 000242                   | North<br>Tailte |

|                                                                    | SEV                                                                                     | 000252                   |                 |

|                                                                    | CLZ                                                                                     | 000243                   |                 |

|                                                                    | SEZ                                                                                     | 000253                   |                 |

|                                                                    | CLN                                                                                     | 000250                   |                 |

|                                                                    | SEN                                                                                     | 000270                   |                 |

|                                                                    | CNZ                                                                                     | 000254                   |                 |

|                                                                    | CCC                                                                                     | 000257                   | • .             |

|                                                                    | SCC                                                                                     | 000277                   |                 |

| Operate Group, | Push/Pop | Agradica, agricum secondo, o periodo do filos de contiguado. |

|----------------|----------|--------------------------------------------------------------|

|                | HALT     | 000000                                                       |

|                | WAIT     | 000001                                                       |

|                | PUS      | 000002                                                       |

|                | POS      | 000003                                                       |

|                | PUSP     | 000004                                                       |

|                | RTI      | 000005                                                       |

|                |          |                                                              |

|                |          |                                                              |

|                |          |                                                              |

Exec mode?

## APPENDIX B:

Typical source and destination configurations are shown below together with the M, D, and REG bit patterns.

| CODE       | SYMBOL     | MEANING                                                                |                                             |

|------------|------------|------------------------------------------------------------------------|---------------------------------------------|

| M D REG    |            |                                                                        |                                             |

| 00 0 000   | %RØ        | E = RØ                                                                 | RØ contains data                            |

| 00 1 000   | @%RØ       | $\mathbf{E} = (\mathbf{R}\emptyset)$                                   | RØ contains address                         |

| 01 0 000   | +(RØ)      | $E = (R\emptyset),$ $(R\emptyset) + 2 \longrightarrow (R\emptyset)$    | Autoincrement                               |

| 01 1 000   | @+(RØ)     | $E = ((R\emptyset)),$ $(R\emptyset) + 2 \longrightarrow (R\emptyset)$  | Autoincrement, defer.                       |

| 10 0 000 , | - (RØ)     | $(R\emptyset)-2 \longrightarrow (R\emptyset),$<br>$E = (R\emptyset)$   | Autodecrement                               |

| 10 1 000   | @- (RØ)    | $(R\emptyset)-2 \longrightarrow (R\emptyset),$<br>$E = ((R\emptyset))$ | Autodecrement, defer.                       |

| 01 0 111   | # <b>L</b> | E = (PC) + 2                                                           | Immediate literal                           |

| 01 1 111   | @#L<br>A   | E = ((PC)+2)                                                           | Defer thru immediate                        |

| 11 0 001   | A(Rl)      | E = (R1) + ((PC) + 2)                                                  | ) Indexed by Rl<br>A is next word           |

| 11 1 001   | A (R1)     | E = (R1) + ((PC) + 2)                                                  | 2)) Index defer Rl                          |

| 11 0 111   | A          |                                                                        | Alternate form of defer thru immediate mode |

| 11 1 111   | @A         |                                                                        | -2)) Above with additional defer. level     |

## NOTES: 1) A can be an expression.

- 2) RØ, Rl designate registers RØ, Rl. These can be named with expressions.

- 3) Note the ease of counting instruction length with this symbology. The base instruction is 2 bytes, and each expression not enclosed by parenthesis or preceded by % adds another word.

## APPENDIX B (continued):

MOV %RØ, %Rl 1 word

MOV #L, %Rl 2 words

MOVB #L, %Rl 2 words

MOV A, B 3 words

MOV A,  $(R\emptyset)$  + 2 words

MOV A(R $\emptyset$ ), B(R1) 3 words

# BASIC PDP11 INSTRUCTIONS

## NOTES: 1.INSTRUCTION LENGTH:

ONE WORD : OPERATE, BRANCH, EXECUTE; OTHERS IF SOURCE AND DESTINATION NOT ENDEXED OR AUTO-INC ON PC.

TWO WORDS: EITHER SOURCE OR DESTINATION IS INDEXED BY NEXT WORD OR THE AUTO-INC OF PC PROVIDES AN IMMEDIATE OFERAND. A WORD IS REQUIRED FOR THIS DATA.

THREE WORDS; BOTH SOURCE AND DESTINATION ARE INDEXED OR HAVE AN IMMEDIATE ORERAND, NEXT WORD AFTER INSTRUCTION REFERS TO SOURCE; NEXT WORD REFERS TO DESTINATION.

- 2, GROUP CODE DOD III IS RESERVED,

- 3. RESERVED INSTRUCTION CODES ARE TRAPPED TO LOCATION 4; ILLEGAL INSTRUCTIONS ARE TRAPPED TO LOCATION Ø.

- 4. TRAP: ST AND PC ARE PUSHED ON LPINEW PC AND ST FROM TRAP LOCATION.