# Digital Equipment Corporation Maynard, Massachusetts

PDP-12 User's Manual

FPP-12

Floating Point Processor

# FPP-12 FLOATING POINT PROCESSOR USER'S MANUAL

1st Edition December 1970 2nd Edition April 1971

Copyright © 1970, 1971 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change with-

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

PDP

FLIP CHIP DIGITAL

**FOCAL**

COMPUTER LAB

#### CONTENTS

|           |                                                                | Page |

|-----------|----------------------------------------------------------------|------|

| CHAPTER 1 | FPP12 PROGRAMMING DATA                                         |      |

| 1.1       | Scope of the Manual                                            | 1-1  |

| 1.2       | Introduction                                                   | 1-1  |

| 1.3       | Floating Point Number System                                   | 1-2  |

| 1.4       | System Description                                             | 1-3  |

| 1.5       | FPP12 Register Organization                                    | 1-4  |

| 1.6       | Active Parameter Table                                         | 1-6  |

| 1.7       | Programming the FPP12                                          | 1-7  |

| 1.7.1     | Initialization                                                 | 1-7  |

| 1.7.2     | Serial vs Parallel Processing                                  | 1-10 |

| 1.7.3     | IOT Instructions                                               | 1-10 |

| 1.7.4     | IOT List                                                       | 1-11 |

| 1.7.5     | Instruction Set-Address Methods                                | 1-12 |

| 1.7.6     | Index Registers                                                | 1-12 |

| 1.7.7     | Instruction Set                                                | 1-12 |

| 1.8       | Data Reference Instructions                                    | 1-13 |

| 1.8.1     | Special Format 1                                               | 1-14 |

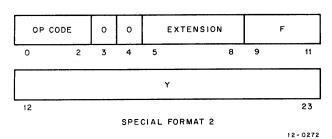

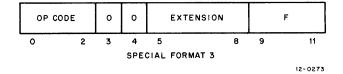

| 1.8.2     | Special Format 2                                               | 1-14 |

| 1.8.3     | Conditional Jumps                                              | 1-15 |

| 1.8.4     | Pointer Moves                                                  | 1-15 |

| 1.8.5     | Special Format 3                                               | 1-16 |

| 1.8.6     | Operate Group - Special Format 3                               | 1-17 |

| CHAPTER 2 | FPP12 PROGRAMMING EXAMPLES                                     |      |

| 2.1       | Introduction                                                   | 2-1  |

| 2.2       | Program Initialization                                         | 2-1  |

| 2.3       | Index Registers as Address Modifiers and Loop Counters         | 2-3  |

| 2.4       | Use of Index Registers to Create Push-Down Stacks              | 2-4  |

| 2.5       | Branch or Jump on Condition Instructions                       | 2-5  |

| 2.6       | Writing Re-entrant Subroutines                                 | 2-5  |

| 2.7       | Use of the FPHLT Instruction                                   | 2-6  |

| 2.8       | Debugging FPP12 Programs on Units Attached to PDP-12 Computers | 2-6  |

| 2.9       | Using the Execute Stop Switch                                  | 2-7  |

| 2.10      | Care Necessary in the Use of Examine and Deposit               | 2-7  |

### CONTENTS (Cont)

|            |                                                           | Page |

|------------|-----------------------------------------------------------|------|

| 2.11       | Additional Programming Hints                              | 2-8  |

| 2.11.1     | Illegal Mantissa                                          | 2-8  |

|            |                                                           |      |

| CHAPTER 3  | FPP12 COMPONENTS                                          |      |

| 3.1        | FPP12 Hardware Description                                | 3–1  |

| 3.2        | Description of Registers                                  | 3-2  |

| 3.3        | Major States                                              | 3-5  |

| 3.4        | Description of Registers                                  | 3-9  |

| 3.5        | Register Gating System                                    | 3-10 |

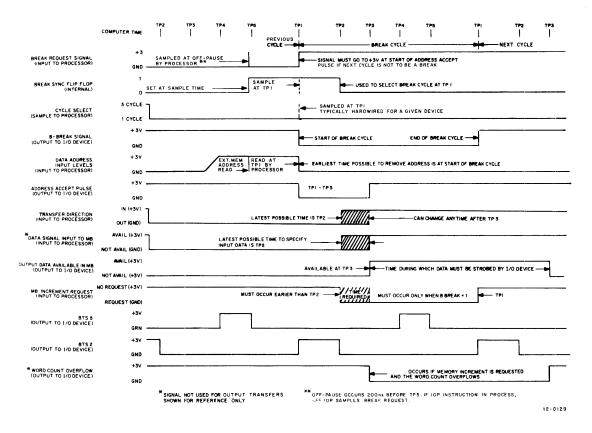

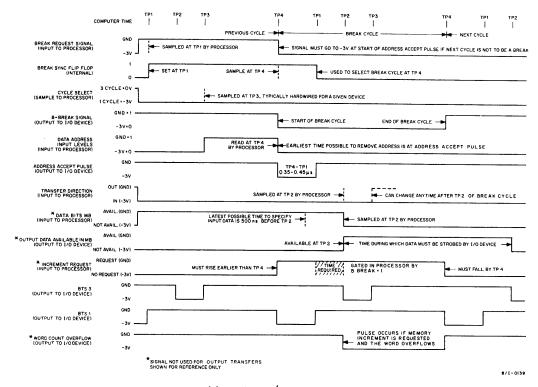

| 3.6        | Data Break Control                                        | 3-10 |

| 3.7        | Modules Introduced in the FPP12                           | 3-11 |

| 3.8        | Flow Diagrams                                             | 3-12 |

| 3.8.1      | INITIATE                                                  | 3-13 |

| 3.8.2      | FETCH                                                     | 3-14 |

| 3.8.3      | DEPOSIT                                                   | 3-15 |

| 3.8.4      | EXIT                                                      | 3-17 |

| 3.8.5      | LDA and STR                                               | 3–17 |

| 3.8.6      | DP ADD and SUB                                            | 3-17 |

| 3.8.7      | ADD/SUB of FP NOS                                         | 3-18 |

| 3.8.8      | MULTIPLY                                                  | 3-19 |

| 3.8.9      | DIVIDE                                                    | 3-19 |

| 3.8.10     | Special Instructions                                      | 3-20 |

| 3.9        | Maintenance Logic                                         | 3-20 |

|            |                                                           |      |

| CHAPTER 4  | FPP12 INSTALLATION                                        |      |

| 4.1        | Installation                                              | 4-1  |

| 4.2        | Ac Power Requirements                                     |      |

| 4.3        | Check Out                                                 | 4-3  |

|            |                                                           |      |

|            | ILLUSTRATIONS                                             |      |

| Figure No. | Title                                                     | Page |

| 1-1        | PDP-12 12/40 System Configuration                         | 1-4  |

| 1-2        | Typical Configuration of the PDP-12 with Multiply Devices | 1-5  |

#### ILLUSTRATIONS (Cont)

| Figure No | . Title                                            | Page |

|-----------|----------------------------------------------------|------|

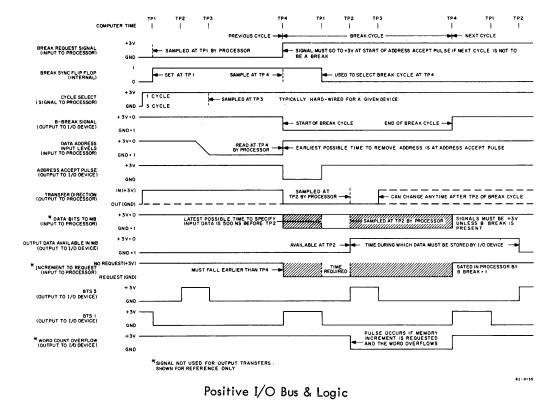

| 3-1       | PDP-12 Single Cycle Data Break Timing              | 3-2  |

| 3-2       | PDP-8 Single Cycle Data Break Timing               | 3-3  |

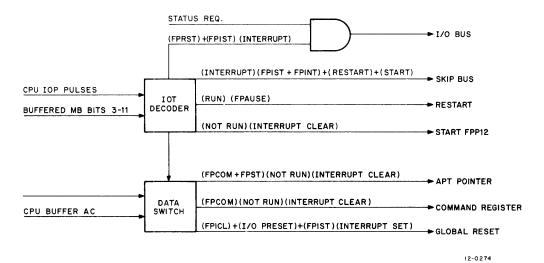

| 3-3       | FPP12 User IOT Decoder System                      | 3-4  |

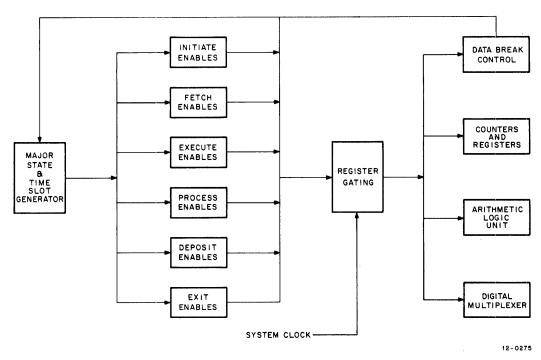

| 3-4       | Timing and Enable System in FPP12                  | 3-4  |

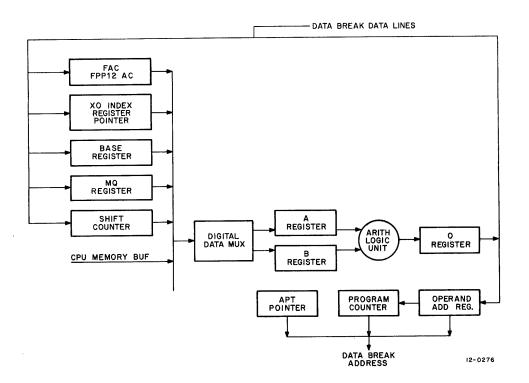

| 3-5       | FPP12 Data Flow System                             | 3-5  |

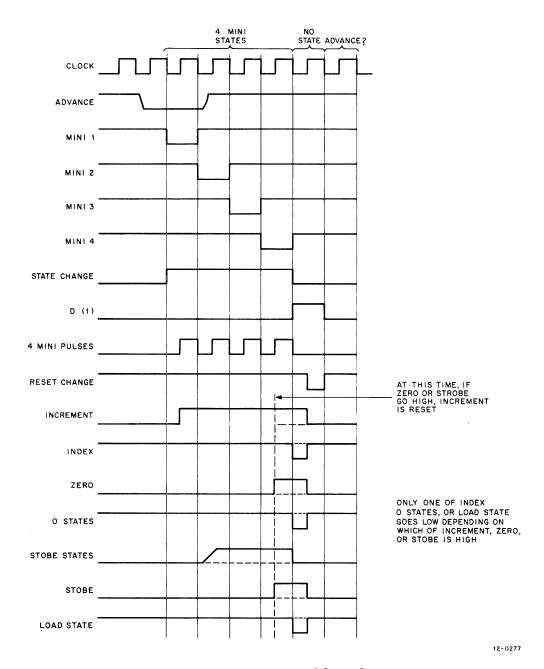

| 3-6       | Timing Diagram of State Generator                  | 3-6  |

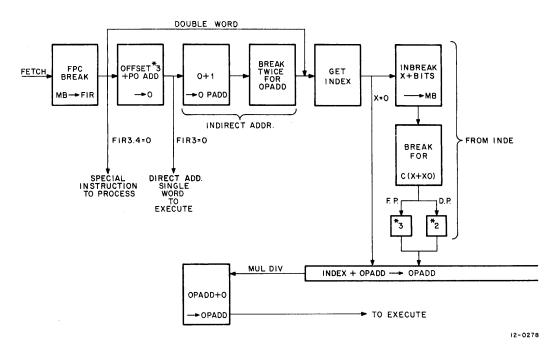

| 3-7       | Block Diagram of FPP12 FETCH Flow                  | 3-15 |

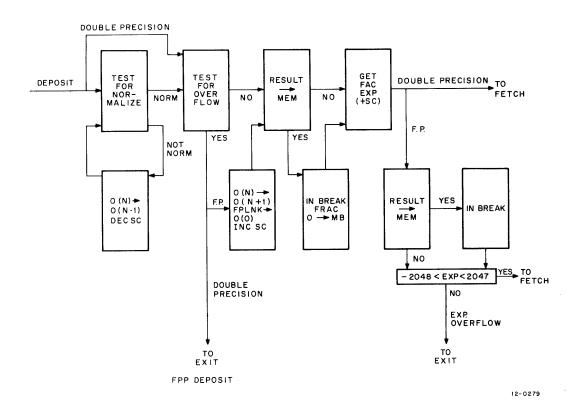

| 3-8       | Block Diagram of FPP12 DEPOSIT Flow                | 3-16 |

|           | TABLES                                             |      |

| Table No. | Title                                              | Page |

| 1-1       | Active Parameter Table Format                      | 1-7  |

| 1-2       | AC After Read Status Instruction                   | 1-8  |

| 1-3       | Command Register Setting                           | 1-8  |

| 1-4       | Instruction Execution Times                        | 1-9  |

| 2-1       | APT After FEXIT in Example 2–1                     | 2-3  |

| 3-1       | Functions Performed by DEC74181                    | 3-13 |

| 3-2       | Equivalence Between Instructions and Flow Routines | 3-21 |

| 3-3       | Definition of AC Bits After IOT 6562 Read States   | 3-22 |

| 4-1       | PDP-8/L, PDP-8/I Positive Bus and PDP-8/E          | 4-1  |

| 4-2       | PDP-8, LINC-8, and PDP-8/1 with Negative Bus       | 4-2  |

| 4-3       | Module Changes for Negative Bus Computers          | 4-2  |

## CHAPTER 1 FPP12 PROGRAMMING DATA

#### 1.1 SCOPE OF THE MANUAL

This manual contains instructions for programming and servicing the Floating Point Processor (FPP12), a peripheral device for PDP-8 and PDP-12 Computers. Chapters 1 and 2 contain programming information. Chapter 3 describes the logical components of the FPP12. Installation and check-out procedures are found in Chapter 4. It is assumed that the reader is familiar with the operation of the PDP-8/I, PDP-8/L, PDP-8, LINC-8, PDP-8/E or PDP-12 Computers. It is suggested that the reader have as a reference the FPP Assembler Manual.

#### 1.2 INTRODUCTION

The Floating Point Processor (FPP12) is a programmable, peripheral, digital processor that attaches to the input/output (I/O) bus of any PDP-8, PDP-8/I, PDP-8/L, PDP-8/E, LINC-8, or PDP-12 Computer. The FPP12 is a parallel processor with its own instruction set. It utilizes the direct memory access or data break facility to "steal" memory cycles from the Central Processor Unit (CPU). Similar to a disk, the FPP12 is activated by the CPU through the use of programmed input/output IOT instructions. Once activated, the FPP12 steals a maximum of 50 percent of the memory cycles from the PDP-8, PDP-8/I, PDP-8/L, or PDP-8/E CPU. For the PDP-12 there are two operating modes, parallel and serial.

In parallel mode, the FPP12 steals a maximum of 50 percent, or every other memory cycle, from the PDP-12, thus permitting the PDP-12 and the FPP12 to operate simultaneously. Once initiated in serial mode, the FPP12 locks out the PDP-12 CPU for the duration of a complete calculation. Serial mode increases the FPP12 calculation speed by approximately 20 percent.

The FPP12 performs arithmetic operations on floating-point numbers 20 to 100 times faster and with 100 to 200 fewer memory cycles than software interpreters. The FPP12 instruction set facilitates the programming of complicated algorithms and the building of compilers for mathematical languages. Variable length instructions are part of a flexible addressing scheme. Direct addressing of 32K of

core memory is available using a 24-bit instruction format. A 12-bit instruction format, in which the operand address is relative to a programmable base register, reduces program length and facilitates re-entrant coding. Any eight sequential core locations can be used as an index register to modify operand addresses. Index registers are adjusted prior to use in address modification, to account for the different number of core locations used in the two data formats permitted by the FPP12.

#### 1.3 FLOATING POINT NUMBER SYSTEM

The term floating point implies a movable binary point similar to the movable decimal point used in scientific notation. An exponent is used to keep track of the number of spaces the binary or decimal point is moved.

Examples of scientific notation:

$$234 = 23.4 \times 10^{1} = 2.34 \times 10^{2}$$

Examples of binary floating-point notation:

$$(1011) = (101.1) \times 2^{1} = (10.11) \times 2^{2} = (1.011) \times 2^{3}$$

$(1.011) \times 2^{3} = 0.1011 \times 2^{4} = 0.01011 \times 2^{5}$

In the example of binary floating-point notation given above, there are four significant bits. However, in the last term, the fraction that multiplies the exponent contains six bits. Given a fixed number of bits, it is desirable to adjust the exponent and the binary point to eliminate leading zeros. This adjustment retains the maximum numerical significance for a given format length. The FPP12 normalizes or removes leading zeros as the last step in every floating-point arithmetic operation.

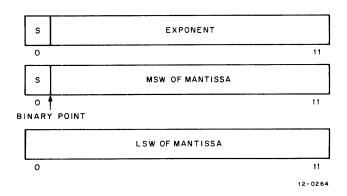

The floating-point data format used by the FPP12 is identical to the format used by the PDP-8 floating-point system (DEC-08-YQYB-D). As shown below, there is a 12-bit signed 2's complement exponent and a 24-bit signed 2's complement mantissa.

The FPP12 carries all calculations to 28 bits of precision, then rounds to 24 bits after normalization; after rounding, the result is rechecked for proper normalization prior to completing the instruction.

In fixed-point arithmetic, the precision of a number varies with the number's magnitude. In addition, the range of fixed-point numbers is generally limited in most mini computers to 12 or 16 bits. With the FPP12, the number range is  $2^{+2047}$  to  $2^{-2048}$ ; precision is maintained at 24 bits throughout the number range. Exceeding the upper limit,  $2^{+2047}$ , causes the FPP12 to interrupt the PDP-12 CPU and set its exponent overflow status bit. A calculation resulting in a exponent smaller than  $2^{-2048}$  is an exponent underflow that can cause a program interrupt. At initialization, the programmer has the option to request that the underflow trap be ignored, in which case the result of calculation in which underflow occurred is set to 0.

#### Fixed-Point 24-Bit Fraction Format

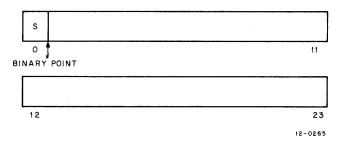

For those calculations where full 24-bit precision is not necessary and where core space is at a premium, the FPP12 can be used in fixed-point 24-bit mode. Each operand consists of a 24-bit signed 2's complement fraction as shown below.

As in the case of the floating-point mode, each calculation is carried to 28 bits of precision and rounded to 24 bits but no normalization is performed. Therefore, leading zeros occur which reduce the precision of subsequent calculations. In fixed-point mode, calculations resulting in a fraction overflow cause the FPP12 to initiate a program interrupt with the fraction overflow status bit set to 1.

#### 1.4 SYSTEM DESCRIPTION

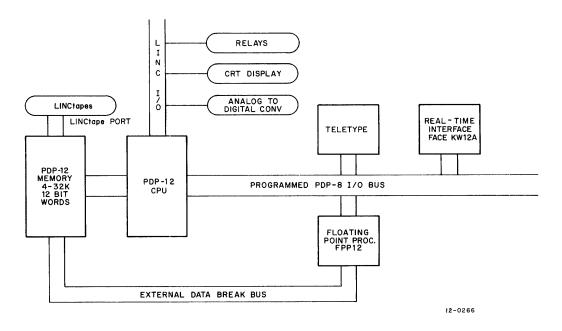

The FPP12 is initialized and interrogated as to its status via PDP-8 IOT instructions issued on the programmed I/O bus. Once initialized, the FPP12 operates as a processor fetching instructions and operands via the data break or direct memory access bus. A typical system configuration consisting of a PDP-12 and a FPP12 is shown in Figure 1-1. Note that the PDP-12 Computer contains two data break ports; one is permanently reserved for the LINCtape control, the other is available for a device

The FPP12 attaches to the EXTERNAL data break and programmed I/O bus of the PDP-12 computer without additional hardware.

Figure 1-1 PDP-12 12/40 System Configuration

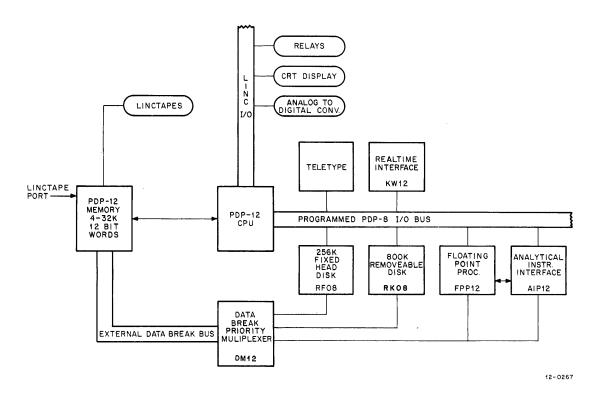

such as a disk, data break card reader control CD12, or the FPP12. If two or more data break devices, in addition to the LINCtape, are attached to the PDP-12, a memory multiplexer (DM12) is generally required (see Figure 1-2). The exception is that the Analytical Instrumentation Package (AIP12) and the FPP12 may both be attached to the data break bus without a memory multiplexer. A special cable that connects the FPP12 to the AIP12 contains the signals necessary to arbitrate data break requests between the AIP12 and the FPP12.

On the PDP-8, PDP-8/I, and PDP-8/L Computers only one direct memory access port is available; attaching an FPP12 and DECtape, for example, requires a memory multiplexer. Each data break device has its own memory port on the PDP-8/E Computer; therefore, a separate memory multiplexer is not required on the PDP-8/E for up to 12 separate data break devices.

#### 1.5 FPP12 REGISTER ORGANIZATION

There are eight registers in the FPP that are of interest to the programmer. The functions of these registers, named below, will be discussed in the remainder of this chapter.

| Register                            | <u>Function</u>                                                 |

|-------------------------------------|-----------------------------------------------------------------|

| Floating Point Accumulator (FAC)    | 36-bit register split into 12-bit exponent and 24-bit fraction. |

| Index Register Address Pointer (X0) | Contains the 15-bit core location of index register 0.          |

Figure 1-2 Typical Configuration of the PDP-12 with Multiple Devices

| Register                             | Function                                                                                                                                                                                                                                                               |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Base Register (Base)                 | Contains the 15-bit base address used in calculating single-word addresses.                                                                                                                                                                                            |

| Floating Point Program Counter (FPC) | Contains the 15-bit address that is the location of the next FPP12 instruction.                                                                                                                                                                                        |

| Active Parameter Table Pointer       | Loaded via IOTs with the 15-bit address of<br>the first location of the Active Parameter<br>Table (APT).                                                                                                                                                               |

| Command Register                     | The command register is loaded with an IOT instruction. The command register selects FPP12 operating modes, sets the FPP12 interrupt enable, chooses the important parameters to be saved in the APT, and fixes the most significant 3 bits of the 15-bit APT pointer. |

| Status Register                      | The status register may be interrogated by the CPU to determine the cause of an exit operation by the FPP12. The status register also indicates if the FPP12 is in the run or (run) $\Lambda$ (FPAUSE) state.                                                          |

#### Register

#### Operand Address Register

#### **Function**

The operand address register is deposited in the APT and contains one of the following:

- a. If the last address-bearing instruction prior to the exit was of the data reference class, the operand address register contains the 15-bit address of the least significant word of the operand.

- b. If the last address-bearing instruction prior to the exit was an executed jump instruction, the operand address register contains the jump address.

- c. If after initialization an exit is performed prior to the execution of a jump or data reference instruction, the operand address register contains the FPC originally set by the APT.

- d. The instructions SET BASE (SET B) and SET X0 REGISTER (SET X) have no effect on the operand address register.

#### 1.6 ACTIVE PARAMETER TABLE

The Active Parameter Table (APT) (refer to Table 1-1) contains information necessary for starting or restarting an FPP12 program. The APT is defined as any two to eight locations in core. The APT pointer is set to point at the first entry of the APT. The initialization procedure for the FPP12 includes two IOT instructions that set up a command register and set the 15-bit APT pointer to the first location of the APT, shown as location P in Table 1-1. Following the second IOT, the FPP12 picks up the contents of the APT. Whenever the FPP12 performs an EXIT, the current contents of the APT overlay the initial APT contents.

The APT performs three services for the programmer.

- a. It reduces the number of IOTs necessary to initialize the FPP12. This reduces the CPU program overhead which is critical in multitask and time-shared environments.

- It automatically saves the status of interrupted FPP12 programs.

- c. It provides convenient access to the information necessary for debugging FPP12 programs and determining the cause of FPP12 "error" exits such as exponent overflow, underflow, or attempted division by 0.

With the exception of the operand address, all parameters contained in the APT are used in initializing the FPP12. The operand address is stored for the use of the CPU program when the FPP12 exits.

Table 1-1

Active Parameter Table Format

| Location |                                     | Co                                             | ntents                                      |                      |

|----------|-------------------------------------|------------------------------------------------|---------------------------------------------|----------------------|

| Р        | Field Bits<br>of Operand<br>Address | Field Bits<br>of Base<br>Register              | Field Bits of<br>Index Register<br>Location | Field Bits<br>of FPC |

|          |                                     | 4.50                                           |                                             |                      |

| P+1      | Lower 12 bits o                     | of FPC                                         |                                             |                      |

| P+2      | Lower 12 bits o                     | Lower 12 bits of Index Register 0 location X 0 |                                             |                      |

| P+3      | Lower 12 bits of Base Register      |                                                |                                             |                      |

| P+4      | Lower 12 bits of operand address    |                                                |                                             |                      |

| P+5      | Exponent of FAC                     |                                                |                                             |                      |

| P+6      | MSW of FAC                          |                                                |                                             |                      |

| P+7      | LSW of FAC                          |                                                |                                             |                      |

#### 1.7 PROGRAMMING THE FPP12

The FPP12 is initialized and interrogated by PDP-8 type IOT instructions. Once started, the FPP12 operates much like an actual processor, fetching instructions and operands and storing results in the PDP-8 or PDP-12 core memory. Data breaks or "stolen" memory cycles are generally requested by the FPP12 as needed. The maximum number of breaks requested is generally one per regular PDP-8 or PDP-12 instruction. This means that while the FPP12 is operating, PDP-8 or PDP-12 programs can be run simultaneously at 50 to 70 percent of normal speed. Typically LINCtape, display, analog data acquisition, and other forms of I/O can be performed by the PDP-12 Computer while the FPP12 is calculating.

An optional mode is available to the FPP12 attached to a PDP-12 Computer. For calculations where the maximum FPP12 program speed is required, setting the proper command register bit (refer to Table 1-2) locks out the PDP-12 processor during FPP12 program execution. Using the "lock out" mode on the PDP-12 speeds up FPP12 programs by 15 to 25 percent (refer to Table 1-4).

#### 1.7.1 Initialization

To execute the first instruction of any program, the FPP12 must have the 15-bit core address of the first instruction that is contained in the first two locations of the APT. The contents of other locations

Table 1-2 AC After Read Status Instruction

| AC Bit | Function if AC Bit Set to 1                                              |

|--------|--------------------------------------------------------------------------|

| 0      | Fixed-point mode.                                                        |

| 1      | Trapped instruction caused exit.                                         |

| 2      | FPHLT instruction caused exit.                                           |

| 3      | Attempted divide by 0 caused exit. The FAC was not altered.              |

| 4      | Fraction overflow in fixed-point mode caused exit.                       |

| 5      | Exponent overflow caused exit.                                           |

| 6      | Exponent underflow has occurred. Exit on exponent underflow is optional. |

| 7 8 9  | Unused                                                                   |

| 10     | The FPP12 is currently paused.                                           |

| 11     | The FPP12 is currently in a run state.                                   |

Table 1–3 Command Register Setting

6533

| AC Bit  | Function when AC Bit Set to 1                                                                            |  |  |

|---------|----------------------------------------------------------------------------------------------------------|--|--|

| AC bits | 0-11 have the following function when the FPCOM IOT is issued.                                           |  |  |

| 0       | Select fixed-point mode upon initiation.                                                                 |  |  |

| 1       | Exit if exponent underflow occurs. Otherwise, set result of cal-culation and continue.                   |  |  |

| 2       | Forbid access to 4K memory fields other than the field that is occupied by the last location of the APT. |  |  |

| 3       | Enable CPU program interrupt when FPP12 Interrupt Request flag is set. Skip is always enabled.           |  |  |

| 4       | Do not store operand address on exits. The operand address is neve retrieved on initiate.                |  |  |

| 5       | Do not store the address of index register 0 from or in the APT.                                         |  |  |

| 6       | Do not store the base register from or in the APT.                                                       |  |  |

| 7       | Do not store the FAC from or in the APT.                                                                 |  |  |

| 8       | Lock out the PDP-12 processor during FPP12 program execution. Unused on PDP-8 FPP12 systems.             |  |  |

(Continued on next page)

Table 1–3 (Cont)

Command Register Setting

| AC Bi | t Function when AC Bit Set to 1                                                                                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | AC bits 0-11 have the following function when the FPCOM IOT is issued.                                                                                                                                                                                     |

| 9     |                                                                                                                                                                                                                                                            |

| 10    | Most-significant 3 bits of APT pointer.                                                                                                                                                                                                                    |

| 11    |                                                                                                                                                                                                                                                            |

| Note: | Setting bits 4-7 of the command register speeds up initiation and exit operations. Setting command register bits 4-7 does not alter the relative position of items on the APT. In multijob environments, command register bits 4-7 are typically set to 0. |

Table 1-4

Instruction Execution Times\*

|                                           |                                                                              | Serial Mode                                |                                              | Parallel Mode**                              |                                              |  |

|-------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|--|

| Instruction                               | Octal Code                                                                   | Double Precision<br>Execution Time<br>(µs) | Floating Point<br>Execution Time<br>(µs)     | Double Precision<br>Execution Time<br>(µs)   | Floating Point<br>Execution Time<br>(µs)     |  |

| FLDA FADD FSUB FDIV FMUL FADDM FMULM FSTA | 0200+X<br>1200+X<br>2200+X<br>3200+X<br>4200+X<br>5200+X<br>6200+X<br>7200+X | 12<br>13<br>13<br>24<br>23<br>17<br>27     | 13<br>19<br>19<br>28<br>27<br>26<br>33<br>13 | 14<br>14<br>14<br>27<br>27<br>24<br>30<br>14 | 16<br>23<br>23<br>31<br>31<br>30<br>39<br>16 |  |

<sup>\*</sup>All times were measured using the single-word direct reference format. Timing tolerance is  $\pm 20\%$ .

of the APT are often useful in starting a program and essential in restarting an interrupt task. Once the appropriate parameters are placed in an APT table by the CPU, two IOTs must be issued. FPCOM (6553) loads a command register and the most significant 3 bits of the APT pointer. The significance of the bits in the command register is shown in Table 1-3. FPST (6555) loads the least significant 12 bits of the APT pointer and starts the FPP12. A typical initiate sequence is shown in Example 2-1. Once initiated, the FPP12 will execute instructions until:

- a. An error condition, such as exponent overflow, occurs.

- b. An FEXIT instruction is encountered.

<sup>\*\*</sup>For these measurements the PDP-12 was performing mostly single cycle instructions.

- c. An FPHLT IOT is issued by this CPU.

- d. An I/O preset is issued by the CPU.

- e. The CPU encounters any type of halt.

#### 1.7.2 Serial vs Parallel Processing

The most efficient use of resources occurs when the CPU and FPP12 are programmed to operate in parallel. For instance, in the display oriented research analysis (DORA) program which faciliates display interactive manipulation of data files, the PDP-12 refreshes a CRT display, performs Teletype <sup>®</sup>, LINCtape, and disk I/O, and samples knob and sense switch positions while the FPP12 is performing floating-point arithmetic. Because the FPP12 and the CPU access the same core memory, the communication methods are virtually unlimited; either processor can alter the other's program or data. Usually the CPU is assigned the job of scheduling and I/O, while the FPP12 performs complex arithmetic. However, in the DORA program, the FPP12 schedules I/O by passing parameters to the PDP-12 CPU.

There are occasions when it is desirable to complete an FPP12 calculation between operations performed by the CPU. Setting the appropriate command register bit in the FPP12 permits serial operation with the PDP-12 Processor. In serial mode, the PDP-12 CPU is locked out from the executing instructions while the FPP12 is operating.

There is no provision for a true serial mode for an FPP12 on a PDP-8 type processor. The fastest wait loop for a PDP-8, PDP-8/L, or PDP-8/L Computer consists of a JMP instruction with the programmed interrupt facility enabled, because data breaks can occur only between complete instructions. On the PDP-8/E Computer, the data break facility is structured so that data breaks may occur after any major state or multistate instructions. Therefore, the particular CPU program in progress does not affect the FPP12 instruction execution time on a PDP-8/E Computer.

#### 1.7.3 IOT Instructions

A complete list follows of IOT instructions with device code 55 that apply to programming the FPP12. IOT instructions with device code 56 are relegated to maintenance programs. The use of maintenance IOTs is presented in Chapter 3. If a conflict exists between the FPP device select codes and the device select codes of another peripheral, the conflict must be resolved in the hardware by altering wired connections in either the FPP12 or the conflicting device. It is recommended that the FPP12 device codes not be altered because of the necessity of changing extensive diagnostic and system software. However, the logic to be altered in changing device codes is found on Prints FPP12-0-CI1, FPP12-0-CI2, and FPP12-0-CI3.

<sup>®</sup> Teletype is a registered trademark of Teletype Corporation.

#### 1.7.4 IOT List

| Mnemonic | Octal Code | <u>Function</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPINT    | 6551       | Skip when the FPP12 Interrupt Request flag is set.                                                                                                                                                                                                                                                                                                                                                                                                                |

| FPICL    | 6552       | Unconditionally reset the FPP12 including all flags. To the FPP12, the IOT FPICL is the same as I/O preset.                                                                                                                                                                                                                                                                                                                                                       |

| FPCOM    | 6553       | If the FPP12 is not in a Run state and the FPP12 Inter-<br>rupt Request flag is not set, the FPP12 command register<br>is loaded with the contents of the AC*. If the FPP12<br>is in a Run state, or if the Interrupt Request flag is set,<br>the FPCOM instruction is ignored.                                                                                                                                                                                   |

| FPHLT    | 6554       | Force the FPP12 to exit, dump its status in the APT, and set the Interrupt Request flag at the end of the current instruction. The FPHLT instruction is used to abort an FPP12 program in a multijob environment or in software debugging. The following special features apply to the FPHLT instruction.                                                                                                                                                         |

|          |            | a. If FPHLT is issued prior to the FPST instruction, the<br>FPP12 will execute only one instruction after in-<br>itiation and then exit with the FPC pointing to the<br>succeeding instruction. This facilitates single step-<br>ping through an FPP12 program under CPU control.                                                                                                                                                                                 |

|          |            | b. If the FPP12 is in a Pause state, the FPP12 will exit<br>with the FPC pointing at the pause instruction. This<br>means that if a job was aborted in a Pause state it<br>will be resumed in a Pause state.                                                                                                                                                                                                                                                      |

|          |            | c. Normally, if an exit is forced by FPHLT, AC02 will be set to a 1 when either read status FPRST or FPIST is issued. However, if the forced exit causes the FPP12 program to abort while an FEXIT instruction is being executed, the CPU forced exit flag is cleared. Thus, the CPU forced exit flag is an absolute indicator that a program was prematurely aborted.                                                                                            |

| FPST     | 6555       | If the FPP12 is not running and the Interrupt Request flag is not set, the least significant 12 bits of the APT pointer are set to the contents of the AC and the FPP is started. If the FPP12 is in a Run state, but paused, the FPST instruction will cause the FPP12 to continue. Otherwise, the FPST instruction has no affect on the FPP12. If the FPST instruction causes the FPP12 to start or continue, the CPU will skip the instruction following FPST. |

| FPRST    | 6556       | Read the FPP12 status register into the AC. FPRST may be issued at anytime.                                                                                                                                                                                                                                                                                                                                                                                       |

| FPIST    | 6557       | Skip if the FPP12 Interrupt Request flag is set. If the skip occurs, read the FPP12 status register in the AC and clear the status flags and the Interrupt Request.                                                                                                                                                                                                                                                                                               |

<sup>\*</sup>AC refers to the PDP-12 or PDP-8 accumulator while FAC refers to the FPP12 accumulator.

#### 1.7.5 Instruction Set-Address Methods

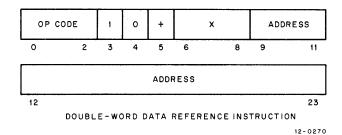

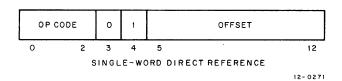

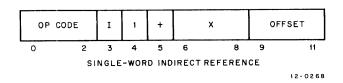

Three types of data reference instructions are available:

- a. 24-bit instruction with a 15-bit absolute address.

- b. 12-bit instruction with a 7-bit relative address.

- c. 12-bit instruction with a 3-bit relative address that specifies a 15-bit indirect address.

Full indexing capability is available for types a and c. The determined operand address points at the exponent of the operand in floating-point mode and at the most significant word of the operand in fixed-point mode.

#### 1.7.6 Index Registers

Any core location may be used as an index register. The core address of the current index register 0 is stored in the X0 register. The X0 register is initially set from the APT, but may be altered by the SET X instruction. Index register X is in location X0+X, where  $X=0,\ldots,7$ .

Accessing an array of data points requires incrementing the address of the current point by the data length to yield the address of each successive point. Index registers are used to accomplish this address modification. The index register is incremented by one to access each successive point, but it is multiplied by the data length, three for floating point and two for fixed point. This quantity is used as the displacement from the address specified in the instruction to yield the address of the current point. Adjusting of index registers simplifies "skipping" through data arrays and permits a single index register to be used as both a loop counter and address modifier (see Example 2-2). Pre-incrementing is selected by bit 5 of data reference instructions types a and c. Instructions are available for setting, testing, and performing arithmetic on index registers. In particular, the instruction ADDX, which adds the contents of bits 12-23 of the instruction to the contents of the index register specified by bits 9-11 of this instruction, is useful in manipulating "push-down stacks".

#### 1.7.7 Instruction Set

The FPP12 instruction set is divided into two basic classes: data reference instructions and special instructions. Data reference instructions are those that operate on the two data formats specified in Paragraph 1.8. Data reference instructions include the basic arithmetic operations plus load and store. All other instructions are special instructions that include index registers modifiers, jumps, pointer moves, and the operate-type instructions.

The instruction set is presented in detail in the following paragraphs. The instruction format follows each group of instructions.

#### 1.8 DATA REFERENCE INSTRUCTIONS\*

| OP Code | Mnemonic | Data Function                 |

|---------|----------|-------------------------------|

| 0       | FLDA     | C(Y) → FAC                    |

| 1       | FADD     | C(Y) + C(FAC) → FAC           |

| 5       | FADDM    | $C(Y) + C(FAC) \rightarrow Y$ |

| 2       | FSUB     | C(FAC) - C(Y) → C FAC         |

| 3       | FDIV     | $C(FAC)/C(Y) \rightarrow FAC$ |

| 4       | - FMUL   | C(FAC) * C(Y) → FAC           |

| 7       | FMULM    | C(FAC) * C(Y) →Y              |

| 6       | FSTA     | C(FAC) → C Y                  |

#### Data Reference Instruction Formats

$Y = C (bits 9-23) + M * (C (X + X0) + C (bit 5)) * \delta (X)$

Y = C (base register) + 3 (offset)

$<sup>\</sup>ensuremath{^{*}\text{In}}$  fixed-point mode the exponent of the FAC is never altered.

Y = C (bits 21-36 of C ((base reg.) +

$$3*$$

offset))

+ (M) \* (C X + X0) + C (bit 5))\*  $8$  (X)

$8$  (X) = 1 if X  $\neq$  0 and 0 if X = 0

M = 2 if fixed-point mode

3 if floating-point mode

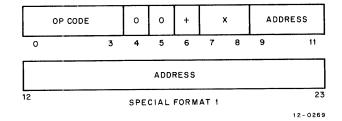

#### 1.8.1 Special Format 1

| OP Code               | Mnemonic                     | <u>Function</u>                                                                                                                                    |

|-----------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                     | NXL                          | The index register $X$ is incremented if bit $5=1$ and a jump is executed to the address contained in bits 9-23, if index register $X$ is nonzero. |

| 3<br>4<br>5<br>6<br>7 | Trapped<br>Instruc-<br>tions | The instruction-trap status bit is set and the FPP12 exits causing a PDP interrupt. The unindexed operand address is dumped into the APT.          |

#### 1.8.2 Special Format 2

| OP Code | Extension | Mnemonic | <u>Function</u>                                                                                       |

|---------|-----------|----------|-------------------------------------------------------------------------------------------------------|

| 0       | 10        | LDX      | The contents of the index register specified by bits 9-11 are replaced by the contents of bits 12-23. |

| 0       | 11        | ADDX     | The contents of bits 12–23 are added to the index register specified by bits 9–11.                    |

#### 1.8.3 Conditional Jumps

Jumps, if performed, are to the location specified by bits 9-23 of the instruction.

| OP Code | Extension | Mnemonic | <u>Function</u>                                                                                                                      |

|---------|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------|

| 7       | 0         | JEQ      | Jump if FAC = 0                                                                                                                      |

| 1       | 1         | JGE      | Jump if FAC $\geq$ 0                                                                                                                 |

| 1       | 2         | JLE      | Jump if $FAC \leq 0$                                                                                                                 |

| 1       | 3         | JA       | Jump always                                                                                                                          |

| 1       | 4         | JNE      | Jump if FAC ≠ 0                                                                                                                      |

| 1       | 5         | JLT      | Jump if FAC < 0                                                                                                                      |

| . 1     | 6         | JGT      | Jump if FAC > 0                                                                                                                      |

| 1       | 7         | JAL      | Jump if impossible to fix the floating-point number contained in the FAC; i.e., if the exponent is greater than (23) <sub>10</sub> . |

#### 1.8.4 Pointer Moves

| OP Code | Extension | Mnemonic | <u>Function</u>                                                                                                                               |

|---------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| ī       | 10        | SETX     | Set X0 to the address contained in bits 9–23 of the instruction.                                                                              |

| 1       | 11        | SETB     | Set the base register to the address contained in bits 9–23.                                                                                  |

| 1       | 13        | JSR      | Jump and save return. Jump to the location specified in bits 9–23 and the return is saved in bits 21–35 of the first entry of the data block. |

| 1       | 12        | ASL      | An unconditional jump is deposited in the address and address + 1, where address is specified by bits 9-23. The EPC is set to address + 2.    |

1.8.5 Special Format 3

|              | OP Code | Extension    | Mnemonic | <u>Function</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|---------|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 0       | 1            | ALN      | The mantissa of the FAC is shifted until the FAC exponent equals the contents of the index register specified by bits 9-11. If bits 9-11 are zero, the FAC is aligned so that the exponent = (23) <sub>10</sub> .* In double-precision mode, an arithmetic shift is performed on the FAC fraction. The number of shifts is equal to the absolute value of the contents of the specified index register. The direction of shift depends on the sign of the index register contents. A positive sign indicates a shift toward the least significant bit, while a negative sign indicates a shift toward the most significant bit. The FAC exponent is not altered by the ALN instruction in double-precision mode. |

| <i>t / v</i> | 0       | 2            | ATX      | The contents of the FAC are fixed and the least significant 12 bits of the mantissa are loaded into the index register specified by bits 9-11. In double-precision mode the least significant 12 bits of the FAC are loaded into the specified index register. The FAC itself is not altered by the FLATX instruction.                                                                                                                                                                                                                                                                                                                                                                                           |

| Fiber        | 0       | 3            | XTA      | The contents of the index register specified by bits 9-11 are loaded right-justified into the FAC mantissa. The FAC exponent is loaded with (23)10 and then the FAC is normalized. This operation is typically termed floating a 12-bit number. In double-precision mode, the FAC is not normalized.                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | 0       | 4            | NOP      | The single-word instruction performs no operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | 0       | 5 <b>-</b> 7 |          | These codes are reserved for instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | 0       | 12-17        | reserved | set expansion and should not be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              | 1       | 14-17        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

<sup>\*</sup>Setting the exponent =  $(23)_{10}$  integerizes or fixes the floating-point number. The JAL instruction tests to see if fixing is possible.

1.8.6 Operate Group - Special Format 3

| OP Code | Extension | 9-11 Bits | Mnemonic | Function                                                                                                              |

|---------|-----------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------|

| 0       | 0         | 0         | FEXIT    | Dump active registers into the APT, reset the FPP12 RUN flip-flop to the 0 state, and interrupt the PDP-12 processor. |

| 0       | 0         | 1         | FPAUSE   | Wait for synchronizing signal. IOT FFST (6555) will restart the instruction following FPAUSE.                         |

| 0       | 0         | 2         | FCLA     | Zero the FAC mantissa and exponent.                                                                                   |

| 0       | 0         | 3         | FNEG     | Complement FAC mantissa.                                                                                              |

| 0       | 0         | 4         | FNORM    | Normalize the FAC. In double-<br>precision mode FNORM is a NOP.                                                       |

| 0       | 0         | 5         | START F  | Start floating-point mode.                                                                                            |

| 0       | 0         | 6         | START D  | Start double-precision mode.                                                                                          |

| 0       | 0         | 7         | JAC      | Jump to the location specified by the least significant 15 bits of the FAC mantissa.                                  |

# CHAPTER 2 FPP12 PROGRAMMING EXAMPLES

#### 2.1 INTRODUCTION

Programming examples for the Floating Point Processor and a procedure for initializing the FPP12 are contained in this chapter. Several examples are provided that utilize index registers. A re-entrant sine subroutine illustrates a technique for writing re-entrant code. Program debugging techniques are discussed in detail. The mnemonics and syntax used in this chapter are consistent with those of the FPP assembler. A complete description of the assembler can be found in the manual entitled, <u>FPP Assembler Manual</u>, DEC-12-AQZA-D. A math package for the FPP is described in a manual entitled FPP Support Library (DEC-12-YEXA-D).

#### 2.2 PROGRAM INITIALIZATION

Each FPP12 program consists of one or more instructions and an Active Parameter Table (APT). Upon initialization, the APT (refer to Table 1–1) contains the initial setting of important FPP12 registers. Whenever the FPP12 finishes or aborts a program, the APT is updated before the CPU is interrupted.

The CPU program in Example 2-1 starts the FPP12 with the APT pointer set to location 01000, which is word 1000 of field 0. The FPP12 normally does not recognize page or field boundaries. If the APT started in location 07777, the least significant 12 bits of the FPC would be found in location 10000.

In Example 2-1, the FPP12 will pick up locations 02000, 02001, 02002, 02003, 02005, 02006, and 02007 of the APT. Note that the operand address, location 02004 in this example, is never retrieved from the APT by the FPP12. After retrieving the contents of location 02007, the FPP12 will fetch its first instruction from location 01000. The 4 in the second digit of the contents of location 01000 indicates that the instruction is a 2-word, direct addressing, data reference instruction. The 0 in the first digit of location 01000 indicates that the instruction is an FLDA. Bits 9-23 of the instruction specify the address, which is not indexed when bits 6-8 are all zero. After fetching the address, the FPP12 will break to 12000, 12001, and 12002 to load the operand into the FAC.

After retrieving the least significant word of the FAC from location 12002, the FPP12 will fetch another instruction from location 01002. The instruction in location 01002 is an FEXIT, equivalent

| / Sample program to initialize FPP12 |                  |                      |                                            |       |                              |                                             |                                                                                          |

|--------------------------------------|------------------|----------------------|--------------------------------------------|-------|------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------|

|                                      |                  | ORG                  | 00020                                      |       |                              | ets assembler<br>) <sub>8</sub> of field 0. |                                                                                          |

| 00020                                | 2000             | APTPT,               | APT                                        | /Poin | ter to A                     | PT                                          | •                                                                                        |

|                                      |                  | ORG 200<br>BEGIN,    | CLA FPCOM TAD APTF FPST HLT FPINT JMP1 HLT | 'T    | /Set Al<br>/If no s<br>/Wait | )'s to FPP12 o                              | command register<br>02000 and start<br>not ready to be started                           |

| / A Samp<br>/ FPP12 F                | le<br>Program is | below                |                                            |       |                              |                                             |                                                                                          |

| Loc                                  |                  | contents             |                                            |       | ORG                          | G 01000                                     |                                                                                          |

| 01000<br>01001<br>01002              |                  | 0401<br>2000<br>0000 |                                            |       | FLD<br>FEX                   | A TAG                                       | /Load contents of<br>/Location TAG into FAC<br>/Dump APT<br>/Into core and interrupt CPU |

| / Active                             | parameter        | table                |                                            |       |                              |                                             | ,                                                                                        |

| Loc                                  |                  | contents             |                                            |       | OR                           | G 02000                                     |                                                                                          |

| 02000<br>02001<br>02002              |                  | 0<br>1000<br>3000    |                                            |       | APT,                         | 0000<br>1000<br>3000<br>4000<br>            | /most sig bits /FPC /X0 /Base /Operand address /FAC exp /FAC MSW /FAC LSW                |

| ORG 12<br>12000<br>12001<br>12002    | 2000             | 0002<br>3000<br>0000 | TAG,                                       | 3.0   |                              |                                             | /constant (3.0) <sub>10</sub>                                                            |

Example 2-1 Sample FPP12 Program

to a halt instruction for the CPU. Prior to stopping, the FPP12 dumps the current APT over the initial APT, beginning with the least significant word of the FAC in location 02007 and ending with location 02000. The APT at the completion of the FEXIT instruction is shown in Table 2-1.

Table 2-1

APT After FEXIT in Example 2-1

| 02000 | 1000 | /current Field Bits |

|-------|------|---------------------|

| 02001 | 1003 | /current FPC        |

| 02002 | 2000 | /X0                 |

| 02003 | 4000 | Base                |

| 02004 | 2002 | /Operand address    |

| 02005 | 0002 | /exponent           |

| 02006 | 3000 | /MSW                |

| 02007 | 0000 | LSW                 |

Only after dumping the APT is the FPP12 Skip or Interrupt flag set. In Example 2-1, the CPU executes a WAIT loop while the FPP12 is operational. It would be far more efficient for the CPU to perform some other task, such as tape or Teletype I/O, while the FPP12 is calculating.

#### 2.3 INDEX REGISTERS AS ADDRESS MODIFIERS AND LOOP COUNTERS

The FPP12 program in Example 2-2 moves a list of (200)<sub>8</sub> floating point numbers from an area of core starting at location ALPHA to an area starting at location BETA. Note that index registers are used both for loop counting and address modification. Index register 1 is set to -1 and index register 0 is set to -200 using the LDX instruction. Index register 1 is incremented prior to use as an address modifier for the FLDA instruction at location LOOP. Index register 0 is used as a loop counter by the JXN instruction.

| BEGIN, | LDX -1, 1<br>LDX -200, 0 | /set index register 1 = -1<br>/set index register 0 = (-200) <sub>8</sub>            |

|--------|--------------------------|--------------------------------------------------------------------------------------|

| LOOP,  | FLDA ALPHA, 1+           | /first C(1 + X0) = C (1 + X0)<br>+1 Then load FAC from loc.<br>ALPHA + C (1 + X0) *3 |

|        | FSTA BETA, 1             | /Store FAC in loc BETA + C<br>(1 + X0) *3                                            |

|        | JXN LOOP, 0+             | /first C $(X0 + 0) = C(X0 + 0)$<br>+1                                                |

|        |                          | /then go to loop if C $(X0 + 0) \pm 0$                                               |

|        | FEXIT                    | /trap to CPU                                                                         |

|        | ORG 4000                 |                                                                                      |

| ALPHA, | OPC 4000                 |                                                                                      |

| BETA,  | ORG 6000<br>0            |                                                                                      |

Example 2-2 Move List from ALPHA to BETA Using Index Registers

It is possible to use the same index register as a loop counter and as an address modifier, because of the method used in the FPP12 hardware to calculate indexed addresses. In the process of formulating an address, the FPP12 checks to see if indexing is required. If indexing is required, the contents of the specified index register are retrieved and "adjusted" by the appropriate multiplier, which is 3 for floating-point mode and 2 for fixed-point mode. Then the adjusted index register is added to the unindexed address and the resulting addition, initially performed with 24 bits of precision, is truncated to 15 bits by dropping the 9 most significant bits of the result. Example 2-3 illustrates the standard method of indexed address calculation. If it is necessary to use index register 5 as a loop counter, additional care must be used in selecting the pointer to list A contained in the instruction. Consider the case where the loop counter is set to (-200)<sub>8</sub>. Then the pointer to list A must be modified to be [A + M(C (I) + (30000)<sub>8</sub>]. C (I) is the initial setting of the index register and M is the number of 12-bit bytes in the data word. Example 2-4 is similar to Example 2-2; however, only one index register is used.

Initially

$$X0 = 14003$$

$C(X0 + 5) = 0001$

Instruction FLDA A, 5 0451

2003

A is location 12003

Address calculation proceeds as follows:

- 1. The contents of  $(X \ 0 + 5)$  are retrieved and multiplied by three.

- The "adjusted" index register is added to 00012003 the unindexed address to yield 00012006.

- 3. This address is truncated to 12006.

Example 2-3 Indexed Address Calculation

#### 2.4 USE OF INDEX REGISTERS TO CREATE PUSH-DOWN STACKS

The subroutines in Example 2-5 illustrate the use of the ADDX instruction in creating push-down or last-in-first-out lists. The PUSH routine is called with an argument in the accumulator. The POP routine returns with elements removed from the stack in the accumulator. These subroutines are designed to be called with the JSA instruction which places an unconditional jump to the return in the first two locations of the subroutine.

The PUSH and POP subroutines in Example 2-5 are valid for either fixed-point or floating-point mode, as long as second and additional calls are in the same mode as the very first call.

```

BEGIN, LDX COUNT, 1

LOOP, FLDA ALPHA-(M*COUNT-50000), 1

JXN LOOP, 1 + FSTA ALPHA-(M*COUNT-50000), 1

M = 3, if floating point mode

2, if fixed point mode

K = (70000)<sub>8</sub>

```

Example 2-4 Index Register 1 is Used as Both an Address Modifier and Counter

```

PUSH,

0

0

FSTA STACK, 2 + /Place contents of AC in stack

JA PUSH /Return from subroutine

POP,

0

FLDA STACK, 2 /Retrieve item from stack

ADDX 2, -1 /Decrement stack pointer

JA POP /Return from subroutine

```

Example 2-5 Push-Down Stacks

#### 2.5 BRANCH OR JUMP ON CONDITION INSTRUCTIONS

Seven conditional jump instructions are provided in addition to the JXN instruction. Six of these, JEQ, JGE, JLE, JNE, JCT, and JGT, test the FAC mantissa. The seventh, JAL, executes a jump if the FAC cannot be represented as a (24)<sub>10</sub> bit binary number. This occurs when the FAC exponent is greater than (23)<sub>10</sub> or (27)<sub>8</sub>.

#### 2.6 WRITING RE-ENTRANT SUBROUTINES

A re-entrant subroutine is one in which the code is not altered during execution. This property permits the interruption of a task which is executing a given re-entrant subroutine and the starting of another task that uses the same subroutine. The advantage of re-entrant coding is that two or more jobs can use the same subroutine without concern as to when a given job is interrupted.

The single-word data reference instructions and a re-entrant jump to subroutine facilitate the writing of re-entrant codes. With the JSR instruction, the return address is saved in bits 21-35 of the location pointed at by the contents of the base register. If it is necessary to store temporary values during subroutine execution, single-word instructions should be used. This will force addressing to be relative to the base register setting. Each task will have a unique base register setting; therefore, the effective addresses for temporary storage for each task will be unique, even though the offsets for the data instructions are never charged in the pure subroutine. The return from the re-entrant subroutine consists

of the two instruction sequence, FLDA ALPHA, JAC, shown in Example 2-6. JSR causes the return address to be deposited into the first location of the data block, ALPHA, which is defined by the base register. The return address is deposited into the FAC with the instruction FLDA ALPHA. The JAC instruction actually executes the return jump by setting FPC equal to bits 9-23 of the FAC.

```

Main Prog

MPROG, JSR SUB

FEXIT

SUB, FLDA ALPHA

JAC

Jump to sub prog.

Load return address

/Jump to the address contained in

/bits 9-23 of the FAC fraction

Base ALPHA

ALPHA, ---

```

Example 2-6 Return from Re-Entrant Subroutine

#### 2.7 USE OF THE FPHLT INSTRUCTION

The FPHLT IOT (6554) permits the CPU to force the abortion of a running FPP12 program or to force the FPP12 to execute one instruction each time it is initialized. In a multitask or time-shared environment, it is often necessary to suspend a calculation prior to completion. When debugging a program, it is often desirable to examine the results of each instruction's execution.

If FPHLT is issued while the FPP12 is executing a program, that program will be aborted at the end of the current FPP12 instruction. The FPP12 will dump the current APT in core and then cause a CPU program interrupt. If the current instruction is anything except FEXIT, status bit 02 will be set to 1 if FPHLT forced the FPP12 to stop program execution.

Issuing FPHLT prior to FPST will cause the FPP to initialize, execute one instruction, then exit. By repeating this procedure, the CPU can force the FPP12 to single step through a program.

## 2.8 DEBUGGING FPP12 PROGRAMS ON UNITS ATTACHED TO PDP-12 COMPUTERS

The PDP-12 console (described in the PDP-12 System Reference Manual) is a powerful tool for debugging FPP12 programs. Using the switches, one can single step through FPP12 programs, observing the transfers between the FPP and the PDP-12 memory on the console lights. Alternatively, the FPP12 program can run until a specific memory address is accessed, in which case the computer will halt, permitting the console light to be examined. While the computer is halted, memory may be examined

and altered with the switch register without disturbing the program counters associated with either the CPU or the FPP12. IOT instructions may be issued with the console switches that examine registers within the FPP12.

If the stop switch is raised during the execution of a FPP12 program, the PDP-12 will stop at the end of a complete instruction or a data break caused by some external device such as the FPP12. Depressing the continue switch with the stop switch raised causes the execution of one CPU instruction or one data break for each actuation of the continue switch. Operating in this mode, the FPP12 will receive one data break for each CPU instruction. This means that every other time the continue switch is depressed a data break will occur. Whenever the break indicator light is lit, the MA and MB lights on the console refer to the data break address and memory buffer contents associated with the FPP12 program. The single step switch causes similar results, except the halts occur at the end of each major state of the CPU instructions. The single step switch is useful when the CPU program that runs in parallel with the FPP12 program contains tape instructions. The stop switch has no affect for the duration of LINCtape instructions.

If bit 8 of the FPP12 command register is set to 1, the CPU will be locked out while FPP12 programs are executing. This is reflected in the fact that the break light will stay on continuously as the continue switch is actuated.

#### 2.9 USING THE EXECUTE STOP SWITCH

If the execute stop switch is raised the PDP-12 will halt whenever the memory location whose address is contained in the left switches is accessed during any cycle except a CPU fetch cycle. Setting the left switches to the first location of the next APT to be used and raising the execute stop switch causes the PDP-12 to halt following the first FPP12 data break following FPST IOT.

## 2.10 CARE NECESSARY IN THE USE OF EXAMINE AND DEPOSIT SWITCHES

Some care is necessary when using the examine and deposit switches, if they are to be used while a FPP12 program is temporarily halted. Problems arise because of the logical implementation of the break field register within the PDP-12. The 4K memory field examined on the first push of the examine switch following a program may be the field into which the FPP12 was breaking when the program stop occurred. To be sure that the proper data for an examine operation is displayed in the MB register, the examine switch should be actuated twice for the first operation following a program stop. When the computer system is restarted, the first PDP-12 cycle following an examine or deposit operation will be a break cycle if the FPP12 is requesting a data break. To ensure that the FPP12 breaks to the proper 4K memory field, the last operation after any series of examines and deposits must be a fill step.

#### 2.11 ADDITIONAL PROGRAMMING HINTS

#### 2.11.1 Illegal Mantissa

In the 2's complement number system the number consisting of a one followed by twenty-three zeros is an illegal number because it and its 2's complement are both equal to -1. The FPP12 logic will not allow this number to be generated as the result of any calculation. For instance, if -1/2 is added to -1/2 the result shows up in the FPP as -1/2 \*2 or -1. It is possible for this number to arise in other than calculations. For instance, it is possible to intentionally place a number into core memory from the CPU's switches. The routine in Example 2-7 illustrates a test for the illegal fraction.

/The value in location A possibly has an illegal fraction

| BEGIN,        | FLDA<br>JGE<br>FNEG | A<br>GOOD | /Get C (A) /If C(A) 0 all is OK /Form 2's complement of fraction |

|---------------|---------------------|-----------|------------------------------------------------------------------|

|               | JLT BAD             |           |                                                                  |

| GOOD,<br>BAD, | FEXIT<br>FEXIT      |           | /Number is OK<br>/Number has illegal fraction                    |

Example 2-7 Test for Illegal Fraction 100000000...000

Example of Re-Entrant Sine and Exponential Subroutines

Examples 2–8 and 2–9 contain the FPP code for calculating SINE (X) and X (X \*\*Y). The comments indicate what each step of the routines is doing. Both subroutines are written in the mnemonics and syntax of the FPP assembler.

```

0001

/ SINE USES THE 1ST 3 ENTRIES IN

ØØØ2

/ THE BLOCK AND INDEX REG. Ø,182

0003

/ X IS PASSED THROUGH THE 2ND ENTRY

0004

/ IN THE BLOCK AND SIN(X) IS RETURNED

0005

/ THROUGH THE SAME LOCATION

0006

ORG 10500

0007

BASE Ø

0010

0011

X=1*3

XSQR=2#3

0012

/ CALCULATE ABSOLUTE VALUE OF X.INDEX

0013

/ REG Ø SET TO Ø INDICATES SIGN OF X

0014

/ WAS NEGATIVE

0015

0016 10500 0201 SINE,

FLDA X

/INITIATE INDEX REG 1

LDX -1.0

0017 10501 0100

10502 7777

/GO TO CAL IF X IS POSITIVE

JGT CAL

0020 10503 1061

10504 0512

/GO TO DONE IF X IS Ø

JEQ DONE

0021 10505 1001

10506 0603

ØØ22 10507 ØØØ3 MOD,

/NEGATE FAC

FNEG

/SET INDEX REG TO ZERO

0023 10510 0100

LDX Ø,Ø

10511 0000

/ REDUCE X TO IST CYCLE USING THE

0024

/ IDENTITY SIN(X)=SIN(N+2+PI+X)

0025

FDIV TWOPI

/DIVIDE X BY 2*PI

0026 10512 3401 CAL.

10513 0607

FSTA X

0027 10514 6201

0030 10515 1071

JAL ERROR

/X IS TOO LARGE

10516 0606

ALN Ø

0031 10517 0010

/GET INTEGER PART

0032 10520 0004

FNORM

FSUB X

0033 10521 2201

FNEG

/GET FRACTIONAL PART

0034 10522 0003

0035 10523 1001

JEQ DONE

/SIN(2*PI*N) IS ZERO

10524 0603

/NORMALIZE TO BETWEEN Ø AND 2*PI

FMUL TWOPI

0036 10525 4401 REM,

10526 2607

0037 10527 6201

FSTA X

/ REDUCE X TO 1ST HALF CYCLE USING

0040

0041

/ THE IDENTITY SIN(X)=-SIN(X-PI) FOR

0042

/ PI<X<=2*PI

FSUB PI

0043 10530 2401

10531 0612

/IF X IS LESS THAN PI GP TO PCHECK

0044 10532 1051

JLT PCHECK

10533 2543

FSTA X

/SET X TO X-PI

0045 10534 6201

/IF INDEX REG Ø WAS -1 SET TO Ø AND

JXN RESET, 0+

0046 10535 2101

10536 0541

/GO TO PCHECK+1

JA PCHECK+1

0047 10537 1031

10540 0544

/IF INDEX REG Ø WAS Ø SET IT TO -1

0050 10541 0100 RESET.

LDX -1.0

10542 7777

```

Example 2-8 SINE Routine (Sheet 1 of 2)

```

0052