1st Edition, April 1969 2nd Printing (Rev), August 1969 3rd Printing (Rev), December 1970 4th Printing (Rev), April 1971 5th Printing, October 1971 6th Printing (Rev), October 1973

Copyright © 1969, 1970, 1971, 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

**COMPUTER LAB**

### **CONTENTS**

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| FOREWORD    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                |

| INTRODUCTIO | )N                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                |

| SYSTEM CONF | FIGURATIONS TABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                |

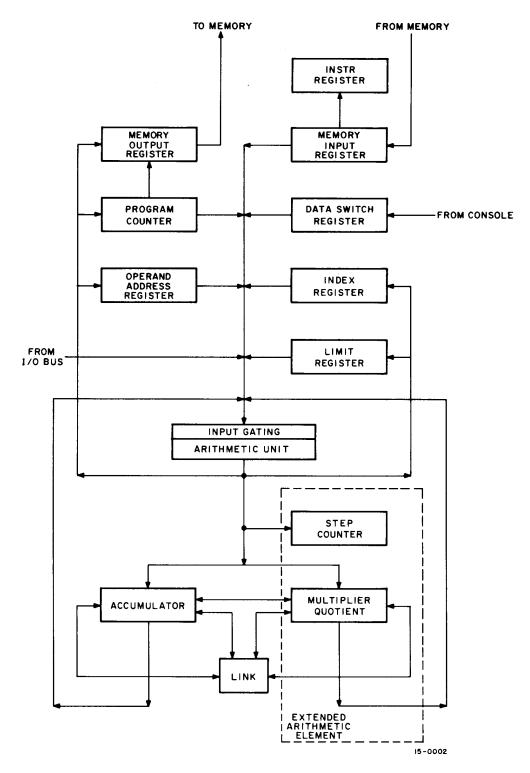

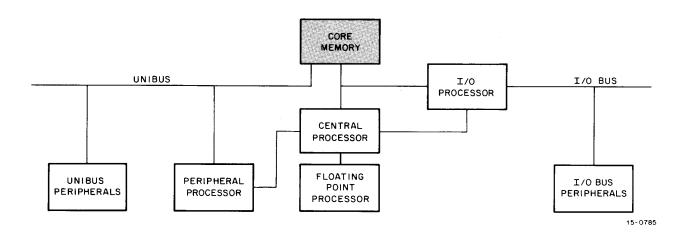

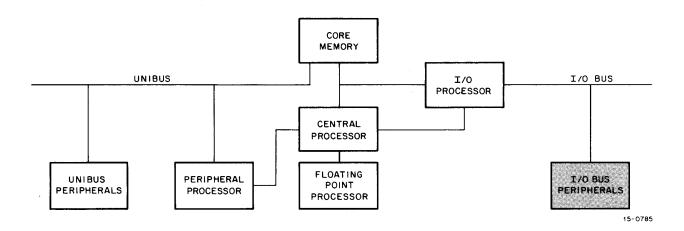

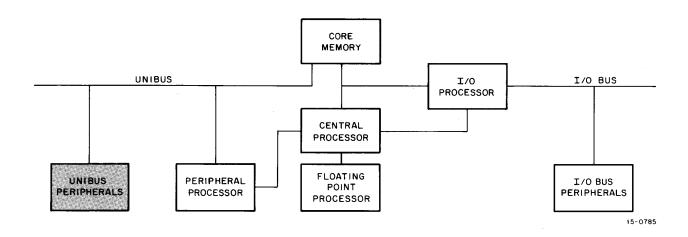

| CHAPTER 1   | CENTRAL PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                |

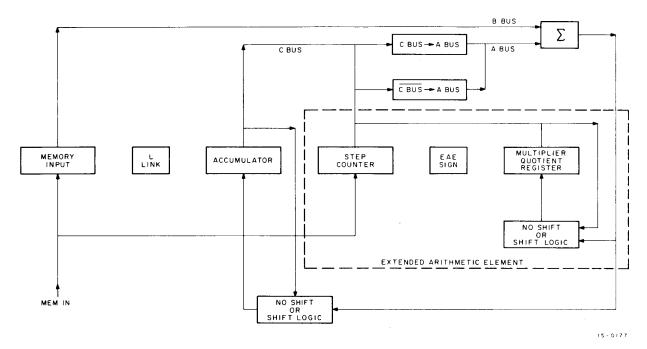

|             | SUMMARY OF CHARACTERISTICS CENTRAL PROCESSOR DESCRIPTION Arithmetic Unit (AU) Instruction Register (IR) Accumulator (AC) Data Switch Register Link (L) Program Counter (PC) Operand Address Register (OA) Memory Input and Output Buffer Register (MI and MO) Index Register (XR) Limit Register (LR) PDP-15 Control Console PROCESSOR EXPANSION Extended Arithmetic Element (EAE) KM15 Memory Protect KT15 Memory Protect and Relocate KF15 Power Failure Protection | 1-1<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-4<br>1-4<br>1-4<br>1-4<br>1-5<br>1-5<br>1-5<br>1-5 |

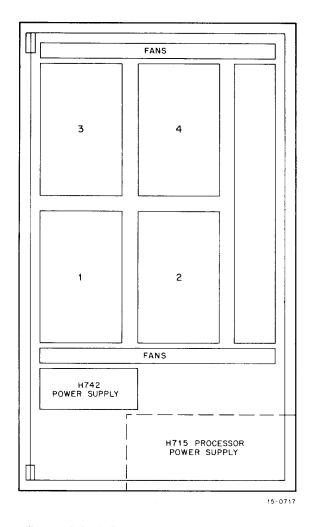

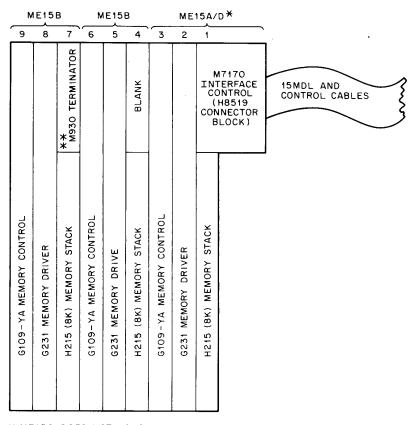

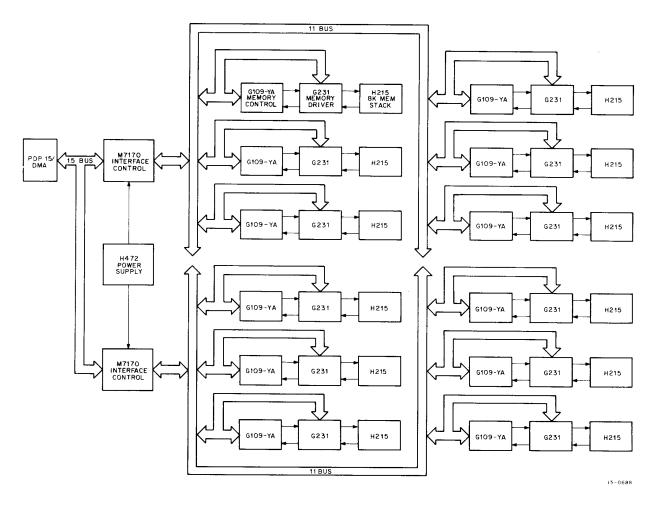

| CHAPTER 2   | MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                |

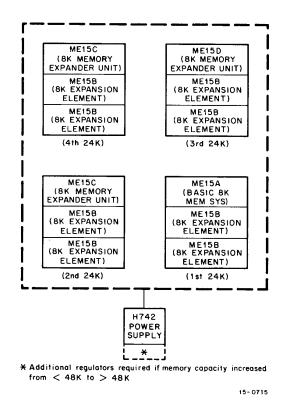

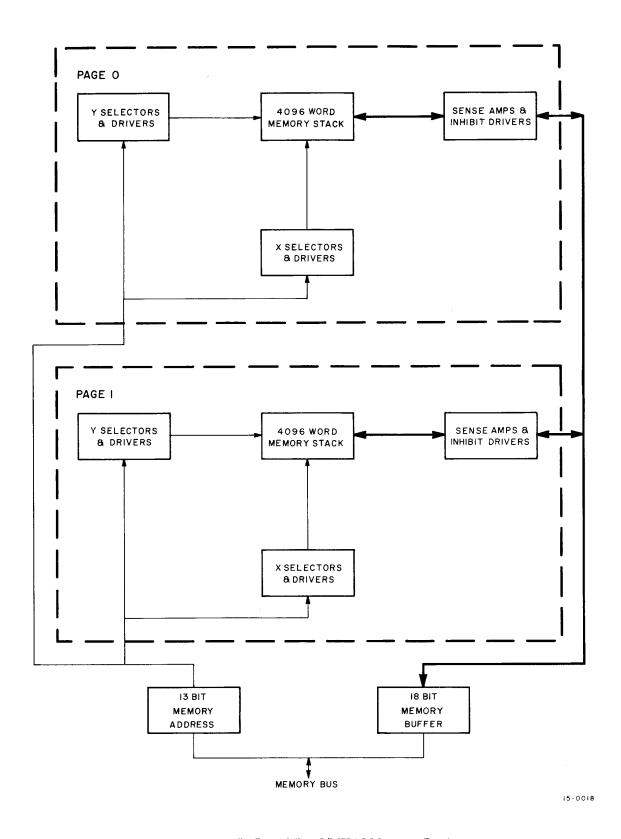

|             | INTRODUCTION  Memory Data Transfer  Memory Loads  ME15 MEMORY  ME15 Memory Specifications  PDP-15 Systems with 8K of MM15 Memory  (no memory mounted on back door)  PDP-15 Systems with 16K of MM15 Memory  (8K mounted on back door)  PDP-15 Systems with 24K of MM15 Memory  (16K mounted on back door)  PDP-15 Systems with 24K of MM15 Memory  (16K mounted on back door)  PDP-15 Systems with Existing ME15 Memory  MM15/MK15 MEMORY                             | 2-1<br>2-2<br>2-3<br>2-5<br>2-6<br>2-6<br>2-7<br>2-7                                           |

|             | MM15/MK15 Memory Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-7                                                                                            |

|           |                                         | Page   |

|-----------|-----------------------------------------|--------|

|           | CORE MEMORY                             | . 2-9  |

|           | Memory Data Transfer                    |        |

|           | Memory Cycles                           |        |

|           | Port Switch                             |        |

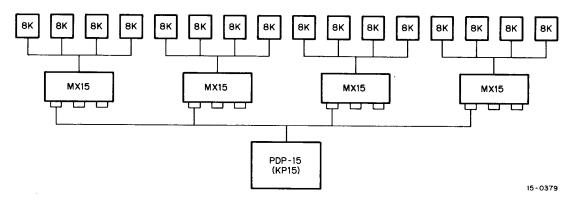

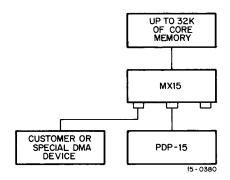

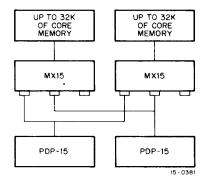

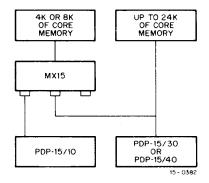

|           | MX15 Memory Bus Multiplexer             |        |

|           | DIRECT MEMORY ACCESS                    |        |

|           | MULTIPROCESSOR SYSTEMS                  |        |

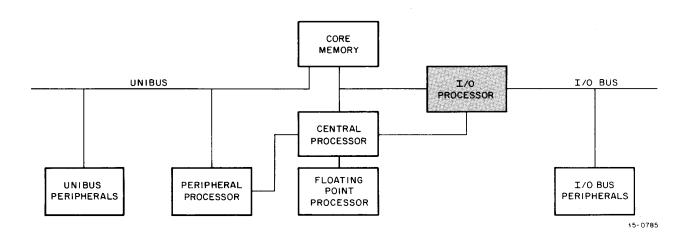

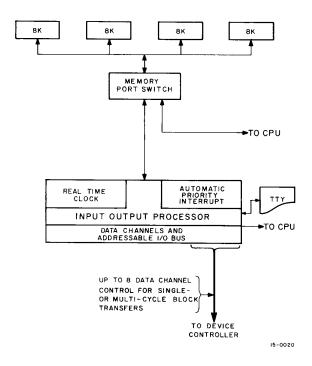

| CHAPTER 3 | INPUT/OUTPUT PROCESSOR                  |        |

|           | SUMMARY OF CHARACTERISTICS              | . 3-1  |

|           | Addressable I/O Bus                     |        |

|           | I/O PROCESSOR                           |        |

|           | Modes of Data Transfer                  |        |

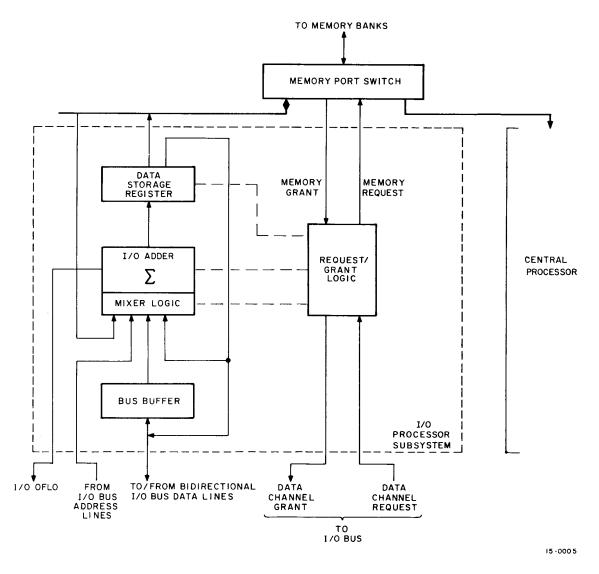

|           | Block Transfer Controller               |        |

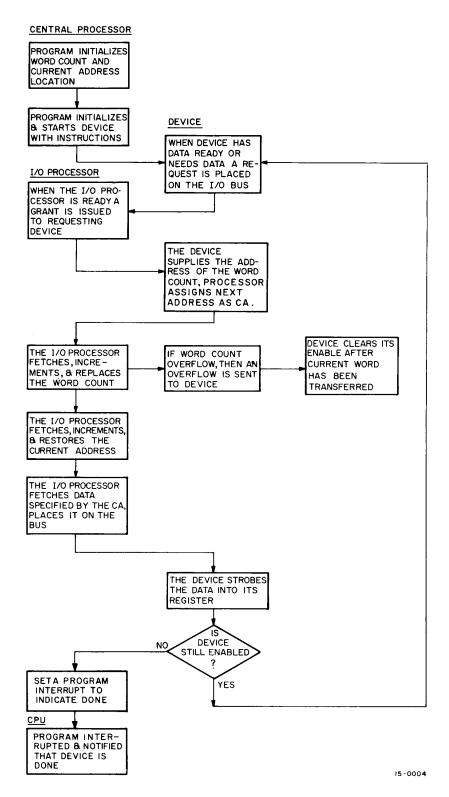

|           | Multicycle Block Transfers              |        |

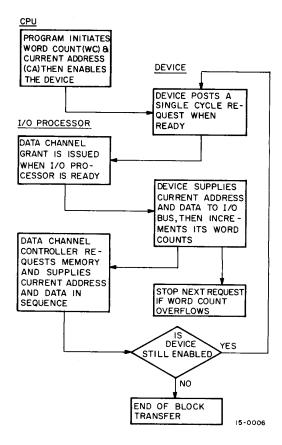

|           | Single Cycle Block Transfers            |        |

|           | Increment Memory                        |        |

|           | Add-to-Memory                           |        |

|           | Real-Time Clock                         |        |

|           | ADDRESSABLE I/O BUS                     |        |

|           | Program-Controlled Transfer             |        |

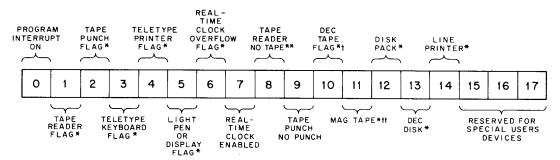

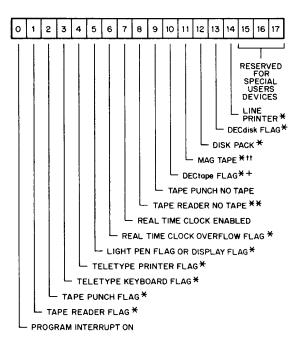

|           | PROGRAM INTERRUPT FACILITY              |        |

|           | Conditional Skip-On Device Status       |        |

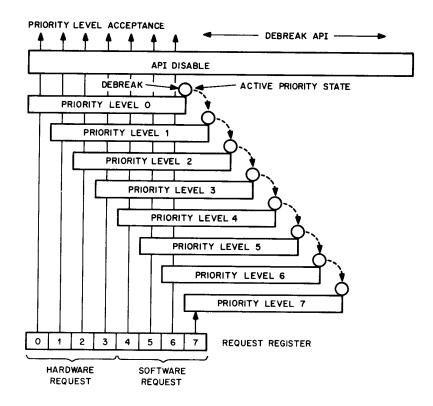

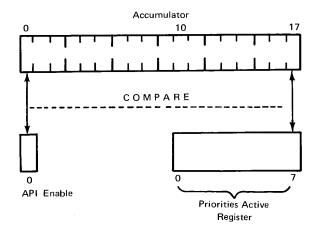

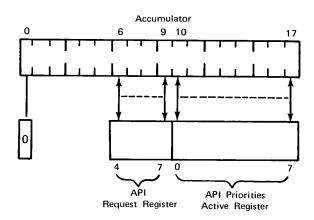

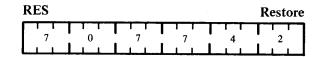

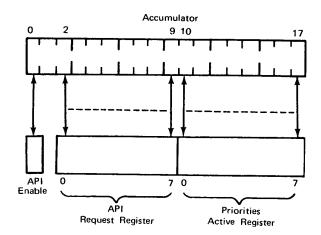

|           | AUTOMATIC PRIORITY INTERRUPT            |        |

|           | API Hardware                            |        |

|           | COMMON I/O BUS                          |        |

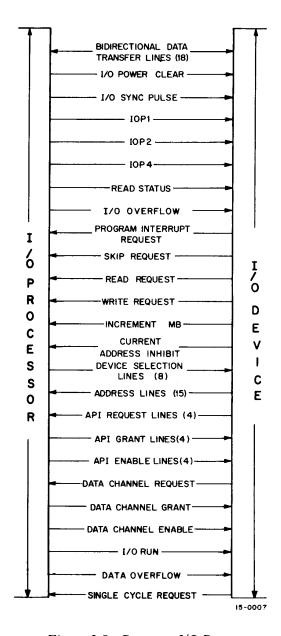

|           | Data Lines                              |        |

|           | Output Control Signals                  |        |

|           | I/O Power Clear                         |        |

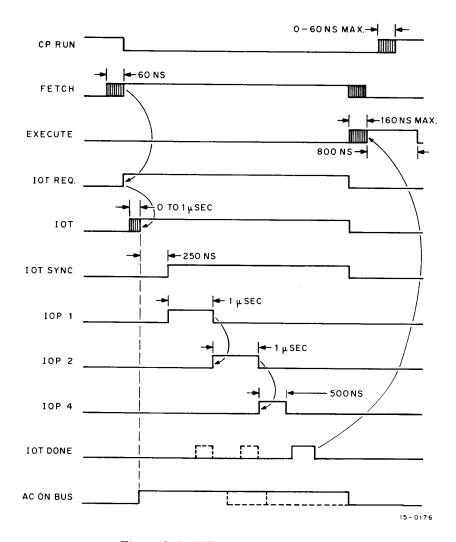

|           | I/O Sync                                |        |

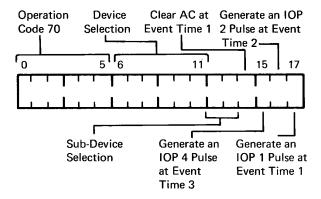

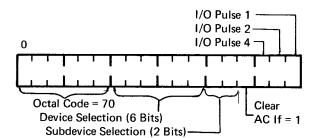

|           | IOP1, IOP2, IOP4                        |        |

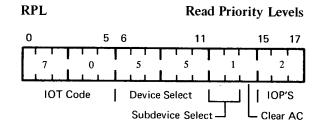

|           | Read Status                             |        |

|           | Input/Output Read Status                |        |

|           | I/O Overflow                            |        |

|           | Data Overflow                           |        |

|           | Input Control Levels                    |        |

|           | Address Lines                           |        |

|           | Multiplexed Control Lines               |        |

|           | I/O Run                                 |        |

|           | Teletype Interface and Hardware Read-In |        |

|           | Priority                                |        |

|           | Latency                                 |        |

|           | Datency                                 | >- 1 / |

|           |                                         | Page  |

|-----------|-----------------------------------------|-------|

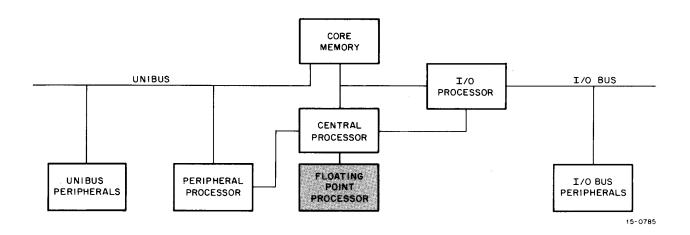

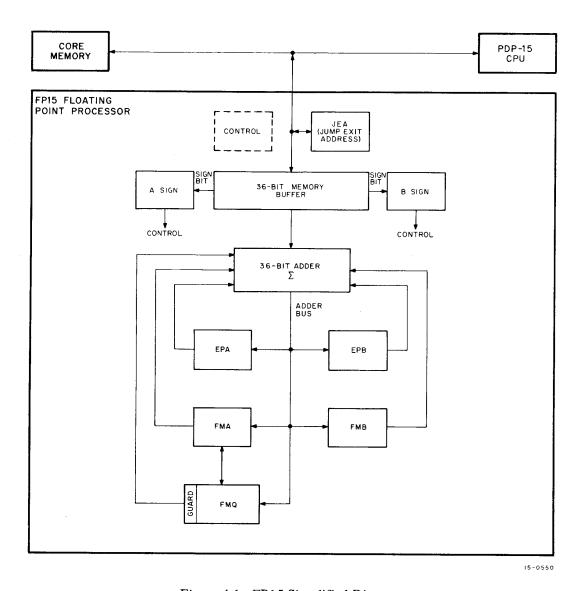

| CHAPTER 4 | FLOATING POINT PROCESSOR FP15           |       |

|           | FP15 FLOATING POINT PROCESSOR           | . 4-1 |

|           | FP15 FUNCTIONAL DESCRIPTION             |       |

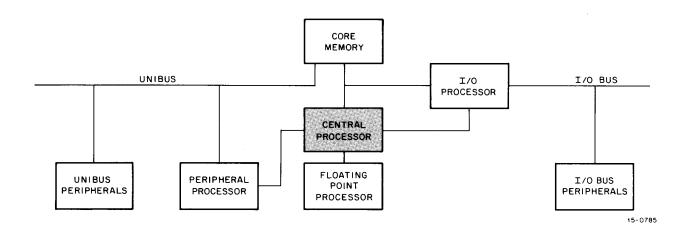

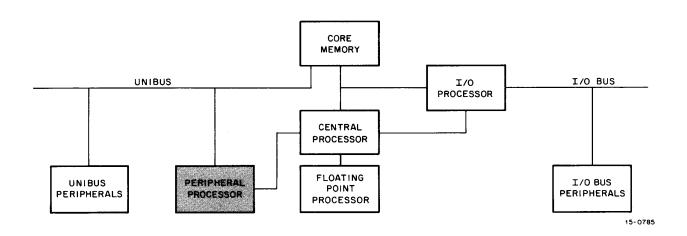

| CHAPTER 5 | PERIPHERAL PROCESSOR UC15               |       |

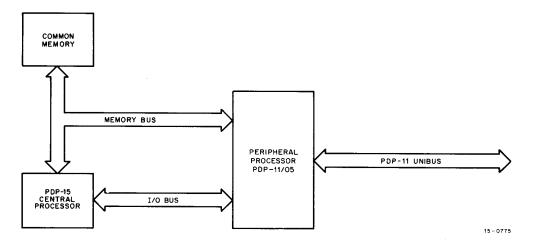

|           | COMMON MEMORY                           | . 5-1 |

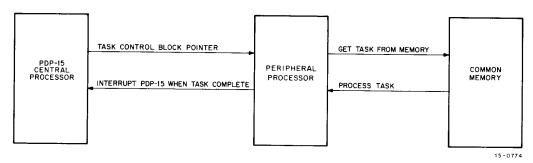

|           | INTERRUPT LINK                          | . 5-2 |

|           | PERIPHERAL PROCESSOR HARDWARE           | . 5-2 |

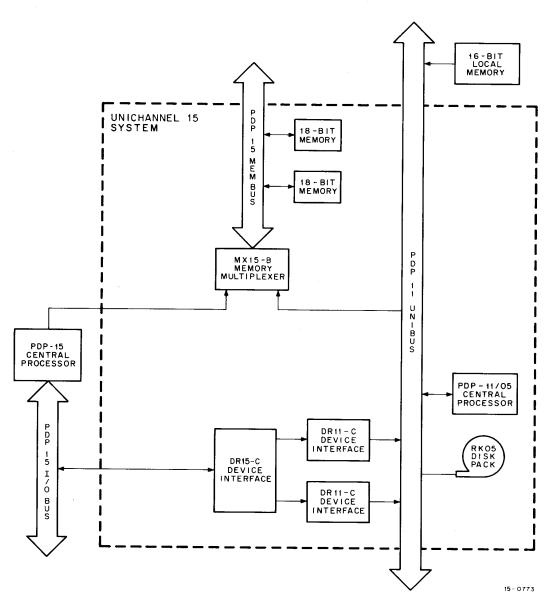

|           | UC15 CONFIGURATIONS                     | . 5-2 |

|           | SPECIFICATION SUMMARY                   | . 5-4 |

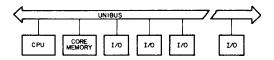

|           | THE UNIBUS AND THE PDP-11/05 PROCESSOR  | . 5-6 |

|           | The Unibus                              | . 5-6 |

|           | PDP-11/05 Processor                     | . 5-6 |

|           | Central Processor                       | . 5-6 |

|           | Instruction Set                         |       |

|           | Priority Interrupts                     | . 5-7 |

|           | Reentrant Code                          |       |

|           | Addressing                              |       |

|           | Stacks                                  |       |

|           | Direct Memory Access                    |       |

|           | Power Fail and Restart                  |       |

|           | PDP-11/05 SPECIFICATIONS                |       |

|           | Physical                                |       |

|           | Electrical                              |       |

|           | Functional                              |       |

| CHAPTED ( |                                         |       |

| CHAPTER 6 | INPUT/OUTPUT BUS PERIPHERALS            |       |

|           | STANDARD INPUT/OUTPUT DEVICES           |       |

|           | PC15 High-Speed Paper Tape Reader/Punch |       |

|           | CR15 Card Reader and Control            |       |

|           | Card Reader Specifications              |       |

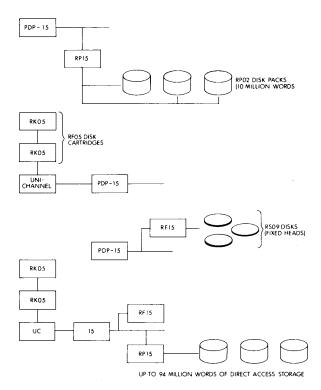

|           | MASS STORAGE DEVICES                    |       |

|           | DECtape                                 |       |

|           | DECtape Features                        |       |

|           | Magnetic Tape Systems                   |       |

|           | Disk Systems                            | . 6-3 |

|           | LINE PRINTERS AND PLOTTERS              | . 6-4 |

|           | LP15 Automatic Line Printer             | . 6-4 |

|           | XY15 Incremental Plotter and Control    |       |

|           | DATA COMMUNICATIONS DEVICES             | . 6-4 |

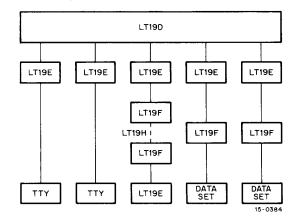

|           | LT19 Multi-Station Teletype Control     | . 6-4 |

|           |                                             | Page |

|-----------|---------------------------------------------|------|

|           | LT15 Teletype Control                       | 6-4  |

|           | Console Printer and Control                 | 6-4  |

|           | LA30 DECwriter                              | 6-5  |

|           | Specifications                              | 6-5  |

|           | Printer                                     | 6-5  |

|           | Data Entry                                  | 6-5  |

|           | Environmental/Physical                      | 6-5  |

|           | DP09A Data Communication System             | 6-5  |

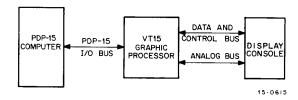

|           | GT15 Graphics Subsystem                     | 6-5  |

|           | VT15 Graphic Processor                      | 6-6  |

|           | Display Processor Specifications            | 6-6  |

|           | DISPLAY SCOPES                              | 6-6  |

|           | Technical Specifications                    | 6-7  |

|           | VL04 Light Pen                              | 6-8  |

|           | VW01 Writing Tablet                         | 6-8  |

|           | LK35 Keyboard Option                        | 6-8  |

|           | VM15 Display Console Multiplexer            | 6-8  |

|           | VP15 Displays                               | 6-8  |

|           | VT05 Alphanumeric Display Terminal          | 6-9  |

|           | ANALOG-TO-DIGITAL CONVERTERS                | 6-9  |

|           | AD15 Analog-to-Digital Converter            | 6-9  |

|           | AM01-A                                      | 6-9  |

|           | ADF15-C                                     | 6-9  |

|           | DIGITAL-TO-ANALOG CONVERTERS                |      |

|           | AA15B Digital-to-Analog Multiplexer Control |      |

|           | DW15A I/O Bus Adapter                       |      |

|           | INDUSTRIAL CONTROL SYSTEM                   |      |

|           | UDC15 Universal Digital Control             |      |

|           | AFC-15 Automatic Flying Capacitor           |      |

|           | INTERPROCESSOR BUFFER SYSTEMS               | 6-10 |

| CHAPTER 7 | UNIBUS PERIPHERALS                          |      |

| CHAPTER / |                                             |      |

|           | LP11 LINE PRINTER                           | 7-1  |

|           | Operation                                   | 7-1  |

|           | 80-Column Model                             | 7-1  |

|           | 132-Column Model                            | 7-1  |

|           | Model Designation                           | 7-2  |

|           | LS11 LINE PRINTER                           | 7-2  |

|           | Specifications                              | 7-2  |

|           | LV11 PRINTER-PLOTTER                        | 7-2  |

|           | Specifications                              | 7-3  |

|           |                                             |      |

|           |                                               | Page  |

|-----------|-----------------------------------------------|-------|

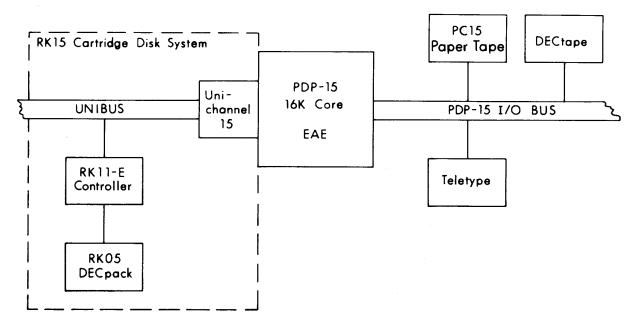

|           | RK15 DISK CARTRIDGE SYSTEM WITH UNICHANNEL 15 | . 7-3 |

|           | RK11E Disk Controller Features                |       |

|           | RK11/RK05 DISK AND CONTROL                    |       |

|           | RK05 Specifications                           |       |

|           | CR11 CARD READER                              | . 7-5 |

|           | Specifications                                |       |

|           | DP11 SYNCHRONOUS INTERFACE                    |       |

|           | XY11 Plotter Control                          |       |

|           | Compatible Digital Plotters                   |       |

|           | PLOTTERS                                      |       |

|           | CalComp-563                                   |       |

|           | CalComp-565                                   |       |

|           | Complot DP-1                                  |       |

|           | Complot DP-10                                 | . 7-8 |

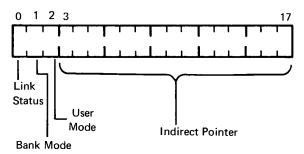

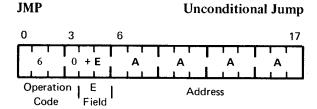

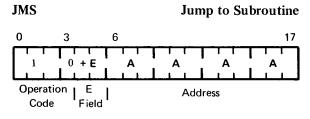

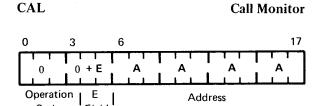

| CHAPTER 8 | ADDRESSING                                    |       |

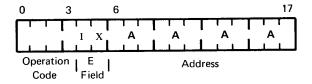

|           | INTERPRETATION OF WORDS FROM MEMORY           | . 8-1 |

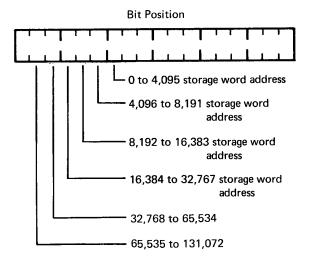

|           | INFORMATION RETRIEVAL FROM MEMORY             | . 8-1 |

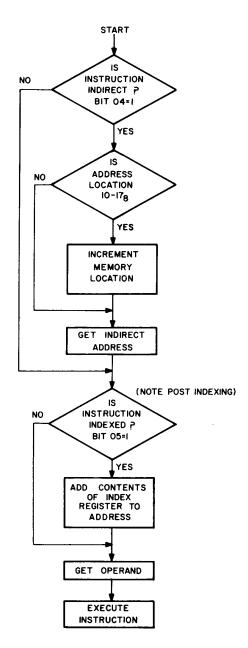

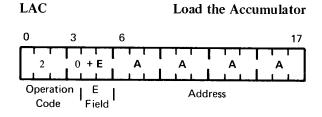

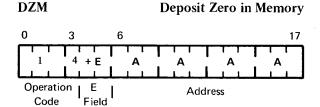

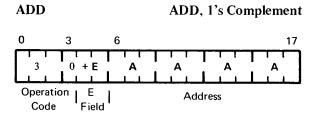

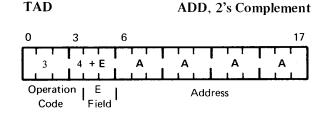

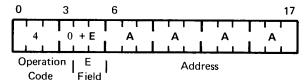

|           | MEMORY REFERENCE INSTRUCTIONS                 | . 8-2 |

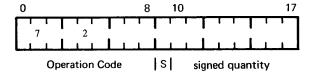

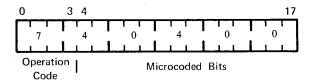

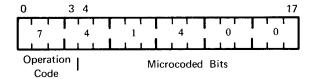

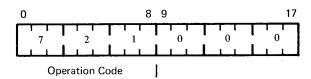

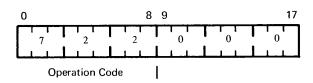

|           | Operation Code Field                          | . 8-2 |

|           | Operand Address Field                         | . 8-2 |

|           | Address Mode                                  | . 8-3 |

|           | Indexing Examples                             | . 8-4 |

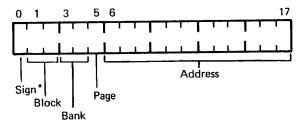

|           | BANK MODE ADDRESSING                          | . 8-5 |

|           | NON/MEMORY REFERENCE INSTRUCTIONS             | . 8-5 |

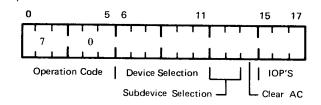

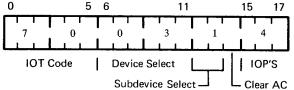

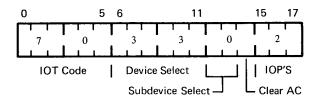

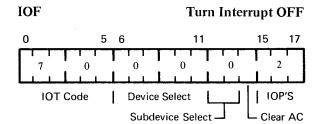

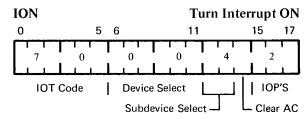

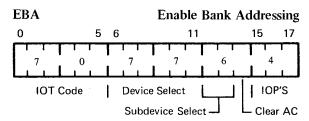

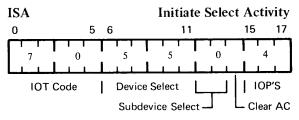

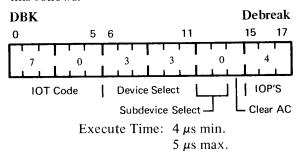

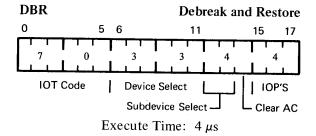

|           | Input/Output Instruction                      | . 8-5 |

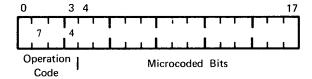

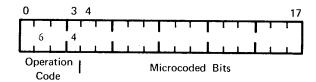

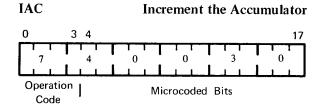

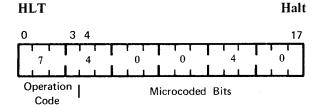

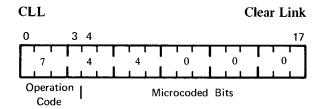

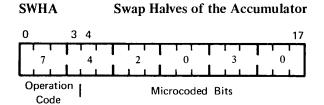

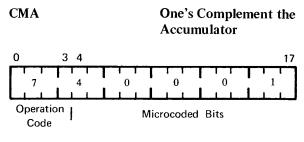

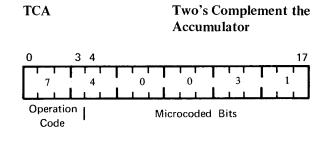

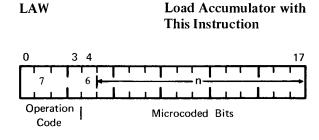

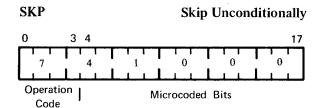

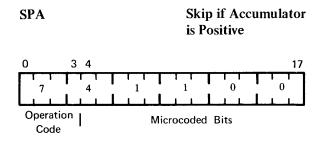

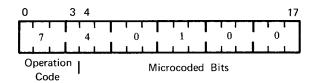

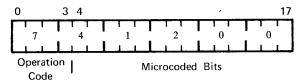

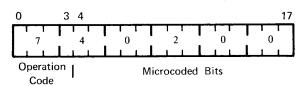

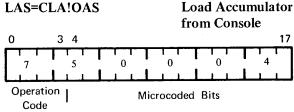

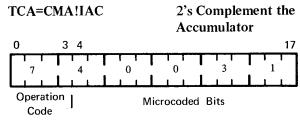

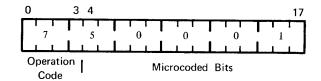

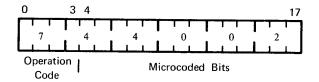

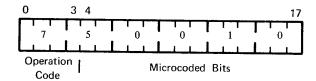

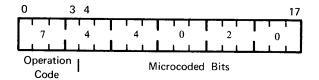

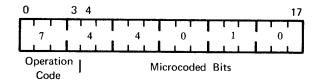

|           | OPERATE INSTRUCTIONS                          | . 8-6 |

|           | Microcoded Operate Instruction                |       |

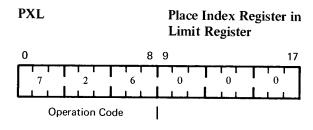

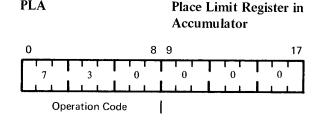

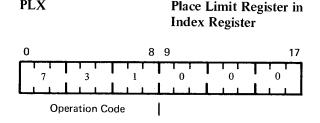

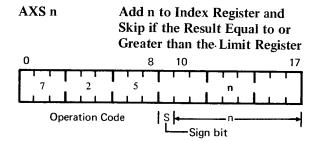

|           | Index Operates                                | . 8-6 |

|           | EAE Instructions                              |       |

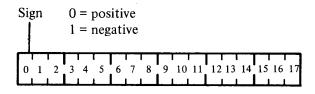

|           | DATA WORDS                                    | . 8-7 |

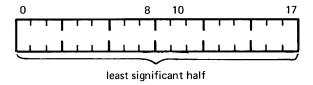

|           | Single-Precision Data                         | . 8-7 |

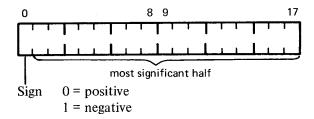

|           | Double-Precision Data                         |       |

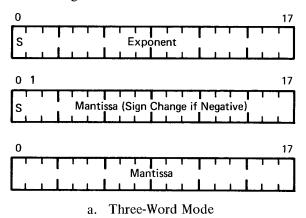

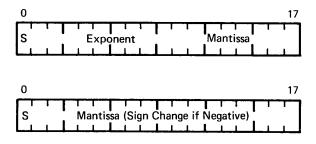

|           | BASIC SOFTWARE FLOATING-POINT FORMATS         |       |

|           | BOOLEAN REPRESENTATION                        | . 8-9 |

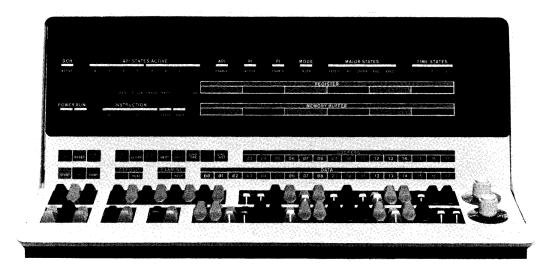

| CHAPTER 9 | PDP-15 CONSOLE                                |       |

|           | INFORMATION/CONTROL SWITCHES                  | . 9-1 |

|           | Data                                          |       |

|           | Address                                       |       |

|           | Register Group                                | . 9-1 |

|            |                                          | Page  |

|------------|------------------------------------------|-------|

|            | Clock                                    | . 9-2 |

|            | Repeat                                   |       |

|            | Single Time                              |       |

|            | Single Step                              |       |

|            | Single Instruction                       |       |

|            | OPERATE CONTROL SWITCHES                 |       |

|            | Start                                    |       |

|            | Execute                                  |       |

|            | Continue                                 |       |

| ,          | Stop                                     |       |

|            | Reset                                    |       |

|            | Read-In                                  |       |

|            | Deposit This                             |       |

|            | Deposit Next                             |       |

|            | Examine This                             | _     |

|            | Examine Next                             |       |

|            | Protect                                  |       |

|            | Bank Mode                                |       |

|            | SPECIAL SWITCHES                         |       |

|            | Register Select                          |       |

|            | Register Group Switch OFF                |       |

|            | Register Group Switch ON                 |       |

|            | Maintenance 1 and 2                      |       |

|            | Power/Repeat Rate                        |       |

|            | INDICATORS                               |       |

|            |                                          |       |

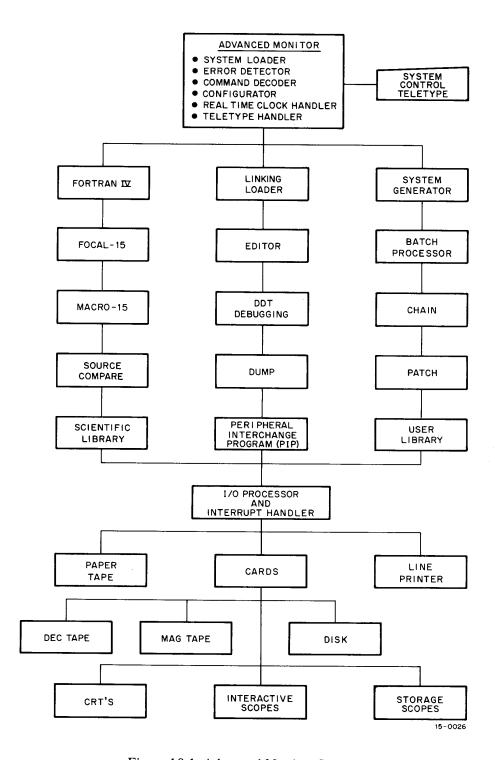

| CHAPTER 10 | SYSTEM SOFTWARE                          |       |

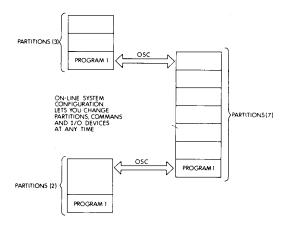

|            | BACKGROUND/FOREGROUND                    | 10-1  |

|            | DECtape or Disk Resident System Software |       |

|            | Interactive Operation                    |       |

|            | Foreground Priority                      |       |

|            | Foreground Protected                     |       |

|            | DECtape/Disk File Structure              |       |

|            | Dynamic Storage Allocation               | 10-2  |

|            | Conversational Mode                      |       |

|            | Programming Languages                    |       |

|            | I/O Device Handlers                      |       |

|            | Programmed Monitor Commands              |       |

|            | Bank and Page Modes                      |       |

|            | ADVANCED MONITOR SYSTEM                  |       |

|            | DISK OPERATING SYSTEM (DOS-15)           |       |

|            | Minimum DOS Configuration                |       |

|            | -                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| BATCH OPERATING SYSTEM SOFTWARE (BOSS-15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10-4  |

| Minimum BOSS Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| COMMON DOS/BOSS SOFTWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10-4  |

| FORTRAN IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10-4  |

| ALGOL 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| FOCAL-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| MACRO-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| MACRO-11 (Unichannel systems only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| Text Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| Graphic Text Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| Text File Preprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| Text File Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| Peripheral Interchange Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| Magnetic Tape Utility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10-6  |

| Interactive Debugger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-6  |

| Library Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| Core Image Save/Restore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| Loaders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| Systems Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| Systems Patch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| Extensive System Peripheral I/O Handlers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| RESOURCE SHARING EXECUTIVE (RSX-PLUS III)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10-8  |

| RSX-PLUS III – Eliminating "System Generation" Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| DOT DITIONS ON A CO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-11 |

| The state of the s | 10-12 |

| UNICHANNEL SOFTWARE (UC15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10-12 |

| PERIPHERAL EXECUTIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-12 |