XVM system reference manual

Copyright © 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

|           |                                             | Page   |

|-----------|---------------------------------------------|--------|

| CHAPTER 1 | XVM PROCESSOR                               |        |

| 1.1       | CENTRAL PROCESSOR DESCRIPTION               | . 1-1  |

| 1.2       | ADDRESSING                                  |        |

| 1.2.1     | XVM CPU Addressing Modes                    |        |

| 1.2.2     | XVM MPU Address Mapping                     |        |

| 1.2.3     | Addressing Examples                         |        |

| 1.3       | INPUT/OUTPUT PROCESSOR                      |        |

| 1.4       | MEMORY                                      | . 1-37 |

| CHAPTER 2 | SYSTEM PROCESSORS                           |        |

| 2.1       | AUTOMATIC PRIORITY INTERRUPT                | 2-3    |

| 2.2       | API HARDWARE                                |        |

| 2.3       | MEMORY MANAGEMENT (MMGR)                    |        |

| 2.4       | DYNAMIC MAPPING                             |        |

| 2.5       | G-MODES                                     |        |

| 2.6       | TRAPS                                       |        |

| 2.7       | MEMORY ADDRESS TRANSLATION                  |        |

| 2.8       | XM15 EXTERNAL PORT                          |        |

| 2.9       | UNICHANNEL LINK                             |        |

| 2.10      | IOT INSTRUCTIONS                            |        |

| 2.11      | REGISTER ADDRESSES                          |        |

| 2.12      | THE UNIBUS AND THE PDP-11 PROCESSOR         | . 2-15 |

| 2.12.1    | The Unibus                                  |        |

| 2.12.2    | PDP-11 Processor                            |        |

| 2.13      | SYSTEM OPERATION                            |        |

| 2.14      | FP15 FUNCTIONAL DESCRIPTION                 | . 2-20 |

| CHAPTER 3 | PERIPHERALS                                 |        |

| CHAPTER 4 | SYSTEM OPERATION                            |        |

| 4.1       | XVM PROCESSOR                               | 4-1    |

| 4.2       | PC15 HIGH-SPEED PAPER-TAPE READER AND PUNCH |        |

| CHAPTER 5 | SYSTEM INSTALLATION                         |        |

| 5.1       | INTRODUCTION                                | 5-1    |

| 5.2       | PREDELIVERY PLANNING                        |        |

| 5.3       | SITE PLANNING                               | _      |

| 5.4       | ENVIRONMENTAL PLANNING                      |        |

| 5.5       | ELECTRICAL PLANNING                         |        |

# **CONTENTS** (Cont)

|            |                                              | Page   |

|------------|----------------------------------------------|--------|

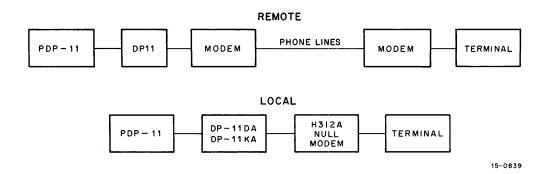

| 5.6        | COMMUNICATIONS                               | . 5-14 |

| 5.7        | UNPACKING                                    | . 5-14 |

| 5.8        | INSPECTION                                   | . 5-15 |

| 5.9        | CABINET INSTALLATION                         |        |

| 5.10       | PERIPHERAL EQUIPMENT INSPECTION              | . 5-16 |

| 5.11       | ELECTRICAL AND MECHANICAL SPECIFICATIONS     | . 5-16 |

| 5.12       | MISCELLANEOUS PART NUMBERS                   | . 5-26 |

| 5.13       | MAINTENANCE AND SERVICE OPTIONS              | . 5-26 |

| 5.14       | FORMS AND CHECKLISTS                         | . 5-28 |

| CHAPTER 6  | INSTRUCTION FORMATS                          |        |

| 6.1        | BASIC INSTRUCTION SET                        | . 6-1  |

| 6.2        | EXTENDED INSTRUCTION SET                     | . 6-36 |

| 6.3        | FLOATING POINT UNIT                          | . 6-68 |

| 6.4        | AUTOMATIC PRIORITY INTERRUPT INSTRUCTION SET | . 6-74 |

| 6.5        | KW15 READ-TIME CLOCK                         |        |

| 6.6        | KF15 POWER FAIL                              | . 6-80 |

| 6.7        | MEMORY MANAGEMENT                            | . 6-81 |

| 6.8        | PERIPHERAL INSTRUCTION SET                   | . 6-84 |

|            | ILLUSTRATIONS                                |        |

| Figure No. | Title                                        | Page   |

| 1-1        | Central Processor, Simplified Block Diagram  |        |

| 1-2        | Real and Virtual Addresses                   |        |

| 1-3        | Memory Addressing                            |        |

| 1-4        | Direct Addressing: Type I                    |        |

| 1-5        | Indirect Addressing: Type II                 |        |

| 1-6        | Auto-Increment Addressing: Type III          |        |

| 1-7        | Indexed Addressing: Type IV                  |        |

| 1-8        | Indirect-Indexed Addressing: Type V          |        |

| 1-9        | Auto-Increment, Indexed Addressing: Type VI  |        |

| 1-10       | Address Modification Flowchart               |        |

| 1-11       | Direct Mapping (DMAP)                        |        |

| 1-12       | Relocated Mapping (RMAP)                     |        |

| 1-13       | Shared Mapping (SMAP)                        |        |

| 1-14       | External Shared Address Space (ESAS) Example |        |

| 1-15       | Boundary Mapping (BMAP)                      | . 1-13 |

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                  | Page   |

|------------|--------------------------------------------------------|--------|

| 1-16       | Shared Mapping Example                                 | 1-19   |

| 1-17       | Multicycle Out Block Transfer Flowchart                |        |

| 1-18       | Multicycle In Block Transfer Flowchart                 | 1-23   |

| 1-19       | Multicycle Transfer Implementation                     |        |

| 1-20       | Single Cycle Block Transfer Flowchart                  |        |

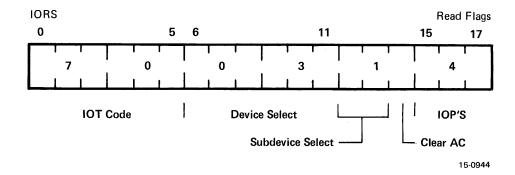

| 1-21       | IOT Instruction Format                                 |        |

| 1-22       | IOT Instruction Timing                                 |        |

| 1-23       | Memory Location Just After a Program Interrupt         |        |

| 1-24       | Common I/O Bus                                         |        |

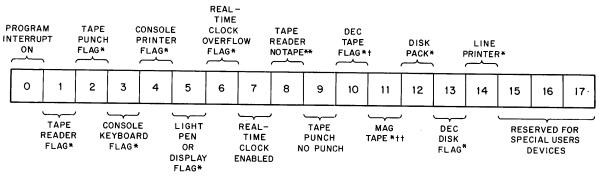

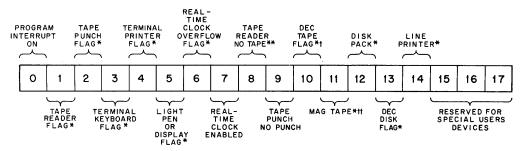

| 1-25       | I/O Read Status Bit Assignments                        |        |

| 1-26       | MF15-U Simplified Block Diagram                        |        |

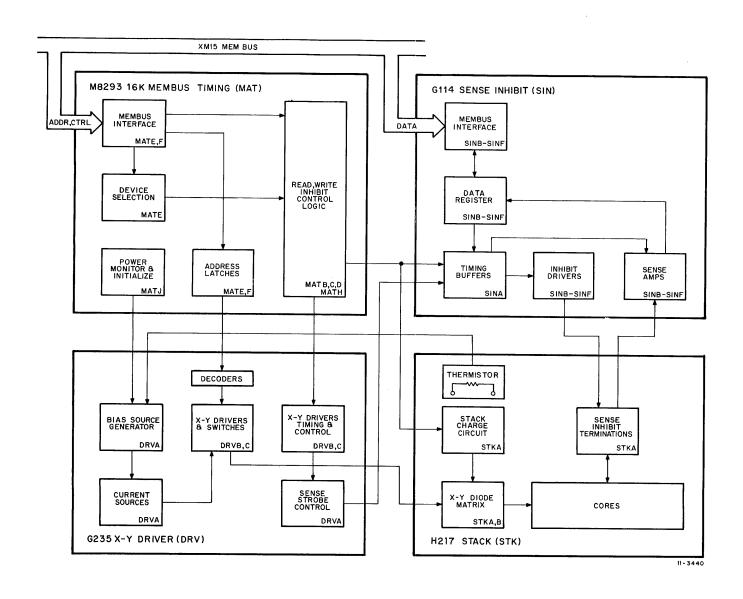

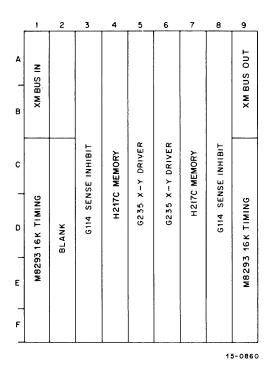

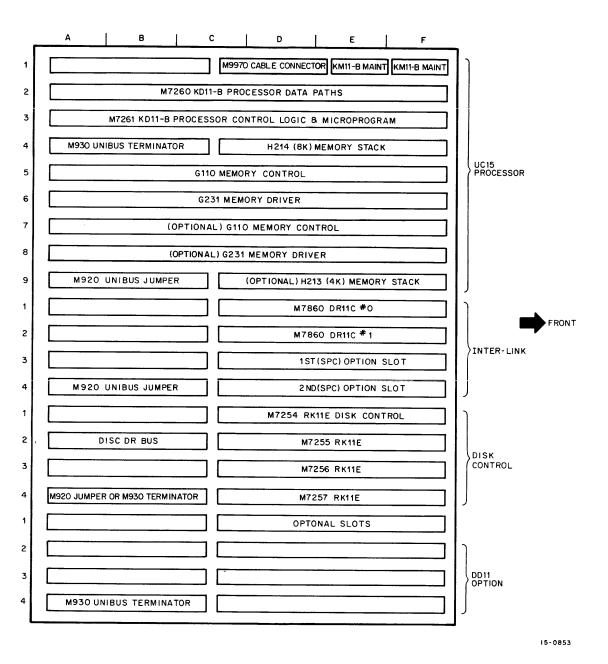

| 1-27       | Assigned Module Slots                                  |        |

| 2-1        | XM15 Basic Block Diagram                               |        |

| 2-2        | API System, Simplified Block Diagram                   |        |

| 2-3        | Memory Management Block Diagram                        |        |

| 2-4        | User's Virtual Address Space in S-MAP                  |        |

| 2-5        | S-Mapping                                              |        |

| 2-6        | Memory Address Translation                             |        |

| 2-7        | Memory Address Shifting Process                        |        |

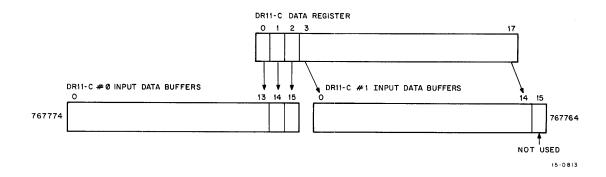

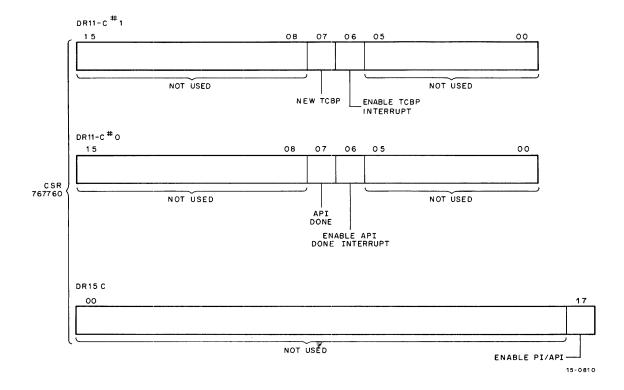

| 2-8        | Data Input                                             |        |

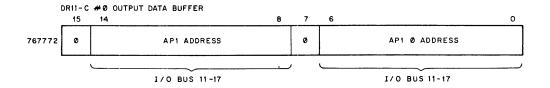

| 2-9        | Data Output                                            |        |

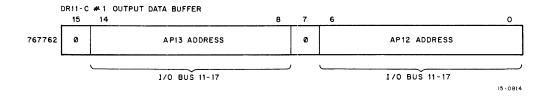

| 2-10       | Status Information                                     |        |

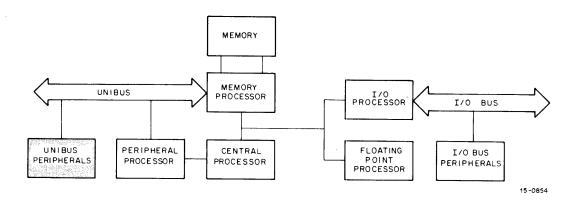

| 2-11       | PDP-11 System, Simplified Block Diagram                |        |

| 2-12       | FP15 Floating Point Processor Simplified Block Diagram |        |

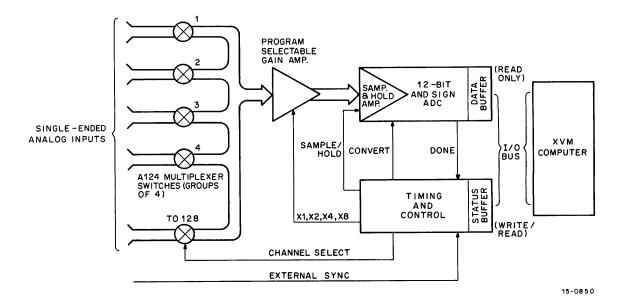

| 3-1        | AD15 Analog-to-Digital Conversion Subsystem            |        |

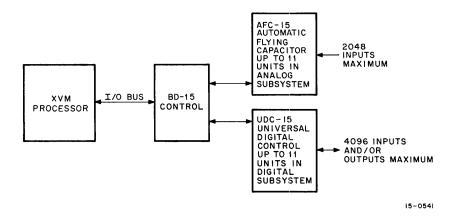

| 3-2        | Industrial Control System                              |        |

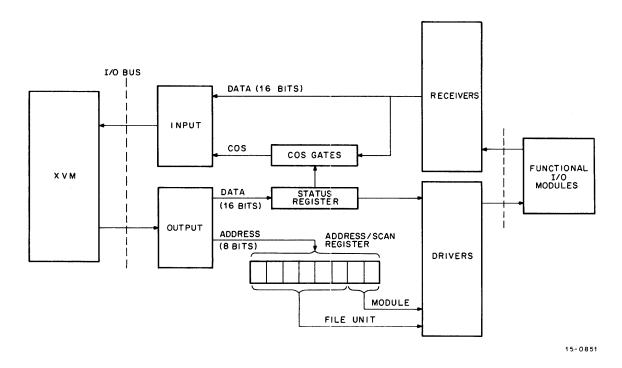

| 3-3        | UDC-15 Input/Output Operation                          |        |

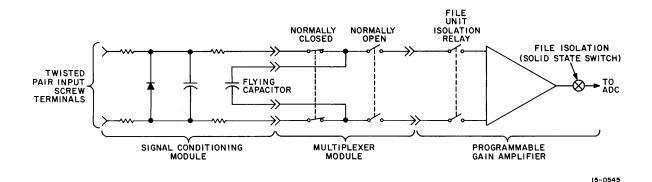

| 3-4        | Flying Capacitor Circuit                               | 3-7    |

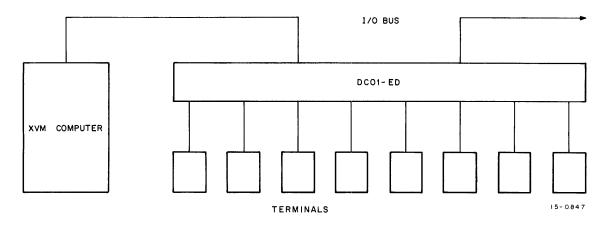

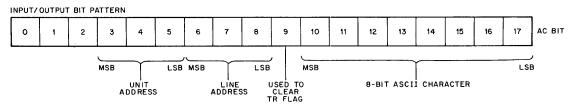

| 3-5        | DC01-ED Block Diagram                                  |        |

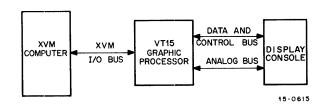

| 3-6        | VT15 Graphic Processor, Block Diagram                  |        |

| 3-7        | VT07 and VT04 Graphic Display Consoles                 |        |

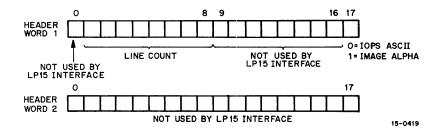

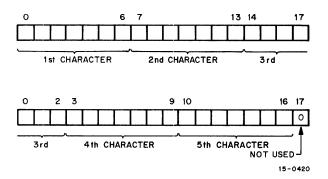

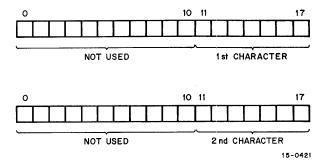

| 3-8        | LP15 Data Buffer Header Format                         |        |

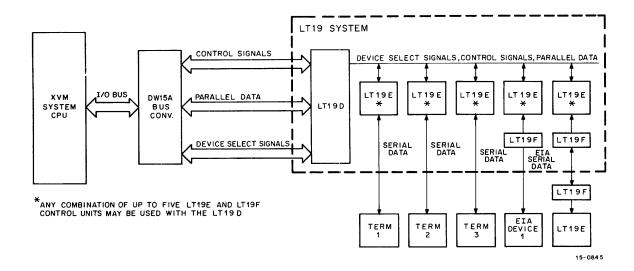

| 3-9        | Typical LT19 System Configuration                      |        |

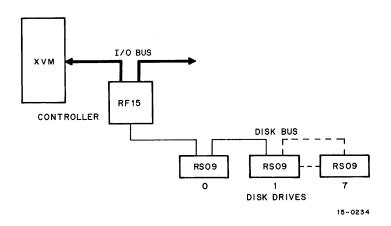

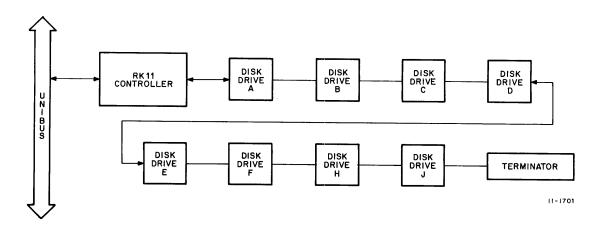

| 3-10       | XVM DECdisk System                                     |        |

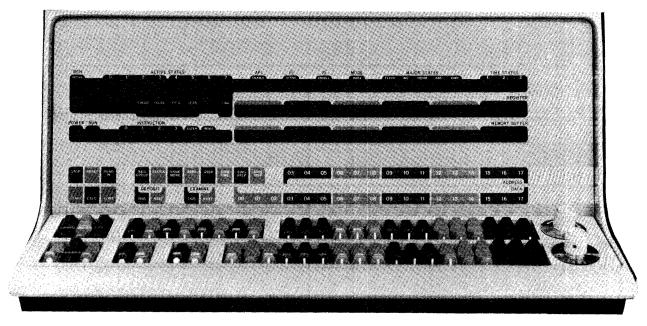

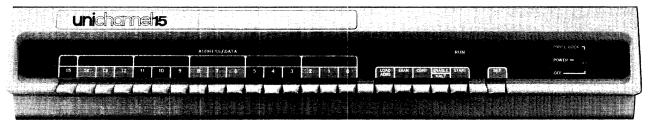

| 4-1        | XVM Console                                            |        |

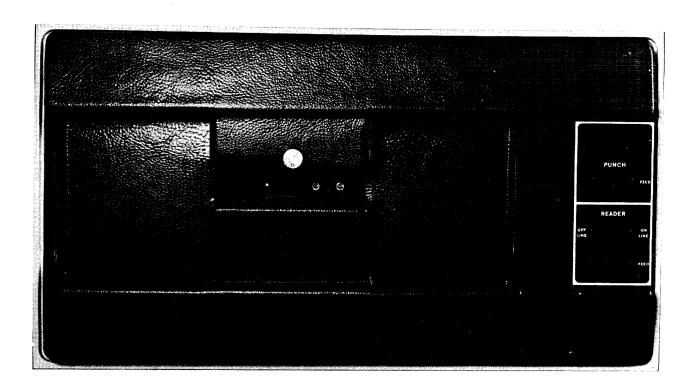

| 4-2        | Peripheral Processor                                   |        |

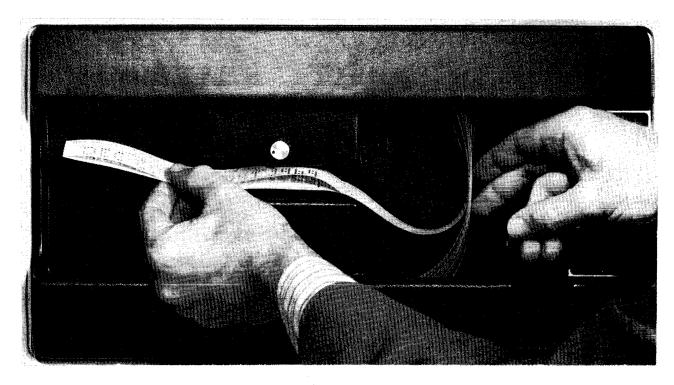

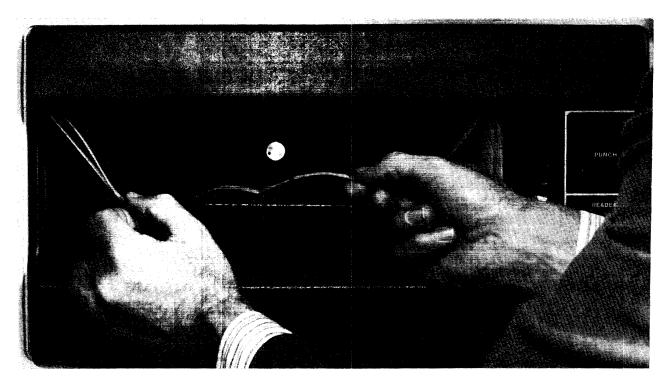

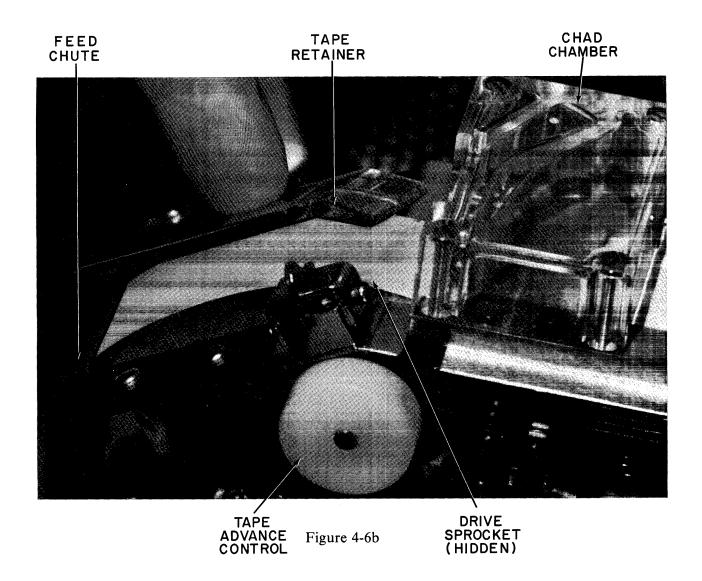

| 4-3        | Paper Tape Reader and Punch                            |        |

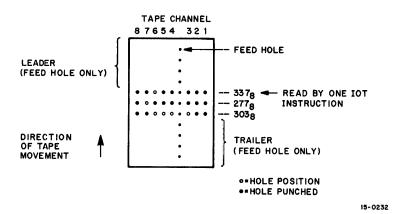

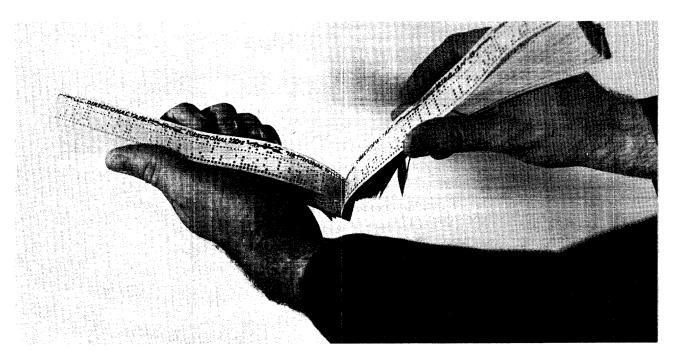

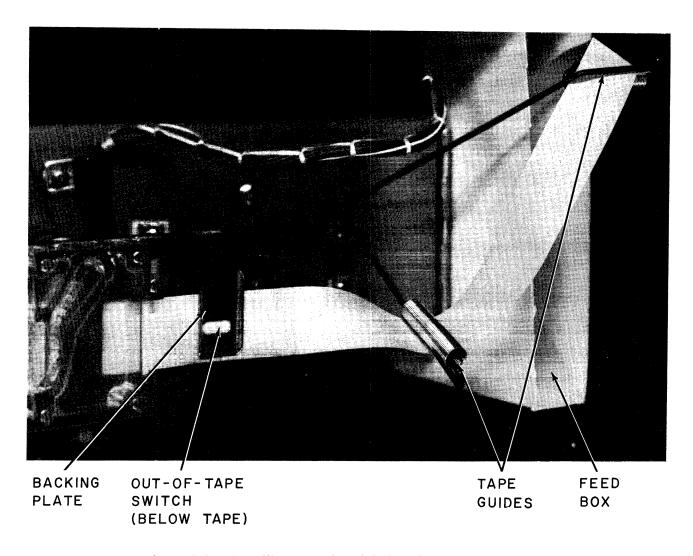

| 4-4        | Orienting the Tape                                     |        |

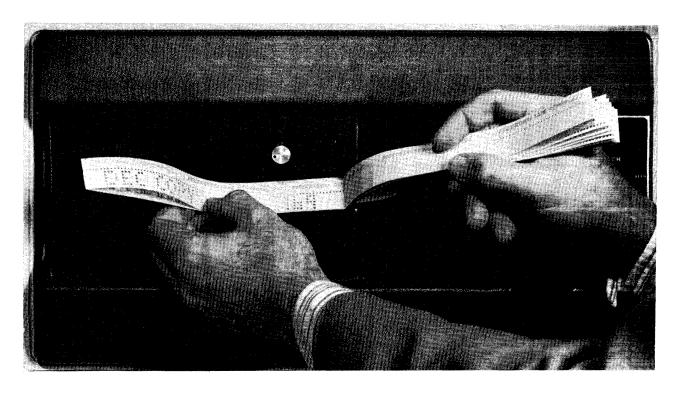

| 4-5        | Installing Tape in Paper Tape Reader                   | . 4-21 |

| 4-6        | Installing Tape in High-Speed Paper Tape Punch         | . 4-24 |

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                             | Page   |

|------------|-------------------------------------------------------------------|--------|

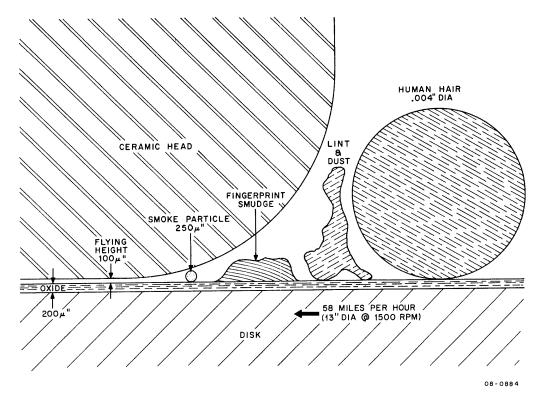

| 5-1        | Relationship of Disk Head, Disk, and Contaminants                 | . 5-8  |

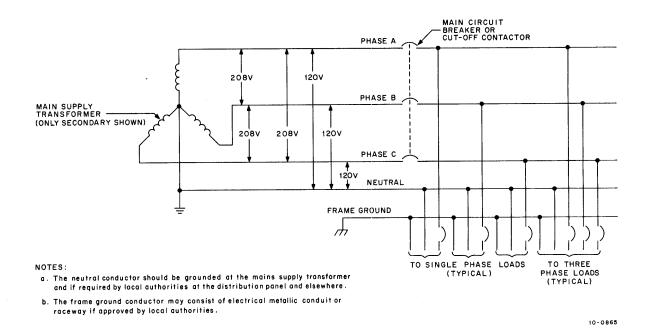

| 5-2        | 60 Hz Power System                                                | . 5-9  |

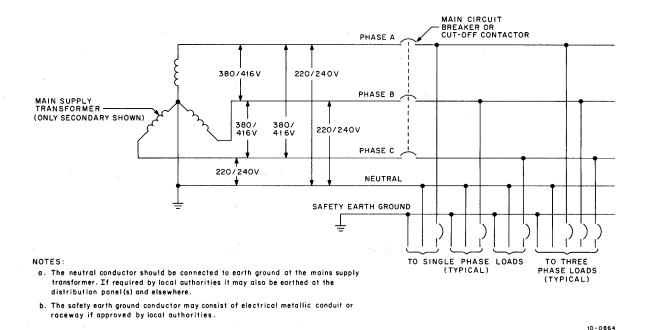

| 5-3        | 50 Hz Power System                                                |        |

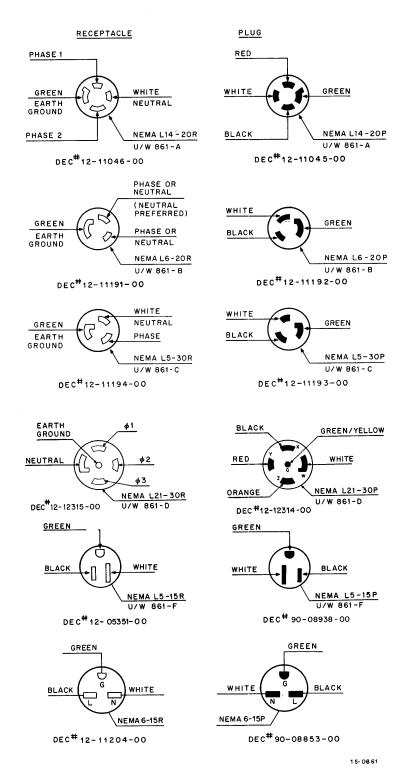

| 5-4        | NEMA Plugs Supplied with Digital Equipment Corporation's Products |        |

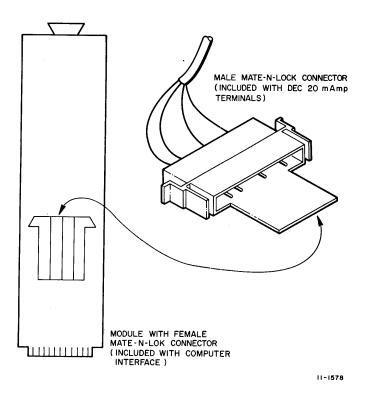

| 5-5        | 20 mA Mate-N-Lok Connector                                        | . 5-15 |

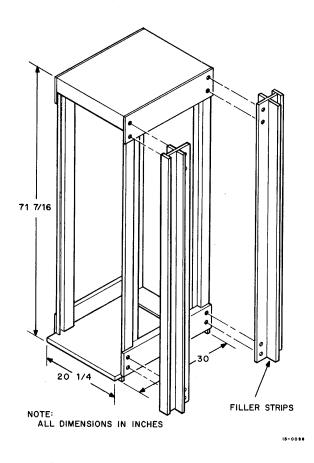

| 5-6        | Cabinet Bolting Diagram                                           | . 5-17 |

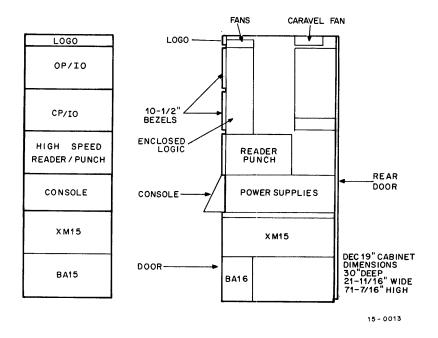

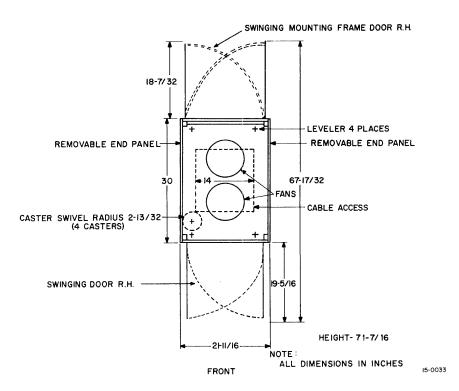

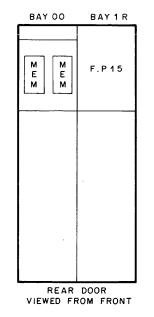

| 5-7        | XVM Basic Configuration                                           | . 5-17 |

| 5-8        | Basic XVM Cabinet                                                 | . 5-18 |

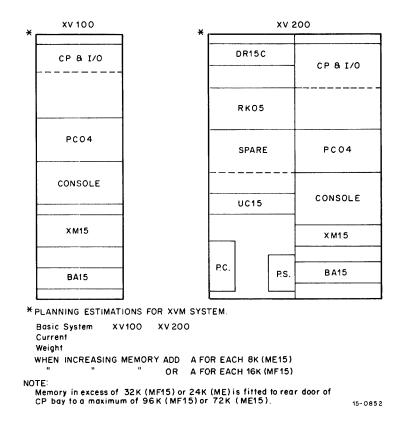

| 5-9        | XV100 and XV200 Physical Configurations                           | . 5-18 |

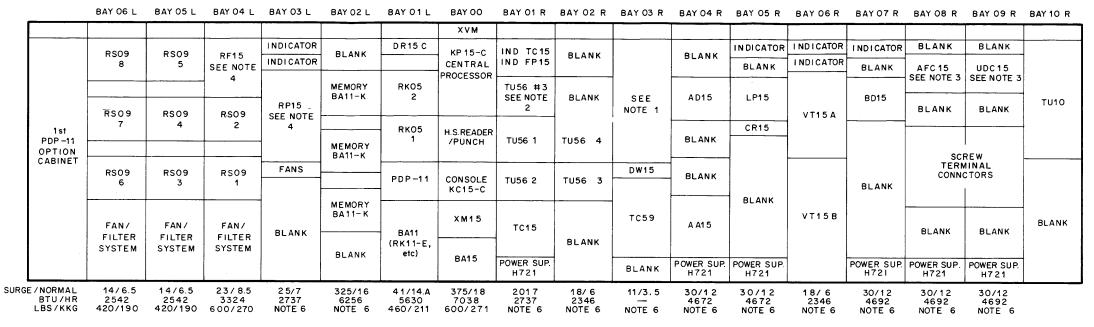

| 5-10       | System Configuration Diagram                                      |        |

| 5-11       | Peripheral Processor Configuration Guide                          | . 5-20 |

| 6-1        | Memory Reference Instruction Word                                 |        |

| 6-2        | Augmented Instruction Format                                      | . 6-2  |

| 6-3        | Instruction Bit Configuration                                     |        |

| 6-4        | Allowable Microinstruction Combinations                           | . 6-10 |

| 6-5        | IOT Instruction Word Format                                       | . 6-31 |

| 6-6        | IOT Instruction Timing                                            | . 6-32 |

| 6-7        | IORS Word Status Bit Assignments                                  | . 6-33 |

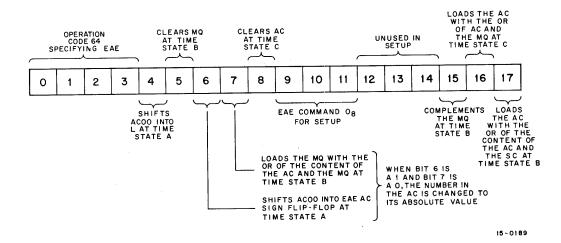

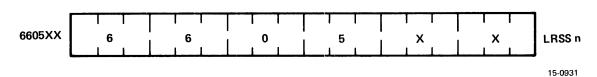

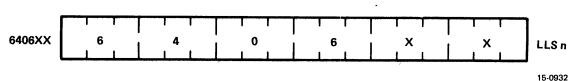

| 6-8        | EAE Setup Microinstructions                                       |        |

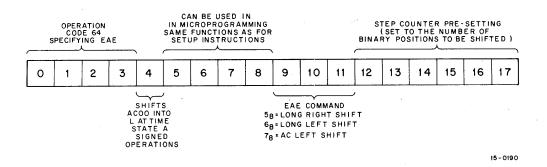

| 6-9        | EAE Shift Microinstructions                                       | . 6-37 |

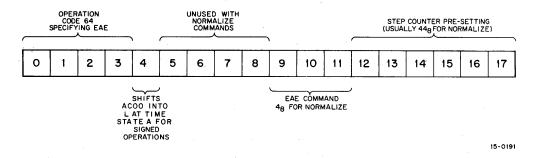

| 6-10       | EAE Normalize Microinstructions                                   | . 6-37 |

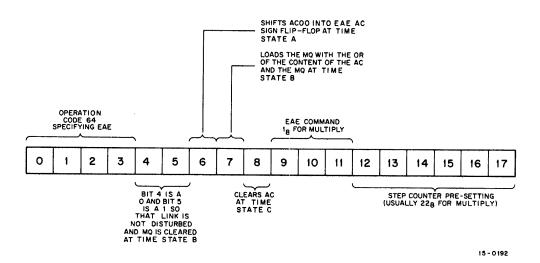

| 6-11       | EAE Multiplication Microinstructions                              | . 6-38 |

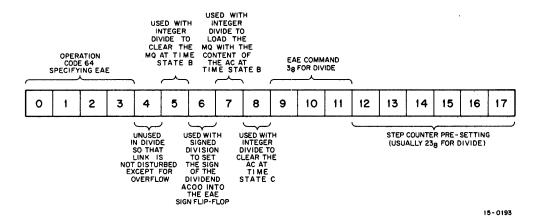

| 6-12       | EAE Division Microinstructions                                    | . 6-38 |

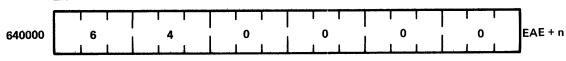

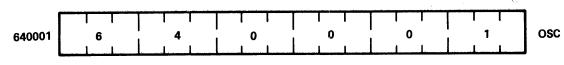

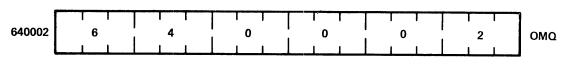

| 6-13       | EAE Simplified Block Diagram                                      | . 6-39 |

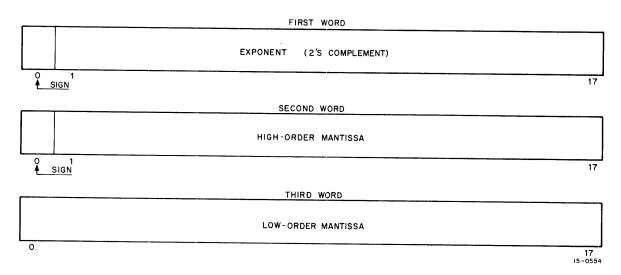

| 6-14       | Floating Point Instruction Format                                 | . 6-68 |

| 6-15       | Floating Point Address Format                                     | . 6-69 |

| 6-16       | Single Precision Integer Format                                   | . 6-69 |

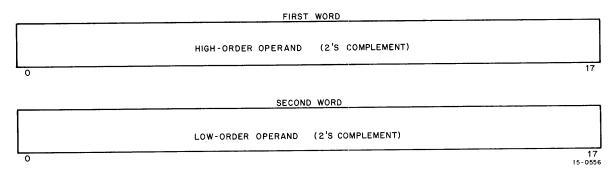

| 6-17       | Extended Integer Format                                           | . 6-69 |

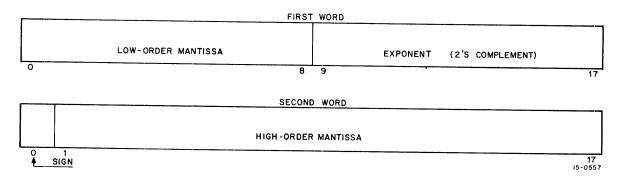

| 6-18       | Single Precision Floating Point Format                            |        |

| 6-19       | Double Precision Floating Point Format                            | . 6-70 |

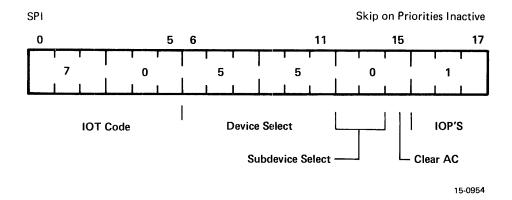

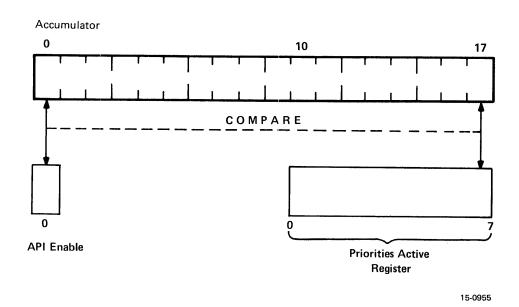

| 6-20       | Skip on Priorities Inactive                                       | . 6-74 |

|            | TABLES                                                            |        |

| Table No.  | Title                                                             | Page   |

| 1-1        | Interface Devices                                                 | . 1-35 |

| 1-2        | MF15-U Core Memory, Specification Summary                         |        |

| 1-3        | ME15 Memory Specifications                                        |        |

| 4-1        | Console Controls                                                  |        |

# TABLES (Cont)

| Table No. | Title                                                  |        |  |  |

|-----------|--------------------------------------------------------|--------|--|--|

| 4-2       | Console Indicators                                     | . 4-10 |  |  |

| 4-3       | Paper-Tape Reader and Punch Controls                   |        |  |  |

| 5-1       | Summary of Site Preparation and Installation Functions |        |  |  |

| 5-2       | Recommended System Environmental Ranges                |        |  |  |

| 5-3       | Voltage Ranges                                         |        |  |  |

| 5-4       | Cabinet-mounted Options                                |        |  |  |

| 5-5       | Current Free-Standing Peripherals                      |        |  |  |

| 5-6       | Optional Peripheral Equipment Cable Lengths            |        |  |  |

| 6-1       | EAE Microinstructions                                  |        |  |  |

| 6-2       | EAE Microinstructions                                  |        |  |  |

| 6-3       | FP15 Instruction Summary                               |        |  |  |

| 6-4       | Input/Output Transfer Instructions                     |        |  |  |

| 6-5       | Standard API Channel/Priority Assignments              |        |  |  |

| 6-6       | IOT Device Selection Codes                             |        |  |  |

#### **FOREWORD**

XVM systems offer comprehensive solutions to data processing needs. They combine new design concepts with a wide array of traditional features that have evolved from DIGITAL's years of leadership in the medium scale scientific computer field. Both elements share the common purpose of simplifying the application of XVM computer systems to accommodate demanding environments.

XVM systems excel in applications where hardware and software components are matched to meet the requirements of the user. These matches of hardware and software components can be viewed at two levels. First, XVM systems come with a complete assortment of support software tools to allow complete programming. These tools, such as monitors, compilers, and system utility components, are the base on which all XVM systems are built. Second, for certain specific turn-key applications, XVM systems come ready to perform applications work with no further programming. At both levels, hardware components allow for modular additions and field upgrades without penalty.

DIGITAL offers a variety of configurations as hardware building blocks to total system capability. These systems differ in their hardware options and peripherals that are required to support various operational software.

The hardware systems are designed with several functional objectives in mind. Among these are the complete autonomy between central processor, input/output processor, and memory, so that processing and I/O operations can occur concurrently in overlapping cycles: A PDP-11 programmable peripheral processor, so that slow speed devices can be spooled to a high performance disk; TTL integrated-circuit construction for high reliability; fast internal speeds, to meet the demands of real-time data processing; core memory expansions to 131,072 words for future growth; floating point hardware for demanding scientific applications; and a sophisticated memory protect system for multiuser integrity in multiprogramming environments. Peripheral device handling and interfacing to instruments are easily accomplished and system growth potential is virtually unlimited with the modular structure of the XVM hardware and software systems.

#### INTRODUCTION

The XVM 18-bit computer has unique capabilities attractively suited to high-speed data acquisition and processing. Expandable core memory (to 131,072 words) and a full complement of processor options and peripherals enable the XVM to handle virtually any medium scale computing requirement.

This manual supplies background information to familiarize the reader with present and potential capabilities of the system.

#### THE XVM SYSTEM

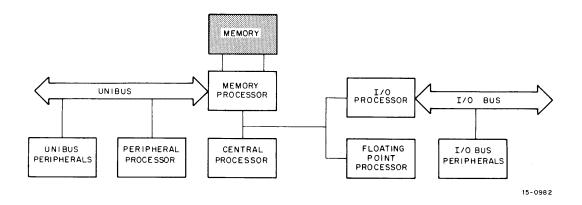

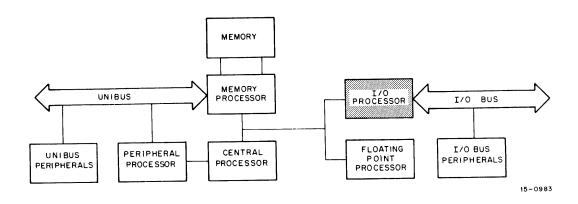

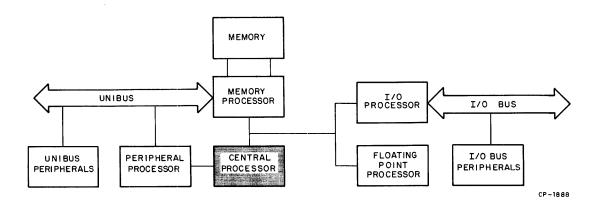

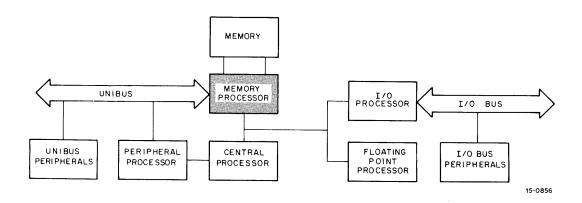

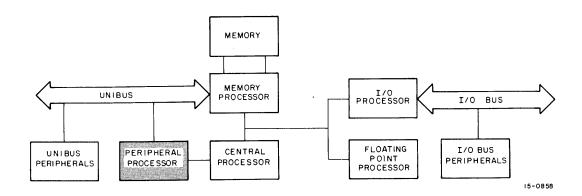

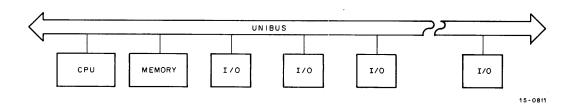

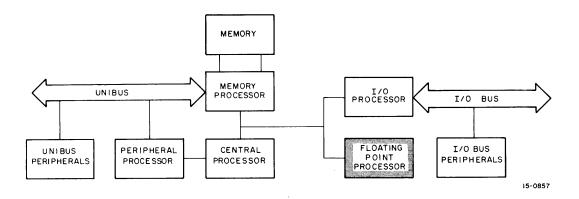

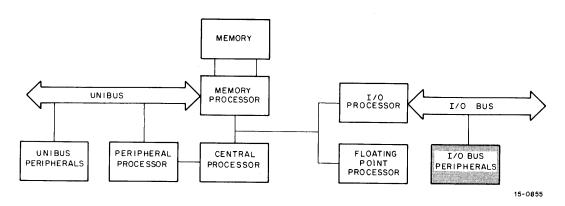

The basic XVM System is organized into three autonomous subsystems: central processor, memory, and I/O processor, each with independent timing and control logic. Communication between these subsystems occurs through use of an effective asynchronous request scheme. Subsystem autonomy facilitates wide scale expansion of the system, increased throughput, high capacity, reliability, and maintainability. Four other major subsystems of the XVM are: the floating point processor, the peripheral processor, the XVM I/O bus peripherals, and the Unibus peripherals.

#### **CENTRAL PROCESSOR (CPU)**

The CPU controls and executes the system's stored programs. By virtue of its control autonomy, the CPU coordinates its operation with that of other subsystems, thus providing supervisory control over the XVM.

As the main unit in this integrated control, the central processor contains arithmetic and control logic hardware for a wide range of operations, including high-speed, fixed point arithmetic and hardware multiply and divide option, extensive test and branch operations implemented with special hardware registers, high-speed input/output instructions, and other arithmetic and control operations.

The basic processor includes a number of major registers for processor-memory communications; it also includes a program counter, an accumulator, an Index register, and a Limit register. Two 18-bit registers provide memory buffer functions. This allows for processor overlap with memory cycle time and affects faster instruction execution times.

#### **MEMORY**

Memory is the primary storage area for computer instructions and system data. Independent read/write control and buffer logic in each memory segment establishes complete autonomy for the memory, i.e., different memories can be accessed simultaneously by different processors. The primary XVM memory systems are the ME15 and MF15 memory units that permit installation and utilization of up to 131,072 words of core memory in 8K or 32K increments.

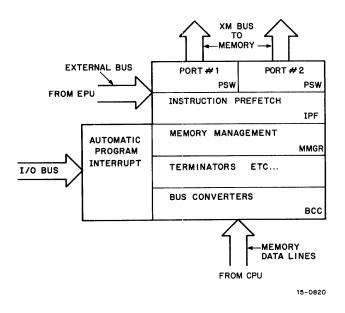

#### **MEMORY PROCESSOR**

The XM15 Memory Processor, located between the memory and the CPU, I/O, and peripheral processors, contains the Memory Management logic, the Instruction Pre-fetch unit, the Automatic Priority Interrupt unit, and the Memory Ports which arbitrate the different memory requests. The XM15 has dual input ports, and may have two output ports to memory. The device will operate with either ME15 (8K) or MF15 memories on one or both of its output ports. Memory interleaving is possible with similar memory types and it is also possible to interleave the two output ports.

#### I/O PROCESSOR

The I/O processor satisfies the peripheral data transfer needs. A diverse line of system peripherals available to the XVM require this processor to interface three modes of input/output:

- 1. Single cycle block data transfer; blocks of data transfer at rates of up to 1 million words per second.

- 2. Multicycle block data transfer; blocks of data transfer at rates up to 250,000 per second for input and 180,000 per second for output.

- 3. Program control data transfers; single word transfers to/from the accumulator in the central processor unit.

The I/O processor provides timing, control, and data lines for information transfers between memory or the central processor and the peripheral devices. It also provides for such features as the automatic priority interrupt system and the real-time clock.

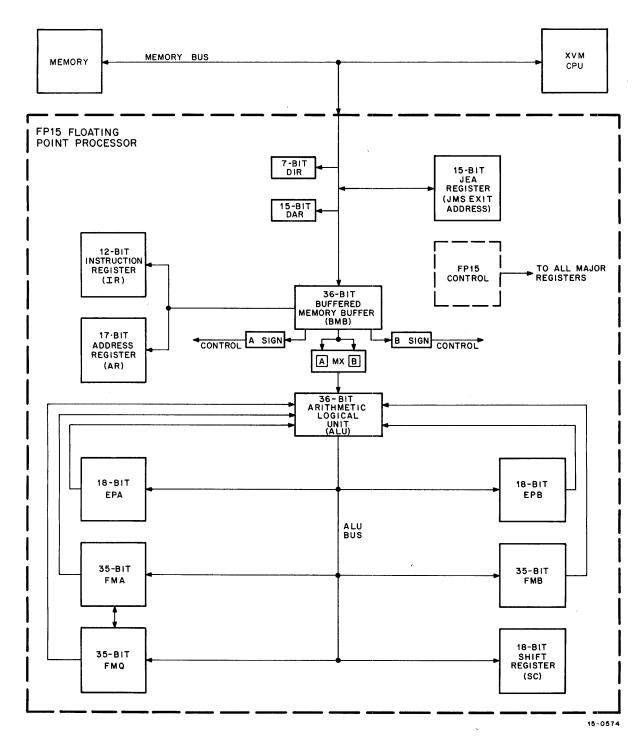

#### **FP15 Floating Point Processor**

The FP15 enables the XVM to perform arithmetic and logic operations using floating point arithmetic. The prime advantage is increased speed over complex floating point software routines. The FP15 has single precision and extended integer capability, as well as single and double precision floating point.

The FP15 is an expansion of the central processing unit and increases the XVM instruction set by over 120 instructions. Floating point instructions intermix with XVM instructions. This In-line mode of operation greatly simplifies programming and ensures fast execution.

#### **Peripheral Processor**

The Unichannel 15 (UC15) is a peripheral processor for XVM that uses a PDP-11 minicomputer. It provides the XVM with a second general purpose processor and a second high-speed I/O bus: The Unibus is an 18-bit pathway permitting transfer of 18-bit words, 16-bit PDP-11 words, or two 8-bit bytes.

# CHAPTER 1 XVM PROCESSOR

#### 1.1 CENTRAL PROCESSOR DESCRIPTION

The central processor (CPU) controls and executes stored programs. By coordinating its operation with that of other subsystems, it provides supervisory control over the XVM system.

The CPU contains arithmetic and control logic for a wide range of operations. These include high-speed, fixed point arithmetic with hardware multiply and divide, extensive test and branch operations implemented with special hardware registers, high-speed input/output instructions, and other arithmetic and control operations.

The XVM CPU contains several major registers for processor-memory communications, – a Program Counter, an Instruction register, an accumulator, an Index register, and a Limit register.

#### **SUMMARY OF CHARACTERISTICS**

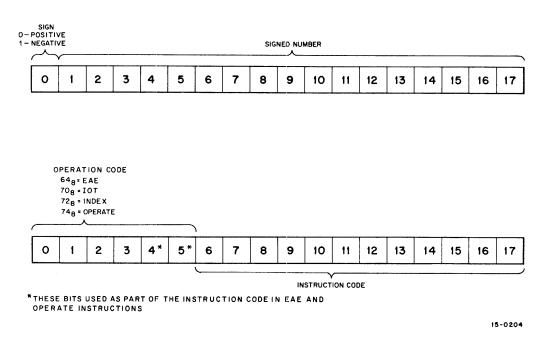

Description – 18-bit parallel operation, asynchronous operation, fixed point signed and unsigned arithmetic (1's and 2's complement)

Instruction Types

Memory Reference

Operates

Register Transfer and Control

Extended Arithmetic Element

Input/Output Transfer

Indexing - 1 Index register, 1 Limit register, 8 auto-increment locations

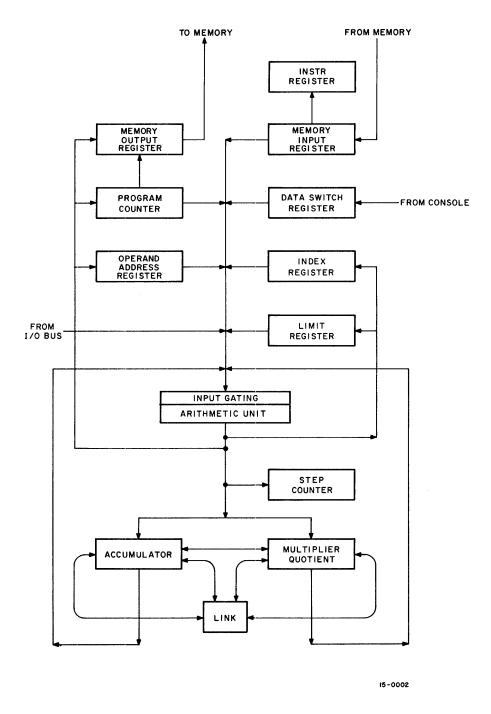

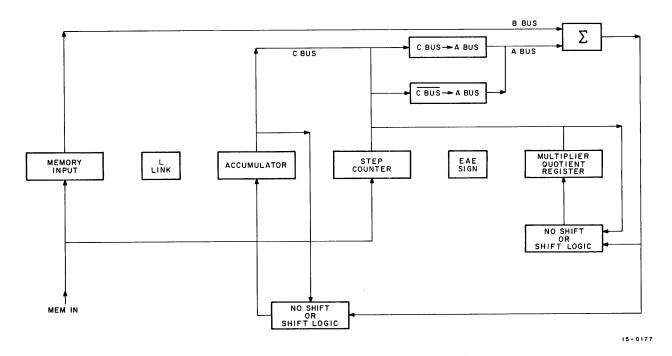

The CPU performs calculations and data processing in a parallel binary mode through step-by-step execution of individual instructions. Both the instructions and the data on which the instructions operate are stored in the core memory of the XVM. The arithmetic and logical operations necessary for executing instructions are performed by the arithmetic unit operating with central processor registers. Figure 1-1 shows a simplified block diagram of the CPU.

Figure 1-1 Central Processor, Simplified Block Diagram

#### Arithmetic Unit (AU)

The XVM Arithmetic Unit (AU) handles all Boolean functions and contains an 18-bit, 85 ns adder. The AU acts as the transfer path for inter-register transfers and shift operations.

#### Instruction Register (IR)

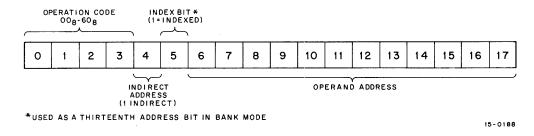

This register accepts the six most significant bits of each instruction word fetched from memory. Of these bits, the four most significant constitute the operation code, the fifth signals when the fetched instruction indicates indirect addressing, and the sixth indicates indexing.

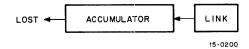

#### Accumulator (AC)

This 18-bit register retains the result of most arithmetic/logical operations.

For all program-controlled input/output transfers, information is transferred between core memory and an external device through the AC. The AC can be cleared and complemented. Its contents can be rotated right or left with the Link. The contents of the memory, buffered through the Memory Input register, can be added to the contents of the AC with the result left in the AC. The contents of both registers can be combined by the logical operations AND and exclusive-OR, the result remaining in the AC. The inclusive-OR can be performed between the AC and the data switches on the operator's console (through the Data Switch register) and the result left in the AC.

#### **Data Switch Register**

The Data Switch register receives and stores an 18-bit word through the console bus from data switches on the console. This allows programs to accept switch data from the operator's console.

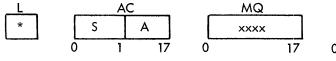

#### Link (L)

This 1-bit register is used to extend the arithmetic capability of the accumulator. In 1's complement arithmetic, the Link is an overflow indicator; in 2's complement arithmetic, it logically extends the accumulator to 19 bits and functions as a Carry register. The program can check overflow into the Link to simplify and speed up single- and multi-precision arithmetic routines.

The Link can be cleared and complemented and its state sensed independent of the accumulator. It is included with the accumulator in rotate operations and in logical shifts.

#### Program Counter (PC)

The PC determines the program sequence (the order in which instructions are performed). This 17-bit register contains the address of the next instruction.

#### Operand Address Register (OA)

The Operand Address register is an internal register that contains the address of the location where data is currently being fetched.

# Memory Input and Output Buffer Register (MI and MO)

Information is read from a memory cell into the Memory Input register and is interpreted as either an instruction or a data word. Information is read from the CPU into memory through the Memory Output register, and is interpreted as either an address or a data word. The use of two internal 18-bit registers for memory buffer functions allows processor overlap with memory cycle time to decrease execution time and to allow autonomous operation of the CPU and memory. They also allow the I/O processor to gain access to memory between cycles of multicycle instructions. By not having to wait for completion of an instruction, I/O device latency is vastly improved.

Index Register (XR)

The 18-bit Index register is used to perform indexing operations with no increase in instruction time. An indexed operation adds the contents of the Index register to the address field of the instruction operand, producing an effective address for the data fetch cycle. Index value can be positive or negative in 2's complement form (+131,072). The Index register can be used with the Limit register, described in the following paragraph.

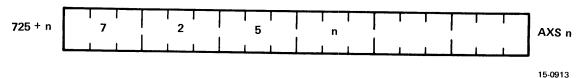

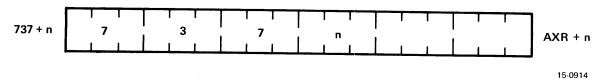

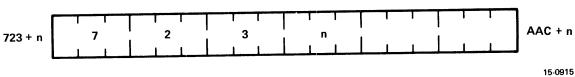

Limit Register (LR)

The 18-bit Limit register enables a program to detect loop completion. The base address of a data array is loaded into the Index register and the ending address is loaded into the Limit register. Within an indexing loop, add to index and skip (AXS) instruction adds a signed value ( $-256_{10} \le Y \le +255_{10}$ ) to the Index register and compares the sum in the index to the contents of the Limit register. If the contents of the Index register are equal to or greater than those of the Limit register, the next instruction is skipped.

#### **XVM Control Console**

The XVM system console contains the controls, switches, and lights required for operator initiation, control, and monitoring of the system. Up to twenty-four 18-bit registers can be displayed to provide the user with visual indication of major registers and buses.

Some of the features of the console are:

- A READ-IN switch to initiate the hardware reading of the bootstrap devices.

- REGISTER indicators and REGISTER DISPLAY switches to allow continual monitoring of key points in the system such as the accumulator, Index register, Limit register, Multiplier-Quotient register, Program Counter, memory address, interrupt status, input/output bus, input/output address, and I/O status.

- Separate ADDRESS and DATA switches to establish an 18-bit data or instruction word to be read into a memory location by the DEPOSIT switch, to be entered into the accumulator by a program instruction, or to be executed by the EXECUTE switch.

- EXAMINE switch to allow the manual examination of the contents of any memory location placed in the ADDRESS switches.

#### **KE15 EXTENDED ARITHMETIC ELEMENT (EAE)**

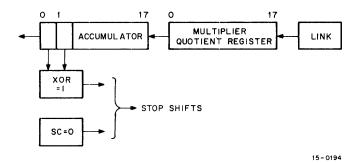

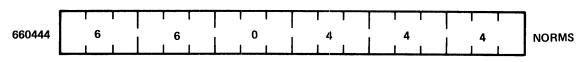

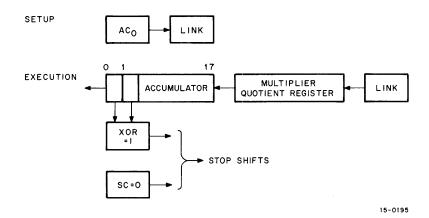

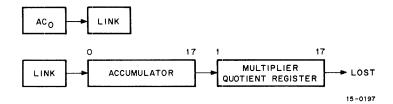

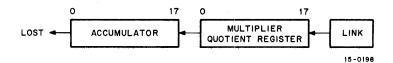

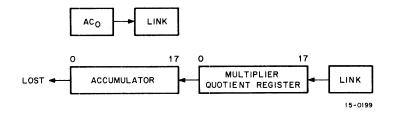

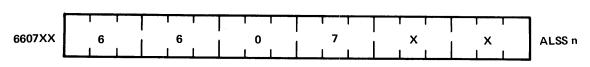

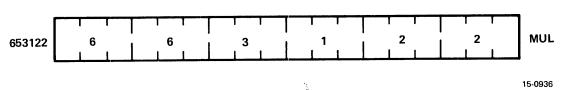

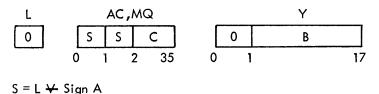

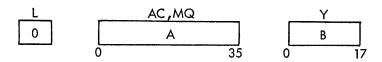

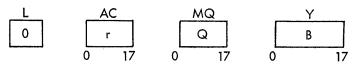

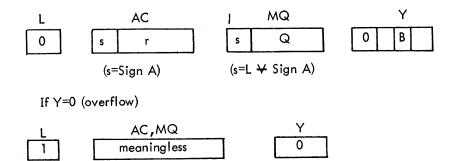

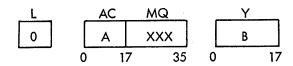

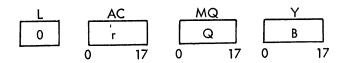

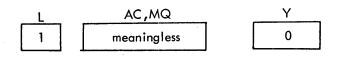

The KE15 Extended Arithmetic Element (EAE) is a standard XVM feature which facilitates high-speed arithmetic operations and register manipulations. The EAE uses an 18-bit Multiplier-Quotient register (MQ) as well as a 6-bit Step Counter register (SC). EAE instructions can be microcoded so that several operations are performed by one instruction to simplify arithmetic programming and reduce execution time.

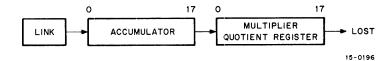

Multiplier-Quotient Register (MQ)

The Multiplier-Quotient register and accumulator perform as a 36-bit register during shifting, normalizing, multiplication, and division operations. The contents of the Multiplier-Quotient register are displayed by the REGISTER indicators on the operator's console when the REGISTER DISPLAY control is in the MQ position.

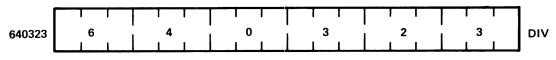

During the multiply instruction, the MQ receives the 18 least significant bits of the double word product formed in the AC and MQ. During the divide instruction, the MQ is the least significant 18 bits of the double word DIVIDEND formed by the AC and MQ.

#### Step Counter (SC)

The Step Counter is used to count the number of steps in an EAE instruction. The step counter is preloaded, except during normalize operations, with the numbers of steps specified by an instruction and is counted down as the instruction is executed. When the SC reaches zero, the EAE operation is terminated.

#### PROCESSOR EXPANSION

#### **KF15 Power Failure Protection**

The basic XVM is not affected by power interruptions of less than 10 ms duration. Active registers in the processor may lose their contents when interrupts of longer duration occur, but memory is not disturbed. The KF15 Power Failure feature, standard on all XVM systems, allows the preservation of the active register contents in the event of longer power interrupts and the automatic restart of the system when power is restored. When the line power failure occurs, the system must be operating with the program interrupt facility or the automatic priority interrupt system enabled in order to sense the KF15's initiation of a program interrupt in time to save the register contents. When power is restored, the processor automatically restarts and the instruction in location 0 is executed.

#### 1.2 ADDRESSING

The following paragraphs explain XVM addressing modes and formats.

#### Words in Memory

Words stored in magnetic core memory are simply strings of 18 bits. There is no method of distinguishing between an instruction word and a data word. The Central Processor Unit (CPU), which decodes and operates an instruction word, can differentiate between instruction and data words because of the sequence in which they appear at the CPU, from memory.

To keep track of the sequence, the processor is provided with a Program Counter which normally holds the address of the next location in sequence in the memory. The word thus located, may point to another location that is the address of a data word or instruction.

There are three main types of instructions:

- 1. Instructions that reference memory indicating in the operand address field the (virtual) location of the data necessary to complete the instruction. For example, ADD the contents of location 000100 to the accumulator.

- 2. Instructions that deal with control, and do not require a memory access. For example, RAL: Rotate the accumulator and link one place to the left.

- 3. Instructions that reference peripheral equipment, and cause information transfers to or from the devices, termed IOT's. For example, TLS: Load console terminal print buffer from AC10-17, and start printing.

#### Addresses

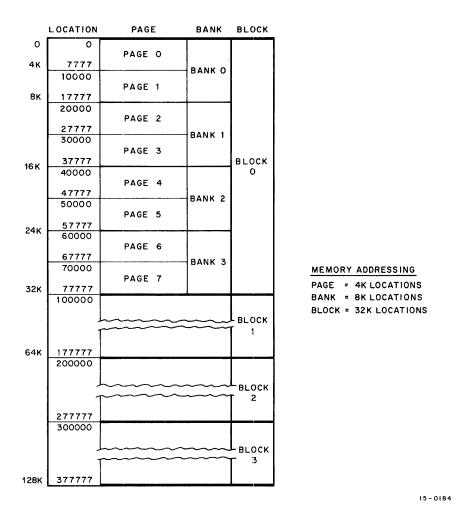

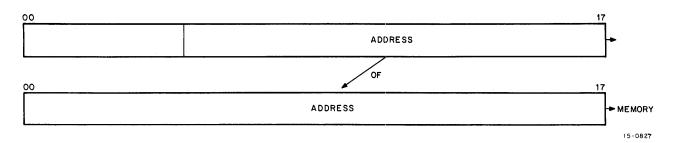

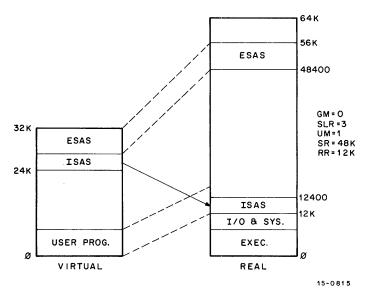

There are two types of addresses: real and virtual. The XVM system uses both types in a variety of ways to facilitate as many operations as possible (Figure 1-2).

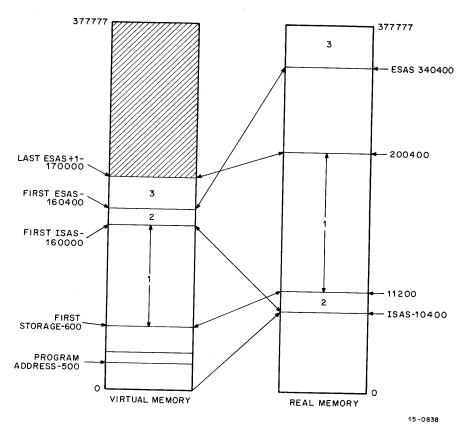

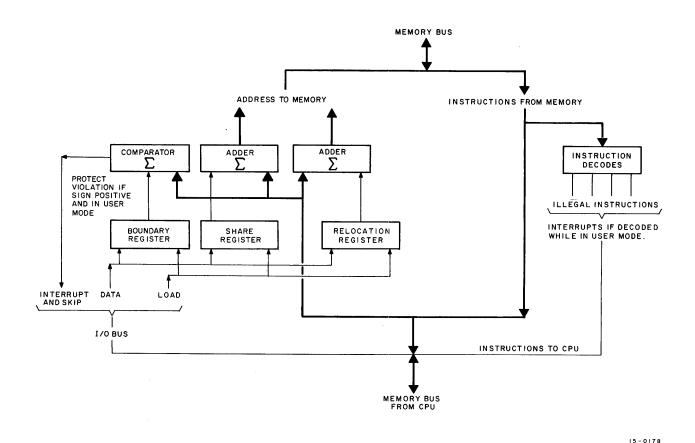

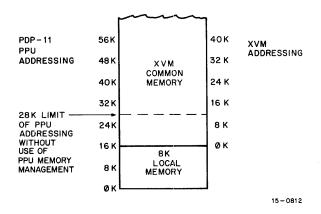

Virtual addresses are those calculated by the CPU and sent to the Memory Processor Unit (MPU). Virtual addressing makes it possible for many users to obey the same rules, use the same addresses, and yet all can use the XVM system at the same time. The virtual addresses are accepted by the MPU and modified if necessary, depending upon which manner of addressing is currently set up within the MPU. The resulting address is then sent to memory as a real address. A real address corresponds to the required location in memory, as shown in Figure 1-3.

Figure 1-2 Real and Virtual Addresses

Figure 1-3 Memory Addressing

#### 1.2.1 XVM CPU Addressing Modes

The XVM Central Processor produces an address in a variety of ways which are described briefly in the following paragraphs to assist the reader in understanding the whole addressing picture. Detailed programming examples are provided in paragraph 1.2.3.

To start with, assume that virtual addresses are un-modified by the MPU.

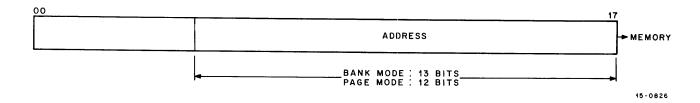

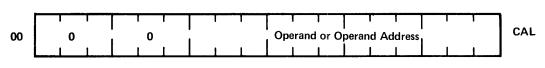

#### Direct Addressing: Type I

A direct address (Figure 1-4) is the most basic type of address. The address field is either 13 or 12 bits long, depending upon whether the XVM CPU is in Bank or Page mode respectively. This type address is usually termed an operand address, because an instruction normally occupies bits 00 to 03.

Figure 1-4 Direct Addressing: Type I

#### **Indirect Addressing: Type II**

An indirect address (Figure 1-5) is more complex than the direct address. The operand address (in the upper box) contains the address of a location, which in turn contains an address of a data word. The width of the address that is passed to memory depends upon the conditions prevailing in the MPU at that time. Normally, either 15- or 17\*-bit addressing is selected by the monitor's software.

Figure 1-5 Indirect Addressing: Type II

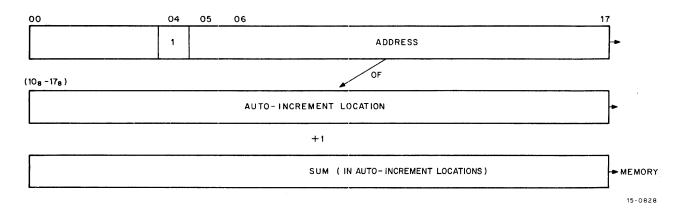

#### **Auto-Increment Addressing: Type III**

The auto-increment address (Figure 1-6) is a special type of indirect addressing. If any one of the addresses 00010 to 00017 should be addressed indirectly, the contents of this "auto-increment" location will be extracted, incremented, and restored. This value is then used as the address of the required data word. When these auto-increment addresses are accessed in any other way, they function as other locations. This feature facilitates the processing of sequential strings of data.

Note that the actual core memory locations affected by the auto-increment process are determined by the current settings of the MPU.

<sup>\*16-</sup> and 18-bit addressing is permitted, but it is not used by current DEC software.

Figure 1-6 Auto-Increment Addressing: Type III

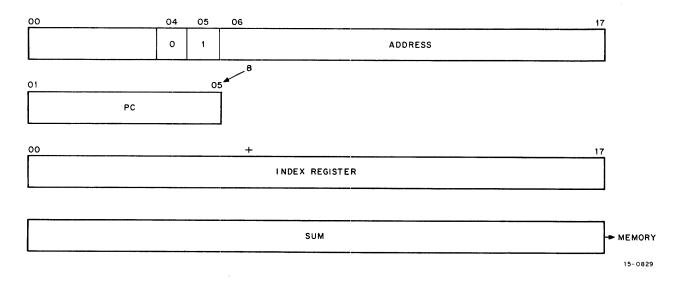

#### Indexed Addressing: Type IV

Indexed addressing (Figure 1-7) makes use of the Index register to address up to 131072 locations. Bit 05 is used to indicate that an indexed reference is being made. It follows that the XVM CPU must be running in Page mode to enable this mode of addressing. The operand address is concatenated with PC01-PC05, from the Program Counter (PC). The result is added to the contents of the Index register (XR) and the sum is used as the memory address. Note that the contents of the Index register may be negative.

Figure 1-7 Indexed Addressing: Type IV

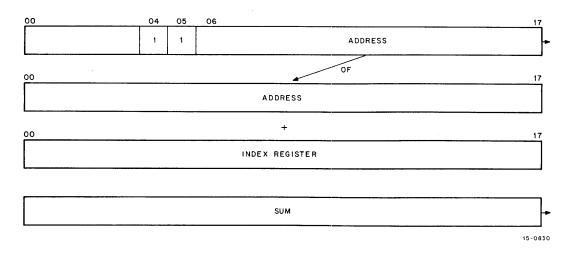

#### Indirect-Indexed Addressing: Type V

Indirect-indexed addressing (Figure 1-8) is the first of the composite types of addressing. The 12 bits of operand address point to (i.e., contain the address of) a location that holds an address. This second address may be 15 or 18 bits wide, depending on the internal settings of the MPU. This address has the contents of the Index register (18 bits) added to it, and the result is sent to the MPU. This will again affect the address such that either 16, 17, or 18 bits of address will be presented to the memory.

Figure 1-8 Indirect-Indexed Addressing: Type V

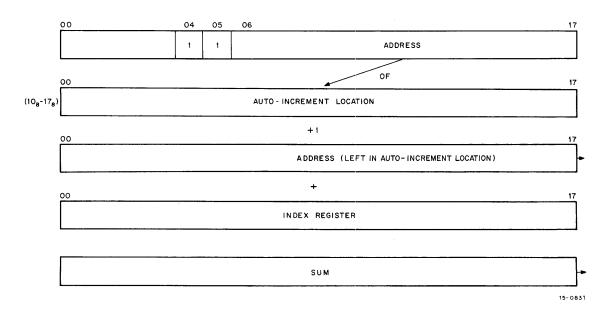

#### Auto-Increment, Indexed Addressing: Type VI

This is the most complex type of XVM CPU address formation (Figure 1-9). The operand address (between 10 and 17<sub>8</sub>), when referenced indirectly, becomes the pointer to an auto-increment location, the contents of which are incremented by one, and used as an address. The contents of this location has the current value of the Index register added to it, and the sum is used as the final address to be sent to the memory via the MPU.

Figure 1-9 Auto-Increment, Indexed Addressing: Type VI

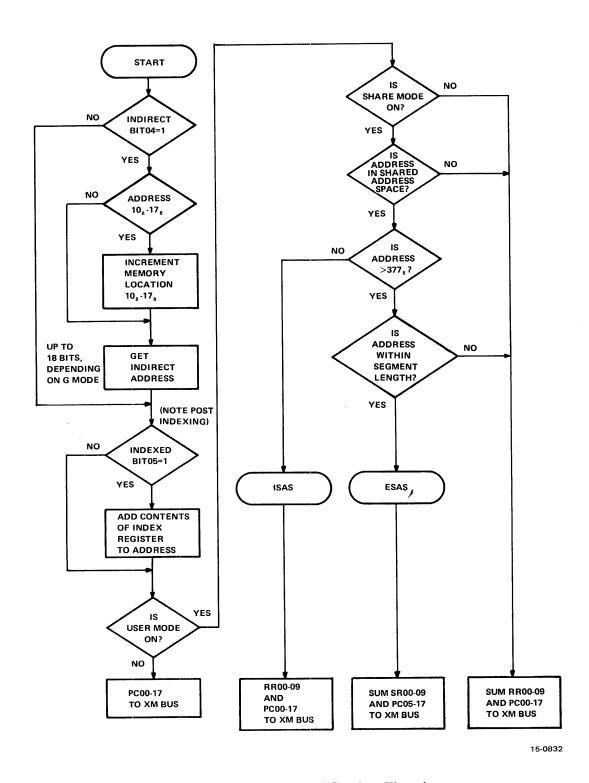

In summary, there are six XVM CPU addressing modes. These are designated Type I through Type VI, in order of their complexity. Figure 1-10 is a flow chart of the address modification sequence.

Figure 1-10 Address Modification Flowchart

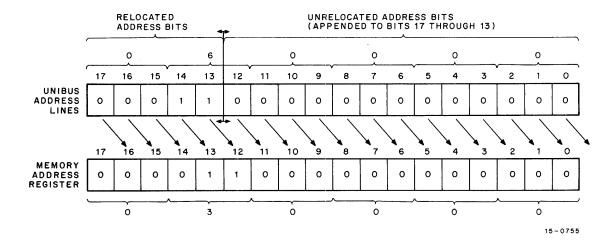

#### 1.2.2 XVM MPU Address Mapping

The following paragraphs briefly describe the four ways that the XVM MPU changes virtual addresses to real addresses before sending the addresses to core memory. The MPU performs a wide variety of functions. However, the majority of these functions are only operative when the system is in User mode (for a full description of User mode, see Chapter 2, Section 1).

There are four ways that the virtual address presented by the CPU can be converted to a real address:

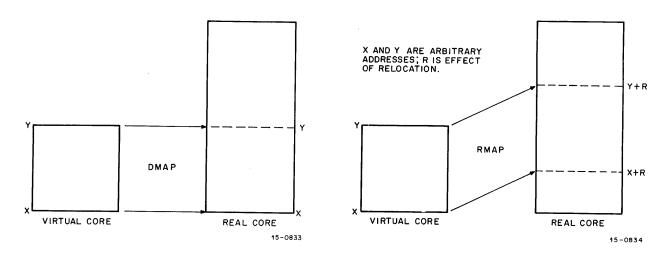

#### Direct Mapping (DMAP)

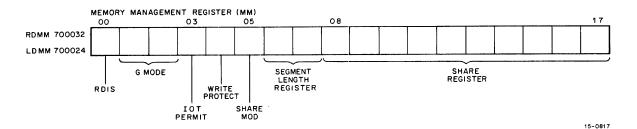

Refer to Figure 1-11. In this mode, the CPU-generated address is passed through the MPU and no modification takes place. This form of addressing is in effect whenever the system is in either of the two following states; first, when the system is in the Executive mode of operation, which means that none of the memory management functions are being used; second, when the system is in User mode, but the Relocate Disable (RDIS) function is operative.

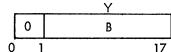

#### Relocated Mapping (RMAP)

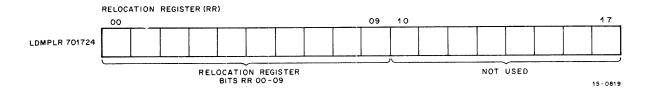

Refer to Figure 1-12. The system, to be in this category of addressing, must be in User mode, and relocation must be enabled (RDIS is false). The addresses presented by the XVM CPU have the contents of another register added to them, so that the correct partition\* is accessed. The Relocation register (RR00-RR09) holds the equivalent of an "offset," which is used to map the virtual address to the user's area of core.

Figure 1-11 Direct Mapping (DMAP)

Figure 1-12 Relocated Mapping (RMAP)

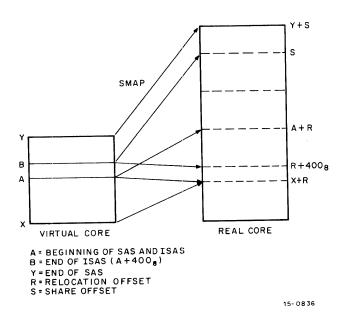

#### Shared Mapping (SMAP)

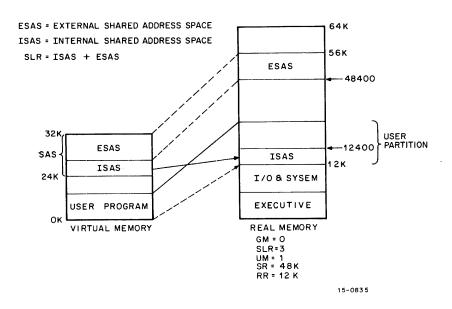

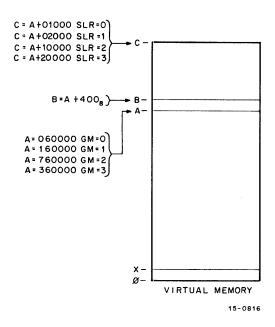

Refer to Figure 1-13. This particular form of address manipulation is the most complex of the XVM addressing schemes. When the system is in User mode and Share mode, the virtual addresses issued by the XVM CPU are examined by the MPU to determine if they lie within the Shared Address Space (SAS). The SAS is defined by two limits; the starting address of the SAS is a function of the G-Mode bits, and the length of the SAS is held by the Segment Length register (SLR). If the CPU address is within the SAS, and furthermore if it is within the first 400<sub>8</sub> locations, then the CPU is referencing the Internal Shared Address Space (ISAS). The address (bits 10-17) is combined with the contents of the Relocation register (RR00-09) and the result is sent to the memory. The location accessed will be within the first 400<sub>8</sub> locations of the user's partition.

<sup>\*&</sup>quot;Partition" refers to the area of real memory that has been assigned to that particular program.

Figure 1-13 Shared Mapping (SMAP)

Refer to Figure 1-14. If the XVM CPU address happens to be within the limits of the SAS, but not within the first 400<sub>8</sub> locations thereof, then the CPU is said to be accessing ESAS (the External Shared Address Space); to reach this area, the CPU address (bits 05-17) is added to the contents of the Share register (SR00-09), which holds another "offset" similar to the Relocation register. The sum of these is then sent to memory.

Figure 1-14 External Shared Address Space (ESAS) Example

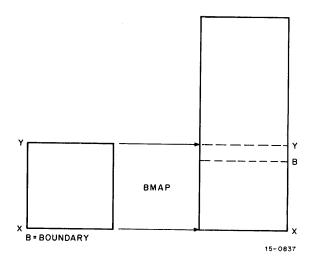

Boundary Mapping (BMAP)

Refer to Figure 1-15. To use the facilities of this separate, special type of mapping, the XVM CPU and MPU must be configured as a "P-Mode" system. The previous two methods of address modification, RMAP and SMAP operate only while the system is configured as an "R-Mode" system.

Figure 1-15 Boundary Mapping (BMAP)

The XVM system, when in BMAP, establishes a boundary in real core below which access is prohibited. This type of mapping is normally used in specialized applications.

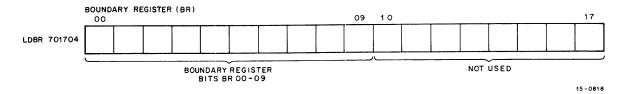

There is another register that is used by the RMAP, BMAP, and SMAP categories, called the Boundary register (BR00-09). It specifies the virtual address that is considered to be the upper limit of the user's partition or the lower limit of the user's allowable memory area in BMAP operation. If an attempt is made to map a virtual address to a real address beyond the zone established by the Boundary value, the XVM CPU will TRAP, because of the boundary violation. The TRAP is an alarm condition which informs the CPU that a violation of some kind exists and must be rectified.

#### 1.2.3 Addressing Examples

Programming examples for each type of addressing (Type I through Type VI) are provided in the following paragraphs. In these examples, it is assumed that the MPU does not modify the address received from the XVM CPU.

Short program examples are also provided to illustrate the effects of the MPU in different address mapping modes.

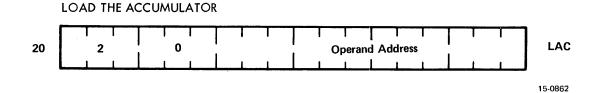

#### Direct Addressing, Type I – Bank or Page Mode

The XVM uses bits 5 through 17 in Bank mode, or bits 6 through 17 in Page mode, as the effective address (EFA) for direct addressing.

The following example illustrates direct addressing:

| PC     | Instruction |             |

|--------|-------------|-------------|

| 000100 | 202222      | (LAC 02222) |

In the example, the instruction fetched from location 000100 specifies "load the AC with the contents of location 2222." Direct addressing is indicated, and the EFA is 002222.

Indirect Addressing, Type II - Bank or Page Mode

Indirect addressing is specified when bit 4 of a memory reference instruction is set. Some of the frequent uses of indirect addressing include building or retrieving blocks of data in core memory and referencing memory locations outside of the page or bank containing the program.

The following examples illustrate indirect addressing (\* Specifies indirect addressing):

| PC     | Instruction |              |

|--------|-------------|--------------|

| 000200 | 221111      | (LAC* 01111) |

The instruction fetched from location 000200 specifies "load the AC with the contents of the memory location specified by the contents of 01111 (located in page 0 of bank 0)." If location 01111 contained 000300, the EFA would be 000300, and the contents of 000300 would be loaded into the accumulator.

Indirect addressing enables the user to reference any memory locations in core, depending on the setting of the MPU. In the above example, memory location 300 can be referenced in any memory page by specifying the page in address bits 3,4, and 5:

| PC     | Instruction |             |

|--------|-------------|-------------|

| 000200 | 221111      | (LAC*01111) |

If location 01111 contains 070300, the contents of location 300 in page 1 of bank 3 are loaded into the accumulator.

# Auto-Increment Addressing, Type III - Bank or Page Mode

Whenever addresses 000010 through 000017 are indirectly referenced by an instruction, the content of the location is incremented by one before it is used as the operand. The auto-increment feature is performed only when the location is referenced indirectly. The locations act as any other memory location when referenced directly.

An auto-increment operation can be initiated from any page, bank, or block of memory. The XVM auto-increments whenever a memory reference instruction specifies indirect addressing, and the address points to any location from 000010 through 000017.

#### NOTE

#### The Auto-increment register is incremented before the content is used as the operand address.

#### Programming examples:

Auto-increment from page 0, bank 0, block 0, and read the data word stored in location 001000 into the accumulator.

| Step 1 | Set the Auto-increment register to the operand address value -1. In this case, 000777. |

|--------|----------------------------------------------------------------------------------------|

| Step 2 | Reference the Auto-increment register with indirect addressing specified.              |

Step 3 The Auto-increment register increments by one, and the EFA is now the new value (001000) in the register.

Steps 1, 2 and 3 are represented in assembly language form as:

| Step 1 | {LAC<br>DAC<br>LAC* | K777<br>10<br>10 | /Auto-increment register 10<br>/C(001000) loaded into AC |

|--------|---------------------|------------------|----------------------------------------------------------|

|        | •                   |                  |                                                          |

|        | •                   |                  |                                                          |

|        | K777                | 000777           | /Constant for initialization                             |

When operating from a memory bank other than bank 0, the initial contents of the Auto-increment register must be set up using indirect addressing. If direct addressing is used, locations 10 through 17 of the bank containing the program are referenced. For example, if operating in bank 2, Step 1 in the previous example must be modified as:

| Step 1    | LAC<br>DAC* | K777<br>K10      | /Deposit in location 10 of 1                                               |

|-----------|-------------|------------------|----------------------------------------------------------------------------|

| Step 2, 3 | LAC*        | 10               | /page 0, bank 0<br>/C(001000) loaded into AC                               |

|           | K777<br>K10 | 000777<br>000010 | /These constants are located /in the same memory bank as /the main program |

#### Indexed Addressing, Type IV - Page Mode Only

The XVM Central Processor has an 18-bit Index register (17 bits + sign) and an 18-bit Program Counter with appropriate data paths and adder circuitry to compute 17-bit effective addresses.

Indexed addressing can only be used in Page mode operation and is indicated when bit 5 of a memory reference instruction is set. With this type of addressing, the user gains access to 131,071 memory locations (000000 through 377777 octal) without adding an additional memory cycle to compute the effective address (as does indirect addressing).

The following example illustrates indexed addressing:

The instruction fetched from location 3000 specifies "load the AC with the content of the effective address calculated by adding PC01-05 (00), the XR (100) and the address field of the instruction (100)." This results in an effective address of 000200 because:

000100 (XR)

$$+000100$$

(PC<sub>1-5</sub>) + (ADDR)

000200 (EFA)

If operating in an extended memory bank or block, indexed addressing can be used to reference other pages, banks, or blocks above or below the operating area.

#### Programming example:

The program is operating in block 2, bank 0, page 1 and must reference location 1000 in block 3, bank 3, page 1 (location 371000):

The EFA is calculated in the following manner:

160000 (XR)

$$+211000$$

(PC<sub>1-5</sub>) + (ADDR)

EFA=371000 (block 3, bank 3, page 1, location 1000)

The program is operating in block 2, bank 0, page 1, and must reference location 1000 in block 0, bank 0, page 0 (location 001000):

The EFA is calculated by:

570000 (XR)

$$+211000$$

(PC<sub>1-5</sub>) + (ADDR)

EFA=001000 (block 0, bank 0, page 0, location 1000)

#### **NOTE**

The XR contains a negative value. In this case, it is the 2's complement value of the current block, bank, and page. All 18 bits (17 bits + sign) of the XR are involved when using indexed addressing. The EFA of the last example can also be calculated in the following manner:

PC=213000 LAC 200,X /(210200 octal)

$$XR = 570600$$

(XR)

$\frac{+210200}{001000}$  (PC<sub>1-5</sub>) + (ADDR)

EFA

#### Indirect Indexed Addressing, Type V - Page Mode Only

Indirect indexed addressing is implemented only in Page mode and is indicated when both the indirect addressing indicator (bit 4) and the indexed address indicator (bit 5) of a memory reference instruction are set.

When indirect indexed addressing is indicated, the XVM CPU first calculates the address indirectly referenced. This calculation is done in exactly the same manner as described in the Indirect Addressing paragraph. The XVM carries the address calculation one step further, when indirect indexing is specified. The contents of the Index register are added to the data word which was retrieved indirectly.

The addition (2's complement) of the XR is always the last step to occur (post indexing).

The following example illustrates indirect indexed addressing:

100,X

/(070100 octal)

XR = 000100

location 200100=007000

The EFA is calculated as:

(contents of location 200100)

(XR)

007100

**EFA**

The instruction fetched from memory location 203000 specifies "deposit the contents of the accumulator into the memory location calculated by retrieving the contents of memory location 200100 (location 100 of the current block, bank, and page) and add the contents of the Index register to the contents of memory location 200100."

The indirect address pointer is calculated by appending bits 1 through 5 of the PC to the 12-bit address (6 through 17) of the instruction word resulting in a 200100 address pointer. An additional memory cycle is required to retrieve the contents (007000) of memory location 200100. The contents of the XR are then added, resulting in a final EFA of 007100.

## Auto-Increment Indexed Addressing, Type VI - Page Mode Only

Auto-increment indexed addressing can be implemented only when operating in Page mode. This type of addressing is specified when the indirect address indicator (bit 4) and the indexed address indicator (bit 5) of the memory reference instruction are both set and address bits 6 through 17 equal a value of 10 through 17 octal.

When this type of addressing is specified, the XVM CPU performs the following steps to calculate the EFA:

- 1. The contents of the Auto-increment register are retrieved, incremented by one, and then restored in the register.

- 2. The new contents of the Auto-increment register are used as an address pointer.

- 3. The contents of the XR bits 0 through 17 are added (2's complement) to the address pointer.

- 4. The sum is used as the final, or effective address (EFA).

The following example illustrates this type of addressing:

Following the procedure given above, the EFA is calculated as:

$$\begin{array}{c|c}

000777 & contents of location 15 \\

+ 1 & increment \\

\hline

001000 & new contents of location 15 \\

used as address pointer

\end{array}$$

$$\begin{array}{c|c}

+001000 & contents of XR & Step 3 \\

\hline

002000 & EFA & Step 4

\end{array}$$

All of the foregoing assumes that the MPU does not modify the address received from the XVM CPU. A small program is used to illustrate the effects of the MPU in different address mapping modes.

| 500 | BEGIN | LAC<br>DAC<br>LAC<br>DAC* | FADD<br>ILOC<br>K<br>ILOC | Relocation Register = 000000<br>Boundary Register = 000000<br>Share Register = 000000<br>User Mode* Share Mode* |

|-----|-------|---------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------|

|     |       | ISZ.                      | ILOC                      |                                                                                                                 |

|     |       | JMP<br>HLT                | 2                         | G-Mode = 0                                                                                                      |

| •   | FADD  | 000600                    |                           |                                                                                                                 |

| •   |       |                           |                           |                                                                                                                 |

| _   | ILOC  | 000000                    |                           |                                                                                                                 |

| 511 | K     | 252525                    |                           |                                                                                                                 |

### Direct Mapping (DMAP)

In DMAP, the constant K is deposited first in location  $600_8$ , and then every succeeding location until the system runs out of memory. When the program attempts to access the last location +1, the system will TRAP to location  $20_8$  absolute, or  $0_8$  if Program Interrupt Enable is on. A pointer, in one or both of these locations, should point to a service routine to handle the "alarm" type conditions.

# Relocated Mapping (RMAP)

```

Relocation Register = 007400

Boundary Register = 020400

Share Register = 000000

User Mode = 1 RDIS = 0

Share Mode = 0

G-Mode = 0

```

In RMAP, the first real address to have the constant deposited in it would be 010200 (FADD + RR). The system will then continue depositing the constant in sequential locations until it attempts to access location 020400 (virtual), at which point the system will be interrupted by the Boundary Violation which causes a TRAP to 0 or  $20_8$ .

#### Shared Mapping (SMAP)

| Boundary Register = 0170400 | User Mode = 1<br>Share Mode = 1<br>RDIS = 0 |

|-----------------------------|---------------------------------------------|

| Share Register = 340000     |                                             |

| G-Mode = 3                  | SLR = 2                                     |

In SMAP, the first address to be accessed would be 011200 (Figure 1-16). The system will then continue to deposit until the virtual address 160000 is produced. This will be changed to 010400 and the constant will be stored in the subsequent  $377_8$  locations. The address was changed because the address 160000 corresponds to the first address of the ISAS. The next significant address will be 160400 which is the first address in ESAS. The address will be modified from 760400 to 340400. This will continue until the end of ESAS is reached by address 167777 (virtual) which is 347777 (real). The next location (170000 virtual) will be relocated to 200400 (real) which will cause a trap because it is above the Boundary register.

Figure 1-16 Shared Mapping Example

**Boundary Mapping (BMAP)**

The BMAP case is less complex than RMAP or SMAP. The program runs as it would normally in DMAP except all virtual addresses are checked to ensure that they are greater than the contents of the Boundary register. Therefore, if the Boundary register was set at 001400, then the contents of location FADD (000600) must be changed to 001400 or greater before the system will execute the program without trapping.

# 1.3 INPUT/OUTPUT PROCESSOR

#### SUMMARY OF CHARACTERISTICS

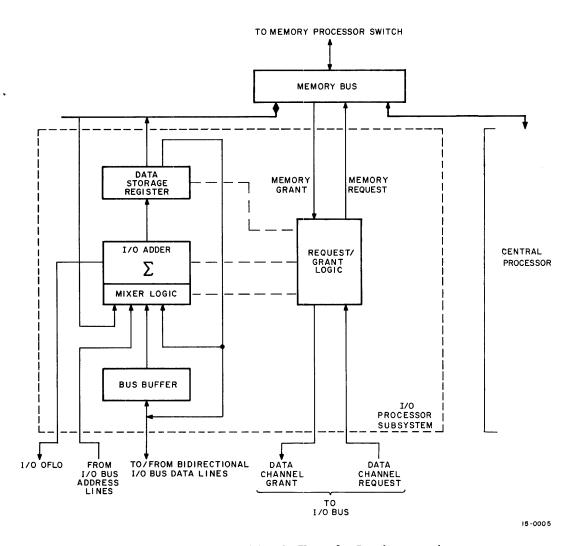

The I/O processor contains two subunits, the data channel controller and the addressable I/O bus.

#### **Data Channel Controller**

Data Transfer Modes - Single and multicycle block transfer, memory-increment, add-to-memory Real-Time Clock - KW15

#### Addressable I/O Bus

Features - Two-cycle skip line, program interrupt, console terminal interface

Data Transfer Modes - Program-controlled data transfers

Device Ports - A maximum of 50 physical ports shared between the data channels and the addressable

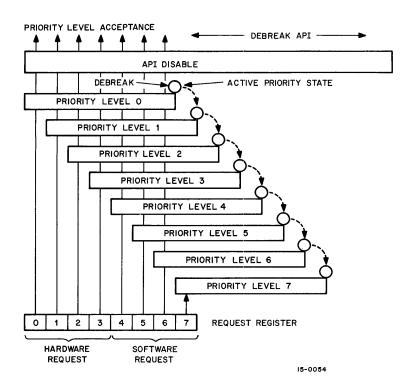

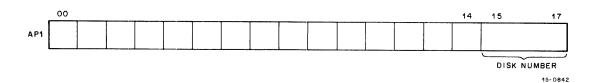

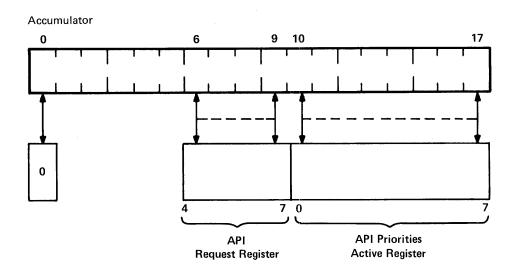

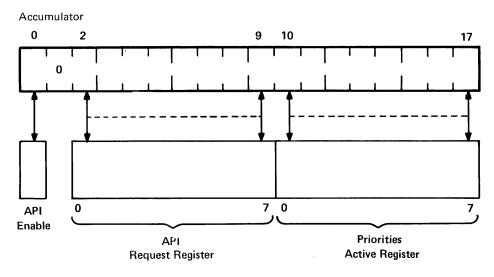

API - Eight levels of automatic priority interrupts - Four hardware levels and four software levels

#### I/O PROCESSOR

The I/O processor contains the control logic and registers necessary to transfer up to 18 bits of parallel data on a common bidirectional I/O bus. Data may be transferred directly between the I/O processor and memory, or between the I/O processor and the accumulator (AC) of the CPU. All transfers are made on a request/grant basis, providing complete autonomy of processors and memory. The I/O processor operates with a 1 µs nominal cycle time.

While transfers are being made between memory and the I/O processor, the CPU is free to operate independently. Requests from the I/O processor for memory access are, however, given priority over CPU requests by the memory bus switch; this can cause the CPU an occasional "cycle-stealing" delay. The structure of the I/O processor provides the following benefits to the user:

Simultaneous data transfers and CPU computing permits high speed processing to meet the demands of real-time applications.

- User-designed or special-purpose equipment can be easily and inexpensively interfaced to the system.

- Synchronous and asynchronous devices can be handled with equal ease.

- Direct memory access devices that would otherwise require additional interface logic require only one interface with the XVM single cycle data channel.

#### **Modes of Data Transfer**

Peripheral devices may transfer data in any one of three modes: single cycle block transfers, multicycle block transfers, and program-controlled transfers.

#### **Block Transfer Controller**

The block transfer controller implements the first two modes of data transfers, and in addition, has an add-to-memory mode and an increment memory mode. The real-time clock is also implemented in this section.

#### **Multicycle Block Transfers**

A 2-word packet in core memory is reserved for each of these channels: locations 22 and 23 for the first, 24 and 25 for the second, 26 and 27 for the third, and 30 and 31 for the fourth and so on in standard software systems. The two words in the packet are used to store the "word count" (WC) (number of words to be transferred in the block), and the "current address" (CA) (where the data is to be transferred). The I/O processor contains the control logic and an adder to automatically fetch, increment, and replace the contents of the two locations.

Data is read into memory and out from memory in three I/O processor cycles. Maximum input rate is 170,000 words/second and maximum output rate is 130,000 words/second.

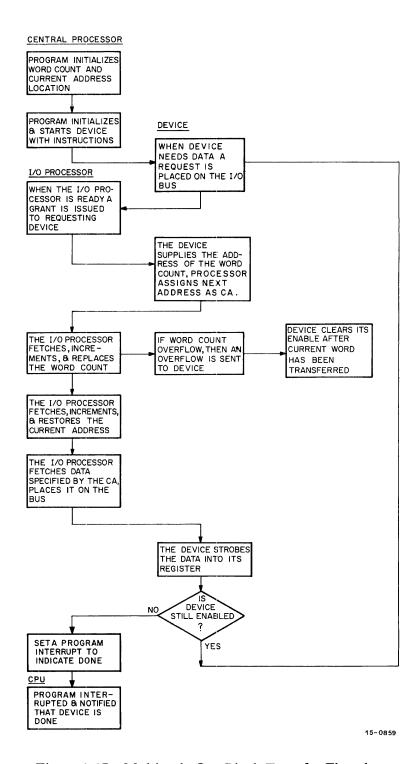

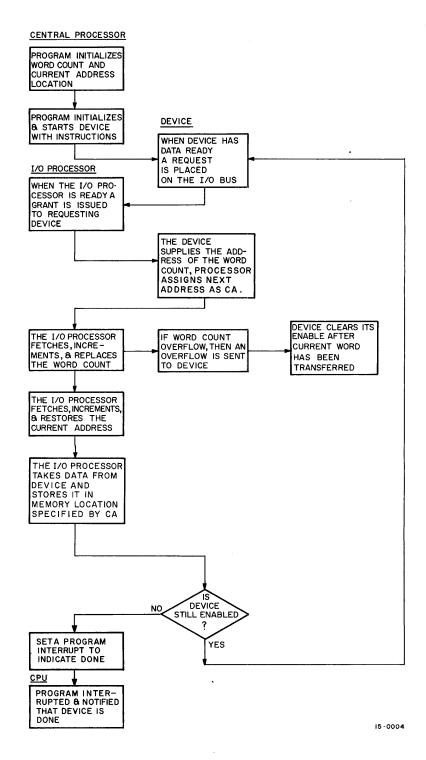

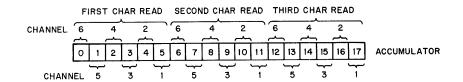

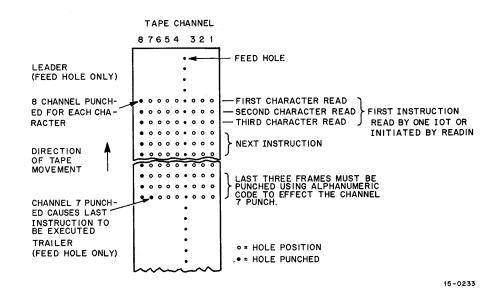

Prior to initiating a multicycle block transfer (flowcharted in Figures 1-17 and 1-18), the program stores the 2's complement of the word count and the current address minus one in the two appropriate memory locations. The transfer is then initiated by an IOT instruction. During the first cycle, the contents of the Word Count location are incremented by one and restored. During the second cycle, the current address is incremented by one and restored, in addition to being transferred to the memory. During the third cycle, the actual data transfer occurs.

The I/O processor continues to transfer data sequentially until the Word Count register reaches 0, at which time an interrupt is generated to notify the monitor that the block transfer is complete. Because these multicycle block transfers are completely automatic and do not require any CPU attention except for I/O transfer initialization, the CPU is free to compute while they are taking place. The only limitation on simultaneity lies in the sharing of memory. The I/O processor has first priority on memory requests and effectively "locks out" the CPU for three cycles. As data transfer rates approach maximum, the CPU can be completely locked out.

Figure 1-19 illustrates how the data channel controller registers implement the multicycle transfers.

Figure 1-17 Multicycle Out Block Transfer Flowchart

Figure 1-18 Multicycle Transfer Implementaion

Figure 1-19 Multicycle Transfer Implementation

Assume the 2-word core memory packets assigned to a given multicycle data channel have been loaded by the respective I/O service routine. For the case of data input to memory, the following occurs:

- 1. An instruction from the service routine enables the device controller. This allows the controller to request a data transfer from the I/O processor.

- 2. When the device controller's data buffer registers are full, it issues a "data channel request."

- 3. The I/O processor, if not busy, acknowledges the request by returning a "data channel grant."

- 4. The device controller then generates a fixed code pointing to its packet address in core memory. This is transmitted over the common I/O bus address lines and is stored in the Data Storage register of the data channel controller through the I/O adder. The adder is inhibited during this operation.

- 5. The I/O processor then generates a "memory cycle request."

- 6. The address data on the I/O bus address lines points to the word count, the first word of the packet. This data is brought out of memory and into the data channel controller's adder. The word count data word is incremented by one and stored back into memory. If, during this incrementing, the adder overflows (indicating that the current address is the last), then an I/O overflow pulse is transmitted back to the device to disable future data channel requests from the line and also to post an interrupt to the monitor, when the DCH transfer is completed.

This "word count" operation occurs in one I/O processor cycle, using one memory cycle.

During the second I/O processor cycle, the fixed address from the device controller is gated through the adder and is incremented by 1. It points to the second word in the packet, the "current address," which is then transmitted back to the adder, incremented by 1, and strobed back to memory.

During the third I/O processor cycle, the contents of the "current address" location is strobed to the memory to point to the data array word where the I/O data will be transferred. The data is then gated from the device controller, through the adder (which is inhibited during this cycle), and into memory.

Data output follows the same sequence (Figure 1-19) with the exception that one additional I/O processor cycle is required to allow the bus to settle after data is strobed out of memory and into the device.

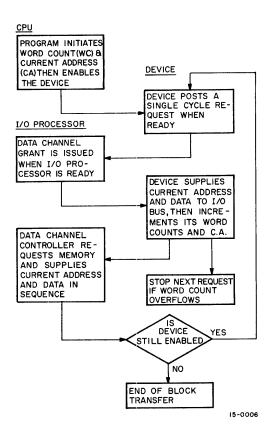

#### Single Cycle Block Transfers

Single cycle block transfers, flowcharted in Figure 1-20, are used by high-speed peripherals that normally transfer complete records (blocks) of information, such as disks and video devices. A single cycle of the I/O processor takes approximately 1  $\mu$ s, allowing a maximum transfer rate of up to one million 18-bit words per second.

High-speed hardware registers, designed into the device controllers of the high-speed peripherals, store the "current address" (the memory cell where data is currently being transferred), and the "word count" (the number of words remaining to be transferred in a block). These registers are loaded by input/output transfer (IOT) instructions issued by the CPU. Device testing and initialization are handled by the CPU via IOTs to provide supervisory control. A subsequent IOT initiates the data transfer. The I/O processor uses the current address information to address core memory, then strobes the data between memory and the device controller. Logic within the device controller then increments the Current Address register and the Word Count register to provide sequential block transfer.

Figure 1-20 Single Cycle Block Transfer Flowchart

When the Word Count register overflows at the end of a block transfer, an interrupt is generated to allow the monitor system to take further action. Typically, this action will include deselecting the device from the I/O bus or reloading the device controller registers for another block transfer. The maximum number of words that may be transferred in a single block is determined by memory size and device capacity.

Figure 1-20 illustrates how the data channel controller registers handle single cycle transfers.

Assuming that the program has initiated the word count and current address of the device controller, and has then enabled it, the following occurs:

- 1. The device controller sends a single cycle data channel request to the I/O processor.

- 2. The I/O processor, as soon as it becomes available, acknowledges the request by returning a "data channel grant" signal.

- 3. The device then strobes both its current address and its data onto the I/O bus to the I/O processor.

- 4. The data channel controller feeds the current address through its adder (which is inhibited throughout the single cycles) to the Data Storage register. A memory cycle is requested, and this address is strobed into a memory bank's address buffer. The data is then strobed off the 18 I/O data lines and into the memory location specified by the current address.

5. During this operation, the device increments its own word count, and disables itself on overflow. It then posts an interrupt to the monitor to indicate that its operation has been completed.

#### **Burst Mode**

The usual method of data transfer is one word per data channel request, whether it is single cycle or multicycle; however, there is one special case.

If the data channel request signal should remain true at the end of the first word (i.e., the device holds it so), then the data channel controller will go into Burst mode (also known as Back-to-Back).

Once in this mode, the CPU is held "locked-out" until the device drops the data channel request signal, and the I/O transfer is completed. This mode will transfer one 18-bit word approximately every microsecond. This mode is only used by certain devices that can handle the 1 MHz rate.

## **Increment Memory**

The Increment Memory mode allows an external device to add one to the contents of any memory location in a single cycle; this feature is most commonly employed in the accumulation of data in histogram form. Effectively, the Increment Memory mode simply goes through the word count cycle of a multicycle channel transfer, and then stops. The maximum rate at which it can increment is 333 kHz. This feature is particularly useful for in-core scaling and counting in pulse height analysis.

#### Add-to-Memory

Add-to-memory is a standard feature of the XVM that adds unique capabilities to the already powerful I/O facilities. In Add-to-Memory mode, the contents of an external register can be added to the contents of a memory location in four cycles. This feature is extremely valuable in signal averaging and other processes requiring successive sweeps for signal enhancement.

The add-to-memory operation is a combination of multicycle data channel input and multicycle data channel output operations. The data transmitted by the device is added to a word read-out of memory as specified by the current address, and the result is rewritten into the same location. It is simultaneously transmitted to the device via the I/O bus. The maximum add-to-memory rate is 130 kHz.

#### **KW15 Real-Time Clock**

When enabled, the KW15 Real-Time Clock counts, in memory location 00007, the number of cycles completed by the line voltage (50 or 60 Hz) or any standard DEC clock module that may be optionally installed. Maximum recommended clock frequency is 10 kHz.

When location 00007 overflows, an internal program interrupt (or API request, if available) is generated, informing the monitor that its preset interval is over. The monitor must either disable the clock or reinitialize location 00007 to the 2's complement of the number of counts it needs to tally.

The incrementing of location 00007 during a real-time clock request occurs via the I/O processor's increment memory facility. A real-time clock request takes priority over API, PI, and IOT requests, but not over block transfers (DCH).

## ADDRESSABLE I/O BUS

The addressable I/O bus implements the program-controlled transfers. It also contains the program interrupt and the automatic priority interrupt (API) feature.

#### **Program-Controlled Transfer**

Program-controlled transfers, implemented by input/output transfer (IOT) instructions, can move up to 18 bits of data between a selected device and the accumulator (AC) in the CPU. The devices involved are connected to the addressable I/O bus portion of the I/O processor. A total of up to 50 device controllers may be attached to this bus and to the data channel. IOT instructions are microcoded to effect response only for a particular device. The microcoding includes issuing both a unique device selection code and the appropriate processor-generated input/output pulses to initiate a specific operation. For an "output" transfer, the program reads a data word from memory into the AC. A subsequent IOT instruction places the data on the bus, selects the device, and transfers the data to the device. For an "input" transfer, the process is reversed; an IOT instruction selects the device and transfers data into the AC. A subsequent instruction in the program transfers the word from the AC to memory. Maximum transfer rate in this mode is about 50 kHz.

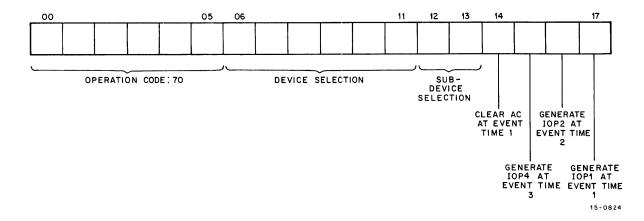

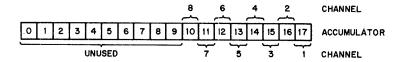

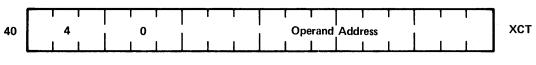

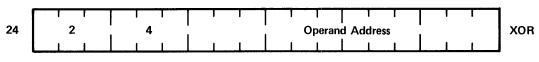

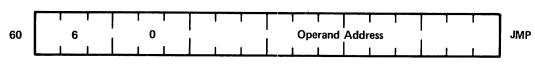

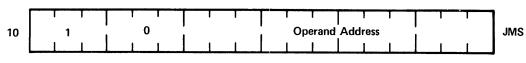

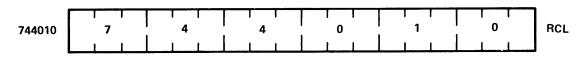

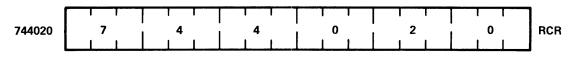

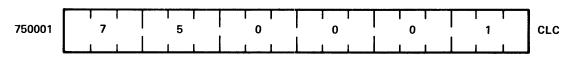

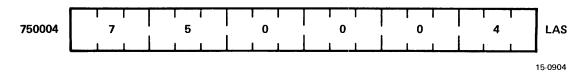

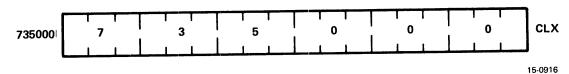

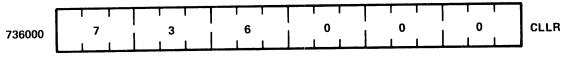

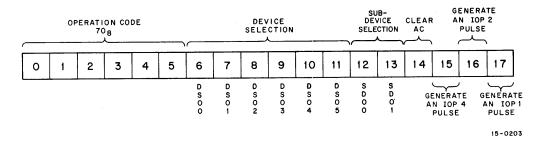

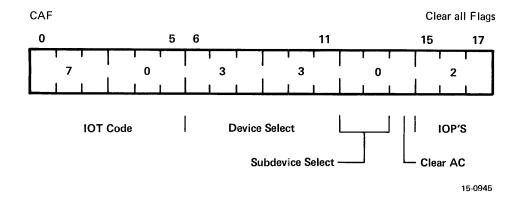

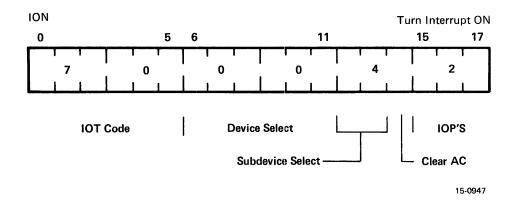

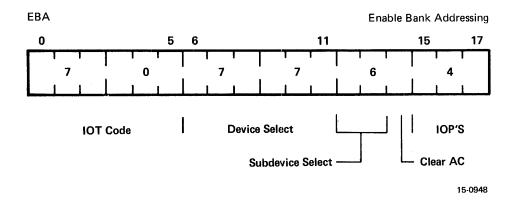

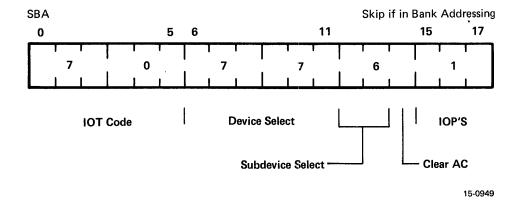

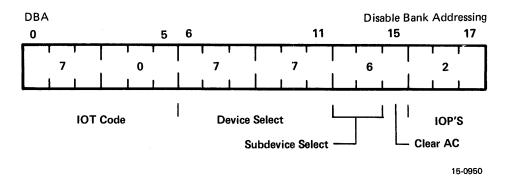

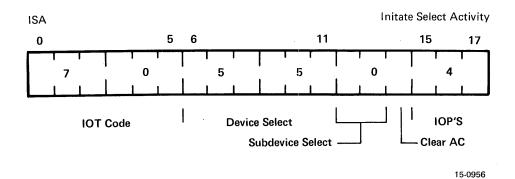

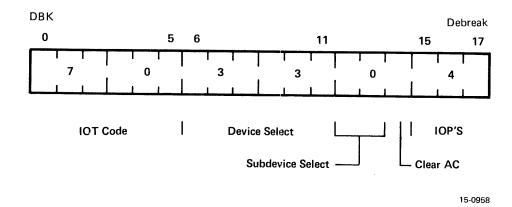

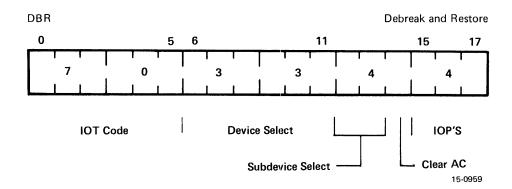

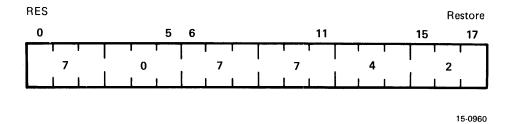

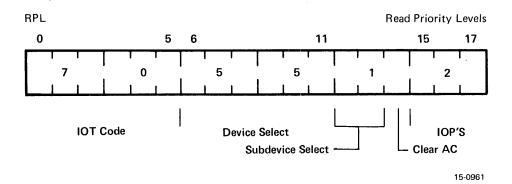

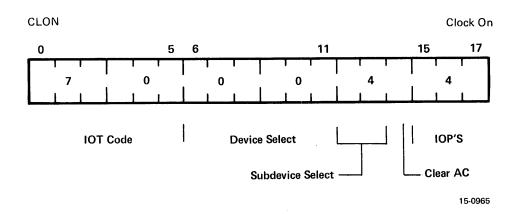

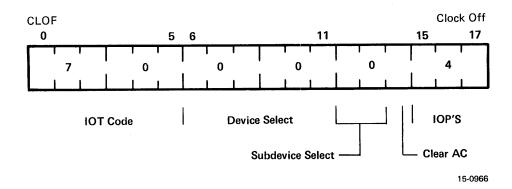

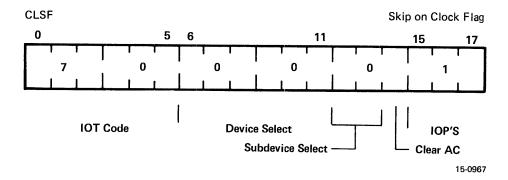

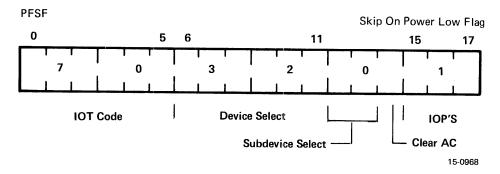

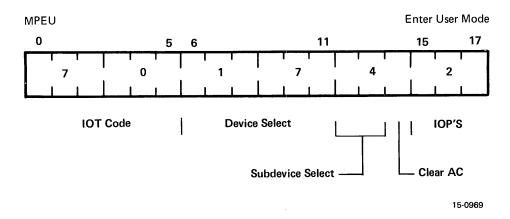

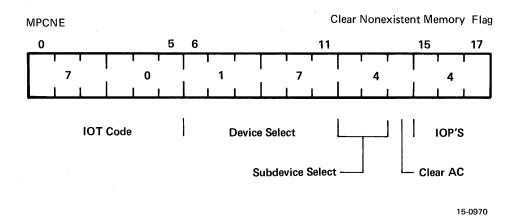

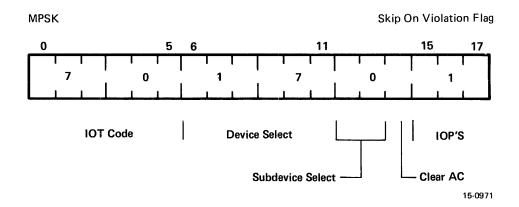

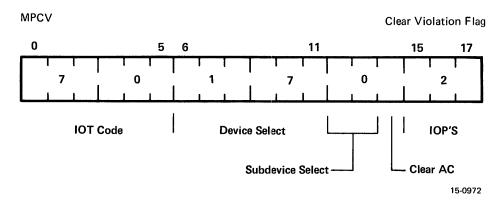

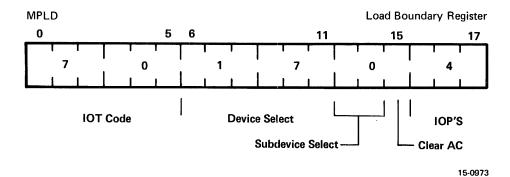

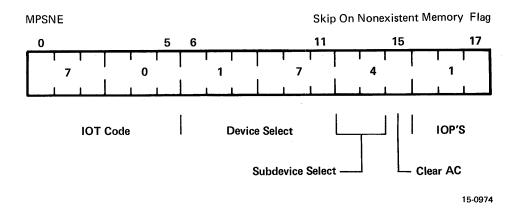

IOT instructions are also used to initialize the single and multicycle channels and the transfer word count and current address information to the single cycle device controllers. In addition, these instructions are used to test or clear device flags, select modes of device operation, and control a number of processor operations. An IOT instruction, Figure 1-21, contains the following information:

- a. An operation code of 70<sub>8</sub>.

- b. An 8-bit device selection code to discriminate between up to 256 user peripheral devices (selection logic in a device's I/O bus interface responds only to its pre-assigned code). In normal practice, bits 6 through 11 perform the primary device selection between up to 64 device codes. Bits 12 and 13 are coded to select an operational mode or subdevice.

- c. A command code (bits 14 through 17) capable of being microprogrammed to clear the AC and issue up to three pulses via the I/O bus.

Figure 1-21 IOT Instruction Format

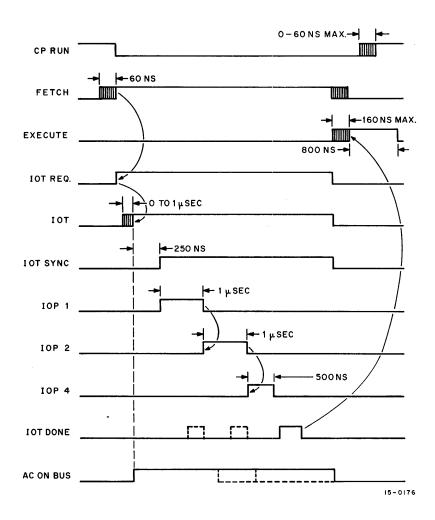

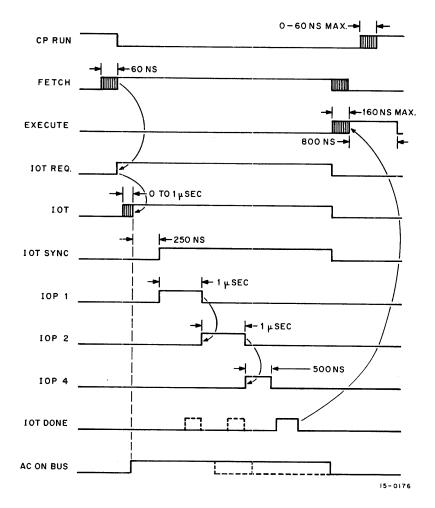

Up to four machine cycles may be required to execute an IOT instruction. These include the IOT fetch from core memory (memory is not accessed thereafter until completion of the IOT), and three sequential cycles designated event times 1, 2, 3 (IOP 1, 2, and 4) (Figure 1-22). In IOT skip instructions, however, only IOP1 is used. These are 2-cycle instructions. Bits 14 and 17 can be coded to initiate clearing of the AC and generation of an IOP1, respectively, during event time 1. Bits 16 and 15 can be coded to initiate generation of an IOP2 and IOP4 pulse during event times 2 and 3, respectively. IOT skip instructions are microprogrammed to produce an IOP1 pulse for testing a device status flag. IOP2 pulses are normally used to effect programmed transfers of information from a device to the processor. Because the AC serves as the Data register for both "input" and "output" transfers, the "clear AC" microinstruction (bit 14) is usually microprogrammed with the IOP2 microinstruction; this combination effects clearing the AC during event time 1. IOP4 pulses are normally used to effect programmed transfers of information from the AC to a selected device. These conventions do not, however, preclude use of the IOP pulses to effect other external functions if the following restrictions are observed.

Figure 1-22 IOT Instruction Timing

The uses of IOPs are:

IOP1 - Only used in an I/O skip instruction to test a device flag.

IOP2 – Usually used to transfer data from the device to the computer, or to clear device's Information register. May not be used to determine a "skip" condition.

IOP4 – Used only to transfer data from the computer to the device. May not be used to determine a "skip" condition or to transfer data to the computer.

## PROGRAM INTERRUPT FACILITY

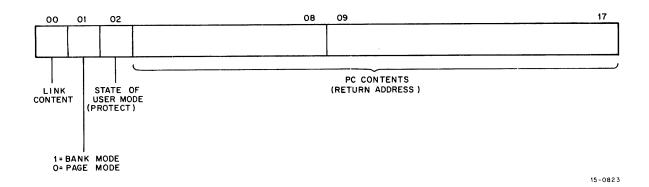

The program interrupt (PI) system, standard on all systems, provides for servicing a peripheral device at rates up to 20 kHz. The program interrupt (PI) facility, when enabled, relieves the main program of the need for repeated flag checks by allowing the status of I/O device flags to automatically cause a program interrupt. The CPU can continue with execution of a program until a previously selected device signals that it is ready to transfer data. At that time, the program in progress is interrupted and automatically the contents of the program counter (15 bits), User/Exec mode (1 bit), bank or page addressing mode, and the link bit (1 bit) is stored in location 000000 (Figure 1-23).

Figure 1-23 Memory Location Just After a Program Interrupt

The instruction in location 000001 is then executed, transferring control to an I/O service routine for IOT instructions. When completed, the routine restores the system to the status prior to the interrupt with a single instruction, allowing the interrupted program segment to continue. Where multiple peripherals are connected to the PI, a search routine containing device status testing (skipping) instructions must be added to determine which device initiated the interrupt request. The program interrupt (PI) control is enabled or disabled by programmed instructions (IOTs). When disabled, the PI ignores all service requests, but such requests normally remain on-line and are answered when the PI is enabled again, unless they are cleared.

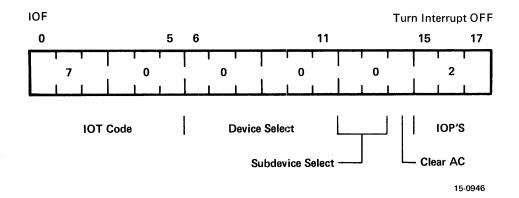

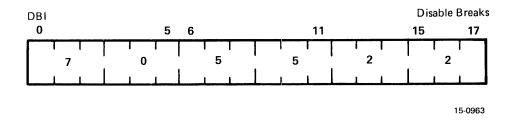

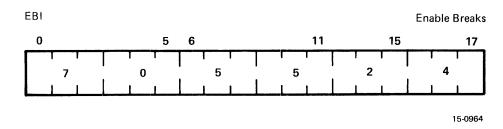

| Mnemonic | Octal  | Code Function  |

|----------|--------|----------------|

| ION      | 700042 | Enable the PI  |

| IOF      | 700002 | Disable the PI |

The PI is automatically disabled when an interrupt is granted or when the RESET key (on the console) is pressed. The PI is temporarily inhibited while the automatic priority interrupt system is processing a priority interrupt request. The PI Enable indicator (PIE on the console) is lighted while the PI is enabled.

#### Free Instruction

When a program interrupt has been accepted, one "free instruction" follows. Simply, this means that program interrupt enable is turned off to prevent another program interrupt from occurring while the hardware is transferring control from one program to the interrupt service routine.

## **Conditional Skip-On Device Status**

The XVM order code includes a group of instructions for testing the status of peripherals. Instructions of this type direct the processor to skip the next instruction if the tested condition is true. This group of instructions allows the test of peripheral devices at the programmer's option. Normally, rather than tying the processor up in a "wait" loop, the device signals that its buffer is ready by generating an interrupt. If it is a program interrupt, the "conditional skip" is used in a "skip chain" to find which device initiated the interrupt. Each skip instruction takes an average of  $1.8 \mu s$ .

## **COMMON I/O BUS**

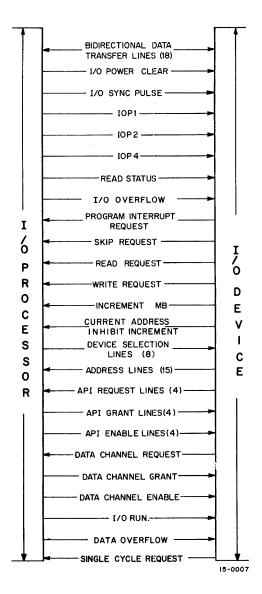

The I/O processor contains a common I/O bus (Figure 1-24) to transfer both data and IOT instructions to the block transfer channels and to the addressable I/O bus. The bus is the major communication path for I/O devices. It consists of cables that link all the I/O device controllers to a common interface point at the I/O processor. All signal lines for command and data transmission arising from the data channels, addressable I/O bus, operation of the multi-level automatic priority interrupt system, program interrupt, I/O status read, and I/O skip facilities, are contained on this bus. The bus length can be up to 75 ft.

#### **Data Lines**

Eighteen data lines constitute the bidirectional facility for transferring data bytes of up to 18 bits between the I/O processor and all I/O devices. Transfers are made on a dc basis with the processor or device allowing bus settling time before data on the lines is strobed into the receiving register. The data lines convey data between the Memory Buffer register and a selected Device Buffer register for block transfer channel operation; they transfer data between the accumulator and a selected Device Buffer register for program-controlled transfers.

## **Output Control Signals**

Eight output control signals are generated to effect specific functions in a selected device.

#### I/O Power Clear

The I/O power clear signal resets all flip-flops storing device-to-processor flag indications (e.g., ready, done, busy). It is generated when power is turned on and off, the occurrence of a clear-all-I/O flags (CAF) instruction, and by actuation of the RESET key on the control console.

#### I/O Sync

I/O sync is used to synchronize I/O device control timing to the processor.

## IOP1, IOP2, IOP4

Microprogrammable signals are used to effect IOT instruction-specified operation within a selected I/O device. The I/O processor generates IOP2 or IOP4 for data channel input or output transfers. The uses of the IOPs are:

IOP1 – To test a device flag (in an I/O skip instruction). It may not be used as a command pulse or to initiate loading, reading from a Device Buffer register.

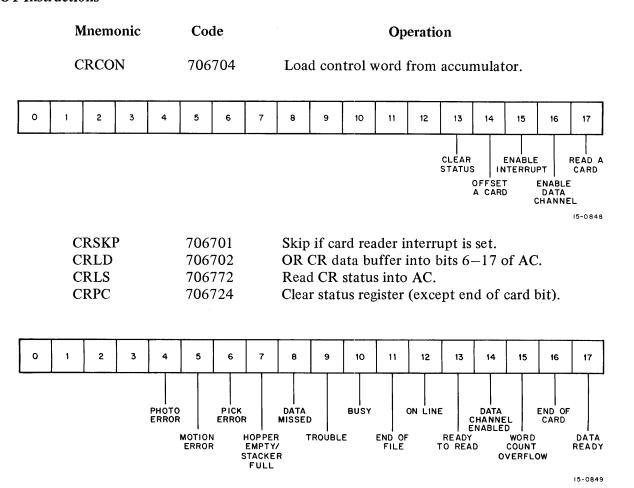

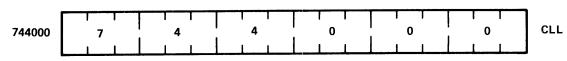

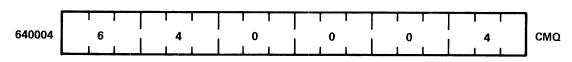

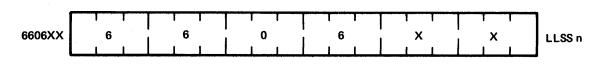

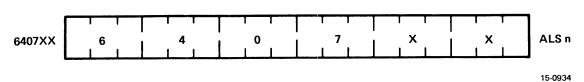

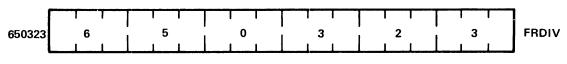

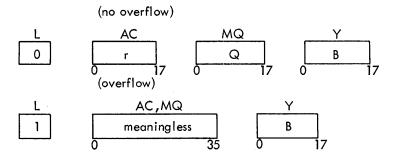

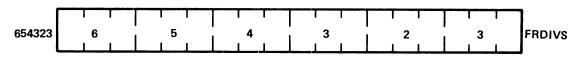

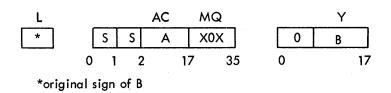

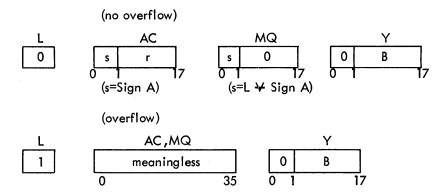

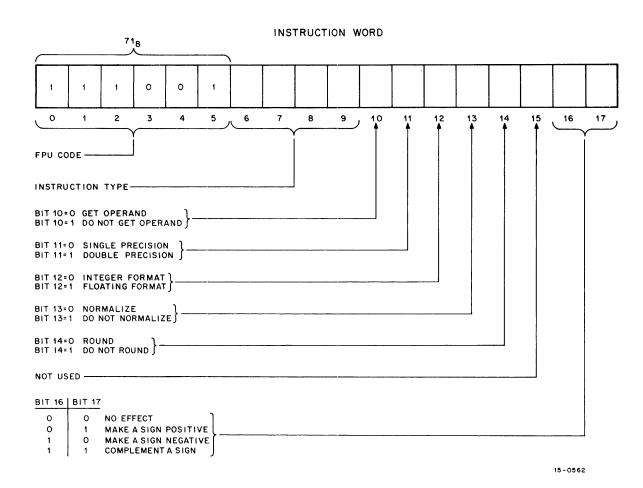

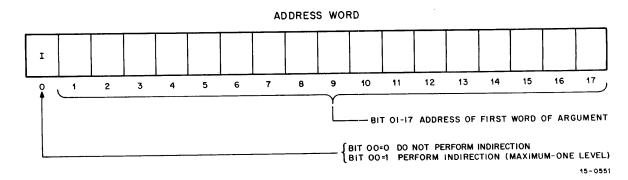

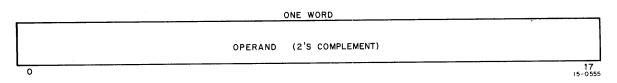

IOP2 - To transfer data from a selected device to the processor or load a device. Not used for skip.