# CIRCUIT INSTRUCTION MANUAL

PDP-6

# CIRCUIT INSTRUCTION MANUAL

COPY NO.

This manual contains proprietary information. It is provided to the customers of Digital Equipment Corporation to help them properly use and maintain DEC equipment. Revealing the contents to any person or organization for any other purpose is prohibited.

## CONTENTS

|              |                                     | Page |

|--------------|-------------------------------------|------|

| 1            | INTRODUCTION AND DESCRIPTION        | 1-1  |

| 1.1          | Introduction and Scope              | 1-1  |

| 1.2          | PDP-6 Modules                       | 1-1  |

| 1.3          | Pertinent Documents                 | 1-3  |

| 2            | INVERTERS AND GATES                 | 2-1  |

| 2.1          | Inverters                           | 2-1  |

| 2.2          | Gates                               | 2-2  |

| 2.2.1        | Diodes                              | 2-2  |

| 2.2.2        | Capacitor-Diode Gates               | 2-3  |

| 2.2.3        | Decoders                            | 2-4  |

| 2.3          | Majority Logic                      | 2-5  |

| 2.3.1        | 6132 Majority Gate                  | 2-5  |

| 2.3.2        | 6131 DC Adder                       | 2-6  |

| 3            | FLIP-FLOPS                          | 3-1  |

| 3.1          | Operation of Component Circuits     | 3-1  |

| 3.1.1        | Unbuffered Flip-Flop                | 3-2  |

| 3.1.2        | NPN Emitter Follower                | 3-3  |

| 3.1.3        | Flip-Flop with Output Buffers       | 3-3  |

| 3.1.4        | Pulse Amplifier                     | 3-5  |

| 3.2          | 1250 Fast Memory Flip-Flop          | 3-6  |

| 3.3          | 1260 Subroutine Card                | 3-6  |

| 3.4          | 4214 Quadruple Flip-Flop            | 3-7  |

| 3.5          | 4217 Four-Bit Counter               | 3-7  |

| 3.6          | 4218 Quadruple Flip-Flop            | 3-7  |

| 3.7          | 4220 Eight-Bit Buffer               | 3-8  |

| 3 <b>.</b> 8 | 4221 Six-Bit Shift Register         | 3-8  |

| 3.9          | 4225 Eight-Bit Counter              | 3-9  |

| 3.10         | 4706 Eight-Bit Teletype Receiver    | 3-9  |

| 3.11         | 4707 Eight-Bit Teletype Transmitter | 3-11 |

| 3.12         | 6203 SC and FE Flip-Flops           | 3-12 |

| 3.13         | 6205 Arithmetic Register Flip-Flops | 3-13 |

## CONTENTS (continued)

|             |                                | Page         |

|-------------|--------------------------------|--------------|

| 3.14        | 6206 MA, PC, and IR Flip-Flops | 3-14         |

| 3.15        | 6227 Eight-Bit Buffer          | 3-14         |

| 4           | AMPLIFIERS                     | 4-1          |

| 4.1         | Basic Pulse Amplifier          | 4-1          |

| 4.2         | 1607 Pulse Amplifier           | 4-2          |

| 4.3         | 1608 Pulse Amplifier           | 4-3          |

| 4.4         | 1609 Pulse Amplifier           | 4-3          |

| <b>4.</b> 5 | 1664 Memory Bus Control        | 4-4          |

| 4.6         | 1665 Pulsed Bus Transceiver    | 4-5          |

| 4.7         | 4606 Pulse Amplifier           | 4-6          |

| 4.8         | 6603 Pulse Amplifier           | 4-7          |

| 4.9         | 6609 Pulse Amplifier           | 4-8          |

| 4.10        | 6615 Arithmetic Bus Driver     | 4-8          |

| 4.11        | 1669 Indicator Driver          | 4-8          |

| 4.12        | 1684 Bus Driver                | 4-9          |

| 4.13        | 4658 I/O Bus Transceiver       | 4-9          |

| 4.14        | 4681 Solenoid Driver           | 4-10         |

| 4.15        | 6684 Bus Driver                | 4-11         |

| 5           | DELAYS                         | 5-1          |

| 5.1         | 1304 Delay                     | 5-1          |

| 5.2         | 4301 Delay                     | 5-2          |

| 5.3         | 4303 Integrating Delay         | 5-3          |

| 5.4         | Delay Lines                    | 5 <b>-</b> 5 |

| 6           | PULSE CIRCUITS                 | 6-1          |

| 6.1         | 1410, 4410 Pulse Generators    | 6-1          |

| 6.2         | 4401 Clock                     | 6-2          |

| 6.3         | 4407 Crystal Clock             | 6-3          |

| 7           | POWER CIRCUITS                 | <i>7</i> -1  |

| 7.1         | 728 Power Supply               | 7-1          |

## CONTENTS (continued)

|        |                                                          | ruge         |

|--------|----------------------------------------------------------|--------------|

| 7.2    | 734 Variable Power Supply                                | 7-2          |

| 7.3    | 778 Power Supply                                         | 7-2          |

| 7.4    | 811 Power Control                                        | 7-2          |

| 7.5    | 823 SCR Power Control                                    | 7-3          |

| 7.6    | 829 Two-Step Power Control                               | 7-4          |

| 7.7    | 832 Two-Step Power Control                               | 7-4          |

| 7.8    | 834, 835 One-Step Power Controls                         | 7 <b>-</b> 5 |

| 8      | MODULE REPAIR                                            | 8-1          |

| 8.1    | Tools and Test Equipment                                 | 8-1          |

| 8.2    | Removal and Replacement                                  | 8-2          |

| 8.3    | Module Troubleshooting                                   | 8-3          |

| 8.3.1  | In-system Troubleshooting                                | 8-3          |

| 8.3.2  | Bench Troubleshooting                                    | 8-4          |

|        | ILLUSTRATIONS                                            |              |

| Figure |                                                          |              |

| 1-1    | Standard — 3 vdc Supply                                  | 1-2          |

| 2-1    | Standard Inverter                                        | 2-1          |

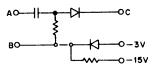

| 2-2    | Negative Diode NAND Gate                                 | 2-2          |

| 2-3    | Negative Diode NOR Gate                                  | 2-3          |

| 2-4    | Basic Positive Capacitor-Diode Gate                      | 2-3          |

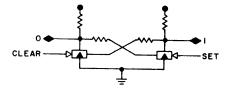

| 3-1    | Basic Flip-Flop                                          | 3-1          |

| 3-2    | Unbuffered Flip-Flop with Positive Capacitor-Diode Input | 3-2          |

| 3-3    | NPN Emitter Follower                                     | 3-3          |

| 3-4    | Flip-Flop with Output Buffer Inverters                   | 3-3          |

| 3-5    | Push-Pull PNP Output Buffer                              | 3-4          |

| 3-6    | Push-Pull Emitter Follower                               | 3-5          |

| 3-7    | Pulse Amplifier                                          | 3-5          |

| 4-1    | Basic Pulse Amplifier with Two Typical Driving Circuits  | 4-2          |

# CHAPTER 1 INTRODUCTION AND DESCRIPTION

#### 1.1 INTRODUCTION AND SCOPE

The purpose of this instruction manual is to aid personnel in maintenance, at the circuit level, of the DEC Programmed Data Processor-6. The manual contains complete descriptions of all circuits found in the Type 166 Arithmetic Processor, Type 162 Fast Memory, and in the control logic for four peripheral devices usually included in the installation: Type 760 Paper Tape Reader, Type 761 Paper Tape Punch, Type 626 Teletype Printer-Keyboard, and Type 461 Card Reader. Also included are all standard logic circuits used in the interfaces and control portions of Core Memories Types 161C and 163C; all special circuits associated with a core stack, such as the regulated power supply, core drivers, switching circuits, and sense amplifier, are described in the maintenance manual for the memory in which they are used. Troubleshooting information is included as it pertains to module replacement and repair; detailed information on system operation and troubleshooting may be found in the maintenance manuals for the PDP-6 arithmetic processor and memory. Descriptions of circuits unique to any equipment not listed above are included in the appropriate maintenance manuals.

Where possible, material common to circuits in a given class, such as basic inverter or flip-flop operation, supply voltages, and common jumper codes, is presented in the introductory remarks for each chapter. Timing characteristics common to each of the three DEC module series (1000, 4000, 6000) are also included here. The remainder of each chapter consists of material applicable to individual circuit types, such as circuit logic (if required), connector information, unique jumper codes, and all special circuitry.

Schematic diagrams for all circuits, with modified logic diagrams of a few complex modules, are grouped at the rear of the manual in order by type number. No figure references are made in individual unit descriptions, but references to applicable schematics are implied.

#### 1.2 PDP-6 MODULES

The DEC Programmed Data Processor-6 is constructed of digital modules and power circuits. The module components are mounted on a dip-soldered epoxy board surrounded by an aluminum frame measuring (with some exceptions)  $1/2 \times 4-1/2 \times 7$  inches. Logic and power connections are made through 22-pin Amphenol plugs, connected to the circuits by flexible wiring to minimize strain.

DEC circuits can be categorized by function and by maximum operating frequency. PDP-6 circuits fall into seven functional groups:

Inverters

Diode gates and decoders

Flip-flops

**Amplifiers**

Delays

Pulse circuits

Power circuits

Most types are discussed in some detail; however, the first two groups (simple inverter and diode networks) are described collectively, since the reader is assumed familiar with basic solid state electronics.

A DEC module (any circuit in the first six classes) is assigned one of three maximum operating frequencies,  $500 \, \text{kc}$ ,  $5 \, \text{mc}$ , or  $10 \, \text{mc}$ —the 4000, 1000, and 6000 series respectively (although some  $4000 \, \text{series}$  modules can operate at 1 mc). Module timing characteristics are commensurate with these speed categories. DEC standard pulse widths are  $0.4 \, \mu \text{sec}$  for the  $4000 \, \text{series}$ ,  $70 \, \text{nsec}$  for the  $1000 \, \text{series}$ , and  $40 \, \text{nsec}$  for the  $6000 \, \text{series}$ . These pulses are  $2.5 \, \text{v}$  in amplitude. Tolerances are  $+2.3 \, \text{to} +3.0 \, \text{v}$  and  $-2.3 \, \text{to} -3.5 \, \text{v}$ . DEC signal levels are standard for all modules at ground and  $-3 \, \text{v}$ . Tolerances are  $0 \, \text{to} -0.3 \, \text{v}$  and  $-2.5 \, \text{to} -3.5 \, \text{v}$ .

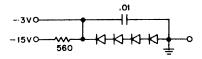

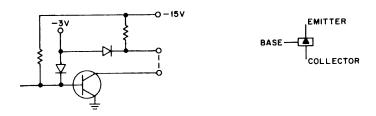

To facilitate system wiring, four connector pins on each module are reserved for supply voltages: two pins, A and B, carry +10 vdc (for ease in submodular marginal checking), pin C supplies -15 vdc and pin D is grounded. Additional pins may be used for ground as necessary. All modules that require it have a built-in source of -3 vdc, which utilizes the 0.75v forward drop of the silicon diode. Four series diodes are used, biased to -15 vdc, usually through 560 ohms (figure 1-1). The resistor accepts enough current to regulate the supply under all load conditions.

Figure 1-1 Standard -3 vdc Supply

Five PDP-6 modules, Flip-Flops 1250 and 6205, and Amplifiers 1664, 1665, and 6615, require special consideration. These types have three times the area of the standard DEC module and are serviced by two DEC mounting panels at each end--a packaging technique that permits a considerable reduction in space, in module types, and in external connections when the number of repetitive, interdependent circuits is large. Each pin designation on these five schematics is therefore two letters, the first indicating the connector (A, upper front; B, lower front; R, upper rear; S, lower rear), the second referencing a single pin of the selected connector. (On logic diagrams of the PDP-6 computer, letter designations of the

appropriate mounting panels replace the front connector prefixes; rear prefixes remain the same.) Two other modules, Flip-Flops 6203 and 6206, are double-length, standard-height types and are serviced by single connectors at both ends. Rear connectors have the usual R prefix.

A number of modules have provision for internal jumpering, which permits their use in a variety of applications without requiring additional external connections. Positions at which jumpers can be used are indicated on the schematics by dotted lines between unlettered terminals. Spare modules are delivered with all jumpers in place, and the technician must cut out the ones not wanted. On the UMLs, the type numbers for jumperable modules are followed by number or letter combinations that indicate jumper configurations (all such connections are shown on the logic drawings). Decoding methods for these symbols are given with the module descriptions.

On some circuit schematics, certain groups of passive components have a type number but no value designations; these are encapsulated elements whose values are called out elsewhere on the schematic. They appear on the modules as rectangular orange capsules.

PDP-6 modules containing only clamped loads, terminating resistors, or indicator lamps are considered self-explanatory and are not discussed here, although their schematics are included at the rear of the manual.

Replacement schematics for the circuits have drawing numbers of the form RS-X-N, where X is a letter indicating drawing size and N is the circuit type number, usually three or four digits. To the right of the drawing number is another, the revision number of the circuit schematic. To the left is a letter that indicates the revision of the circuit board. The revision letter is etched on the board and printed after the type number on the aluminum frame of the module.

#### 1.3 PERTINENT DOCUMENTS

The following documents augment these discussions presented in this book.

- a. System Modules Catalog, C-100

- b. PDP-6 Arithmetic Processor 7F-67 (166)

- c. PDP-6 Fast Memory Type 1621 Core Memory Type 161C, F-67 (162-161C)

- d. PDP-6 Fast Memory Type 1621 Core Memory Type 163C, F-67 (162-163C)

Within this text constant reference is made to standard modules and configurations. All module information such as detailed circuit schematics can be found in the module catalog. References to PDP-6 applications of decoders, etc., can be further studied in the PDP-6 Arithmetic Processor 166 Manual.

# CHAPTER 2 INVERTERS AND GATES

Mosí logical operations in the PDP-6 are performed with saturating inverters and diode gates. Because of their relatively simple design and because of the consistent use of inverters as gate buffer amplifiers, both groups are described in this chapter. For information on number of circuits per module, pin connections, jumpers, etc, refer to the DEC System Module Catalog, C-100. Many of these modules have clamped loads that do not appear at the output connectors but may be jumpered internally to inverter collectors. The presence of a jumper is indicated by a 1 in a jumper code of n bits (octal), where n is the number of clamped loads in the module. From left to right the bits correspond to the alphabetical order of the collector pins at the connector. An R is used in place of a number to indicate that all clamped loads are connected.

#### 2.1 INVERTERS

An inverter can be used as a level gate or a pulse gate. Inverter transistors are pnp type, and operate either in saturation or in cutoff. The collector-emmitter impedance of a saturated transistor is very low; at cutoff, it is very high. If the emitter is grounded and the collector is connected to a negative load, the collector output is inverted with respect to the base input. Base input loading is supplied by the 3K resistor (figure 2-1); a saturating base current of 1 ma therefore flows through the transistor when -3 vdc is present at the input. A bypass capacitor at the input provides overdriving current which speeds switching. The more positive input to an inverter usually is derived from the collector of a saturated transistor (approximately -0.2v). Base bias at 0 vdc (input unterminated) is supplied by a divider between +10 and -15 vdc. This allows marginal checking inverter base leakage (simultaneously checking collector saturation voltage of the stage preceding the inverter) and inverter dc gain.

Figure 2-1 Standard Inverter

The diode in the clamped load limits the negative voltage at the inverter output, supplying the current needed to maintain the output at -3v. With a 1.5K load resistor, diode current is a maximum of 8 ma under no-load conditions and decreases to 0 as the current drawn from the external load increases to 8 ma.

Delay through a 4000-series inverter is 300 nsec (defined as the time between the point of 10% input change and 10% output change); the 1000-series delay is 20 nsec, whereas that of a 6000-series inverter is approximately 12 nsec.

#### 2.2 GATES

The PDP-6 diode modules are of three basic types: simple networks for general purpose pulse and level gating; capacitor-diode gates; and decoders.

#### 2.2.1 Diodes

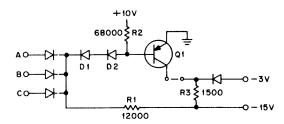

The diode gate modules contain two or more diode logic gates, consisting of a number of diode-coupled inputs driving an inverter base. A clamped load is available for each inverter. The gating diodes provide either the AND or the OR function for a given assertion level; the transistor amplifies and inverts the diode output so that the diode-inverter combination is properly termed a NAND or NOR gate. In the negative NAND gate shown in figure 2-2, Q1 is driven into conduction only if A, B, and C are all negative (-3 vdc), allowing R1 to forward-bias the transistor emitter-base junction. With ground at any input, R2 reverse-biases the junction and cuts off the transistor.

Figure 2-2 Negative Diode NAND Gate

If the source of a nominal ground input is the collector of a saturated transistor, the actual input voltage is slightly negative. The drop across the gate diodes further reduces the voltage applied to the inverter. To compensate for these reductions in input ground levels, two series silicon diodes, D1 and D2, are employed as level shifters between the gate proper and the inverter base. The shift is large enough to ensure positive bias at the base and hence reliable cutoff when any normal ground input is applied to the gate.

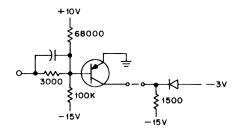

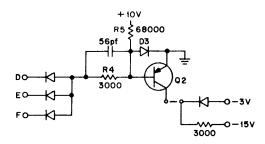

The negative diode NOR gate shown in figure 2-3 drives Q2 into saturation through input resistor R4 when -3 vdc is applied to D, E, or F. When none of the inputs are negative, R5 cuts off Q2 by reverse-biasing the emitter-base junction. A diode, D3, is always placed across this junction to prevent the transistor base from being driven too positive when no input connections are made. R5 may actually be two resistors connected to both +10v supplies, as is done in module 6116. This prevents undue sensitivity of the circuit to marginal voltages.

Figure 2-3 Negative Diode NOR Gate

#### 2.2.2 Capacitor-Diode Gates

In the basic positive capacitor-diode gate shown in figure 2-4, a positive pulse or level change at A produces a positive pulse at C, provided a ground enabling level has been present at B for a certain interval before the pulse. This interval depends on the resistor-capacitor time constant, and is the time required for the common junction voltage to rise sufficiently close to ground. The gate is inhibited when the junction voltage falls close enough to -3 vdc that the input pulse cannot forward bias the diode. A clamped load often connects to the gating level input. In the basic negative gate the diode polarity is reversed, and the pulse input, enabling input, and output are negative. A complete capacitor-diode circuit provides pulse amplification in an inverter, which is associated with a single gate or shared among several. In all positive gate modules the inverter is at the pulse input; in all negative modules, at the pulse output. Thus, regardless of the polarity of the gating level, all modules accept a negative pulse or level change and produce a positive-going output.

Figure 2-4 Basic Positive Capacitor-Diode Gate

The circuit at the left in the 4127 schematic is typical of negative capacitor-diode gates. A -3 vdc level applied to F enables the gate; a negative pulse or level change at E then generates a positive-going output pulse at H. The delay inherent in this circuit requires that the gating level be present at least 1 µsec before arrival of the pulse. When F becomes negative, the C1-D1 junction falls from ground to -3v, the fall time being determined by the time constant of C1-C2. After this interval, a negative pulse applied to E is sufficient to forward-bias D1 and pass through the diode to the load. The gate output is referenced by R5 to a dc level of -3v. D2 and R1 prevent the gate input from going more negative than -3v, preventing undue sensitivity of the circuit to noise at E. When D1 is forward-biased by a pulse at E, the negative pulse at the D1-R5 junction is coupled through C2 to the Q1 base. As the transistor turns on, output H rises to ground. At the trailing edge of the input pulse, D1 is cut off. The Q1 base is normally biased positive by R3-D3 to reduce noise susceptibility.

The circuit in the upper left of the 4128 schematic is typical of positive capacitor-diode gates. The pulse input P can be driven by a standard negative pulse or by a negative-going level change with a maximum fall time of 5 µsec. Each gate is enabled by a ground level that must be present at least 1.5 µsec before arrival of the pulse; however, for a transfer of 1s or 0s only, all off gates must be disabled for 4.5 µsec before readin. If the D2 cathode is tied to the base of a saturated transistor, it is near ground potential. A -3v to ground pulse or level change at the Q1 collector is coupled through C4 but can forward-bias D2 only in the presence of a ground level at F.

#### 2.2.3 Decoders

The decoder modules contain special diode configurations that decode a given binary information group to an assertion at one of several possible outputs. The Type 1151 contains an 8-section diode matrix that is driven by the 1 and 0 outputs of three flip-flops. Each section is a 3-diode negative AND gate, which receives a unique combination of inputs representing one of the eight states of the three flip-flops. The assertion of a specific binary input configuration thus turns on a single output inverter. For example, when all flip-flops are 0, the output of the gate at the far left of the schematic, whose inputs are connected to the flip-flop 0 outputs, is at -3 vdc. The outputs of all other diode gates are at ground. At any time, therefore, all inverter outputs are negative except the one driven by the satisfied diode gate. The entire module can be gated on or off at the common emitter connection of the inverters, or the emitters can be jumpered to ground internally or grounded at the connector.

Types 4151 and 6151 are identical to the 1151 in all respects except speed. The 6150 is similar to the 6151 except for inverted logical sense (all inputs to a gate must be at ground to obtain a unique negative decoder output), internally grounded emitters, and a common enable input to the diode matrix.

The Type 6155 contains two binary-to-quarternary networks. Each output inverter is driven by a 3-input diode AND gate, which is in turn driven by the outputs of two flip-flops and a common enabling level. When all three inputs to a given gate are negative, the ground output of its associated inverter is uniquely asserted.

#### 2.3 MAJORITY LOGIC

In the memory protection and relocation networks are two circuits that employ majority logic. Type 6131 is a dc adder which uses majority logic to develop the carry output; Type 6132 contains two majority gates which form part of the borrow chain in an arithmetic comparison.

In addition there must be a carry to the next more significant bit if two or more of the three inputs (two summands and a carry) are 1s. For subtraction, the minuend bit is complemented, and the carry output then represents a borrow to the next bit. If inverter or diode gates were used to develop the carry output, separate AND gates to decode all four possible input cases that necessitate a carry would be necessary, as well as an OR gate to form the output. Majority logic does not differentiate as to the source of the logic inputs; instead, all three are fed to precision resistors and the voltage at the junction point is compared to a fixed threshold by a difference amplifier. The summing resistors are paralleled by speed-up capacitors and the two-stage difference amplifier used in both modules operates far from saturation. Consequently the propagation delay for the carry is less than 10 nsec per bit.

#### 2.3.1 6132 Majority Gate

This module consists of two gate circuits and appropriate internal supply voltages. The output of a gate is asserted whenever at least two of its three inputs are asserted. In the protection logic the A input (pins X and E respectively of the left and right gates) is an MA bit on 1, the B input is a PR bit on 0. These inputs are labeled  $\overline{A}$  IN and  $\overline{B}$  IN because they are made through inverters and hence require opposite assertion to C IN, which is the carry from the next less significant stage. The carry out is available at both polarities. Since these circuits are used in series, the carry output of the left gate is wired internally as the carry input to the other but is available at the connector via an internal jumper. If the A and B inputs to a series of gates represent 1s in a pair of numbers, C is the carry function. If one set of inputs, e.g., B, represents 0s, C is the borrow function of B-A.

The A and B inputs have ground assertion and drive standard DEC 6000-series inverters with clamped loads (for example Q1-Q4 in the left gate). The three majority logic resistors (R3-R6-R9) are tied together at the left base of Q2, the first stage of the difference amplifier. The carry input is asserted negative at R3 to correspond logically with the inverted signals at R6 and R9. The two emitters of Q2 are tied together to R8, a current sink to -15 vdc. When two or more of the inputs to the resistance summing

network are -3v, the sum point (left base of Q2) falls below -1.5v, cutting off the left side of Q2 and allowing the right side to conduct all current. Conversely when two or more inputs are at ground, the summing point rises above -1.5v turning on the left side and cutting off the right. Neither Q2 collector can saturate however because current sink R8 conducts a maximum of 1.5 ma which cannot bring either collector below ground.

The difference amplifier output stage is Q3 whose bases are driven directly by the Q2 collectors. The emitter current source for Q3 is R:4 to +10 vdc; the collectors are clamped to 0 and -3 vdc by D2 and D3 on the left, D4 and D6 on the right. Coils L1 and L2 provide shunt inductive frequency compensation for the Q2 collectors to enhance propagation speed. C4 and C8 as well as the various capacitors associated with the series voltage supply at the right serve to keep voltage supply points free from transients.

#### 2.3.2 6131 DC Adder

This module contains a majority gate, an exclusive OR network, and supplies for the necessary internal voltages. If bits from two summands are asserted ground at pins E and F, and a carry in is asserted ground at L, negative at T, a bit of the sum appears at outputs X and Y (ground and negative, respectively) and the carry out to the next more significant stage appears in both polarities at U and K. The negative sum out is also available at pin W isolated through a resistor to drive an indicator. A fifth input, pin H, receives a ground enable level. When the enable falls to -3 vdc, the F input is negated internally and consequently the sum output is identical to the E input (assuming there is no carry in, which would ordinarily be the case). In the computer, these circuits relocate memory addresses for the user mode. For this application input E receives an MA bit, F an RLR bit, the carry inputs come from the next less significant adder, and H receives the relocate enable level from executive mode control.

In the schematic the inverters for inputs E, F, and H are at the top left. Below these are two exclusive OR stages and an output current switch (difference amplifier). To the right of center is a difference amplifier for the majority gate and at the far right is the series-diode voltage source. Except for the input inverters and common internal supply, the sum and carry networks are completely independent. Inputs E and F drive Q2 and Q6, the latter paralleled by Q8 so that a negative level at H prevents negative assertion of the F input at the Q6 collector. Both inverter loads are clamped at -3 vdc by D1 and D2. L is the carry input of the majority gate, whose input for the adder is T.

The adder uses two exclusive OR stages to produce a sum in the same way as do the arithmetic register bits except that the output depends only on the propagation of level changes rather than pulsed flip-flop changes. The first stage produces a partial sum from the two summand inputs; the second stage then inverts this partial sum whenever there is a carry. In other words when neither or both summands are asserted, the sum output is equal to the carry input; otherwise the sum is the inversion of the carry. The first stage consists of transistors Q3 and Q5 with associated RC base feeds. The Q3 and Q5 collectors are

OR pair, the base of one transistor is driven through an RC network from the emitter of the other. Consequently when both emitters are at the same voltage both transistors are cut off; only when the two emitter drive signals differ can one of the pair saturate. The collectors are at -3v whenever the E and F inputs are identical, at ground when they differ.

The second exclusive OR stage is Q1 and Q7 with similar cross connection from emitters to bases. The first stage drives the Q1 emitter through an RC network; the emitter of Q7 receives the carry, asserted ground at T, through a similar RC net. When E and F are identical, the Q7 base is -3v so Q7 conducts whenever there is a carry. When E and F differ, the Q7 base is at ground and Q1 determines the sum as the complement of the carry. In order to prevent saturation in this stage the Q1-Q7 collector junction is not clamped at -3 vdc; only the input inverters and the first exclusive OR stage can saturate. Since emitter current sources R2 and R16 cannot allow current sufficient to bring the second-stage collectors more positive than -3v, saturation does not occur. The Q1-Q7 collector junction drives the left base of Q4, but the right base is held at -4.5v from the series-diode voltage source at the far right. When either Q1 or Q7 conducts, the left half of Q4 supplies all the current through R14 to -15v, pulling the sum 1 output, pin Y, down to the -3v clamp level. The right collector of Q4 floats, clamped at ground by D7, thus negating the sum 0 output at pin X. When Q1 and Q7 are both cut off, the right half of Q4 brings the X output negative, whereas the floating left collector allows Y to return to the ground clamp level.

Input inverters Q2 and Q6 also drive R11 and R10, two of the three majority logic input resistors. The third resistor R17 is driven directly by the negative carry input at pin L. The junction point of the three resistors drives the left base of Q9, the first of two difference amplifier stages that develop the carry output. The Q9 emitters are paralleled; current sink R23 accepts enough current to drive Q10 but not enough to saturate Q9. The right base of Q9 is held at -1.5v from the diode voltage supply. The difference amplifier formed by Q9 and Q10 is identical to that in the majority gate discussed in the preceding section. It develops the carry output at pin K (at the left Q10 collector), clamped at 0 and -3 vdc by D10 and D9. The complement is available at pin U from the right collector, clamped by D11 and D12.

# CHAPTER 3 FLIP-FLOPS

Of the flip-flop types used in PDP-6, the 1260, 4706, 4707, 6203, 6205, and 6206 perform rather complex logical operations, so modified logic diagrams for these modules have been included with the schematics to make circuit identification and component location easier. In many flip-flop modules, jumpers select the outputs that appear at the connector or select the flip-flop states produced by a preset pulse. In either case the side of a flip-flop to which a jumper is connected is indicated by a bit in a jumper code of n bits (octal), where n is the number of jumperable flip-flops in the module. The bits left to right correspond to the alphabetical order of the flip-flop outputs at the connector. Other codes unique to particular modules are given in the module descriptions.

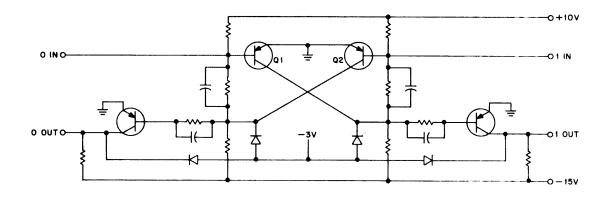

The flip-flop, or bistable multivibrator, is a two-state device used primarily for short term storage. A simple flip-flop can be constructed by interconnecting two grounded-emitter inverters (figure 3-1). When one inverter is cut off, its output is negative; this holds the other transistor on, which in turn holds the first transistor off. The state of the flip-flop can be changed by driving either the base of the conducting transistor or the collector of the nonconducting one with a positive-going pulse (although the latter method requires a more powerful driving source). It is this ability of the flip-flop to remain in the state to which it is driven, even after removal of the activating signal, which permits its use as a storage device.

Figure 3-1 Basic Flip-Flop

It is often desirable to reduce flip-flop output impedance in order to drive heavier loads. For this reason, many flip-flop modules are equipped with buffer inverter or emitter follower amplifiers at the outputs. Delay networks are used in PDP-6 flip-flops when speed considerations prevent the use of capacitor-diode gates and intrinsic circuit delay is not sufficient to allow output terminals to be sensed while input terminals are being pulsed.

#### 3.1 OPERATION OF COMPONENT CIRCUITS

To avoid repetition, six circuits basic to the operation of many PDP-6 flip-flops are discussed in this section. Although component values may differ in some instances when the same circuit is represented in several speed lines, the descriptions of these circuits are not dependent on operating frequency.

#### 3.1.1 Unbuffered Flip-Flop

Figure 3-2 shows this circuit, with a type of input gating commonly used with 4000-series flip-flops, the positive capacitor-diode gate. The flip-flop is stable in either of two states: Q1 conducting and Q2 cut off, or vice versa. Its state can be changed by applying a positive-going pulse to the base of the conducting transistor or to the collector of the nonconducting transistor.

Figure 3-2 Unbuffered Flip-Flop with Positive Capacitor-Diode Input

Since the collectors of Q1 and Q2 are resistively cross-connected to the opposite bases, R2 and R3 hold the flip-flop in its new state after the disappearance of the trigger pulse. Base bypass capacitors C3 and C4 provide overdriving current to the transistors to speed switching. The flip-flop is said to be in the 0 state when the 0 output terminal is quiescent at -3 vdc and the 1 output is grounded. Q2 remains saturated and Q1 cut off until the flip-flop is set through capacitor-diode gate D2-C2-R4. This gate is enabled by a ground level at the R4 input, raising the D2-C2 junction to ground. A standard positive voltage step applied to the C2 input then forward-biases D2 (if a ground enable is present at R4) and turns off Q2. The sharp negative spike caused by the differentiation of the pulse trailing edge is discharged through R4.

As the positive-going trigger reverse-biases Q2, the resulting negative transition at its collector is coupled through the parallel combination of R2 and C3 to the Q1 base. As this point falls below the Q1 emitter, Q1 conducts and its collector rises to ground. This level is, in turn, coupled through C4 and R3 back to the Q2 base, allowing R8 to maintain Q2 at cutoff. The flip-flop is now in the 1 state. D3-R5 and D4-R6 are output clamped loads. The flip-flop is cleared back to 0 by enabling the C1-R1-D1 gate and applying a positive pulse to the Q1 base. Unbuffered flip-flop delay is approximately 50 nsec, 25 nsec, and 12 nsec for the 4000, 1000, and 6000 series, respectively.

#### 3.1.2 NPN Emitter Follower

The npn emitter follower, shown in figure 3-3, with clamped loads at input and output, is often used as an auxiliary amplifier for positive-going set and clear trigger pulses where no signal inversion is desired. Its output impedance is low for positive-going pulses or level changes; current is supplied to the load by the transistor rather than by a load resistor.

Figure 3-3 NPN Emitter Follower

Since, as a current amplifier, the npn emitter follower can operate with less drain on external trigger circuits than would a diode-clamped load configuration, it permits the use of remote trigger sources that may require long transmission lines and terminating resistors.

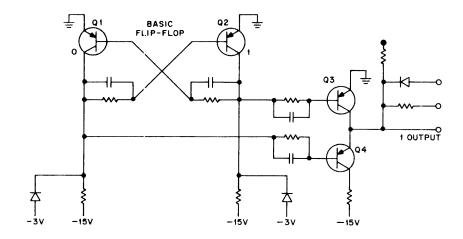

### 3.1.3 Flip-Flop with Output Buffers

Addition of output buffer amplifiers to the basic flip-flop substantially increases its driving capability and provides isolation from noise in the external load. When inverters are used as the amplifying element, the asserted output cannot be taken from the collector of the cutoff transistor. Instead the buffer inverter driven by the opposite collector provides the output (figure 3-4).

Figure 3-4 Flip-Flop with Output Buffer Inverters

The pnp output buffer transistor is saturated when turned on and therefore has considerable drive capability at ground assertion. At negative assertion, however, the drive capability is limited by the conductance of the clamped load resistor acting as a current sink. When increased drive capability is required at negative assertion, a push-pull output buffer is used. Figure 3-5 shows a basic flip-flop, Q1-Q2, which drives push-pull output buffer Q3-Q4 to develop the negatively asserted 1 output. When the flip-flop is set, Q2 conducts and Q3 is cut off, allowing Q4 to behave as an emitter follower driven by the -3 vdc level from the cutoff Q1 collector.

Figure 3-5 Push-Pull PNP Output Buffer

The current drive capability at the negative 1 output to the right of the figure is limited only by the Q4 collector resistance. Since Q4 never saturates, it can release the output for transition to ground level without requiring elimination of minority carrier storage caused by collector saturation. When the flip-flop is cleared, Q1 conducts and Q4 is therefore cut off; the Q2 collector load draws current through the Q3 base resistance to saturate Q3 and negate the 1 output at ground.

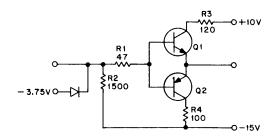

Push-pull complementary emitter followers (figure 3-6) are also used when the flip-flop is required to supply large amounts of current to the load at both logic levels. For ground level inputs, Q1 supplies current to the load through R3. The output point is then more negative than the Q1-Q2 base connection because of the forward drop of the Q1 emitter-base diode, and Q2 is therefore biased to cutoff. When the input is held at -3.75 vdc by D1-R2, Q2 conducts current from the load to -15 vdc through R4, and Q1 is cut off. R3 and R4 limit the load currents: this circuit can maintain a ground level up to 80 ma drain and a -3 vdc level up to 120 ma.

Figure 3-6 Push-Pull Emitter Follower

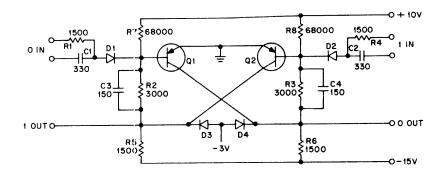

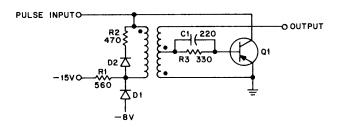

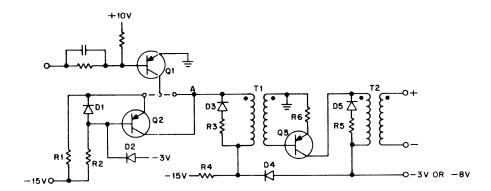

#### 3.1.4 Pulse Amplifier

Pulse amplifiers (figure 3-7) standardize amplitude and width of carry pulses from one flip-flop in a register to the next. In the pulse transformer-inverter combination shown in figure 3-7, the pulse input point when quiescent is held to -8 vdc by the RI-DI clamped load, through the low resistance primary of the transformer. The output terminal is at ground. The leading edge of a positive-going input pulse is coupled to the output as a sharp negative step (dots indicate relative winding polarities). A negative step of smaller amplitude is applied to the base of feedback transistor QI from the secondary center tap. The transistor amplifies and inverts this portion of the output pulse and returns it to the input, where it maintains ground potential even if the input pulse should prematurely disappear.

Figure 3-7 Pulse Amplifier

Output pulse width is therefore determined primarily by the pulse transformer and R1. The pulse ends when the transformer primary current reaches the value of current through R1. Current through clamp diode D1 is then reduced to zero, additional primary current increases the voltage drop across R1, and primary voltage begins to fall. The induced base drive to Q1 falls, reducing feedback, and the transformer voltages rapidly collapse. D2 and R2 prevent ringing by dissipating all stored energy in the first back swing after pulse completion.

#### 3.2 1250 FAST MEMORY FLIP-FLOP

The Type 1250 is a quadruple module containing 24 flip-flops, interconnected to form three contiguous bits of eight flip-flop registers. In PDP-6, two groups of twelve Type 1250 modules make up a bank of sixteen 36-bit fast memory registers. Additional circuits include three diode readout gates and three noninverting digit amplifiers. A readout gate comprises eight 2-input negative AND gates with outputs ORed together, amplified and inverted. A digit amplifier is made up of two standard inverter amplifiers which supply incoming data to the register selected by the active write line.

Clear inputs are DEC standard 70-nsec positive-going pulses, applied separately to each register. Write signals are standard negative pulses which trigger the flip-flop collector through input buffer inverters. Buffer inverter emitters in each vertical column are gated by a single digit amplifier with output assertion at ground. Flip-flop registers can be sampled nondestructively and must be cleared before readin. The clear must precede the write by at least 100 nsec. Read signals are standard negative pulses. To sample one of the eight registers, the appropriate read line, ANDed with the 0 outputs of that register by the three diode networks, is pulsed. Transistors Q79, Q80, and Q81 invert the gate outputs, so the output of the sampled register appears at BZ, BL, and AE with negative assertion for 1s.

The operation of the 1250 Flip-Flop is identical to that of the basic flip-flop with one exception: clamped loads to -3 vdc are not used at the collectors of 1250 Flip-Flops. Instead, all flip-flop collectors are referenced through 1500 ohms to the parallel combination of R55 and R56, shown in the bottom right of the schematic. Since half of the 48 load resistors are at all times tied to grounded flip-flop collectors, load resistors for the off transistors operate into a voltage divider between -15 vdc and ground.

#### 3.3 1260 SUBROUTINE CARD

This module contains three circuits, each comprising a flip-flop, a pulse amplifier, and two diode gates. Each circuit provides reentry to an asynchronous time chain by producing a single output pulse upon receipt of a restart pulse while the flip-flop is set (a logic diagram of this module precedes the schematic). The following describes the circuit including Q1 to Q6 and Q19. Flip-flop Q2-Q3 may be set either by grounding H or by applying a -3v pulse to K. While the flip-flop is 1 (-3 vdc at L, 0 vdc at H), a negative-going pulse or level change at J appears at E, amplified and standardized to 70 nsec duration. The flip-flop is cleared by grounding L or by applying a -3v pulse to the D1 or D2 cathode at F or E (a pulse at F clears the entire module). Note that the output pulse at E is applied back to the clear input of the flip-flop via D2 and Q1, so once the restart pulse has been received, no further output pulses can be produced until the flip-flop is again set.

The flip-flop used in the 1260 is the basic one discussed above. It is collector-gated with standard input buffer inverters, Q1 and Q4; the D5-D7-Q5 diode gate is also of standard design. The pulse amplifier (Q6-Q19-T1-T2) is similar to that in the Type 1609 Pulse Amplifier-Standardizer.

#### 3.4 4214 QUADRUPLE FLIP-FLOP

The Type 4214 contains four flip-flops, each with both inputs and both outputs available at the connector. Each pair of flip-flops shares a common direct clear input at P or R. The module operates at any frequency up to 1 mc, using the basic flip-flop discussed above, but without internal capacitor-diode gates.

The common clear inputs require DEC standard 0.4-µsec positive pulses, which must precede readins by at least 1 µsec. The set and clear inputs to each flip-flop may be driven by positive capacitor-diode gates or by DEC standard 0.4 µsec positive pulses. Since all 1 and 0 outputs are available, the flip-flops may also be set or cleared at their collectors. Typical flip-flop output delay is 50 nsec.

#### 3.5 4217 FOUR-BIT COUNTER

The Type 4217 contains four flip-flops, a pulse inverter-amplifier, positive capacitor-diode gates, and a negative dc supply. Depending upon external connections, the module may function as a counter or a buffer register with 1s transfer parallel readin. All input signals are applied to the flip-flops through positive capacitor-diode gates such as the C18-R37-D22 combination. The negative dc supply, consisting of D26 to D29 and R41, has a -0.75v tap at the D26-D27 junction and a -2.25v tap at the D28-D29 junction. Two capacitor-diode gates at each flip-flop have a common pulse input and are conditioned by the flip-flop outputs to form a complementing gate. Complement inputs for flip-flops A, B, C, and D are pins X, T, N, and H. Complement and clear signals are DEC standard 0.4-µsec positive pulses; the readin at F is a 0.4-µsec negative pulse.

The module may be connected as a 4-bit counter by tying the complement inputs of flip-flops B, C, and D either to the 1 outputs (up counter) or to the 0 outputs (down counter) of the preceding flip-flops. Count pulses are applied to pin X. For example, if the counter is initially clear and is connected for up counting, a pulse at X complements FFA to 1 because the gate is enabled by ground at the Q9 collector. The arrival of a second count pulse at X returns FFA to 0, causing its 1 output to rise to ground. This positive-going transition is coupled through the complement gate of FFB to the Q7 base, and sets FFB. Counting continues in this manner until the counter recycles to all 0s or is cleared by a pulse at E. The count may begin with any desired number, using the parallel readin gates and pulse input F. When the register functions as a down counter, the carry chain must be inhibited while the initial number is read in. A long time constant in the clear circuit prevents carry propagation when the register is cleared (this is necessary in the up count configuration).

#### 3.6 4218 QUADRUPLE FLIP-FLOP

This module contains four flip-flops, a pulse inverter-amplifier, eight positive capacitor-diode gates, and a negative dc supply. Depending upon external connections, the Type 4218 may be used as a

shift register, or buffer register with jam transfer parallel readin. All input signals arrive at the flip-flops through positive capacitor-diode gates such as the D1-C11-R29 combination. The negative dc supply, consisting of D17 to D20 and R28, has a -0.75v tap at the D17-D18 junction and a -2.25v tap at the D19-D20 junction. The readin at P is a DEC standard 0.4-µsec negative pulse. Levels at E, H, S, and V gate the pulse at the set inputs of the flip-flops; levels at F, K, U, and X gate the pulse at the clear inputs. Gating levels must be present at least 1 µsec before readin for assertion (ground) and 2 µsec for negation. All four flip-flops are cleared simultaneously by a DEC standard 0.4 µsec positive pulse at R. A clear pulse must precede a readin by at least 1 µsec. Total flip-flop delay is less than or equal to 50 nsec.

For readin, complementary levels are connected to the two input gates of each flip-flop. The readin pulse thus loads (or shifts) Os and 1s simultaneously, regardless of the prior states of the flip-flops.

#### 3.7 4220 EIGHT-BIT BUFFER

This module contains eight flip-flops, each with positive capacitor-diode readin gates, a negative dc supply, and two pulse inverters, one to clear the flip-flops, the other to drive the gates. The gate driver inverter output is applied to an emitter follower whose low impedance output prevents cross coupling between capacitor-diode gates. For each flip-flop, the 1 input and a single output are available at the module connector. An output pin may, however, be connected either to the 1 or to the 0 output eyelet of its associated flip-flop with an internal jumper. The jumper code is an octal number representing an 8-bit binary number that identifies the output used for each flip-flop.

The clear and readin inputs require DEC standard 0.4-µsec negative pulses. A clear pulse must precede readin by at least 1 µsec. Level inputs are DEC standard signals, asserted at ground through positive capacitor-diode gates. Gating levels must be present at least 1 µsec before readin for assertion and 2 µsec for negation. Total flip-flop delay is less than or equal to 50 nsec.

#### 3.8 4221 SIX-BIT SHIFT REGISTER

This module comprises six flip-flops, positive capacitor-diode gates, three pulse-inverter amplifiers, and a negative dc supply. The flip-flops are internally connected as a shift register and may be preset with a 1s transfer parallel readin. All signals are applied to the flip-flops through positive capacitor-diode gates such as the C1-R2-D42 combination. The negative dc supply, consisting of D34 to D37 and R5, has a -0.75v tap at the D36-D37 junction.

Clear, shift, and readin pulses at Z, X, and Y respectively are DEC standard 0.4-µsec negative pulses. The output of readin inverter Q15 drives npn emitter follower Q16, which provides a low impedance signal to prevent cross coupling between capacitor-diode gates. Pins R, S, T, U, V, and W are the

parallel inputs and are asserted at ground. Gating levels must be present at least 1  $\mu$ sec before readin for assertion and 2  $\mu$ sec for negation. A clear pulse must precede readin by at least 1  $\mu$ sec. Total flip-flop delay is less than or equal to 50 nsec.

Flip-flops 1 to 5 have single output terminals (H, J, K, L, and M); each may be jumpered internally to either the 1 or the 0 output of the associated flip-flop. Both outputs of flip-flop 6 are available at the connector. An additional jumper provision allows the clear line to be connected either to the set or clear input of flip-flop 1. The octal number in the jumper code therefore represents a 5-bit binary number that indicates which flip-flop outputs appear at the connector. The number is followed by S or C to denote the connection of the clear line to flip-flop 1.

#### 3.9 4225 EIGHT-BIT COUNTER

The Type 4225 contains eight flip-flops with complement inputs internally connected in a counter configuration, a single inverter used for presetting, and a negative dc supply. Both collectors of each flip-flop are available at the module connector and serve both as inputs and outputs. A series of jumper connections in the complement circuits of the register allows a choice of either binary or BCD counting (appropriate connections are indicated by B and D at the jumper eyelets). Flip-flops 4 and 8 have separate set and clear gates, rather than single complement gates, to facilitate alternate counter connections. For either mode, pin Y is the LSB count input and accepts a standard 0.4-µsec positive pulse or positive-going level change. The complement network for each flip-flop comprises two capacitor-diode gates with a common pulse input. The gates are conditioned by the flip-flop outputs. The preset inverter, Q17, accepts a negative pulse of 1 µsec minimum duration at Z. The pulse is inverted and applied through a capacitor-diode network to eight jumper eyelets. The register may be preset in any desired way by jumpering these eyelets to the appropriate flip-flop bases. The octal number in the jumper code represents the 8-bit number to which the module is preset. The number is followed by B or D to indicate binary or decimal operating mode.

#### 3.10 4706 EIGHT-BIT TELETYPE RECEIVER

This module contains 14 flip-flops and a one-shot multivibrator (pulse shaper), with all gating implemented by positive capacitor-diode networks. Eight of the flip-flops make up a shift register; the remainder perform various control functions associated with the transfer of 8-bit Teletype characters from a unipolar line into the shift register. An 880-cps clock provides all timing at S. Usually the maximum transfer rate is 10 characters per second. The 100-msec period required for a single character transfer is divided into eleven equal unit intervals as follows:

START--one unit

8-bit character--eight units

STOP--two units (or more; prolonged STOP indicates idle line)

A timing diagram and a modified logic diagram accompany the schematic.

Between transfers, the Teletype receiver is inhibited by the STOP signal (ground) at T, holding the D26 cathode negative and inhibiting the ACTIVE set gate. Pin U must be at ground to enable the module. When START (-3v) arrives at T, the D26 cathode is grounded through inverter Q33, allowing R65 to enable the ACTIVE set gate. The following clock pulse at S sets ACTIVE, inhibiting the diode gate at the D24 cathode and generating a preset pulse through Q35 and its associated capacitor-diode gate. The preset pulse sets all shift register bits; it clears IN LAST UNIT and the MSB of the 3-bit counter (the other two are both 0 at this time). Since the counter is enabled when ACTIVE is 1, the next clock begins the first 8-count cycle. Every 4-court triggers the shift one-shot input gate, which is conditioned by the O state of IN LAST UNIT. The single pulse resulting at the Q24 collector is inverted by Q22, amplified by npn emitter follower Q21, and applied to the shift register input gates. Since 1 inputs at T are asserted at ground, the first shift transfers START into the register as a 0; the next eight pulses shift in the character. After seven bits have been read, the () in IN1 enables the set gates to IN LAST UNIT and FLAG: the eighth shift thus sets both flip-flops (FLAG lights an indicator mounted on the module). The 1 state of IN LAST UNIT inhibits the shift one-shot and enables the ACTIVE clear gate, C2-D31-R76, so the next 4-count clears ACTIVE. Since the STOP leve (ground) is now present at T, the receiver is disabled until the arrival of the next START. For a standard 2-unit STOP code, jumpers C and D are present. IN LAST UNIT then enables the counter for one more cycle until the next 4-count clears it (this is the case shown in the timing diagram). For 1-1/2 units, B and D allow the next 0-count to clear IN LAST UNIT. For a 1-unit code the same 4-count that clears ACTIVE also clears IN LAST UNIT because of jumpers C and E. In any case the counter is inhibited when IN LAST UNIT clears, so it stops with the two less significant bits clear.

Transient inputs at T are prevented from activating the receiver by a diode gate which samples the outputs of all shift register bits and the pin T input. If the START level does not persist for at least five clock pulses, R64 enables an auxiliary ACTIVE clear gate, C23-R80-D32, which is pulsed by the first SHIFT, deactivating the receiver.

The flip-flops and positive capacitor-diode gates used in the 4706 module, as well as the npn emitter follower (Q21), are discussed at the beginning of this chapter. The one-shot multivibrator, comprising Q23 and Q24, is similar to the standard bistable multivibrator, or flip-flop, with the exception that no dc path exists from the Q23 collector back to the Q24 base. The device is therefore capable of only one stable state, in which Q24 conducts and Q23 is cut off. A positive pulse applied to the Q24 base momentarily cuts off Q24, driving Q23 into conduction. The positive transition at the Q23 collector is

coupled through C2 back to the Q24 base. The C2-R6 time constant primarily determines the duration of the negative level at the Q24 collector. As C2 discharges through R6, Q24 is eventually biased back into conduction and reverts to its quiescent state.

There is only one output terminal for each character flip-flop, and it can be connected to either the 1 or 0 side with an internal jumper. The jumper code thus includes an octal number equivalent to eight bits which indicate the outputs used. Following the number an F indicates a jumper that causes FLAG to be cleared when reception of a new character begins; an A indicates a jumper that allows ACTIVE to be sampled at pin M; and the letters associated with the STOP code jumpers indicate which of those are present.

#### 3.11 4707 EIGHT-BIT TELETYPE TRANSMITTER

The Type 4707 Transmitter receives 8-bit characters from the PDP-6 I/O bus and sends out each character serially as a Teletype signal on a unipolar line. The module comprises 15 flip-flops and associated inverter and positive capacitor-diode logic. Ten flip-flops are connected as a shift register; the remainder perform various control functions associated with the character transfer. Timing is governed by a 220-cps clock input at T. Usually the maximum operating speed is 10 characters per second. The 100-msec cycle is divided into eleven equal units as follows:

START: one unit

8-bit character: eight units

STOP: two units (completing the cycle; longer indicates idle line)

A modified logic diagram and a timing diagram are included with the schematic. The module uses the basic flip-flop, capacitor-diode gate, and npn emitter follower discussed at the beginning of the chapter.

The transmitter is inactive until readin occurs at N, loading a character into the 8-bit OUT register and setting ENABLE, which in turn conditions the ACTIVE set gate through the D59-D61-D62 gate. The next clock sets ACTIVE, enabling the set input gate of a complementing flip-flop (FREQ DIV) and clearing OUT LINE to generate the START level at V. Subsequent clocks trigger the frequency divider, which generates a shift pulse through inverters Q23, Q22, and emitter follower Q21 on every transition to 0. The first shift moves the initial 1 from ENABLE into OUT8, shifts the character one place to the left, and sends out the first character bit by shifting OUT1 into OUT LINE. Each shift sends out a bit and clears ENABLE, so 0s follow the initial 1 through the register. The eighth shift places 1 in OUT1, followed by 0s in the remainder of the register and in ENABLE. This condition enables the ACTIVE 0 input through the large diode gate; thus the next and last shift clears ACTIVE while shifting 1 into OUT LINE.

The signal now at pin V is the STOP level, which usually must persist for at least four clock pulses. This time interval is supplied by a pair of STOP flip-flops that furnish a 4-count in the sequence 01, 11, 10, 00, provided jumpers A and B are present (this is the case shown in the timing diagram). The

O transition in ACTIVE, besides setting FLAG (which lights an indicator mounted on the module), also sets OUT S1. The next three clocks continue the count, of which all steps except 00 inhibit the ACTIVE set gate in case a new readin has already occurred. The transmitter is reactivated by the first clock following the 00 count or a readin, whichever happens later. However, a negative level at R extends the inhibit indefinitely by holding OUT S1 on.

For a STOP code of 1-1/2 units, jumpers A and C enable the ACTIVE set gate at the same configuration, but the STOP flip-flops cycle through a 3-count: 01, 10, 00. For a 1-unit code, the absence of A enables the set gate on OUT S1(0), and C causes OUT S1 to set and clear on two clocks.

Either polarity may be selected at output V (and its opposite at W) by jumpering the desired OUT LINE output to the Q41 base. The jumper code thus includes a 0 or 1 to indicate the output used. An F indicates a jumper that allows FLAG to be cleared when a new character is received; the letters associated with the STOP code jumpers indicate which of those are present.

#### 3.12 6203 SC AND FE FLIP-FLOPS

This module contains two 10-mc flip-flops, the ith bits of the 9-bit shift counter and floating exponent register. It is double size and is serviced by two standard 22-pin connectors (rear connector pin designations have the prefix R). A tap on the load resistance for the internal -3 vdc supply provides -8v for the pulse transformer primary clamp.

A logic diagram for the 6203 module, showing transistor numbers, is included with the schematic. In addition to standard inverter and diode gates, three special circuits are associated with the basic flip-flops and output buffers (all are discussed at the beginning of the chapter). Npn emitter followers Q11 and Q19 change SC state directly by grounding the appropriate flip-flop collector. The LC networks at the Q11 and Q19 bases delay the state change about 50 nsec from the leading edge of an incoming trigger pulse. The SC complement network, shown in the lower half of the logic diagram, operates entirely through this pulse delay to prevent race conditions. A pulse amplifier (upper left) is used for SC carry propagation.

Transistors Q12 and Q20 make up the basic SC flip-flop; Q8 and Q22 are its output buffers. A direct set input is provided at T, which triggers the flip-flop through npn emitter follower Q24; this input requires positive-going pulses from a pulse inverter, and includes the clamped load. SC may be cleared at RL through the pulse delay by a DEC standard 40-nsec negative pulse. The 1 and 0 outputs are at M and L; the resistor-coupled output at R may drive an indicator amplifier.

The FE flip-flop is unbuffered and may clear directly at the Q34 base by applying a 40-nsec positive pulse to RE. It may be set at < by a level or positive-going pulse to ground. The J output is resistor-coupled for connection to an indicator driver.

#### 3.13 6205 ARITHMETIC REGISTER FLIP-FLOPS

This module contains four flip-flops, each the ith bit of one of the 36-bit processor registers, AR, MQ, MB, and MI. It also includes AR carry circuits. The module is triple size (in area) and is serviced by four standard 22-pin connectors. Pin designations are two letters, the first naming the connector (A, upper front; B, lower front; R, upper rear; S, lower rear), the second naming the pin. On the processor logic diagrams the front connectors are labeled by mounting panel. The internal -3 vdc supply for this module is derived from four series-connected silicon diodes, loaded to -15 vdc. A tap on the supply load provides -8v for the pulse transformer primary clamp. Three logic diagrams with transistor numbers for all flip-flops in the 6205 module accompany the schematic.

MI flip-flop logic, shown with MB, is considerably simpler than that of the other three, since MI is required only to store a memory bit and drive an indicator circuit. It is set by the 1 state of MB and a negative pulse at SN, through an input pulse inverter Q30. A negative pulse at SR clears the flip-flop through Q1; output point BS includes a series 3K resistor to drive the indicator.

Most of the input circuitry on AR, MB, and MQ consists of inverter networks that implement the many set and clear conditions required by logical, arithmetic, and transfer operations. All pulse inputs to the three flip-flops are bused to the rear connectors (R and S) from the arithmetic Bus Driver 6615, which produces 25-nsec pulses instead of the usual 6000-series 40-nsec pulses. To prevent race problems, flip-flop response time is carefully standardized at manufacture to ensure approximately 50-nsec delay between the input pulse leading edge and the signal response at the flip-flop output buffers. All input level conditioning is performed by the buffers (the basic flip-flop drives only the buffer), consequently input gating conditions cannot change until somewhat after the trailing edge of a pulse that changes the flip-flop state.

Trigger circuits on the 6205 differ from those on other modules: an emitter-driven pnp stage drives both basic flip-flop transistor bases through a pulse transformer. The clear and set triggers for all three flip-flops are identical; e.g., the clear trigger for AR (at the right in the schematic) consists of Q58 with pulse transformer T5. The Q58 base is clamped to -3.7v while its collector is loaded to -15v through the T5 primary. When one of the clear gates (at the top) is pulsed, it pulls the Q58 emitter toward ground so that Q58 saturates, placing approximately 13v across the T5 primary. The LC network at the Q58 collector introduces a short delay which adds to the transition time of input inverters, flip-flop, and output buffers to give the total flip-flop transition time. The T5 secondary simultaneously turns on Q74 through D29 and turns off Q75 through D31. Since both flip-flop transistors are pulsed, the output buffers provide simultaneously changing signals when the flip-flop is triggered.

The basic flip-flops, output buffers, and register clear inputs for AR, MB, and MQ are identical; all are 10-mc types using the push-pull pnp output buffer, and each has additional npn emitter-follower

input triggers that change flip-flop state by shorting the appropriate collector to ground. The emitter-follower pulse inputs at the front connectors are the only inputs that do not use the pulse amplifier trigger circuit described above. Clamped loads are included at the emitter-follower bases for the required external pulse inverters.

The AR circuits include an output pulse amplifier with additional networks for carry output gating and carry completion detection. The pulse amplifier consists of Q64 and pulse transformer T7 in the configuration described at the beginning of this chapter. If AR is 1, it delivers a 25-nsec negative pulse at AF when an input pulse appears at AH. The output is also triggered by a negative pulse at RH, if AR is 0 and MB is 1. These conditions are set up at two transistor AND gates, Q60-Q62, and Q61-Q63. A parallel output at AE is ORed with its counterparts on all other 6205 modules through D59 to detect the carry output; AE is therefore at ground potential only when carry propagation has terminated.

#### 3.14 6206 MA, PC, AND IR FLIP-FLOPS

This module contains three flip-flops, the ith bits of the 18-bit processor registers, PC, MA, and IR. The module is double size and is serviced by a standard 22-pin connector at each end (rear connector pin designations have the prefix R). A tap on the load resistance for the -3 vdc internal supply provides -8v for the primary clamps of two pulse transformers. A logic diagram with transistor numbers is included with the schematic.

The MA flip-flop input circuits consist primarily of inverter networks that implement the memory address transfer logic. The diode comparison gate shown at the bottom of the logic diagram generates an output at K if the state of MA is the same as that of the corresponding memory address switch. Other MA circuits include a count net which complements the flip-flop through a delayed trigger circuit (Q15-Q23) when pulsed at P, and also generates a carry at N if MA contains 1.

The PC flip-flop circuits consist simply of a complement-carry network driving a pulse amplifier similar to that of MA, and a PC set gate. E is the count input for this flip-flop, and F is the carry output.

IR flip-flop circuits consist of a simple direct set network and two pnp-npn push-pull emitter-follower amplifiers (Q1-Q2 and Q10-Q11), one at each flip-flop output.

All 6206 circuits, including buffered and unbuffered flip-flops, npn emitter followers, push-pullemitter-follower amplifier, and pulse amplifier-standardizer, are discussed at the beginning of the chapter.

#### 3.15 6227 EIGHT-BIT BUFFER

This module contains eight 10-mc flip-flops with no interconnections other than a clear line. Two inverters are provided for clearing: one, with input connection at P, clears a minimum of four and

a maximum of seven flip-flops; the inverter driven at R clears a minimum of one and a maximum of four. Clear signals at P and R are negative-going transitions resulting from level changes or DEC standard 40-nsec negative pulses; they are applied through Q17 and Q18 to the bases of the appropriate transistors. Positive-going levels or pulses applied directly to the flip-flop collectors can be used for individual setting and clearing.

Flip-flops with outputs T-S, V-U, and W-X may be cleared through either Q17 or Q18, depending upon internal jumper connections. Jumper identification for this module is therefore a 3-symbol code, one for each ambivalent flip-flop. P or R indicates the input connection; 0 indicates no connection.

# CHAPTER 4 AMPLIFIERS

Amplifier types in the PDP-6 fall into two categories, pulse amplifiers and level amplifiers. The former are used not only to amplify short duration signals but also to shape and standardize them in amplitude and width; circuits for these modules are characterized by toroidal-core transformers, which generate pulses at relatively high currents with very short rise times. The level amplifiers are special-purpose modules usually associated with the in/out system and the memory bus; they function as solenoid, bus, and indicator drivers.

All PDP-6 pulse amplifiers except the Type 4606 operate in either the 5- or 10-mc speed range and must be driven by the collector of an inverter, which may be included on the module. The input to the base of this inverter must be a negative-going signal with an amplitude between 2 and 5v. For all 6000 series modules and for the Type 1609, the fall time of the negative pulse or level change must be less than 25 nsec; duration at 2v must be greater than 25 nsec. The remaining 1000 series modules require a fall time less than 50 nsec and a width greater than 50 nsec at 2v. Delay through a 5- or 10-mc pulse amplifier is approximately 25 nsec. The Type 4606 can be triggered by 2.5-4v level changes or pulses, of either polarity, having a rise (or fall) time less than 0.4 µsec and a duration at 2v greater than 70 nsec. For any PA, pulse amplitudes less than 0.5v cannot result in an output pulse. In general, a pulse amplifier produces output pulses characteristic of its speed line: 0.4 µsec, 70 nsec, and 40 nsec for the 4000, 1000, and 6000 series, respectively.

#### 4.1 BASIC PULSE AMPLIFIER

To avoid repetition, this section describes a basic pulse amplifier that with minor variations forms a part of five modules. The schematic of figure 4-1 shows two input inverter configurations. Normally Q1 drives T1 directly. When Q1 is a high speed transistor (such as the MD94) with a breakdown rating below 8v, but the needed drive power to Q3 requires a -8v clamp at the T1 primary, common base stage Q2 is added to provide voltage standoff to Q1. The Q2 emitter (and Q1 collector) can go no more negative than -4.5v.

Under quiescent conditions, the transistor driving T1 terminal A is cut off so the T1 primary is held to -8 vdc by the D4-R4 clamp. Since no current flows in the T1 secondary at this time, Q3 is open circuited with its base and emitter at ground, and no current flows in the T2 primary. When A is pulled up to ground from its previous -8v level, the T1 primary inductance initially impedes current flow through it and R4 to the -15v supply, while the increasing magnetic field develops a sharp current pulse in the secondary (dots indicate the more positive winding polarities during the pulse). Q3 is immediately saturated

by this pulse, whose current amplitude is approximately proportional to the rate of change of the T1 primary current. As the R3-R4 junction rises toward ground potential, the primary current building toward the steady state maximum (10 ma in this case) proceeds more slowly, with a corresponding decrease in the T1 secondary current and voltage, until conduction through the Q3 base-emitter junction can no longer be maintained and Q3 cuts off. When the ground at A is removed, the reverse current spike generated by the T1 primary is damped out through R3 and D3. In addition to the inductance of the T1 primary and secondary, two other factors are primarily responsible for determining pulse width at the Q3 collector: the silicon  $V_{be}$  of Q3, and the emitter to ground potential established by R6. Increasing R6 decreases the pulse width and reduces T1 secondary current. Transformer T2 provides current amplification of the pulse generated at the Q3 collector. Positive output pulses are available at the T2 secondary when the negative terminal is grounded and vice versa. R5 and D5 damp the T2 primary backswing in the same manner as D3-R3.

Figure 4-1 Basic Fulse Amplifier with Two Typical Driving Circuits

# 4.2 1607 PULSE AMPLIFIER

This module contains three of the basic pulse amplifiers (common-base input circuit) and three input inverters. The amplifiers, Q2-Q3, Q5-Q6, and Q8-Q9, are driven at H, L, and P. Their outputs are available at E-F, J-K, and M-N. Inverters Q1, Q4, and Q7 can be used in series for logic gating or with grounded emitters as individual triggering inputs. The triggering input to an inverter base is usually a DEC 70-nsec negative pulse, but the input requirement is satisfied by any negative transition meeting the specifications cited in the introduction to this chapter. The output generated by this signal is a DEC standard 70-nsec pulse, delayed by 25 nsec and capable of driving 16 units of pulse load.

Each amplifier has a separate 8v supply provided by a low-resistance voltage divider between -3 and -15 vdc (example: R11-R16). Capacitors such as C2 and C4 flatten the pulse top by maintaining a high rate of change of primary current for a longer time.

# 4.3 1608 PULSE AMPLIFIER

The Type 1608 contains two dual-output pulse amplifiers and two input inverters. The amplifiers are the basic type (common-base input circuit) with a duplicated second state. They are Q2-Q3-Q4 and Q6-Q7-Q8, and are driven at K and R. Outputs of the first are available at H-J and E-F; those of the second at N-P and L-M. Inverters Q1 and Q5 can be used in series for logic gating or with grounded emitters as individual triggering inputs. Input and output characteristics and all circuit parameters are identical to those of the Type 1607, except for the dual output stage that allows a single input pulse to produce a pair of output pulses of the same or opposite polarities. Since each pulse amplifier output is an independent transformer winding, transformers may be connected in parallel to increase the driving current, or in series to increase the pulse voltage amplitude for special purposes. Each output can drive 16 units of pulse load.

#### 4.4 1609 PULSE AMPLIFIER

The six pulse amplifiers contained in this module differ from other PDP-6 pulse amplifiers by using feedback networks to transform very short-duration pulses into standard DEC 70-nsec signals. The Type 1609 is therefore useful as an interface between the 1000 and 6000 series. The amplifiers, Q1-Q2, Q3-Q4, Q5-Q6, Q7-Q8, Q9-Q10, and Q11-Q12, are driven at E, J, M, R, U, and X. Their outputs are available at H-F, L-K, P-N, T-S, W-V, and Z-Y. Pulse transformers in this module are referenced through suitable resistors directly to -15 vdc rather than to an intermediate negative supply. The internal -3 vdc source is loaded through 195 ohms to the -15 vdc supply, maintaining approximately 60-ma no-load current through the four series diodes. This relatively high current level reduces transients that occur on the -3v line when inputs are pulsed.

Pulse amplifier inputs must be driven from the collectors of one or more pulse inverters. The signal at the pulse inverter base must have a rise time less than 25 nsec; pulse width (at 2v) may run from 25 nsec up. When these input conditions are met, the output is a DEC standard 2.5v 70-nsec pulse that is negative if the positive terminal is grounded and vice versa. Outputs can drive 10 units of pulse load each and should not be used without terminating resistors. Although resistor values are ultimately dependent upon line length, 47 ohms is approximately correct when driving 1-5 units; 82 ohms is generally used to drive 6-10 units.

Consider the Q1-Q2 circuit as typical. It differs from the basic pulse amplifier in two respects: the T1 and T2 primaries are not clamped to -8 vdc, and the feedback circuit of Q1 has been added. To ensure a 70-nsec output from a pulse source as short as 25 nsec, Q1 is effectively placed in parallel with the driving source. A portion of the pulse amplifier output is fed back to the Q1 base by a separate T2 secondary winding. This signal saturates the transistor, maintaining the ground level at E for 70 nsec, when the circuit constants end the pulse. Capacitors C1 and C2 aid in flattening the output pulse top.

#### 4.5 1664 MEMORY BUS CONTROL

This module contains four gated pulse amplifiers and a 7-input AND gate for positive signals (expandable to 9). It is quadruple size, with four 22-pin connectors, and has been designed specifically for use in the PDP-6 two-way memory bus system. The Type 1664 accepts a DEC standard 70 nsec negative pulse or a level change meeting the requirements for the 1000 series set forth in the beginning of this chapter. Each pulse amplifier output drives the center of a 93-ohm coaxial cable (50 ohms dc to ground) with a 100-nsec negative pulse.