# DATA CONTROL TYPE

# DATA CONTROL TYPE 136 INSTRUCTION MANUAL

COPY NO. 226

This manual contains proprietary information. It is provided to the customers of Digital Equipment Corporation to help them properly use and maintain DEC equipment. Revealing the contents to any person or organization for any other purpose is prohibited.

## CONTENTS

| Section |                                             | Page |

|---------|---------------------------------------------|------|

| 1       | INTRODUCTION AND DESCRIPTION                | 1-1  |

|         | Introduction                                | 1-1  |

|         | Abbreviations                               | 1-1  |

|         | Pertinent Documents                         | 1-2  |

|         | General Description                         | 1-3  |

|         | Purpose of Data Control System              | 1-3  |

|         | Programmed Operations                       | 1-3  |

|         | Logical Organization of Data Control        | 1-5  |

|         | Bidirectional Output and Input              | 1-5  |

|         | System Operating Specifications             | 1-7  |

|         | Physical Characteristics                    | 1-8  |

|         | Power Requirements                          | 1-8  |

| 2       | THEORY OF OPERATION                         | 2-1  |

|         | Processor Interface                         | 2-1  |

|         | Cabling - Processor to Data Control         | 2-1  |

|         | IC Register as Control Interface            | 2-2  |

|         | Device Selection Decoding                   | 2-2  |

|         | Input Signals from Processor                | 2-3  |

|         | Priority Interrupt Request Lines            | 2-4  |

|         | Data Buffer and Data Accumulator            | 2-4  |

|         | Data Buffer (DCDB)                          | 2-5  |

|         | Data Accumulator (DCDA)                     | 2-6  |

|         | Control Status Register (DCIC)              | 2-9  |

|         | Character Counter IC20-22 and Shift Counter | 2-9  |

|         | Error Bit IC23                              | 2-11 |

|         | Data Control Status Bits IC24-26            | 2-12 |

|         | Input/Output Flip-flop IC27                 | 2-13 |

|         | Character Mode Bits IC28-29                 | 2-14 |

|         | Internal Device Address IC30-32             | 2-14 |

# CONTENTS (continued)

| Section |                                            | Page |

|---------|--------------------------------------------|------|

|         | Priority Interrupt Assignment Bits IC33-35 | 2-14 |

|         | Device Interface                           | 2-13 |

|         | Cabling - Data Control to I/O Devices      | 2-13 |

|         | Data Control Outputs to I/O Devices        | 2-15 |

|         | Inputs to Data Control from I/O Devices    | 2-16 |

|         | Resulting Internal Command Pulses          | 2-19 |

|         | Output Cycle                               | 2-23 |

|         | CONO Out Instruction                       | 2-24 |

|         | First DATAO Instruction                    | 2-25 |

|         | Second DATAO Instruction                   | 2-28 |

|         | Output Transfer Sequence                   | 2-30 |

|         | Input Cycle                                | 2-31 |

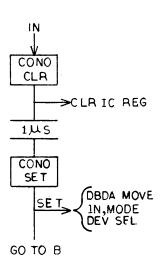

|         | Input Cycle CONO Instruction               | 2-31 |

|         | First Readin Sequence                      | 2-32 |

|         | Completion of First Readin Sequence        | 2-32 |

|         | Second Readin Sequence                     | 2-32 |

|         | Completion of Second Readin Sequence       | 2-32 |

|         | First DATAI Instruction                    | 2-33 |

|         | Subsequent Operations                      | 2-33 |

| 3       | INSTALLATION                               | 3-1  |

|         | Site Selection                             | 3-1  |

|         | Unpacking                                  | 3-1  |

|         | Inspection                                 | 3-2  |

|         | Cable Connections                          | 3-2  |

|         | Preoperational Checkout                    | 3-3  |

| 4       | OPERATING PROCEDURES AND PROGRAMMING       | 4-1  |

|         | Controls and Indicators                    | 4-1  |

# CONTENTS (continued)

| Section  |                                                | Page |

|----------|------------------------------------------------|------|

|          | Controls                                       | 4-1  |

|          | Indicators                                     | 4-3  |

|          | Processor Instruction Coding                   | 4-3  |

|          | Sample Programs                                | 4-4  |

|          | Use of Data Control Without Priority Interrupt | 4-4  |

|          | Use of Data Control With Priority Interrupt    | 4-5  |

| 5        | MAINTENANCE                                    | 5-1  |

|          | Use of Drawings                                | 5-1  |

|          | Equipment Layout                               | 5-1  |

|          | Preventive Maintenance                         | 5-2  |

|          | Recommended Spare Parts                        | 5-2  |

|          | Module Spares                                  | 5-2  |

|          | Component Spares                               | 5-3  |

|          | Mechanical Spares                              | 5-4  |

| Appendix |                                                |      |

| Al       | FOLDOUT TABLES                                 | A1-1 |

| A2       | ENGINEERING DRAWINGS                           | A2-1 |

|          |                                                |      |

|          | ILLUSTRATIONS                                  |      |

| Figure   |                                                |      |

| 1-1      | System Application                             | 1-4  |

| 1-2      | Logical Organization of Type 136 Data Control  | 1-6  |

|          |                                                |      |

|          | TABLES                                         |      |

| Table    |                                                |      |

| 4-1      | Front Panel Indicator Lamps                    | 4-3  |

|          |                                                |      |

# ENGINEERING DRAWINGS

| Drawing         |                                                 | Page  |

|-----------------|-------------------------------------------------|-------|

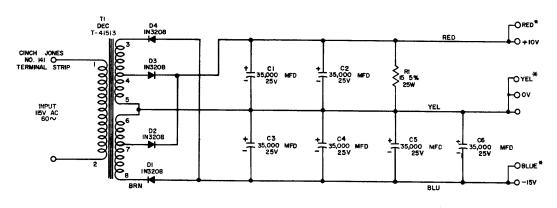

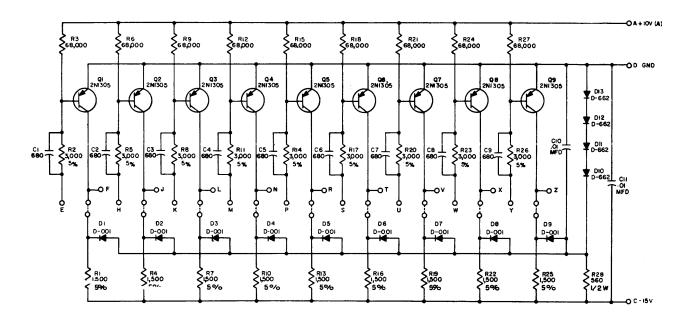

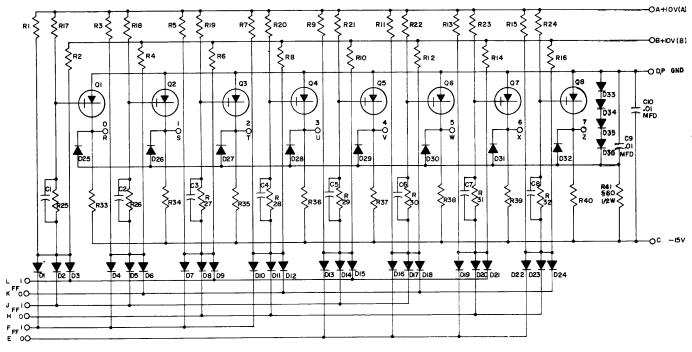

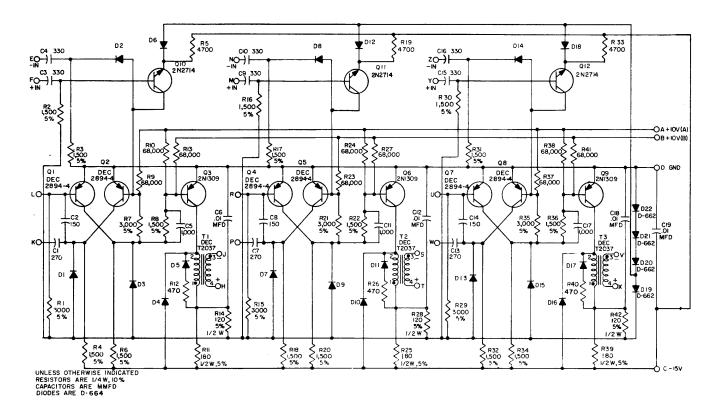

| RS-728          | Power Supply                                    | A2-6  |

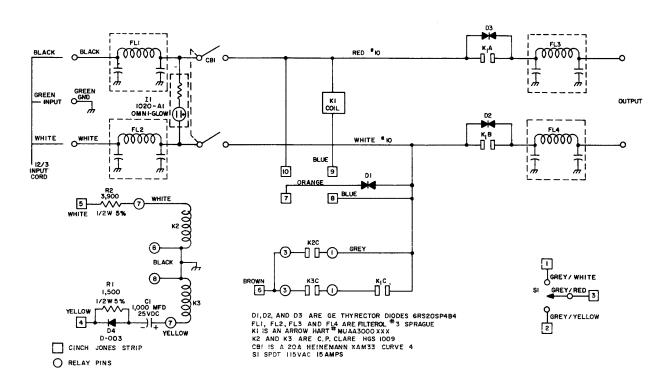

| RS-811          | Power Control                                   | A2-6  |

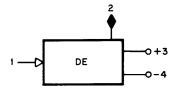

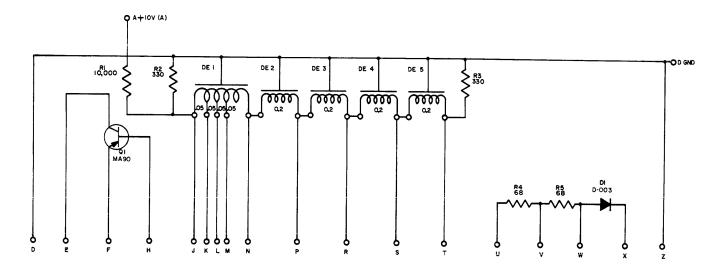

| RS-1310         | Delay Line                                      | A2-7  |

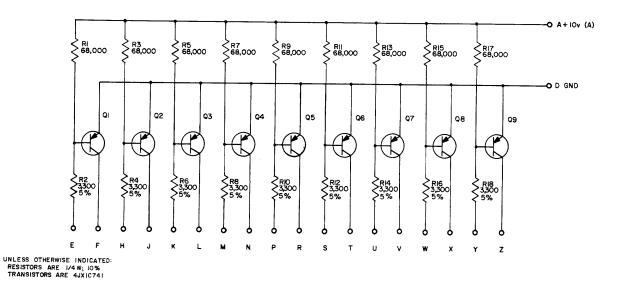

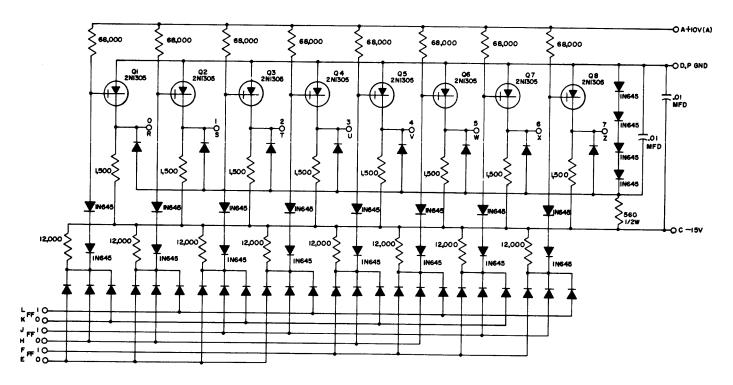

| RS-1669         | Indicator Driver                                | A2-7  |

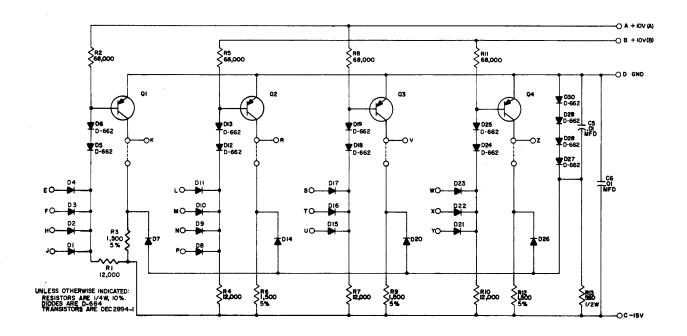

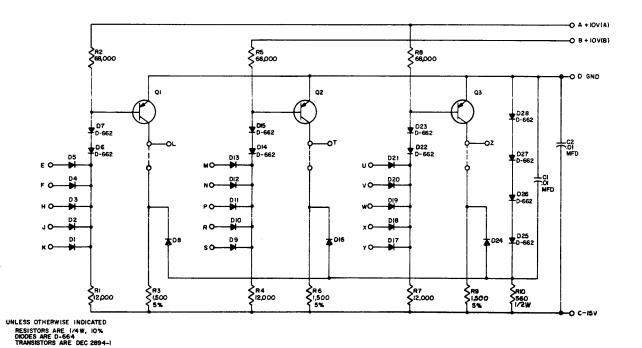

| RS-4102         | Inverter                                        | A2-8  |

| CS-4112         | Diode                                           | A2-8  |

| RS-4113         | Diode                                           | A2-9  |

| RS-4118         | Diode Gate                                      | A2-9  |

| RS-4127         | Capacitor Diode Inverter                        | A2-10 |

| RS-4129         | Capacitor Diode Inverter                        | A2-10 |

| RS-4143         | Diode Unit                                      | A2-11 |

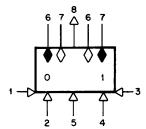

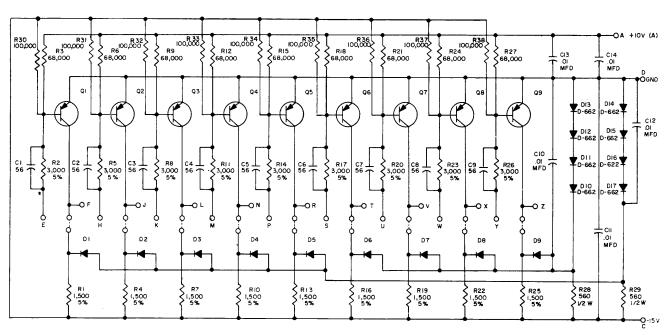

| RS-4150         | Binary-to-Octal Decoder                         | A2-11 |

| RS-4151         | Binary-to-Octal Decoder                         | A2-12 |

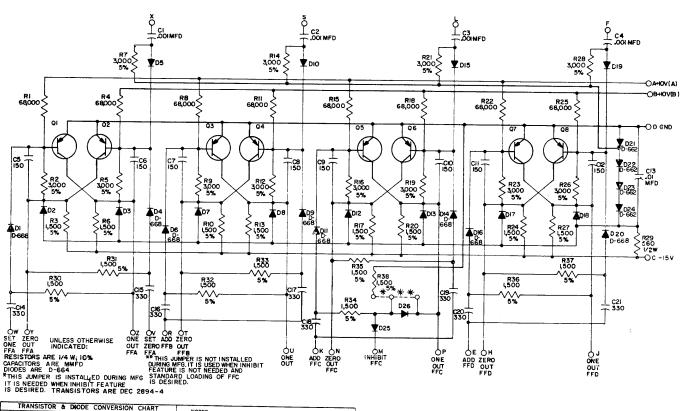

| RS-4215         | Four-Bit Counter                                | A2-12 |

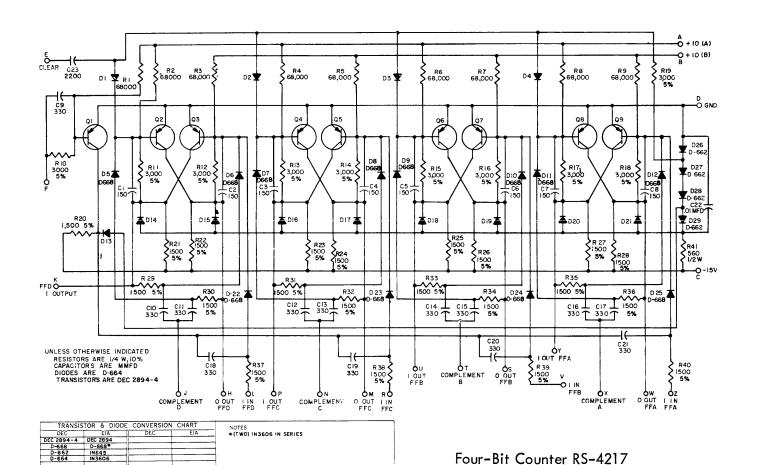

| RS-4217         | Four-Bit Counter                                | A2-13 |

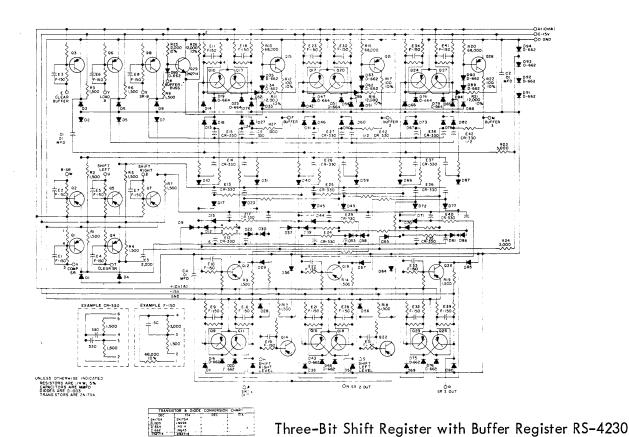

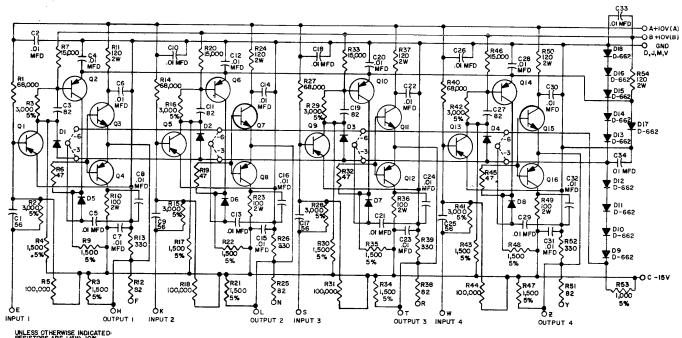

| RS-4230         | Three-Bit Shift Register with Buffer Register   | A2-13 |

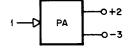

| RS-4604         | Pulse Amplifier                                 | A2-14 |

| RS-4606         | Pulse Amplifier                                 | A2-14 |

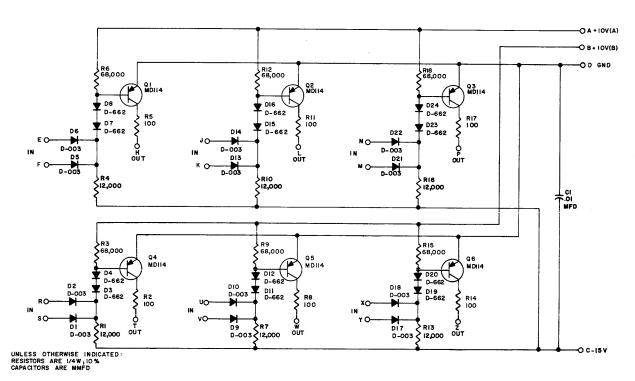

| RS-4657         | I/O Bus Driver                                  | A2-15 |

| RS-6102         | Inverter                                        | A2-15 |

| RS-6115         | Diode                                           | A2-16 |

| RS-6117         | Diode                                           | A2-16 |

| RS-6684         | Bus Driver                                      | A2-17 |

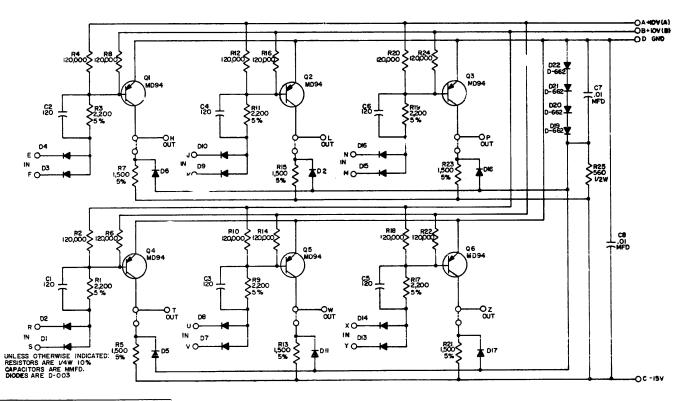

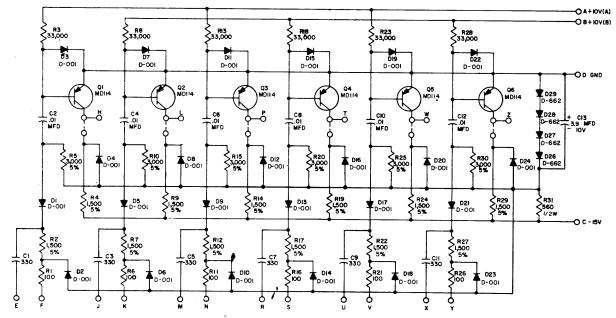

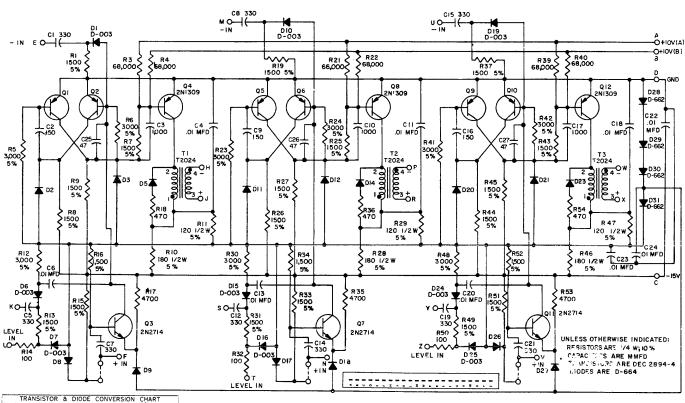

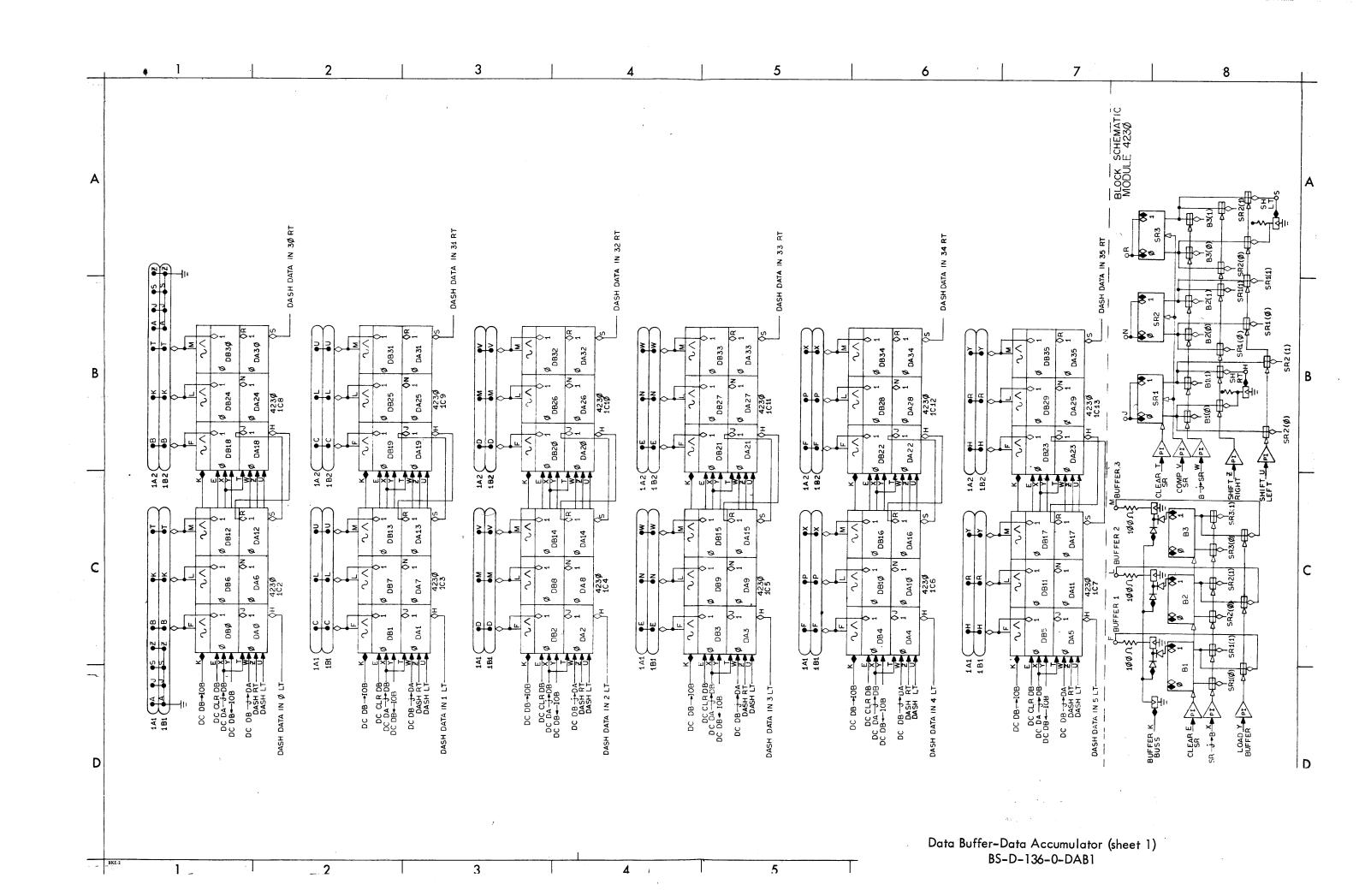

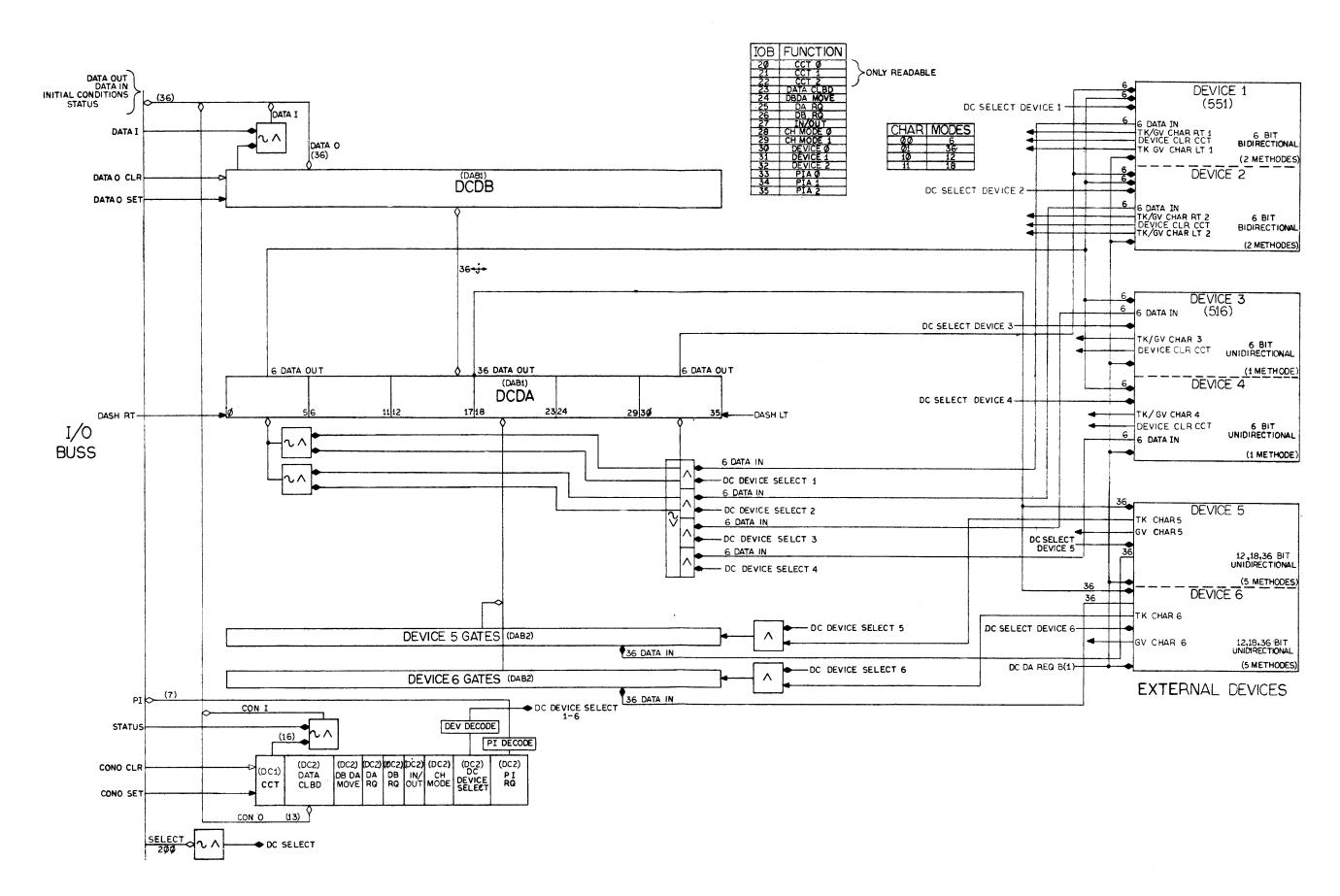

| BS-D-136-0-DAB1 | Data Buffer-Data Accumulator (sheet 1)          | A2-19 |

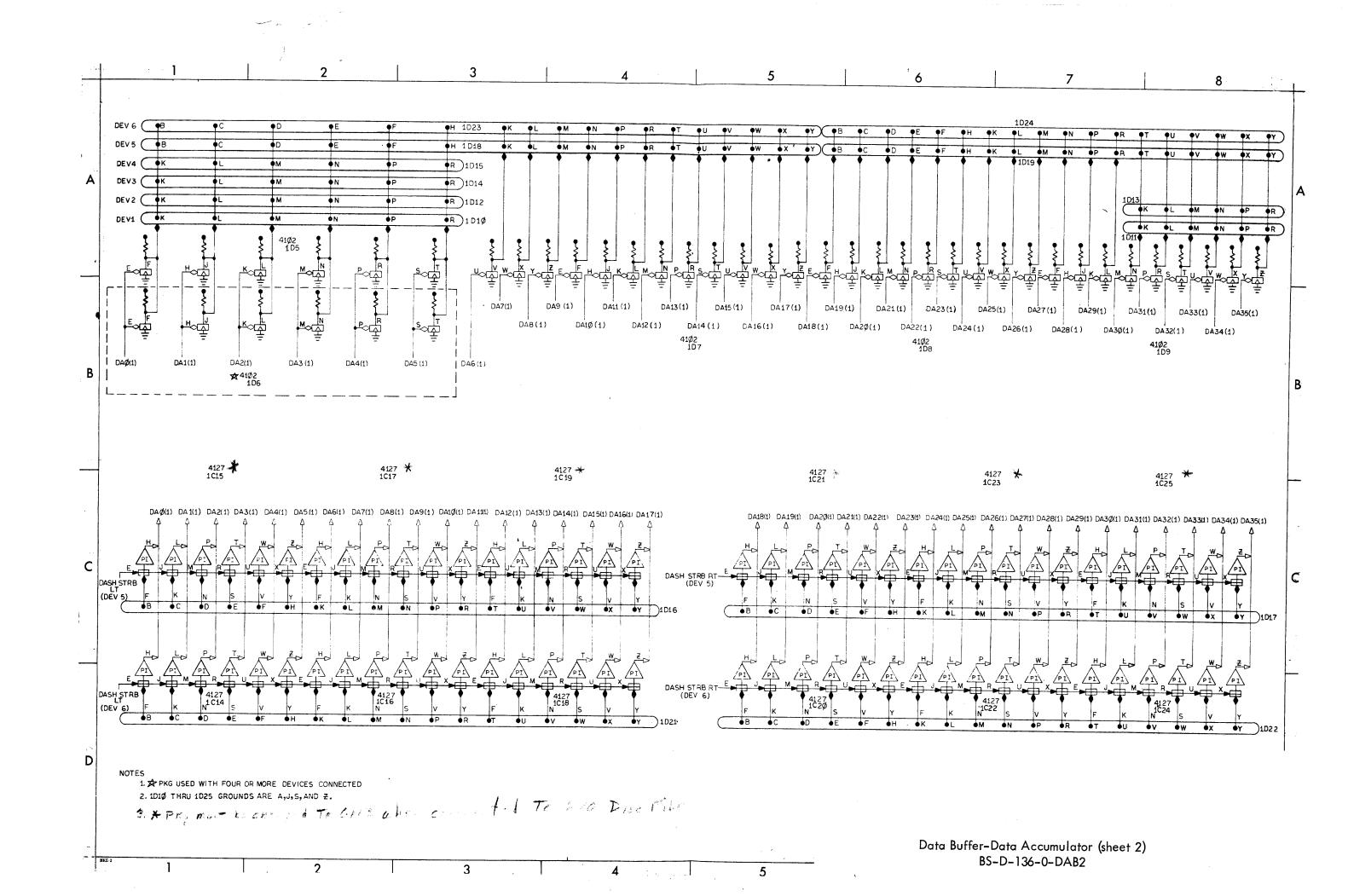

| BS-D-136-0-DAB2 | Data Buffer-Data Accumulator (sheet 2)          | A2-21 |

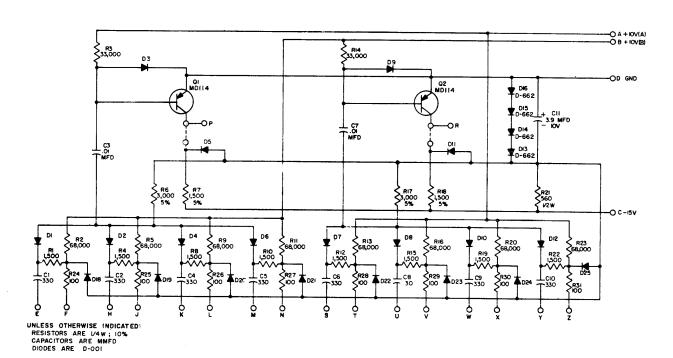

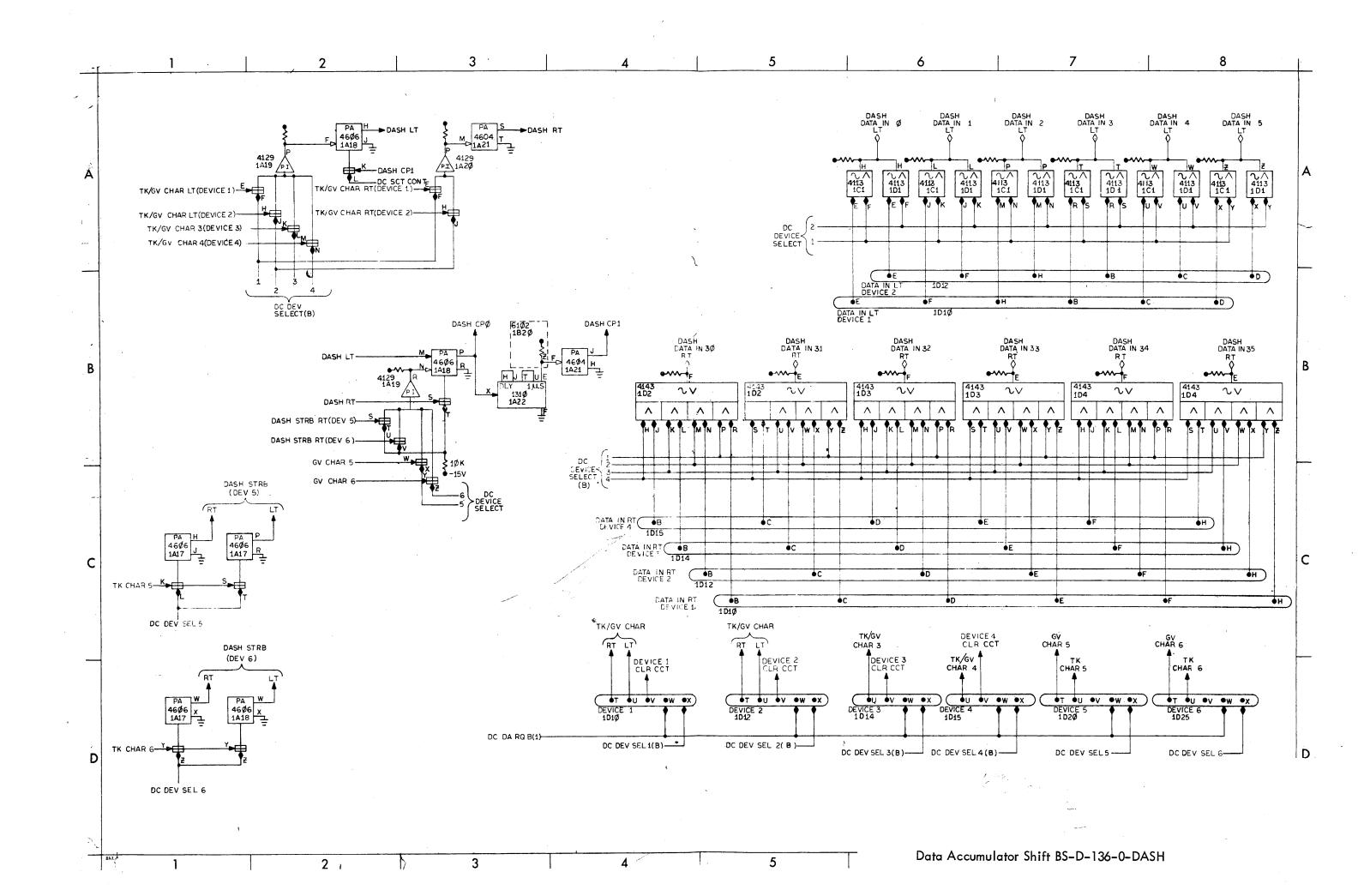

| BS-D-136-0-DASH | Data Accumulator Shift                          | A2-23 |

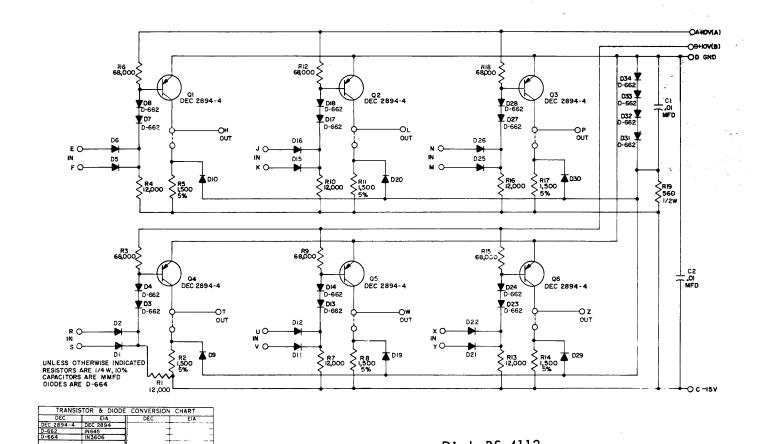

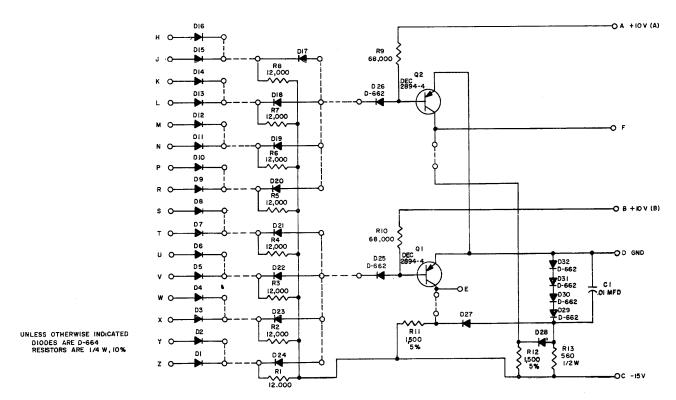

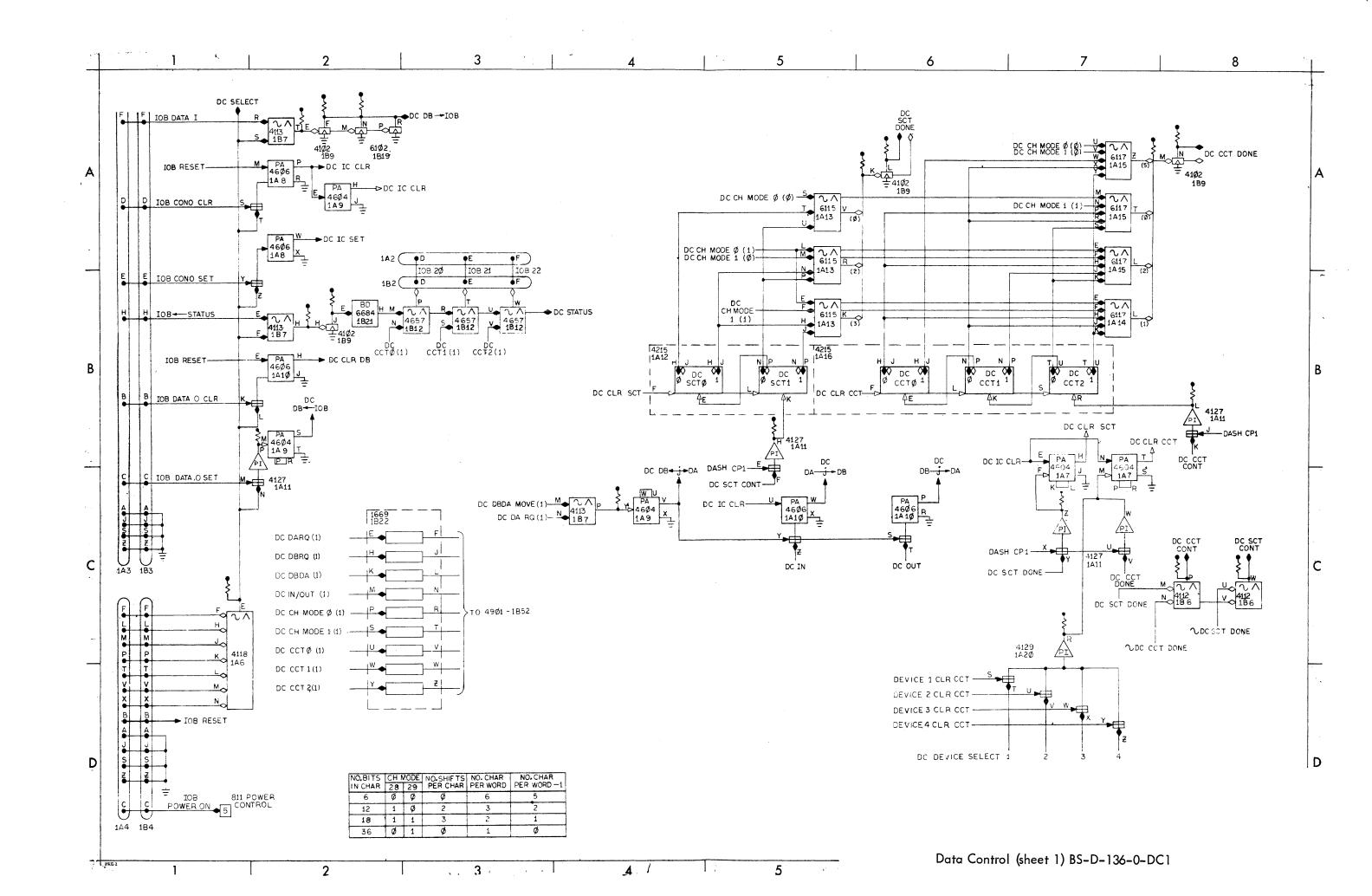

| BS-D-136-0-DC1  | Data Control (sheet 1)                          | A2-25 |

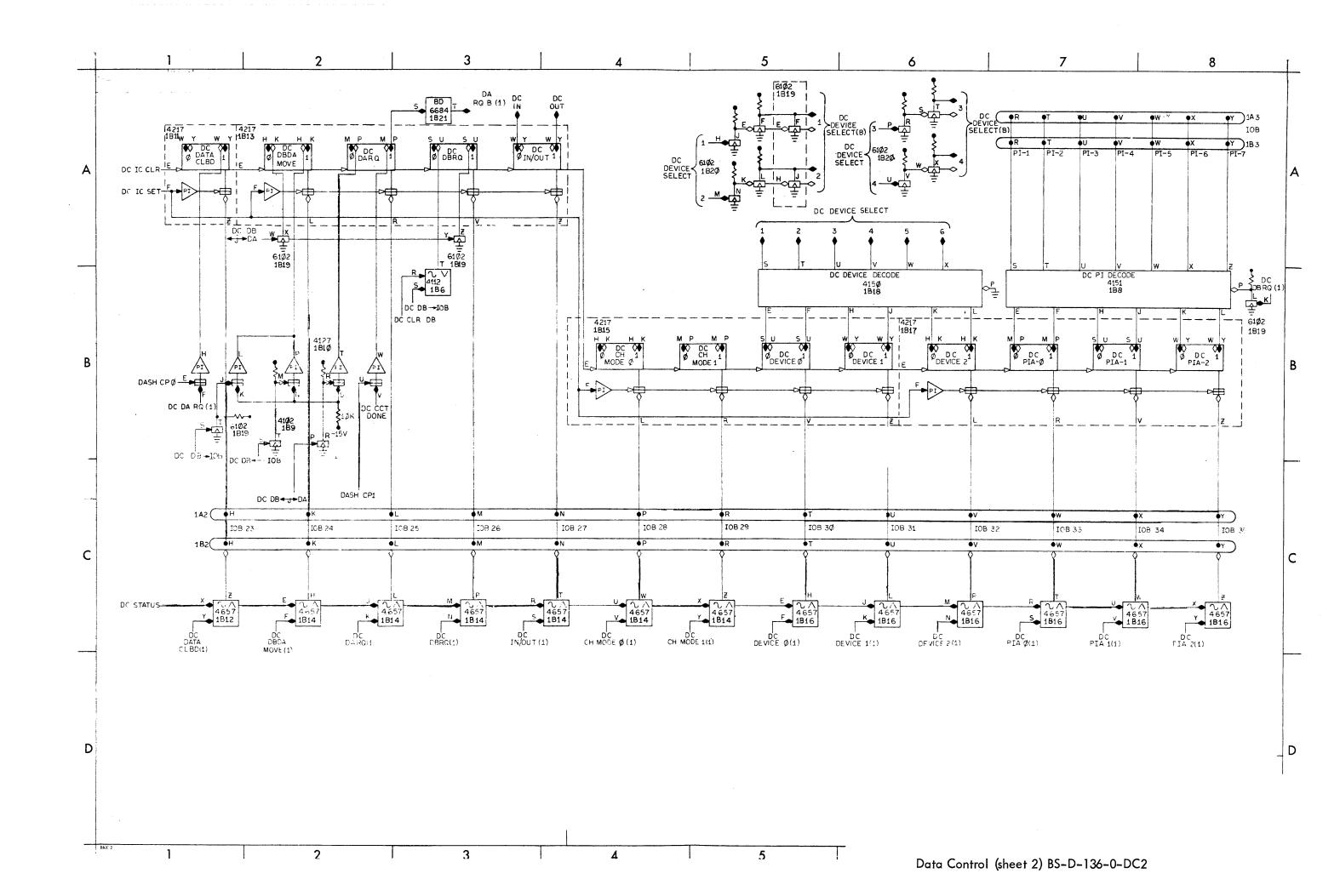

| BS-D-136-0-DC2  | Data Control (sheet 2)                          | A2-27 |

| CD-D-166-0-IOMB | Methode Plug Connections at Processor Interface | A2-29 |

# ENGINEERING DRAWINGS (continued)

| Drawing          |                                                | Page  |

|------------------|------------------------------------------------|-------|

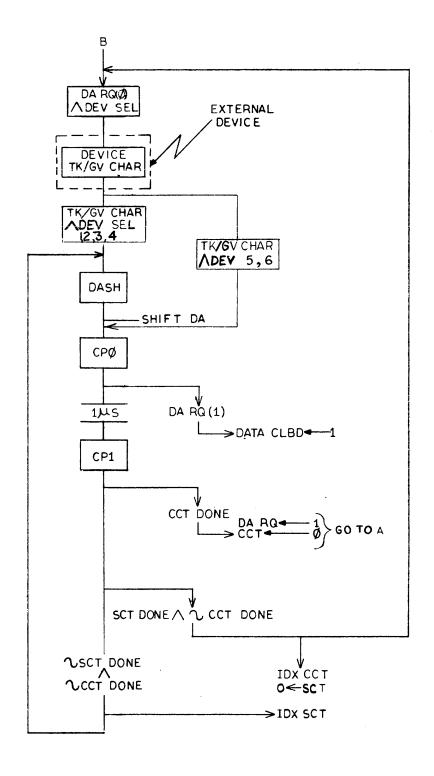

| FD-D-136-0-FD1   | Flow Diagram                                   | A2-31 |

| ID-D-136-0-EDC   | External Device Connections                    | A2-33 |

| SD-D-136-0-DCSD  | Data Control System Diagram                    | A2-35 |

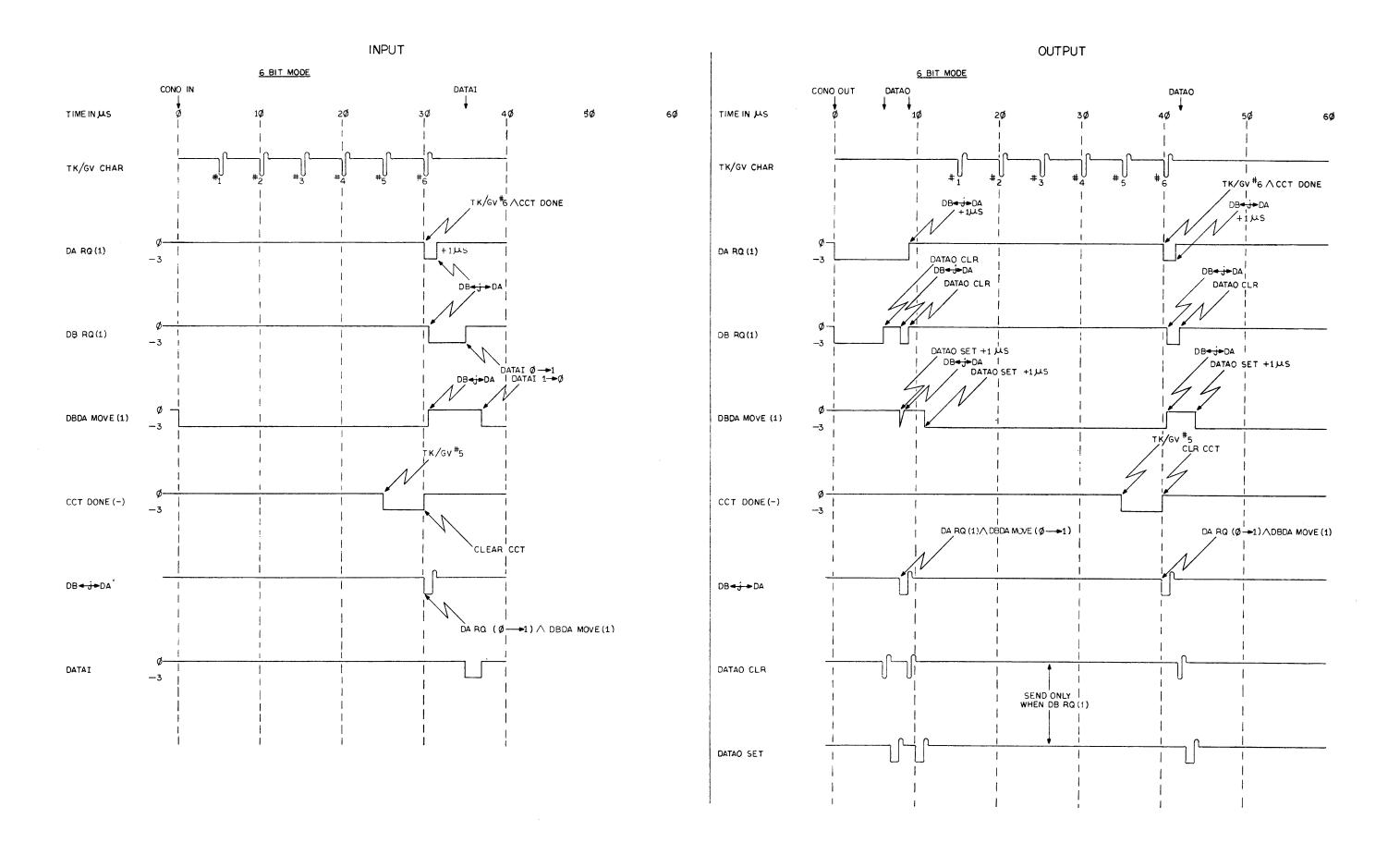

| TD-D-136-0-TD1   | Timing Diagram                                 | A2-37 |

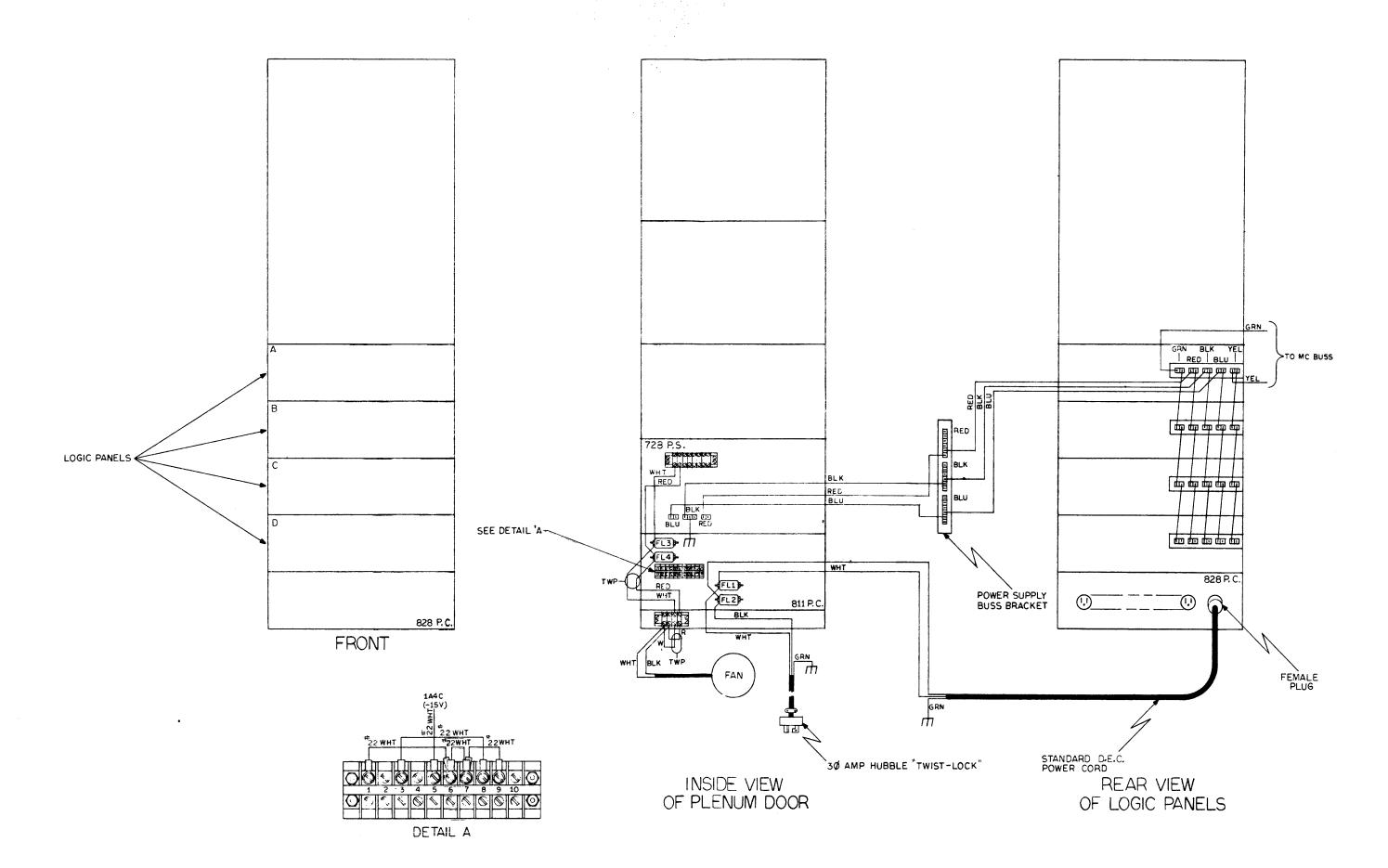

| PW-D-136-0-DCPW  | Data Control Power Wiring                      | A2-39 |

| UML-D-136-0-DCML | Utilization Module List (sheet 1)              | A2-41 |

| UML-D-136-0-DCML | Utilization Module List (sheet 2)              | A2-43 |

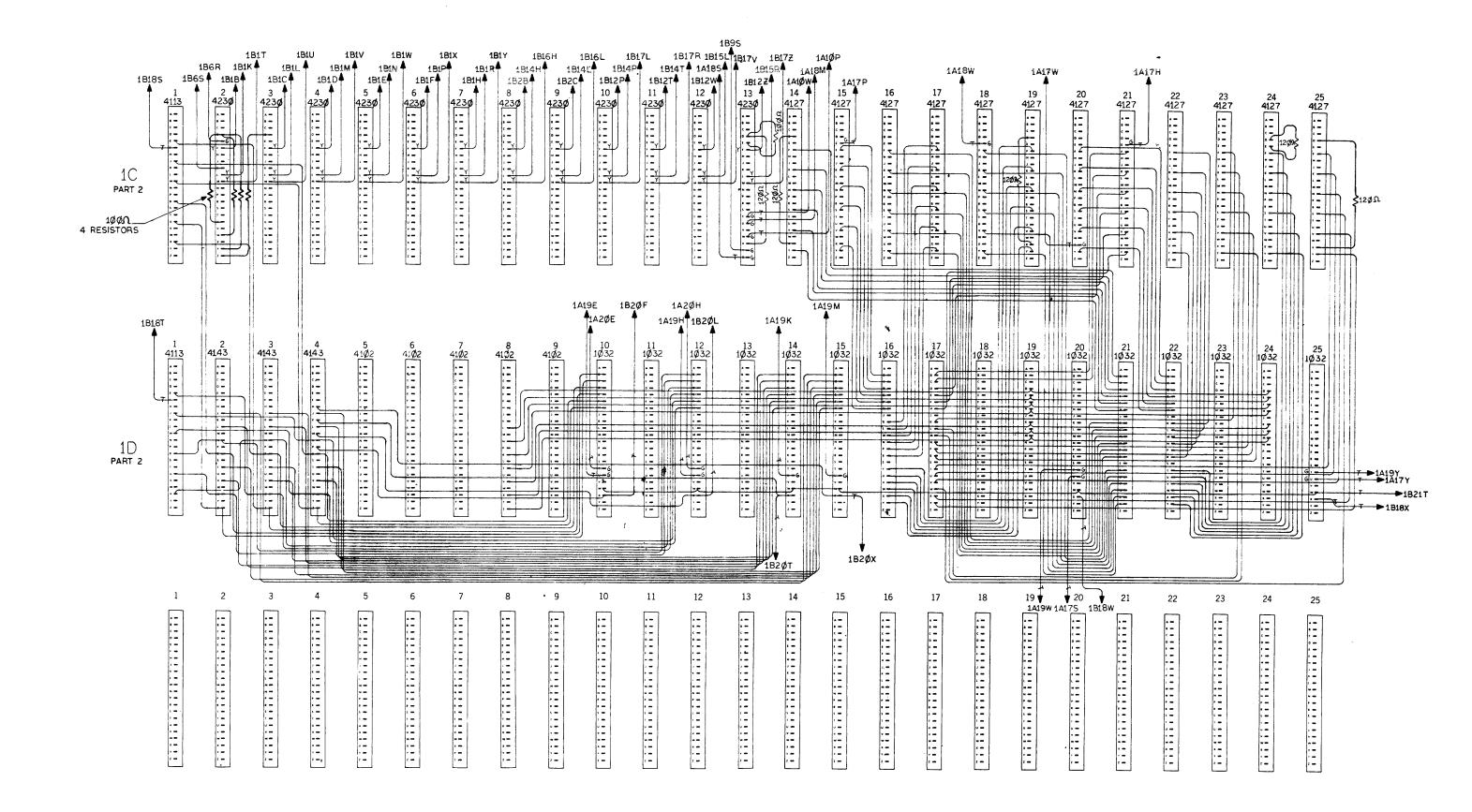

| WD-D-136-1-DAB1  | Data Buffer and Data Accumulator Racks C and D | Δ2_15 |

#### SECTION 1

#### INTRODUCTION AND DESCRIPTION

#### INTRODUCTION

The purpose of this instruction manual is to aid personnel in the installation, operation, and maintenance of the DEC Data Control Type 136.

Anyone who wishes to learn the details of the system logic can save considerable time by first noting the conventions used on the engineering drawings. These conventions are explained in Appendix 2. It is recommended that this section of the manual be scanned before reading Section 2.

#### **Abbreviations**

The following abbreviations are used throughout this manual.

CCT Character Counter

C(DA) Contents of Data Accumulator

CHAR Character

CLBD Clobbered

CLR Clear

CONI Condition In

CONO Condition Out

CP0, CP1 Command Pulse 0, 1

DA Data Accumulator

DASH Data Accumulator Shift

DATAI Data In

DATAO Data Out

DB Data Buffer

DC Data Control

DEC Digital Equipment Corporation

DEV Device

| GV   | Give                                                            |

|------|-----------------------------------------------------------------|

| IC   | Control Status Register (IC is mnemonic for Initial Conditions) |

| 1/0  | Input/Output                                                    |

| IOB  | Input/Output Bus                                                |

| IOS  | Input/Output Selection                                          |

| IOT  | Input/Output Transfer                                           |

| IR   | Instruction Register                                            |

| LT   | Left                                                            |

| MCV  | Marginal Check Voltage                                          |

| PA   | Pulse Amplifier                                                 |

| PI   | Priority Interrupt                                              |

| PIA  | Priority Assignment                                             |

| PDP  | Programmed Data Processor                                       |

| RQ   | Request                                                         |

| RT   | Right                                                           |

| SCT  | Shift Counter                                                   |

| STRB | Strobe                                                          |

| TK   | Take                                                            |

|      |                                                                 |

#### Pertinent Documents

The following publications serve as source material and complement the information in this manual.

<u>Programmed Data Processor-6 Handbook, F-65</u> – contains programming information for the Data Control Type 136.

System Modules Catalog, C-100 - describes the functional operation of the elements of the various logical modules comprising the data control. It is suggested that this handbook be referenced when reviewing the data control logic diagrams in Appendix 2 of this manual.

PDP-6 Installation Manual, F-68 - gives environmental, power, and cabling requirements as well as other information for installation of the 136 Data Control in a PDP-6 system.

PDP-6 Maintenance Manual, F-67 - covers topics not repeated in this manual which are essential to efficient maintenance of the data control when used with the PDP-6.

#### GENERAL DESCRIPTION

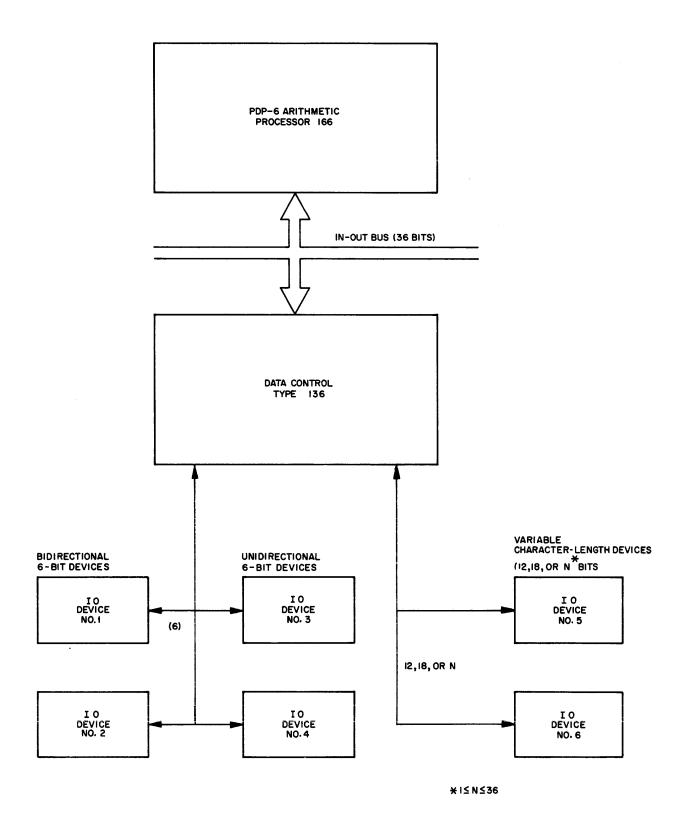

The Data Control Type 136 is a programmable buffer unit through which the PDP-6 Processor can control up to six input-output devices (Figure 1-1). Of the six I/O devices, two are unidirectional 6-bit devices, two are bidirectional 6-bit devices, and two are variable character-length devices. The variable character-length devices can handle data words composed of three 12-bit characters, two 18-bit characters, or one n-bit character where n can be any integer from 1 to 36.

#### Purpose of Data Control System

Besides saving processor time by matching the format and timing requirements of the various asynchronous I/O devices to the PDP-6 processor, the data control also frees the processor from the necessity of exercising detailed program control over the micro-operations required for the various in-out transfers. Because most of the required sub-operations are built into the data control logic, the programmer need not be concerned with the detailed byte manipulations required by the various I/O devices. The CONO DATA CONTROL instruction need only specify the device to be used, the number of bits per character, and whether an output or input operation is to be performed.

#### **Programmed Operations**

The details of data control programming are described in Section 4; the present paragraph briefly lists the primary variables of data control operations which are controlled by a CONO DATA CONTROL instruction in the processor program.

#### **Device Selection**

A 3-bit field of the CONO-instruction effective address specifies to which of the six possible I/O devices a given output or input sequence is to apply.

Figure 1-1 System Application

#### Input/Output

A single bit of the CONO-instruction effective address determines whether the data control is to treat the operations that follow as an output or input sequence.

#### Character Mode

A 2-bit field of the CONO-instruction effective address determines whether the data control is to transfer out (or read in) characters of 6, 12, 18, or n bits. Once the character mode has been specified, the built-in logic of the data control internally programs the requisite number of data shifts.

#### Priority Interrupt Assignment

A 3-bit field of the CONO-instruction effective address can assign a priority interrupt request channel to the data control. If such assignment is made, a PI channel can be chosen at any of seven ranked priority levels. This permits the data control to request a priority interrupt break with the Arithmetic Processor Type 166.

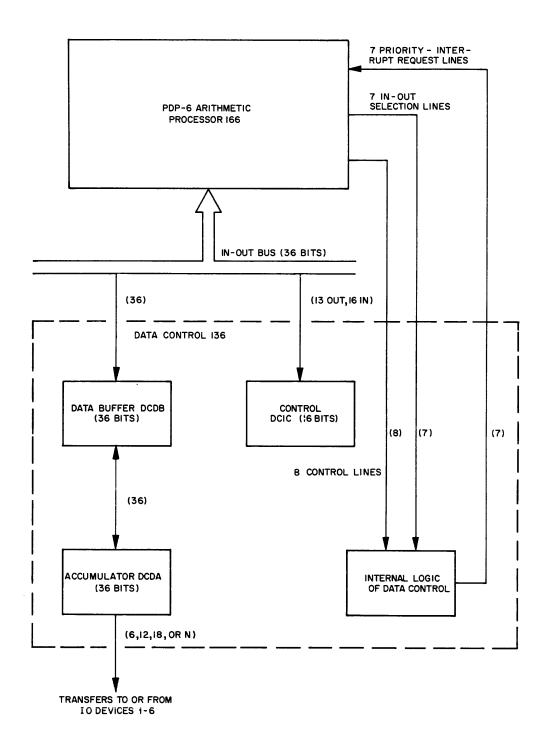

#### Logical Organization of Data Control

The data control contains a 16-bit control-status register called IC (Initial Conditions) and two 36-bit data registers, the data accumulator DA, and the data buffer DB (Figure 1-2). The internal logic of the data control governs the transfer of data through these registers and between them, the processor, and the I/O devices.

The data control internal logic is controlled by signals from two sources: the processor, and the IC register of the data control itself. Eight control inputs are sent to the data control from the processor (See Input Signals from Processor in Section 2). During CONI DATA CONTROL instructions, the processor can sample the contents of all 16 IC bits (see Figure 1-2).

#### Bidirectional Output and Input

The capability for both left and right data shifts is built into the data accumulator, DA. This enables the data control to operate with bidirectional input-output devices for example, DECtape (formerly Microtape) Control 551 and DECtape Transport 555. Because the direction of tape

Figure 1-2 Logical Organization of Type 136 Data Control

motion determines the sequence of data bytes within a data word, the data control's bidirectional accumulator is a particularly useful feature. Depending on the current direction of tape motion, bytes can be shifted in or out from either end of the DA. The bidirectional accumulator permits correctly ordered data words to be read or written immediately while the DECtape moves in either direction. This frees the processor program from the necessity of reshuffling the bytes within a data word to remedy an inversion.

#### System Operating Specifications

APPLICATION

PDP-6 Input-Output Buffer

| APPLICATION                                                                                                                                                                                                                   | PDP-0 Input-Output butter                                                                                                 |                                                                                    |                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------|

| TIMING                                                                                                                                                                                                                        | Asynchronous                                                                                                              |                                                                                    |                             |

| INPUT-OUTPUT DEVICES                                                                                                                                                                                                          |                                                                                                                           |                                                                                    |                             |

| Number of Devices Controlled Unidirectional 6-Bit Devices Bidirectional 6-Bit Devices Variable Character Length Devices Character Modes Available (Variable Character Length Devices Only) Character Modes Available (cont'd) | 1-6 0-2 0-2 0-2 Three 12-bit characters per word  Two 18-bit characters per word One n-bit character per word  1 < n < 36 |                                                                                    |                             |

| BUFFER STORAGE                                                                                                                                                                                                                |                                                                                                                           |                                                                                    |                             |

| Media<br>Quantity                                                                                                                                                                                                             | 500 kc flip-flops<br>Two 36-bit registers (one a bidirectional<br>shift register)                                         |                                                                                    |                             |

| STATUS-CONTROL REGISTER                                                                                                                                                                                                       | 16 bits, 13 programmable                                                                                                  |                                                                                    |                             |

| MAXIMUM DATA RATE OF DATA CONTROL LOGIC                                                                                                                                                                                       | Character<br>Mode                                                                                                         | Minimum<br>Interval Between<br>Characters                                          | Characters<br>per<br>Second |

| (Ordinarily not relevant. System speed normally limited by I/O device data rate.)  PROGRAMMABLE FUNCTIONS                                                                                                                     | Selection of ch                                                                                                           | 3 µsec<br>4 µsec<br>5 µsec<br>3 µsec<br>O device from up to<br>aracter mode from f |                             |

|                                                                                                                                                                                                                               |                                                                                                                           | out or output mode<br>fority interrupt requ                                        | est channel                 |

**ERROR BIT**

One lost-data flag (described in Section 2)

PRIORITY INTERRUPT CHANNELS

7 ranked channels available. Any one, or

none, may be used

#### Physical Characteristics

CONSTRUCTION One standard all steel construction DEC cabinet,

containing four logic racks

MODULES Standard DEC system plug-in units, series 1000,

4000, and 6000

POWER EQUIPMENT Power Supply unit 728; Power Control unit 811

LOGIC Solid-state. Transistors and crystal diodes utiliz-

ing static logic levels (0 vdc and -3 vdc)

**DIMENSIONS**

Height

69-1/2 inches

Width

22-1/4 inches

Depth

27-1/8 inches

**CLEARANCE**

Front Doors 8-3/4 inches

Rear Door 14-7/8 inches

WEIGHT 73 pounds

#### Power Requirements

LINE VOLTAGE INPUT 105 to 125 volts, 60 cycle, single phase

Power plug - Hubble Twist-Loc 3-prong,

30-ampere, 250-volt

CURRENT CONSUMPTION 5 amperes surge 30 amperes normal

POWER CONSUMPTION 345 Watts

HEAT DISSIPATION 1175 BTU per hour

#### SECTION 2

#### THEORY OF OPERATION

Tables A1-1 through A1-6 are referenced throughout this and subsequent sections. These tables are contained in Appendix 1 on foldout pages.

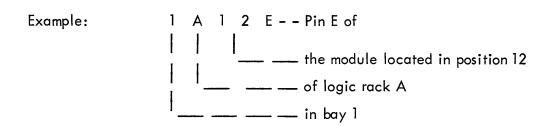

Engineering drawings pertinent to the 136 Data Control are also referred to in this chapter. They are included in Appendix 2 and listed in the table of contents. The entire engineering drawing number is given with each reference so that either the reduced drawings in Appendix 2 of this manual or those that were supplied with the equipment may be consulted. Each block schematic number is followed by a comma and letters and/or numbers which refer to zones on the drawing. See Appendix 2 for an explanation on DEC logic symbols and codes.

#### PROCESSOR INTERFACE

These paragraphs describe the interchange of data and control information between the PDP-6 and the data control.

#### Cabling - Processor to Data Control

There are four 18-conductor cables from the PDP-6 processor to the I/O control units. Each cable is wired to two 22-terminal Methode plugs connected in parallel. The remaining four terminals, A, J, S, and Z, are used for grounding the shielding of the 18 conductors. Two of the four 18-conductor cables from the processor comprise the 36-bit I/O bus. These two cables are connected to Methode plugs 1A1-1B1 and 1A2-1B2 respectively. The 18 more significant data bits IOB0-17 enter the data control through Methode plugs 1A1-1B1. Methode plugs 1A2-1B2 receive the remaining 18 data bits IOB18-35 and also (via bus lines IOB20-35) the 16 IC control register bits IC20-35.

The remaining two 18-conductor cables between the processor and the data control are used for control information. One of these two cables is connected to Methode plugs 1A4-1B4. This cable carries the 14 IOS selection lines (described below under Device Selection Decoding) as well as the two ungated input signals, POWER ON and IOB RESET.

The second 18-conductor control cable enters through Methode plugs 1A3-1B3. This cable carries the six gated command signal inputs from the processor to the data control (IOB CONO SET, IOB CONO CLEAR, IOB DATAO SET, IOB DATAO CLEAR, IOB STATUS, and IOB DATAI; all described under Input Signals from Processor). The same cable also includes the seven priority interrupt request lines from the data control to the processor.

The specific terminal assignments of all four of the 18-conductor cables connected to Methode plugs 1A1-1A4 are listed in engineering drawing CD-D-166-0-IOMB in Appendix 2.

#### IC Register as Control Interface

The 16-bit control-status register, IC, is the principal interface for the exchange of control information between the processor and the data control. Most of the processor control information that governs the data control operation is transferred through the I/O bus and stored in the IC register. During the CONO instruction the processor determines the state of 13 of the 16 IC bits. The resulting state of IC determines the operations carried out by the data control logic during subsequent output or input instructions.

The IC register also serves to store control information moving in the opposite direction – from the data control to the processor. Since the processor samples the contents of all 16 IC bits with a CONI instruction, the state of DB RQ, status bit number 26, can readily be used to synchronize processor operations to appropriate phases of the data control output or input sequence. In a similar manner DA RQ, status bit number 25, synchronizes the operations of the I/O devices to the data control output or input sequence (see Table A1-1).

#### Device Selection Decoding

The device selection code portion of the IOT instructions determines which I/O device is to be utilized by a given instruction. The command levels produced by the IOT instruction must actuate only the selected I/O device, and must not be allowed to affect other non-selected devices. The gating function is performed by the device selection levels. These levels are applied to the data control and other I/O devices through the I/O selection lines.

The 14 I/O selection lines IOS3-9 represent both states of the seven bits of the device code contained in bits 3-9 of the processor instruction register, IR. (Assertion is at ground.) Seven

of the 14 IOS lines, one from each bit in IR3-9, are applied to an IOS decoder in the data control. The specific input connections made determine the selection code for a given data control unit. The decoder is shown in Appendix 2 in system block diagram SD-D-136-0-DCSD, D1, and in drawing BS-D-136-0-DC1, C-D1. The first data control incorporated in the PDP-6 installation is assigned the device selection code 200 octal.

#### Input Signals from Processor

Various input levels and pulses are applied to the data control by the processor. These include two ungated signals (not associated with any IOT instruction and applied to all I/O devices and control units), and six gated command signals applied only to the specific unit specified by the device selection code of the current IOT instruction.

#### **Ungated Signals**

There are two ungated input signals, the POWER ON level, and the IOB RESET pulse (see column 1, BS-D-136-0-DC1.

<u>POWER ON</u> - The POWER ON line drops to -15 vdc whenever computer power is turned on. This line is connected to the remote terminal of the LOCAL/REMOTE switch on the power control for each device. Normally, the LOCAL/REMOTE switches are left in the REMOTE position, so that the -15 vdc POWER ON level causes all peripheral equipment to be turned on when computer power is turned on.

<u>IOB RESET</u> - This line supplies negative pulses to clear the control registers and data buffers of all equipment attached to the I/O bus. The IOB RESET pulse is generated when computer power goes on or when the operator presses the I/O RESET key on the computer console.

#### Gated Command Signals

The six command lines are applied to the data control through Methode plugs 1A3-1B3 (drawing BS-D-136-0-DC1, column 1). These lines are connected to all control units, but are gated by the selection level from the IOS decoder so that they can affect only the control unit for the addressed device. The six command lines carry four output command pulses and two input command levels.

Output Command Pulses - There are two pairs of negative command pulses which implement the basic output instructions. Each of these two pairs includes a clear pulse followed by a set pulse.

The CONO instruction (see Section 4) produces an IOB CONO CLEAR pulse followed 1  $\mu$ sec later by an IOB CONO SET pulse. The principal function of the CONO CLEAR is to clear the data control IC register and shift counter. The CONO SET then loads the 13 low order IC register bits from the I/O bus. The processor places information on the bus for 2.5  $\mu$ sec. The clear occurs at the 1  $\mu$ sec point; the set occurs at the 2  $\mu$ sec point.

Similarly, the DATAO instruction (see Section 4) produces an IOB DATAO CLEAR pulse followed 1 µsec later by an IOB DATAO SET pulse. These pulses clear the data control data buffer, and then load it from the I/O bus. The processor again places information on the bus for 2.5 µsec, and again the clear is at the 1 µsec point and the set at the 2 µsec point.

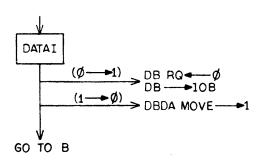

Input Command Levels – There are two negative command levels which implement the basic input instructions. These command levels gate the input information that is held by the data control onto the I/O bus for 2.5 µsec. The processor reads the information from the bus onto its I/O register at the 2 µsec point. The IOB STATUS level gates the contents of the entire IC register onto the I/O bus during the execution of each CONI instruction. Similarly, IOB DATAI gates the contents of the data buffer onto the bus during DATAI instructions.

#### Priority Interrupt Request Lines

There are seven priority interrupt request lines running from data control to processor. The data control requests a priority interrupt by placing a ground on one of these seven PI request lines. To assign a priority to the data control, a CONO instruction loads a 3-bit number into the PIA (priority assignment) field of the IC register, IC33-35. (Refer to Priority Interrupt Assignment Bits IC33-35).

#### DATA BUFFER AND DATA ACCUMULATOR

The data control contains two 36-bit data registers, the data buffer register DB, and the data accumulator DA. Both the data buffer and the data accumulator are shown in engineering

drawing BS-D-136-0-DAB1. Each of the 12 4230 flip-flop modules shown in simplified block form is composed of logical elements identical to those illustrated in the detailed block schematic at column 8 of the figure. Each of the 12 4230 modules contains 3 bits of the data buffer DB, and 3 bits of the data accumulator DA. The 12 modules are arranged in 6 pairs of 2 modules each; each pair contains 6 bits of DB and 6 bits of DA. The 6 DA bits are connected to form a bidirectional 6-bit shift register.

Note that the bits contained in each module pair do not represent adjacent bit positions. Rather, each bit in a given module pair represents a bit position six bits less significant than the next bit to the left. Therefore, when the accumulator is operated as a conventional bidirectional shift register, each shift of one bit position to the left or to the right on the six module pairs causes the entire contents of the accumulator to be shifted six bits to the left or the right.

#### Data Buffer (DCDB)

The data buffer DB is a 36-bit storage register with no shift requirement. The various operations it performs in response to applied input signals are described below.

#### I/O Bus Transfers

Processor output data can be parallel transferred from the 36-bit I/O bus into DB. This transfer is produced by the application of a negative-going pulse, DC DB — IOB, to the terminal Y ("LOAD BUFFER") inputs of the 12 4230 modules. For input, the 36-bit data word in the buffer can be read into the processor via the I/O bus. The data is placed on the bus by applying a negative level, DC DB — IOB, to the terminal K ("BUFFER BUS") emitter-follower inputs.

#### Buffer-Accumulator Transfers

When the DC DB —J> DA pulse is applied to the W terminals, it jam transfers the contents of DB into the data accumulator. Note that the apparently converse pulse DC DA —J> DB (applied to the X and T terminals) not only jam transfers the contents of the accumulator into the buffer, but also clears the accumulator.

#### **Buffer Clear**

The buffer is cleared by DC CLR DB at terminal E.

#### Data Accumulator (DCDA)

The data accumulator DA is a 36-bit bidirectional shift register capable of successive 6-bit shifts in either direction. The various operations it performs in response to applied input signals are described below.

#### Accumulator Output

The accumulator contents are always available at output terminals J, N, and R of each module. Ground levels at these terminals correspond to ones in the corresponding bits of the accumulator. These accumulator output levels are applied to the output inverter buffers shown in engineering drawing BS-D-136-0-DAB2, A-B. During output operations, the I/O devices sample the inverter outputs at appropriate phases of the device operating cycles (negative levels at the inverter outputs correspond to accumulator bits containing ones).

Devices 3 and 4 receive only the six high order bits DA0-5. The bidirectional devices, I/O devices 1 and 2, receive the six high order bits during normal tape motion, but during reverse tape motion these devices receive instead the six low order bits DA30-35. The variable character-length devices, I/O devices 5 and 6, receive data in bytes of 12, 18, or n bits  $(1 \le n \le 36)$  (refer to Data Control Outputs to I/O Devices).

#### Accumulator-Buffer Transfers

The application of DC DA  $\rightarrow$  DB to the X and T terminals of the 12 4230 modules causes the jam transfer of C(DA)\* into DB and clears DA.

#### Accumulator Dash Data Inputs

Data can be read in from I/O devices 1-4 to the six low order (right-end) bits of the accumulator, DA30-35. In addition to this right-end readin, the bidirectional I/O devices, devices 1 and 2, can also read data into the six high order (left-end) bits of the accumulator, DA0-5.

<sup>\*</sup>C(DA) means contents of data accumulator.

Data transfer from I/O devices 1-4 into the low order bits is carried out as follows. Data is presented to the six terminal S inputs shown in engineering drawing BS-D-136-0-DAB1, B.

The data inputs are designated DASH DATA IN 30 RT through DASH DATA IN 35 RT. A ground DASH DATA IN level corresponds to a 1 input from the corresponding bit position of the selected I/O device. The detailed block schematic in column 8 of BS-D-136-0-DAB1 shows how the data is read into the accumulator applying a DASH LT pulse to the U terminals of all 12 4230 modules. This pulse strobes the input data from the I/O device into the six low order bits of the accumulator, and simultaneously shifts the previous contents of the entire accumulator six bit-positions left. (See page 2-5, second paragraph).

During reverse tape motion, the bidirectional devices, I/O devices 1 and 2, read data into the six high order bits of the accumulator, DA0-5. This operation is exactly similar to the low-order-bits transfer described above. The terminal H data inputs (BS-D-136-0-DAB1, C) are designated DASH DATA IN 0 LT through DASH DATA IN 5 LT. The data is strobed in by presenting a DASH RT pulse to the Z terminals of all 12 4230 modules. This pulse reads the input data from the I/O device into the six high order bits and shifts the accumulator right six bit-positions.

#### Accumulator Dash Strobe Inputs

The two variable-character-length devices, I/O devices 5 and 6, can read data into the accumulator in bytes of 12, 18, or n bits ( $1 \le n \le 36$ ). These devices always send each input byte of less than 36 bits into the low order end of the accumulator.

The data transferred in from devices 5 and 6 does not enter the accumulator in the same way as the data from I/O devices 1 through 4. If the IC30-32 bits select I/O device 5 for a readin sequence, that device sends the data control a TK CHAR 5 pulse (take a character from device 5) when it is ready to send data into the data control. This pulse (BS-D-136-0-DASH,C1) generates DASH STRB LT and DASH STRB RT pulses. Similarly, if IC30-32 select I/O device 6 for a readin sequence, the TK CHAR 6 pulse generates DASH STRB LT and DASH STRB RT pulses.

Input data levels from device 5 are applied to the negative capacitor-diode gates shown in drawing BS-D-136-0-DAB2, 7C; negative levels correspond to 1 bits. The number of input

terminals used, 12, 18 or n, depends on the size of the input bytes that device 5 sends to the data control. For bytes of less than 36 bits the active input terminals are always those at the low order end of the accumulator.

The input data levels are strobed into the accumulator by device 5 DASH STRB pulses. If a negative input level is applied to a given capacitor-diode gate, the pulse inverter output of that gate generates a positive pulse at DASH STRB time, thereby setting the flip-flop to the 1 state. Input levels from device 6 are strobed into the accumulator by the same process.

#### Accumulator Shifts

The entire contents of the accumulator are shifted left six bit-positions by applying a DASH LT pulse to the U terminals of all 12 4230 modules. Application of a DASH RT pulse to the Z terminals produces a 6-bit right shift.

For I/O devices 1-4 the contents of the accumulator are always shifted left six bit-positions whenever a character is read into the six low order bits of the accumulator. This is necessary to prevent the destruction of the data previously read in. When reading in data from the bidirectional devices in reverse tape motion, C(DA) (the contents of DA) are shifted right six bit-positions as each new character is read in.

Devices 5 and 6, the variable character-length devices, are read in at the DASH STRB pulse but do not start to shift C(DA) until 1 µsec after DASH STRB. The accumulator is then shifted left six bit-positions every microsecond until there is room for the next byte of input data to be read in. For 12-bit bytes, the shifts are required; 18-bit bytes take three shifts; n-bit bytes are not shifted at all. For operations involving devices 5 or 6, no shifts ever follow the final character of the data word.

For output operations of all six I/O devices, the direction and number of accumulator shifts is the same as for input. Data is normally transferred out to the I/O devices from the high order (left-end) accumulator bits, and C(DA) are shifted left for each character that is transferred out. In reverse tape motion, the bidirectional devices 1 and 2 transfer out data from the low order (right-end) accumulator bits, and shift right as each new character is transferred out.

#### CONTROL STATUS REGISTER (DCIC)

The internal logical operations of the data control are controlled largely by the 16-bit control-status register IC (mnemonic for Initial Conditions) and the 2-bit shift counter SCT. The IC register is composed of 16 identical 500-kc flip-flops. However, the conditions controlling these flip-flops and the uses to which they are applied are so diverse that each of the nine data fields (which together comprise the 16 IC bits) may be regarded as an essentially separate register. Thirteen of the 16 IC bits, IC23-35, are shown on engineering drawing BS-D-136-0-DC2, A-B. The remaining three IC bits, IC20-22, make up the 3-bit character counter shown in drawing BS-D-136-0-DC1, B6-7. The nine data fields making up the IC register are listed in Table A1-1, a foldout sheet in Appendix 1.

The 2-bit shift counter SCT0-1 is a separate auxiliary register, entirely internal to the data control. Because it can neither be controlled nor sampled by the processor, it is not considered to be part of the IC register. However, because the logical conditions governing the shift counter operations are closely interrelated with the conditions governing the operation of the character counter, the two counters are described together below. The shift counter is shown in BS-D-136-0-DC1, B5.

#### Character Counter IC20-22 and Shift Counter

The character counter (CCT 0-2) and the shift counter (SCT 0-1) are shown in drawing BS-D-136-0-DC1, B. Decoder nets which determine when the counters have reached the assigned count (DC CCT DONE and DC SCT DONE) are shown immediately above the counters. The control nets which govern the counting and clearing of the counters are also shown in the same drawing at zone C7-8.

#### Function

The character counter keeps track of the number of characters of a given data word which have been read in or transferred out. It completes its count at a number one less than the number of characters in the data word. The resulting DC CCT DONE (Character Counter Done) level serves two functions. First, during operations by I/O devices 5 or 6, it prevents the final

character from being shifted left. Second, and even more important, it is the character counter done level which enables the final command pulse of the readin or transfer out sequence to terminate the sequence by setting the DA RQ flip-flop.

The shift counter is only used by the variable character-length devices. When devices 5 or 6 are operating in the 12 or 18-bit mode, the shift counter keeps track of the number of 6-bit left shifts which have been made after the readin or transfer out of a given character. The DC SCT CONT level (which is asserted until the shift counter completes its assigned count) controls the generation of the repetitive DASH LT pulses that shift all non-final 12 or 18-bit characters left to make room for the next character.

#### CP1 Pulses

The CP1 pulse strobes all stepping and clearing of both counters. The generation of this pulse is described later in this section. A CP1 pulse is generated whenever any I/O device sends a command pulse to the data control. A CP1 pulse is also generated by the DASH LT pulse whenever the accumulator contents are shifted left.

#### Counter Done Levels

The character mode in which the data control operates (see Character Mode Bits IC28-29) determines the correct final count for both the shift counter and the character counter. The final count of the shift counter corresponds to the number of shifts required per character (after the command pulse that reads the character in or transfers it out). The final count of the character counter is always one less than the number of characters in the data word. The shift counter done level DC SCT DONE is generated by the decoders in BS-D-136-0-DC1, A-B5; the decoders in zone A-B7 of this drawing generate the character counter done level DC CCT DONE. Operation of these two sets of decoders is summarized in Table A1-2.

#### Shift Counter Continue

The shift counter is stepped and a DASH LT pulse is generated at each CP1 pulse which occurs while the DC SCT CONT (Shift Counter Continue) level is asserted negative. The level rises to ground if either the shift counter or character counter finishes its assigned count, that is, at the assertion of either SCT DONE or CCT DONE (see BS-D-136-0-DC1, C8).

#### Character Counter Continue

The character counter is stepped at each CP1 pulse which occurs while the DC CCT CONT (Character Counter Continue) level is asserted negative. The level is asserted only when the shift counter is done (BS-D-136-0-DC1, C8). This insures that the character counter is stepped only by those CP1 pulses corresponding to actual command pulses from the I/O devices, and not by the CP1 pulses resulting from repetitive DASH LT pulses in 12 or 18-bit operation. The latter class of CP1 pulses are counted by the shift register only; they represent merely shifts within a given character and not new characters. When the DC CCT DONE level is asserted, the DC CCT CONT level ends.

#### Clear Counter Levels

The circuits which clear the shift counter and character counter are also shown in BS-D-136-0-DC1, C7. Both shift counter and character counter are cleared by the initial data control clear pulse, DC IC CLR. The character counter is also cleared by the first CP1 pulse which occurs after the character counter completes its count. There is one further possibility of clearing the character counter. Under certain circumstances it may be desirable to clear the character counter by an externally generated clear pulse from one of the I/O devices. The negative capacitor-diode gate permits the option of connecting any of I/O devices 1-4 for an external character counter clear.

The shift counter is always cleared at the first CP1 pulse occurring after either the shift counter or the character counter is done.

#### Error Bit IC23

The DATA CLBD (Data Clobbered) error bit is set to 1 by any CPO pulse generated when DA RQ contains 1. This error condition indicates either that an output command pulse has been sent to the data control while DA is empty, or else that an input command pulse has been sent to the data control while DA is still loaded with the previous data word.

The latter condition is the more serious one; its detection is the primary purpose of the data CLBD error bit. If an I/O device should attempt to read in data before the previous data word

were advanced from the accumulator to the data buffer, data would be lost. This error condition could arise only through an equipment malfunction or a programming error at the I/O device.

#### Data Control Status Bits IC24-26

The three status bit flip-flops DBDA MOVE, DA RQ, and DB RQ synchronize the processor and I/O device operations to the data control as well as governing the internal operations of the data control itself.

#### DBDA MOVE IC24

The DBDA MOVE (data buffer data accumulator move) flip-flop is shown in BS-D-136-0-DC2, A2. Its output is applied to input terminal M of diode gate 1B7 (BS-D-136-0-DC1, C3); a negative-to-ground transition at the output of that gate initiates all transfers (in either direction) between the data buffer and the data accumulator. A transfer can be initiated in either of two ways. When the DA RQ flip-flop is in the 1 state, the 0 to 1 transition of DBDA MOVE causes a rising edge at the output of gate 1B7, thus triggering pulse amplifier 1A9 and producing a DA —J> DB or DB —J> DA transfer. Similarly, when the DBDA MOVE flip-flop is in the 1 state, the 0 to 1 transition of the DA RQ flip-flop causes the transfer.

#### DA RQ Flip-flop IC25

The data accumulator request flip-flop DA RQ (BS-D-136-0-DC1, A2) indicates the status of the accumulator both to the I/O devices and to the internal logic of the data control. At most phases of the data control operating cycle, the state of DA RQ indicates whether or not the data accumulator is fully loaded with data. During output operations, a 0 in the DA RQ indicates that the accumulator is loaded. During input operations, however, a 1 in DA RQ indicates that the accumulator is loaded, and a 0 indicates that the accumulator is empty and free to receive data.

For either output or input operations, a 0 in DA RQ indicates that the data control is ready to act on commands from the I/O devices (to transfer out the data word in DA during

output, or to read in a new data word to the empty DA during input). Conversely, during both output and input operations, a 1 in DA RQ indicates that the accumulator is not ready to execute a transfer out or readin sequence (refer to Table A1-3).

#### DB RQ Flip-flop IC26

The data buffer request flip-flop DB RQ (BS-D-136-0-DC1, A3) indicates the status of the data buffer both to the I/O devices and to the internal logic of the data control. At most phases of the data control operating cycle, the state of DB RQ indicates whether or not the data buffer DB is loaded with data. The immediate meaning of the state of DB RQ is the same as that of DA RQ described above. Either flip-flop in the 0 state during output, or in the 1 state during input, signifies that the corresponding register is loaded with data. When DB RQ contains a 1 during output (indicating that the buffer is empty), the data control is ready to accept output data from the processor. Moreover, when DB RQ contains a 1 during input (indicating that the buffer is loaded) the data control is ready to read data into the processor.

#### Status-Bit Configuration Tables (Tables A1-4 and A1-5)

The configurations of the three status-bit flip-flops after each phase of the data control output operations are summarized in Table A1-4. Input configurations are similarly summarized in Table A1-5. These two tables are frequently referred to in the paragraphs below describing the data control output and input cycles. Once the data control logic has been learned, these two tables and the system flow diagram, FD-D-136-0-FD1, can serve as a ready-reference summary of the data control operating cycle.

#### Input/Output Flip-flop IC27

The input/output flip-flop, DC IN/OUT, is shown in engineering drawing BS-D-136-0-DC2, A.S. It indicates to the data control logic whether the current operation is an input operation or an output operation. The outputs of the in/out flip-flop are applied to input terminals Z and T of pulse amplifiers 1A10 (BS-D-136-0-DC1, C5). The state of the flip-flop determines whether the dual purpose transfer pulse DC DB < J> DA produces a DC DA - J> DB pulse which jam transfers C(DA) into DB during input cycles, or a DC DB - J> DA pulse, which jam transfers C(DB) into DA during output cycles.

#### Character Mode Bits IC28-29

The two character-mode flip-flops CH MODE 0 and CH MODE 1 are shown in BS-D-136-0-DC2, B4. The states of these flip-flops determine the character mode in which the data control operates (refer to Table A1-2). The outputs from the character mode flip-flops are applied to the decoder nets shown in BS-D-136-0-DC1. Thus they determine the final contents of the shift counter that produce the DC SCT DONE level, and the final contents of the character counter that produce the DC CCT DONE level.

#### Internal Device Address IC30-32

The three internal device address flip-flops, DC DEVICE 0, DC DEVICE 1, and DC DEVICE 2, are shown in BS-D-136-0-DC2, 5-6. The 3-bit binary number contained in these three flip-flops indicates to the data control logic which of the six subsidiary devices is to be used for a given input or output operation.

The contents of the three internal device address flip-flops correspond directly to the I/O device numbers. When the flip-flops contain 010 (2 octal) I/O device 2 is selected; 100 (4 octal) selects I/O device 4, and so on. This 3-bit internal device address addresses an I/O device only from the selected data control. It should not be confused with the 7-bit device selection code used by the processor to address the selected I/O device directly, nor with the second 7-bit device selection code used by the processor to address the selected data control; levels 1-4 are first sent through the buffer-inverter circuits shown in BS-D-136-0-DC2, A5-6.

#### Priority Interrupt Assignment Bits IC33-35

The three priority interrupt assignment flip-flops, PIA-0, PIA-1, and PIA-2, are shown in BS-D-136-0-DC2, B7-8. The processor can assign a priority-interrupt request channel to the data control by means of a CONO instruction which sets these three bits to some number from 1 to 7. If all three PIA bits are left 0, no priority interrupt channel is assigned (see Section 4).

Until the contents of PIA0-2 are changed by another CONO from the processor, the data control can request a break on the assigned channel. The data control requests a break on the assigned channel when the DB RQ flip-flop is set to the 1 state. If this occurs during

an output sequence, it indicates that the DB register is empty and is therefore ready to receive more data from the processor. If it occurs during an input sequence, it indicates that the DB register is loaded with data and is therefore ready to read data into the processor. Both output levels from each of the three PIA flip-flops are applied to the binary-to-octal decoder 1B8 (BS-D-136-0-DC2, B7-8). When inactive, the seven PIA outputs from this decoder are negative levels. When the DB RQ flip-flop is set to 1, the PIA line corresponding to the assigned channel is grounded.

#### **DEVICE INTERFACE**

This section describes the interchange of data and control information between the data control and its subsidiary I/O devices.

#### Cabling - Data Control to I/O Devices

There are 16 22-conductor coaxial cables from the data control to the six I/O devices. Devices 1 and 2, the bidirectional devices, require two cables each. Unidirectional devices 3 and 4 have only one cable apiece. Devices 5 and 6, the variable character-length devices, are each assigned five cables. The 16 cables are wired to 22-pin Methode plugs in rack positions 1D10 through 1D25. The specific terminal assignments of all 16 cables are shown in engineering drawing ID-D-136-0-EDC.

#### Data Control Outputs to I/O Devices

The data control sends the I/O devices both control information and data levels.

#### Control Information

Output control information is sent to I/O Devices 1 through 6 through the six Methode plugs shown in BS-D-136-0-DASH, D. All six devices receive the state of the DA RQ flip-flop; furthermore each device receives its own device select signal. The negative 1 output of the DA RQ flip-flop is amplified by the 6684 Bus Driver 1B21 (BS-D-136-0-DC2, A3). The amplified output is then sent to the six I/O devices through the W terminals of the six Methode plugs (BS-D-136-0-DASH, D). When DA RQ contains a 1, the output is quiescent in the assertion state shown (W terminals negative). This indicates to the selected I/O device that

the data control is not ready. When the DA RQ output is active, the W terminals are at ground. This indicates to the I/O devices that the DA RQ flip-flop contains 0 and that the data control is ready.

The data control sends DC DEVICE SEL levels to the six I/O devices so that a given device responds to data control operations only when the internal device address in IC30-32 selects that device; refer to Internal Device Address IC30-32. The negatively asserted DC DEVICE SELECT level for each device is applied to the X terminal of the corresponding Methode plug (BS-D-136-0-DASH, D).

#### Data-Level Outputs

The ground assertion 1 outputs of the 36 accumulator flip-flop are applied to the output buffer-inverters shown in BS-D-136-0-DAB2, A-B. During output operations, the I/O devices sample the inverter outputs at appropriate phases of the device operating cycles. Negative levels at the inverter outputs correspond to accumulator bits containing ones. The outputs from the six high order accumulator bits, DA0-5, are applied to all six I/O devices. The output data levels are sampled only by the selected device. If bidirectional I/O device 1 or 2 is selected, the high order (left-end) accumulator bits are sampled only during normal tape motion. During reverse tape motion output cycles, the bidirectional devices 1 and 2 receive the six low order bits CA30-35. All 36 outputs are available for connection to the variable character-length devices 5 and 6. Data may be transferred out to these two devices in bytes of 12, 18, or n bits. For 12 or 18-bit characters I/O devices 5 and 6 always sample data from the high order end of the accumulator. For n-bit (n < 36) single-character data words, devices 5 and 6 sample from the low order end of the DA.

### Inputs to Data Control from I/O Devices

Besides providing input levels that read data into the data control, the I/O devices also send command pulses to the data control. During output cycles, these pulses indicate to the data control when the selected I/O device is ready to accept another data character. During input cycles, command pulses from the I/O device let the data control know when a new data

character is ready to be read in. The command pulse inputs from the I/O devices govern the generation by the data control of internal command pulses, which in turn cause the data control to sample and shift at appropriate intervals.

#### Command Pulses from I/O Devices

Command pulse control information to the data control is not the same for all six I/O devices; the specific command pulses sent to the data control depend upon which I/O device is selected.

Bidirectional Devices 1 and 2 - The bidirectional devices send the same command pulses to the data control during both the output cycle and the input cycle. However, the command pulses from these devices do vary depending upon whether the device is functioning in normal tape motion. For both output and input cycles in normal tape motion, a TK/GV CHAR LT (Take or Give a Character Left) command pulse is sent to the data control.

During an output cycle, this pulse indicates to the data control that the I/O device has sampled the output levels from the six high order accumulator bits, DA0-5, and that the data control may shift the accumulator contents left six bits, thus bringing the next character of the data word into position to be sampled by the device. During an input cycle, the TK/GV CHAR LT command pulse indicates that the I/O device has applied a 6-bit input character to the low order accumulator DASH DATA IN RT inputs (described under Data-Level Inputs from I/O Devices below) and that the data control may shift the contents of the accumulator left six bit-positions, and at the same time strobe the input character into the six low-order bit-positions which are made available by the shift.

For both output and input cycles in reverse tape motion, the bidirectional devices send a TK/GV CHAR RT (Take or Give a Character Right) command pulse to the data control.

Unidirectional Devices 3 and 4 - For both output and input cycles, devices 3 and 4 send a TK/GV CHAR LT command pulse to the data control. This pulse serves exactly the same function for unidirectional devices 3 and 4 as it does the bidirectional devices 1 and 2 during normal tape motion.

Variable Character-Length Devices 5 and 6 - The variable character-length devices send the data control a GV CHAR command pulse during the output cycle, but send a TK CHAR command pulse during the input cycle. The GV CHAR command pulse indicates to the data control that the device has accepted the character, and that unless that character was the last in the output data word, the data control must shift the accumulator left by one character length in order to bring the next character into the high order bit positions.

During input operations, devices 5 and 6 send the data control a TK CHAR command pulse when they have presented an input character to the low order strobe data inputs of the accumulator (refer to the following paragraph). This indicates to the data control that it may strobe the character into the low order accumulator bits and then begin to shift the accumulator contents left to make room for the next character that will be read in (unless the character was the last one in the input data word).

#### Data-Level Inputs from I/O Devices

The paths by which the I/O devices transmit data into the data control also vary depending upon which device is selected for input and (for the bidirectional devices 1 and 2) depending upon which direction of tape motion the device is using.

Dash Data In Right - Devices 1 through 4 read information into the low order (right-end accumulator bits through the DASH DATA IN RT networks shown in BS-D-136-0-DASH, B4-8. These input networks are used by bidirectional devices 1 and 2 only during normal tape motion. The I/O devices apply six input data levels (called DATA IN RT levels) to the Methode plugs shown in BS-D-136-0-DASH, C4-8. Negative levels correspond to 1 bits.

If one of the DC DEVICE SELECT levels 1-4 is asserted negative, data from the corresponding device is gated into the six diode gates 1D2-1D4, and appears at the output terminals of these gates as the six data levels DASH DATA IN 30 RT through DASH DATA IN 35 RT. Since the gates invert the data levels, ground DASH DATA IN RT levels correspond to 1 bits from the devices. The DASH DATA IN RT outputs from the diode gates are strobed into the six low order (right-end) accumulator bits DA30-35 by the same DASH LT pulse that shifts the accumulator contents left. The accumulator readin is described earlier in this section under Accumulator Dash Data Inputs.

<u>Dash Data In Left</u> - During reverse tape motion, bidirectional devices 1 and 2 read information into the high order (left-end) accumulator bits through the DASH DATA IN LT networks shown in BS-D-136-0-DASH, A5-8. The I/O devices apply six DATA IN LT input levels to the Methode plugs 1D10 and 1D12. Negative levels at the gate inputs correspond to 1 bits read in from the I/O devices; the gate outputs are inverted and thus generate ground DASH DATA IN LT levels to represent 1 bits from the devices.

Variable Character-Length Data - The variable character-length devices 5 and 6 send data into the data control through the negative capacitor diode gates shown in BS-D-136-0-DAB2, C-D. The number of active inputs depends on the length of the input data byte; for bytes of less than 36 bits, the data is always sent into the low order bits of the accumulator. Negative inputs represent 1 bits; inactive inputs are not connected. Data from I/O device 5 is gated into the accumulator by the DASH STRB LT (DEV 5) and DASH STRB RT (DEV 5) pulses; data from I/O device 6 is gated into the accumulator by the (DEV 6) DASH STRB pulses.

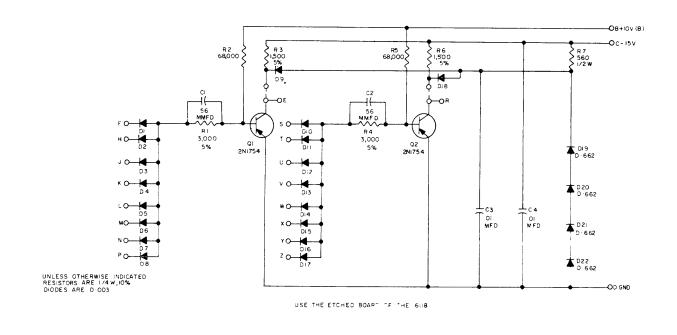

#### Resulting Internal Command Pulses

Three sets of internally generated command pulses are produced by the data control in response to the incoming command pulses from the I/O devices. These pulses are: the dash strobe pulses; the dash left and dash right pulses; and the CPO and CP1 pulses. These pulses strobe data into the accumulator, initiate the accumulator shifts, and control the shift and character counters that indicate to the data control when it has become to the end of a character or data word.

#### Dash Strobe Pulses

The dash strobe pulses, DASH STRB (DEV 5) and DASH STRB (DEV 6) gate in the variable character-length input data for I/O devices 5 and 6. The pulse amplifiers which generate the DASH STRB (DEV 5) pulse and those which generate the DASH STRB (DEV 6) pulse are shown in BS-D-136-0-DASH, D1. Each of these pulses is generated by two pulse amplifiers and applied to two independent lines, DASH STRB LT (which strobes data through capacitor-diode gates into the 18 high order accumulator bits) and DASH STRB RT (for the 18 low order bits of DA). For either device, the DASH STRB RT and DASH STRB LT lines are always pulsed together.

### Dash Left and Dash Right Pulses

The DASH LT pulse always causes the accumulator contents to be shifted left six bit-positions. Furthermore, during input cycles of I/O devices 1-4, DASH LT strobes the input data carried by the six levels DASH DATA IN 30 RT through DASH DATA IN 35 RT into the six low order (right-end) bit-positions of the accumulator (the six bit-positions made available by the left shift).

The DASH RT pulse always causes the accumulator contents to be shifted right six bit-positions, and during input cycles strobes the DASH DATA IN 0 LT through DASH DATA IN 5 LT levels from bidirectional I/O device 1 or 2 into the six high order (left-end) accumulator bit-positions.

Conditions When Dash Right and Dash Left Are Generated (I/O Devices 1-4) - The pulse amplifiers that generate the DASH LT and DASH RT pulses are shown in BS-D-136-0-DASH, A2-3. Pulse amplifier 1A21 generates DASH RT whenever I/O device 1 or 2 is selected and takes or gives a character in reverse tape motion.

Pulse amplifier 1A18 generates the DASH LT pulse under two sets of conditions; one set of conditions applies to I/O devices 1-4, the other applies to I/O devices 5 and 6. The first set of DASH LT conditions, which is implemented by the negative capacitor diode gate at input terminal F of the pulse amplifier, is almost exactly similar to the DASH RT conditions. This set of conditions causes a DASH LT pulse to be generated when a character has been transferred out to or read in from selected I/O device 1-4. (If bidirectional device 1 or 2 is selected, the device must be in normal tape motion to produce a DASH LT.)

Conditions When Dash Left is Generated (I/O Devices 5 and 6) - The second set of input conditions which causes the generation of a DASH LT pulse is less self-evident. The variable character-length devices 5 and 6 can read in or accept data in bytes of 12, 18, or n bits. The n-bit bytes are single-character data words which are not shifted, and thus require no DASH LT pulses. However, each 12-bit character which is read in or transferred out (except the final character in the data word) must be followed by a 12-bit left shift of the accumulator contents. Each non-final 18-bit character is followed by an 18-bit left shift. To implement

these left accumulator shifts, it is necessary, when operating in 12-bit mode, to generate two DASH LT pulses for each character except the last. When operating in 18-bit mode, three DASH LT pulses are needed. Each DASH LT pulse produces a 6-bit left shift.

Circuits Used to Produce Dash Left Pulse - There are four sets of circuits involved in producing the correct dash left shift operations: 1) Pulse amplifier 1A18 is the final circuit which generates the required DASH LT output pulses; 2) the shift counter keeps track of the number of shifts executed; 3) the character counter indicates when the final character of the data word is being transferred out or read in; 4) finally the CPO-CP1 (Command Pulse 0 - Command Pulse 1) network produces the CP1 pulses which initiate the DASH LT pulses and step the shift counter.

The conditions for generating DASH LT during output and input cycles of I/O devices 1-4 are implemented by the capacitor-diode gate at input F of pulse amplifier 1A18 (BS-D-136-0-DASH, A2). Terminals K and L of this same pulse amplifier receive the inputs which govern the generation of DASH LT during output and input cycles by I/O devices 5 and 6. Pulse amplifier 1A18 generates a DASH LT pulse at the arrival of each CP1 pulse at terminal K so long as the DC SCT CONT (Shift Counter Continue) level is asserted at terminal L.

As soon as either the shift counter or the character counter completes its assigned count (indicating that the contents of the accumulator have been sufficiently shifted) the SCT CONT level rises to ground. This prevents any further CP1 pulses from generating a DASH LT, and also resets the shift counter. For a more detailed description of the shift counter operations and logic levels refer to Character Counter IC20–22 and Shift Counter.

## DASH CP0 and CP1 Pulses

The DASH CP0 and CP1 pulses (Command Pulse 0 and Command Pulse 1) are generated by the network shown in BS-D-136-0-DASH, B2-3. The CP1 pulse is simply a CP0 pulse delayed 1 µsec by 1310 Delay Line 1A22. The CP1 pulse is the signal that steps the shift counter and character counter and that initiates the appropriate number of DASH LT signals during device 5 and 6 operations with 12- and 18-bit characters. The CP0 pulse is used only for the single purpose of setting the DATA CLBD error flip-flop.

Generated by Device Command Pulses - A CP0 pulse and a CP1 pulse are generated whenever any I/O device sends a command pulse to the data control. Any command pulse from I/O devices 1-4 must produce either a DASH LT or a DASH RT; either of these pulses triggers CP0 and CP1. The variable character-length device command pulses also initiate CP0 and CP1. When a character is transferred out to device 5 or 6, the GV CHAR 5 or GV CHAR 6 pulse directly produces CP0 and CP1. When a character is read in from I/O device 5 or 6, the TK CHAR 5 or TK CHAR 6 pulse first generates a corresponding DASH STRB (DEV 5) or DASH STRB (DEV6) pulse which then triggers pulse amplifier 1A18 to produce CP0 and CP1.

Repetitive Shifts - In addition to following every command pulse from the six I/O devices, CPO and CPI may also be produced by DASH LT pulses which are not themselves initiated by command pulses. As mentioned previously, each DASH LT pulse produces a CPI 1 µsec later. Note, however, that the DASH LT pulse itself can in turn be produced by CPI so long as the DC SCT CONT level is asserted negative (BS-D-136-0-DASH, A2).

The result of this reciprocal causal relationship is a loop. The external command pulse from the I/O device which occurs when a character is first transferred out or read in (for example, GV CHAR 5) causes the generation of the first CPI pulse for that character. This first CPI pulse in turn produces a DASH LT pulse (the first DASH LT of the current character) and also constitutes the first shift counter step signal of the current character; CPI steps the SCT to 01. The first DASH LT pulse initiates a second CPI (after a delay of 1 µsec). This second CPI pulse steps the shift counter to 10 (2 octal) and at the same time produces a second DASH LT pulse.

If 12-bit characters are being transferred out to the I/O device, the shift counter is done after being stepped by the second CP1. The second DASH LT can then produce a third CP1 (delayed 1 µsec), but that third CP1 cannot get through to trigger pulse amplifier 1A18. (It is no longer gated through by the DC SCT CONT level. That level ceased to be asserted when the shift counter reached its assigned count, 2 octal, at the second CP1 pulse.) Consequently, no third DASH LT pulse is ever generated. The third CP1 does not step the shift counter, but instead resets it. If 18-bit characters are being transferred out to the I/O device, or being read in from it, the process is similar, except that the shift counter is not done until it reaches a count of 11 (3 octal).

Final Characters Not Shifted for I/O Devices 5 and 6 - During input cycles involving devices 5 and 6, the last character of the data word (the first and only character in n-bit mode, the second character in 18-bit mode, or the third character in 12-bit mode) must not be shifted. If it were shifted, data would be lost out the left end of the accumulator (or for n-bit input cycles at least displaced). During output cycles involving devices 5 and 6, it would of course do no harm to shift the empty accumulator after the last character is transferred out, but this would be useless and is not done.

The logic which implements the data control shift operations prevents any shift pulses from being generated by the readin or transfer out of the final 12, 18, or n-bit character. The command pulse from I/O device 5 or 6 concurrent with the transfer out or readin of the final character does produce a CPO and CP1 pulse. However, the CP1 is prevented from triggering a DASH LT by the removal of the DC SCT CONT level when the character counter reaches its final assigned count.

The final count of the character counter is always one less than the number of characters in the data word; refer to Table A1-2. The character counter is done at the count of zero for n-bit characters, at the count of one for 18-bit characters, and at the count of two for 12-bit characters. When it reaches its final count in 12- or 18-bit mode, it produces a DC CCT DONE (Character Counter Done) level, thereby terminating the negative DC SCT CONT level and preventing the generation of further DASH LT pulses. In n-bit mode, there is only one character to a data word. Both the character counter and the shift counter are done at the initial zero count. Consequently, no DASH LT pulses are generated.

During output or input cycles involving I/O devices 1-4, completion of the character counter count does not prevent generation of a DASH LT or DASH RT pulse. Such a shift pulse is generated concurrently with the final (sixth) character of the output or input data word. The sixth and final shift pulse is harmless for output cycles, and necessary during input cycles.

## OUTPUT CYCLE

The simplified output cycle described in the present section consists of a CONO (Conditions Out) instruction followed by a series of DATAO instructions. Although for practical operations

other routines are employed (refer to Section 4 for a description of sample programs), the input signals to the data control, and the resulting internal cycle, are identical in both cases; the only difference lies in the intervening instructions executed by the processor.

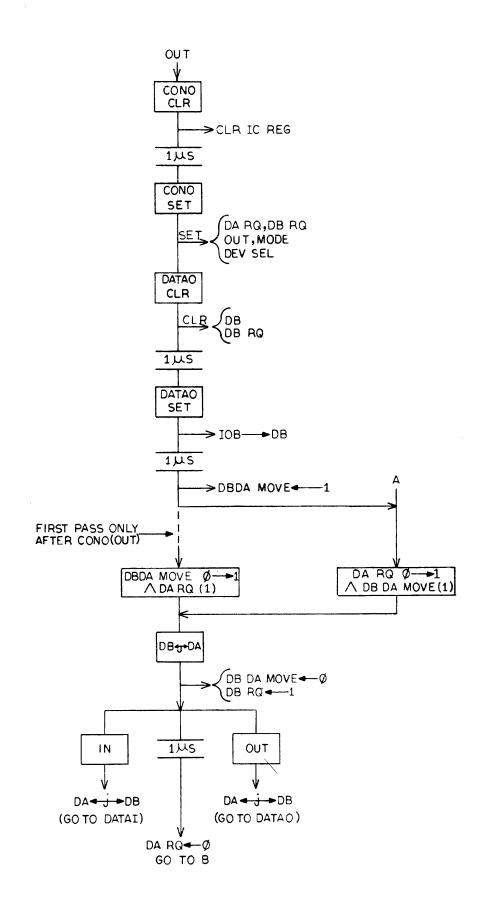

## CONO Out Instruction

The CONO Out (Conditions Out) instruction clears the IC register and the accumulator (preserving the contents of the accumulator in DB), and then sets the contents of the IC register to control codes such as those shown in Table A1-6. This prepares the data control for the following DATAO instructions, enabling it to dispatch the data out in appropriate bytes to a selected I/O device, and if required, enabling it to generate a priority interrupt request when more data is needed from the processor. Also see Table A1-7.

## CONO Clear Pulse

The processor initiates the data control output sequence by sending the data control on IOB CONO CLR pulse (I/O Bus Conditions Out Clear). This pulse is represented by the initial operation (CONO CLR) of the output flow chart, engineering drawing FD-D-136-0-FD1. It occurs 1 µsec before time 0 of the output timing sequence shown in TD-D-136-0-TD1. The data control receives IOB CONO CLR over one of the I/O bus command lines (BS-D-136-0-DC1, A1); it clears all flip-flops in the IC and DA; the accumulator contents are preserved in the DB.

#### **IOB** Reset Pulse

The clearing function described above can be initiated not only by IOB CONO CLR, but also by IOB RESET (BS-D-136-0-DC1, A1). The latter command line is pulsed whenever computer

power is turned on, and whenever the operator presses the I/O reset key on the computer console. The IOB reset triggers pulse amplifiers 1A8 and 1A9, generating negative and positive DC IC CLR pulses in the same manner as IOB CONO CLR. However, IOB RESET also triggers pulse amplifier 1A10 (BS-D0136-0-DC1, B2), generating an additional clear pulse, DC CLR DB, which clears the data buffer.

## **Device Selection Gating**

Because IOB RESET is intended to clear all I/O control units, it causes an unconditional triggering of pulse amplifiers 1A8, 1A9, and 1A10. It is not gated by any device selection code. In contrast, IOB CONO CLR, and in fact all of the eight control line inputs to the data control except IOB RESET and POWER ON, are intended only for one specific addressed control unit, the unit selected by the device selection code in bits 3 through 9 of the CONO instruction. Consequently, these signals are all gated by the output of diode net 1A6 (BS-D-136-0-DC1, D1).

## CONO Set Pulse

One µsec after IOB CONO CLR (at time 0 of the output sequence in TD-D-136-0-TD1) the processor sends an IOB CONO SET pulse (I/O Bus Conditions Out Set) to the data control (BS-D-136-0-DC1B2). The CONO SET is gated by the data control device selection level and then triggers pulse amplifier 1A8 (BS-D-136-0-DC1, A2). The resulting DC IC SET output pulse causes the parallel transfer of the information on the I/O bus into bits 23 through 35 of the IC register. It is assumed for the present example that this sets the IC register flip-flops to the states indicated in Table A1-6. (See also line 2 of Table A1-4.)

## First DATAO Instruction

At the completion of the CONO Out instruction, the data control is ready to respond to the next processor instruction, a DATAO (Data Out) instruction. The purpose of this instruction is to transfer a 36-bit data word from the processor into the data control data buffer, from there to transfer it to the data control accumulator, and then finally to shift it out into the selected I/O device.

### **DATAO Clear Pulse**