PDP-8 Family Maintenance Manual

## DF32-D,E

**Disk File and Control**

F8~59-020 11-18-75

RECOMMENDED SPAPES LEVEL

ORIGINAL DATE 111-05-74 REVISION DATE 111-13-75

OPTION : DF32-D DESCRIPTION : 32K 12 BIT DEC DISK & CONT

|   | DEC PART NO. | DESCRIPTION VE                       | DORE        | COST        | 94%       |        | STOCK LEV |        |      |      |       | c.1, |

|---|--------------|--------------------------------------|-------------|-------------|-----------|--------|-----------|--------|------|------|-------|------|

|   |              |                                      |             |             | 704       | 95%    | 904       | 808    |      | 704  | 50%   |      |

|   | 0G294-00     | DISC WRITER                          |             |             |           |        |           | •••••  |      |      |       |      |

|   | 0G295-00     | SEPIES SHITCH                        |             | 8.87        | 1         |        |           |        |      |      |       |      |

|   | 0G296-00     |                                      |             | 11.34       | i         |        |           |        |      |      |       |      |

|   | 0M101-00     | CENTER TAP SELECTOR                  |             | 12.70       | i         | 1      |           |        |      |      |       |      |

|   |              | BUS DATA INTERFACE                   |             | 5.60        | :         |        |           |        |      |      |       | .0   |

|   | 0×103-00     | DEVICE BELECTOR                      |             | 6,60        | i         | 1      | 1         |        |      |      |       | .0   |

|   | 0M111-00     | INVERTER                             |             |             |           |        |           |        |      |      |       |      |

|   | 0#112-00     | NOR GATE                             |             | 5,92        | 1         |        |           |        |      |      |       |      |

|   | 0M113-00     | 10-2 INPUT NAND GATE                 |             | 6.38        | 1         | 1      |           |        |      |      |       |      |

|   | 0H115-00     | TOUR THOU WAND GATE                  |             | 4.72        | ĭ         | •      | •         |        |      |      |       | .0   |

|   |              | INPUT NAND GATE                      |             | 5,13        | i         | 1      |           |        |      |      |       |      |

|   | 0M117-00     | INPUT NAND GATE                      |             | 4,81        | i         | •      |           |        |      |      |       | .0   |

|   | 0M160-00     | EXPANDER                             |             |             |           |        |           |        |      |      |       |      |

|   | 0×205-00     | 50 FLIP FLOP                         |             | 4,71        | 1         |        |           |        |      |      |       |      |

|   | 04206-00     | SIX FLIP FLOPS                       |             | 4,26        | 1         | . 1    | 1         | 1      |      | 1    |       |      |

|   | 0H233-00     | DISK SHAFT REG.                      |             | 6,63        | 1         | 1      | -         | •      |      | •    |       | .17  |

|   | 0#302-00     | ONE SHOT DELAY                       |             | 5.37        | 1         | ī      | 1         |        |      |      |       | .01  |

|   | 0302-00      | ONE SHUT DELAY                       |             | 16.84       | 1         | i      | •         |        |      |      |       | .05  |

|   | 0×310-00     | DELAY LINE                           |             |             |           |        |           |        |      |      |       | . 05 |

|   | 0×602-00     | PULSE GENERATOR                      |             | 15,48       | 1         |        |           |        |      |      |       | .01  |

|   | 0×617-00     | INPUT NAND GATE BUFFER               |             | 7.28        | 1         | 1      | 1         | 1      |      |      |       |      |

|   | 0M623-00     | BUS DRIVER                           |             | 6.51        | 1         |        |           | -      |      |      |       | .08  |

|   | 0M902-00     | RESISTOR TERMINATOR                  |             | 10.89       | 1         |        |           |        |      |      |       |      |

|   |              | PESTSION TERMINATUR                  |             | 4,99        | . 1       |        |           |        |      | ,    |       |      |

| - | 0×906-00     | CABLE TERMINATUR                     |             |             | _         |        |           |        |      |      |       |      |

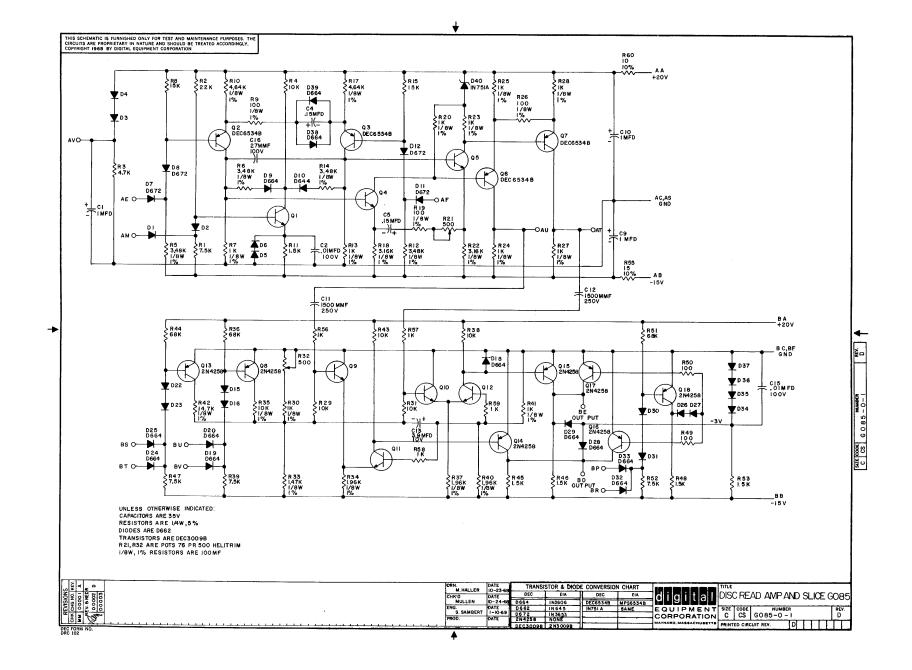

|   | G0850-00     | DISC PEAD AMP 6 SLICE                |             | 9,43        | 3         |        |           |        |      |      |       |      |

|   | 10-05767-00  | 10 MFD 330V 108/DO NOT USE 1         |             | 26,30       | 1         | 1      | 1         | 1      |      |      |       | . 15 |

|   | 12-01434-00  | PLY, G.P., 115V COIL, DPDT, 2A, OCTA | - NEW DESI  | 4,78        | 1         |        |           | _      |      |      |       |      |

|   | 12-05358-00  | DISK-10 INCH HICKEL COBALT           |             | 8.45        | 1         |        |           |        |      |      |       |      |

|   |              | DISK-10 INCH HICKEL COBALT           |             | 322,40      | 1         | 1      | 1         | . 1    |      | 1    |       | , 55 |

|   | 30-05359-00  | HEAD, FLYING 4 TRACK                 |             | 42.67       | ٠.        |        |           |        |      | •    |       | •    |

|   | 70-05315-01  | MOTOR+HUB GOCY OF32                  |             |             | 1.        | 1      | 1         | 1      |      | 1    | . 1   | .96  |

|   | 70-05315-02  | MOTOR+HUB SOCY DF32                  |             | 95,98       | 1         | 1      | 1         | 1      |      |      | •     | . 36 |

|   | 74-06308-00  | DATA HEAD HARNESS                    |             | 97,03       | 1         |        | _         |        |      |      |       | .04  |

|   |              |                                      |             | 50.09       | 1         |        |           |        |      |      |       | .01  |

|   |              |                                      | TOTAL       | COST        | 812,24    | 557,54 | 521,37    | 498,89 | 369, | , 33 | 46,93 |      |

|   |              | ***********                          |             |             | ******    |        |           |        |      |      |       |      |

|   |              | 4150                                 | LLAMFOUS PA | PTS AND SPE | CIAL TOUR | .5     |           |        |      |      |       |      |

|   |              |                                      |             |             |           |        |           |        |      |      |       |      |

|   | 10-02938-00  | .01 MFD 600V 10% 663UW M _H          | (10         | .21         |           |        |           |        |      |      |       |      |

|   | 11-00113-00  | D 662 OS 600PCb(STABISTOD)           |             | .05         |           |        |           |        |      |      |       |      |

|   | 13-00496-00  | 15 K 1/4H 5% CC                      | (13-00      | .03         |           |        |           |        |      |      |       |      |

|   | 15-02979-00  | DEC36388 PNP 300HH ST 24 P           |             |             |           |        |           |        |      |      |       |      |

|   | 15-03100-00  | DEC30098 NPN 200M# 81 20 45 P        |             | .12         |           |        |           |        |      |      |       |      |

|   |              |                                      |             | .17         |           |        |           |        |      |      |       |      |

|   | 19-05576-00  | DEC 7410 NAND LATE-TRIPLE SIN        |             |             |           |        |           |        |      |      |       |      |

# PDP-8 FAMILY DF32-D,E DISK FILE AND CONTROL MAINTENANCE MANUAL

1st Printing August 1970 2nd Printing August 1971 3rd Printing July 1972

Copyright © 1970, 1971, 1972 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

**FOCAL**

DIGITAL

**COMPUTER LAB**

### CONTENTS

|           |                                            | Page |

|-----------|--------------------------------------------|------|

| CHAPTER 1 | INTRODUCTION                               |      |

| 1.1       | Scope                                      | 1-1  |

| 1.2       | Equipment Application                      | 1-2  |

| 1.3       | DF32-D,E Description                       | 1-2  |

| 1.3.1     | Disk Assembly                              | 1-5  |

| 1.3.2     | Logic Module Assembly                      | 1-6  |

| 1.4       | DS32-D,E Description                       | 1-6  |

| CHAPTER 2 | INSTALLATION                               |      |

| 2.1       | Cabinet Installation                       | 2-1  |

| 2.2       | Power Requirements                         | 2-1  |

| 2.3       | Cable Requirements                         | 2-2  |

| CHAPTER 3 | OPERATION AND PROGRAMMING                  |      |

| 3.1       | Operation                                  | 3-1  |

| 3.2       | Programming                                | 3-3  |

| CHAPTER 4 | THEORY OF OPERATION                        |      |

| 4.1       | General                                    | 4-1  |

| 4.1.1     | Write Operation                            | 4-5  |

| 4.1.2     | Read Operation                             | 4-5  |

| 4.2       | Disk                                       | 4-9  |

| 4.2.1     | Disk Format                                | 4-9  |

| 4.2.2     | Disk Timing                                | 4-12 |

| 4.2.3     | Disk Recording Technique                   | 4-14 |

| 4.3       | Logic Circuits                             | 4-14 |

| 4.3.1     | Logic Timing                               | 4-14 |

| 4.3.2     | Search Operation                           | 4-17 |

| 4.3.3     | Write Operation                            | 4-21 |

| 4.3.4     | Read Operation                             | 4-23 |

| 4.3.5     | Data Track Selection and Lock-Out Switches | 4-26 |

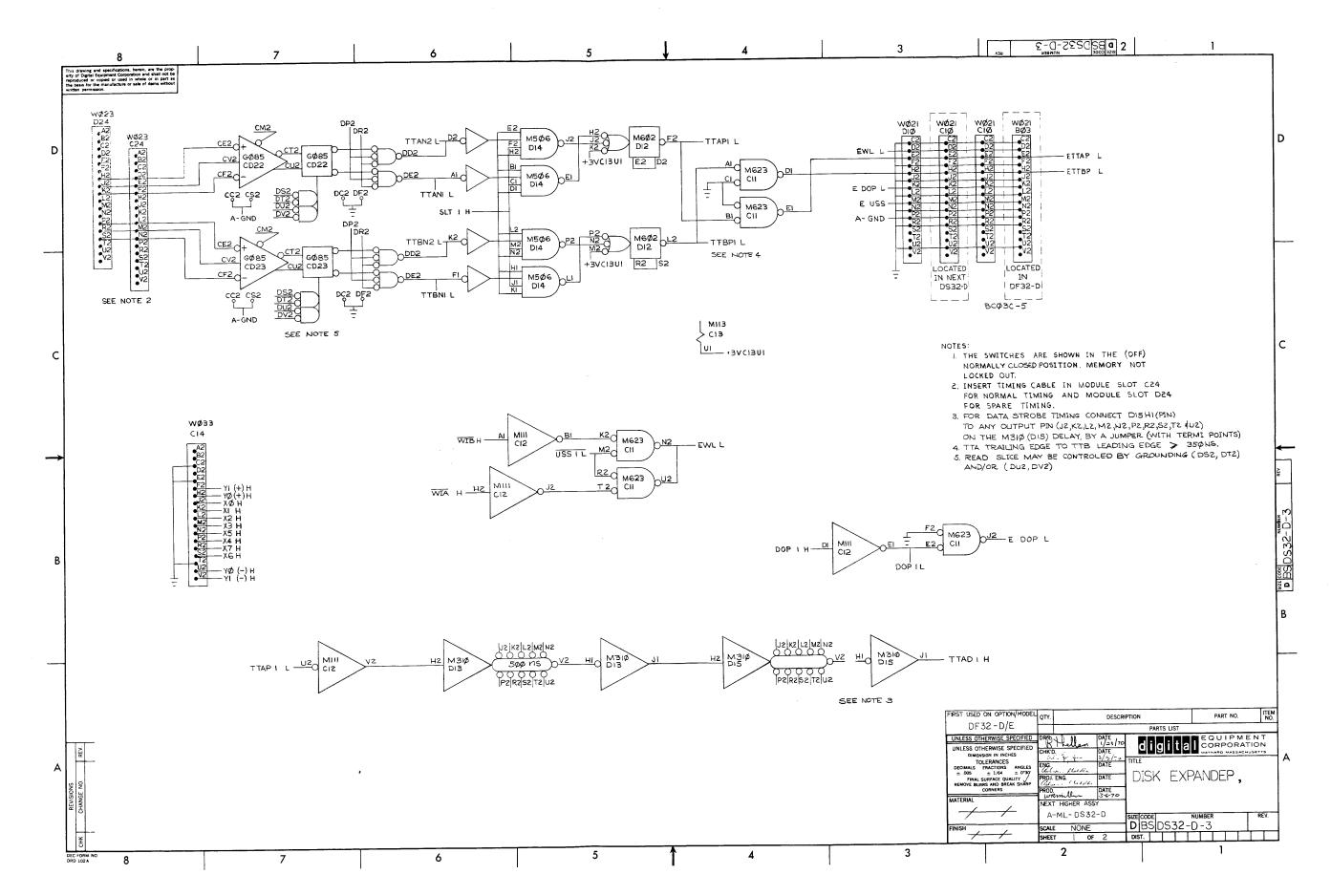

| 4.3.6     | Disk Expander Operation                    | 4-31 |

| 4.3.7     | Error Flags                                | 4-31 |

### CONTENTS (Cont)

|            |                                                             |          | Page |

|------------|-------------------------------------------------------------|----------|------|

| CHAPTER 5  | MAINTENANCE                                                 |          |      |

| 5.1        | General                                                     |          | 5-1  |

| 5.2        | Procedure for Cleaning the Disk ar                          | nd Heads | 5-1  |

| 5.2.1      | Preliminary Action                                          |          | 5-1  |

| 5.2.2      | Disk Removal and Cleaning                                   |          | 5-1  |

| 5.2.3      | Head Cleaning                                               |          | 5-2  |

| 5.2.4      | Disk Replacement                                            |          | 5-2  |

| 5.2.5      | Final Check                                                 |          | 5-4  |

| 5.3        | Adjustments                                                 |          | 5-5  |

| 5.4        | Troubleshooting                                             |          | 5-9  |

| 5.5        | Module List                                                 |          | 5-11 |

| CHAPTER 6  | ENGINEERING DRAWINGS                                        |          | 6-1  |

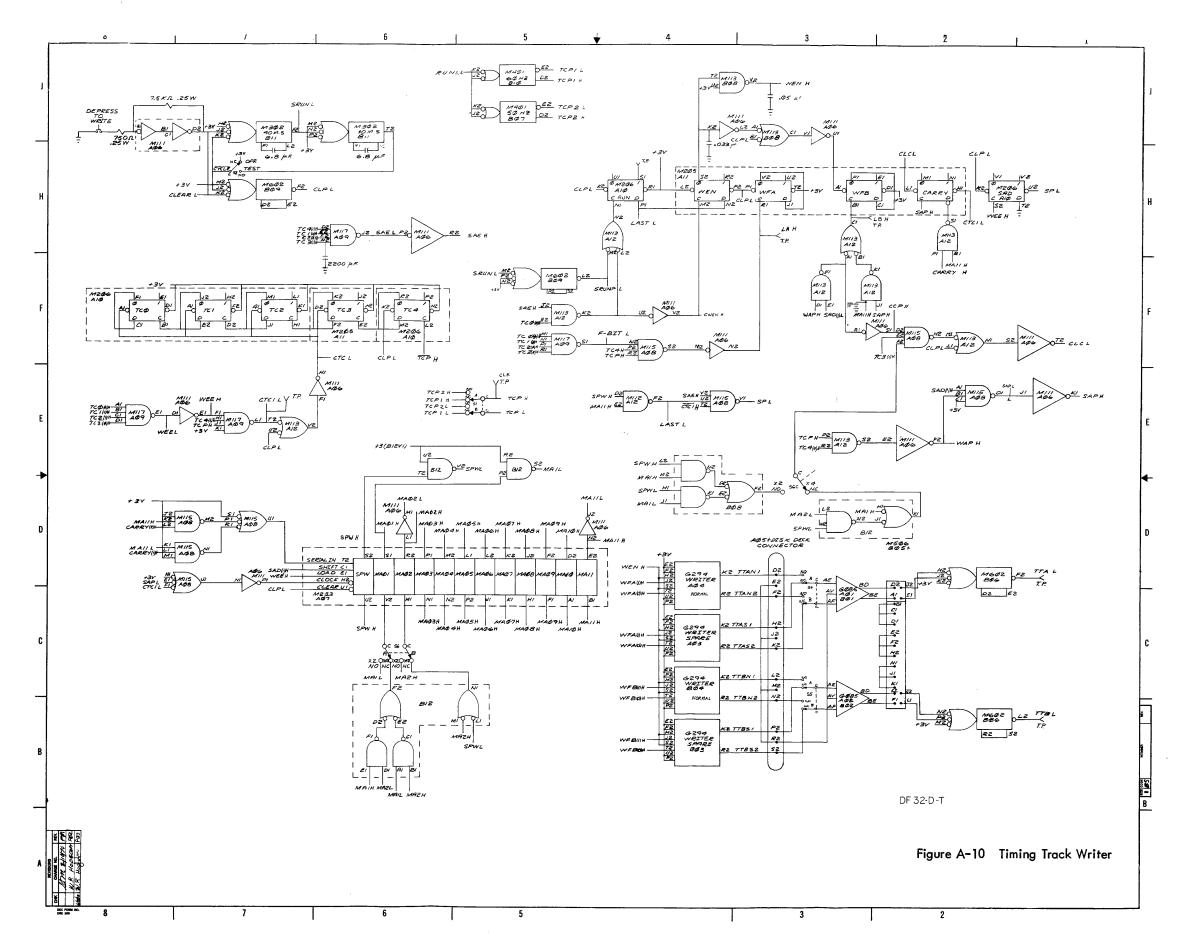

| APPENDIX A | TIMING TRACK WRITER                                         |          |      |

| A.1        | Introduction                                                |          | A-1  |

| A.2        | Operation                                                   |          | A-1  |

| A.3        | Operating Switches                                          |          | A-2  |

| A.4        | Theory of Operation                                         |          | A-2  |

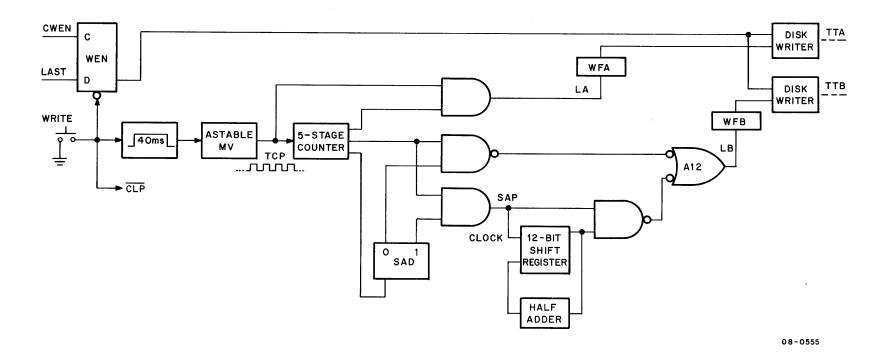

| A.4.1      | General                                                     |          | A-2  |

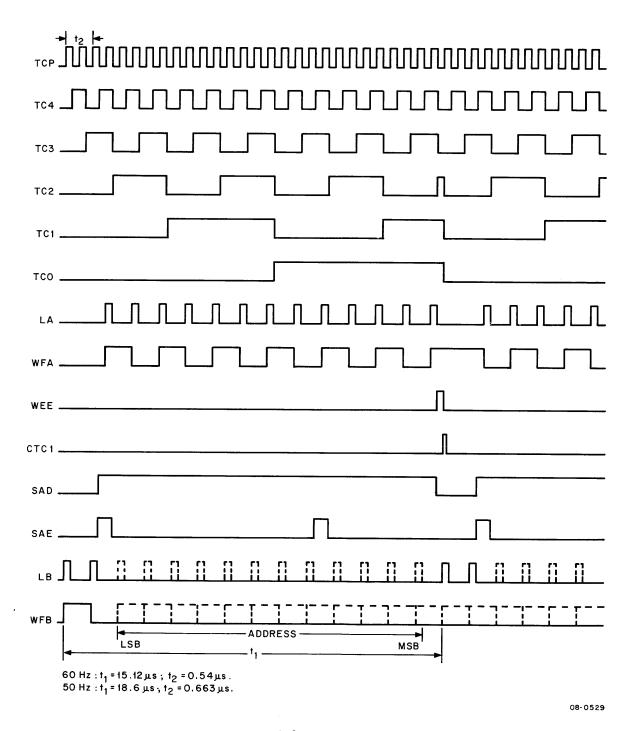

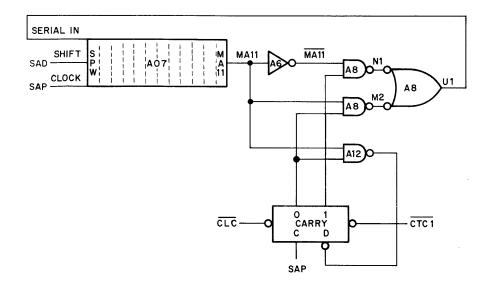

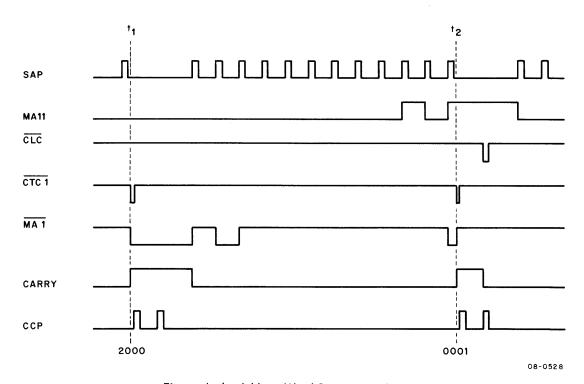

| A.4.2      | Detailed Logic Discussion                                   |          | A-4  |

| A.5        | Adjustment Procedure                                        |          | A-11 |

|            | ILLUSTRATIONS                                               |          |      |

| Figure No. | Title                                                       | Art No.  | Page |

| 1-1        | Disk and Logic Module Assembly                              | 5077-2   | 1-3  |

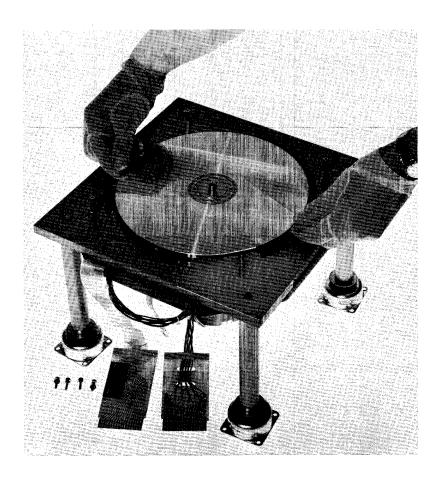

| 1-2        | Disk Assembly with Top Dust<br>Cover Removed                | 3490-3   | 1-5  |

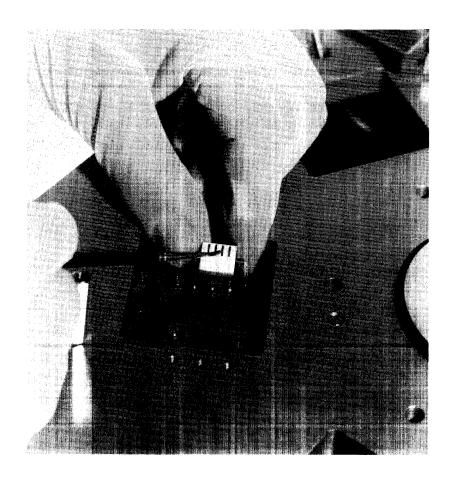

| 1-3        | Disk Assembly with Disk Removed and Recording Heads Exposed | 3490-1   | 1-6  |

| 2-1        | DF32-D/DS32-D Mounting Locations                            | 08-0578  | 2-2  |

| 3-1        | DE32-D Front Panel                                          | 5022_3   | 3_2  |

### ILLUSTRATIONS (Cont)

| Figure No.   | Title                                                                   | Art No. | Page         |

|--------------|-------------------------------------------------------------------------|---------|--------------|

| 3-2          | DS32-D Front Panel                                                      | 5151-2  | 3-2          |

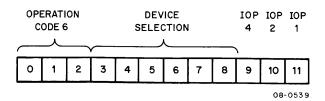

| 3-3          | IOT Instructions                                                        | 08-0539 | 3-3          |

| 3-4          | Programming Example                                                     |         | 3-8          |

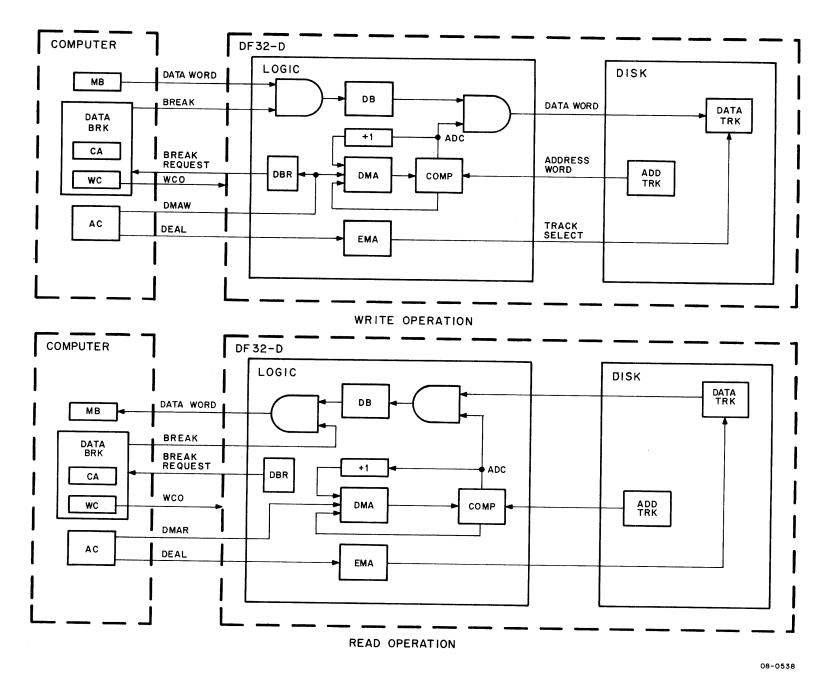

| 4-1          | DF32-D Block Diagram, Write and Read Operations                         | 08-0538 | 4-4          |

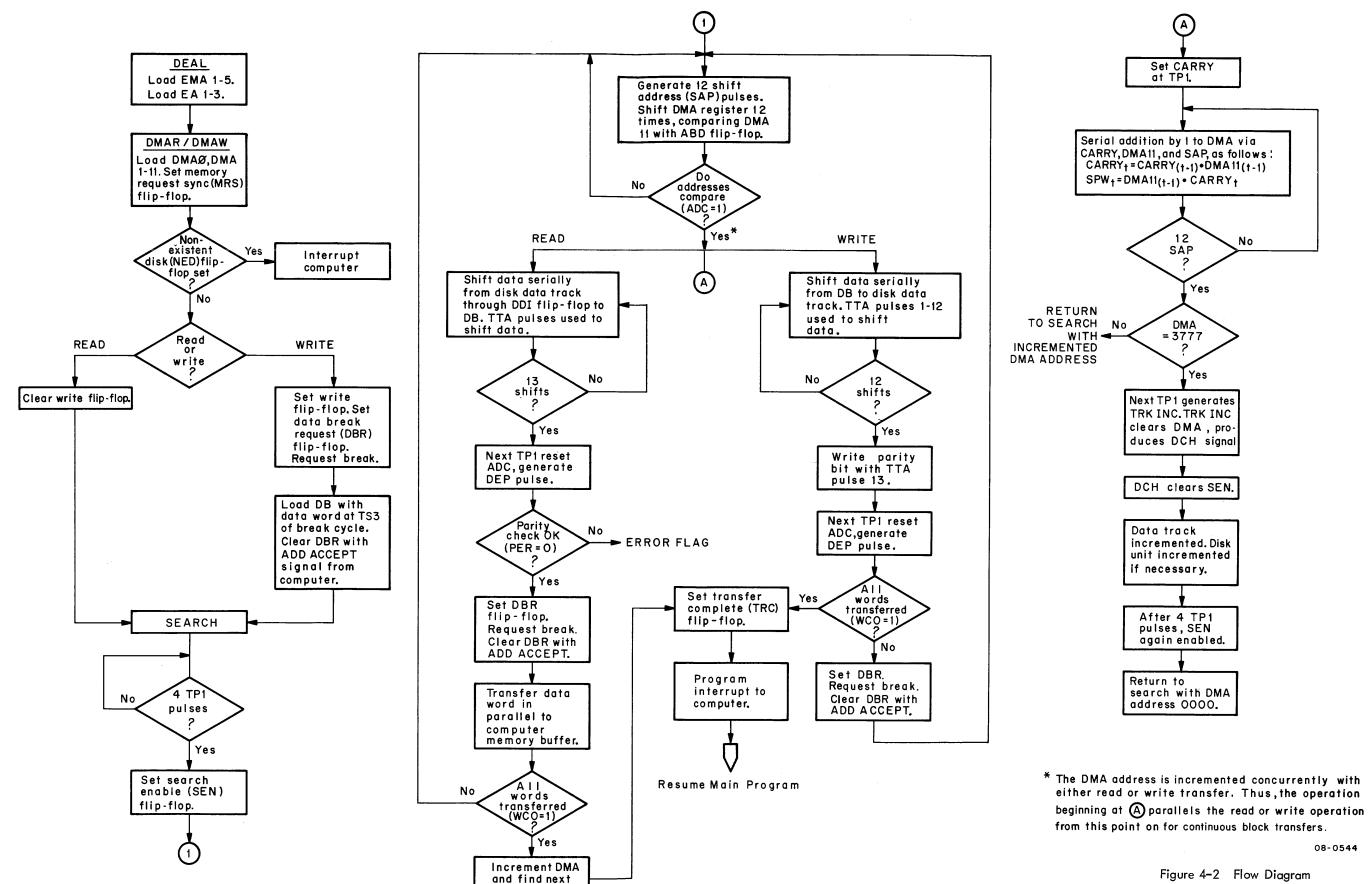

| 4-2          | Flow Diagram                                                            | 08-0544 | 4-7          |

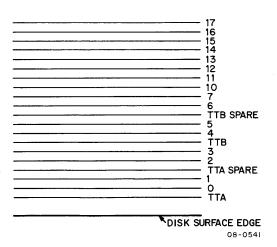

| 4-3          | Disk Track Order                                                        | 08-0541 | 4-9          |

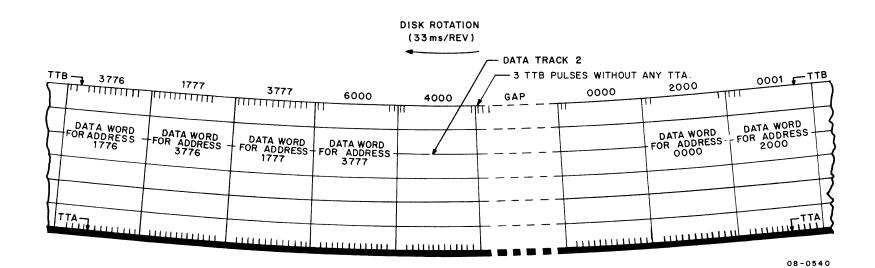

| 4-4          | Disk Format                                                             | 08-0540 | 4-10         |

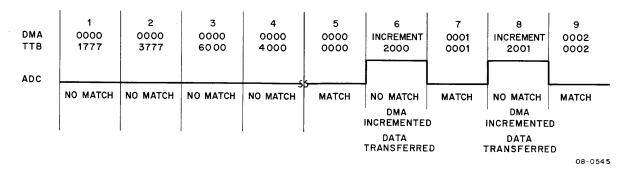

| 4-5          | Search/Transfer Operation Timing                                        | 08-0545 | 4-11         |

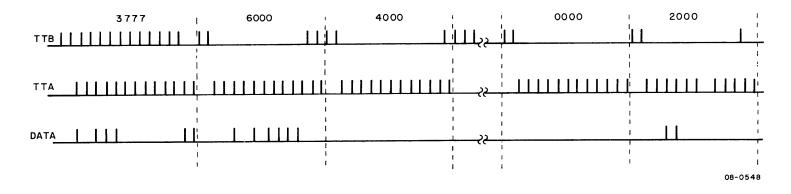

| 4-6          | Disk Track Timing                                                       | 08-0548 | 4-13         |

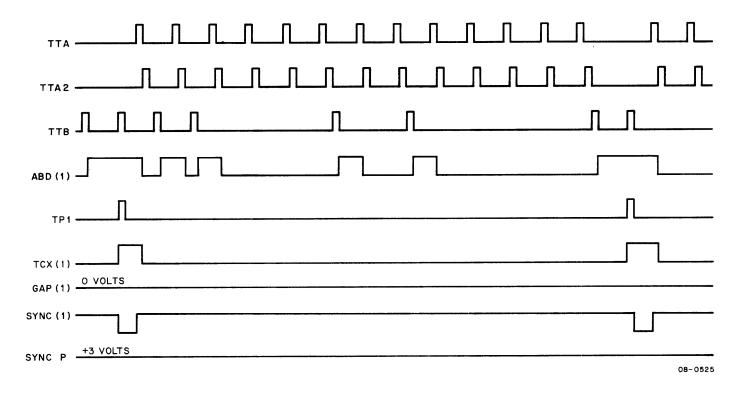

| 4-7          | Basic Timing Signals                                                    | 08-0525 | 4-15         |

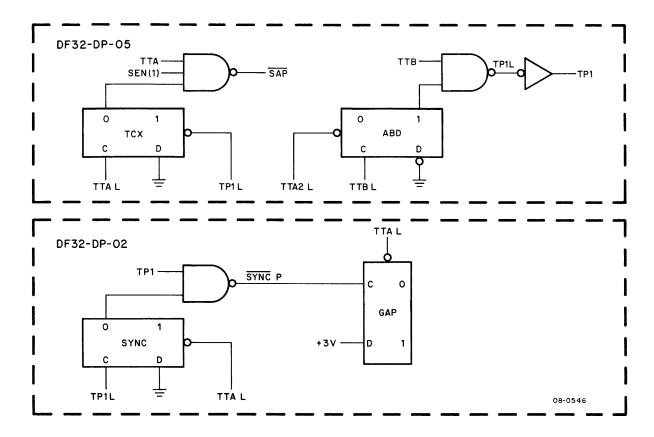

| 4-8          | Basic Timing Logic                                                      | 08-0546 | 4-16         |

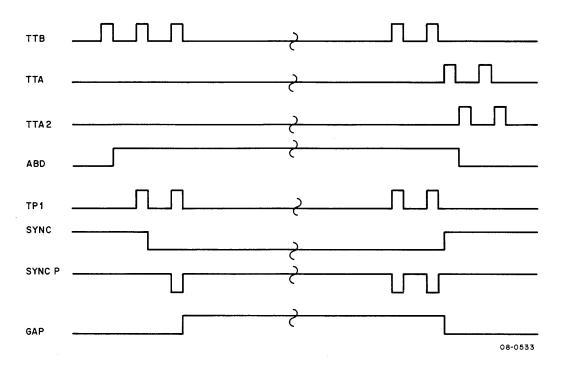

| 4-9          | GAP Timing                                                              | 08-0533 | 4-17         |

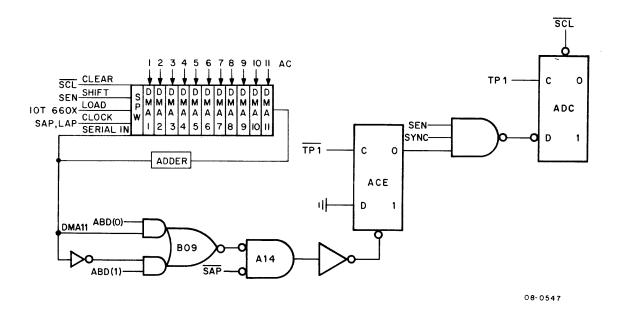

| 4-10         | Address Search, Simplified Logic<br>Block Diagram                       | 08-0547 | 4-18         |

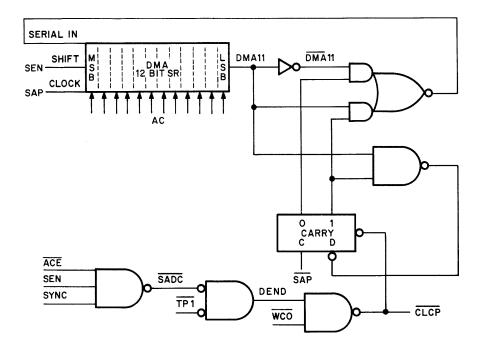

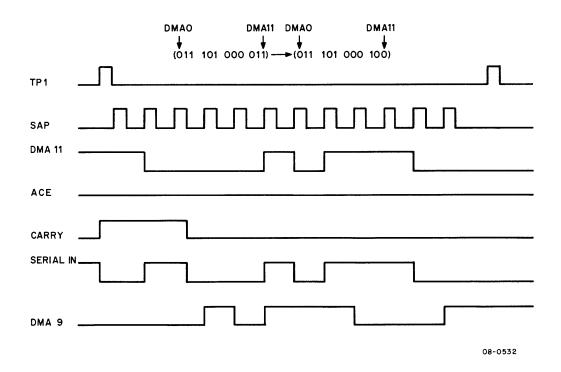

| 4-11         | DMA Incrementation and Timing                                           | 08-0532 | 4-20         |

| 4-12         | Write Operation Simplified<br>Logic – Block Diagram                     | 08-0535 | 4-22         |

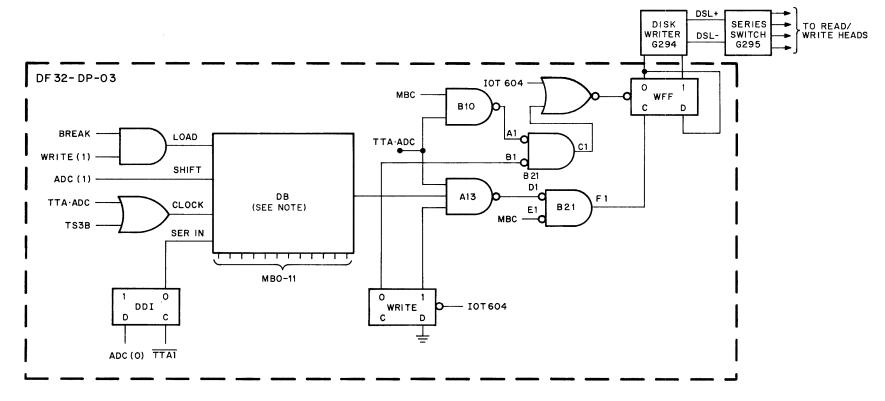

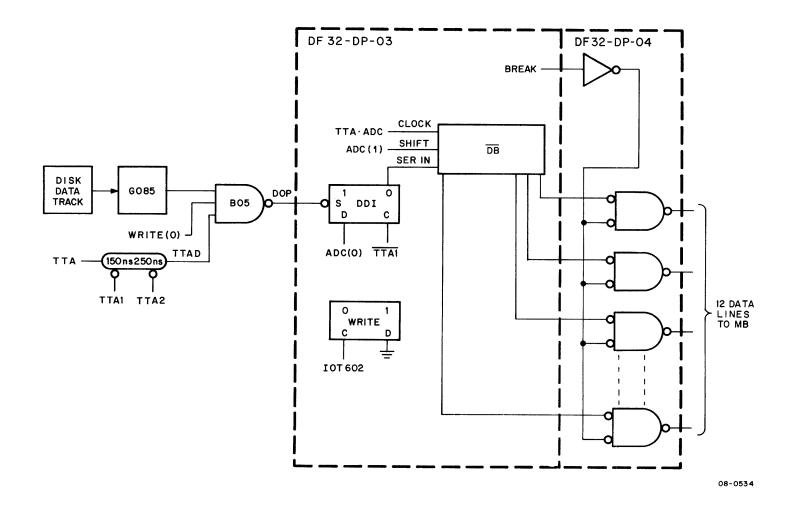

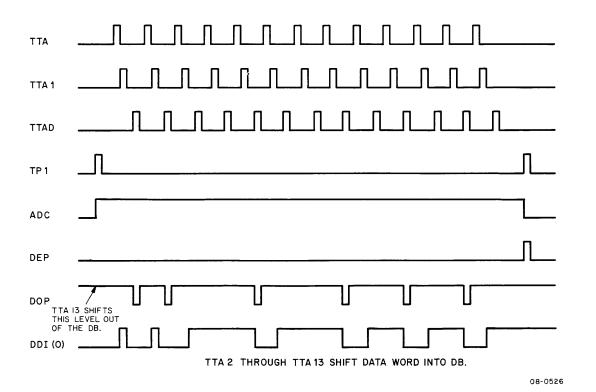

| 4-13         | Read Operation Simplified<br>Logic – Block Diagram                      | 08-0534 | 4-24         |

| 4-14         | DB Loading of Data Word –<br>Timing Diagram                             | 08-0526 | 4-25         |

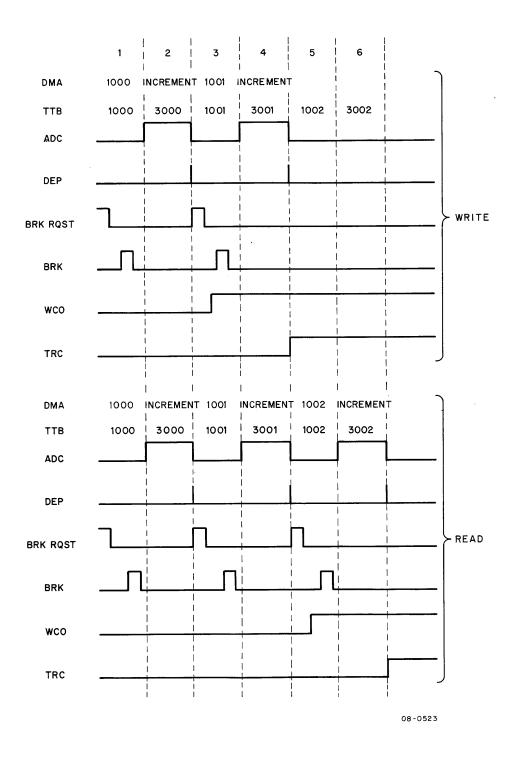

| 4-15         | Read/Write Termination                                                  | 08-0523 | 4-27         |

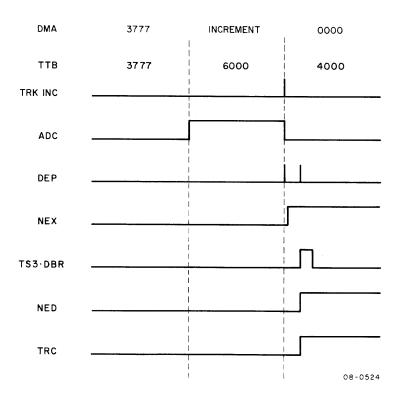

| 4-16         | Last Word/Last Disk Timing<br>Diagram                                   | 08-0524 | 4-28         |

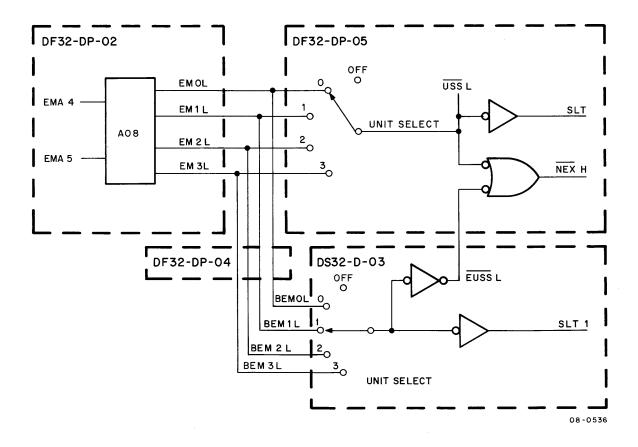

| 4-17         | Unit Select Circuit                                                     | 08-0536 | 4-29         |

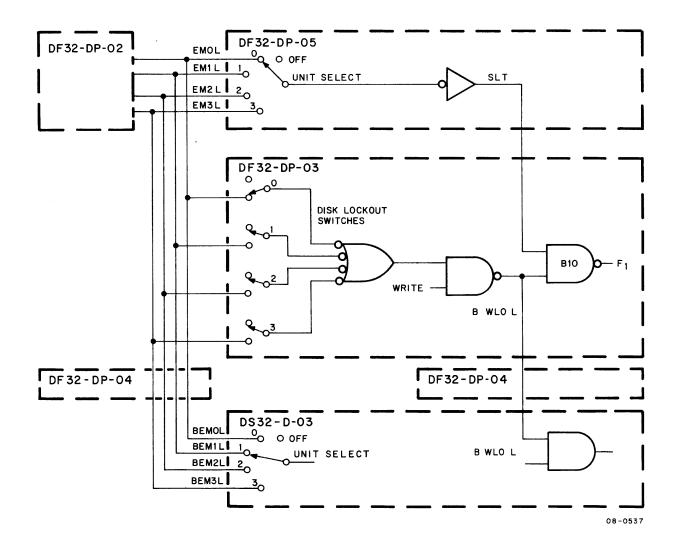

| 4-18         | Lock-Out Select                                                         | 08-0537 | 4-30         |

| 5-1          | Disk Removal                                                            | 3490-2  | 5-3          |

| 5-2          | Head Cleaning                                                           | 3490-4  | 5-4          |

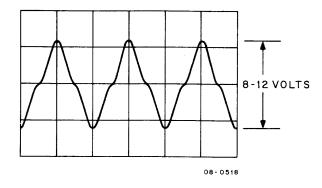

| 5-3          | Output Signal at Pin AT (CT)                                            | 08-0518 | 5 <b>-</b> 7 |

| 5 <b>-</b> 4 | Output Signal at Pin BD (DD)                                            | 08-0519 | 5-7          |

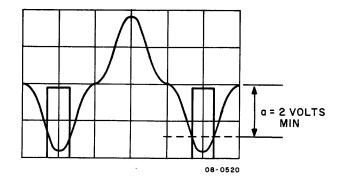

| 5-5          | Slice Level Obtained by Combining Outputs from Pins (CT) AT and (DD) BD | 08-0520 | <b>5-</b> 7  |

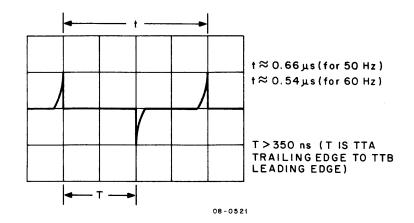

| 5-6          | TTA and TTB Pulse                                                       | 08-0521 | 5-8          |

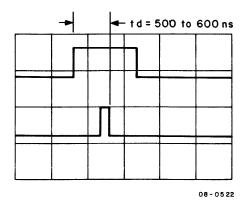

| 5-7          | TTAD Pulse and Associated<br>Data Pulse                                 | 08-0522 | 5-8          |

### ILLUSTRATIONS (Cont)

| Figure No. | Title                         | Art No. | Page         |

|------------|-------------------------------|---------|--------------|

| A-1        | DF32-D-15 Timing Track Writer | 5391-1  |              |

| A-2        | TTW Block Diagram             | 08-0555 | A <b>-</b> 3 |

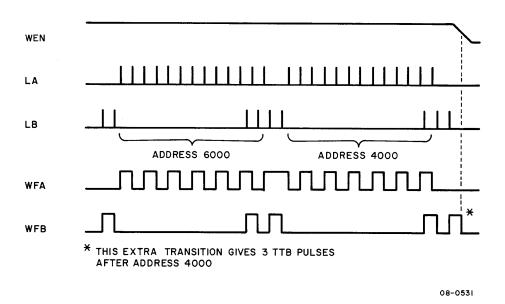

| A-3        | Timing Diagram                | 08-0529 | A-5          |

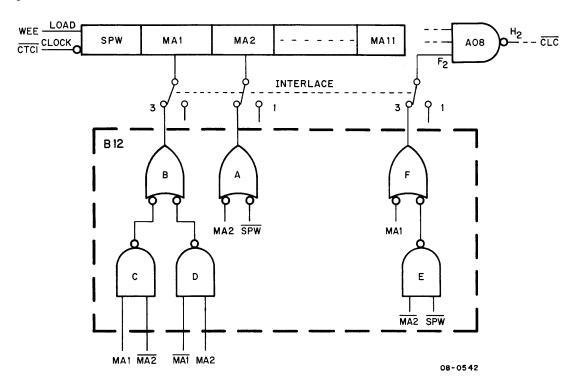

| A-4        | Address Word Incrementation   | 08-0528 | A-8          |

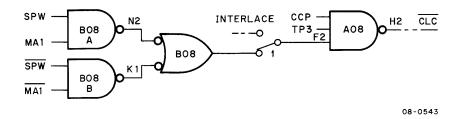

| A-5        | Address Increment             | 08-0543 | A-9          |

| A-6        | Last TTB Generation           | 08-0531 | A-9          |

| A-7        | Alternate Address Logic       | 08-0542 | A-10         |

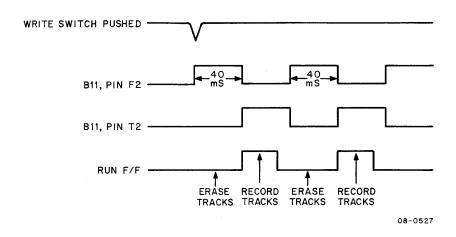

| A-8        | Timing Write Cycle (Test)     | 08-0527 | A-11         |

| A-9        | LA-LB Relationship            | 08-0530 | A-12         |

| A-10       | Timing Track Writer           |         | A-13         |

### ENGINEERING DRAWINGS

| Drawing No.     | Title                                     | Page |

|-----------------|-------------------------------------------|------|

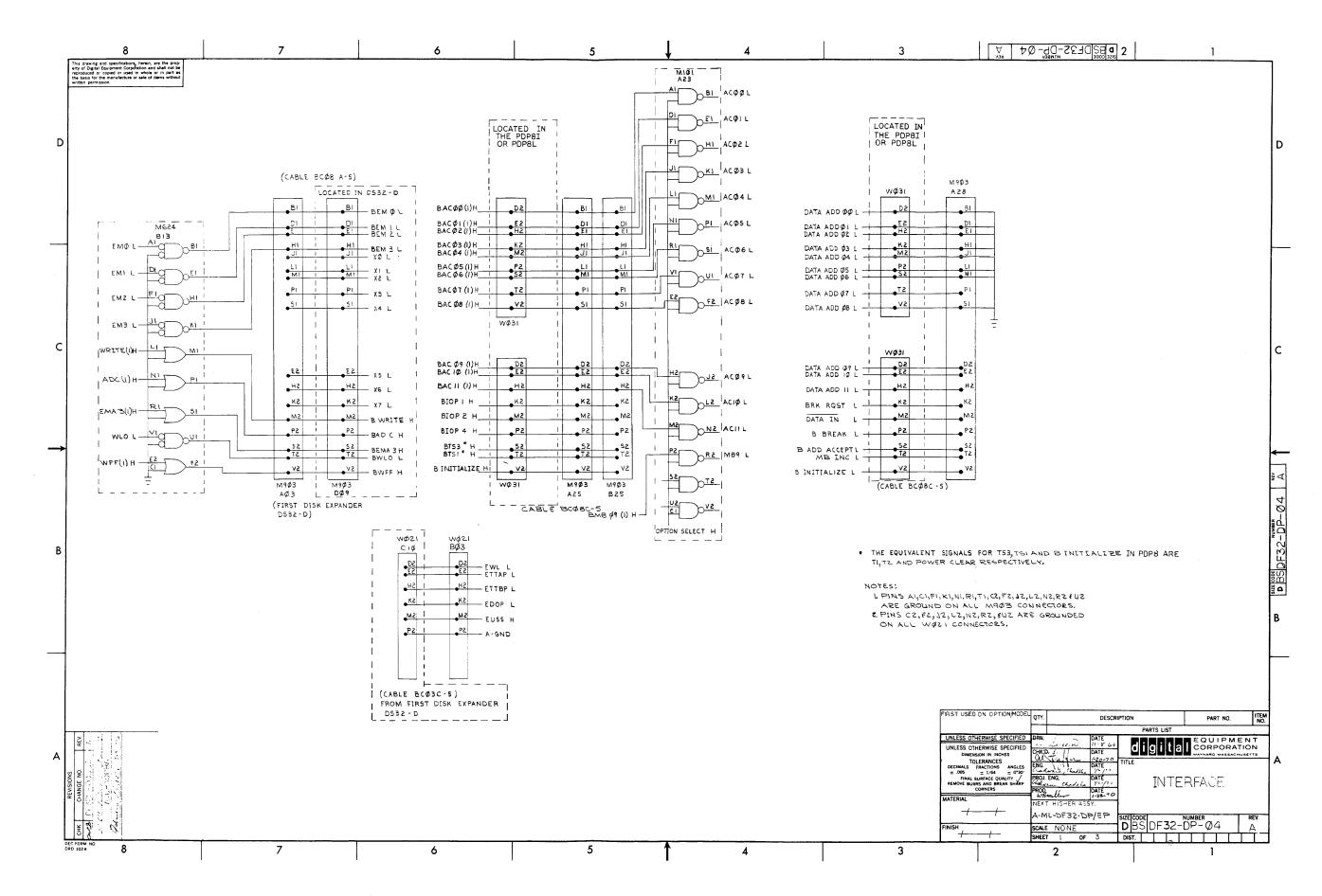

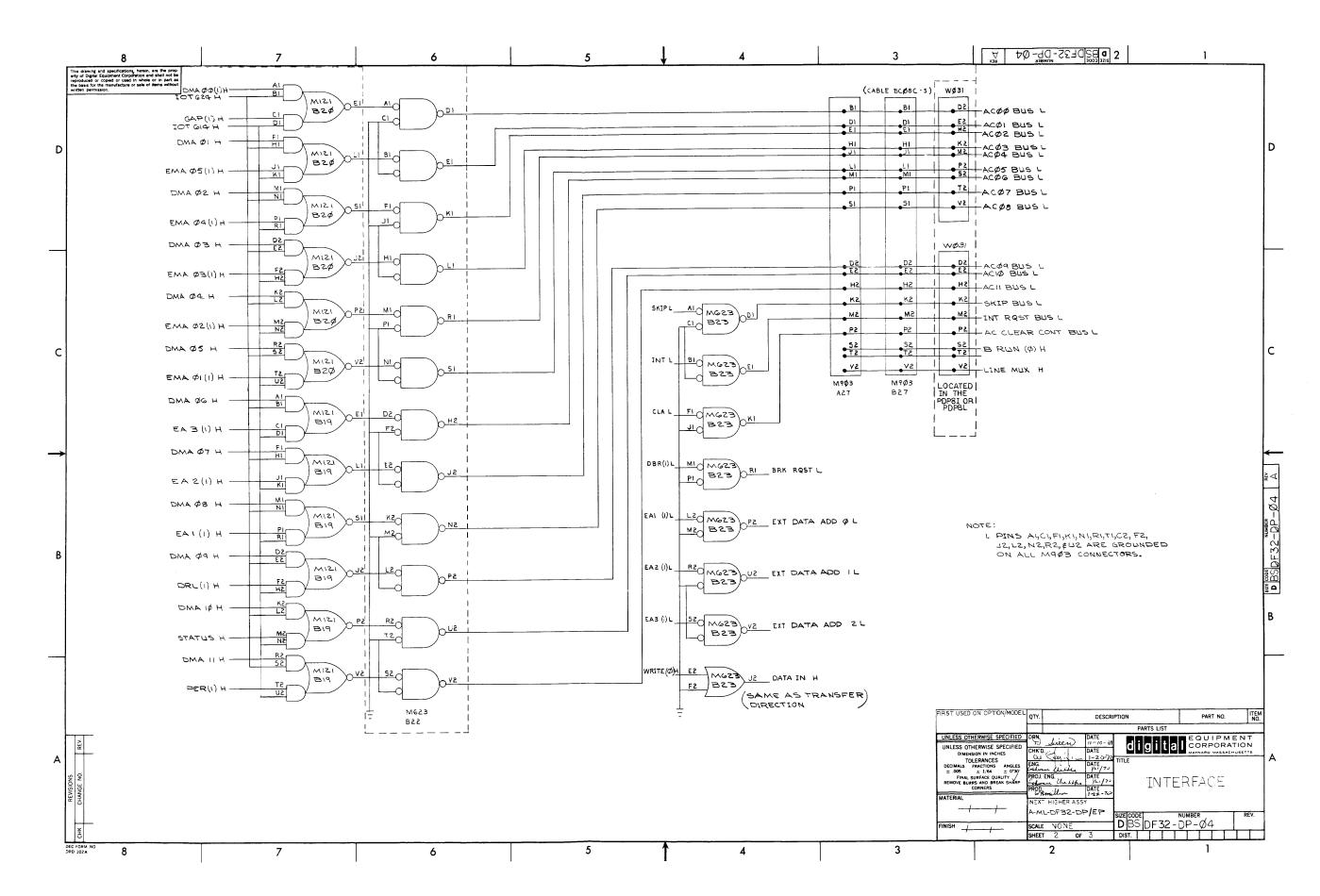

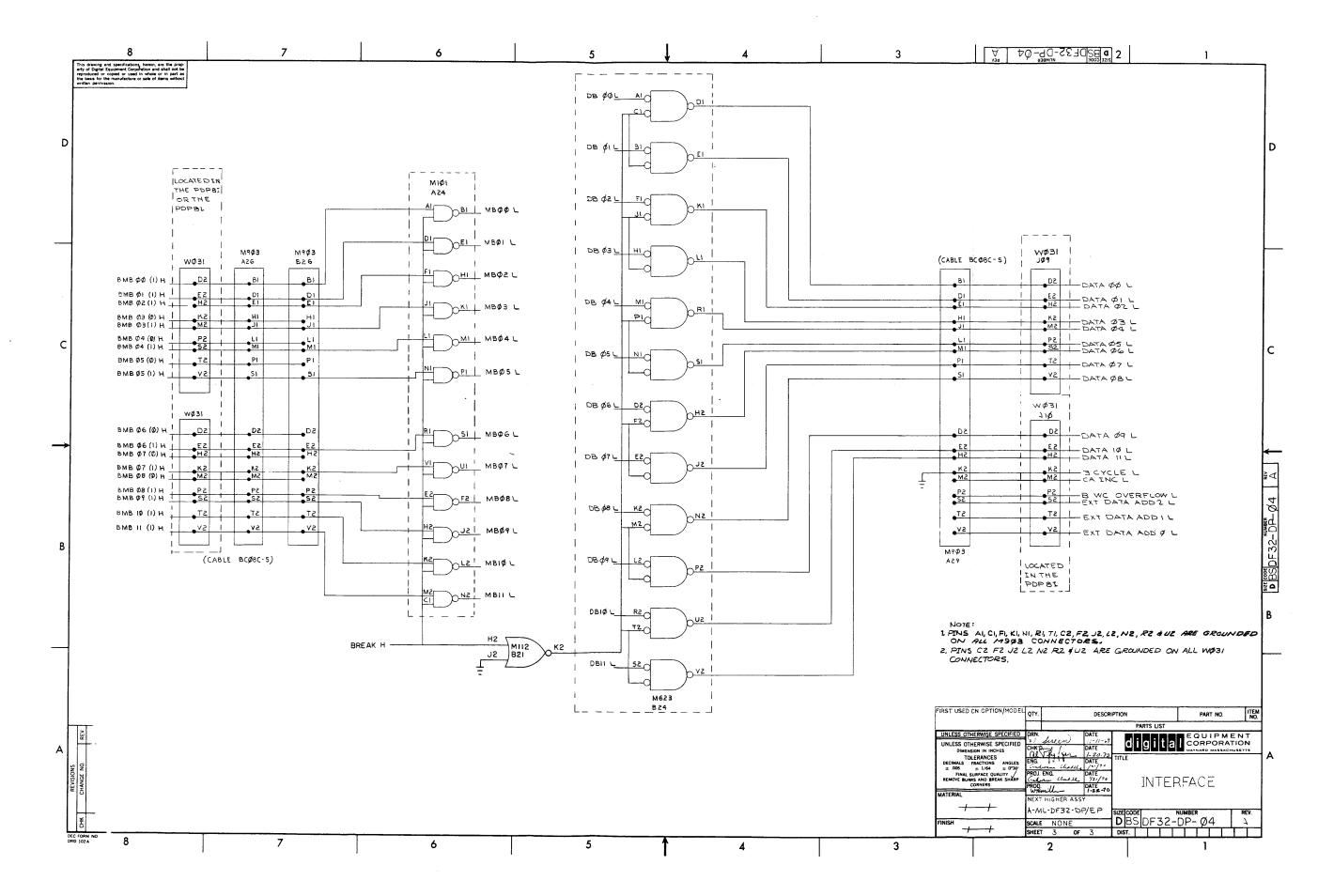

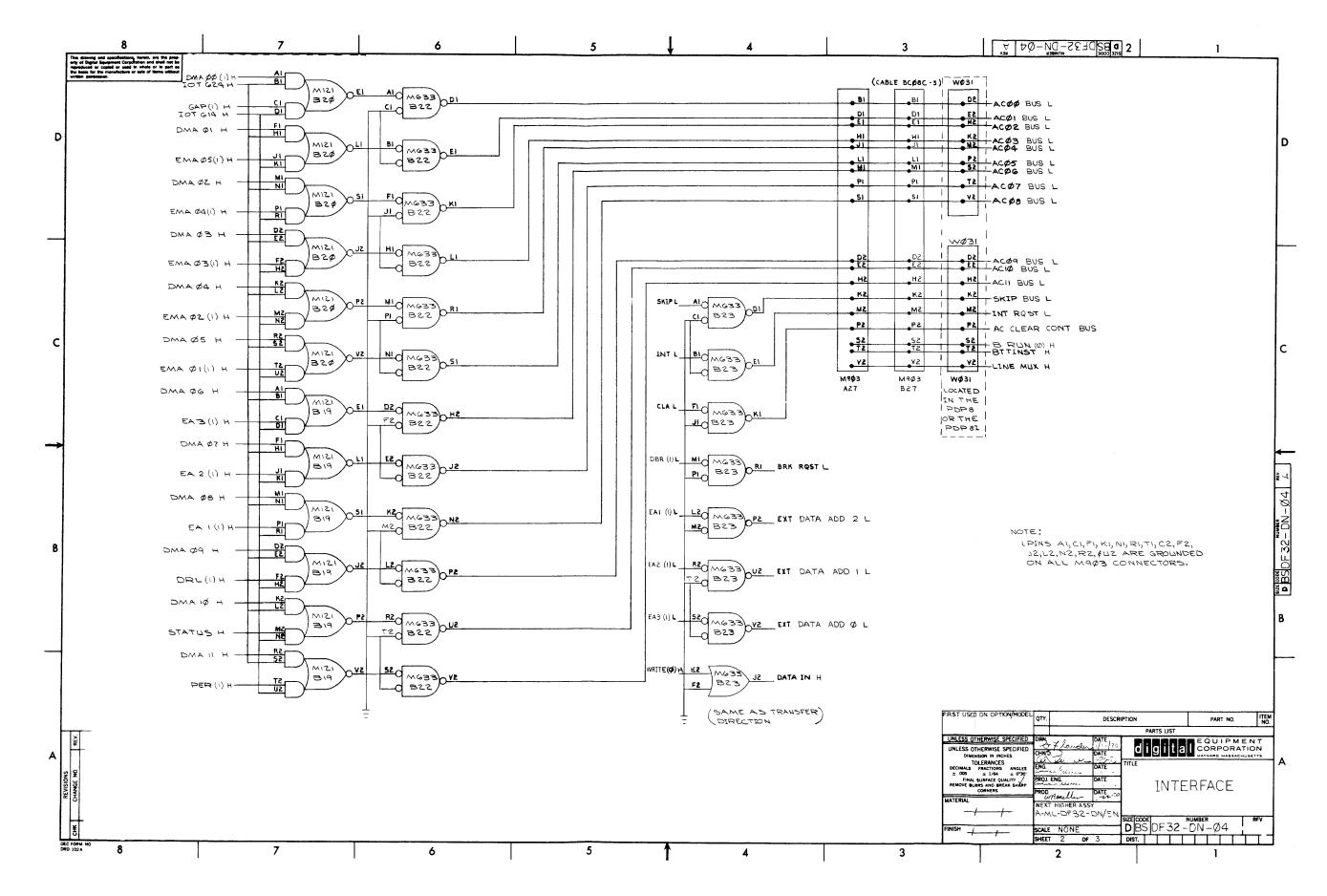

| D-BS-DF32-DP-04 | Interface (3 sheets)                      | 6-3  |

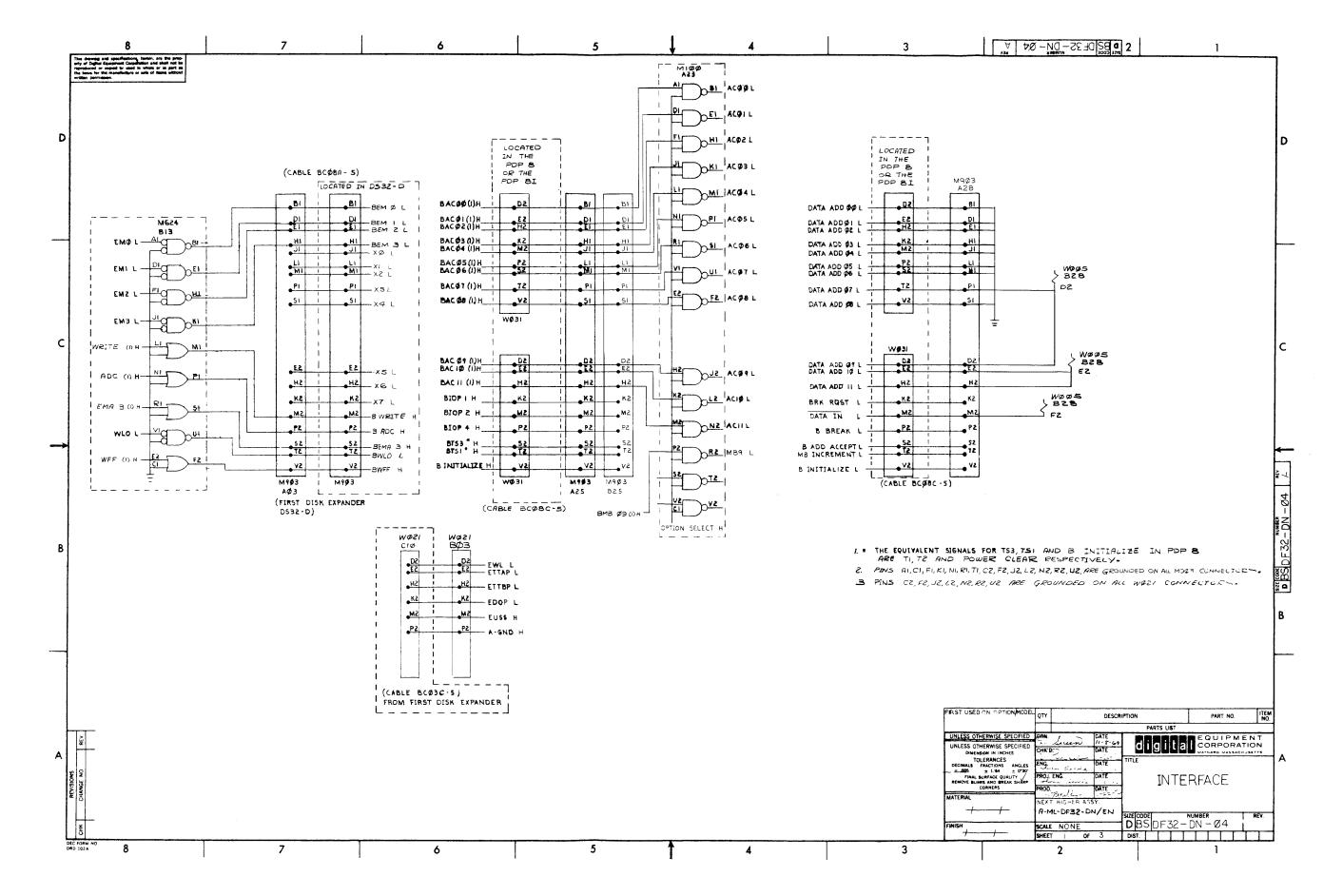

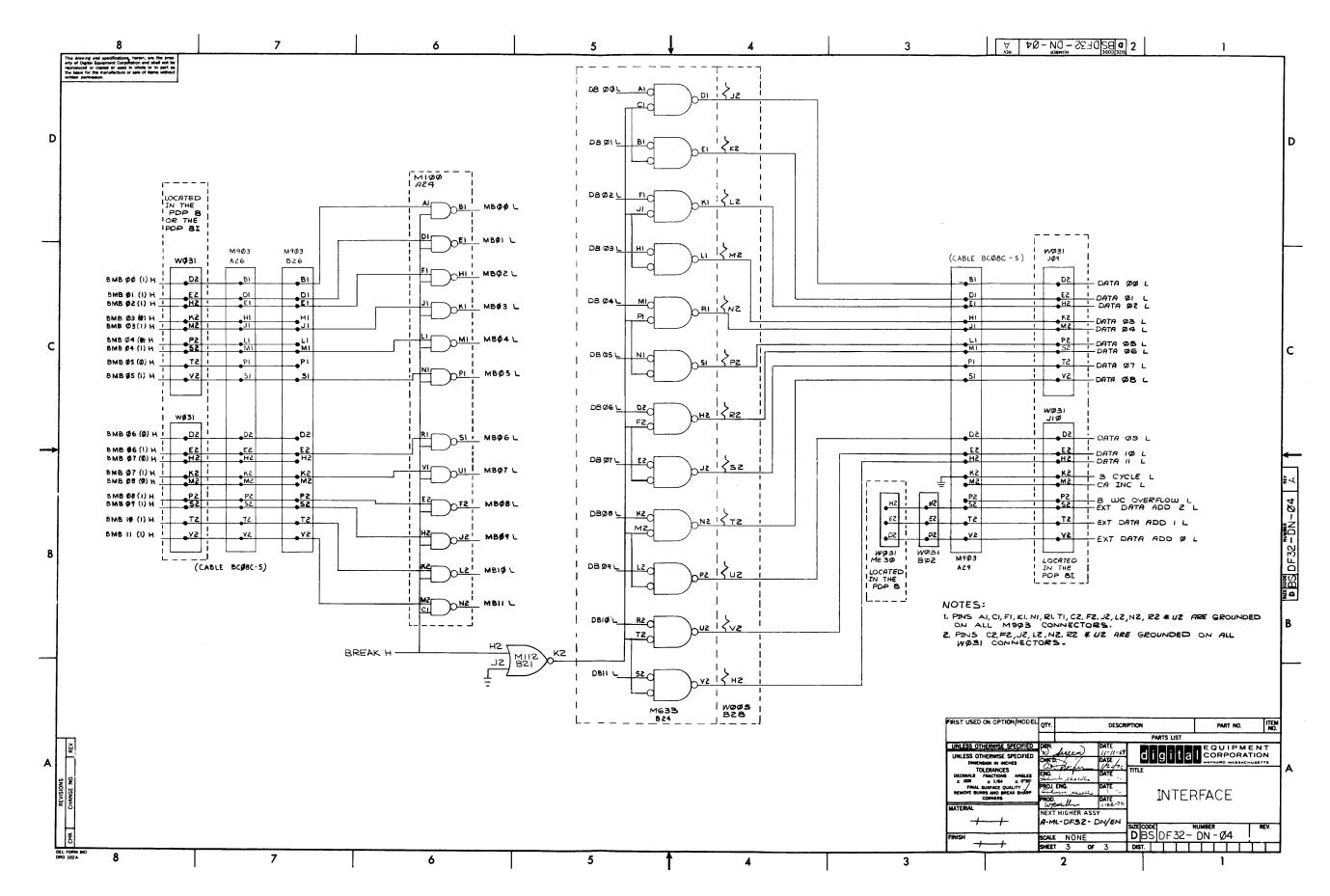

| D-BS-DF32-DN-04 | Interface (3 sheets)                      | 6-9  |

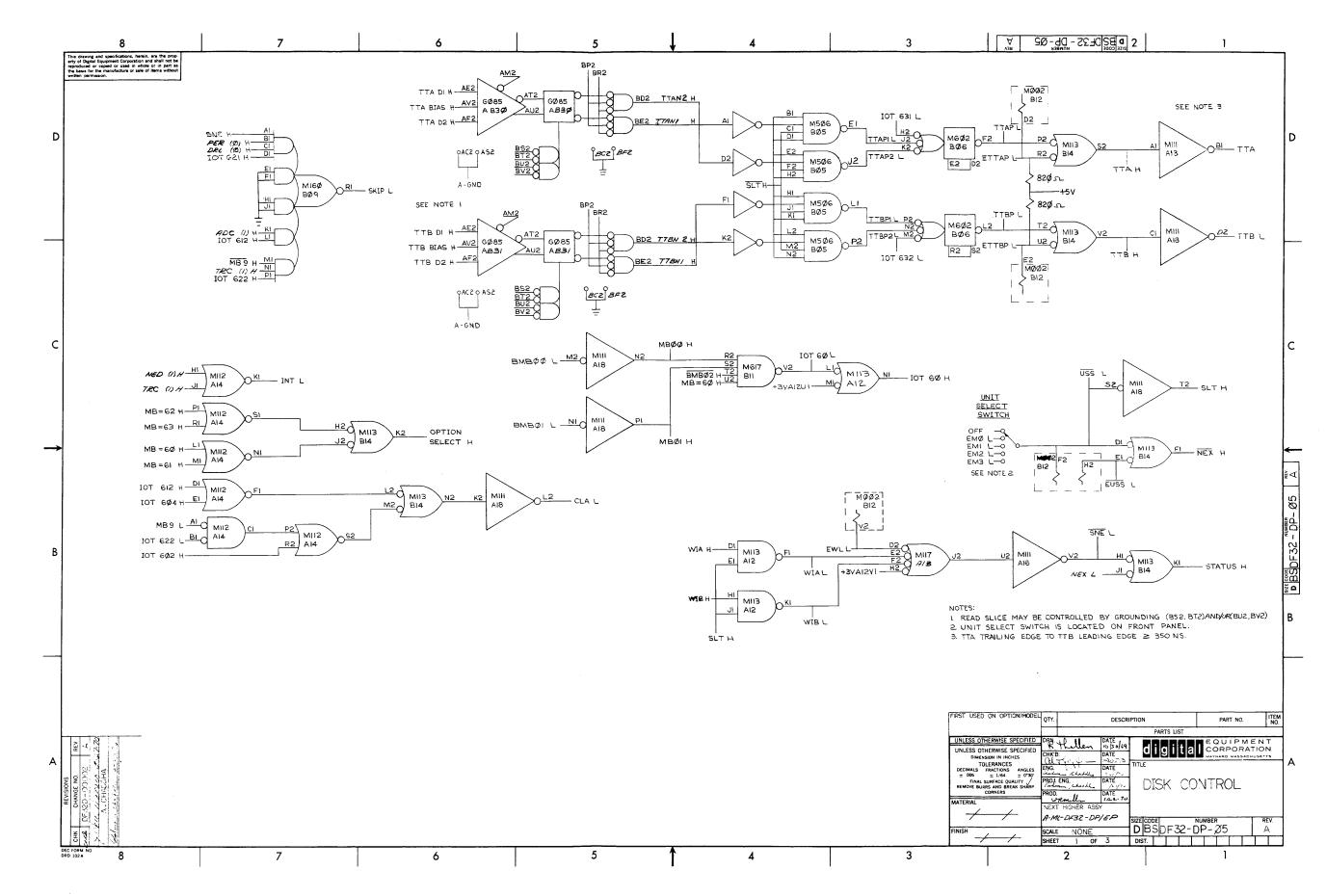

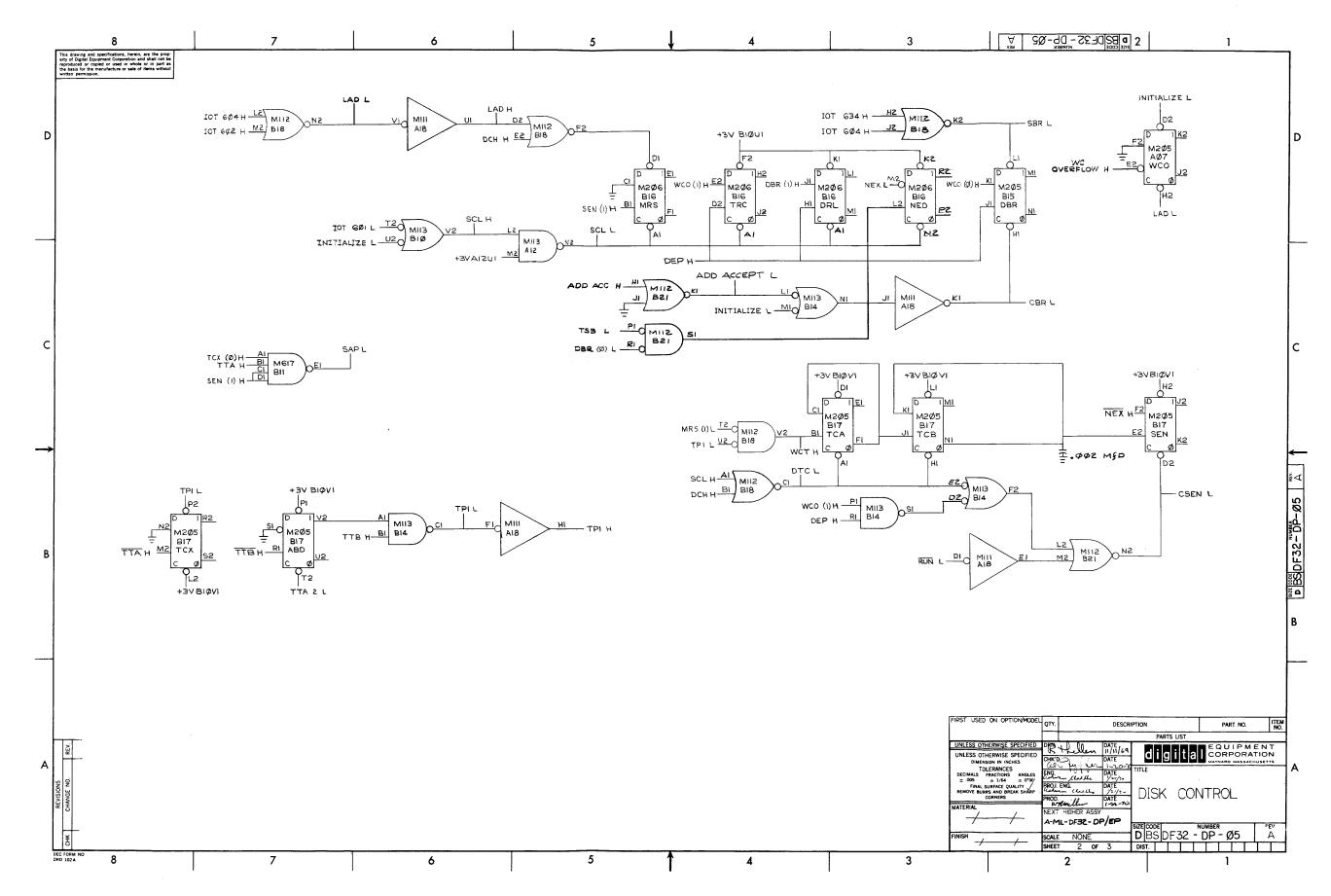

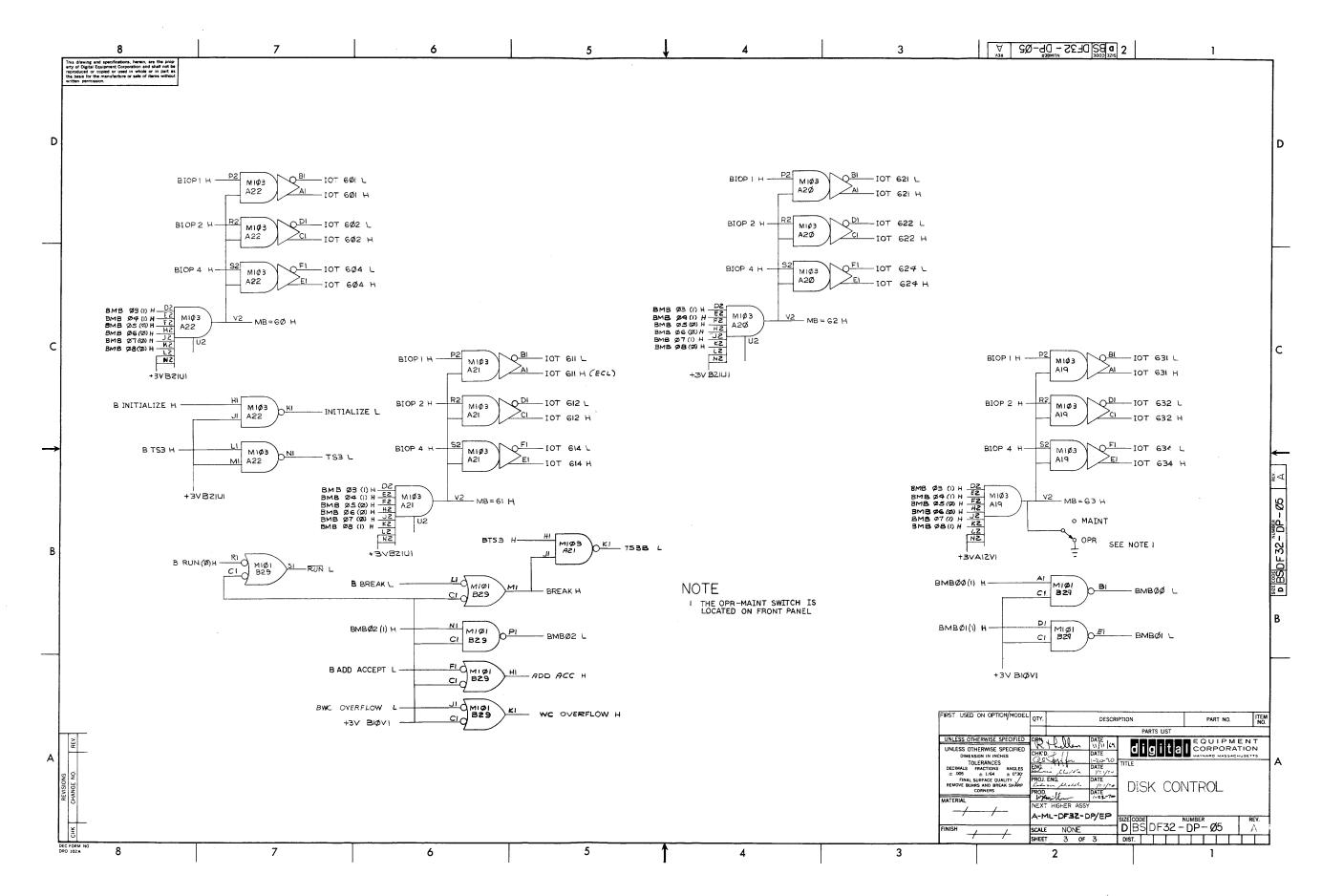

| D-BS-DF32-DP-05 | Disk Control (3 sheets)                   | 6-15 |

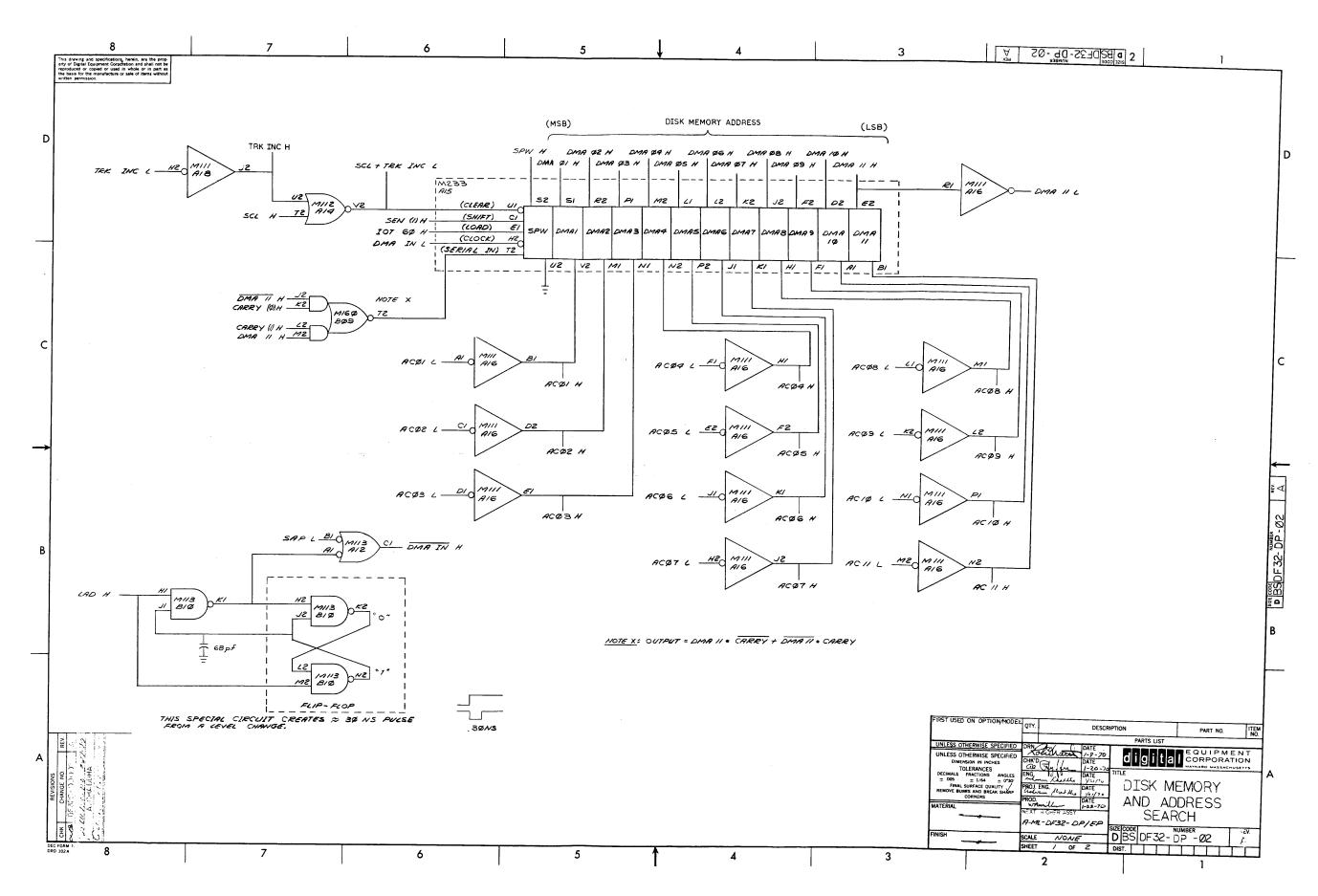

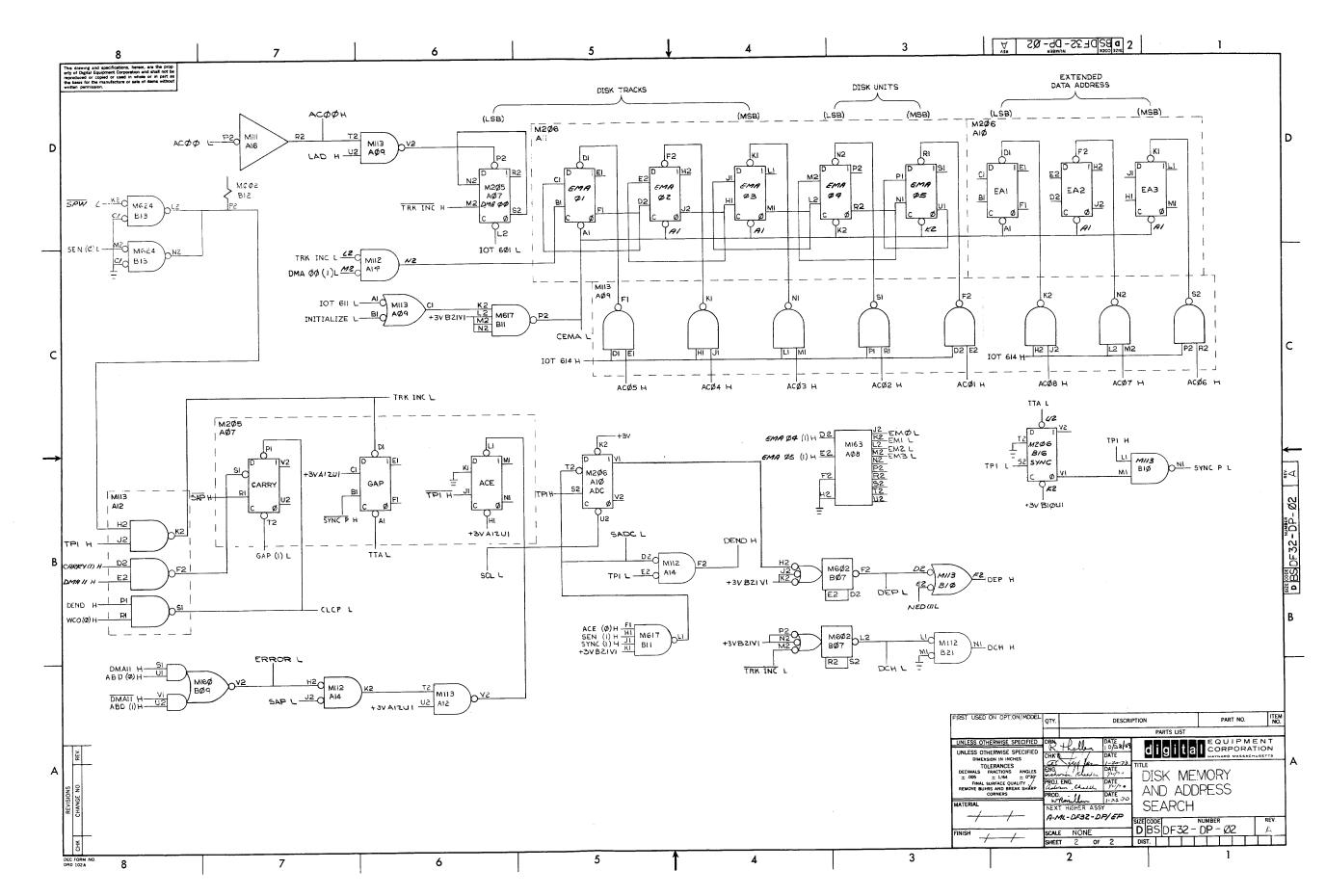

| D-BS-DF32-DP-02 | Disk Memory and Address Search (2 sheets) | 6-21 |

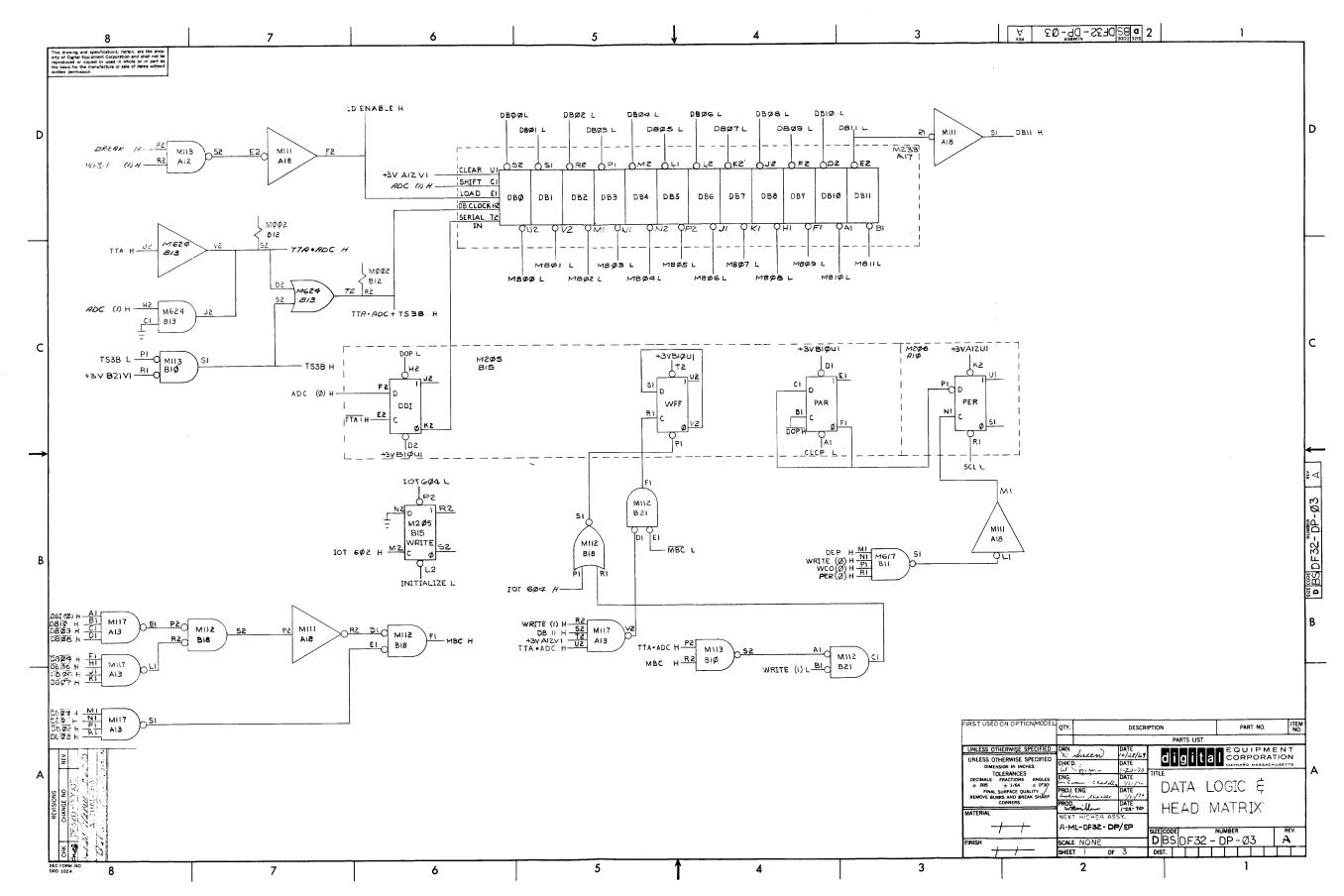

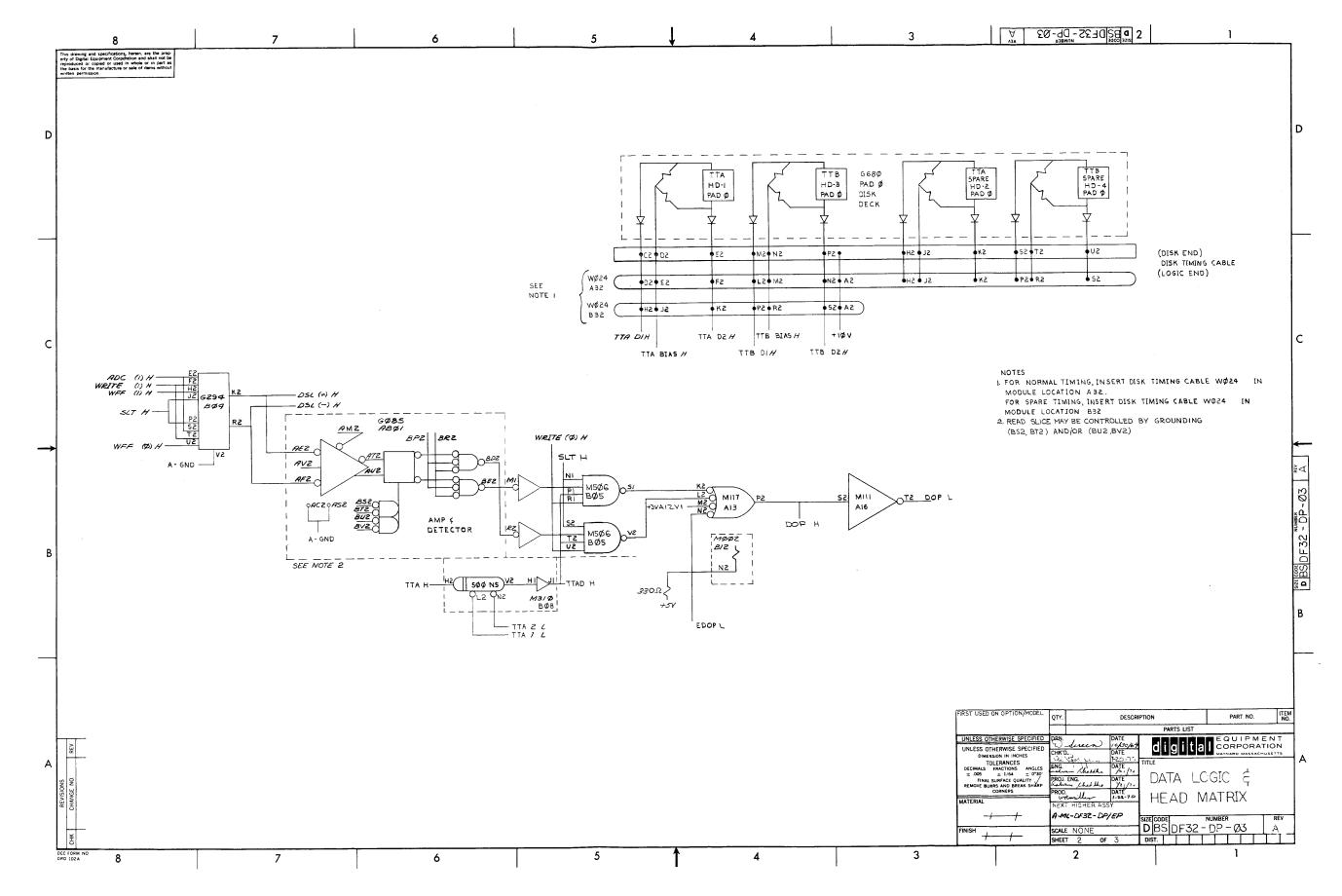

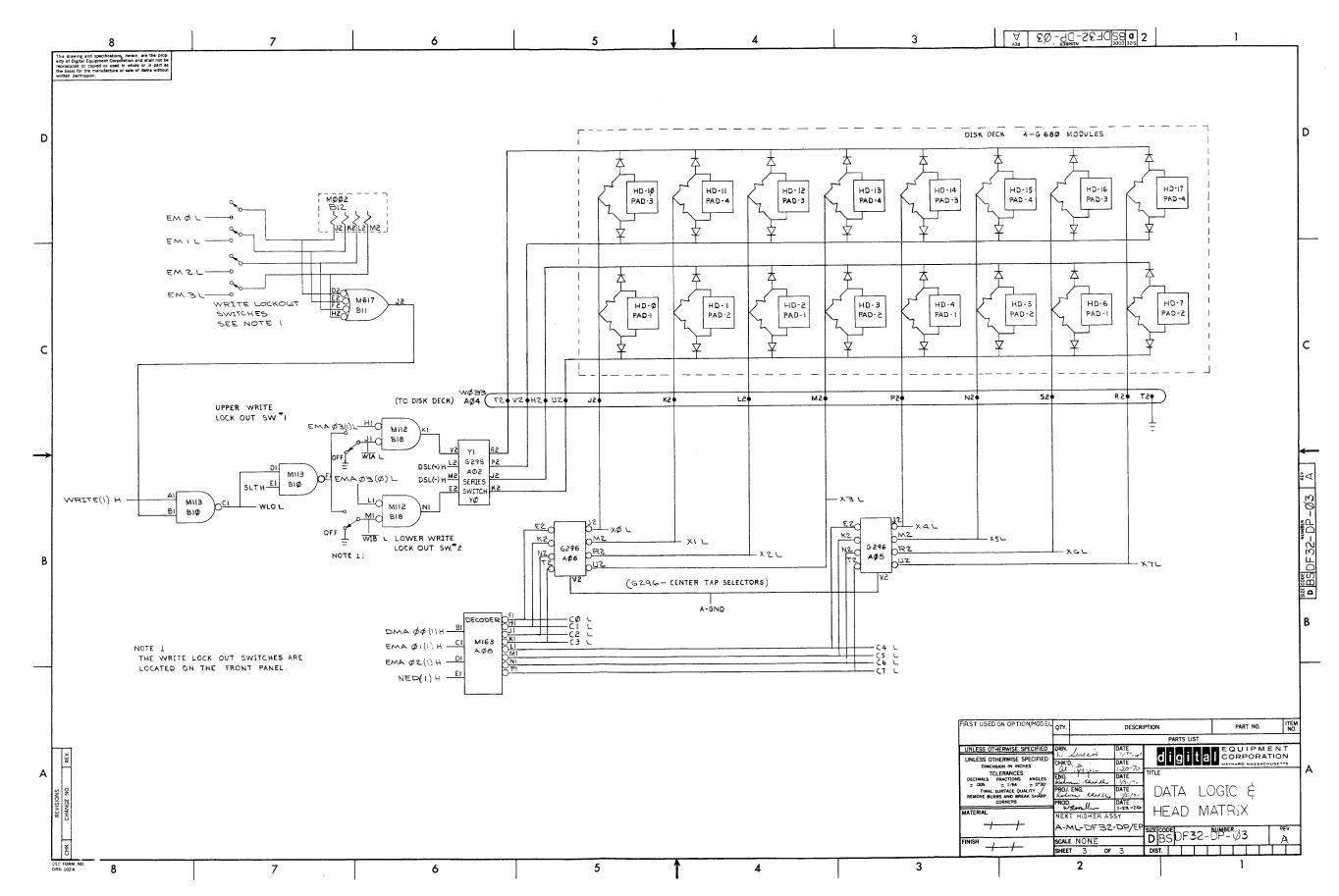

| D-BS-DF32-DP-03 | Data Logic and Head Matrix (3 sheets)     | 6-25 |

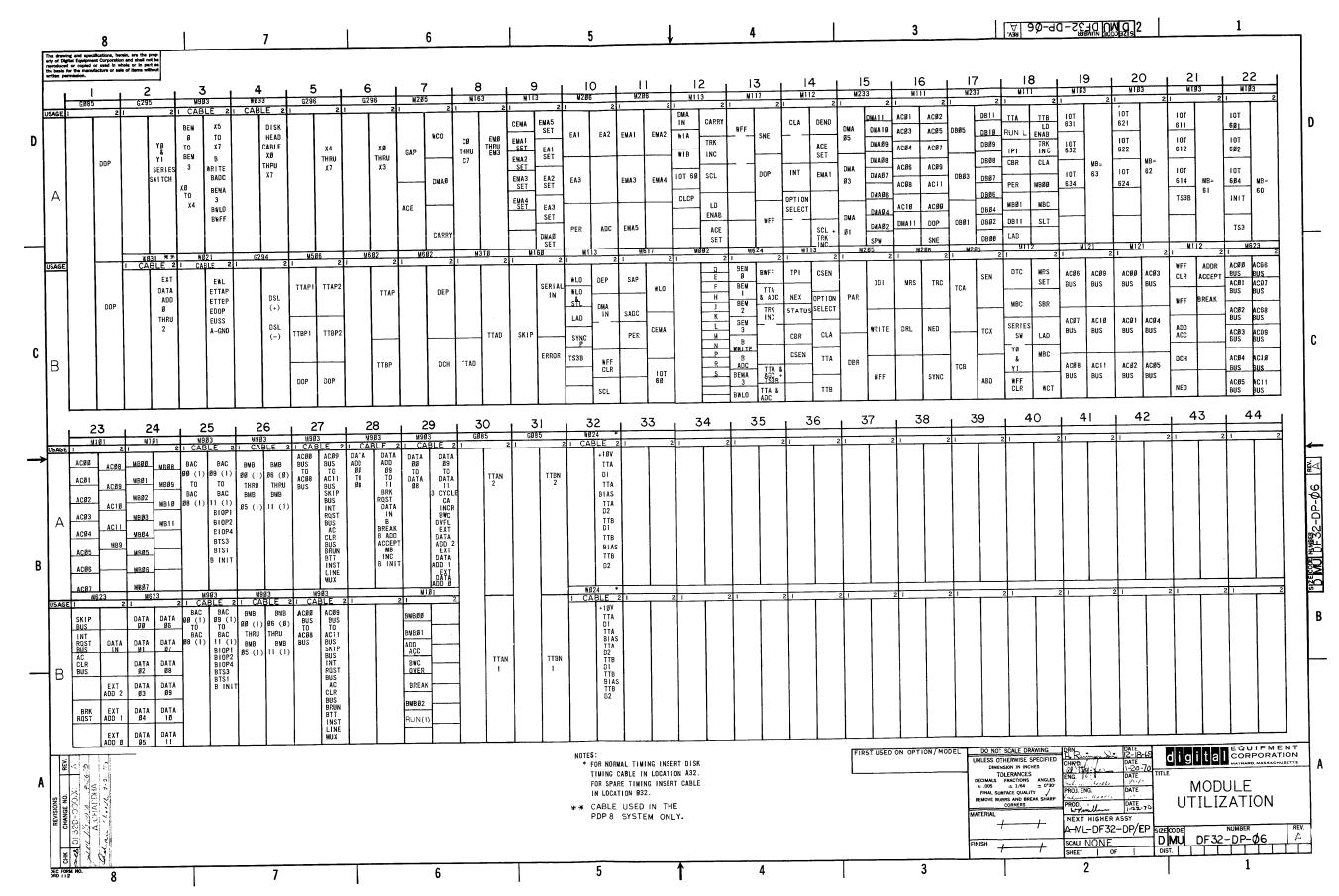

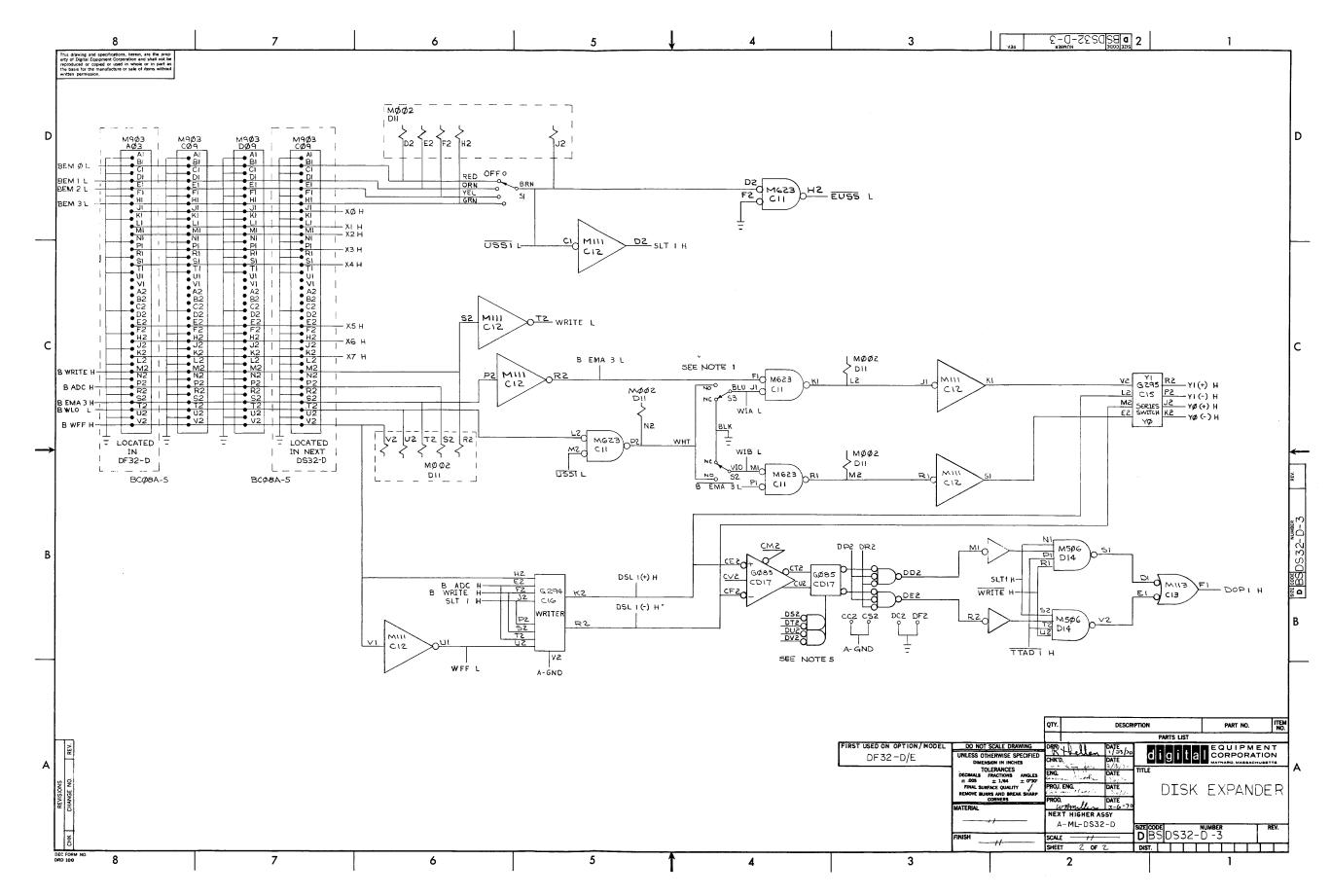

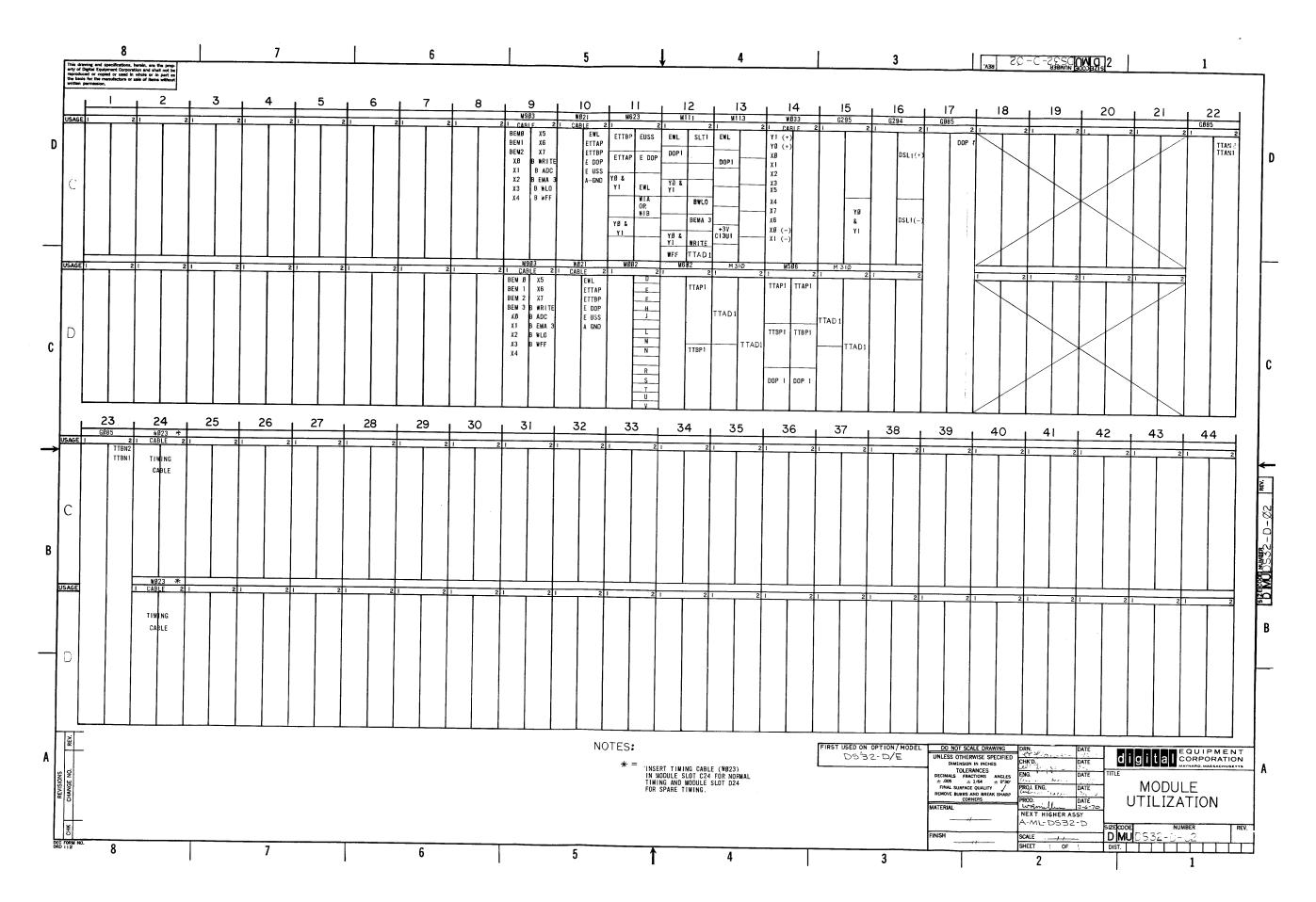

| D-MU-DF32-DP-06 | Module Utilization                        | 6-31 |

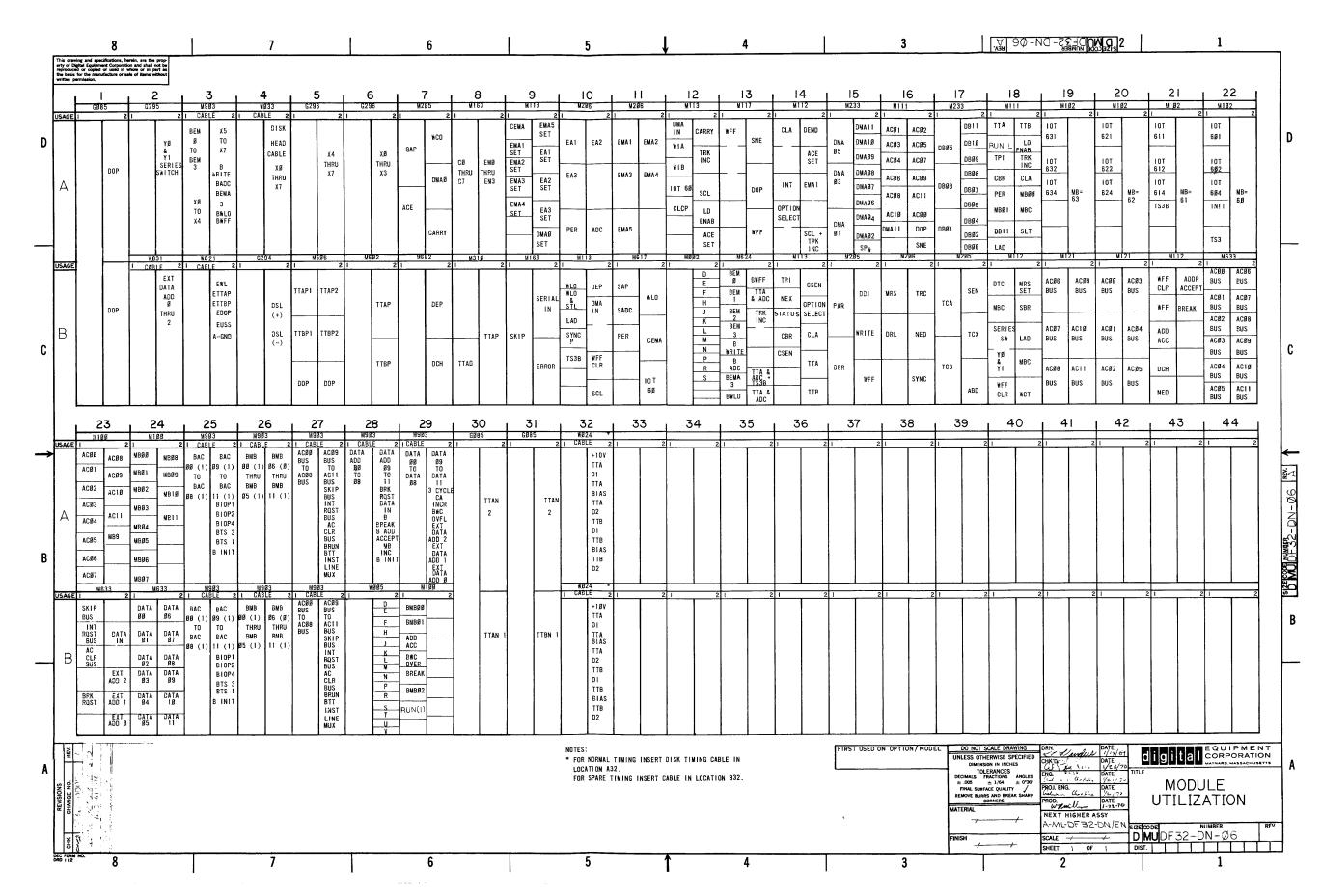

| D-MU-DF32-DN-06 | Module Utilization                        | 6-33 |

| D-BS-DS32-D-03  | Disk Expander (2 sheets)                  | 6-35 |

| D-MU-DS32-D-02  | Module Utilization                        | 6-39 |

| C-CS-G085-0-1   | Disk Read Amplifier and Slice Rectifier   | 6-41 |

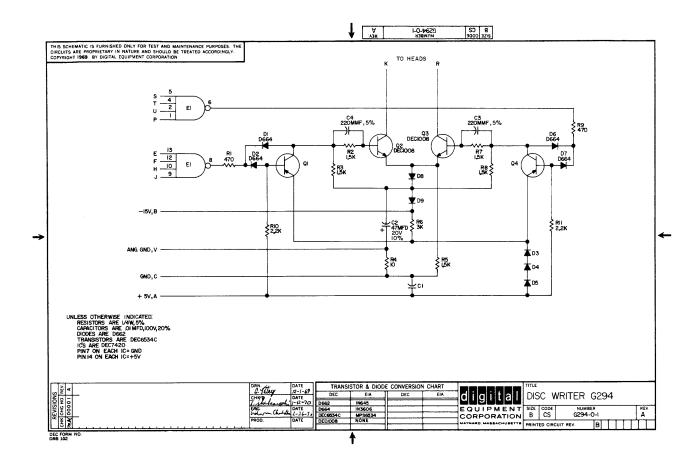

| B-CS-G294-0-1   | Disk Writer                               | 6-42 |

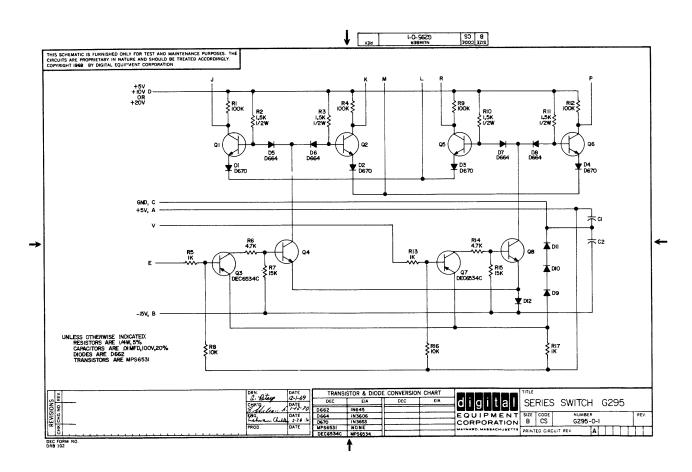

| B-CS-G295-0-1   | Series Switch                             | 6-42 |

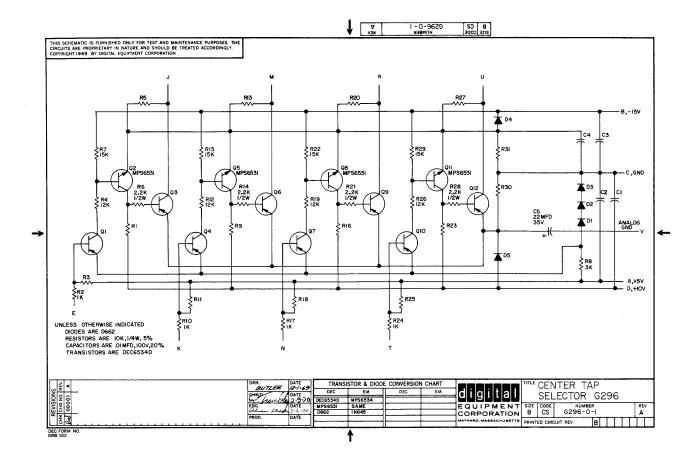

| B-CS-G296-0-1   | Center Tap Selector                       | 6-43 |

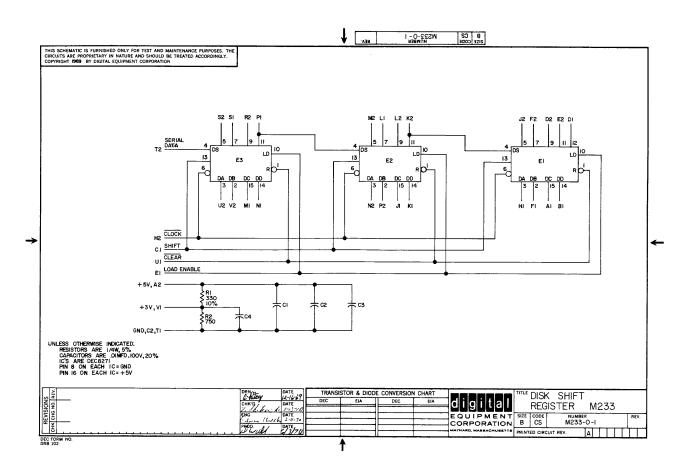

| B-CS-M233-0-1   | Disk Shift Register                       | 6-43 |

### **TABLES**

| Table Number | Title                              | Page         |

|--------------|------------------------------------|--------------|

| 1-1          | Reference Publications             | 1-1          |

| 1-2          | Operating and Maintenance Programs | 1-1          |

| 1-3          | DF32-D,E Subsystem Specifications  | 1-3          |

| 2-1          | Cable Requirements                 | 2-3          |

| 2-2          | DF32-D/Computer Cable Connections  | 2-3          |

| 2-3          | DF/DS32-D Cable Connections        | 2-4          |

| 3-1          | DF32-D Operating Control Functions | 3-1          |

| 3-2          | DS32-D Operating Control Functions | 3-3          |

| 3-3          | DF32-D Instructions                | 3 <b>-</b> 4 |

| 3-4          | IOT Instructions                   | 3-5          |

| 4-1          | DF32-D/DS32-D Signal Mnemonics     | 4-1          |

| 5-1          | Module List                        | 5-12         |

| A-1          | TTW Operating Switches             | A-2          |

### Chapter 1 Introduction

### 1.1 SCOPE

This manual describes the DF32-D, E Disk File and Control Unit and the DS32-D, E Disk Extender Unit. The information is intended primarily for maintenance personnel familiar with the DEC PDP-8 family of computers. Table 1-1 lists supplementary publications and Table 1-2 lists operating and maintenance programs available for use with the disk file system.

Table 1-1

Reference Publications

| Title                      | Description                                                                                  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------|--|--|

| Logic Handbook             | Function and specifications of FLIP CHIP® modules, cabinets, power supplies and accessories. |  |  |

| PDP-8 Maintenance Manual   | Theory, operation and maintenance information on the PDP-8.                                  |  |  |

| PDP-8/I Maintenance Manual | Theory, operation and maintenance information on the PDP-8/I.                                |  |  |

| PDP-8/L Maintenance Manual | Theory, operation and maintenance information on the PDP-8/L.                                |  |  |

| Small Computer Handbook    | Operation and programming of PDP-8/L and PDP-8/I computers and peripheral equipment.         |  |  |

Table 1-2

Operating and Maintenance Programs

| Program                                                         | Description                                                                              |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|

| DF32-D Software Package                                         | Perforated program tapes, symbolic assembly, assembly language, and utility subroutines. |

| DF32-D Diskless Logic Tests<br>(Maintenance)<br>MAINDEC-8I-D5FA | Tests master logic without the disk in operation.                                        |

### Table 1-2 (Cont) Operating and Maintenance Programs

| Program                                                                             | Description                                    |

|-------------------------------------------------------------------------------------|------------------------------------------------|

| DF32/DF32-D Disk Data<br>Mini Disk, Interface Address,<br>Data Test MAINDEC-08-D5CD | Tests master logic with the disk in operation. |

| DF32/DF32-D Multi Disk Exer-<br>ciser MAINDEC -08-D5DB                              | Tests master disk and up to three slave disks. |

### 1.2 EQUIPMENT APPLICATION

The DF32-D,E subsystem is comprised of the DF32-D,E Disk File and Control and as many as three DS32-D,E Disk Extenders. This subsystem is part of a major system built around either a PDP-8, PDP-8/I, or PDP-8/L computer. The subsystem expands the memory capacity of the particular computer by providing a quickly-accessed storage facility. The subsystem stores information transferred from the computer memory and returns this information on command. The DF32-D,E and each DS32-D,E store up to 32,768 13-bit words. The subsystem can thus expand the computer memory by as many as 131,072 words.

### 1.3 DF32-D,E DESCRIPTION

The DF32-D,E Disk File and Control Unit can be used with either 60- or 50-Hz primary power, and with either a positive or negative computer bus. Thus, four distinct units are available. The complete nomenclature of a particular unit is one of the following:

| DF32-DP | 115V, 60 | Hz, positive bus |

|---------|----------|------------------|

| DF32-DN | 115V, 60 | Hz, negative bus |

| DF32-EP | 115V, 50 | Hz, positive bus |

|         |          | Hz. negative bus |

#### NOTE

All of the above can be used in 230V systems. A multitap transformer (DEC P/N 16-2283) can be provided for this purpose.

For convenience, the nomenclature DF32-D will be cited, except where basic differences must be noted.

The DF32-D is a random access, bulk storage device that uses a magnetic recording process to record information on an aluminum disk. The unit consists of two assemblies: the disk assembly and the

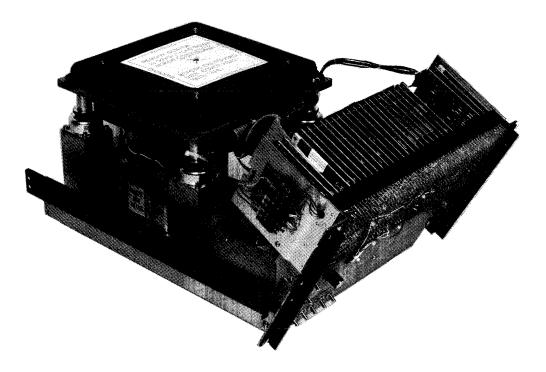

logic module assembly (see Figure 1-1). The disk assembly is mounted on shock-absorbing columns at the rear of the frame. The logic modules are inserted in mounting connectors at the front. The wiring side of the connectors faces the front of the unit. The frame is equipped with track slides for easy access and can be installed in any 19-in. equipment rack. The frame is 10-1/2 in. high, 19 in. wide, and 23-1/4 in. deep from the mounting surface, with a 2-3/8 in. extension in front of the mounting surface. (Refer to Table 1-3 for subsystem specifications.)

Figure 1-1 Disk and Logic Module Assembly

Table 1-3

DF32-D,E Subsystem Specifications

| Storage Capacity   | DF32-D,E: 32,768 13-bit words<br>DS32-D,E: 32,768 13-bit words                                                                    |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                    | Three DS32-D,E extender disks may be used with each DF32-D,E master unit, resulting in a system capacity of 131,072 13-bit words. |

| Data Transfer Rate | DF32-D: 32 µs/word<br>DF32-E: 39 µs/word                                                                                          |

| Access Time        |                                                                                                                                   |

| Average            | DF32-D: 16.67 ms<br>DF32-E: 20.00 ms                                                                                              |

| Maximum            | DF32-D: 33 ms<br>DF32-E: 40 ms                                                                                                    |

### Table 1–3 (Cont) DF32–D,E Subsystem Specifications

| Bit-to-Bit Transfer Rate  Addressing Scheme  DF32-D: 1.10 µs serial DF32-E: 1.33 µs serial DF32-E: 1.33 µs serial DF32-E: 1.33 µs serial DF32-E: 1.33 µs serial Random or absolute addressing from 0 to 32,768 words; variable block size: from 1 to 4096 words.  Internal read/write, serial; external transfer, parallel, 12 bits per word  Recording Medium  Nickel-cobalt, rhodium plated surface of a 10-in. diameter aluminum disk  Non-Return to Zero Inhibit (NRZI)  16 2048 Bit Density Number of Disk Timing Tracks Bit Density Number of Disk Timing Tracks Tracks per Inch Track Width O.020  Special Features  Write inhibit of lower/upper 16K of any 32K disk surface: inhibit of one or more 32K disks of an expanded configuration 20, in groups (pads) of four  DF32-D: 115V, 60 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-D: 15V, 00 mA +10V, 65 mA -15V, 702 mA DS32-D, E+20V, 300 mA +10V, 53 mA +5V, 677 mA -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 7058 or H709/H7098 Power Supply +5V, -15V: one H716 required for DF32-D, E and one H716 required for the three DS32-D, E T0 to 80°F, 20 to 80% relative humidity |                              |                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------|

| block size: from 1 to 40% words.  Internal read/write, serial; external transfer, parallel, 12 bits per word  Recording Medium  Nickel-cobalt, rhodium plated surface of a 10-in. diameter aluminum disk  Recording Method  Number of Disk Data Tracks  Data Words per Track  Bit Density  Number of Disk Timing Tracks  Tracks per Inch  Track Width  Special Features  Write inhibit of lower/upper 16K of any 32K disk surface: inhibit of one or more 32K disks of an expanded configuration  20, in groups (pads) of four  DF32-D: 115V, 60 Hz, single phase  DF32-D; E 120V, 300 mA  +10V, 65 mA +5V, 3.6 mA -15V, 702 mA  DS32-D, E 20V, 300 mA +10V, 35 mA +5V, 3.6 mA -15V, 777 mA -15V, 777 mA -15V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 705B or H709/H709B Power Supply  +5V, -15V: one H716 required for DF32-D, E and one H716 required for the three DS32-D, E and one                                                                                                                                                                                                                                                                                                 | Bit-to-Bit Transfer Rate     |                                                       |

| Recording Medium  Nickel-cobalt, rhodium plated surface of a 10-in. diameter aluminum disk  Non-Return to Zero Inhibit (NRZI)  Non-Return to Zero Inhibit (NRZI)  16  Data Words per Track  Bit Density  Number of Disk Timing Tracks  Tracks per Inch  Track Width  Special Features  Number of Recording Heads  Power Requirements  ac  DF32-D: 115V, 60 Hz, single phase  DF32-E: 115V, 50 Hz, single phase  DF32-D, E +20V, 300 mA  +10V, 45 mA  -15V, 702 mA  DS32-D, E +20V, 300 mA  +10V, 35 mA  -15V, 770 mA  -15V, 770 mA  -15V, 777 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three  DS32-D, E provided by one DEC type 7058 or H709/H7098  Power Supply  +5V, -15V: one H716 required for DF32-D, E and one  H716 required for the three DS32-D, E                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Addressing Scheme            |                                                       |

| aluminum disk  Recording Method  Number of Disk Data Tracks  Data Words per Track  Bit Density  Number of Disk Timing Tracks  Tracks per Inch  Track Width  Special Features  Write inhibit of lower/upper 16K of any 32K disk surface: inhibit of one or more 32K disks of an expanded configuration  20, in groups (pads) of four  DF32-D: 115V, 50 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-D, E+20V, 300 mA +10V, 65 mA +5V, 3.6 mA -15V, 702 mA  DS32-D, E+20V, 300 mA +10V, 35 mA -15V, 707 mA -15V, 707 mA -15V, 707 mA -15V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 705B or H709/H709B Power Supply  +5V, -15V: one H716 required for the three DS32-D, E and one H716 required for the three DS32-D, E                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data Assembly                |                                                       |

| Number of Disk Data Tracks Data Words per Track Bit Density Number of Disk Timing Tracks Tracks per Inch Track Width Special Features  Number of Recording Heads Power Requirements ac  dc  DF32-D: 115V, 60 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-D, E +20V, 300 mA +10V, 65 mA -15V, 702 mA  DS32-D, E +20V, 300 mA +10V, 35 mA -15V, 770 mA -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 7058 or H709/H7098 Power Supply +5V, -15V: one H716 required for DF32-D, E and one H716 required for the three DS32-D, E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Recording Medium             |                                                       |

| Data Words per Track Bit Density  Number of Disk Timing Tracks  Tracks per Inch  Track Width  Special Features  Write inhibit of lower/upper 16K of any 32K disk surface: inhibit of one or more 32K disks of an expanded configuration  20, in groups (pads) of four  Power Requirements  ac  DF32-D: 115V, 60 Hz, single phase  DF32-E: 115V, 50 Hz, single phase  DF32-D, E +20V, 300 mA  +10V, 65 mA  +5V, 3.6 mA  -15V, 702 mA  DS32-D, E +20V, 300 mA  +10V, 35 mA  -15V, 677 mA  -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three  DS32-D, E provided by one DEC type 705B or H709/H709B  Power Supply  +5V, -15V: one H716 required for DF32-D, E and one  H716 required for the three DS32-D, E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Recording Method             | Non-Return to Zero Inhibit (NRZI)                     |

| Bit Density  Number of Disk Timing Tracks  Tracks per Inch  Track Width  Special Features  Number of Recording Heads  Power Requirements ac  DF32-D: 115V, 60 Hz, single phase DF32-D, E +20V, 300 mA +10V, 65 mA +5V, 3.6 mA -15V, 702 mA  DS32-D, E +20V, 300 mA +10V, 35 mA +5V, 677 mA -15V, 677 mA -15V, 770 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 705B or H709/H709B Power Supply +5V, -15V: one H716 required for DF32-D, E and one H716 required for the three DS32-D, E and one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Number of Disk Data Tracks   | 16                                                    |

| Number of Disk Timing Tracks Tracks per Inch Track Width Special Features  Number of Recording Heads Power Requirements ac  DF32-D: 115V, 60 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-D, E +20V, 300 mA +10V, 65 mA +5V, 3.6 mA -15V, 702 mA  DS32-D, E +20V, 300 mA +10V, 35 mA +5V, 677 mA -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 7058 or H709/H7098 Power Supply +5V, -15V: one H716 required for DF32-D, E and one H716 required for the three DS32-D, E and one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Data Words per Track         | 2048                                                  |

| Tracks per Inch Track Width  Special Features  Write inhibit of lower/upper 16K of any 32K disk surface: inhibit of one or more 32K disks of an expanded configuration  20, in groups (pads) of four  DF32-D: 115V, 60 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-D, E +20V, 300 mA +10V, 65 mA -5V, 3.6 mA -15V, 702 mA  DS32-D, E +20V, 300 mA +10V, 35 mA +5V, 677 mA -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 705B or H709/H709B Power Supply +5V, -15V: one H716 required for DF32-D, E and one H716 required for the three DS32-D, E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bit Density                  | 1170 BPI, maximum                                     |

| Track Width  Special Features  Write inhibit of lower/upper 16K of any 32K disk surface: inhibit of one or more 32K disks of an expanded configuration  20, in groups (pads) of four  DF32-D: 115V, 60 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-D, E +20V, 300 mA +10V, 65 mA -15V, 702 mA  DS32-D, E +20V, 300 mA +10V, 35 mA -15V, 707 mA -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 705B or H709/H709B Power Supply +5V, -15V: one H716 required for DF32-D, E and one H716 required for the three DS32-D, E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Number of Disk Timing Tracks | Two, plus spare for each: all prerecorded             |

| Special Features  Write inhibit of lower/upper 16K of any 32K disk surface: inhibit of one or more 32K disks of an expanded configuration  20, in groups (pads) of four  DF32-D: 115V, 60 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-D, E +20V, 300 mA +10V, 65 mA +5V, 3.6 mA -15V, 702 mA  DS32-D, E +20V, 300 mA +10V, 35 mA +5V, 677 mA -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 705B or H709/H709B Power Supply +5V, -15V: one H716 required for DF32-D, E and one H716 required for the three DS32-D, E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Tracks per Inch              | 30                                                    |

| inhibit of one or more 32K disks of an expanded configuration  20, in groups (pads) of four  DF32-D: 115V, 60 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-D, E +20V, 300 mA +10V, 65 mA -15V, 702 mA  DS32-D, E +20V, 300 mA +10V, 35 mA +5V, 3.6 mA -15V, 677 mA -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 705B or H709/H709B Power Supply +5V, -15V: one H716 required for DF32-D, E and one H716 required for the three DS32-D, E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Track Width                  | 0.020                                                 |

| Power Requirements ac  DF32-D: 115V, 60 Hz, single phase DF32-E: 115V, 50 Hz, single phase DF32-D, E +20V, 300 mA +10V, 65 mA +5V, 3.6 mA -15V, 702 mA  DS32-D, E +20V, 300 mA +10V, 35 mA +5V, 677 mA -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D, E and three DS32-D, E provided by one DEC type 705B or H709/H709B Power Supply +5V, -15V: one H716 required for DF32-D, E and one H716 required for the three DS32-D, E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Special Features             | • • • • • • • • • • • • • • • • • • • •               |

| DF32-D: 115V, 60 Hz, single phase DF32-E: 115V, 50 Hz, single phase  DF32-D,E +20V, 300 mA +10V, 65 mA +5V, 3.6 mA -15V, 702 mA  DS32-D,E +20V, 300 mA +10V, 35 mA +5V, 677 mA -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D,E and three DS32-D,E provided by one DEC type 705B or H709/H709B Power Supply +5V, -15V: one H716 required for DF32-D,E and one H716 required for the three DS32-D,E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Number of Recording Heads    | 20, in groups (pads) of four                          |

| +10V, 65 mA +5V, 3.6 mA -15V, 702 mA  DS32-D,E +20V, 300 mA +10V, 35 mA +5V, 677 mA -15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D,E and three DS32-D,E provided by one DEC type 705B or H709/H709B Power Supply +5V, -15V: one H716 required for DF32-D,E and one H716 required for the three DS32-D,E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ac                           | DF32-E: 115V, 50 Hz, single phase                     |

| +10V, 35 mA<br>+5V, 677 mA<br>-15V, 377 mA  NOTE  +20V, +10V: requirements for one DF32-D,E and three<br>DS32-D,E provided by one DEC type 705B or H709/H709B<br>Power Supply  +5V, -15V: one H716 required for DF32-D,E and one<br>H716 required for the three DS32-D,E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ac ac                        | +10V, 65 mA<br>+5V, 3.6 mA                            |

| +20V, +10V: requirements for one DF32-D,E and three DS32-D,E provided by one DEC type 705B or H709/H709B Power Supply +5V, -15V: one H716 required for DF32-D,E and one H716 required for the three DS32-D,E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              | +10V, 35 mA<br>+5V, 677 mA                            |

| DS32-D,E provided by one DEC type 705B or H709/H709B Power Supply +5V, -15V: one H716 required for DF32-D,E and one H716 required for the three DS32-D,E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              | NOTE                                                  |

| H716 required for the three DS32-D,E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              | DS32-D, E provided by one DEC type 705B or H709/H709B |

| Recommended Environment 70 to 80°F, 20 to 80% relative humidity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              | •                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Recommended Environment      | 70 to 80°F, 20 to 80% relative humidity               |

Table 1-3 (Cont)

DF32-D,E Subsystem Specifications

| Physical Characteristics<br>Height | 10-1/2 in.                                                                          |  |

|------------------------------------|-------------------------------------------------------------------------------------|--|

| Width                              | 19 in.                                                                              |  |

| Depth                              | 21–1/4 in. from mounting surfaces; 2–3/8 in. extension in front of mounting surface |  |

| Weight                             | 65 lb, approximate                                                                  |  |

### 1.3.1 Disk Assembly

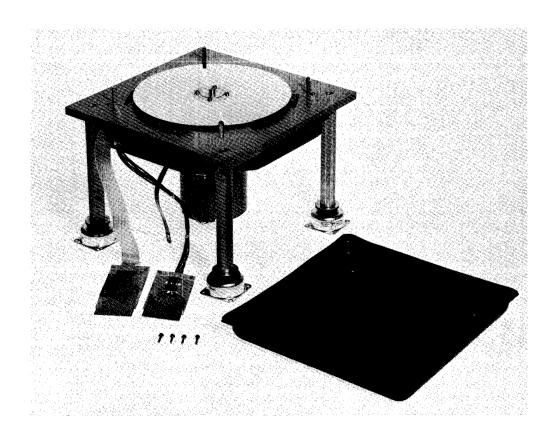

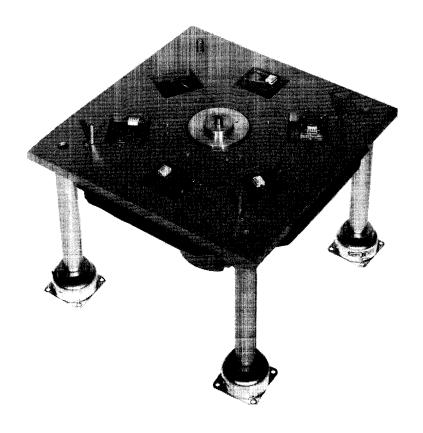

The disk assembly includes a 10-in. diameter aluminum disk, 20 recording heads, and a drive motor mounted on a base plate, supported by four shock-absorbing columns. Top and bottom dust covers protect the disk and heads. Electrical signals are sent through two connector cards that plug into the logic module assembly. Figure 1-2 is the disk assembly with the top dust cover removed. Figure 1-3 is the assembly with the disk removed and recording heads exposed. Note that there are four heads on each head shoe.

Figure 1-2 Disk Assembly with Top Dust Cover Removed

Figure 1-3 Disk Assembly with Disk Removed and Recording Heads Exposed

### 1.3.2 Logic Module Assembly

The logic module assembly includes the logic modules, the module mounting panels, controls, and switches. The logic for the DF32-D is contained on DEC logic modules, which are inserted in the mounting connectors. Connections between the modules are made by wiring the connector pins. The modules consist of G-series (discrete components) and M-series (integrated circuit) modules. The majority of these modules are the M-series, which use high speed TTL integrated circuits to implement the logic. Table 5-1 lists the DEC modules in the DF32-D. Drawing DF32-DP-06 (Section 6) shows the location of each module in the connector blocks, and the identity of the signals furnished by each module.

### 1.4 DS32-D,E DESCRIPTION

The disk extender (as well as the master controller) can be used with either 60- or 50-Hz power, and with either a positive or negative bus. The following extender units are available:

DS32-D.....115V, 60 Hz, positive and negative bus DS32-E.....115V, 50 Hz, positive and negative bus

For convenience, the short nomenclature, DS32-D, will be used.

The DS32-D is similar to the DF32-D in appearance and in overall dimensions. The disk assembly is identical to that of the DF32-D; however, the logic module assembly is significantly different. The logic module assembly contains fewer logic modules because the DS32-D operation is controlled by the DF32-D control circuits. A completely extended DF32-D subsystem consists of one DF32-D Disk File and Control, three DS32-D Disk Extenders, a DEC Type 705B or H709/H709B Power Supply, two DEC Type H716 Power Supplies, and a power control panel.

### Chapter 2 Installation

#### 2.1 CABINET INSTALLATION

The DF32-D subsystem will normally be an addition to a system built around a PDP-8, PDP-8/I, or PDP-8/L computer. This computer will be either pedestal or rack mounted. If other peripheral equipment is rack mounted in a DEC standard computer cabinet, it may be possible to incorporate the DF32-D subsystem into the existing mounting configuration. Refer to the appropriate computer maintenance manual for a discussion of mounting arrangements in the DEC cabinet.

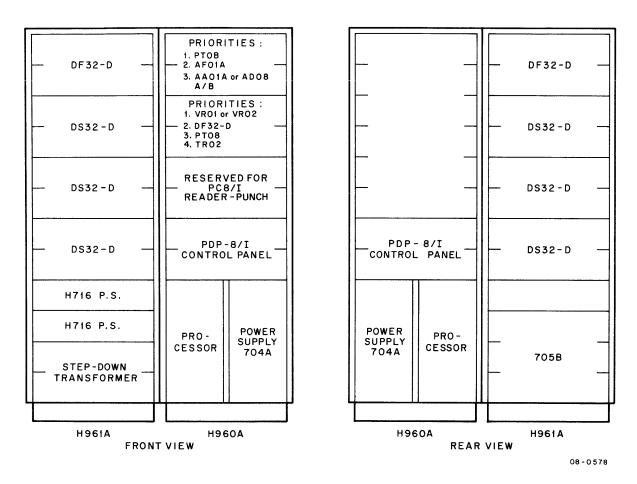

Additional cabinet space may be required if the DF32-D subsystem includes disk extenders. In this event, the DF32-D should be mounted at the top with the extender disks mounted below. Cables must be kept as short as possible; therefore, all extender units should be mounted in the same cabinet as the DF32-D. Although any 19-in. equipment rack can be used, a DEC standard computer cabinet is suggested for convenience and appearance. Various panel doors and cover plates can be purchased along with the basic 19-in. frame. A typical system is shown in Figure 2-1. Refer to the Logic Handbook for a guide to available cabinet hardware.

If the DF32-D is to be installed in a cabinet of an existing system in the field, it may be necessary to install the cabinet portion of the track slide assembly. Two types of track slides are used, depending upon the type of DEC cabinet in which the equipment is being mounted. DEC Type CAB8 Cabinets use Chassis Track Slides (C300-S-20), while the new DEC H960 and H961 Cabinets use Slides 12-91-54. When the cabinet location of the equipment has been selected, the track slide housing should be mounted with four No. 10-32 Rivinuts.

#### 2.2 POWER REQUIREMENTS

The DF32-D/E requires a 115V ac, single-phase power source. The DF32-D is designed for 60-Hz operation; the DF32-E is designed for 50-Hz operation. AC connections are made directly to the dc power supplies listed in Table 1-3. DC power connections to the logic modules are made at a power end panel located on the left side of either DF32-D or DS32-D.

#### NOTE

The disk motor should not be turned on and off any more than is absolutely necessary. There is contact between the disk and the heads when the disk is stopped. Excessive starting and stopping creates excessive wear on both disk and heads. The disk motor ac power should, therefore, be supplied directly from a power source and not from the power control switch.

Figure 2-1 DF32-D/DS32-D Mounting Locations

### 2.3 CABLE REQUIREMENTS

Connections between the computer and the DF32-D are made by shielded mylar interfacing cable, terminated on either end by single- or double-sided connector boards. Cable requirements are shown in Table 2-1 for each combination of DF32-D and computer.

Table 2-1

Cable Requirements

| Computer | Type of DEC Standard<br>Interface Cable Needed | Number of Cables<br>Needed | Cable Components                        |

|----------|------------------------------------------------|----------------------------|-----------------------------------------|

| PDP-8    | BC08C-5                                        | 5                          | 5 ft. 1–1/4 in. mylar M903 to<br>2 W031 |

|          |                                                | 1                          | 5 ft. 1–1/4 in. mylar W021 to<br>W021   |

| PDP-8/I  | BC08C-5                                        | 5                          | 5 ft. 1–1/4 in. mylar M903 to<br>2 W031 |

| PDP-8/L  | BC08A-5                                        | 5                          | 5 ft. 1-1/4 in. mylar M903 to<br>M903   |

Table 2-2 gives cable connections between the DF32-D and associated computer.

Table 2-2 DF32-D/Computer Cable Connections

|                             | Computer Receptacle Connector |                               |                   |

|-----------------------------|-------------------------------|-------------------------------|-------------------|

| DF32-D Receptacle Connector | PDP-8<br>(W031)               | PDP-8/I<br>(W031)             | PDP-8/L<br>(M903) |

| A25 (M903)                  | ME-34<br>MF-34                | J01<br>J02                    | D36               |

| A26 (M903)                  | ME-35<br>MF-35                | J03<br>J04                    | D35               |

| A27 (M903)                  | PE-02<br>PF-02                | J05<br>J06                    | D34               |

| A28 (M903)                  | PE-03<br>PF-03                | J07<br>J08                    | C36               |

| A29 (M903)                  | PE-04<br>PF-04                | J09<br>J10                    | C35               |

| BO2 (WO31)                  | ME-30                         | J11<br>(Negative<br>bus only) |                   |

Connections between the DF32-D and DS32-D are also made by standard DEC interfacing cable.

Table 2-3 gives cable requirements and cable connections for DF/DS32-D combinations.

Table 2-3 DF/DS32-D Cable Connections

| Cable   | Number Required | From                            | То                              |

|---------|-----------------|---------------------------------|---------------------------------|

| BC03D-5 | 1               | DF32-D, B03 (W021<br>Connector) | DS32-D, C10 (W021<br>Connector) |

| BC08A-5 | 1               | DF32-D, A03 (M903<br>Connector) | DS32-D, D09 (M903<br>Connector) |

### **Chapter 3 Operation and Programming**

### 3.1 OPERATION

No special operating procedures are required for the DF32-D or the DS32-D. The DF32-D front panel is shown in Figure 3-1; the DS32-D front panel is shown in Figure 3-2. The DF32-D operating controls are described in Tables 3-1 and 3-2.

Table 3-1 DF32-D Operating Control Functions

| Control              | Function                                                                                                                       |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------|

| UNIT SELECT          | Assigns disk selection number.                                                                                                 |

| UPPER 16K            | When in the ON position, inhibits writing on the upper 16K word positions of the DF32–D if write lockout is enabled.           |

| LOWER 16K            | When in the ON position, inhibits writing on the lower 16K word positions of the DF32–D if write lockout is enabled.           |

| OPR/MAINT            | Normally in the OPR position; when in the MAINT position, enables maintenance IOT instructions (for diskless diagnostic test). |

| DISK 0 WRITE LOCKOUT | When in the ON position, enables write lockout selection on unit 0.                                                            |

| DISK 1 WRITE LOCKOUT | When in the ON position, enables write lockout selection on unit 1.                                                            |

| DISK 2 WRITE LOCKOUT | When in the ON position, enables write lockout selection on unit 2.                                                            |

| DISK 3 WRITE LOCKOUT | When in the ON position, enables write lockout selection on unit 3.                                                            |

Figure 3-1 DF32-D Front Panel

Figure 3-2 DS32-D Front Panel

Table 3-2

DS32-D Operating Control Functions

| Control                  | Function                                                                                                                                             |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| UNIT SELECT<br>UPPER 16K | Assigns disk selection number.  When in the ON position, inhibits writing on the upper 16K word positions of the DS32-D if write lockout is enabled. |

| LOWER 16K                | When in the ON position, inhibits writing on the lower 16K word positions of the DS32-D if write lockout is enabled.                                 |

#### 3.2 PROGRAMMING

The programming of the DF32-D is typical of an input/output (I/O) device attached to a PDP-8 family computer. Input/output transfer (IOT) instructions control device operation. The 3-cycle data break facility of the computer is used to transfer data between core memory and the DF32-D. The word count (WC) register (memory address 7750) of the data break facility specifies the number of word transfers, and the current address (CA) register (memory address 7751) of the data break facility specifies the starting address of the transfer. The DF32-D contains a disk buffer (DB) register to buffer the data between core memory and the disk; a disk memory address (DMA) register to specify the disk data address; an extended memory address (EMA) register to specify the disk and track; and an extended address (EA) register to specify the core memory field when the computer memory capacity has been expanded.

The IOT instructions initiate a data transfer and provide the DF32-D with the information it needs to take part in the transfer (see Figure 3-3). Bits 0, 1, and 2 represent the operation code. When the computer recognizes operation code 6, indicating an IOT instruction, the computer generates an IOP pulse. IOP1 is generated if a 1 is present in bit 11 of the IOT instruction; IOP2 is generated if a 1 is present in bit 10 of the IOT instruction; IOP4 is generated if a 1 is present in bit 9 of the IOT instruction. These IOP pulses are sent to the peripheral device designated by bits 3 through 8 of the IOT. Selection circuits within the device then generate IOT pulses, which specify device control operations. The IOT instructions that apply to the DF32-D are listed in Tables 3-3 and 3-4.

Figure 3-3 IOT Instructions

Table 3–3 DF32–D Instructions

| Mnemonic | Octal | Operation                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCMA     | 6601  | Clear the disk memory address register, parity error, and completion flags. This instruction clears the disk memory request flag and interrupt flags.                                                                                                                                                                                                                                         |

| DMAR     | 6603  | Load the disk memory address register with the information (initial address) stored in the accumulator (AC). Then clear the AC. Begin to read information from the disk into the specified core location. Clear parity error and completion flags. Clear interrupt flags.  AC <sub>0-11</sub> → DMA <sub>0-11</sub>                                                                           |

| DMAW     | 6605  | Load the disk memory address register with the information (initial address) stored in the accumulator (AC). Begin writing information onto the disk from the specified core location. A data break must be allowed to occur within 64 µs after this instruction is issued. Clear parity error and completion flags.  Clear interrupt flags.  AC <sub>0-11</sub> -DMA <sub>0-11</sub>         |

| DCEA     | 6611  | Clear the disk extended address and memory address extension register. $0 \rightarrow EMA_{5-1}$ $0 \rightarrow EA_{3-1}$                                                                                                                                                                                                                                                                     |

| DSAC     | 6612  | Skip the next instruction if the address confirmed flag is a 1. This flag is set for 16 $\mu s$ (AC is cleared). 0 $\rightarrow$ AC                                                                                                                                                                                                                                                           |

| DIEF     | 6614  | Load the following information into the accumulator: Gap (Simulated photocell) flag $\rightarrow$ AC $_0$ $EMA_{5-1} \xrightarrow{\rightarrow} AC_{1-5}$ $EA_{3-1} \xrightarrow{\rightarrow} AC_{6-8}$ data late flag $\rightarrow$ AC $_9$ write lockout flag $\rightarrow$ AC $_{10}$ parity error flag $\rightarrow$ AC $_{11}$                                                            |

| DEAL     | 6615  | Clear the disk extender address and memory address extension registers. Then load the disk extender address and memory address extension registers with the track address data held in the accumulator. $AC_{6-8} \xrightarrow{+EA_{3-1}}$ , core memory extension $AC_{1-5} \xrightarrow{+EMA_{5-1}}$ , disk address extension (128, 96, 64, 32K) $AC_{0;9-11}$ , used with DEAC instruction |

| DEAC     | 6616  | Clear the accumulator, then load the contents of the disk ex-<br>tended address register into the accumulator to allow program<br>evaluation. Skip the next instruction if address confirmed<br>flag is a 1.                                                                                                                                                                                  |

Table 3-3 (Cont)

DF32-D Instructions

| Mnemonic       | Octal   | Operation                                                                                                                                                   |

|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEAC<br>(Cont) |         | 128, 96, 64, 32K: EMA <sub>5-1</sub> →AC <sub>1-5</sub> Computer memory EA <sub>3-1</sub> →AC <sub>6-8</sub> Simulated photocell sync mark →AC <sub>0</sub> |

|                |         | Data request late flag → AC <sub>9</sub>                                                                                                                    |

|                |         | Nonexistent disk flag or write lock switch "on" →AC <sub>10</sub> *                                                                                         |

|                |         | Parity errors → AC                                                                                                                                          |

| DFSE           | 6621    | Skip next instruction if the parity error, data request late, or write lock switch flag is a 1 (no error).                                                  |

| DFSC           | 6622    | Skip next instruction if the completion flag is a 1 (data transfer is complete).                                                                            |

| DMAC           | 6626    | Clear the accumulator, then load the contents of the disk memory address register into the accumulator to allow program evaluation.  DMA 0-11 → AC 0-11     |

|                | <u></u> | NOTE                                                                                                                                                        |

- 1. During read the final address will be the last address transferred +1.

- 2. During write the final address will be the last address transferred.

- 3. The nonexistent disk condition will appear following the completion of a read data transfer if the address acknowledged was the last address of a disk and the next word to be addressed falls within a nonexistent disk. The completion flag for this data transfer is set by the nonexistent disk condition.

\*Write lock switch status is true only when the disk module contains a write command.

Table 3-4

IOT Instructions

| Instruction | Description                                                                                                                              |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6601: DCMA  | 1. Generates SCL (start clear), which clears: a. TRC FF (transfer complete) b. NED FF (nonexistent disk) c. MRS FF (memory request sync) |  |

Table 3-4 (Cont)

IOT Instructions

| Instruction | Description                                                                                                                                                                                                                                                                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6601 (Cont) | d. ADC FF (address confirmed) e. DRL FF (data request late) f. PER FF (parity error)                                                                                                                                                                                                 |

|             | <ul> <li>2. Generates DTC (disk time clear) which clears:</li> <li>a. SEN FF (search enable)</li> <li>b. TCA FF (time counter "A")</li> <li>c. TCB FF (time counter "B")</li> </ul>                                                                                                  |

|             | 3. Clears the disk memory address register                                                                                                                                                                                                                                           |

| 6602:       | 1. Clears the accumulator.                                                                                                                                                                                                                                                           |

|             | 2. Clears the WRITE FF (setting transfer direction to read).                                                                                                                                                                                                                         |

|             | <ul> <li>3. Generates LAD (load address), which:</li> <li>a. Causes a jam transfer from the accumulator to the disk memory address register by generating LAP and IOT 60.</li> <li>b. Clears WCO FF (word count overflow).</li> <li>c. Sets MRS FF (memory request sync).</li> </ul> |

| 6604:       | 1. Clears the accumulator.                                                                                                                                                                                                                                                           |

|             | 2. Sets the R/W FF, setting transfer direction to write.                                                                                                                                                                                                                             |

|             | 3. Generates LAD.                                                                                                                                                                                                                                                                    |

|             | 4. Sets DBR FF (data break request).                                                                                                                                                                                                                                                 |

|             | NOTE                                                                                                                                                                                                                                                                                 |