# LAB-8/E MAINTENANCE MANUAL

# LAB-8/E MAINTENANCE MANUAL

1st Edition, March 1972 2nd Printing (Rev) August 1973

Copyright © 1972, 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

**COMPUTER LAB**

UNIBUS

# CONTENTS

|           |                                                             | Page |

|-----------|-------------------------------------------------------------|------|

| CHAPTER 1 | INTRODUCTION                                                |      |

| 1.1       | Purpose of Manual                                           | 1-1  |

| 1.2       | System Features                                             | 1-1  |

| 1.2.1     | Analog-to-Digital Converter (AD8-EA)                        | 1-3  |

| 1.2.2     | Analog Preamplifier and Multiplexer (AM8-EA)                | 1-3  |

| 1.2.3     | Point-Plot Display Control (VC8-E)                          | 1-3  |

| 1.2.4     | Buffered Digital I/O (DR8-EA)                               | 1-3  |

| 1.2.5     | Real-Time Programmable Clock (DK8-EP)                       | 1-3  |

| 1.2.6     | Analog Input Panels (AM8-ED and AM8-EC)                     | 1-4  |

| 1.2.7     | Real-Time Programmable Clock Input Panel (DK8-EF)           | 1-4  |

| 1.2.8     | Digital I/O Panel (DR8-EB)                                  | 1-4  |

| 1.3       | Physical Description                                        | 1-7  |

| 1.4       | Documentation                                               | 1-7  |

| CHAPTER 2 | INSTALLATION                                                |      |

| 2.1       | Site Considerations                                         | 2-1  |

| 2.1.1     | Power Source                                                | 2-2  |

| 2.2       | I/O Panels and Cabling Requirements                         | 2-2  |

| 2.2.1     | A/D Converter Connections                                   | 2-2  |

| 2.2.2     | Buffered Digital I/O Connections                            | 2-4  |

| 2.2.3     | Real-Time Programmable Clock Input Connections              | 2-5  |

| 2.2.4     | Point-Plot Display (VC8-E) Control Connections              | 2-5  |

| 2.3       | Fire And Safety Precautions                                 | 2-6  |

| 2.4       | Installation Procedures                                     | 2-6  |

| 2.4.1     | Unpacking and Inspection                                    | 2-6  |

| 2.4.2     | Installation Procedure                                      | 2-12 |

| 2.5       | Acceptance Test                                             | 2-18 |

| 2.5.1     | Central Processor Acceptance Test                           | 2-19 |

| 2.5.2     | Analog-to-Digital Converter (AD8-EA) and Analog Multiplexer |      |

|           | (AM8-EA) Acceptance Test                                    | 2-19 |

| 2.5.2.1   | Acceptance Test                                             | 2-20 |

| 2.5.3     | Point-Plot Display Control (VC8-E) Acceptance Test          | 2-24 |

| 2.5.3.1   | Control Logic Acceptance Test                               | 2-24 |

| 2.5.3.2   | VC8-E Ramp Slewing Test                                     | 2-25 |

| 2.5.3.3   | VC8-E Display Test                                          | 2-25 |

| 2.5.4     | Real-Time Clock (DK8-EP and DK8-ES) Acceptance Test         | 2-28 |

| 2.5.4.1   | Acceptance Tests                                            | 2-28 |

| 2.5.4.2   | DK8-ES Acceptance Test                                      | 2-29 |

| 2.5.5     | Buffered Digital I/O (DR8-EA) Acceptance Tests              | 2-30 |

| 2.5.5.1   | Visual Inspection and Test Setup                            | 2-31 |

| 2.5.5.2   | DR8-EA Acceptance Test Without DR8-EB Panel                 | 2-31 |

Pg 2-17 Tech 602 mod's

| CHAPTER 3 | OPERATING PROCEDURES                                               | Page        |

|-----------|--------------------------------------------------------------------|-------------|

| 3.1       | Computer Operation                                                 | 2.4         |

| 3.1.1     | Controls and Indicators                                            | 3-1<br>3-1  |

| 3.1.2     | Keyboard Operation                                                 |             |

| 3.1.2     | Printer Operation                                                  | 3-5<br>3-6  |

| 3.1.4     | Paper-Tape Reader Operation                                        | 3-6         |

| 3.1.5     | Operating Procedures                                               | 3-6         |

| 3.1.6     | Manual Data Storage and Modification                               | 3-6<br>3-6  |

| 3.1.6.1   | Power for Manual Operation                                         | 3-6<br>3-6  |

| 3.1.6.2   | Memory Addressing for Manual Operation                             | 3-6<br>3-6  |

| 3.1.6.3   | Manual Data Input to Addressed Memory Location                     | 3-6<br>3-6  |

| 3.1.6.4   | Checking the Contents of Any Address In Core Memory                | 3-0<br>3-7  |

| 3.1.7     | Loading Data Under Program Control                                 | 3-7<br>3-7  |

| 3.1.7.1   | Initializing the System                                            | 3-7<br>3-7  |

| 3.1.8     | Program Loading Operation                                          | 3-7<br>3-8  |

| 3.1.9     | Loaders                                                            | 3.9         |

| 3.1.9.1   | Read-In-Mode (RIM) Loader                                          | 3.9<br>3.9  |

| 3.1.9.2   | Binary (BIN) Loader                                                | 3-9<br>3-11 |

| 3.1.10    | Off-Line Teletype Operation                                        | 3-11        |

| 3.2       | Display System Operating Procedures                                | 3-12        |

| 3.2.1     | VR14 Display Operation                                             | 3-13        |

| 3.2.2     | Guidelines for VC8-E Interfacing for Oscilloscopes and XY Plotters | 3-15        |

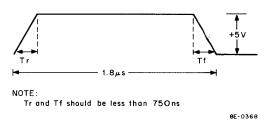

| 3.2.2.1   | Intensification Pulse                                              | 3-15        |

| 3.2.2.2   | X and Y Outputs                                                    | 3-15        |

| 3.2.2.3   | Drive Capabilities                                                 | 3-15        |

| 3.2.2.4   | External Controls                                                  | 3-15        |

| 3.2.2.5   | Ground Loops                                                       | 3-16        |

| 3.2.2.6   | VC8-E Restrictions                                                 | 3-16        |

| CHAPTER 4 | PRINCIPLES OF OPERATION                                            |             |

|           | Section 1                                                          |             |

|           | System Operation                                                   |             |

| 4.1       | Introduction                                                       | 4-3         |

| 4.1.1     | Analog Data Input to the A/D Converter                             | 4-4         |

| 4.1.2     | A/D Converter (AD8-EA)                                             | 4-4         |

| 4.1.3     | Buffered Digital I/O (DR8-EA)                                      | 4-4         |

| 4.1.4     | Real-Time Programmable Clock (DK8-EP)                              | 4-6         |

| 4.1.5     | Point-Plot Display Control (VC8-E)                                 | 4-6         |

| 4.1.6     | 33 ASR Teletype                                                    | 4-9         |

| 4.1.7     | HQ Power Supply                                                    | 4-9         |

|           |                                                             | Page |

|-----------|-------------------------------------------------------------|------|

|           | Section 2                                                   |      |

|           | Analog-To-Digital Converter (AD8-EA)                        |      |

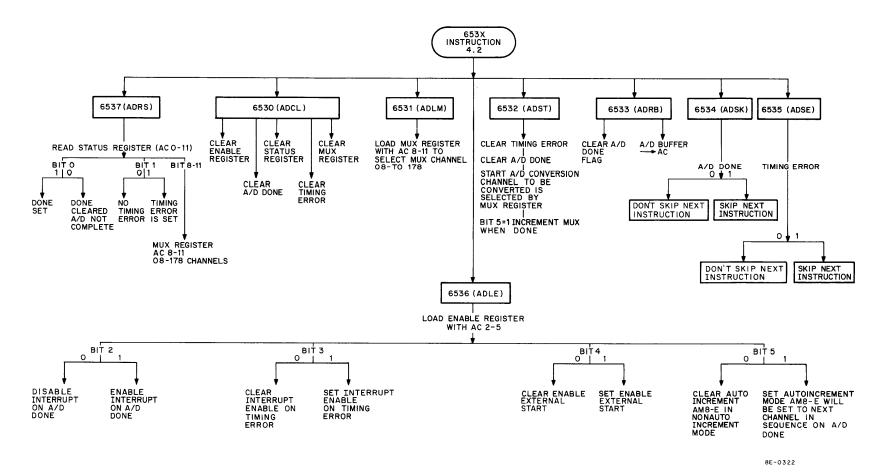

| 4.2       | Introduction                                                | 4-11 |

| 4.2.1     | A/D Converter Block Diagram                                 | 4-14 |

| 4.2.2     | A/D Converter Detailed Logic                                | 4-17 |

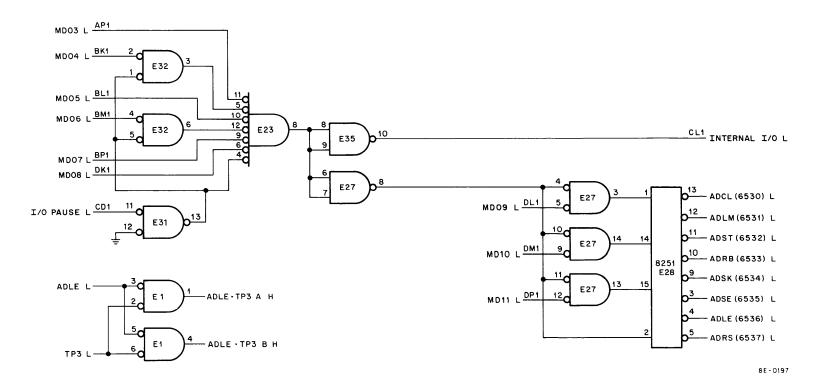

| 4.2.2.1   | Device and Operation Select Logic                           | 4-17 |

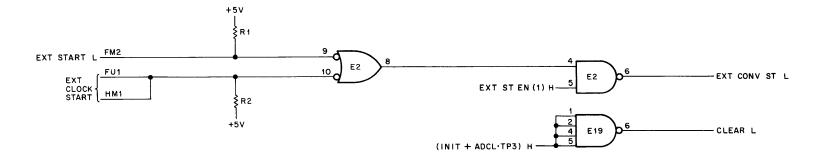

| 4.2.2.2   | External A/D START and Time Pulse Logic                     | 4-17 |

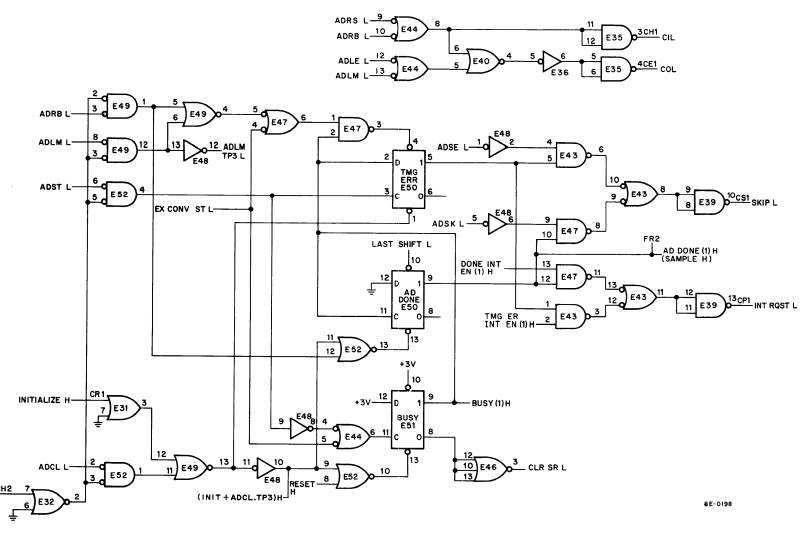

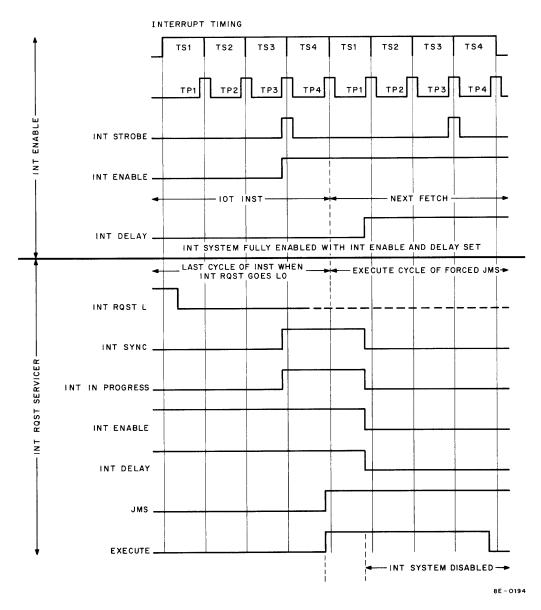

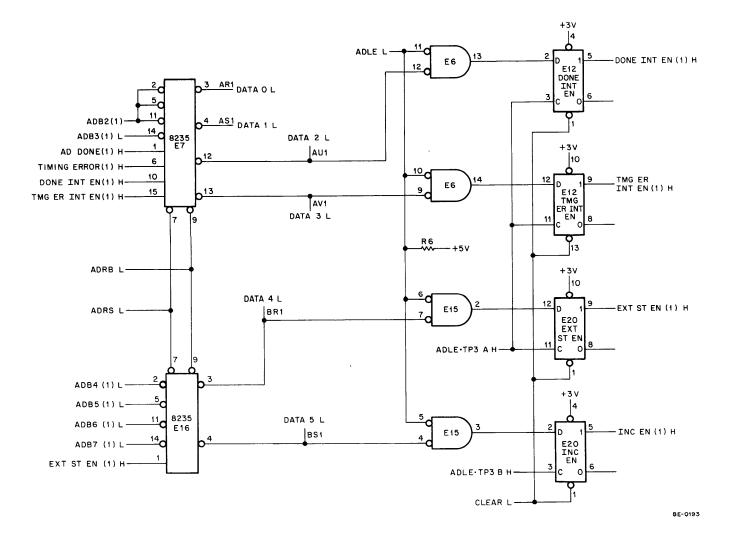

| 4.2.2.3   | Interrupt, Skip, and Control Logic                          | 4-17 |

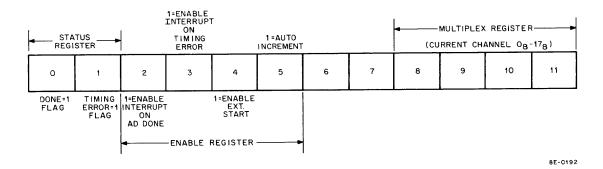

| 4.2.3     | Status Register                                             | 4-21 |

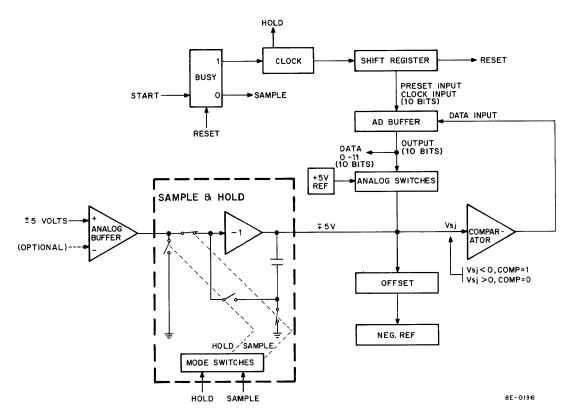

| 4.2.4     | BUSY Flip-Flop                                              | 4-21 |

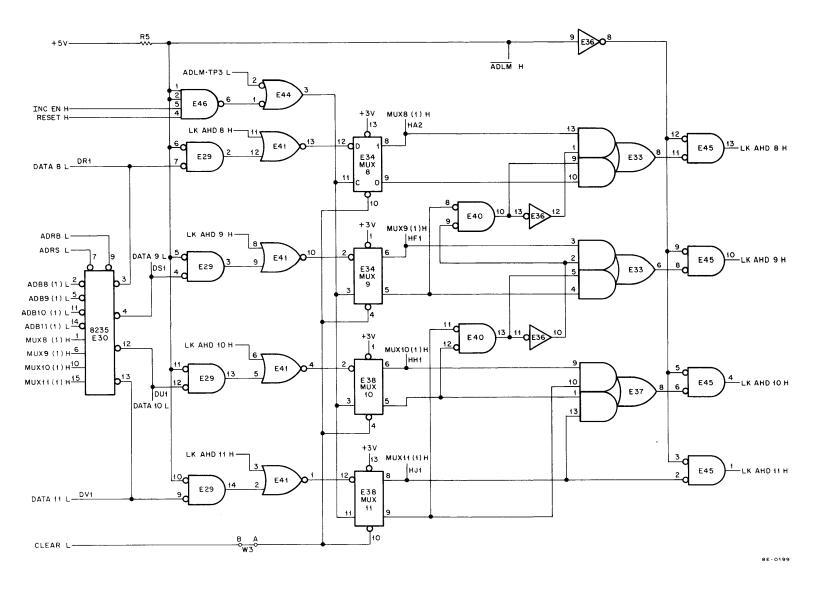

| 4.2.5     | MUX Register Logic                                          | 4-21 |

| 4.2.6     | Enable Register                                             | 4-23 |

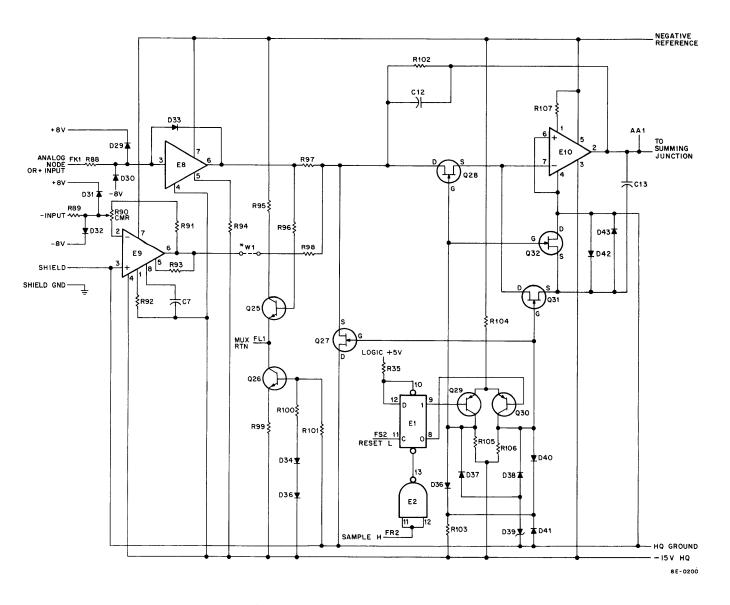

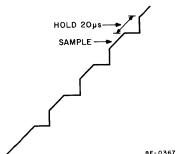

| 4.2.7     | Analog Buffer and Sample and Hold Circuits                  | 4-23 |

| 4.2.8     | A/D Converter Internal Clock                                | 4-26 |

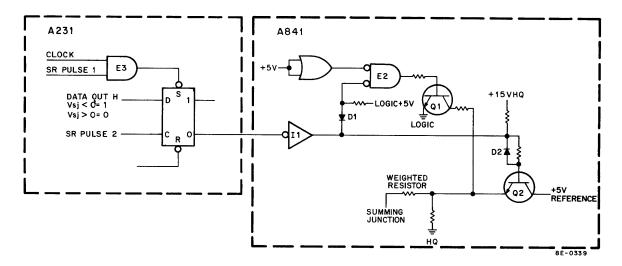

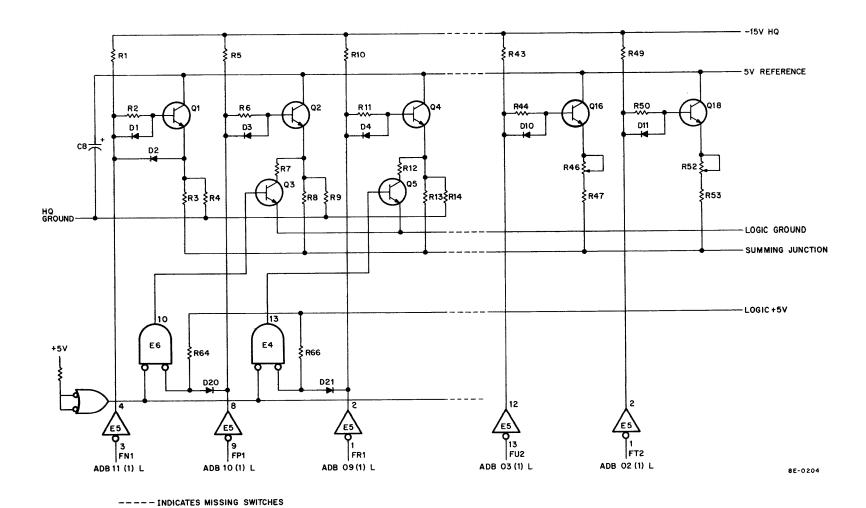

| 4.2.9     | Analog Switches                                             | 4-26 |

| 4.2.10    | Comparator                                                  | 4-31 |

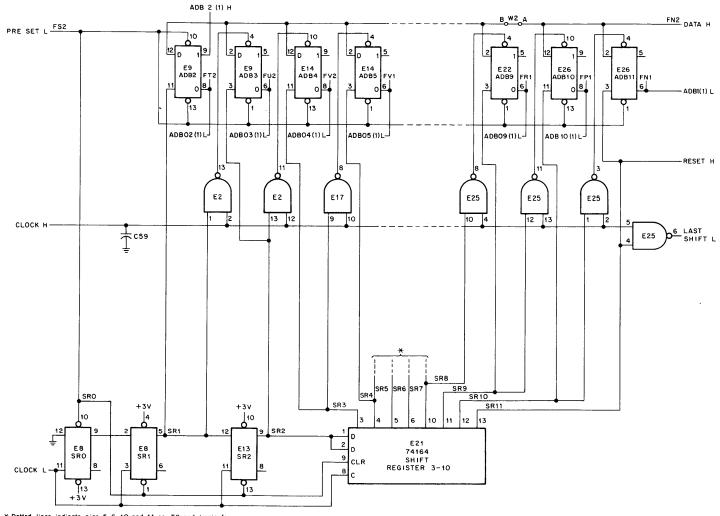

| 4.2.11    | A/D Buffer and Shift Register                               | 4-31 |

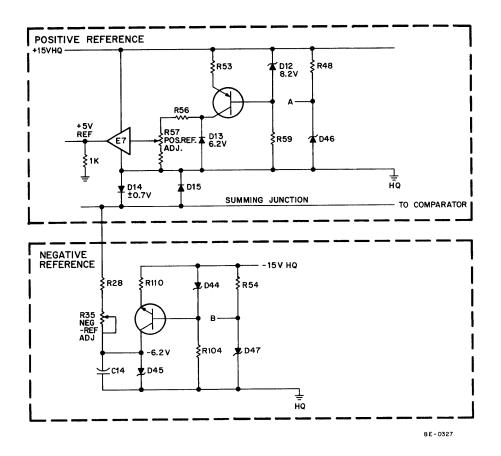

| 4.2.12    | Positive and Negative References                            | 4-33 |

|           | Section 3                                                   |      |

|           | Analog Preamplifier and Multiplexer                         |      |

| 4.3       | Introduction                                                | 4-35 |

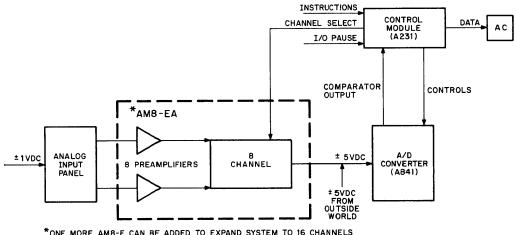

| 4.3.1     | Analog Preamplifier and Multiplexer Expander Block Diagram  | 4-35 |

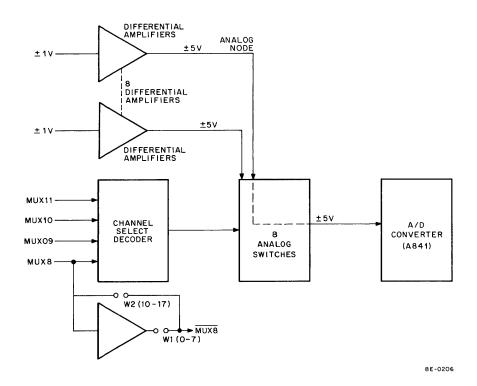

| 4.3.2     | Analog Preamplifier and Multiplexer Expander Detailed Logic | 4-36 |

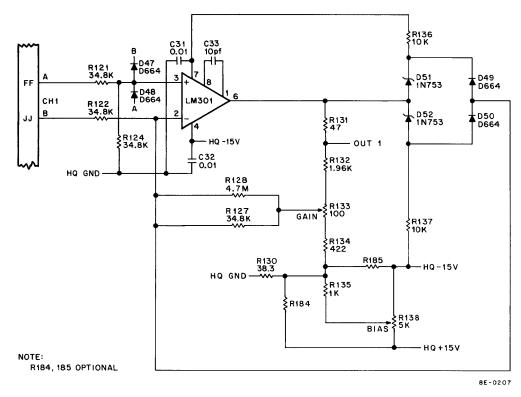

| 4.3.2.1   | Differential Amplifiers                                     | 4-36 |

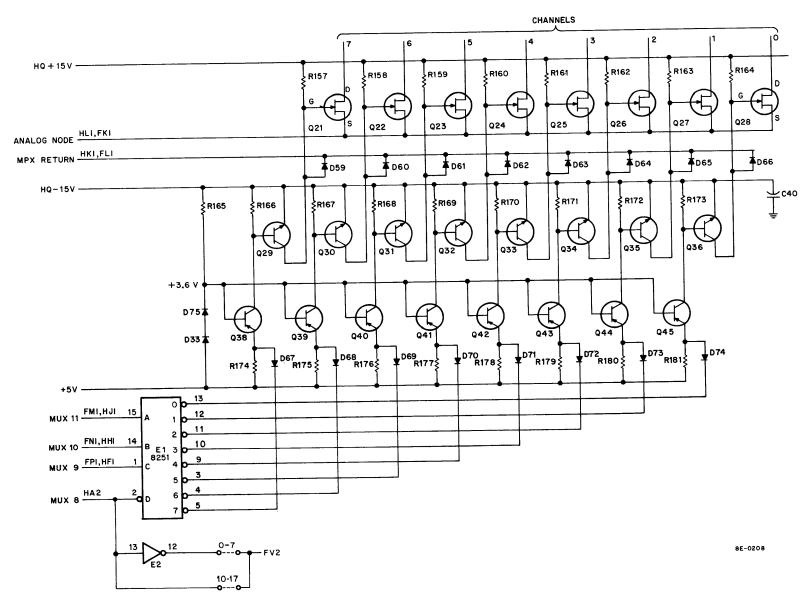

| 4.3.2.2   | Channel Decoder and Analog Switches                         | 4-37 |

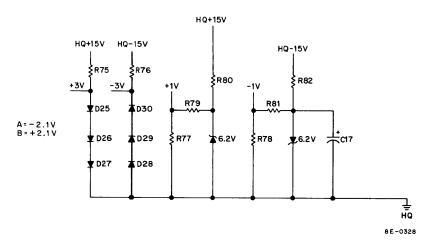

| 4.3.2.3   | Reference Voltages                                          | 4-39 |

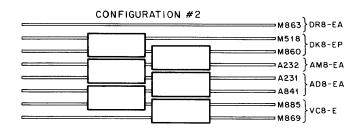

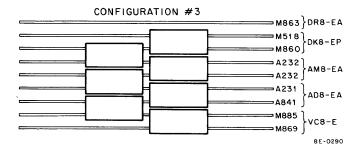

| 4.3.2.4   | Optional Multiplexer Configurations                         | 4-39 |

|           | Section 4                                                   |      |

|           | Point-Plot Display Control (VC8-E)                          |      |

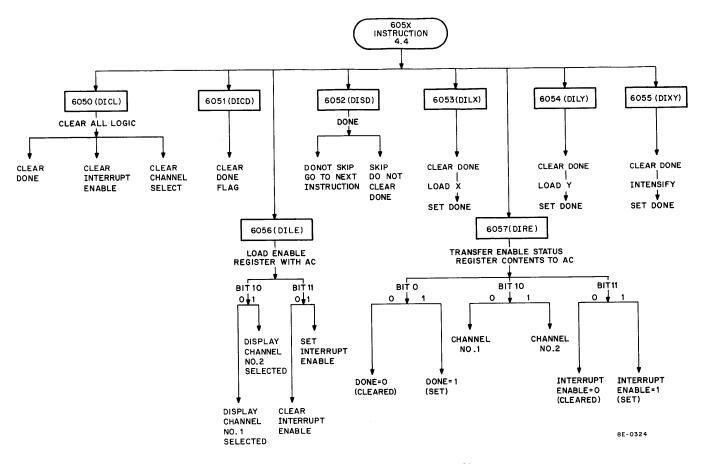

| 4.4       | Introduction                                                | 4-43 |

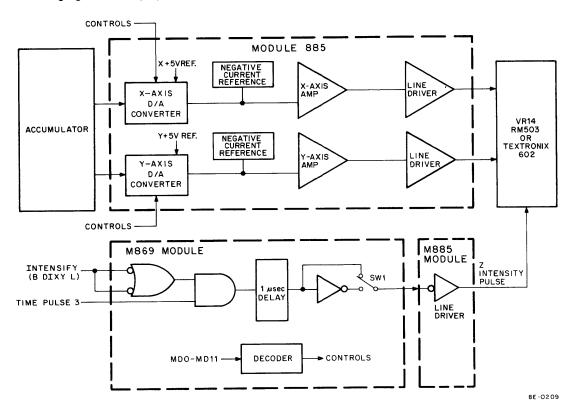

| 4.4.1     | Functional Block Diagram Description                        | 4-46 |

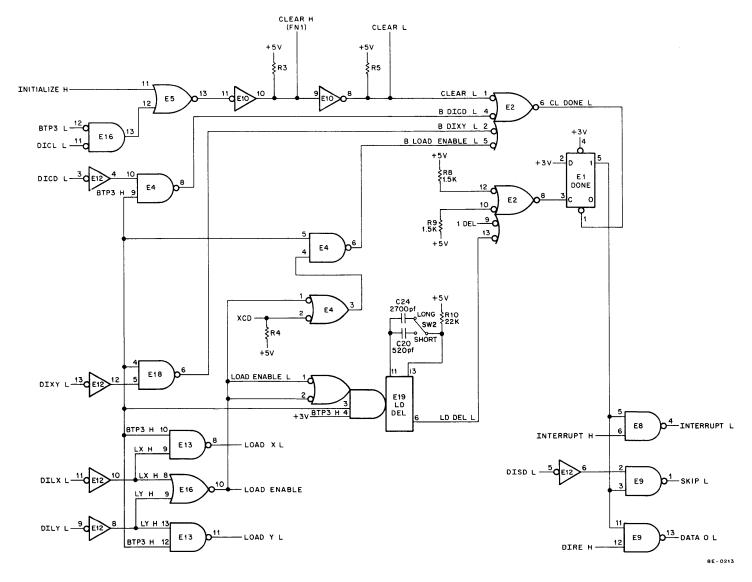

| 4.4.2     | Point-Plot Display Control Detailed Logic                   | 4-49 |

| 4.4.2.1   | Device and Operaiton Select Logic                           | 4-49 |

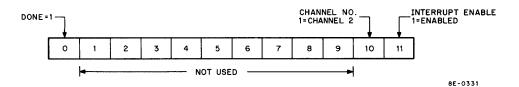

| 4.4.2.2   | Enable/Status Register                                      | 4-49 |

| 4.4.2.2.1 | DONE Logic                                                  | 4-49 |

| 4.4.2.2.2 | Interrupt Enable Logic                                      | 4-51 |

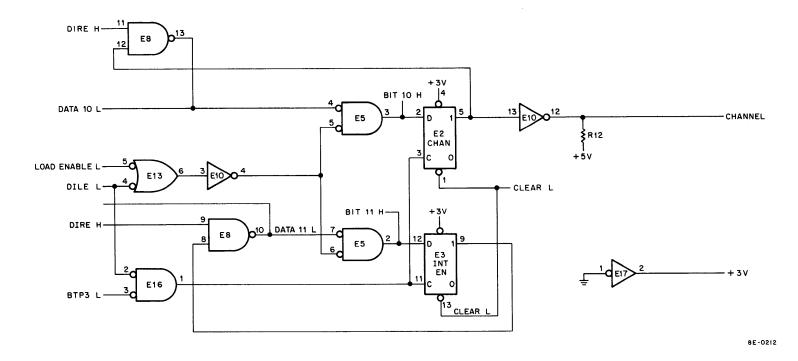

| 4.4.2.2.3 | Channel Select Logic                                        | 4-51 |

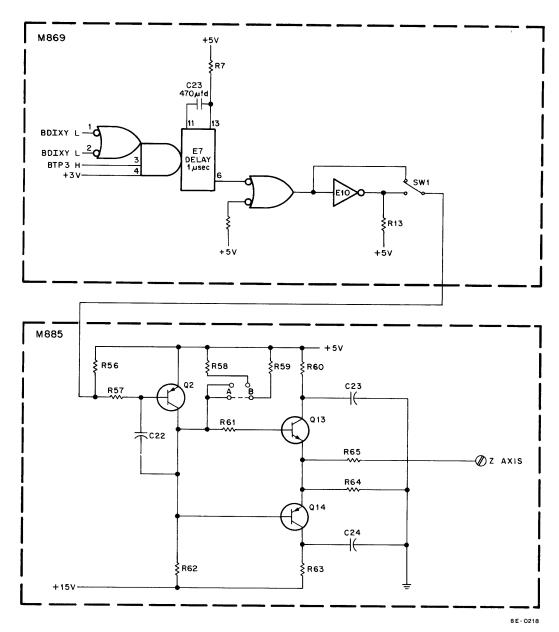

| 4.4.2.3   | Intensity Pulse Generation                                  | 4-51 |

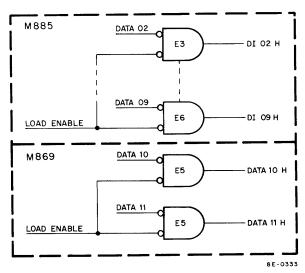

| 4.4.2.4   | Data Gates                                                  | 4-51 |

| 4.4.2.5   | Holding Registers                                           | 4-51 |

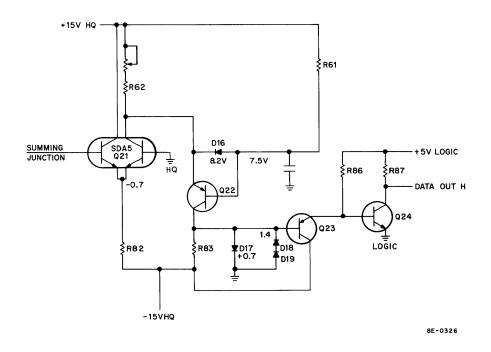

| 4.4.2.6   | Analog Switches and Summing Amplifier                       | 4-53 |

| 4427      | Positive Reference Source                                   | 4-54 |

|           |                                                                    | Page |

|-----------|--------------------------------------------------------------------|------|

|           | Section 5                                                          |      |

|           | Buffered Digital I/O (DR8-EA)                                      |      |

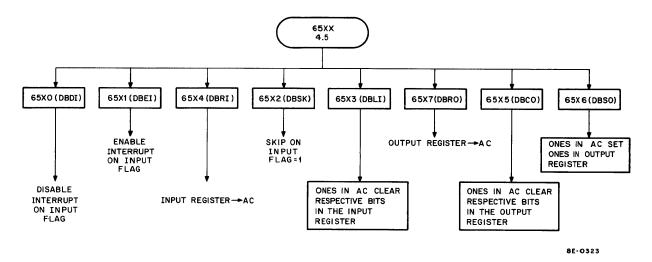

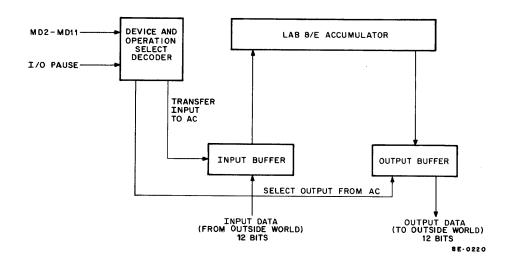

| 4.5       | Introduction                                                       | 4-57 |

| 4.5.1     | Buffered Digital I/O Functional Block Diagram                      | 4.57 |

| 4.5.2     | Buffered Digital I/O Detailed Logic                                |      |

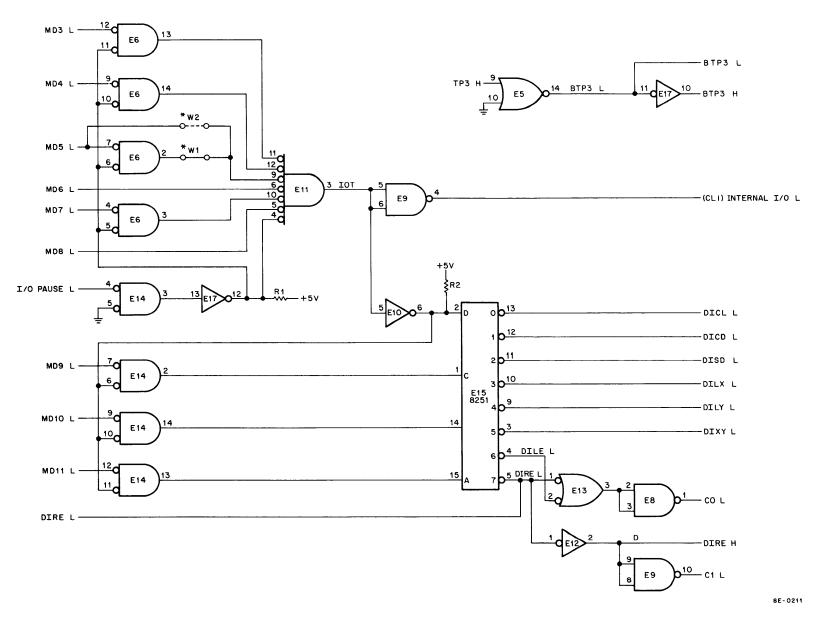

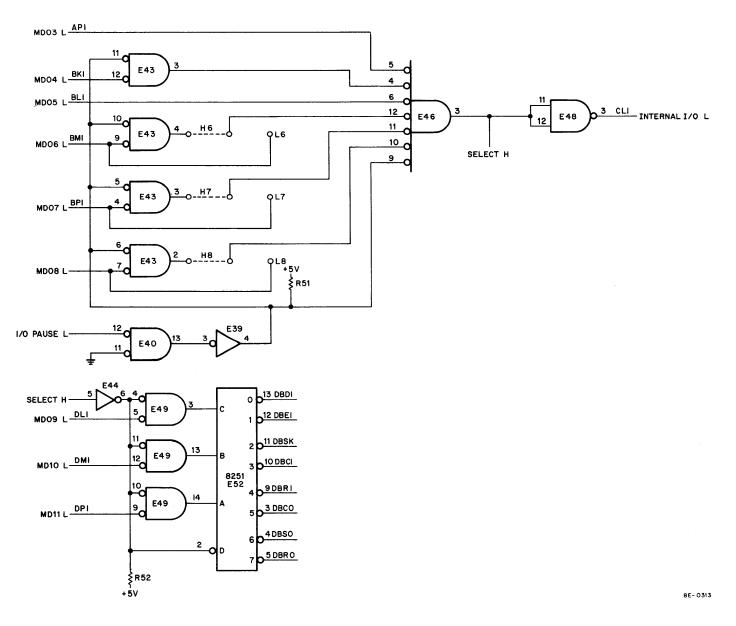

| 4.5.2.1   | Device Select and Operation Decoder                                | 4.59 |

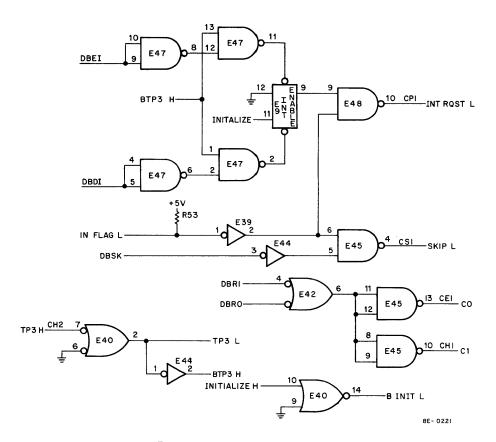

| 4.5.2.2   | Interrupt and Skip Logic                                           | 4.59 |

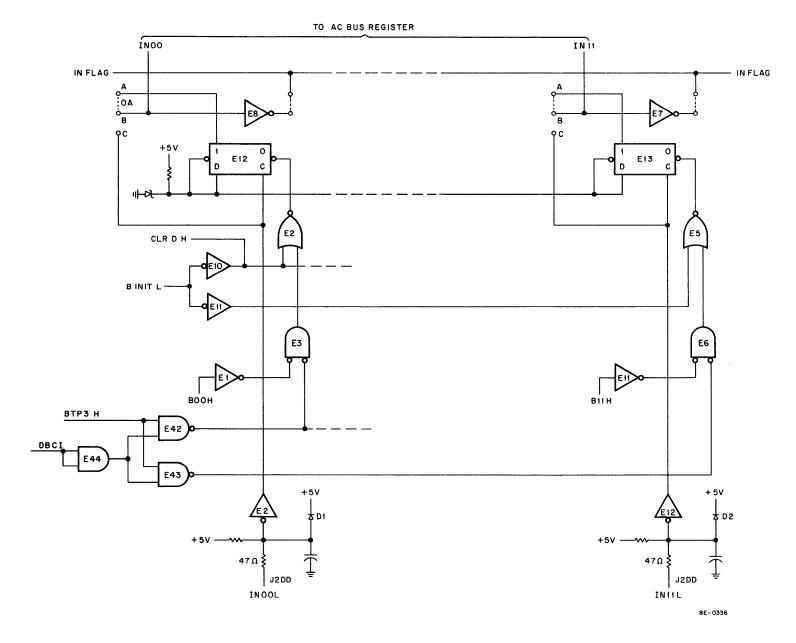

| 4.5.2.3   | Input Register and Control Logic                                   | 4.59 |

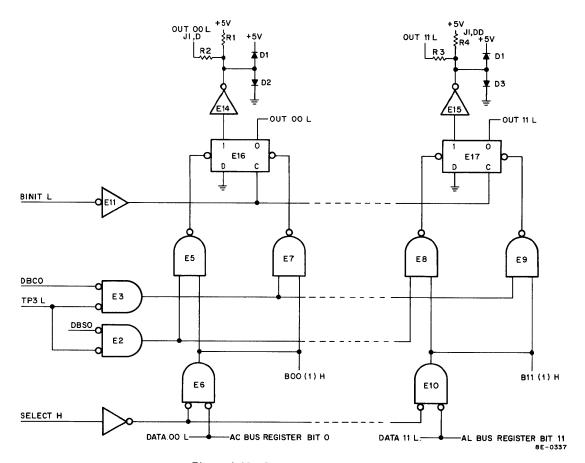

| 4.5.2.4   | Output Register and Control Logic                                  | 4-61 |

| 4.5.2.5   | AC Bus Register                                                    | 4-64 |

|           | Section 6                                                          |      |

|           | Real-Time Programmable Clock (DK8-EP)                              |      |

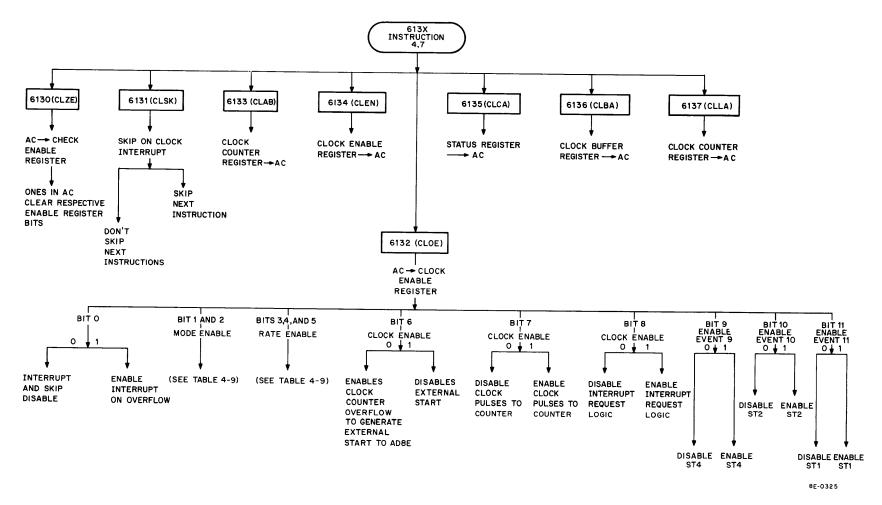

| 4.6       | Introduction                                                       | 4-65 |

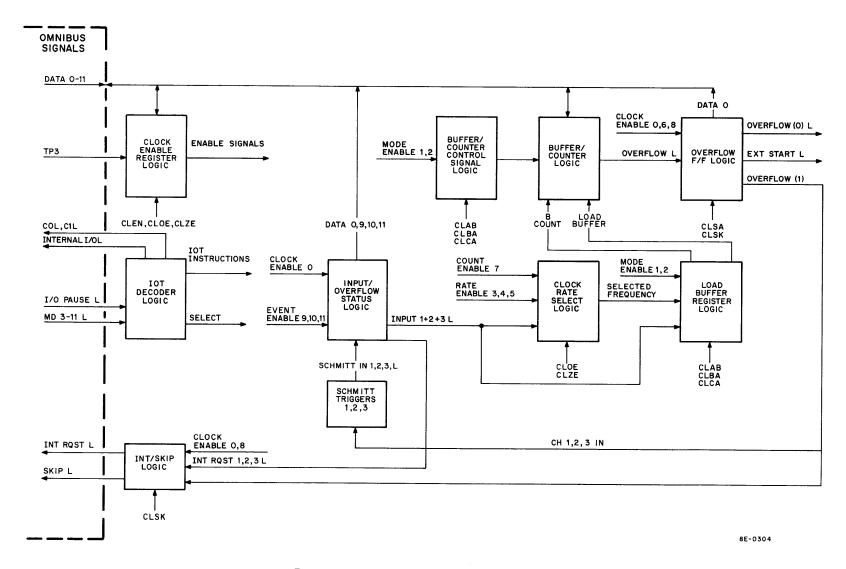

| 4.6.1     | Block Diagram Discussion                                           | 4-66 |

| 4.6.2     | Detailed Logic                                                     | 4.71 |

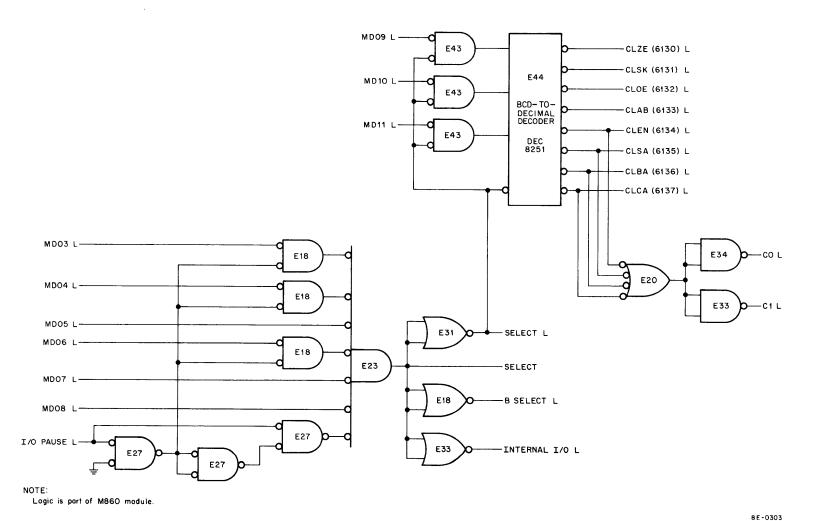

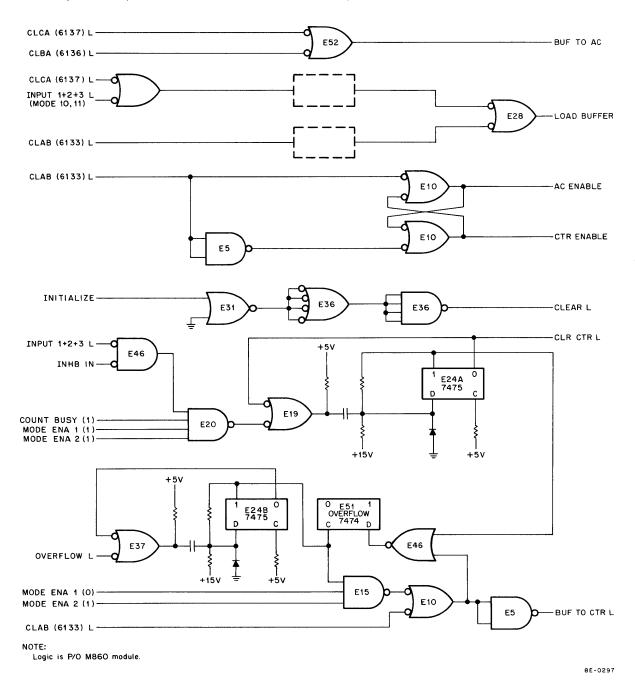

| 4.6.2.1   | IOT Decoder Logic                                                  | 4.71 |

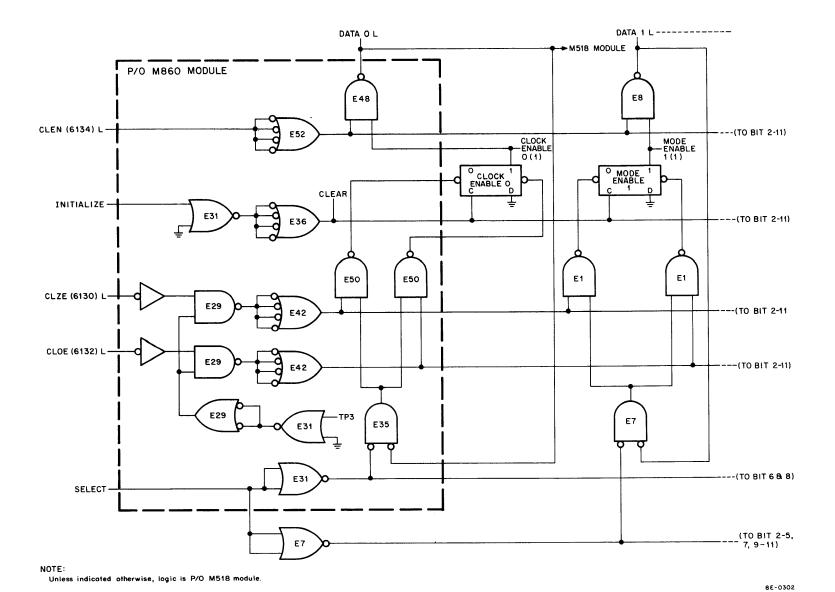

| 4.6.2.2   | Clock Enable Register Logic                                        | 4.71 |

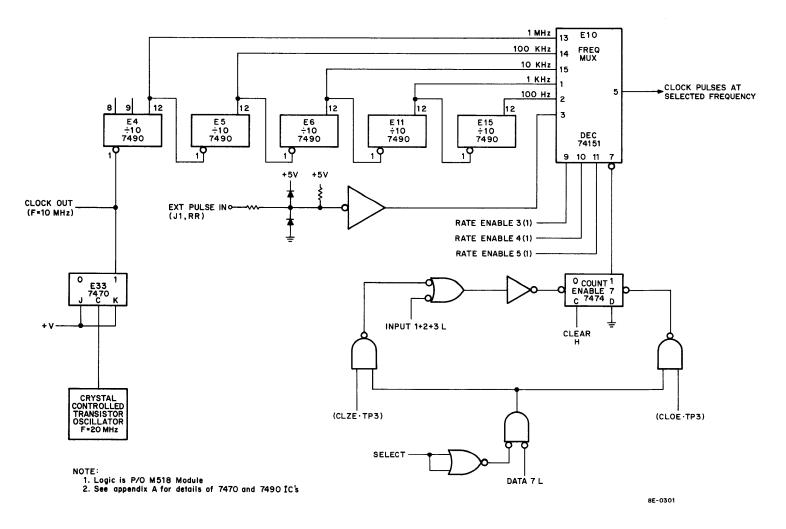

| 4.6.2.3   | Clock Rate Select Logic                                            |      |

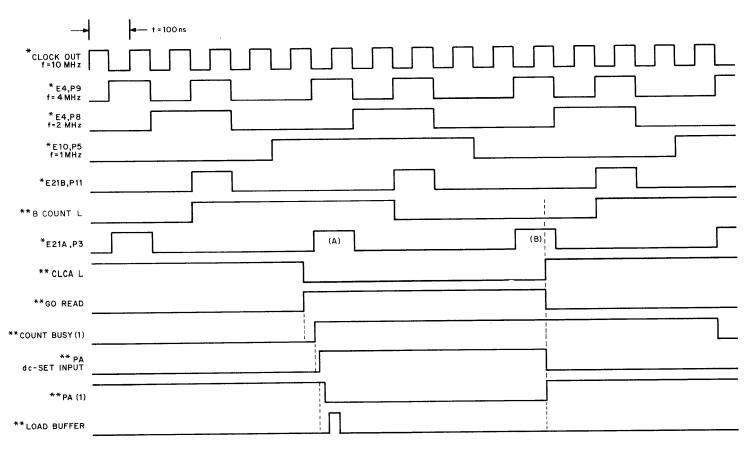

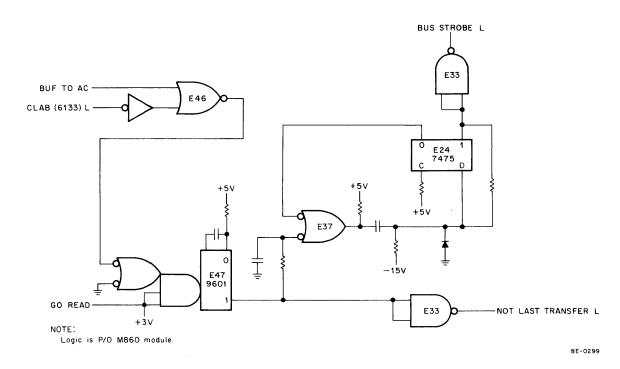

| 4.6.2.4   | Load Buffer Register Logic                                         |      |

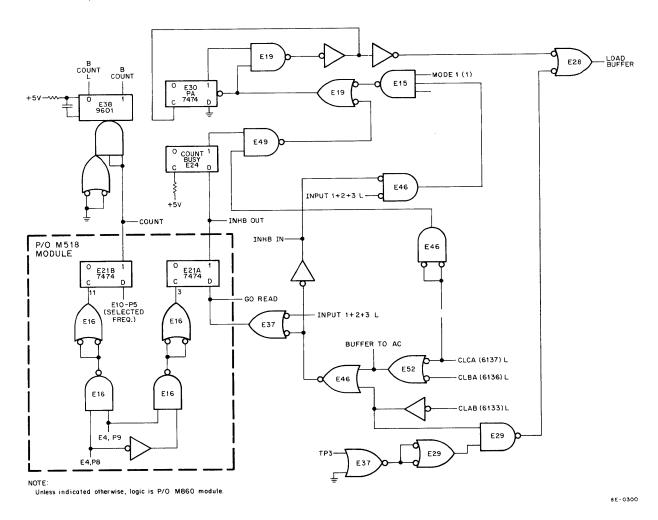

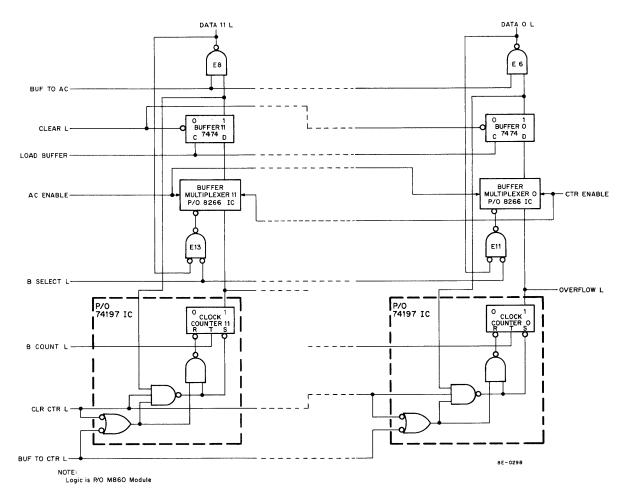

| 4.6.2.5   | Clock Buffer/Clock Counter Logic                                   |      |

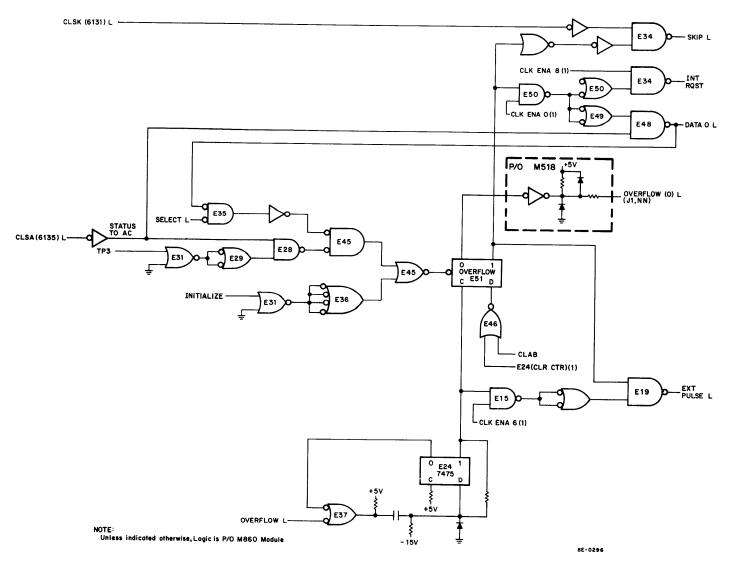

| 4.6.2.6   | Overflow Flip-Flop Logic                                           |      |

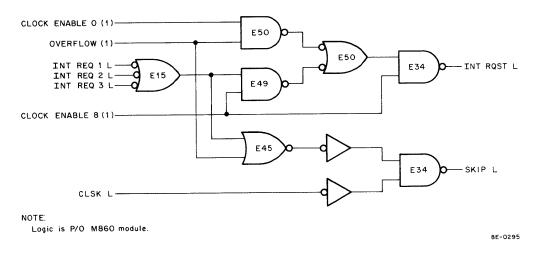

| 4.6.2.7   | Interrupt/Skip Logic                                               | 4-80 |

| 4.6.2.8   | Input/Overflow Status Logic                                        | 4-82 |

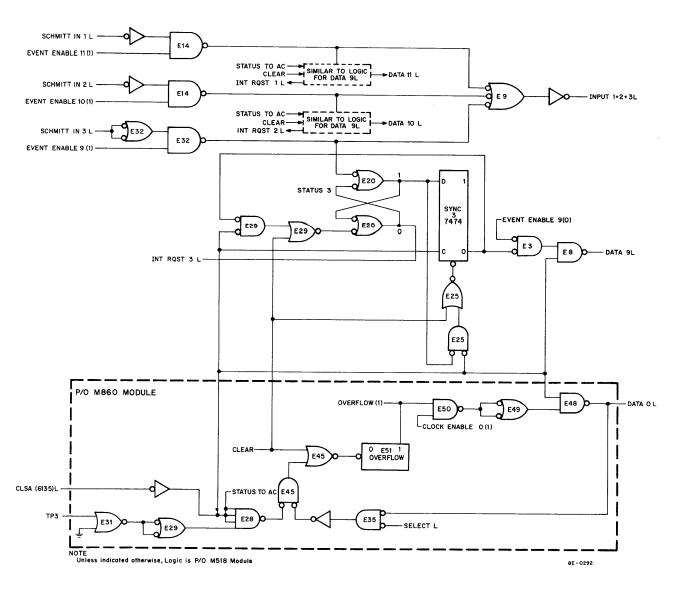

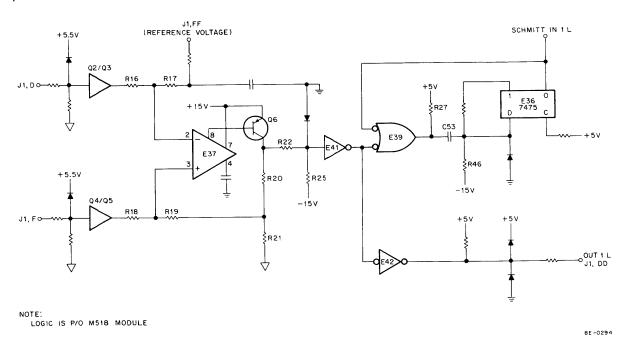

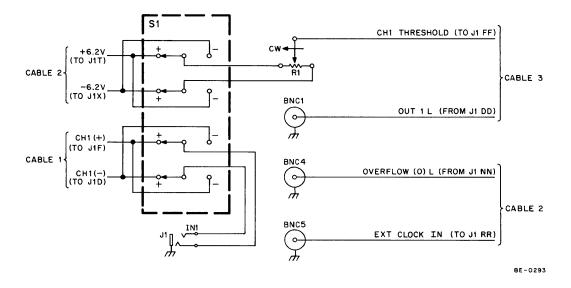

| 4.6.2.9   | Schmitt Trigger Logic                                              | 4-84 |

|           | Continu 7                                                          |      |

|           | Section 7 High Quality Power Supply                                |      |

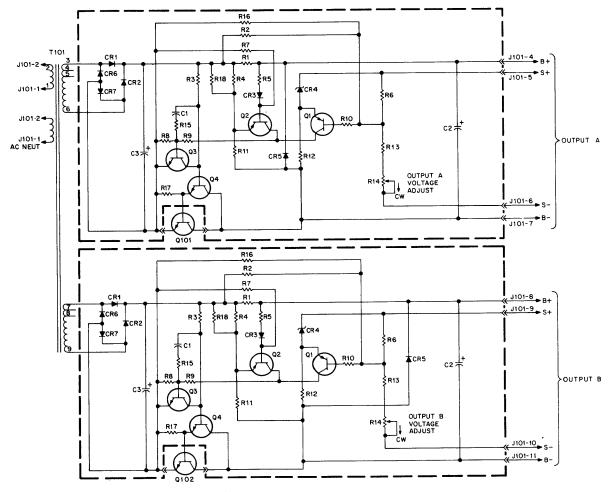

| 4.7       | Introduction                                                       | 4.87 |

| 4.7.1     | High Quality Power Supply Operation                                | 4.87 |

| 4.7.1.1   | Regulator Circuitry                                                | 4.87 |

| 4.7.1.2   | Current-Limiting Circuitry                                         | 4-89 |

| CHAPTER 5 | MAINTENANCE                                                        |      |

|           | Section 1                                                          |      |

|           | Preparation for Maintenance and Maintenance Requirements           |      |

| 5:1       | Equipment                                                          | 5-3  |

| 5.1.1     | Programs                                                           | 5-4  |

| 5.1.1.1   | Display Line on VR14 or User Oscilloscope                          | 5-4  |

| 5.1.1.2   | Display Converted Value in AC (AD8-EA only or channel 0 of AM8-EA) | 5-4  |

| 5.1.1.3   | Display Converted Value in MQ with AM8-EA                          | 5-5  |

|           |                                              | Page |

|-----------|----------------------------------------------|------|

| 5.1.1.4   | Display Converted Value of A/D on VR14       | 5-5  |

| 5.1.1.5   | Start A/D Converter with Real-Time Clock     | 5-6  |

| 5.1.2     | Preventive Maintenance Inspections           | 5-6  |

| 5.1.3     | Scheduled Maintenance                        | 5-7  |

| 5.1.3.1   | Weekly Preventive Maintenance Schedule       | 5-8  |

|           | Section 2                                    |      |

|           | Corrective Maintenance                       |      |

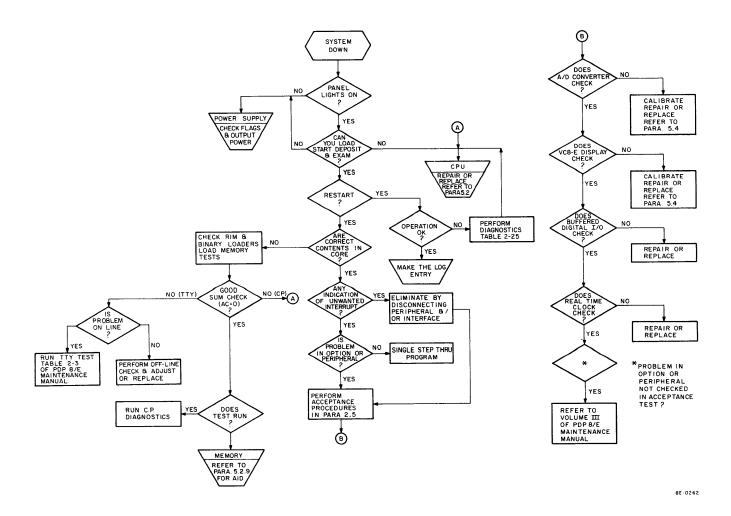

| 5.2       | Maintenance Procedures                       | 5-9  |

| 5.2.1     | Preliminary Investigation                    | 5-9  |

| 5.2.2     | System Troubleshooting                       | 5-9  |

| 5.2.3     | Logic Troubleshooting                        | 5-11 |

| 5.2.4     | Circuit Troubleshooting                      | 5-11 |

| 5.2.5     | Repairs and Replacements                     | 5-12 |

| 5.2.6     | Validation Tests                             | 5-15 |

| 5.2.7     | Log Entry                                    | 5-15 |

| 5.2.8     | CPU Troubleshooting                          | 5-16 |

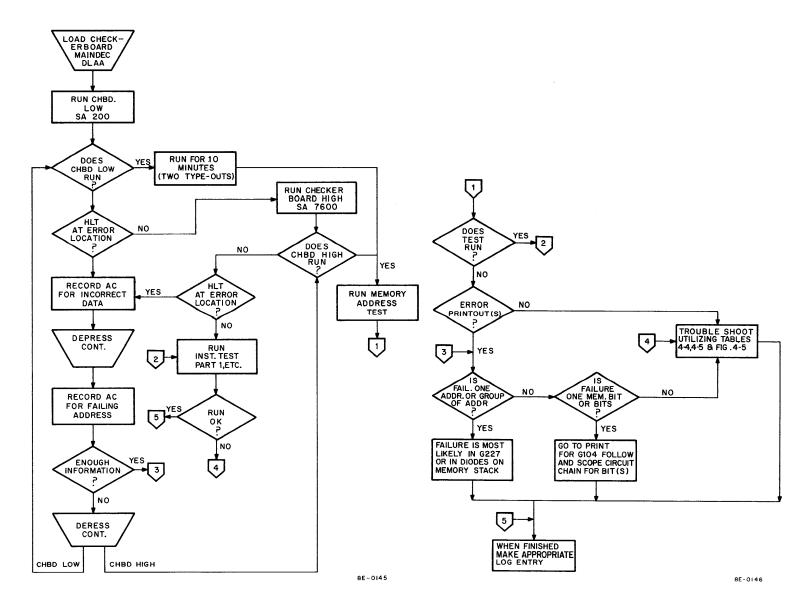

| 5.2.9     | Memory Troubleshooting                       | 5-17 |

| 5.2.9.1   | Memory Resistance Checks                     | 5-19 |

| 5.2.9.2   | Memory Circuit Variables                     | 5-20 |

| 5.2.9.2.1 | Field Select Jumpers                         | 5-21 |

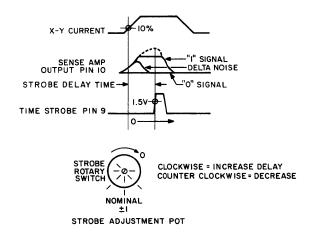

| 5.2.9.2.2 | Strobe Adjustment                            |      |

| 5.2.9.2.3 | Slice Level                                  | 5-21 |

| 5.2.9.2.4 | XY Current Control (G227)                    | 5-21 |

| 5.2.9.2.5 | Temperature Tracking                         | 5-21 |

| 5.2.9.2.6 | Inhibit Current                              | 5-21 |

| 5.2.9.2.7 | Strobe Setting Procedure                     | 5-21 |

| 5.2.10    | H724 Power Supply Troubleshooting Procedures | 5-23 |

| 5.2.10.1  | Overcurrent Protection                       | 5-24 |

| 5.2.10.2  | Hold-Up Time                                 | 5-24 |

| 5.2.10.3  | Thermal Protection                           | 5-24 |

| 5.2.10.4  | Contact Protection                           | 5-24 |

| 5.2.10.5  | Input Switching                              | 5-24 |

| 5.2.10.6  | POWER ON/OFF Switch Adjustment               | 5-24 |

| 5.2.10.7  | Parallel Operation                           | 5-24 |

| 5.2.10.8  | Large Configuration                          | 5-24 |

|           | Section 3                                    |      |

|           | Teletype Maintenance                         |      |

| 5.3       | Introduction                                 | 5-25 |

| 5.3.1     | Special Tools                                | 5-25 |

| 5.3.2     | Programs                                     | 5-25 |

|            |                                                                     | Page |  |  |

|------------|---------------------------------------------------------------------|------|--|--|

|            | Section 4                                                           |      |  |  |

|            | System Calibration                                                  |      |  |  |

| 5.4        | Calibration of the LAB-8/E Options                                  | 5-27 |  |  |

| 5.4.1      | A/D Converter (AD8-EA) Calibration Procedure                        | 5-27 |  |  |

| 5.4.1.1    | Minor Calibration 5                                                 |      |  |  |

| 5.4.1.2    | Major Calibration 5-                                                |      |  |  |

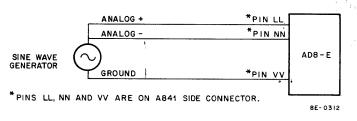

| 5.4.2      | Common Mode Rejection (CMR) Calibration                             | 5-29 |  |  |

| 5.4.3      | Calibration of the Point-Plot Display Control (VC8-E)               |      |  |  |

|            | Using VR14 or Tektronix 602 Display                                 | 5-29 |  |  |

| 5.4.4      | VC8-E Calibration Procedure Without a VR14 or VR03                  | 5-31 |  |  |

| 5.4.5      | Analog Preamplifier and Multiplexer (AM8-EA) Calibration Procedure  | 5-32 |  |  |

| 5.4.6      | VR14 Calibration                                                    | 5-33 |  |  |

| 5.4.7      | Calibration of the Tektronix 602 Using the VC8-E                    | 5-34 |  |  |

|            | Section 5                                                           |      |  |  |

|            | Preventive Maintenance Procedures                                   |      |  |  |

| 5.5        | Preventive Maintenance                                              | 5-35 |  |  |

| 5.5.1      | Weekly Tasks                                                        | 5-35 |  |  |

| 5.5.2      | Preventive Maintenance Tasks                                        | 5-35 |  |  |

|            | Section 6                                                           |      |  |  |

|            | Corrective Maintenance                                              |      |  |  |

| 5.6        | Corrective Maintenance Procedures                                   | 5-37 |  |  |

|            | Section 7                                                           |      |  |  |

|            | Special Troubleshooting Procedures                                  |      |  |  |

| 5.7        | Test Clock (M499)                                                   | 5-39 |  |  |

| CHAPTER 6  | LAB-8/E SYSTEM SPARE PARTS                                          |      |  |  |

| 6.1        | Introduction                                                        | 6-1  |  |  |

| 6.2        | LAB-8/E Central Processor (PDP-8/E and 33 ASR Teletype Spare Parts) | 6-1  |  |  |

| 6.3        | Basic LAB-8/E System Spare Parts                                    | 6-1  |  |  |

| APPENDIX A | IC CIRCUIT DESCRIPTION                                              |      |  |  |

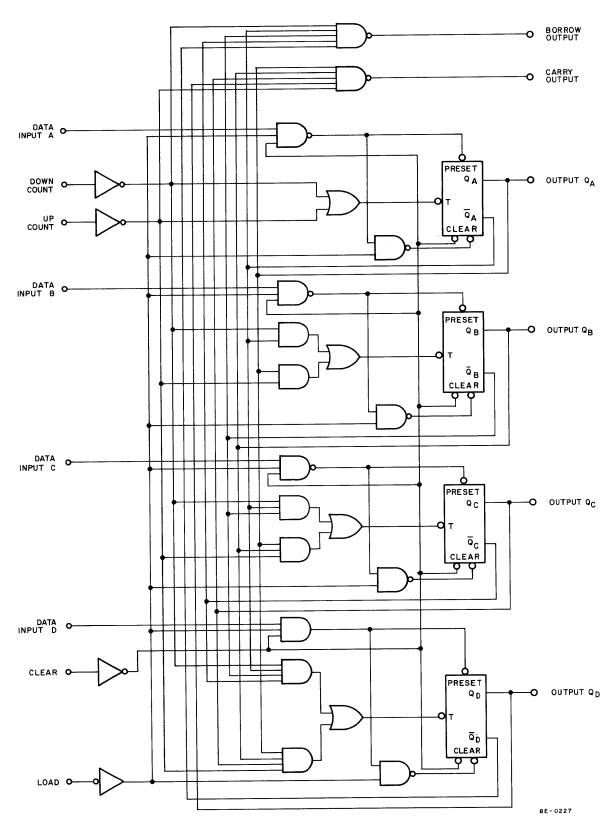

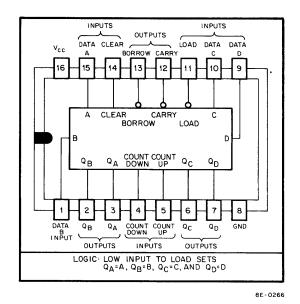

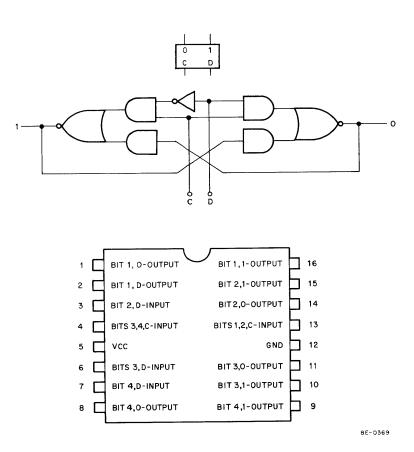

| A.1        | SN 74193 IC                                                         | A-1  |  |  |

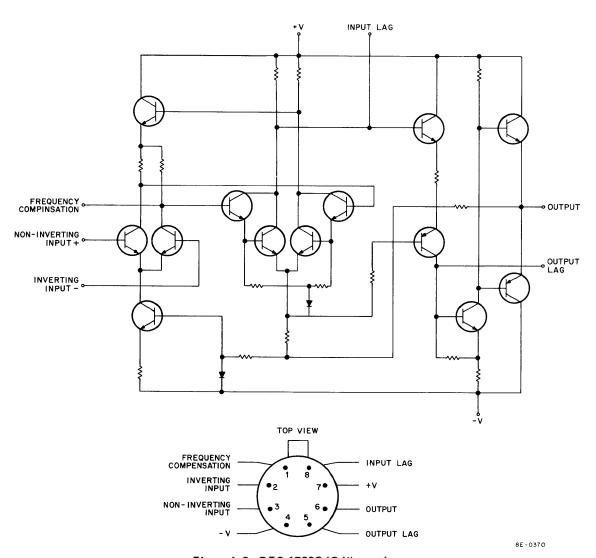

| A.2        | DEC 1709C IC                                                        | A-1  |  |  |

| A.3        | DEC 7475 IC                                                         | A-4  |  |  |

| A.4        | DEC 7490 IC                                                         | A-4  |  |  |

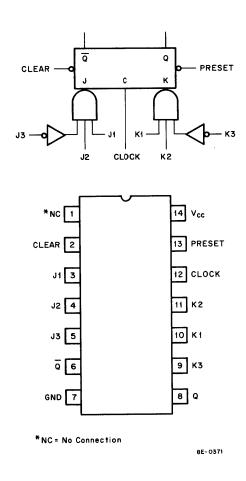

| A.5        | DEC 7470 IC                                                         | A-4  |  |  |

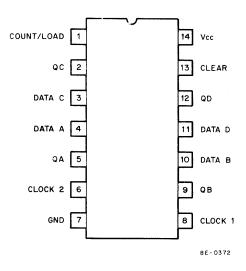

| A.6        | DEC 74197 IC                                                        | A-4  |  |  |

|            |                                                                     |      |  |  |

APPENDIX B LAB-8/E MODULE JUMPER REQUIREMENTS

# **ILLUSTRATIONS**

| Figure No. | Title                                                     |      |

|------------|-----------------------------------------------------------|------|

| 1-1        | LAB-8/E Basic System                                      | 1-2  |

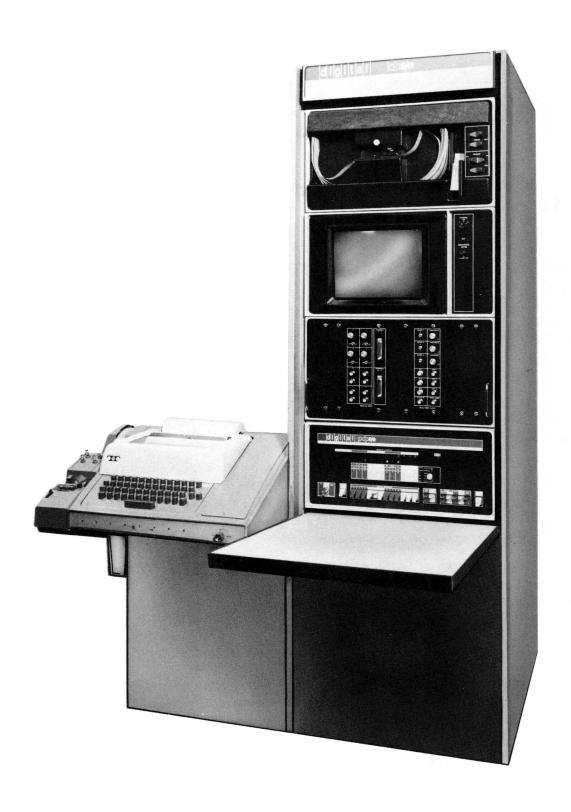

| 1-2        | LAB-8/E Rack-Mounted Version                              | 1-8  |

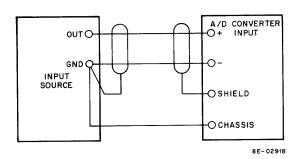

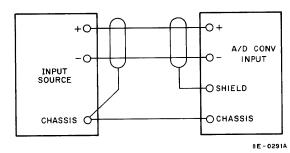

| 2-1        | Single-Ended Measurement Connection                       | 2-2  |

| 2-2        | Differential Input Measurement Connection                 | 2-2  |

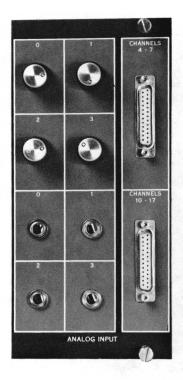

| 2-3        | AM8-ED Analog Input Panel                                 | 2-3  |

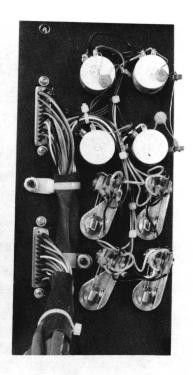

| 2-4        | AM8-EC Analog Input Panel, Front and Rear View            | 2-3  |

| 2-5        | Front View of DB-25S Connector and Telephone Plug         | 2-3  |

| 2-6        | Edge Connector Installation (top view)                    | 2-15 |

| 2-7        | Analog Inputs for Accuracy Check                          | 2-20 |

| 2-8        | Negative Input Checkout                                   | 2-22 |

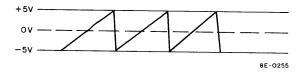

| 2-9        | Oscilloscope Display for Ramp Test                        | 2-25 |

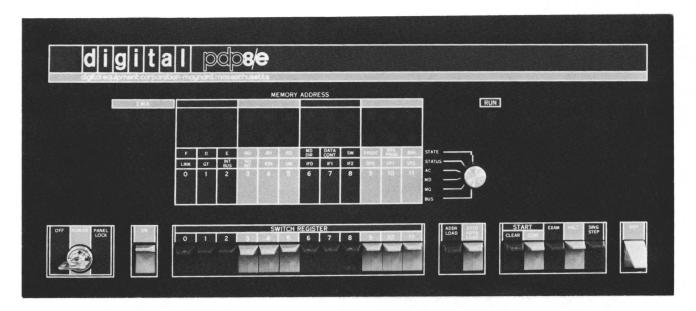

| 3-1        | Programmer's Console                                      | 3-1  |

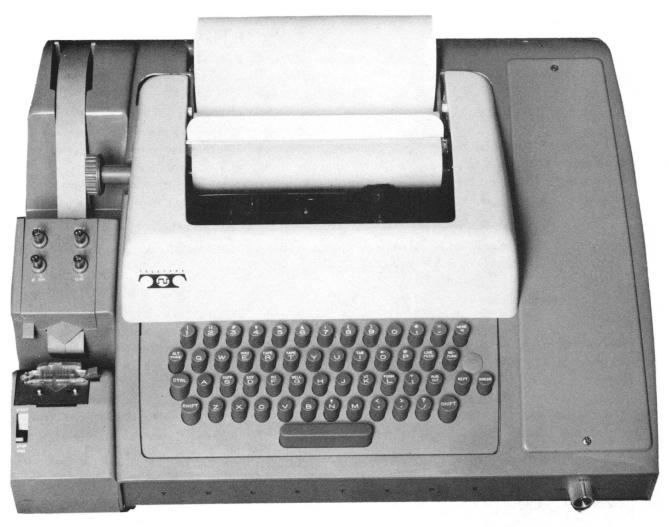

| 3-2        | Teletype Model 33 ASR Console                             | 3-2  |

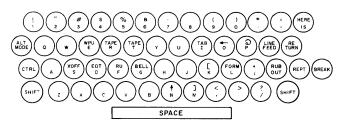

| 3-3        | Teletype Keyboard                                         | 3-5  |

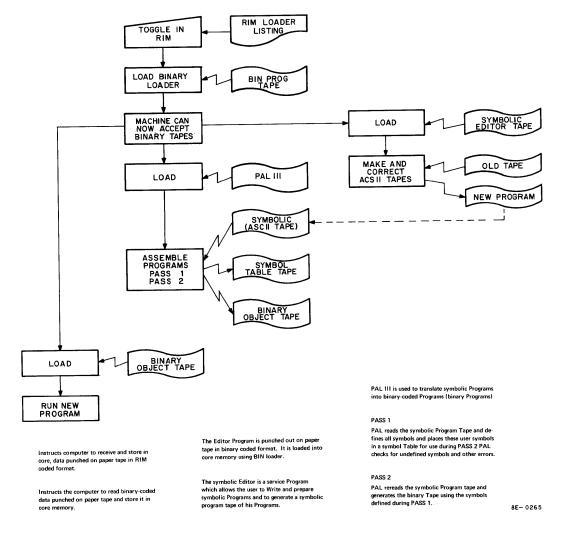

| 3-4        | Loading Data Under Program Control                        | 3-8  |

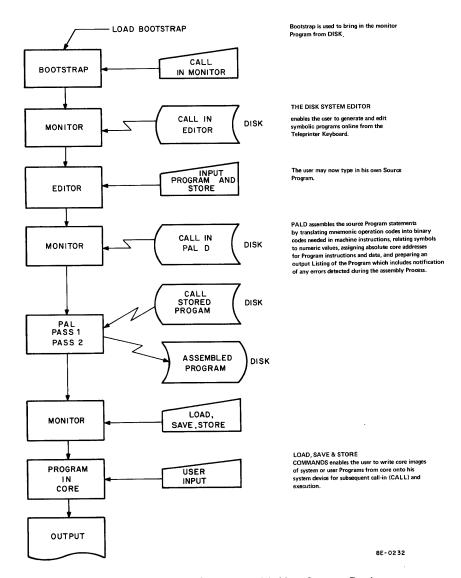

| 3-5        | Loading Programs with Mass Storage Devices                | 3-9  |

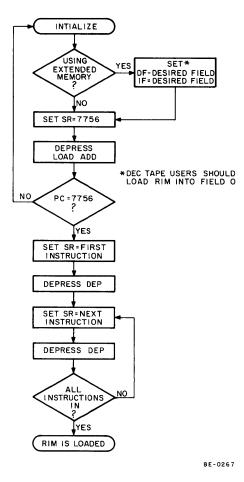

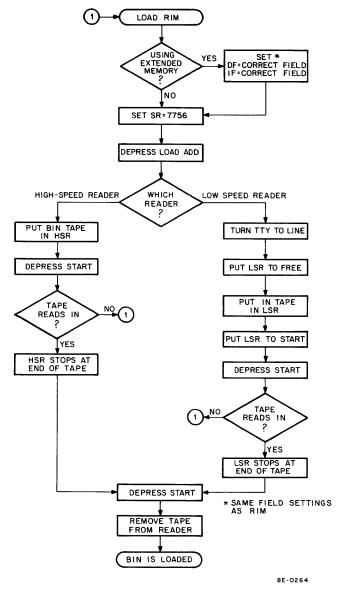

| 3-6        | Loading the RIM Loader                                    | 3-10 |

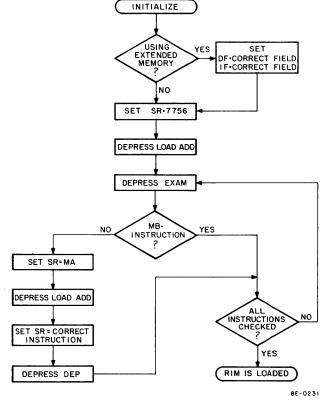

| 3-7        | Checking the RIM Loader                                   | 3-10 |

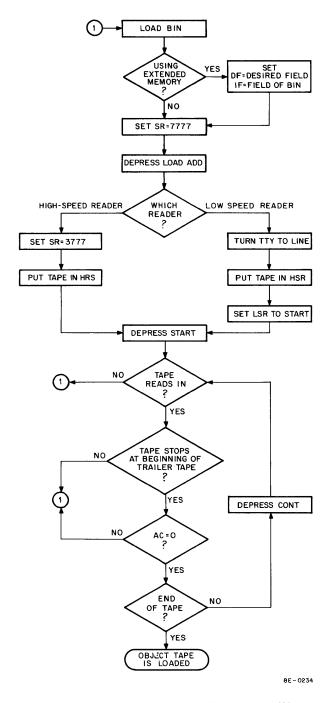

| 3-8        | Loading the BIN Loader                                    | 3-11 |

| 3-9        | Loading a Binary Tape Using BIN                           | 3-12 |

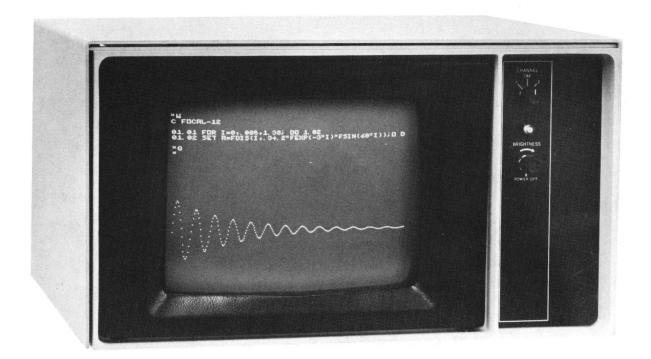

| 3-10       | VR14 Display Oscilloscope                                 | 3-13 |

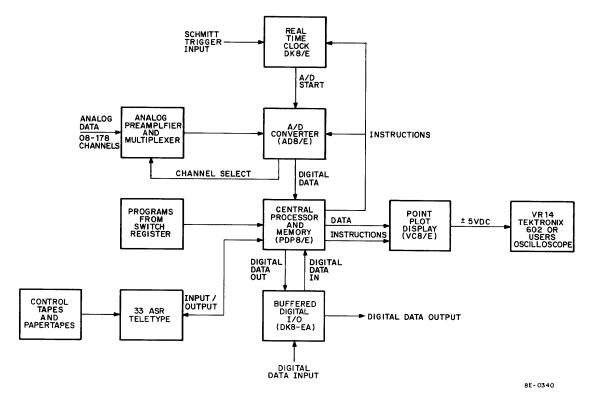

| 4-1        | LAB-8/E Block Diagram                                     | 4-3  |

| 4-2        | A/D Converter Flow Chart                                  | 4-5  |

| 4-3        | Buffered Digital I/O Flow Chart                           | 4-6  |

| 4-4        | Real-Time Programmable Clock Flow Chart                   | 4-7  |

| 4-5        | Point-Plot Display Control Flow Chart                     | 4-8  |

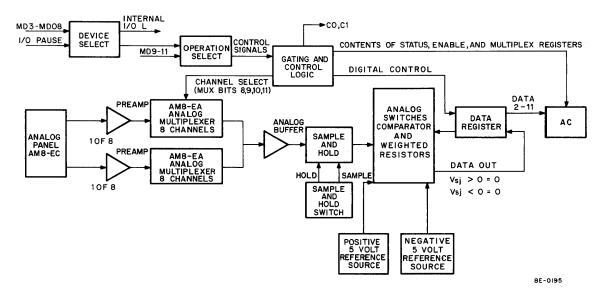

| 4-6        | Analog-to-Digital Converter Block Diagram                 | 4-11 |

| 4-7        | Enable/Status Register Contents                           | 4-12 |

| 4-8        | A/D Converter Functional Block Diagram                    | 4-14 |

| 4-9        | A/D Buffer and Switch Logic                               | 4-17 |

| 4-10       | Device and Operation Select Logic                         | 4-18 |

| 4-11       | Interrupt, Skip, and Control Logic                        | 4-19 |

| 4-12       | Interrupt Timing Diagram                                  | 4-20 |

| 4-13       | MUX Register Logic                                        | 4-22 |

| 4-14       | Enable Register Logic                                     | 4-24 |

| 4-15       | Analog Buffer and Sample and Hold Circuits                | 4-25 |

| 4-16       | Signal at AA1 with a Slow Ramp Input to the A/D Converter | 4-26 |

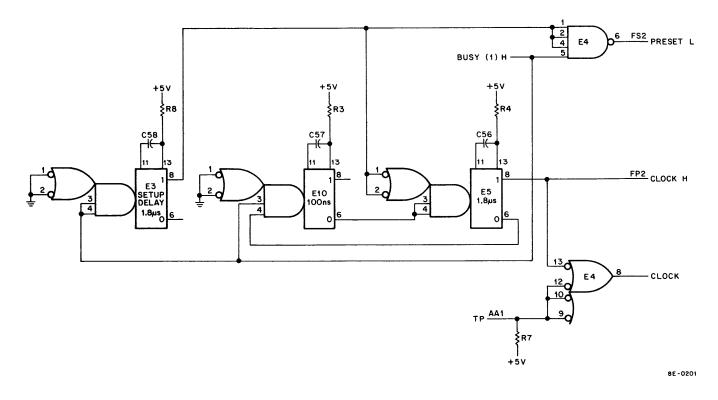

| 4-17       | Analog-to-Digital Converter Internal Clock                | 4-27 |

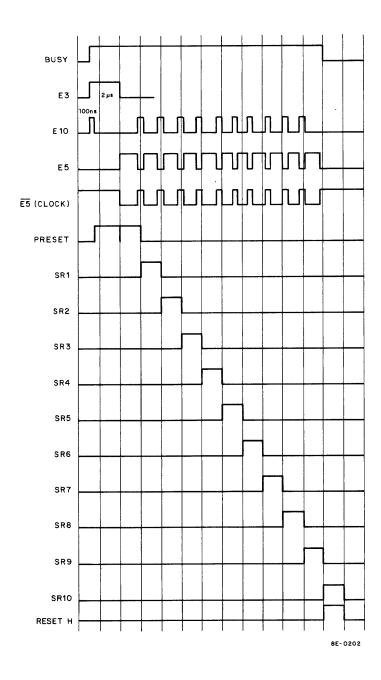

| 4-18       | Analog-to-Digital Converter Internal Timing Diagram       | 4-28 |

| 4-19       | A/D Converter Shift Register and Data Buffer              | 4-29 |

| 4-20       | Analog Switches                                           | 4-30 |

| 4-21       | Comparator Circuits                                       | 4-31 |

| 4-22       | A/D Buffer Signal                                         | 4-32 |

| 4-23       | Summing Junction and Comparator Output Signals            | 4-33 |

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                   | Page |

|------------|---------------------------------------------------------|------|

| 4-24       | Signals at AA1 and Collector of Q20 on the A841 Module  | 4-33 |

| 4-25       | Positive and Negative References                        | 4-34 |

| 4-26       | Analog Preamplifier and Multiplexer Block Diagram       | 4-35 |

| 4-27       | Analog Preamplifier and Multiplexer Expander Functional |      |

|            | Block Diagram                                           | 4-36 |

| 4-28       | Differential Amplifier                                  | 4-37 |

| 4-29       | Channel Decoder and Analog Switches                     | 4-38 |

| 4-30       | AM8-EA Reference Voltages                               | 4-39 |

| 4-31       | Point-Plot Display of Coordinate Data                   | 4-43 |

| 4-32       | Point-Plot Display Control Block Diagram                | 4-44 |

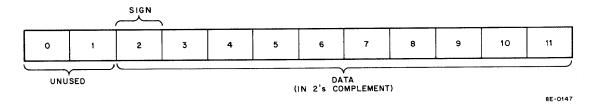

| 4-33       | AC Input Data Format                                    | 4-44 |

| 4-34       | Analog Switches and Summing Amplifier                   | 4-45 |

| 4-35       | One Analog Switch and Summing Amplifier                 | 4-45 |

| 4-36       | Device and Operation Select Logic                       | 4-48 |

| 4-37       | Enable/Status Register                                  | 4-50 |

| 4-38       | Enable/Status Register Word Contents                    | 4-51 |

| 4-39       | DONE and Interrupt Logic                                | 4-52 |

| 4-40       | Intensity Pulse Logic                                   | 4-53 |

| 4-41       | Data Gates                                              | 4-54 |

| 4-42       | X-Axis Holding Register                                 | 4-54 |

| 4-43       | Analog Switches and Summing Amplifier                   | 4-55 |

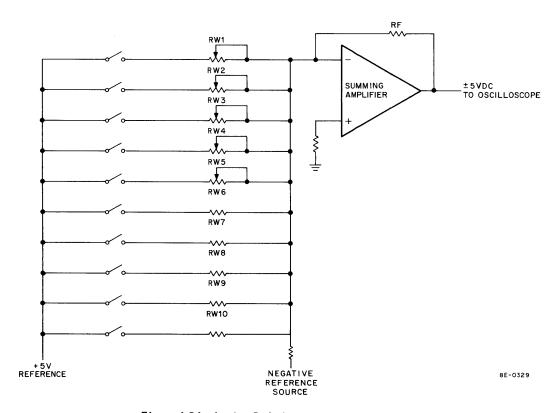

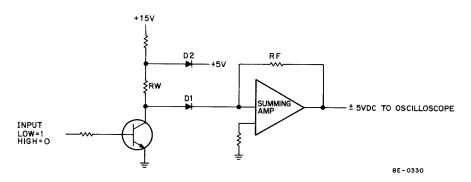

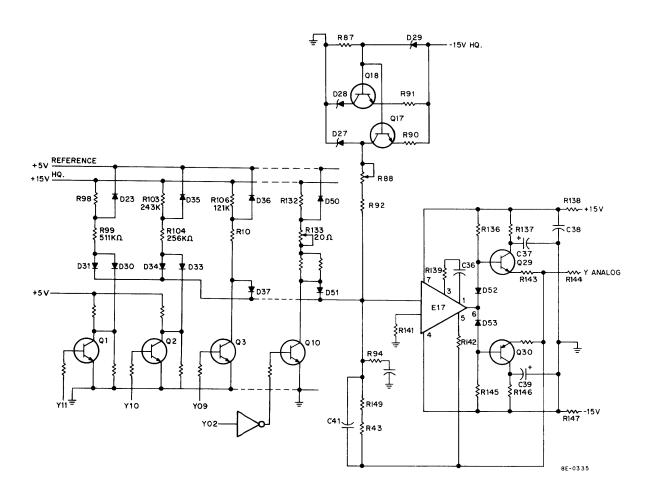

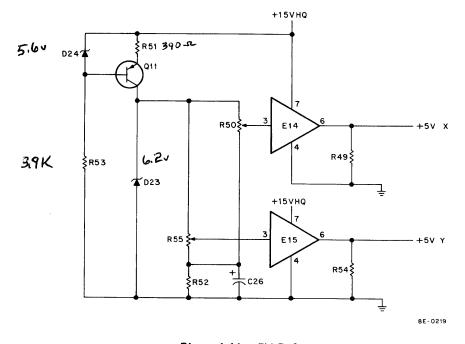

| 4-44       | +5V Reference                                           | 4-55 |

| 4-45       | Buffered Digital I/O Block Diagram                      | 4-57 |

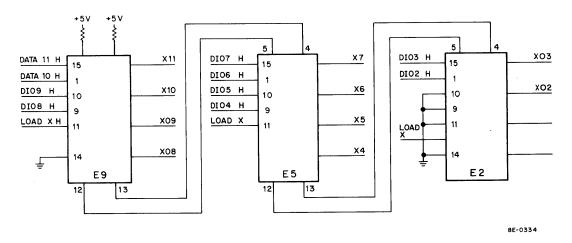

| 4-46       | Device Select and Operation Decoder Logic               | 4-60 |

| 4-47       | Interrupt and Skip Logic                                | 4-61 |

| 4-48       | Input Buffer Register and Logic                         | 4-62 |

| 4-49       | Output Register and Logic                               | 4-63 |

| 4-50       | AC Bus Register                                         | 4-63 |

| 4-51       | DK8-EP Functional Block Diagram                         | 4-67 |

| 4-52       | IOT Decoder Logic                                       | 4-69 |

| 4-53       | Clock Enable Register Logic                             | 4-72 |

| 4-54       | Clock Rate Select Logic                                 | 4-73 |

| 4-55       | Load Buffer Register Logic                              | 4-74 |

| 4-56       | Load Buffer Register Timing                             | 4-76 |

| 4-57       | NOT LAST TRANSFER Logic                                 | 4-77 |

| 4-58       | Clock Buffer/Clock Counter Logic                        | 4-78 |

| 4-59       | Clock Buffer/Clock Counter Control Signals              | 4-79 |

| 4-60       | OVERFLOW Flip-Flop Logic                                | 4-81 |

| 4-61       | Interrupt/Skip Logic                                    | 4-82 |

| 4-62       | Input/Overflow Status Logic                             | 4-83 |

| 4-63       | Schmitt Trigger Logic                                   | 4-84 |

| 4-64       | DK8-EF Front Panel Schematic                            | 4-85 |

| 4-65       | High Quality Power Supply Schematic                     | 4-88 |

# ILLUSTRATIONS (Cont) Title

Page

Figure No.

| 4-66                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

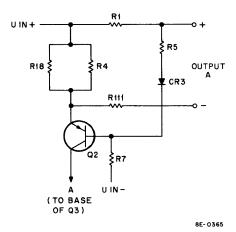

| 4-00                                                                               | Current Limiting Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-88                                                    |

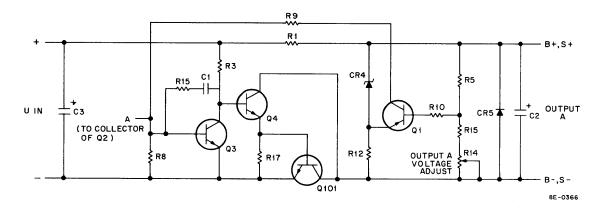

| 4-67                                                                               | Regulator Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-89                                                    |

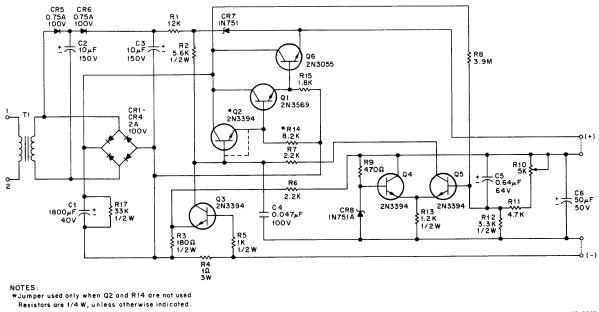

| 4-68                                                                               | Power Mate (20885-8) HQ Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-90                                                    |

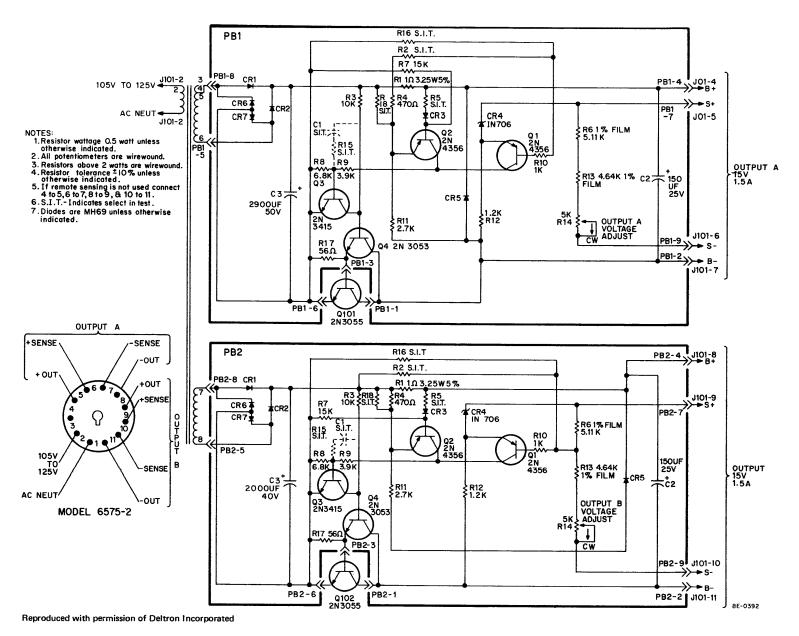

| 4-69                                                                               | Deltron (C13495) HQ Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-91                                                    |

| 5-1                                                                                | System Troubleshooting Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-10                                                    |

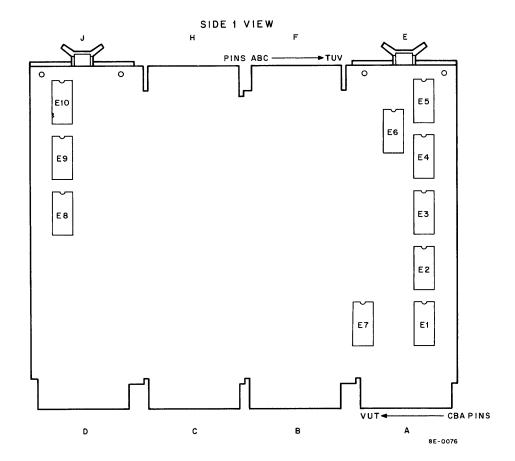

| 5-2                                                                                | IC Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-13                                                    |

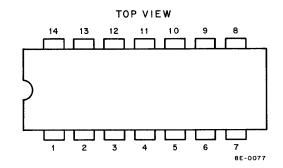

| 5-3                                                                                | IC Pin Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-13                                                    |

| 5-4                                                                                | Memory Troubleshooting Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-18                                                    |

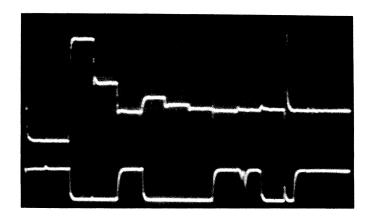

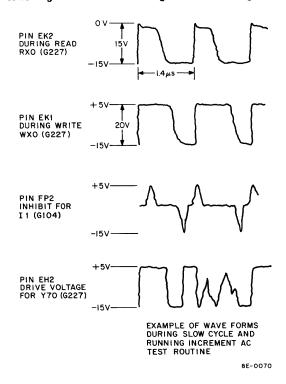

| 5-5                                                                                | Memory Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-20                                                    |

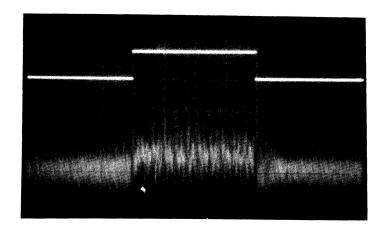

| 5-6                                                                                | Setting of Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-22                                                    |

| 5-7                                                                                | AD8-EA Common Mode Rejection Calibration Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-29                                                    |

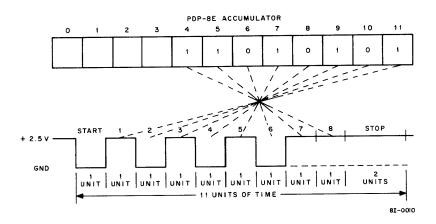

| 5-8                                                                                | Teletype Signal Waveform and Bit Relationship for the Character U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-38                                                    |

| A-1                                                                                | 74193 IC Logic Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A-2                                                     |

| A-2                                                                                | 74193 IC Pin Location (Top View)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A-3                                                     |

| A-3                                                                                | DEC 1709C IC Illustrations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A-3                                                     |

| A-4                                                                                | DEC 7475 IC Illustrations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A-6                                                     |

| A-5                                                                                | DEC 7490 IC Illustrations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A-7                                                     |

| A-6                                                                                | DEC 7470 IC Illustrations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A-8                                                     |

| A-7                                                                                | DEC 74197 IC Illustrations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A-9                                                     |

| Table No.                                                                          | TABLES Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                    |

|                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | i auc                                                   |

| 4.4                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                       |

| 1-1                                                                                | LAB-8/E System Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-4                                                     |

| 1-1<br>1-2                                                                         | LAB-8/E System Specifications<br>LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-4                                                     |

| 1-2                                                                                | LAB-8/E System Specifications<br>LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and<br>Engineering Drawings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-4<br>1-9                                              |

| 1-2                                                                                | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-4<br>1-9<br>2-1                                       |

| 1-2<br>2-1<br>2-2                                                                  | LAB-8/E System Specifications  LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings  Summary of Installation Functions  AM8-ED and AM8-EC Analog Panel Pin Connections                                                                                                                                                                                                                                                                                                                                                                                                          | 1-4<br>1-9<br>2-1<br>2-3                                |

| 1-2<br>2-1<br>2-2<br>2-3                                                           | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable                                                                                                                                                                                                                                                                                                                                                                       | 1-4<br>1-9<br>2-1<br>2-3<br>2-4                         |

| 1-2<br>2-1<br>2-2<br>2-3<br>2-4                                                    | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments                                                                                                                                                                                                                                                                                                                                | 1-4<br>1-9<br>2-1<br>2-3<br>2-4<br>2-4                  |

| 1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5                                             | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly                                                                                                                                                                                                                                                                                          | 1-4<br>1-9<br>2-1<br>2-3<br>2-4<br>2-4<br>2-4           |

| 1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6                                      | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly Real-Time Programmable Clock Connections                                                                                                                                                                                                                                                 | 1-4<br>1-9<br>2-1<br>2-3<br>2-4<br>2-4<br>2-4<br>2-5    |

| 1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7                               | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly Real-Time Programmable Clock Connections VC8-E Cable Connections                                                                                                                                                                                                                         | 1-4 1-9 2-1 2-3 2-4 2-4 2-5 2-5                         |

| 1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8                        | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly Real-Time Programmable Clock Connections VC8-E Cable Connections AD8-EA Accessory and Component List                                                                                                                                                                                     | 1-4 1-9 2-1 2-3 2-4 2-4 2-5 2-5 2-7                     |

| 1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9                 | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly Real-Time Programmable Clock Connections VC8-E Cable Connections AD8-EA Accessory and Component List AD8-ES Accessory and Component List                                                                                                                                                 | 1-4 1-9 2-1 2-3 2-4 2-4 2-5 2-5 2-7 2-8                 |

| 1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10         | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly Real-Time Programmable Clock Connections VC8-E Cable Connections AD8-EA Accessory and Component List AM8-EA Accessory and Component List                                                                                                                                                 | 1-4 1-9 2-1 2-3 2-4 2-4 2-5 2-5 2-7 2-8 2-8             |

| 1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9                 | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly Real-Time Programmable Clock Connections VC8-E Cable Connections AD8-EA Accessory and Component List AM8-EA Accessory and Component List AM8-EA Accessory and Component List                                                                                                             | 1-4 1-9 2-1 2-3 2-4 2-4 2-5 2-5 2-7 2-8 2-8 2-9         |

| 1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11 | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly Real-Time Programmable Clock Connections VC8-E Cable Connections AD8-EA Accessory and Component List AD8-ES Accessory and Component List AM8-EA Accessory and Component List AM8-EC Accessory and Component List AM8-ED Accessory and Component List                                     | 1-4 1-9 2-1 2-3 2-4 2-4 2-5 2-5 2-7 2-8 2-8             |

| 1-2 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12                             | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly Real-Time Programmable Clock Connections VC8-E Cable Connections AD8-EA Accessory and Component List AM8-EA Accessory and Component List AM8-EA Accessory and Component List                                                                                                             | 1-4 1-9 2-1 2-3 2-4 2-4 2-5 2-5 2-7 2-8 2-8 2-9         |

| 1-2 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-13                        | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly Real-Time Programmable Clock Connections VC8-E Cable Connections AD8-EA Accessory and Component List AM8-EA Accessory and Component List AM8-EC Accessory and Component List AM8-EC Accessory and Component List AM8-ED Accessory and Component List DK8-EF Accessory and Component List | 1-4 1-9 2-1 2-3 2-4 2-4 2-5 2-5 2-7 2-8 2-8 2-9 2-9 2-9 |

| 1-2 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-13 2-14                   | LAB-8/E System Specifications LAB-8/E Handbooks, User's Manuals, Maintenance Manuals, and Engineering Drawings Summary of Installation Functions AM8-ED and AM8-EC Analog Panel Pin Connections Analog Connection Using 7008533 Cable BC08J-X Connection and Bit Assignments Connections for DR8-EB Panel Assembly Real-Time Programmable Clock Connections VC8-E Cable Connections AD8-EA Accessory and Component List AM8-EA Accessory and Component List AM8-EC Accessory and Component List AM8-ED Accessory and Component List DK8-EF Accessory and Component List DK8-EF Accessory and Component List | 1-4 1-9 2-1 2-3 2-4 2-4 2-5 2-5 2-7 2-8 2-8 2-9 2-9     |

# **TABLES (Cont)**

| Table No. | Title                                                                 | Page |

|-----------|-----------------------------------------------------------------------|------|

| 2-18      | DR8-EC Accessory and Component List                                   | 2-11 |

| 2-19      | VC8-E Accessory and Component List                                    | 2-11 |

| 2-20      | VM03 Accessory and Component List                                     | 2-12 |

| 2-21      | Recommended LAB-8/E Module Installation Positions                     | 2-12 |

| 2-22      | High Quality Power Supply Parameters                                  | 2-14 |

| 2-23      | Switch Requirements for VC8-E Modules                                 | 2-16 |

| 2-24      | VM03 Tektronix 602 Modification Kit Parts List                        | 2-17 |

| 2-25      | LAB-8/E Acceptance Test Diagnostics                                   | 2-19 |

| 2-26      | A/D Converter and Analog Preamplifier and Multiplexer Acceptance Test | 2-20 |

| 2-27      | Switching Points and Theoretical Voltage Readings                     | 2-21 |

| 2-28      | Theoretical Voltage and Reading in the AC                             | 2-22 |

| 3-1       | Programmer's Console Control and Indicator Functions                  | 3-2  |

| 3-2       | Special Keyboard Functions                                            | 3-5  |

| 3-3       | RIM Loader Programs                                                   | 3-10 |

| 3-4       | VR14 Input Voltages                                                   | 3-13 |

| 3-5       | VR14 Controls                                                         | 3-14 |

| 3-6       | Unit Top Panel Control Settings                                       | 3-14 |

| 4-1       | Enable/Status Register                                                | 4-13 |

| 4-2       | C-Line Logic Levels                                                   | 4-20 |

| 4-3       | MUX Register Contents and Look-Ahead Bits                             | 4-23 |

| 4-4       | Applied Voltages and Octal Equivalents                                | 4-32 |

| 4-5       | Resistors for Changing Input Configuration                            | 4-40 |

| 4-6       | AM8-EA Configuration Change Parts List                                | 4-40 |

| 4-7       | Point-Plot Display Control Enable/Status Register                     | 4-46 |

| 4-8       | IOT Device Code                                                       | 4-59 |

| 4-9       | DK8-EP IOT Instructions                                               | 4-68 |

| 4-10      | Clock Enable Register Enable Signals                                  | 4-70 |

| 4-11      | Frequencies Selected by Rate Enable Bits 3-5                          | 4-70 |

| 4-12      | Control Signals for Clock External and Internal Transfers             | 4-78 |

| 4-13      | High Quality Power Supply Parameters and Specifications               | 4-87 |

| 4-14      | Side Connector for HQ Power Input and Output                          | 4-87 |

| 5-1       | Maintenance Equipment                                                 | 5-3  |

| 5-2       | Processor Preventive Maintenance Schedule                             |      |

|           | (3 months or 500 hours)                                               | 5-7  |

| 5-3       | Processor Troubleshooting                                             | 5-16 |

| 5-4       | Memory Data Errors — Possible Causes                                  | 5-19 |

| 5-5       | Memory Module Test Point Voltage Levels                               | 5-19 |

| 5-6       | Memory Circuit Variables                                              | 5-20 |

| 5-7       | H724 Power Supply Parameters                                          | 5-23 |

| 5-8       | Component Troubleshooting Aid for H724 Power Supply                   | 5-23 |

| 5-9       | POWER ON/OFF Switch Adjustment                                        | 5-24 |

| 5-10      | Teletype Maintenance Tools                                            | 5-25 |

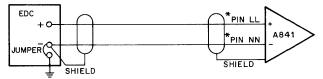

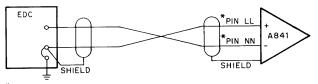

| 5-11      | EDC Connection to A841 Module                                         | 5-28 |

# **TABLES (Cont)**

| Table No. | Title                                                        | Page |

|-----------|--------------------------------------------------------------|------|

| 5-12      | EDC Voltage and AC Readings                                  | 5-28 |

| 5-13      | Major Calibration Voltages and AC Readings                   | 5-29 |

| 5-14      | AM8-EA Calibration Connections                               | 5-33 |

| 5-15      | Gain and Bias Potentiometers                                 | 5-34 |

| 5-16      | Connections of Teletype Cable                                | 5-37 |

| 5-17      | Teletype Cabling, Fusing, and Test Points                    | 5-37 |

| 6-1       | Analog-To-Digital Converter (AD8-EA) Recommended Spare Parts | 6-1  |

| 6-2       | Point-Plot Display Control (VC8-E) Spare Parts               | 6-2  |

| 6-3       | Analog Preamplifier and Multiplexer Expander (AM8-EA)        |      |

|           | Recommended Spare Parts                                      | 6-2  |

| 6-4       | Buffered Digital I/O (DR8-EA) Recommended Spare Parts        | 6-2  |

| 6-5       | Real-Time Programmable Clock (DK8-EP)                        |      |

|           | Recommended Spare Parts                                      | 6-3  |

|           |                                                              |      |

# CHAPTER 1 INTRODUCTION

#### 1.1 PURPOSE OF MANUAL

This manual provides the user with the installation procedures, theory of operation, and maintenance procedures necessary to install and operate the LAB-8/E System manufactured by Digital Equipment Corporation.

The theory of operation and maintenance procedures for the LAB-8/E processor are contained in the *PDP-8/E Maintenance Manual, Volume I.* When operating and performing maintenance on the LAB-8/E, the user should be familiar with Chapter 4 of the PDP-8/E manual. This manual deals with the options that have been added to the PDP-8/E to form the LAB-8/E System. Paragraph 1.4 contains a list of companion documents to this manual and other documentation for the LAB-8/E.

#### 1.2 SYSTEM FEATURES

The LAB-8/E System performs arithmetic calculations, controls machine operations, makes on-line measurements of both analog and digital information, displays data on an oscilloscope, and stores large quantities of data for future use and/or modification. The user may use control tapes provided by Digital, or write his own programs to shape the LAB-8/E to his own needs and to perform sophisticated handling of analog or digital data. The LAB-8/E is a truly sophisticated system allowing flexibility for the user in data acquisition and processing.

The LAB-8/E design enables the user to purchase the basic LAB-8/E and to add on options as requirements increase. The basic system comprises the following:

- a. A PDP-8/E general purpose 12-bit digital computer with a basic 4096-word memory and a 1.2- $\mu$ s cycle time.

- b. A 33 ASR Teletype<sup>®</sup>, 10-bit I/O device with a paper-tape reader and punch.

- c. A laboratory mounting panel with precision power supply for use with LAB-8/E peripherals.

- d. A 10-bit Analog-to-Digital Converter with sample and hold circuitry and optional preamplifier and multiplexer expander.

- e. A 10-bit Point-Plot Display Control for the graphical display of data on an oscilloscope.

- f. A Real-Time Clock with five programmable ranges from 1 μs per count to 10 ms per count, plus three Schmitt triggers.

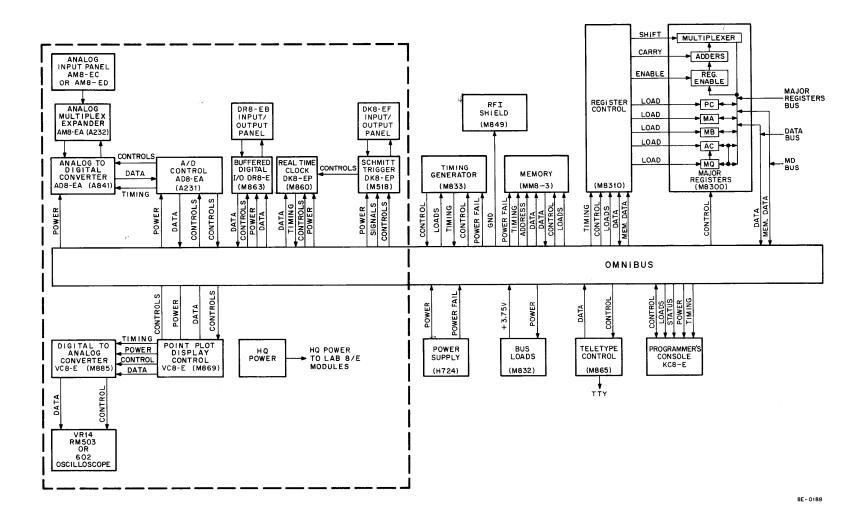

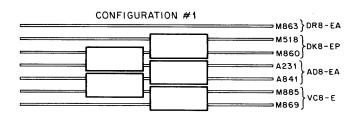

Expansion is easily accommodated through a two-way bus, called OMNIBUS (M), which all LAB-8/E modules plug into directly or indirectly. Figure 1-1 shows the basic PDP-8/E and the options added, shown inside the dotted lines, to form the basic LAB-8/E. One OMNIBUS contains 20 non-dedicated slots that can contain up to

<sup>®</sup>Teletype is a registered trademark of Teletype Corporation.

OMNIBUS is a trademark of Digital Equipment Corporation.

Figure 1-1 LAB-8/E Basic System

20 PDP-8/E or LAB-8/E options. The user can add one or more additional OMNIBUS modules to accommodate more options, if required.

Three categories of options are provided with the LAB-8/E: internal options, OMNIBUS options, and external options. Internal options are units, such as Extended Memory, and Extended Arithmetic Element, that extend the capability of the processor but do not control peripherals. OMNIBUS options include internal and external options that plug directly into the OMNIBUS. External options are units that indirectly plug into the OMNIBUS through an I/O Bus Adapter interface.

The specifications for the LAB-8/E Central Processor and options are shown in Table 1-1. The options are described in the following paragraphs.

#### 1.2.1 Analog-to-Digital Converter (AD8-EA)

The Analog-to-Digital (A/D) Converter consists of the A841 and A231 modules. The A841 module contains analog circuitry, including the A/D weighing switches, comparator, and sample and hold. The A231 module contains all the control logic for the A841 module. The AD8-EA receives a  $\pm 5$  Vdc signal and produces a 9-bit  $\pm 100$  signal word representing the input. The two modules are joined by an H851 Edge Connector.

#### 1.2.2 Analog Preamplifier and Multiplexer (AM8-EA)

The AM8-EA is a single A232 quad module containing eight analog preamplifiers and eight multiplexer channels that select the output of one preamplifier to be applied to the A/D converter. An additional module expands the multiplexer to 16 channels. Input to the AM8-EA is  $\pm 1V$  differential and the output is  $\pm 5V$  single-ended to the A841 module of the AD8-EA.

# 1.2.3 Point-Plot Display Control (VC8-E)

The VC8-E consists of the M885 and M869 modules. The M885 module receives 9 bits + sign of digital data and converts it to  $\pm 5$  Vdc voltage to be applied to the oscilloscope display. The M869 module contains all the control logic to control the Digital-to-Analog (D/A) converter.

#### 1.2.4 Buffered Digital I/O (DR8-EA)

The DR8-EA consists of one M863 module. It can provide 12 digital inputs and 12 digital outputs for the LAB-8/E and can be used to sense external events. The inputs and outputs are TTL compatible; ground (0V) represents logical true and high (+3V) represents logical false.

#### 1.2.5 Real-Time Programmable Clock (DK8-EP)

The DK8-EP consists of the M860 and M518 modules. The M518 module contains the input logic and Schmitt triggers. The M860 module contains the control logic, registers, and IOT decoding logic. The DK8-EP provides a programmable time base that allows the user to control and/or record internal and external events. It can be used to measure time between events, record number of events in a given time, or initiate repetitive operations at specified intervals of time.

#### NOTE

The following panels are single-width or double-width modules which are mounted in the H945 option cabinet, Nuclear Installation Module (NIM) Binary Loader (BIN), for connecting inputs and/or outputs to the LAB-8/E System.

## 1.2.6 Analog Input Panels (AM8-ED and AM8-EC)

The AM8-ED and AM8-EC panels are used to supply inputs to the analog multiplexer and are mounted in the H945 cabinet. The AM8-ED has two DB-25S 25-pin connectors with matching plugs. The AM8-EC has four inputs from potentiometer channels 0 through 3. As on the AM8-ED, channels  $4_8$  through  $17_8$  are supplied on the DB-25S.

# 1.2.7 Real-Time Programmable Clock Input Panel (DK8-EF)

The DK8-EF panel has inputs for the Schmitt triggers. It also provides connections for EXT CLOCK or EXT START signals.

# 1.2.8 Digital I/O Panel (DR8-EB)

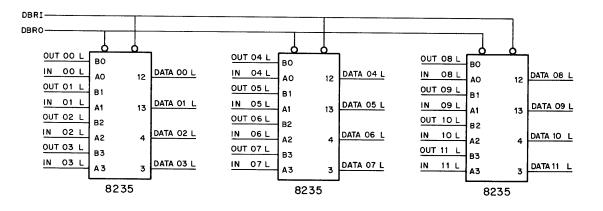

The DR8-EB provides a front panel assembly with two M904 modules, with connections for input and output to the DR8-EA Buffered Digital I/O.

Table 1-1

LAB-8/E System Specifications

| Equipment                             | Specifications                                                                                                                                                                                                                                                                               |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Central Processor                     |                                                                                                                                                                                                                                                                                              |

| Processor Speed                       | Two memory cycles:                                                                                                                                                                                                                                                                           |

|                                       | a. Fast cycle accomplishes a FETCH, Internal IOT, or DEFER (non-Auto Index) in 1.2 $\mu$ s.                                                                                                                                                                                                  |

|                                       | b. Slow cycle accomplishes (after FETCH) an instruction execution, or DEFER (Auto Index) in 1.4 $\mu$ s.                                                                                                                                                                                     |

| Instruction Execution Time (MRI only) | The instruction execution time, beginning with the instruction completely executed, requires one fast and one slow memory cycle, or 2.6 $\mu$ s.                                                                                                                                             |

| Word Length                           | 12 bits                                                                                                                                                                                                                                                                                      |

| Addressing                            | Direct memory addressing is controlled on front panel or<br>through the Data Break system. Programmed addressing is<br>accomplished as a function of software. 200 octal memory<br>locations may be directly accessed (except when on page 0)<br>by the program during any one memory cycle. |

| Program Loading                       | Programs may be loaded by Read-In-Mode (RIM) or Binary Loader (BIN). RIM is read into memory using toggle switches on front panel. BIN is a program used to load other programs.                                                                                                             |

| Input/Output Capability               | Three types of input/output transfers (IOTs) are provided:                                                                                                                                                                                                                                   |

|                                       | a. Programmed input/output or transfers                                                                                                                                                                                                                                                      |

|                                       | b. Programmed Interrupts                                                                                                                                                                                                                                                                     |

|                                       | c. Data Break                                                                                                                                                                                                                                                                                |

|                                       | Data Break is a method used to read out of, or write into, a block of memory during normal processing.                                                                                                                                                                                       |

(continued on next page)