DEC-8E-HR2B-D-DK8-EP

# PROGRAMMABLE REAL-TIME CLOCK OPTION

The information in this preliminary manual will become, in its final form, a part of the PDP-8/E Maintenance Manual, Volume 2.

**PRELIMINARY**

Copyright © 1971 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

**COMPUTER LAB**

### CONTENTS

| Section                                                            |                                                                                                                                                                                                                                                                                         | Page                                            |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|

| 1.0                                                                | Introduction                                                                                                                                                                                                                                                                            | 1                                               |  |

| 2.0                                                                | Block Diagram                                                                                                                                                                                                                                                                           | 2                                               |  |

| 3.0                                                                | Detailed Logic                                                                                                                                                                                                                                                                          | 6                                               |  |

| 3.1                                                                | IOT Decoder Logic                                                                                                                                                                                                                                                                       | 6                                               |  |

| 3.2                                                                | Clock Enable Register Logic                                                                                                                                                                                                                                                             | 8                                               |  |

| 3.3                                                                | Clock Rate Select Logic                                                                                                                                                                                                                                                                 |                                                 |  |

| 3.4                                                                | Load Buffer Register Logic                                                                                                                                                                                                                                                              |                                                 |  |

| 3.5                                                                | Clock Buffer/Clock Counter Logic                                                                                                                                                                                                                                                        |                                                 |  |

| 3.6                                                                | Overflow Flip-Flop Logic                                                                                                                                                                                                                                                                |                                                 |  |

| 3.7                                                                | Int/Skip Logic                                                                                                                                                                                                                                                                          |                                                 |  |

| 3.8                                                                | Input/Overflow Status Logic                                                                                                                                                                                                                                                             | 24                                              |  |

| 3.9                                                                | Schmitt Trigger Logic                                                                                                                                                                                                                                                                   | 26                                              |  |

| 4.0                                                                | Maintenance                                                                                                                                                                                                                                                                             | 28                                              |  |

| 5.0                                                                | Spare Parts                                                                                                                                                                                                                                                                             | 28                                              |  |

|                                                                    | ILLUSTRATIONS                                                                                                                                                                                                                                                                           |                                                 |  |

|                                                                    |                                                                                                                                                                                                                                                                                         |                                                 |  |

| Figure N                                                           | o. Title                                                                                                                                                                                                                                                                                | Page                                            |  |

| Figure N                                                           | o. Title  DK8-EP Block Diagram                                                                                                                                                                                                                                                          | Page                                            |  |

|                                                                    |                                                                                                                                                                                                                                                                                         | _                                               |  |

| 2-1                                                                | DK8-EP Block Diagram                                                                                                                                                                                                                                                                    | 3                                               |  |

| 2-1<br>3-1                                                         | DK8-EP Block Diagram IOT Decoder Logic                                                                                                                                                                                                                                                  | 3 7                                             |  |

| 2-1<br>3-1<br>3-2                                                  | DK8-EP Block Diagram  IOT Decoder Logic  Clock Enable Register Logic                                                                                                                                                                                                                    | 3<br>7<br>9                                     |  |

| 2-1<br>3-1<br>3-2<br>3-3                                           | DK8-EP Block Diagram  IOT Decoder Logic  Clock Enable Register Logic  Clock Rate Select Logic                                                                                                                                                                                           | 3<br>7<br>9<br>10                               |  |

| 2-1<br>3-1<br>3-2<br>3-3<br>3-4                                    | DK8-EP Block Diagram  IOT Decoder Logic  Clock Enable Register Logic  Clock Rate Select Logic  Load Buffer Register Logic                                                                                                                                                               | 3<br>7<br>9<br>10<br>12                         |  |

| 2-1<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5                             | DK8-EP Block Diagram  IOT Decoder Logic  Clock Enable Register Logic  Clock Rate Select Logic  Load Buffer Register Logic  Load Buffer Register Timing                                                                                                                                  | 3<br>7<br>9<br>10<br>12<br>14                   |  |

| 2-1<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6                      | DK8-EP Block Diagram  IOT Decoder Logic  Clock Enable Register Logic  Clock Rate Select Logic  Load Buffer Register Logic  Load Buffer Register Timing  Not Last Transfer Logic                                                                                                         | 3<br>7<br>9<br>10<br>12<br>14                   |  |

| 2-1<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7               | DK8-EP Block Diagram  IOT Decoder Logic  Clock Enable Register Logic  Clock Rate Select Logic  Load Buffer Register Logic  Load Buffer Register Timing  Not Last Transfer Logic  Clock Buffer/Clock Counter Logic                                                                       | 3<br>7<br>9<br>10<br>12<br>14<br>16             |  |

| 2-1<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8        | DK8-EP Block Diagram  IOT Decoder Logic  Clock Enable Register Logic  Clock Rate Select Logic  Load Buffer Register Logic  Load Buffer Register Timing  Not Last Transfer Logic  Clock Buffer/Clock Counter Logic  Clock Buffer/Clock Counter Control Signals                           | 3<br>7<br>9<br>10<br>12<br>14<br>16<br>17       |  |

| 2-1<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9 | DK8-EP Block Diagram  IOT Decoder Logic  Clock Enable Register Logic  Clock Rate Select Logic  Load Buffer Register Logic  Load Buffer Register Timing  Not Last Transfer Logic  Clock Buffer/Clock Counter Logic  Clock Buffer/Clock Counter Control Signals  Overflow Flip-Flop Logic | 3<br>7<br>9<br>10<br>12<br>14<br>16<br>17<br>19 |  |

# TABLES

| Table No. | Title                                                     | Page |

|-----------|-----------------------------------------------------------|------|

| 2-1       | DK8-EP IOT Instructions                                   | 4    |

| 2-2       | Clock Enable Register Enable Signals                      | 5    |

| 3-1       | Frequencies Selected By Rate Enable Bits 3, 4, and 5      | 11   |

| 3-2       | Control Signals for Clock External and Internal Transfers | 18   |

| 4-1       | M518 Module J1 Connector Pin Letters and Assignments      | 28   |

#### 1.0 INTRODUCTION

The Programmable Real Time Clock, DK8-EP, consists of two PDP-8/E quad modules that plug into the OMNIBUS and are interconnected by an H851 edge connector. The M860 module, Real Time Clock Control, contains a 12-bit binary counter, a 12-bit buffer register, and logic that controls not only the counter/register operation but also the companion quad module operation. This second quad module is the M518, Input Logic and Schmitt Triggers. Included on this module is a 12-bit storage register, logic that derives five different clock frequencies from a crystal-controlled oscillator, and three Schmitt trigger circuits that enable the user to control certain clock operations from external sources.

The DK8-EP provides a programmable time base that allows the user to control and/or record the occurrence of events both internal and external to the PDP-8/E. For example: the Clock can be used to count the number of events in a given amount of time; it can be used to measure the amount of time between two given events; or, it can be used to initiate repetitive operations at specified intervals of time.

To perform these and similar operations, the major logic components listed must interact. The fundamental component is the 12-bit storage register, called the Clock Enable Register. This register can be loaded, bit by bit, under program control. Different bits are used to control different functional sections of the DK8-EP. For example, bit 7 of the register enables internally generated clock pulses to be applied to the 12-bit binary counter, called the Clock Counter Register; bit 9, by enabling one of the Schmitt trigger circuits, allows an external source to control some aspect of Clock operation. The Clock Enable Register can be set or cleared under program control and its contents can be transferred to the CPU AC Register at any time by a program instruction.

The Clock Counter Register counts clock pulses in a way that is predetermined by the state of Clock Enable Register bits 1 and 2. For example, the Clock Counter Register can count from 0 to 4096 repetitively, generating a signal (OVERFLOW L) each time it overflows to 0. In other circumstances the programmer might wish the OVERFLOW L signal to be generated each 2000 clock pulses. The

Clock Counter Register can be preset, to a count of 2096 in this example, so as to produce the desired result. The contents of the Clock Counter Register can be transferred to the AC Register at any time by a program instruction. However, to accomplish this transfer the logic makes use of a 12-bit Clock Buffer Register.

This Clock Buffer Register is essential to the DK8-EP operation. Data is transferred between the AC Register and the Clock Counter Register via the Clock Buffer Register. To preset the Clock Counter Register, as in the example outlined, the program causes the Clock Buffer Register to be loaded from the AC Register with the preset count. Bits 1 and 2 of the Clock Enable Register can then be set so that the preset count, 2096, is loaded into the Clock Counter Register each time the OVERFLOW L signal is generated. Thus, the Clock Counter Register counts repetitively from 2096 to 4096, as is desired. The Clock Buffer Register can be controlled not only by the program but also, to a certain extent, by an external source. For example, Clock Enable Register bits 9, 10, and 11 allow an external source to cause the Clock Buffer Register to be loaded. However, transfers between the AC and Buffer Registers are limited to program control.

#### 2.0 BLOCK DIAGRAM

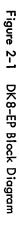

The functional block diagram, shown in Figure 2-1, illustrates the relationship between the registers and the remainder of the Clock logic. Each functional block shown in Figure 2-1 is discussed in detail in a separate section and the applicable logic can be found in the indicated figures.

The IOT Decoder logic provides signals in response to the eight IOT instructions listed in Table 2-1. These IOT signals are distributed to the various functional sections as shown in Figure 2-1. The enabling signals from the Clock Enable Register are also shown on the block diagram. These enabling signals are listed and explained in detail in Table 2-2.

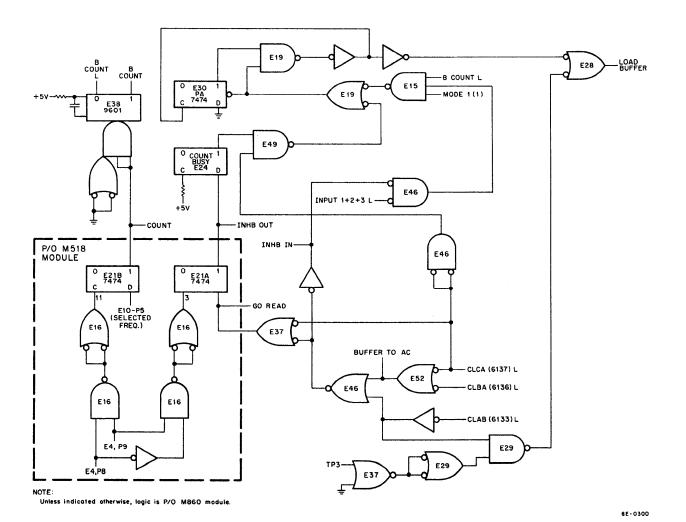

For operation not involving external sources, the signal flow description can begin with the Clock Rate Select logic. The desired frequency of clock pulses is selected by the Rate Enable bits, while the Count Enable bit gates the clock pulses to the Load Buffer Register logic. This logic converts the clock pulses to B COUNT pulses that are counted by the Clock Counter Register. The logic also generates the LOAD BUFFER signal in response to program instructions and ensures that the B COUNT and LOAD BUFFER signals do not occur at the same moment (the significance of this is detailed in Section 3.4).

The LOAD BUFFER signal causes the Clock Buffer Register to be loaded with either data from the AC Register, via the DATA 0-11 lines, or data from the Clock Counter Register. The B COUNT pulses

# Table 2-1 DK8-EP IOT Instructions

| Octal Code | Mnemonic      |                            | Function                                                                                                              |

|------------|---------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 6130       | CLZE          | Each bit in the Cloc       | Register per AC Register.<br>k Enable Register is cleared if<br>t in the AC Register is set. The<br>anged.            |

| 6131       | CLSK          | the following interru      | errupt.  Attraction is skipped if either of apt conditions exists (the Clock by connected to the computer in-         |

|            |               | a. An enabled Sc           | hmitt trigger has fired.                                                                                              |

|            |               | b. The Clock Cou           | unter Register has overflowed.                                                                                        |

| 6132       | CL <b>D</b> E | Each bit in the Clock      | gister per AC Register.<br>k Enable Register is set if the<br>the AC Register is set. The AC<br>d.                    |

| 6133       | CLAB          | the Clock and loaded       | k Buffer Register.<br>AC Register are transferred to<br>d into both the Clock Buffer<br>er Registers. The AC Register |

| 6134       | CLEN          | ferred to the compute      | er to AC Register.<br>Clock Enable Register are trans-<br>er and JAMed into the AC<br>Enable Register is unchanged.   |

| 6135       | CLSA          | Schmitt input circuit      | rflow flip-flop and of the three<br>s is transferred to the computer<br>AC Register. Only the follow-                 |

|            |               | AC Bit                     | Status Condition                                                                                                      |

|            |               | 0<br>9<br>10<br>1 <b>1</b> | Overflow flip-flop Schmitt input 3 Schmitt input 2 Schmitt input 1                                                    |

| 6136       | CLBA          | ferred to the compute      | to AC Register.<br>Clock Buffer Register are transer<br>or and JAMed into the AC<br>Buffer Register is unchanged.     |

| 6137       | CLCA          | ferred, via the Clock      | Clock Counter Register are trans-<br>k Buffer Register, to the computer<br>AC Register. The Clock Counter             |

## Table 2–2 Clock Enable Register Enable Signals

| Register Bit | Enable Signal Name                              | Function                                                                                                                                                                                                                           |

|--------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | Clock Enable 0                                  | Enables a status check of the Overflow flip-flop (CLSA), an instruction skip on an overflow condition (CLSK), and a possible interrupt request on an overflow condition.                                                           |

| 1<br>2       | Mode Enable 1<br>Mode Enable 2                  | Determine the Clock Counter Register mode of count-<br>ing. The four possible modes are:                                                                                                                                           |

|              |                                                 | OO Register counts at the selected rate with over-<br>flow occurring every 4096 counts.                                                                                                                                            |

|              |                                                 | Ol Register counts at the selected rate. At each overflow a preset count is loaded into the Register from the Clock Buffer Register. Thus, overflow occurs every (4096 minus preset count) counts.                                 |

|              |                                                 | 10 Register counts at the selected rate. An external event can sample the register at any time, causing the sample count to be transferred to the Clock Buffer Register. The Clock Counter Register continues counting.            |

|              |                                                 | 11 Register counts at the selected rate. An external event can sample the register at any time. The sample count is transferred to the Clock Buffer Register and the Clock Counter Register is cleared before it resumes counting. |

| 3<br>4<br>5  | Rate Enable 3<br>Rate Enable 4<br>Rate Enable 5 | Selects the frequency of the internally-generated clock pulses. See Table 3-1, Section 3.3.                                                                                                                                        |

| 6            | Clock Enable 6                                  | Enables each Clock Counter Register overflow to generate the EXT PULSE L pulse that can be used by other OMNIBUS-connected devices.                                                                                                |

| 7            | Count Enable 7                                  | Enables clock pulses to be applied to the Clock Counter                                                                                                                                                                            |

| <del>8</del> | Clock Enable 8                                  | Connects the Clock interrupt logic to the computer interrupt system, enabling the Clock interrupt conditions to assert the OMNIBUS INT RQST L signal.                                                                              |

| 9            | Event Enable 9                                  | Enable Schmitt trigger firings to turn on the clock, to                                                                                                                                                                            |

| 10<br>11     | Event Enable 10<br>Event Enable 11              | cause a program interrupt, to sample the Clock<br>Counter Register.                                                                                                                                                                |

are counted by the Clock Counter Register in a way that is determined by signals from the Buffer/Counter Control Signal logic. These signals are asserted by combinations of IOT signals and Mode Enable bits 1 and 2.

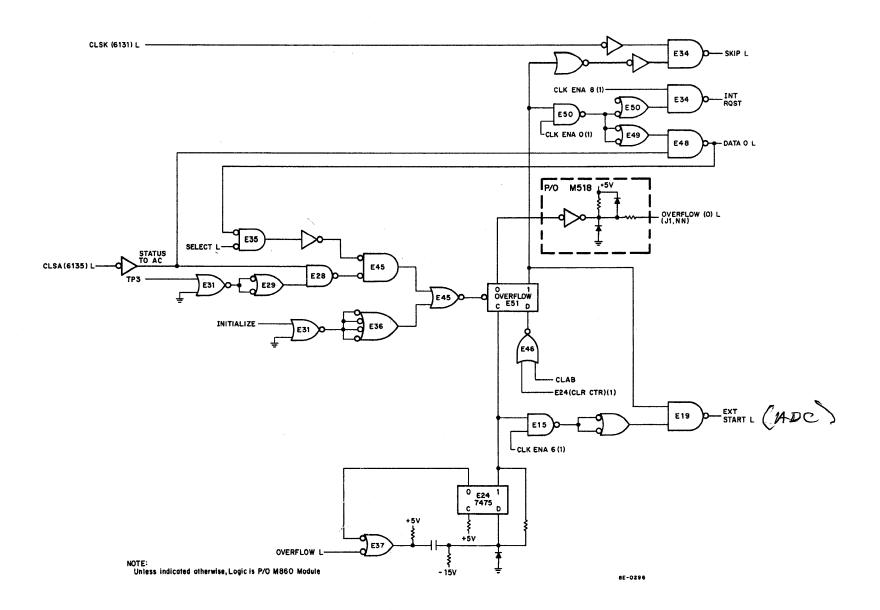

The OVERFLOW L signal that is generated by the Clock Counter Register is applied to the Overflow Flip-flop logic. This logic asserts two signals that can be used by devices, Analog-to-Digital converters, for instance, to initiate some operation. OVERFLOW (0) L is suitable for external devices, while EXT PULSE L is designed to be used by OMNIBUS devices. The status of the Overflow flip-flop itself, can be checked under program control and transferred to bit 0 of the AC Register via the DATA 0 line.

The logic also provides the OVERFLOW (1) signal that is applied to the Int/Skip logic. Thus, each time the Clock Counter Register overflows internal and external devices can begin some operation, or the DK8-EP can request a program interrupt, or a program instruction can be skipped, or any combination of these events can occur, depending on the state of Clock Enable bits 0, 6, and 8.

Except for transfers between the Clock Buffer Register and the AC Register, the Clock operates in much the same manner when operation is initiated by external sources. Signals applied to the external input channels can activate one or more of the Schmitt triggers. The resulting signal, SCHMITT IN 1 L (or 2, or 3) is applied to the Input/Overflow Status logic. Here the status of each input channel can be checked under program control and forwarded to the AC Register (Event Enable bit 9 enables the status of Schmitt trigger input 1 to be transferred to AC 9 via DATA 9).

The Input/Overflow Status logic allows the external event to generate the appropriate INT RQST (1, 2, or 3) L signal. This signal is applied to the Int/Skip logic and can cause a program interrupt. The INPUT 1+2+3 L signal is also asserted by the Input/Overflow Status logic and causes the Clock Rate Select logic to produce clock pulses. The Load Buffer Register logic and the Buffer/Counter logic then operate as already outlined.

#### 3.0 DETAILED LOGIC

#### 3.1 IOT Decoder Logic

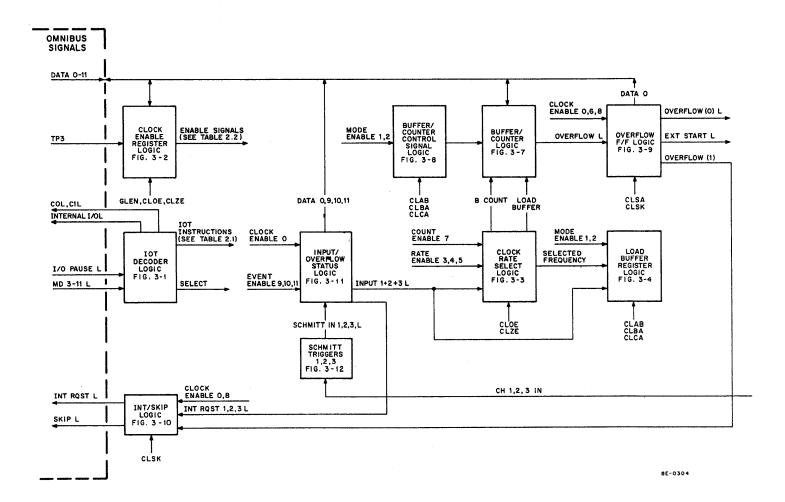

The IOT Decoder logic is shown in Figure 3-1. The SELECT signal is asserted by NAND gate E23 when a 613X instruction is decoded. The SELECT signal, in turn, asserts the B SELECT L signal, the INTERNAL I/O L signal, which causes the Positive I/O Bus Interface to ignore the IOT Instruction, and the SELECT L signal, which is used to gate MD bits 9, 10, and 11 to the BCD-Decimal decoder. The decoder, a DEC 8251 IC (see Volume 1, Appendix A for details), provides instructions 6130 through 6137, as illustrated in Figure 3-1.

0. 0000

Note that instructions 6134 through 6137 cause the OMNIBUS CO L and C1 L signals to be asserted. Each of these instructions call for a transfer of data to the CPU AC Register. With C0 L and C1 L both asserted the data is JAM-transferred into the AC Register, rather than being ORed with data already in the register.

#### 3.2 Clock Enable Register Logic

The Clock Enable Register logic is shown in Figure 3-2. The register, itself, consists of 12 DEC 7474 flip-flops, only two of which are shown in the logic. Each flip-flop is given a descriptive title that characterizes the function of the flip-flop. For example: the Mode Enable 1 flip-flop is used to select, along with Mode Enable 2, the particular mode of operation of the Clock Counter Register, the Count Enable 7 flip-flop enables the Frequency Multiplexer to produce clock pulses at the selected frequency; the Event Enable 9 flip-flop enables an external event to control Clock operations (see Table 2-2 for a complete listing of the Enable signals and their functions).

Three program instructions deal exclusively with the Clock Enable Register. The CLEN (6134) instruction gates the register contents onto the DATA 0-11 lines. The information on the DATA lines is gated through the CPU Major Register gating and loaded into the AC Register. The CLZE (6130) and CLOE (6132) instructions clear and set, respectively, those Clock Enable Register flip-flops that correspond to set AC Register bits. For example, if the 0-bit of the AC Register is logic 1, the Clock Enable 0 flip-flop can be set by the CLOE instruction or cleared by the CLZE instruction.

The Clock Enable Register, as a whole, can be cleared by the CLEAR signal. This signal is generated by the INITIALIZE signal that is produced when power is turned on, when the CLEAR key is depressed, or when the CAF instruction is issued.

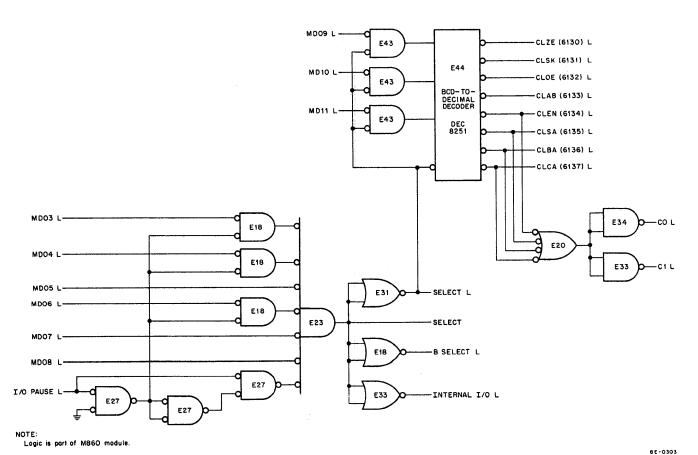

#### 3.3 Clock Rate Select Logic

The Clock Rate Select logic is shown in Figure 3-3. The basic clock frequency, 20 MHz, is provided by a crystal-controlled oscillator (see the logic drawing, E-CS-M518). This frequency is divided by the J-K flip-flop, E33 (when both the J and the K inputs are high, the 1-output is changed with each positive transition at the C input). The 10 MHz clock frequency is applied to a chain of DEC 7490 decade counters, each counter being wired to divide by ten. The output of each counter, which can be monitored at a test point, is applied to the Frequency multiplexer, E10, a DEC 74151 IC. An external pulse source of any frequency can also be applied to the multiplexer, via pin RR on J1 of the M518 module. The desired frequency of clock pulses is obtained by selectively setting or clearing Rate Enable flip-flops 3, 4, and 5 with the CLOE or CLZE IOT instructions. Table 3-1 shows the relationship between the 1-outputs of these flip-flops and the multiplexer output frequency.

DATA O L

NOTE:

Unless indicated otherwise, logic is P/O M518 module.

8E-0302

DATA 1 L -----

Table 3-1

Frequencies Selected By Rate Enable Bits 3, 4, And 5

| Contents of Bits 3, 4, and 5 | Selected Multiplexer Output |

|------------------------------|-----------------------------|

| 000                          | No output                   |

| 001                          | External frequency          |

| 010                          | 100 Hz                      |

| 011                          | 1 kHz                       |

| 100                          | 10 kHz                      |

| 101                          | 100 kHz                     |

| 110                          | 1 MHz                       |

| 111                          | No output                   |

Note that Count Enable 7 must be cleared if output pulses are to be obtained from the multiplexer. This particular Clock Enable Register flip-flop is illustrated because it differs from the remaining Register flip-flops in an important way. Bit 7 can be cleared by an external event as well as by program instructions. Any of the three Schmitt trigger input circuits can cause the INPUT 1+2+3 L signal to be asserted, thereby clearing the Count Enable 7 flip-flop and, thus, turning on the clock.

#### 3.4 Load Buffer Register Logic

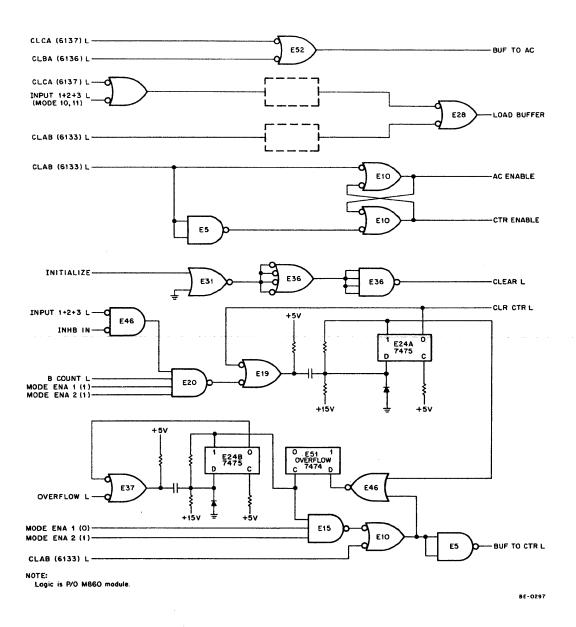

The Load Buffer Register logic is shown in Figure 3-4. The logic generates the LOAD BUFFER signal that loads the Clock Buffer Register and the B COUNT pulses that are counted by the Clock Counter Register. The LOAD BUFFER signal can be asserted in response to either the 6133 IOT instruction or the 6137 IOT instruction. Also, the signal can be asserted in response to an external event.

If the 6133 instruction is decoded, NAND gate E29 is enabled at TP3 time and, in turn, enables NOR gate E28 that asserts the LOAD BUFFER signal. If an external events generates the INPUT 1+2+3 L signal, E28 again asserts the LOAD BUFFER signal. However, the enabling path, for two reasons, is more complex than is that of the 6133 instruction. First, the external event is allowed to generate the LOAD BUFFER signal only when Mode 10 or Mode 11 has been selected by Mode Enable bits 1 and 2 (NAND gate E15 can be enabled in either case). Second, an external event must not be allowed to assert the LOAD BUFFER signal when an IOT instruction is being carried out (NAND gate E46 is inhibited by the INHB IN signal during an IOT instruction). To illustrate the need for this prohibition, consider the 6136 and 6137 instructions. If the 6136 instruction is issued, the BUF TO AC signal is asserted. This signal gates the Clock Buffer Register output to the DATA lines. If the INHB IN signal

were not asserted, an external event could generate the LOAD BUFFER signal during the IOT. Thus, the result would be identical to that achieved by a 6137 instruction.

The majority of the logic is devoted to making the 6137 instruction work. While the 6133 instruction loads the Clock Buffer Register with data from the CPU AC Register, the 6137 instruction loads the Clock Buffer with the contents of the Clock Counter Register. Precautions have been taken to insure that, if the 6137 instruction is issued, the LOAD BUFFER signal is not asserted at the moment that the Clock Counter is changing its count. Thus, false counts that would result from reading the Clock Counter as one or more bits are in transition are prevented from occurring.

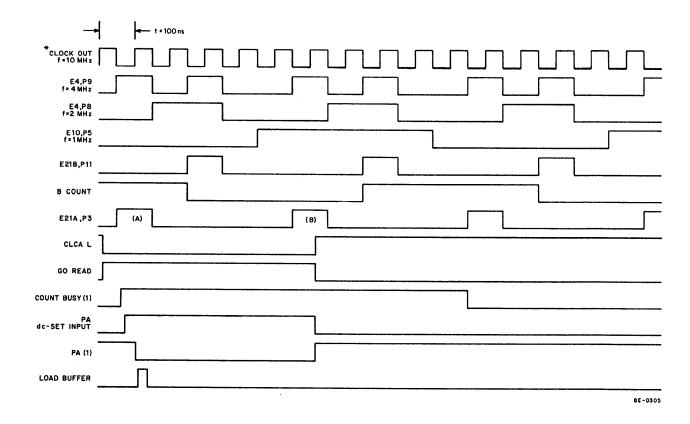

The precautionary logic includes flip-flop E21A and latch E24 in Figure 3-4. These two components and related gates generate signals that are illustrated in the timing diagram of Figure 3-5. Also shown in the timing diagram are signals generated by flip-flop E21B and one-shot E38. Both figures are referred to during the following discussion.

Flip-flops E21A and E21B are clocked by signals derived from the first decade counter in the Clock Rate select logic (see Figure 3-3). The D-input of E21B is controlled by the selected frequency output of the Frequency Multiplexer. In the timing diagram this frequency is chosen as 1 MHz. When E21B is set, its 1-output triggers one-shot E38; E38 produces the B COUNT signal for approximately 300 ns. The Clock Counter Register then counts the B COUNT pulses, which occur at the selected frequency.

When the 6137 instruction is issued, the CLCA L signal produced by the IOT Decoder logic (Section 3.1) asserts the GO READ signal. Because the clock is free-running, the GO READ signal can occur at any time with respect to the signal at the C-input of E21A. If it occurs at the instant shown in the timing diagram (just before the pulse marked (A)), E21A is set 200 ns before the B COUNT signal is negated (because each bit of the Clock Counter Register consists of a master-slave flip-flop, the Register bits are in transition on the trailing edge of the B COUNT pulse). Thus, the LOAD BUFFER signal causes the Clock Counter to be loaded into the Clock Buffer approximately 100 ns before the Clock Counter can change in response to the next B COUNT pulse (a delay of approximately 100 ns is introduced by the gating between E21A and NOR gate E28). If the GO READ signal is asserted just after the leading edge of pulse (A), E21A is set by pulse (B), 300 ns after the B COUNT signal is negated. Thus, the Clock Buffer is loaded approximately 200 ns after the Clock Counter changes in response to the B COUNT pulse, enough time for the data to settle in the Clock Counter.

The amount of time between pulse (A) and pulse (B) is always 500 ns. Therefore, the GO READ signal must be asserted for a longer amount of time to insure that either (A) or (B) can set flip-flop E21A. This requirement is not met by normal CPU timing. In addition, under normal CPU timing it would be possible to lose the data that is being transferred from the Clock Counter Register. This could happen

Figure 3-5

Load Buffer Register Timing

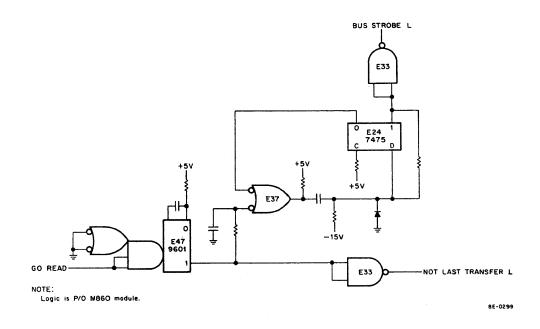

if the CLCA L signal were asserted just after the (A) pulse, for example. Under normal CPU timing for an internal IOT instruction (6137 is such an instruction), the AC LOAD L signal is asserted at TP3 time. In the present example, TP3 could occur before the count has been placed on the CPU Major Register Bus. Thus, the count would be lost. Both these difficulties can be overcome by increasing the period of time during which the CLCA L signal is asserted. The logic shown in Figure 3-6 is designed to increase the available time to approximately 650 ns.

When GO READ is asserted, one-shot E47 is triggered and remains set for approximately 650 ns. The OMNIBUS NOT LAST TRANSFER L signal is asserted for the same amount of time. Because NOT LAST TRANSFER L is low when TP3 of the IOT instruction (6137 in the present example) occurs, the CPU timing is interrupted and stalled in TS3. Until normal timing is resumed, the OMNIBUS I/O PAUSE L signal remains low (see Section 3.1, IOT Decoder logic), keeping CLCA L low and, thus, GO READ high. When one-shot E47 times out, NOT LAST TRANSFER L is negated. Perhaps 40 ns later, time enough for the NOT LAST TRANSFER line to settle, latch E24 causes the OMNIBUS BUS STROBE L signal to be asserted. This signal causes normal CPU timing to begin from the point of interruption. I/O PAUSE L is negated, in turn negating the CLCA L signal and, finally, the GO READ signal.

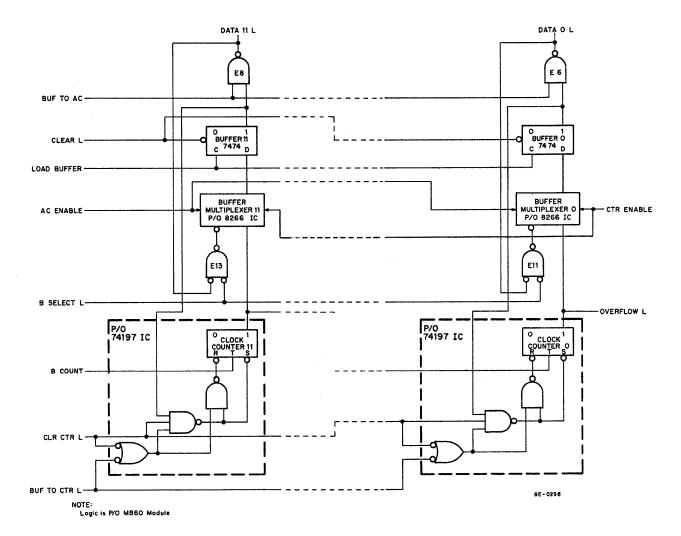

#### 3.5 Clock Buffer/Clock Counter Logic

The Clock Buffer/Clock Counter logic is shown in Figure 3-7. The logic for bits 1-10 is identical to that for bit 11. The Clock Buffer Register is a storage register composed of DEC7474 IC flip-flops. The Clock Counter Register is a presettable binary counter composed of DEC 74197 ICs (see Appendix A for a detailed description). Each bit can be preset at the S input and cleared at the R input. The B COUNT pulses are applied to the bit 11 toggle (T) input; the negative transition of each B COUNT pulse causes the 1-output to change. The 1-output of each bit is connected to both the following bit's T input and the Buffer Multiplexer, a DEC 8266 IC.

The logic enables the exchange of data between the Clock Buffer Register and the Clock Counter Register, and between these two registers and the CPU AC Register. Data transfers between the Clock Buffer and the Clock Counter can be controlled by external events. However, transfers between these two registers and the AC can be accomplished only under program control. The first type of transfer, between Clock Buffer and Clock Counter, can be considered an 'internal' transfer (internal to the clock), while the second can be considered as 'external'. Three different transfers can be grouped under each type, as shown in Column 1 of Table 3-2. Column 2 of this table shows both the source register and the destination register of each transfer, and Column 3 shows the control signals that must be asserted for each transfer. For example, if the DK8-EP is operating in Mode 10, an external event can cause a transfer from the Clock Counter to the Clock Buffer by asserting the CTR ENABLE and the LOAD BUFFER signals. The output of the Clock Counter Register is applied to the Buffer Multiplexer.

Figure 3-6 Not Last Transfer Logic

Figure 3-7 Clock Buffer/Clock Counter Logic

Table 3-2

Control Signals for Clock External and Internal Transfers

| Transfer Type | From/To                    | Control Signal Asserted               |

|---------------|----------------------------|---------------------------------------|

| Internal      |                            |                                       |

| Mode 01       | Clock Buffer/Clock Counter | BUF TO CTR L, CTR ENABLE              |

| Mode 10       | Clock Counter/Clock Buffer | CTR ENABLE, LOAD BUFFER               |

| Mode 11       | Clock Counter/Clock Buffer | CTR ENABLE, LOAD BUFFER,<br>CLR CTR L |

| External      |                            |                                       |

| CLAB          | AC Register/Clock Counter  | AC ENABLE, LOAD BUFFER, BUF TO CTR L  |

| CLBA          | Clock Buffer/AC Register   | BUF TO AC, CTR ENABLE                 |

| CLCA          | Clock Counter/AC Register  | CTR ENABLE, LOAD BUFFER, BUF TO AC    |

Because CTR ENABLE is asserted (this signal is asserted for all transfers except CLAB), the Clock Counter data is gated through the Multiplexer to the Clock Buffer, which is then loaded by the LOAD BUFFER signal. Note that Mode 11 transfers are similar, but that the CLR CTR L signal clears the Clock Counter after data is transferred to the Clock Buffer.

The data placed in the Clock Buffer by either of these internal transfers can be passed on to the AC only by an external type of transfer. The CLBA instruction asserts the BUF TO AC signal that gates the Clock Buffer output onto the OMNIBUS DATA lines. The information on the DATA lines is then gated to the AC Register and loaded at BUS STROBE L time.

Data can be transferred from the AC to the Clock Counter by the CLAB instruction. In this case, information in the AC Register is placed on the DATA lines and gated to the Buffer Multiplexer (B SELECT L is asserted by the IOT Decoder logic, see Section 3.1). The AC ENABLE signal is asserted, gating the data to the Clock Buffer. The LOAD BUFFER signal loads the register and the BUF TO CTR L signal gates the Clock Buffer output to the S input of the Clock Counter.

The control signals are asserted by the logic illustrated in Figure 3-8. Two signals, BUF TO AC and AC ENABLE, are used only during external transfers and, thus, are asserted only by program instructions (note that the AC ENABLE and CTR ENABLE signals are mutually exclusive). However, because the Clock Buffer is loaded during both external and internal transfers, external events as well as program instructions can generate the LOAD BUFFER signal. Likewise, the BUF TO CTR L signal is used for both internal and external transfers (the Mode 01 transfer can be accomplished only when the MSB of the Clock Counter Register asserts the OVERFLOW L signal).

Figure 3-8 Clock Buffer/Clock Counter Control Signals

On the other hand, the CLR CTR L signal is asserted only when a Mode 11 transfer is initiated by an external event. Bistable latch E24A asserts the CLR CTR L signal. Note that the 1-output of the latch is applied to the Overflow flip-flop, E51, via NOR gate E46. The MSB of the Clock Counter might go from a high to a low when CLR CTR L is asserted. Such a transition asserts the OVERFLOW L signal, thereby enabling NOR gate E37. The 1-output of latch E24B goes high. Were E46 not enabled, the Overflow flip-flop would be set unintentionally. The same problem could arise when the CLAB instruction is issued; thus, NOR gate E10 is also applied to E46.

Although the CLR CTR L signal can be asserted only by an external event, the Clock Counter can be cleared under program control. The Clock Buffer must first be cleared. This can be done either by issuing a CAF (Clear All Flags) instruction or by depressing the Clear key on the computer Programmer's Console. The INITIALIZE signal is asserted by either method (and by power turn-on as well). The CLEAR L signal then clears the Clock Buffer Register and the contents of the Clock Buffer can be transferred to the Clock Counter.

#### 3.6 Overflow Flip-Flop Logic

The Overflow flip-flop logic is shown in Figure 3-9. The logic monitors the MSB of the Clock Counter Register via the OVERFLOW L signal. When the register asserts the OVERFLOW L signal the Overflow flip-flop, E51, is normally set (NOR gate E46 prevents the flip-flop from being set unintentionally; see Section 3.5, Clock Buffer/Clock Counter logic). The set state of the flip-flop enables the logic to assert various signals selectively. The selectivity depends on both the state of certain Clock Enable Register flip-flops and the particular program instruction, if any, that is issued.

First, consider the OVERFLOW (0) L signal and the EXT PULSE L signal. These signals have similar purposes – to initiate some operation, such as analog-to-digital conversion, when overflow of the Clock Counter Register occurs. When OVERFLOW L is asserted latch E24 enables NAND gate E5, provided that the Clock Enable 6 flip-flop was set by some previous CLOE instruction (see Section 3.2, Clock Enable Register logic), and sets the Overflow flip-flop, E51. The 1-output of E51 enables NAND gate E19 thereby asserting the EXT PULSE L signal. E24 remains latched for approximately 500 ns (the duration of the latch is determined by the RC time constant of the D input; see Appendix A for details). Thus, the EXT PULSE L signal is a pulse that can be generated each time an overflow occurs. The EXT PULSE L pulse is designed to be used with an analog-to-digital converter that plugs into the OMNIBUS (the signal can be taken from the M860 module, conveniently, only via an H851 Top Block connector). In such an application, the EXT PULSE L pulse sets the rate at which an analog signal is sampled by the analog-to-digital converter. The 0-output of E51 is buffered before it asserts the OVERFLOW (0) L signal. This signal, once asserted, remains so until E51 is cleared under

2]

program control. The OVERFLOW (0) L signal is made available at a 40-pin connector on the M518 module. Thus, it can be used by both external and internal devices in a variety of applications.

No matter what the application, the OVERFLOW (0) L signal is useful, generally, only when it can be continuously asserted. Therefore, flip-flop E51 must be repeatedly cleared. The flip-flop can be cleared not only by the INITIALIZE signal (generated at power turn-on, by the <u>CLEAR</u> key or by the <u>CAF</u> instruction) but also by the 6135 instruction, Status to the AC. The 6135 instruction can clear E51 only if the Clock Enable 0 flip-flop has been previously set by a CLOE instruction. Thus, when E51 is set NAND gate E50 is enabled and it, in turn, enables NOR gate E49. When CLSA is issued, the STATUS TO AC signal enables NAND gate E48, asserting the DATA 0 L signal. At TP3 time E51 is cleared and can be set by the next Clock Counter Register overflow.

The status of E51 can be checked either by the CLSK instruction, alone, or via the interrupt system and the CLSK instruction. The interrupt system can be used only if the Clock Enable 8 flip-flop has been set. Then, E51 can assert the INT RQST L signal and the CLSK instruction in the interrupt servicing routine will cause a skip to the DK8-EP subroutine. There, CLSA causes the status of E51 to be transferred via the DATA 0 line to AC0.

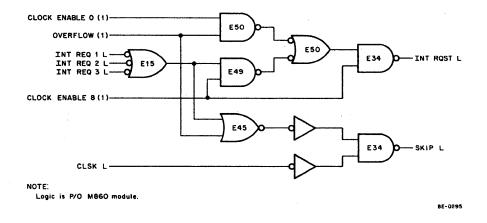

#### 3.7 Int/Skip Logic

The Int/Skip logic is shown in Figure 3-10. As indicated in previous discussions, program interrupts can be caused by external events and by overflow from the Clock Counter Register. The DK8-EP can be logically connected to the computer interrupt system if the Clock Enable 8 flip-flop is set by a CLOE instruction. When this flip-flop, alone, is set an external event can cause a program interrupt. The event causes the INT REQ 1, 2, or 3 L signal to be generated by the Input/Overflow Status logic. This signal first enables NOR gate E15 and finally causes NAND gate E34 to assert the OMNIBUS INT RQST L signal.

If the OVERFLOW (1) signal from the Overflow flip-flop logic is to generate an interrupt request, the Clock Enable 0 flip-flop also must be set. Then this signal can cause the INT RQST L signal to be asserted by NAND gate E34.

When the computer enters the interrupt servicing routine in response to the DK8-EP interrupt request, the CLSK instruction causes NAND gate E34 to assert the OMNIBUS SKIP L signal. Thus, the computer can be directed to the particular subroutine that services the request. If the Clock is not connected to the computer interrupt system, one can still make use of the CLSK instruction. The program can enter a waiting loop which checks the status of the two conditions (overflow and external event). When either condition is met, the appropriate subroutine is entered.

Figure 3-10 Int/Skip Logic

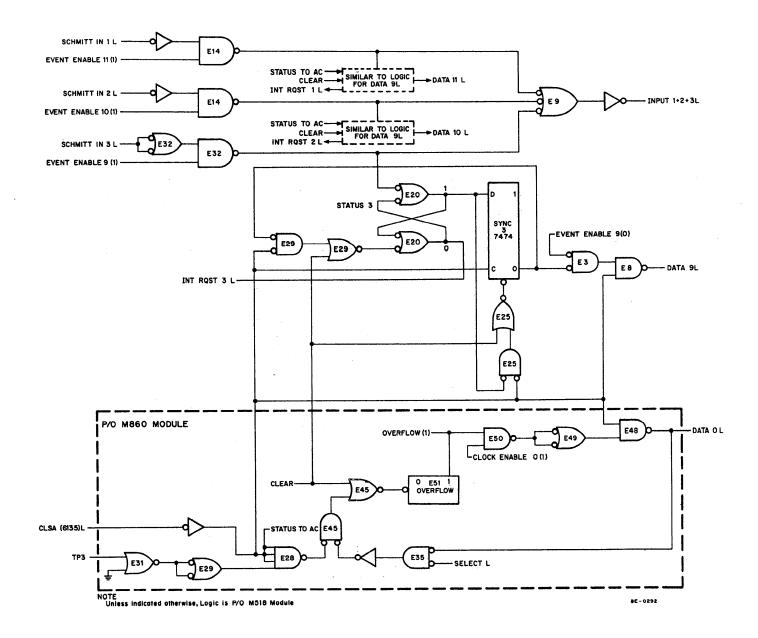

#### 3.8 Input/Overflow Status Logic

The Input/Overflow Status logic is shown in Figure 3-11. The logic enables the programmer to check the status of the Overflow flip-flop and the Schmitt trigger input channels. Input channel 3 is illustrated fully in Figure 3-11; the logic functions as follows. An external event can cause the SCHMITT IN 3 L signal to be asserted. If the Enable Event 09 flip-flop has been set by a previous CLOE IOT instruction, the SCHMITT IN 3 L signal sets the Status 3 flip-flop and asserts the INPUT 1+2+3 L signal. The latter signal can either actuate the clock or cause the contents of the Clock Counter Register to be transferred to the Clock Buffer Register. When the Status 3 flip-flop is set, it asserts the INT RQST 3 L signal. This signal can result in a program interrupt request, if the Clock Enable 8 flip-flop has been set by some previous CLOE instruction.

Assume that the external event causes a program interrupt. The OMNIBUS INT RQST L signal is asserted and the CPU enters the interrupt servicing routine. The CLSK instruction in the servicing routine causes the program to proceed to the DK8-EP subroutine. Here, it might be desirable to determine how often the event occurs in a given amount of time. Or, one might wish to determine which input channel caused the program interrupt. The CLSA IOT instruction accomplishes either of these tasks. When this instruction is issued, the Select logic generates the CLSA L signal that, in turn, generates the STATUS TO AC signal. The leading edge of the STATUS TO AC signal sets the Sync 3 flip-flop (the D-input of the flip-flop is high because the Status 3 flip-flop is set). Both NAND gate E3 and NAND gate E8 are enabled, the latter gate asserting the DATA 09 L signal. Remember that the CLSA L signal causes the OMNIBUS C0 L and C1 L signals to be asserted, resulting in a JAM transfer to the AC Register of the information on the DATA 09 line.

At approximately the same time that the DATA 09 L signal is asserted, the Status 3 flip-flop is cleared via NAND gate E29 (the Sync 3 flip-flop 0-output enables E29). Approximately 500 ns later (a function of the CPU Timing Generator) the CLSA L signal is negated. The Sync 3 flip-flop is then cleared via NAND gate E25. The two flip-flops are cleared so that only one occurrence of an event is transferred for each interrogation and so that an indication of an event occurs only when the event actually does occur.

The Overflow flip-flop also can cause a program interrupt (see Figure 3-10 for the Interrupt logic). The CLSA instruction allows the programmer to differentiate between external event-generated interrupts and overflow-generated interrupts, for example. If the Overflow flip-flop is set, and if the Clock Enable 0 flip-flop has been set by some CLOE instruction, the CLSA L signal causes the DATA 0 L signal to be asserted. At the same time, the C0 L and C1 L signals are asserted and the data is JAMed into the AC Register. At TP3 time the Overflow flip-flop is cleared via NAND gate E45; the flip-flop can now be set by a new overflow from the Clock Counter Register.

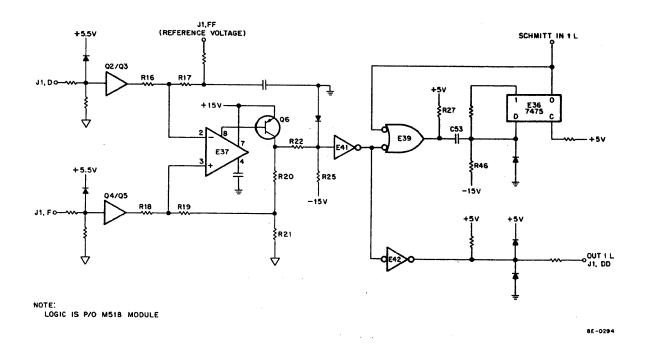

#### 3.9 Schmitt Trigger Logic

The Schmitt Trigger logic for Channel 1 is shown in Figure 3-12. The logic for Channel 2 and 3 is not included but is identical to that shown for Channel 1. The logic consists of a Schmitt Trigger circuit, those components to the left of inverter E41, and the two output pulse-shaping circuits to the right of E41.

The Schmitt Trigger circuit is built around a DEC 1709C IC, E37 (see Appendix A-2 for details). This IC is an operational amplifier that is being used as a comparator in the Schmitt Trigger. In this application only half of the IC internal circuitry is being used, the output of E37 being taken from pin 8 rather than pin 6. The output at pin 8 has the same relationship to the input at pins 2 and 3 as does the output at pin 6; i.e., pin 8 inverts the input at pin 2 but not the input at pin 3. For clarity, many of the components comprising the Schmitt Trigger inputs have been represented by the logic inverters designated Q2/Q3 and Q4/Q5. See logic drawing E-CS-M518-0-1 for the actual circuits. The differential input to the Schmitt Trigger is applied between J1D and J1F. The firing threshold voltage, which can be varied between +5V and -5V, is applied at J1FF. The hysteresis voltage, 0.3V, is determined by the value of resistors R20, R21, and R22.

Assume a threshold voltage of +4V. Until this voltage is exceeded by the differential input, the non-inverting input of E37, pin 3, is positive with respect to the inverting input, pin 2, and pin 8 is at approximately +15V. Thus, transistor Q6 is in the non-conducting state and the input to inverter E41 is near ground. Both the SCHMITT IN 1 L and the OUT 1 L signals are negated. When the differential input crosses the threshold, going positive, the inverting input goes positive with respect to the non-inverting input. The voltage at pin 8 drops to near-ground and Q6 switches on. The positive-going edge at the input of E41 triggers the latch circuit and E36 generates a pulse (duration determined by C53/R46 time constant), the SCHMITT IN 1 L signal, that is applied to the Input/Overflow Status logic. The OUT 1 L signal goes low when E41 is enabled, remaining low until the Schmitt Trigger is reset. The Trigger remains in the fired state until the differential input falls below +3.7V (threshold voltage minus hysteresis voltage). When this occurs, Q6 is turned off and remains off until the threshold is again exceeded.

The Schmitt Trigger logic is part of the M518 module, Input Logic and Schmitt Triggers. The DK8-EP user must provide cabling for the Schmitt Trigger differential inputs and the outputs, as well as for ground connections and the threshold voltages. These connections to the M518 module are made via J1 on the module. Table 4-1 lists the J1 pin numbers and the respective signal names.

Figure 3-12 Schmitt Trigger Logic

#### 4.0 MAINTENANCE

General instructions concerning preventive and corrective maintenance are given in Volume 1, Chapter 4 of the Maintenance manual. When corrective maintenance is required, the technician should use the maintenance program, MAINDEC-8E-D8AA, to determine the nature of the problem. The option schematics, E-CS-M860-0-1, and E-CS-M518-0-1, must be referred to for component locations and pin numbers. Test points have been provided on the option to facilitate troubleshooting.

Table 4-1 lists the J1 pin letters and their respective signal names.

Table 4–1

M518 Module J1 Connector Pin Letters and Assignments

| Pin | Signal Name                |

|-----|----------------------------|

| D   | CH1 Differential input (+) |

| F   | CH1 Differential input (-) |

| J   | CH2 Differential input (+) |

| Ĺ   | CH2 Differential input (-) |

| N   | CH3 Differential input (+) |

| R   | CH3 Differential input (-) |

| Ť   | +6.2 Volts out             |

| ·   | Schmitt Trigger common     |

| ×   | -6.2 Volts out             |

| Ž   | Schmitt Trigger OUT 3 L    |

| BB  | Schmitt Trigger OUT 2 L    |

|     |                            |

| DD  | Schmitt Trigger OUT 1 L    |

| FF  | CH1 Threshold voltage      |

| JJ  | CH2 Threshold voltage      |

| LL  | CH3 Threshold voltage      |

| NN  | OVERFLOW (0) L             |

| RR  | External pulse input       |

| TT  | Not used.                  |

The following pins are ground: A,B,C,E,H,K,M,P,S,U,W,Y,AA, CC,EE,HH,KK,MM,PP,SS,UU,VV.

#### 5.0 SPARE PARTS

To be supplied.