KT8-A memory management control user's guide

EK-KT08A-UG-001

#### Copyright © 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

#### Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS |

|---------|--------------|---------|

| DEC     | DECSYSTEM-20 | OMNIBUS |

| PDP     | DIBOL        | OS/8    |

| DECUS   | EDUSYSTEM    | RSTS    |

| UNIBUS  | VAX          | RSX     |

|         | VMS          | IAS     |

### **CONTENTS**

|           |                                        | Page |

|-----------|----------------------------------------|------|

| CHAPTER 1 | INTRODUCTION                           |      |

| 1.1       | SCOPE OF MANUAL                        | 1-1  |

| 1.2       | GENERAL DESCRIPTION                    | 1-1  |

| 1.3       | KT8-A SPECIFICATIONS                   | 1-3  |

| 1.4       | RELATED DOCUMENTS                      | 1-4  |

| 1.5       | SOFTWARE                               | 1-5  |

| 1.5.1     | Diagnostic                             | 1-5  |

| 1.5.2     | System                                 | 1-5  |

| CHAPTER 2 | INSTALLATION                           |      |

| 2.1       | GENERAL                                | 2-1  |

| 2.2       | SINGLE-BOX CONFIGURATIONS              | 2-2  |

| 2.3       | DOUBLE-BOX CONFIGURATIONS              | 2-3  |

| 2.4       | MEMORY MODULE INSTALLATION             | 2-4  |

| 2.5       | KM8-AC MODULE INSTALLATION             | 2-6  |

| 2.6       | VERIFICATION                           | 2-6  |

| CHAPTER 3 | OPERATION AND PROGRAMMING              |      |

| 3.1       | OPERATION                              | 3-1  |

| 3.1.1     | Power-up Conditions                    | 3-1  |

| 3.1.2     | PDP-8/A Programmer's Console Functions | 3-1  |

| 3.2       | PROGRAMMING                            | 3-2  |

| 3.2.1     | KT8-A Instructions                     | 3-2  |

| 3.2.2     | Functional Description                 | 3-14 |

| 3.2.3     | Programming Examples                   | 3-16 |

| 3.2.3.1   | 128K-Word Memory Implementation        | 3-16 |

| 3.2.3.2   | KT8-A as I/O Controller                | 3-17 |

| 3.2.3.3   | KT8-A in a System Environment          | 3-18 |

| 3.2.3.4   | Context Switching                      | 3-20 |

| 3.2.3.5   | User Mode Hidden State                 |      |

| 3.2.3.6   | Modified User Mode                     | 3-22 |

| 3.2.3.7   | Programming Notes                      | 3-23 |

## **FIGURES**

| Figure No. | Title                                                                       | Page |

|------------|-----------------------------------------------------------------------------|------|

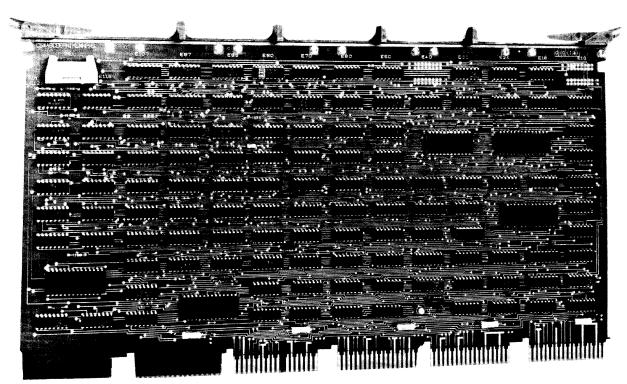

| 1-1        | KT8-A (M8416) Module                                                        | 1-1  |

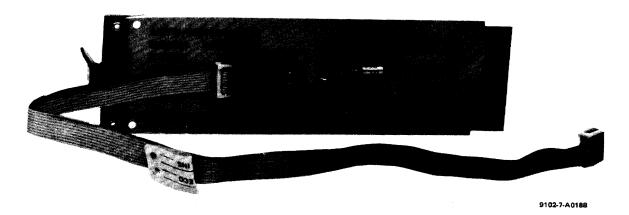

| 1-2        | M9020 Terminator and Cable                                                  | 1-2  |

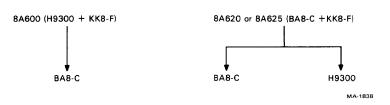

| 2-1        | KT8-A Double-Box Configurations                                             | 2-1  |

| 2-2        | Representative KT8-A System Configuration, 8A600 Computer                   |      |

| 2-3        | Representative KT8-A System Configuration, 8A400 Computer                   |      |

| 2-4        | Representative KT8-A System Configuration, 8A600 Computer with BA8-C Expand |      |

| 2-5        | Representative KT8-A System Configuration, Single-Box Memory                |      |

| 3-1        | KT8-A Related Programmer's Console Functions                                |      |

| 3-2        | Bus Display Bit Assignment                                                  |      |

| 3-3        | Mode Control Functional Diagram                                             |      |

| 3-4        | Memory Extension Functional Diagram                                         |      |

| 3-5        | Memory Management Functional Diagram                                        |      |

| 3-6        | 62X1 CDF IOT Instruction                                                    |      |

## **TABLES**

| Table No. | Title                                                                     | Page |

|-----------|---------------------------------------------------------------------------|------|

| 1-1       | KT8-A Specifications                                                      | 1-3  |

| 2-1       | KT8-A Single-Box Configurations                                           | 2-1  |

| 2-2       | MS8-CA Switch Settings for Field Assignments                              | 2-5  |

| 2-3       | MS8-CB Switch Settings for Field Assignments                              |      |

| 2-4       | MM8-AB Modifications for Field Assignments                                |      |

| 2-5       | KM8-AC Jumper Configuration for Disabling Memory Extension and Time-Share |      |

| 3-1       | KT8-A Registers                                                           |      |

| 3-2       | KM8-A/KM8-E Compatible Instructions                                       | 3-7  |

| 3-3       | KI8-A Expanded Instructions                                               |      |

| 3-4       | KT8-A Programmability Modes                                               |      |

# CHAPTER 1

#### 1.1 SCOPE OF MANUAL

The KT8-A is an Omnibus option that provides memory extension (up to 128K words) and memory management capability for PDP-8/A systems. This manual describes the KT8-A, tells how to install it in a system, and gives detailed operating and programming instructions. Paragraph 1.4 lists additional documents helpful to the KT8-A user.

#### 1.2 GENERAL DESCRIPTION

The logic and circuit components that comprise the KT8-A are mounted on a single hex-size printed circuit board (M8416 module). The module can be inserted in the Omnibus of all PDP-8/A computers, except the 8A100. When the KT8-A is installed in a two-box system (any combination of H9300 and BA8-C boxes) containing memory in both boxes, a terminator module (M9020) and an interconnecting cable must be used to achieve bank select signal continuity between boxes. The M8416 is pictured in Figure 1-1, while the M9020 and the cable that connects the two modules are shown in Figure 1-2.

9102-2-A0187

Figure 1-1 KT8-A (M8416) Module

Figure 1-2 M9020 Terminator and Cable

The basic function of the KT8-A is to furnish PDP-8/A memory extension, i.e., to supply the five highest-order address bits for PDP-8/A memory. Memory addresses are generated by the CPU and by direct memory access (DMA) peripherals. However, the CPU can provide only a 12-bit address (bits MA0-MA11) and DMA devices are limited to 15-bit addresses (bits MA0-MA11 and EMA0-EMA2); consequently, to achieve the full potential of 128K word memory address space, the KT8-A adds five bits to a CPU-generated address and two bits to a DMA-generated address.

Earlier PDP-8 memory extension controls, the KM8-E and the KM8-A, are capable of supplying only 15 bits of memory address (up to 32K words). However, programs that were written for these options are compatible with the KT8-A. Furthermore, the KM8-AC can be used with the KT8-A to provide bootstrap and/or power fail/auto-restart capabilities (the memory extension and time-share feature of the KM8-AC must be disabled in this application).

In addition to the memory extension function, the KT8-A performs memory management, which provides two important advantages for an operating system. First, memory management allows an operating system to monitor the I/O operations and memory access of a program that is under the system's control. Second, memory management enables an operating system to execute a program originally constructed for exclusive use of the computer.

Unlike memory management carried out by the KM8-E, wherein the operating system must perform certain calculations each time the running program tries to access a different 4K memory field, the KT8-A is set up by its operating system to perform these calculations automatically. Thus, the KT8-A requires a less complex operating system than the KM8-E and results in faster execution of the running program.

#### 1.3 KT8-A SPECIFICATIONS

Table 1-1 lists the significant specifications of KT8-A systems.

Table 1-1 KT8-A Specifications

| Item                                                   | Specification                                                                                                                         |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| CPU Memory Address Space                               | Programmable – 32 K (2 <sup>15</sup> ), 64K (2 <sup>16</sup> ), or 128K (2 <sup>17</sup> ) words                                      |

| DMA Memory Address Space                               | Programmable – 32K or 128K words                                                                                                      |

| Addressing Space Accessible without KT8-A Intervention | 4K Segments (2 <sup>12</sup> )                                                                                                        |

| Memory Compatibility                                   | Total memory less than or equal to 32K - Any PDP-8/A memory type can be used                                                          |

|                                                        | Total memory greater than 32K – Only MM8-AB, MS8-CA, MS8-CB memories can be used.                                                     |

| Enclosure Compatibility                                | KT8-A can be used in all BA8-C and H9300 boxes†                                                                                       |

| Option Compatibility                                   | All PDP-8/A options are compatible, except KM8-AA and KM8-AB                                                                          |

| Software Compatibility                                 | All programs written for PDP-8/A and PDP-8/E are compatible, except instruction 6200 (LXM)                                            |

| Device Codes                                           | Permanent: 20–27                                                                                                                      |

|                                                        | Program Enabled: 17 and 30-37                                                                                                         |

| Mode Control                                           | Foreground/background 32K/64K/128K KM8-A/KM8-E or Extended Instruction Set Maintenance mode                                           |

| Background Program Options<br>(Programmable)           | Dynamic Memory Relocation (4K increments) Memory Protection (4K boundaries) I/O Instruction Trap                                      |

| Power Consumption                                      | KT8-AA: +5 V @3.7 A<br>KT8-AB: +5 V @5.7 A<br>KT8-EX: +20 V @0.1 A                                                                    |

| Environmental Requirements                             |                                                                                                                                       |

| Operating Temperature* Operating Humidity              | 5° C-50° C (41° F-122° F)<br>10%-95%, with a maximum wet bulb temperature of 32° C<br>(90° F) and a minimum dew point of 2° C (36° F) |

The maximum allowable operating temperature is based on operation at sea level, i.e., at 760 mm Hg (29.92 inches Hg); maximum allowable operating temperature will be reduced by a factor of 1.8° C/1000 m (1.0° F/1000 ft) for operation at higher altitude sites.

<sup>†</sup> H9194 backplanes in the H9300 box must have a sticker (P/N 3615653-00) reading "KT8-A COMPATIBLE" affixed to the component side of the backplane; if the sticker is not present, the backplane must be modified according to DEC ECO H9194-00003.

#### 1.4 RELATED DOCUMENTS

The following documents contain information of interest to the KT8-A user.

| Document Title                                    | Document Number | Remarks                                           |

|---------------------------------------------------|-----------------|---------------------------------------------------|

| PDP-8/A Miniprocessor<br>User's Manual            | EK-8A002-MM-002 | Available in hard copy.                           |

| PDP-8/A Minicomputer Handbook                     | EB-06219-76     | Available in hard copy.                           |

| PDP-8 Family Configuration Guide                  | EK-OPDP8-SP-001 | Available in hard copy.                           |

| KT8-A Technical Manual                            | EK-KT08A-TM-001 | In Microfiche library;<br>available in hard copy. |

| MS8-C MOS Memory Operation and Maintenance Manual | EK-MS8C-TM001   | In Microfiche library;<br>available in hard copy. |

Hard copy documents can be ordered from:

Digital Equipment Corporation 444 Whitney St. Northboro, MA 01532

ATTN:

Communication Services (NR2/M15)

**Customer Services Section**

For information concerning microfiche library, contact:

Digital Equipment Corporation 132 Parker St. Maynard, MA 01754

ATTN:

Micropublishing Group

PK3-2/T12

#### 1.5 SOFTWARE

#### 1.5.1 Diagnostic

The KT8-A uses the following diagnostic software:

**Program Title**

**Program Number**

KT8-A Memory Management Diagnostic

MAINDEC-08-DJKTA-A

Extended Address Test,

MAINDEC-08-DHKMC-C

**Extended Memory Data and Checkerboard Test**

MAINDEC-08-DHKMA-D

DEC/X8 Monitor, Version 2, and all support modules appropriate to Version 2.

#### 1.5.2 System

OS/8, Version 3D/128K, support will include greater-than-32K functions of GET, SAVE, ODT, and RUN. Verson 2 of MACREL/LINKER will support greater-than-32K assemblies and linkages. RTS8, Version 3, is capable of using all available memory and supports up to 32K OS/8 background task. Existing OS/8 and assembly language programs can work with the KT8-A option installed, but will not fully utilize the KT8-A features. Programs can be written under PAL8 to make use of KT8-A extended functions. Early versions of OS/8 utilities do not support extended memory.

# CHAPTER 2 INSTALLATION

#### 2.1 GENERAL

There are three types of KT8 options. The KT8-AA consists of the M8416 module alone; this type is found in a system configuration that is arranged and shipped by DIGITAL. The KT8-AB consists of an M8416 module and a KM8-AC option (memory extension and timeshare, power fail/auto-restart, and bootstrap); this type is intended to be an addition to an existing PDP-8/A system. The KT8-EX consists of an M9020 terminator module and a cable that connects the M9020 to the KT8-A; this type is required in a 2-box system when memory is to occupy space in both boxes.

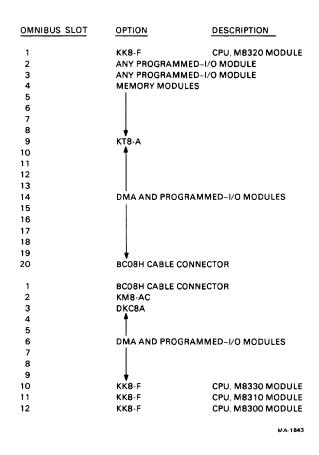

The KT8 can be installed in all PDP-8/A computers, although it cannot be used in systems that include a PDP-8/E or PDP-8/M. Thus, there are a number of possible 1-box and 2-box configurations involving the KT8. Table 2-1 summarizes the possible 1-box configurations, while Figure 2-1 illustrates the possible 2-box configurations. Note that an 8A600 computer can be expanded only with a BA8-C box, while the 8A620 or 8A625 computers can be expanded with both a BA8-C box and an H9300 box.

| PDP-8/A Computer        | CPU Type | Chassis Type    |

|-------------------------|----------|-----------------|

| 8A205<br>8A400<br>8A405 | KK8-A    | H9300 (12-slot) |

| 8A600                   | KK8-F    |                 |

| 8A420<br>8A425          | KK8-A    | BA8-C (20-slot) |

| 8A620<br>8A625          | KK8-F    | ·               |

Table 2-1 KT8-A Single-Box Configurations

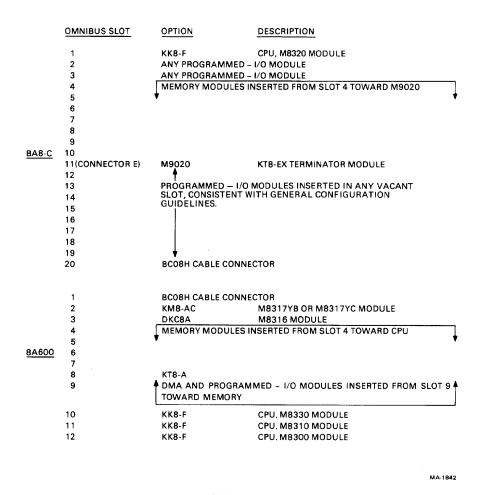

Figure 2-1 KT8-A Double-Box Configurations

#### 2.2 SINGLE-BOX CONFIGURATIONS

In a single-box configuration the KT8-A can be inserted in any Omnibus slot that has an 'E' connector. Practically, the module should be placed in slot 4, 8, or 11, depending on the box type and the CPU type. For example, Figure 2-2 lists the Omnibus slots and their contents for a repesentative 8A600 system containing a KT8-A. The KT8-A can be inserted in any of slots 4 through 8. However, memory should be placed as far away from the CPU as possible (refer to the *PDP-8 Family Configuration Guide*); hence, the most practicable location for the KT8-A is in slot 8. (DMA modules must always be placed between memory and the CPU; in this context the KT8-A is not considered to be a memory module; hence, DMA modules can be placed between the KT8-A and memory.) Figure 2-3 represents a different configuration. Here, the KT8-A occupies slot 4 again so that there will be maximum separation of CPU and memory.

| OMNIBUS SLOT | OPTION       | DESCRIPTION                                           |

|--------------|--------------|-------------------------------------------------------|

| 1            | KK8-F        | CPU, M8320 MODULE                                     |

| 2            | KM8-AC       | M8317YB OR M8317YC MODULE                             |

| 3            | DKC8A        | M8316 MODULE                                          |

| 4            | MEMORY MODU  | ILES INSERTED FROM SLOT 4 TOWARD CPU                  |

| 5            | •            | ·                                                     |

| 6            |              |                                                       |

| 7            |              |                                                       |

| 8            | KT8-A        |                                                       |

| 9            | DMA AND PROG | RAMMED-I/O MODULES INSERTED FROM SLOT 9 TOWARD MEMORY |

| 10           | KK8-F        | CPU. M8300 MODULE                                     |

| 11           | KK8-F        | CPU, M8310 MODULE                                     |

| 12           | KK8-F        | CPU, M8330 MODULE MA-1839                             |

Figure 2-2 Representative KT8-A System Configuration, 8A600 Computer

| 1 KK8-A CPU 2 KM8-AC M8317YB OR M8317YC MODULE 3 DKC8A M8316 MODULE 4 KT8-A                     |        |

|-------------------------------------------------------------------------------------------------|--------|

| 3 DKC8A M8316 MODULE                                                                            |        |

| WIGS TO WIGHDOLE                                                                                |        |

| 4 KT8-A                                                                                         |        |

|                                                                                                 |        |

| 5 DMA AND PROGRAMMED-I/O MODULES INSERTED FROM SLOT 5 ▼ TOWARD MEMORY                           | 1      |

| 6                                                                                               | •      |

| 7                                                                                               |        |

| 8 MEMORY MODULES INSERTED FROM SLOT 8 TOWARD CPU                                                | 1      |

| PROGRAMMED-I/O MODULES INSERTED IN ANY VACANT SLOT, CONSISTENT WITH GENERAL CONFIGURATION RULES | -<br>] |

| 10                                                                                              | •      |

| 11                                                                                              |        |

| 12<br>Mā.18e                                                                                    | 40     |

Figure 2-3 Representative KT8-A System Configuration, 8A400 Computer

#### 2.3 DOUBLE-BOX CONFIGURATIONS

A 2-box system can be comprised of two BA8-C boxes or one BA8-C and one H9300 box (an H9300 box cannot be used to expand another H9300 box). In either combination the KK8-F CPU must be used.

Figure 2-4 shows a representative 8A600 system expanded with a BA8-C box. Memory is contained in both boxes; hence, the M9020 terminator must be inserted in an 'E' connector of the BA8-C so that bank select signals generated by the KT8-A can be supplied to all memories (a quad-size programmed-I/O module could be inserted in the same Omnibus slot occupied by the M9020). The M9020 (and the KT8-A in the 8A600) can be inserted in any slot having an E connector; however, its placement in slot 11, assuming slots 4 through 10 are occupied by memory, means that memory will be as far away from the CPU as is possible.

Figure 2-4 Representative KT8-A System Configuration, 8A600 Computer with BA8-C Expander

If memory were to be contained in only one box, it would be installed in the expander. In this case, the KT8-A would be moved to slot 11 of the expander (if memory occupied slots 4 through 10), or to slot 9 (if memory occupied only slots 4 through 8). This latter situation is illustrated in Figure 2-5.

Figure 2-5 Representative KT8-A System Configuration, Single-Box Memory

#### 2.4 MEMORY MODULE INSTALLATION

The KT8 can be used with any combination of MM8-AB memory (16K core), MS8-CA memory (16K MOS), and MS8-CB memory (32K MOS). Each memory module is assigned a field of bus addresses before being inserted in the Omnibus. The field assignment is made by switches on both the MS8-CA and MS8-CB modules. Tables 2-2 and 2-3 show how the switches are set for these MOS memories (refer to the MS8-C MOS Memory Operation and Maintenance Manual, EK-MS8C-TM-001, for more information).

The field assignments for the MM8-AB memory require modification to the module itself. A wire must be added between two connector fingers to make a bank assignment and a jumper must be connected between two terminal posts to make a field assignment (the terminal post locations are shown in the PDP8/A Miniprocessor User's Manual). Table 2-4 indicates the wire and jumpers that must be added to achieve the desired field assignment (refer to DEC ECO MM8-AB, Number 7 for complete instructions concerning modification).

Table 2-2 MS8-CA Switch Settings for Field Assignments

| Assigned<br>Bank | Bank and Field<br>Field | Switch Off (All Others On) |

|------------------|-------------------------|----------------------------|

| 0                | 0-3 (0-16K)             | S1-1                       |

|                  | 4-7 (16-32K)            | S1-2                       |

| 1                | 0-3 (32-48K)            | S1-3                       |

|                  | 4-7 (48-64K)            | S1-4                       |

| 2                | 0-3 (64-80K)            | S1-5                       |

|                  | 4-7 (80-96K)            | S1-6                       |

| 3                | 0-3 (96-112K)           | S1-7                       |

|                  | 4-7 (112-128K)          | S1-8                       |

Table 2-3 MS8-CB Switch Settings for Field Assignments

| Assigned Bank and Field<br>Bank Field |               | Switch Off (All Others On) |

|---------------------------------------|---------------|----------------------------|

| 0                                     | 0-7 (0-32K)   | S1-1, S1-2                 |

| 1                                     | 0-7 (32-64K)  | S1-3, S1-4                 |

| 2                                     | 0-7 (64-96K)  | S1-5, S1-6                 |

| 3                                     | 0–7 (96–128K) | S1-7, S1-8                 |

Table 2-4 MM8-AB Modifications for Field Assignments

| Assigned Bank and Field<br>Bank Field |                | Connect These<br>Fingers With a Wire* | Connect a Jumper at<br>These Terminal Post<br>Locations<br>(Other Locations Blank) |

|---------------------------------------|----------------|---------------------------------------|------------------------------------------------------------------------------------|

|                                       | 11614          | ringers veittra vene                  | (Other Lucations Blank)                                                            |

| 0                                     | 0-3 (0-16K)    | AB1 – EB2                             | 1-2, 1-3                                                                           |

|                                       | 4–7 (16–32K)   | AB1 – EB2                             | 1-2, 2-4                                                                           |

| 1                                     | 0-3 (32-48K)   | AB1 – ED2                             | 3-4, 1-3                                                                           |

|                                       | 4-7 (48-64K)   | AB1 – ED2                             | 3-4, 2-4                                                                           |

| 2                                     | 0-3 (64-80K)   | AB1 – EL2                             | 3-4, 1-3                                                                           |

|                                       | 4-7 (80-96K)   | AB1 – EL2                             | 3-4,2-4                                                                            |

| 3                                     | 0-3 (96-112K)  | AB1 – ER2                             | 3-4, 1-3                                                                           |

|                                       | 4-7 (112-128K) | AB1 – ER2                             | 3-4 2-4                                                                            |

<sup>\*</sup> There is a feed-through connector on the printed circuit board just above pin AB1. One end of the wire can be soldered into this feed-through; the other end of the wire must be soldered to the pin itself.

#### 2.5 KM8-AC MODULE INSTALLATION

In cases where the KT8 is being added to an existing system, the KM8-AC option (memory extension and timeshare, power fail/auto-restart, and bootstrap) may be present. The KM8-AC can continue to be used with the KT8 to provide power fail/auto-restart and/or bootstrap capability. However, the memory extension and timeshare portion of the KM8-AC option must be disabled. This is done by arranging jumpers W1 through W4 on the KM8-AC module (M8317-YB or M8317-YC) as indicated in Table 2-5 (the *PDP-8/A Miniprocessor User's Manual* shows the location of the jumpers).

Table 2-5 KM8-AC Jumper Configuration for Disabling Memory Extension and Time-Share

| Jumper Location | *Jumper |  |

|-----------------|---------|--|

| <b>W</b> 1      | OUT     |  |

| W2              | IN      |  |

| W3              | IN      |  |

| W4              | IN      |  |

<sup>\*</sup> When the KM8-AC is used with the KT8-A, this jumper arrangement must be employed.

#### 2.6 VERIFICATION

When the various modules have been configured properly and installed in the backplane, verify system operation by running the KT8-related software diagnostics.

- Load and run the KT8-A Memory Management Diagnostic as described in the diagnostic description for five minutes; there must be no errors.

- 2. Load and run the Extended Address Test for one pass; there must be no errors.

- Load and run the Extended Memory Data and Checkerboard Test for one pass; there must be no errors.

If a problem occurs during verification, contact the DIGITAL Field Service organization.

## CHAPTER 3 OPERATION AND PROGRAMMING

#### 3.1 OPERATION

#### 3.1.1 Power-up Conditions

When the KT8-A is turned on, these registers and flip-flops are cleared:

Instruction Field Register Instruction Bank Register Data Field Register Data Bank Register Instruction Field Buffer Instruction Bank Buffer Interrupt Inhibit flip-flop User Mode flip-flop User Interrupt flip-flop User Size Register Relocation Register Extended Mode Register Last Break Register

The contents of these elements are undefined:

Save Register Break Map

#### 3.1.2 PDP-8/A Programmer's Console Functions

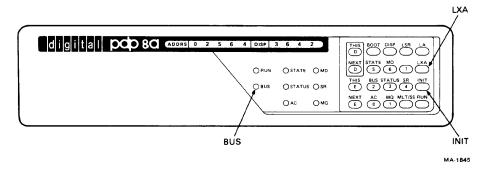

Both the instruction field (identified by the instruction bank register and the instruction field register) and the data field (identified by the data bank register and the data field register) can be set from the programmer's console. To do so, enter the four octal digits on the console key pad (see Figure 3-1). As each octal digit is entered, it appears in the DISP readout on the console (refer to the PDP-8/A Miniprocessor User's Manual for console operating instructions). When all four digits are entered, press the LXA button. This loads the instruction field and data field, clears the user mode buffer, the user mode flip-flop, the relocation register, the user size register, and the extended mode register, and puts the KT8-A in the KM8-A/KM8-E compatible mode.

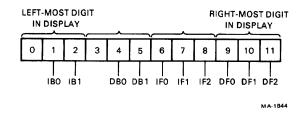

The contents of the four registers can be checked by pressing the BUS button and then the DISP button. The console BUS indicator lights and the contents of the PDP-8/A DATA bus are displayed in the DISP readout. The readout is interpreted as illustrated in Figure 3-2.

When the console INIT button is pressed (or the CAF instruction is issued), the user interrupt flag, the last break register, the maintenance register, the interrupt inhibit flip-flop, and the fatal flip-flop are cleared.

When the console LXA button is pressed, the user size register, the relocation register, the extended mode register, the user mode flip-flop, and the interrupt inhibit flip-flop are cleared.

Figure 3-1 KT8-A Related Programmer's Console Functions

Figure 3-2 Bus Display Bit Assignment

#### 3.2 PROGRAMMING

#### 3.2.1 KT8-A Instructions

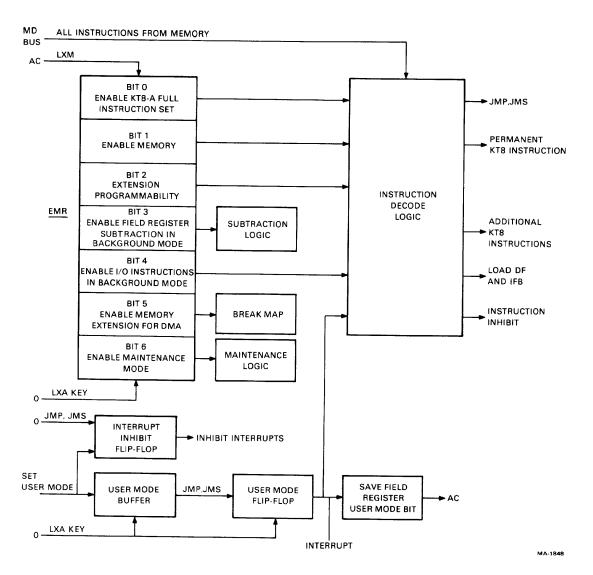

The KT8-A logic includes registers and control flip-flops that are described in Table 3-1. Figures 3-3, 3-4, and 3-5; and Paragraph 3.2.2., illustrate how these registers and flip-flops are used.

There are two sets of instructions for the KT8-A. One set, that of KM8-A/KM8-E compatible instructions, is appropriate when KM8-A/KM8-E software is used with the KT8-A. The other set, that of KT8-A expanded instructions, is used with software designed expressly for use with the KT8-A. The LXM instruction (load extended mode register), in a category of its own, determines which set is to be performed; a description of this instruction follows. Tables 3-2 and 3-3 list and describe the two sets selectable with the LXM instruction.

LXM,6200,Load eXtended Mode register – The AC register is defined as shown below and is cleared upon the execution of this instruction.

| AC Bit | Contents                                                                                                                                                                                                                                                                                                 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | EMM – Enable Memory Management instructions. When this bit = 1, the entire KT8-A instruction set is active. When this bit = 0, only the KM8-A/KM8-E instructions are performed.                                                                                                                          |

| 1, 2   | EN5, EN9 – ENable MD bits 5 and 9 of the CIF and CDF instructions such that they define bank bit 0 and bank bit 1, respectively. These control bits are independent of the EMM bit. Thus, memory access can be extended with the EN5 and EN9 instructions without enabling the other KT8-A instructions. |

Table 3-1 KT8-A Registers

| Register                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction Field Register (IFR) | 5-bit register linked with the CPU's program counter (PC). Identifies the 4K-unit of memory from which instructions are being executed. Loaded from the instruction field buffer or from the programmer's console; cleared at power-up or upon interrupt.                                                                                                                                                                                                                                                                                                                             |

| Instruction Field Buffer (IFB)   | Programmable 5-bit register whose contents are transferred to the IFR upon execution of a JMP or JMS instruction. Loaded from the programmer's console; cleared at power-up or upon interrupt.                                                                                                                                                                                                                                                                                                                                                                                        |

| Data Field Register (DFR)        | Programmable 5-bit register whose contents become the most significant bits of the operand address for indirect AND, TAD, ISZ, and DCA instructions. Loaded from the programmer's console; cleared at power-up or upon interrupt.                                                                                                                                                                                                                                                                                                                                                     |

| Extended Mode Register (EMR)     | Programmable 7-bit register that is loaded with parameters that define KT8-A operation, in particular, that group of instructions that are to be decoded by the KT8-A. Cleared at power-up and by the LXA key.                                                                                                                                                                                                                                                                                                                                                                        |

| User Mode Buffer (UMB)           | Programmable 1-bit register whose contents are transferred to the User Mode register upon execution of a JMP or JMS instruction. Cleared at power-up, upon interrupt and when the IFR and DFR are loaded from the programmer's console.                                                                                                                                                                                                                                                                                                                                               |

| User Mode (UM) Flip-flop         | Serves as a switch for multi-level software, i.e., when equal to 0, the foreground mode is selected, when equal to 1 the background mode is selected. The UM flip-flop is loaded from the user mode buffer upon execution of JMP and JMS instructions; the flip-flop is cleared at power-up, upon interrupt, and when the IFR and DFR are loaded from the programmer's console.                                                                                                                                                                                                       |

| User Interrupt Flip-flop         | In the background mode, this flip-flop is set when an illegal instruction is detected. Tested and cleared under program control or the INIT key.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| User Size Register (USR)         | Programmable 6-bit register that defines the number of contiguous memory fields to which a background program has access. In background mode the value of a field change is compared to the USR; if the USR is greater than the value specified by the change field instruction, normal operation continues; if not, the instruction is inhibited, an interrupt is generated, and the user interrupt flip-flop is set. A zero in the USR causes all change field instructions issued in background mode to result in an interrupt. The USR is cleared at power-up and by the LXA key. |

| Save Field Register (SFR)        | 11-bit register that the IFR, the DFR, and the UM flip-flop are transferred to upon interrupt. The SFR can be transferred to the AC for data retention, or its contents can be restored to the IFR, the DFR, and the UM flip-flop (see RMF instruction).                                                                                                                                                                                                                                                                                                                              |

| Relocation Register              | Programmable 5-bit register. Used in the background mode to change the memory area in which a program operates. The field value specified in instructions that change the instruction field or data field are added to the contents of the relocation register. The result is loaded into the IFB or DFR. Cleared at power-up and by the LXA key.                                                                                                                                                                                                                                     |

Table 3-1 KT8-A Registers (Cont)

| Register                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maintenance Register        | 10-bit register that monitors the bank select and EMA lines. Loaded during each break cycle, whenever a data field access is made, and in maintenance mode during the execute cycle of a JMS instruction and the fetch cycle following a JMP instruction. Read by an I/O instruction and cleared by the CAF instruction.                                                                                                                                                             |

| Interrupt Inhibit Flip-flop | Set when IFB is changed or user mode buffer is set. When the interrupt inhibit flip-flop is set, the interrupt latency time is increased by an amount equal to the time between an instruction that changes the IFB or sets the UM flip-flop and the next JMP or JMS. When the interrupt inhibit flip-flop is set in the background mode, any illegal instruction issued causes an unrecoverable interrupt to occur immediately. Cleared upon execution of a JMP or JMS instruction. |

| Fatal Flip-flop             | When set, this flip-flop indicates that an illegal instruction was issued in the background mode while the interrupt inhibit flip-flop was set. The flip-flop is accessible to the program and is displayed by the programmer's console in bit 3 of the status word. Cleared when the user interrupt flip-flop is 0.                                                                                                                                                                 |

| Last Break Register (LBR)   | 4-bit register that is loaded with the priority number of the last device to have requested a break. The LBR is loaded with 17 at power-up and when a CAF instruction is issued. Each time a break occurs, a number between 0 and 148 is loaded.                                                                                                                                                                                                                                     |

| Break Map                   | Programmable 13 X 2-bit register file that provides two additional address bits (bank bits) for the 15-bit address generated by a DMA device. The break map is activated by the EBM bit of the EMM word; when the map is not enabled, all data breaks are to bank 0.                                                                                                                                                                                                                 |

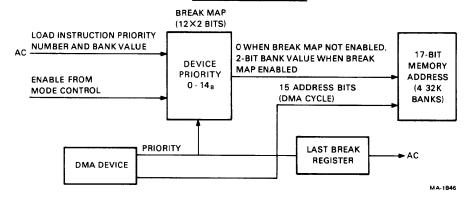

Figure 3-3 Mode Control Functional Diagram

#### DMA ADDRESS EXTENSION

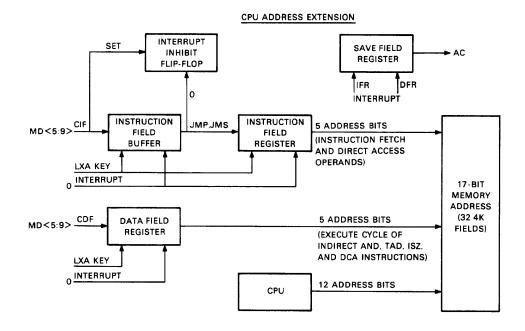

Figure 3-4 Memory Extension Functional Diagram

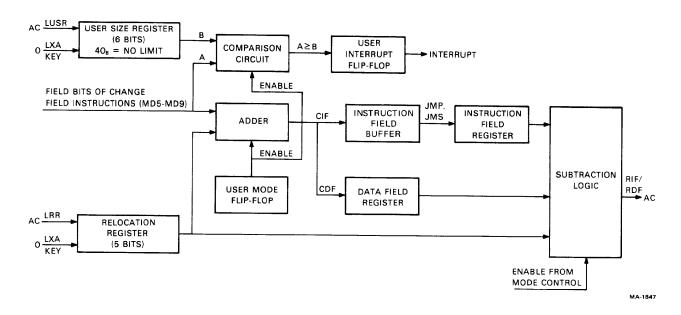

Figure 3-5 Memory Management Functional Diagram

Table 3-2 KM8-A/KM8-E Compatible Instructions

| Instr | uction   |                                                                                               |                                                                                                                                                                                      |

|-------|----------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Octal | Mnemonic | Description                                                                                   |                                                                                                                                                                                      |

| 62N1  | CDF      | Change Data Field as defined by MD bits 6-8 (N) of the instruction. MD6=DF0, MD7=DF1, MD8=DF2 |                                                                                                                                                                                      |

| 62N2  | CIF      |                                                                                               | Field buffer as defined by MD bits 6-8 (N) of the the interrupt inhibit flip-flop. MD6=IF0, MD7=IF1,                                                                                 |

| 62N3  | CDF, CIF | Combination of the                                                                            | CDF and CIF instructions                                                                                                                                                             |

| 6004  | GTF      | GeT Flags – Loads status bits into the                                                        | s the contents of the save field register and CPU<br>AC register as shown below                                                                                                      |

|       |          | AC Bit                                                                                        | Contents                                                                                                                                                                             |

|       |          | 0                                                                                             | Link                                                                                                                                                                                 |

|       |          | 1                                                                                             | Greater Than flag                                                                                                                                                                    |

|       |          | 2                                                                                             | Interrupt bus                                                                                                                                                                        |

|       | !        | 3                                                                                             | Fatal flip-flop                                                                                                                                                                      |

|       |          | 4                                                                                             | Interrupt on                                                                                                                                                                         |

|       |          | 5                                                                                             | Save user mode                                                                                                                                                                       |

|       |          | 6                                                                                             | Save field bit 0 (IF bit 0)                                                                                                                                                          |

|       | 1        | 7                                                                                             | SF1 (IF1)                                                                                                                                                                            |

|       | i l      | 8<br>9                                                                                        | SF2 (IF2)                                                                                                                                                                            |

|       |          | 9<br>10                                                                                       | SF3 (DF0)                                                                                                                                                                            |

|       |          | 11                                                                                            | SF4 (DF1)                                                                                                                                                                            |

|       |          | 1 1                                                                                           | SF5 (DF2)                                                                                                                                                                            |

| 6005  | RTF      | fer, and data field r                                                                         | ads the link, user mode buffer, instruction field buf-<br>egister from the AC register as shown below. RTF<br>iterrupt system (ION) and sets the interrupt inhibit<br>ext JMP or JMS |

Table 3-2 KM8-A/KM8-E Compatible Instructions (Cont)

| Inst  | ruction  |                                  |                                                                                                                                       |

|-------|----------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Octal | Mnemonic | Description                      |                                                                                                                                       |

| -     |          | AC Bit                           | Contents                                                                                                                              |

|       |          |                                  |                                                                                                                                       |

|       |          | 0                                | Link                                                                                                                                  |

|       |          | 1 2                              | Greater Than flag                                                                                                                     |

|       |          | 3                                |                                                                                                                                       |

|       |          | 4                                |                                                                                                                                       |

|       |          | 5                                | User mode buffer                                                                                                                      |

|       |          | 6                                | Save field bit 0 (IF bit 0)                                                                                                           |

|       |          | 7                                | SF1 (IF1)                                                                                                                             |

|       |          | 8                                | SF2 (IF2)                                                                                                                             |

|       |          | 9                                | SF3 (DF0)                                                                                                                             |

|       |          | 10                               | SF4 (DF1)                                                                                                                             |

|       |          | 11                               | SF5 (DF2)                                                                                                                             |

| 6204  | CINT     | Clear user INTerrup              | t flag                                                                                                                                |

| 6214  | RDF      | Read Data Field – Ir<br>7, and 8 | nclusive-OR of the data field register with AC bits 6,                                                                                |

| 6224  | RIF      | Read Instruction Fi              | eld – Inclusive-OR of the instruction field register and 8                                                                            |

| 6234  | RIB      |                                  | er – Inclusive-OR of the save field register (not in-<br>node) with AC bits 6 through 11, as shown below                              |

|       |          | AC Bit                           | Contents                                                                                                                              |

|       |          | 6                                | SFO (IFO)                                                                                                                             |

|       |          | 7                                | SF1 (IF1)                                                                                                                             |

|       |          | 8                                | SF2 (IF2)                                                                                                                             |

|       |          | 9                                | SF3 (DF0)                                                                                                                             |

|       |          | 10                               | SF4 (DF1)                                                                                                                             |

|       |          | 11                               | SF5 (DF2)                                                                                                                             |

| 6244  | RMF      |                                  | old – Transfers the contents of the save field register buffer, instruction field buffer, and data field buffer; pt inhibit flip-flop |

| 6254  | SINT     | Skip if user INTerru             | pt flag is set                                                                                                                        |

| 6264  | CUF      | Clear User mode flip             | o-flop and buffer                                                                                                                     |

| 6274  | SUF      | Set User mode buff               | er and set interrupt inhibit flip-flop                                                                                                |

Table 3-3 KT8-A Expanded Instructions

| Instruction   | n        |                                                                                                                                                           |                                                                                                                                                                                                |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Octal         | Mnemonic | Description                                                                                                                                               |                                                                                                                                                                                                |

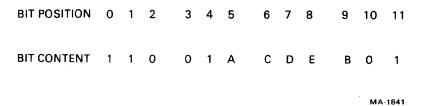

| 6 01X NNN Y01 | CDF      | Change data field as defined by MD bits 5 through 9 and bits EN9 of the extended mode word; the order of significance of the ant field is MD5, 9, 6, 7, 8 |                                                                                                                                                                                                |

|               |          | MD Bit                                                                                                                                                    | Contents                                                                                                                                                                                       |

|               |          | o                                                                                                                                                         | 1                                                                                                                                                                                              |

|               |          | 1                                                                                                                                                         | 1                                                                                                                                                                                              |

|               | ĺ        | 2 3                                                                                                                                                       | 0<br>0                                                                                                                                                                                         |

|               |          | 4                                                                                                                                                         | 1                                                                                                                                                                                              |

|               |          | 5                                                                                                                                                         | во                                                                                                                                                                                             |

|               |          | 6                                                                                                                                                         | FO                                                                                                                                                                                             |

|               |          | 7                                                                                                                                                         | F1                                                                                                                                                                                             |

|               |          | 8 9                                                                                                                                                       | F2<br>B1                                                                                                                                                                                       |

|               |          | 10                                                                                                                                                        | 0                                                                                                                                                                                              |

|               |          | 11                                                                                                                                                        | i                                                                                                                                                                                              |

| 6 01X NNN Y10 | CIF      | Change instruction f<br>bits EN5 and EN9 o<br>inhibit flip-flop                                                                                           | ield buffer as defined by MD bits 5 through 9 and if the extended mode word; also set the interrupt                                                                                            |

|               |          | MD Bit                                                                                                                                                    | Contents                                                                                                                                                                                       |

|               |          | О                                                                                                                                                         | 1                                                                                                                                                                                              |

|               |          | 1                                                                                                                                                         | 1                                                                                                                                                                                              |

|               |          | 2 3                                                                                                                                                       | 0<br>0                                                                                                                                                                                         |

|               |          | 4                                                                                                                                                         | 1                                                                                                                                                                                              |

|               |          | 5                                                                                                                                                         | BO                                                                                                                                                                                             |

|               |          | 6                                                                                                                                                         | FO                                                                                                                                                                                             |

|               |          | 7                                                                                                                                                         | F1                                                                                                                                                                                             |

|               |          | 8<br>9                                                                                                                                                    | F2<br>B1                                                                                                                                                                                       |

|               |          | 10                                                                                                                                                        | 1                                                                                                                                                                                              |

|               |          | 11                                                                                                                                                        | Ö                                                                                                                                                                                              |

| 6 01X NNN Y11 | CDF, CIF | Combination of the (                                                                                                                                      | CDF and CIF instructions                                                                                                                                                                       |

| 6004          | GTF      | GeT Flags – Loads<br>status bits into the A                                                                                                               | the contents of the save field register and CPU<br>AC register as shown below                                                                                                                  |

|               |          | AC Bit                                                                                                                                                    | Contents                                                                                                                                                                                       |

|               |          | 0                                                                                                                                                         | Link                                                                                                                                                                                           |

|               |          | 1                                                                                                                                                         | Greater Than flag                                                                                                                                                                              |

|               |          | 2                                                                                                                                                         | Interrupt bus                                                                                                                                                                                  |

|               |          | 3                                                                                                                                                         | Fatal flip-flop                                                                                                                                                                                |

|               |          | 4<br>5                                                                                                                                                    | Interrupt on<br>Save user mode                                                                                                                                                                 |

|               |          | 6                                                                                                                                                         | Save diser mode Save field bit 0 (IF bit 0)                                                                                                                                                    |

|               |          | 7                                                                                                                                                         | SF1 (IF1)                                                                                                                                                                                      |

| ]             |          | 8                                                                                                                                                         | SF2 (IF2)                                                                                                                                                                                      |

| )             |          | 9                                                                                                                                                         | SF3 (DF0)                                                                                                                                                                                      |

|               |          | 10<br>11                                                                                                                                                  | SF4 (DF1)<br>SF5 (DF2)                                                                                                                                                                         |

| 6005          | RTF      | fer, and data field reg<br>also turns on the into                                                                                                         | ds the link, user mode buffer, instruction field bufgister from the AC register as shown below. RTF errupt system (ION) and sets the interrupt inhibit t JMP or JMS. (Bank bits are unchanged) |

Table 3-3 KT8-A Expanded Instructions (Cont)

| Instru |          |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|----------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Octal  | Mnemonic | Description                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |          | AC Bit                                                                                                            | Contents                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |          | 0                                                                                                                 | Link                                                                                                                                                                                                                                                                                                                                                                                                                        |

|        |          | 1                                                                                                                 | Greater Than flag                                                                                                                                                                                                                                                                                                                                                                                                           |

|        |          | 2                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |          | 3                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| l      |          | 4<br>5                                                                                                            | User Mode buffer                                                                                                                                                                                                                                                                                                                                                                                                            |

|        |          | 6                                                                                                                 | Save field bit 0 (IF bit 0)                                                                                                                                                                                                                                                                                                                                                                                                 |

| į      |          | 7                                                                                                                 | SF1 (IF1)                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        |          | 8                                                                                                                 | SF2 (IF2)                                                                                                                                                                                                                                                                                                                                                                                                                   |