# PDP-9 MAINTENANCE MANUAL VOLUME 1

1st printing March 1967 2nd printing June 1967 3rd printing Nov. 1967 4th printing Feb. 1968 5th printing Aug. 1969 6th printing Nov. 1971 7th printing April 1972

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

COMPUTER LAB

## CONTENTS

# CHAPTER 1 INTRODUCTION

| 1.1    | Scope                                       | 1-1   |

|--------|---------------------------------------------|-------|

| 1.2    | Purpose                                     | 1-1   |

| 1.3    | Physical Description                        | 1-1   |

| 1.4    | Functional Description                      | 1-3   |

| 1.5    | Options                                     | 1-5   |

| 1.6    | Reference Documents and Programs            | 1-5   |

| 1.7    | Reference Conventions                       | 1-5   |

| 1.8    | Terminology                                 | 1-5   |

| 1.9    | Engineering Drawings and Circuit Schematics | 1-7   |

| 1.10   | System Specifications                       | 1-7   |

| 1.10.1 | Dimensions                                  | 1-7   |

| 1.10.2 | Operating Characteristics                   | 1-7   |

| 1.10.3 | Functional Characteristics                  | 1-8   |

|        | CHAPTER 2<br>OPERATION                      |       |

| 2.1    | Scope                                       | 2-1   |

| 2.2    | Standard Controls and Indicators            | 2-1   |

| 2.2.1  | Operator Console                            | 2-1   |

| 2.2.2  | Marginal Check Panel and Maintenance Panel  | 2-4   |

| 2.2.3  | Paper Tape Reader/Punch                     | 2-6   |

| 2.2.4  | Teletype Unit                               | 2-7   |

| 2.2.5  | Power Control 841 A                         | 2-8   |

| 2.2.6  | Core Memory Banks                           | 2-9   |

| 2.3    | Operating Procedures                        | 2-9   |

| 2.3.1  | Manual Data Storage and Modification        | 2-9   |

| 2.3.2  | Storing Binary Data Using READ IN Key       | 2-10  |

| 2.3.3  | Storing Data Under Program Control          | 2-11  |

| 2.3.4  | Assembling Programs                         | 2-11  |

| 2.3.5  | Teletype Code                               | 2-12  |

| 2.3.6  | Local Teletype Operation                    | 2-12  |

| 237    | Maintenance Programs                        | 2_1.2 |

# CHAPTER 3 SYSTEM DESCRIPTION

| 3.1     | Computer Organization                      | 3-1  |

|---------|--------------------------------------------|------|

| 3.1.1   | Central Processor                          | 3-1  |

| 3.1.1.1 | Control Memory (CM)                        | 3-1  |

| 3.1.1.2 | Adder (ADR)                                | 3-1  |

| 3.1.1.3 | Accumulator (AC)                           | 3-1  |

| 3.1.1.4 | AC Link (LINK)                             | 3-5  |

| 3.1.1.5 | Arithmetic Register (AR)                   | 3-5  |

| 3.1.1.6 | Optional Multiplier-Quotient Register (MQ) | 3-5  |

| 3.1.1.7 | Program Counter (PC)                       | 3-5  |

| 3.1.1.8 | Instruction Register (IR)                  | 3-5  |

| 3.1.1.9 | Memory Buffer Register (MB)                | 3-5  |

| 3.1.2   | Core Memory System                         | 3-6  |

| 3.1.2.1 | Direct Addressing                          | 3-7  |

| 3.1.2.2 | Indirect Addressing                        | 3-7  |

| 3.1.2.3 | Autoindexing                               | 3-7  |

| 3.1.2.4 | Extend Mode Addressing                     | 3-8  |

| 3.1.3   | I/O Control                                | 3-8  |

| 3.2     | Instruction Word Formats                   | 3-8  |

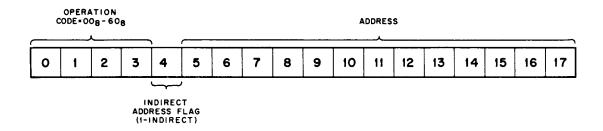

| 3.2.1   | Memory Reference Instructions              | 3-9  |

| 3.2.2   | Augmented Instructions                     | 3-9  |

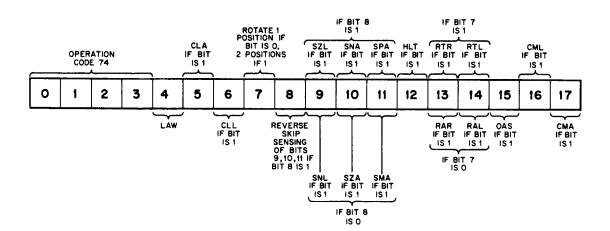

| 3.2.2.1 | Operate                                    | 3-9  |

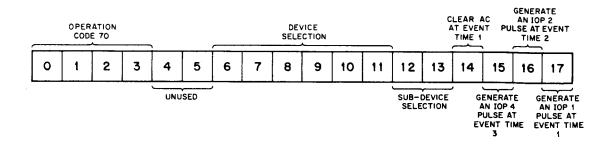

| 3.2.2.2 | Input/Output Transfer                      | 3-9  |

| 3.2.2.3 | Optional EAE                               | 3-10 |

| 3.3     | Data Formats                               | 3-11 |

| 3.3.1   | Sign and Magnitude Notation                | 3-11 |

| 3.3.2   | Complement Notations                       | 3-11 |

| 3.3.3   | Data Words                                 | 3-13 |

| 3.3.3.1 | Magnitude of Data Words                    | 3-14 |

| 3.3.3.2 | Floating-Point Formats                     | 3-14 |

| 3.3.4   | Scaling                                    | 3-15 |

| 3.4     | Control Memory System                      | 3-16 |

| 3.4.1          | Organization                            | 3-16 |

|----------------|-----------------------------------------|------|

| 3.4.2          | Timing and Control                      | 3-18 |

| 3.4.3          | Control Memory MC09A                    | 3-19 |

| 3.4.4          | Address Selectors G210                  | 3-19 |

| 3.4.5          | Current Sources                         | 3-20 |

| 3.5            | Central Processor Logic                 | 3-20 |

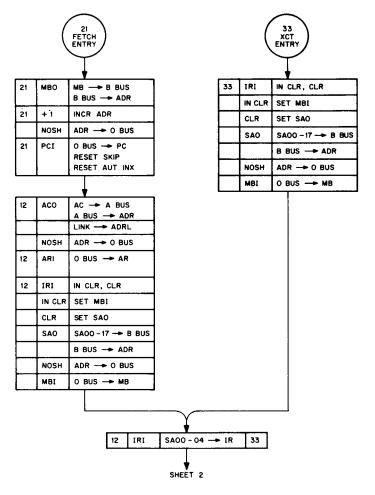

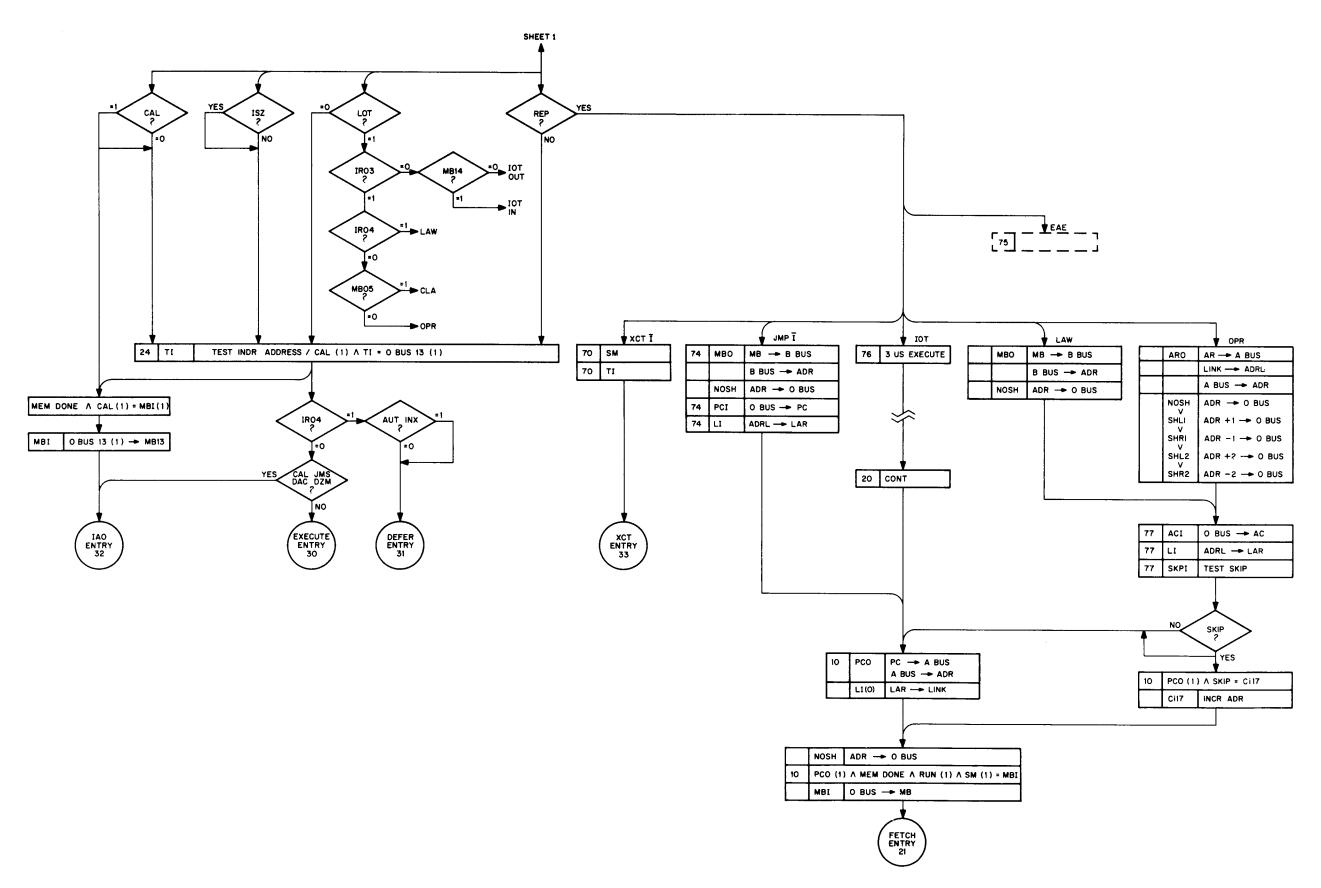

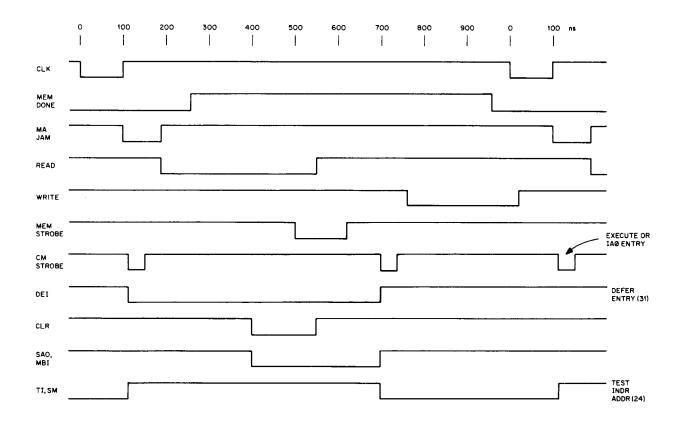

| 3.5.1          | Fetch Cycle                             | 3-20 |

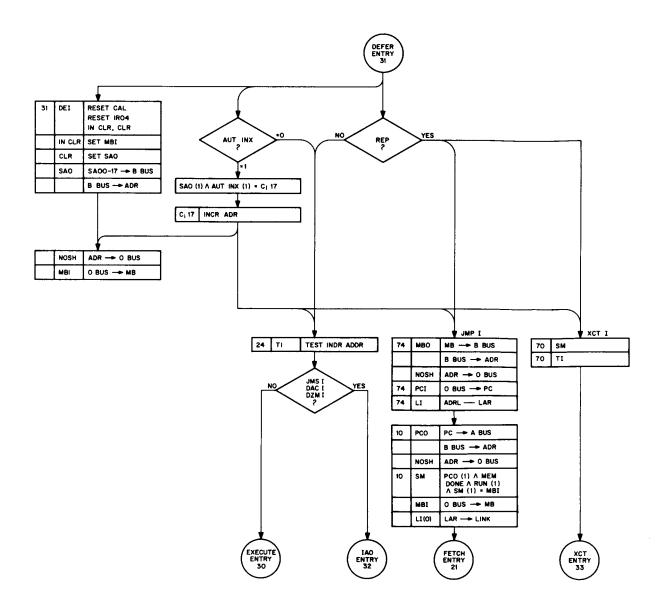

| 3.5.2          | Defer Cycle                             | 3-26 |

| 3.5.3          | Autoindexing                            | 3-28 |

| 3.5.4          | IA0 Cycle                               | 3-29 |

| 3.5.5          | Execute Cycle                           | 3-29 |

| 3.5.6          | Memory Reference Instructions           | 3-31 |

| 3.5.6.1        | 1s Complement Add (ADD)                 | 3-31 |

| 3.5.6.2        | Logical AND (AND)                       | 3-33 |

| 3.5.6.3        | Call Subroutine (CAL)                   | 3-34 |

| 3.5.6.4        | Deposit Accumulator (DAC)               | 3-36 |

| 3.5.6.5        | Deposit Zero in Memory (DZM)            | 3-37 |

| 3.5.6.6        | Increment and Skip if Zero (ISZ)        | 3-38 |

| 3.5.6.7        | Jump (JMP)                              | 3-39 |

| 3.5.6.8        | Jump to Subroutine (JMS)                | 3-40 |

| 3.5.6.9        | Load the Accumulator (LAC)              | 3-41 |

| 3.5.6.10       | Skip if AC Differs (SAD)                | 3-42 |

| 3.5.6.11       | 2s Complement Add (TAD)                 | 3-43 |

| 3.5.6.12       | Execute (XCT)                           | 3-44 |

| 3.5.6.13       | Exclusive OR (XOR)                      | 3-45 |

| 3 <b>.</b> 5.7 | Operate (OPR) Instructions              | 3-46 |

| 3.5.7.1        | No Operation (NOP)                      | 3-47 |

| 3.5.7.2        | Complement the Accumulator (CMA)        | 3-47 |

| 3.5.7.3        | Complement the LINK (CML)               | 3–48 |

| 3.5.7.4        | Inclusive OR the AC/DATA Switches (OAS) | 3-48 |

| 3.5.7.5        | Rotate One Position Left (RAL)          | 3-49 |

| 3.5.7.6        | Rotate One Position Right (RAR)         | 3-49 |

| 3.5.7.7        | Halt Program (HLT)                      | 3-50 |

| 3.5.7.8  | Skip on Minus Accumulator (SMA)                    | 3-50          |

|----------|----------------------------------------------------|---------------|

| 3.5.7.9  | Skip on Zero Accumulator (SZA)                     | 3-50          |

| 3.5.7.10 | Skip on Non-Zero LINK (SNL)                        | 3-51          |

| 3.5.7.11 | Unconditional Skip (SKP)                           | 3-52          |

| 3.5.7.12 | Skip on Positive Accumulator (SPA)                 | 3-52          |

| 3.5.7.13 | Skip on Non-Zero Accumulator (SNA)                 | 3-53          |

| 3.5.7.14 | Skip on Zero LINK (SZL)                            | 3-53          |

| 3.5.7.15 | Rotate Two Positions Left (RTL)                    | 3-54          |

| 3.5.7.16 | Rotate Two Positions Right (RTR)                   | 3-54          |

| 3.5.7.17 | Clear the LINK (CLL)                               | 3-55          |

| 3.5.7.18 | Set the LINK (STL)                                 | 3-55          |

| 3.5.7.19 | Clear the LINK and Rotate One Position Left (RCL)  | 3-55          |

| 3.5.7.20 | Clear the LINK and Rotate One Position Right (RCR) | 3-56          |

| 3.5.7.21 | Clear the Accumulator (CLA)                        | 3-56          |

| 3.5.7.22 | Clear and Complement the Accumulator (CLC)         | 3-56          |

| 3.5.7.23 | Load AC from DATA Switches (LAS)                   | 3-56          |

| 3.5.7.24 | Get the LINK Content (GLK)                         | 3-56          |

| 3.5.7.25 | Load the Accumulator with 76XXXX (LAW)             | 3-57          |

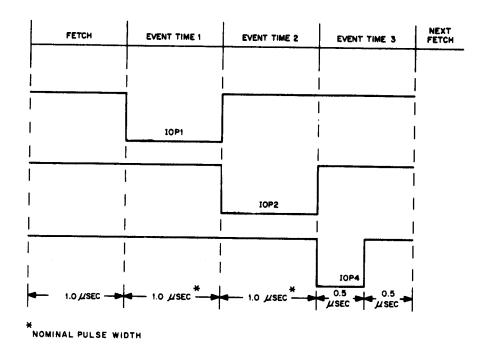

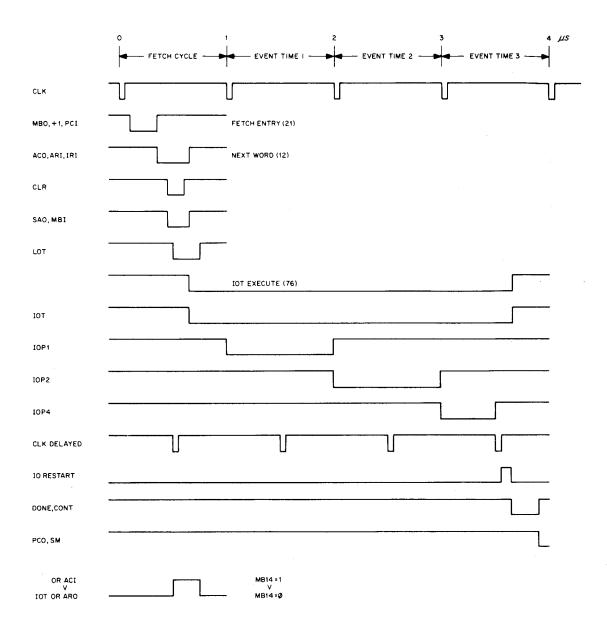

| 3.5.8    | Input/Output Transfer (IOT) Instructions           | 3-57          |

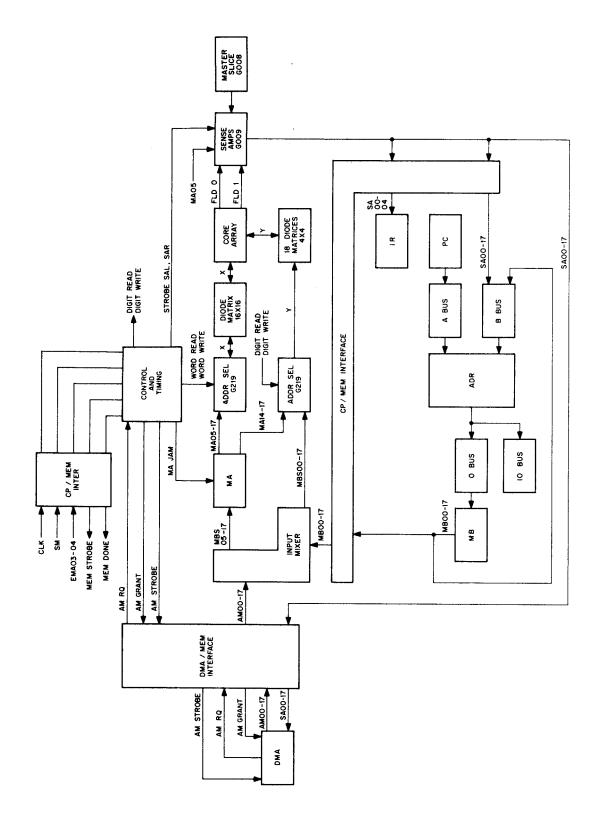

| 3.6      | Core Memory System                                 | 3-60          |

| 3.6.1    | Organization                                       | 3-60          |

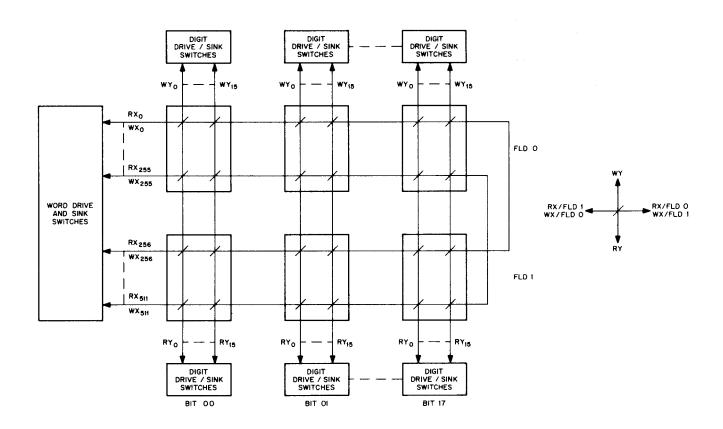

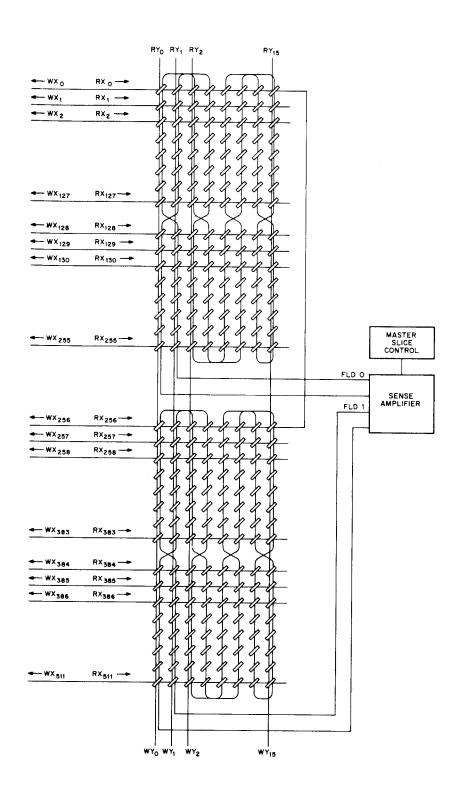

| 3.6.2    | Core Array and Field Selection                     | 3-60          |

| 3.6.3    | Control and Timing                                 | 3-63          |

| 3.6.4    | Address Selectors G219                             | 3-68          |

| 3.6.4.1  | Digit Drive Selection                              | 3-69          |

| 3.6.4.2  | Word Drive Selection                               | 3-69          |

| 3.6.5    | Core Sensing Circuits                              | 3-72          |

| 3.6.6    | Current Sources                                    | 3-73          |

| 3.6.6.1  | Control Module G804                                | 3-74          |

| 3.6.6.2  | Negative Regulator G805                            | 3-74          |

| 3.6.6.3  | Resistor Boards G622                               | 3-74          |

| 3.7      | Manual Control                                     | 3-75          |

| 3.7.1    | Primary Power Distribution                         | 3 <b>-</b> 75 |

| 3.7.2          | Power Supplies                   | 3-75 |

|----------------|----------------------------------|------|

| 3.7.3          | Main Clock                       | 3-76 |

| 3.7.4          | Manual Controls                  | 3-77 |

| 3.7.4.1        | Power Turn-On                    | 3-77 |

| 3.7.4.2        | START Key                        | 3-78 |

| 3.7.4.3        | PROGRAM STOP Key                 | 3-80 |

| 3.7.4.4        | CONTINUE Key                     | 3-80 |

| 3.7.4.5        | DEPOSIT                          | 3-81 |

| 3.7.4.6        | DEPOSIT NEXT                     | 3-83 |

| 3.7.4.7        | EXAMINE                          | 3-84 |

| 3.7.4.8        | EXAMINE NEXT                     | 3-84 |

| 3.7.4.9        | READ IN Key                      | 3-85 |

| 3.7.4.10       | I/O RESET Key                    | 3-89 |

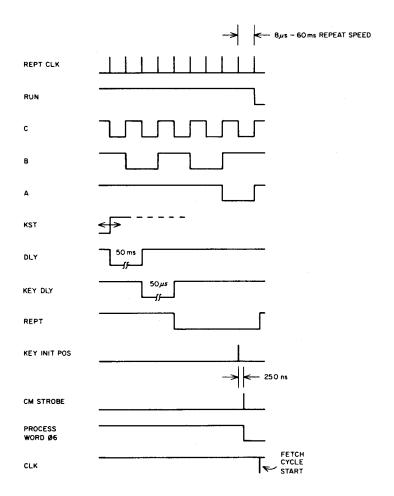

| 3.7.4.11       | REPT and REPEAT SPEED Switches   | 3-89 |

| 3.7.4.12       | SING INST and SING STEP Switches | 3-90 |

| 3.7.4.13       | CLK Switch                       | 3-90 |

| 3.7.4.14       | Other Controls                   | 3-90 |

| 3.7.5          | Display Indicators               | 3-91 |

| 3.7.5.1        | REGISTER Indicator               | 3-91 |

| 3.7.5.2        | LINK Indicator                   | 3-92 |

| 3.7.5.3        | MEMORY BUFFER Indicator          | 3-92 |

| 3.7.5.4        | INSTRUCTION Indicator            | 3-92 |

| 3.7.5.5        | PIE Indicator                    | 3-93 |

| 3.7.5.6        | CLK Indicator                    | 3-93 |

| 3.7.5.7        | SING STEP Indicator              | 3-93 |

| 3.7.5.8        | SING INST Indicator              | 3-93 |

| 3.7.5.9        | REPT Indicator                   | 3-93 |

| 3.7.5.10       | PRGM STOP Indicator              | 3-93 |

| 3.7.5.11       | DATA Indicator                   | 3-94 |

| 3.7.5.12       | Other Indicators                 | 3-94 |

| 3.7.6          | Marginal Check Panel             | 3-94 |

| 3 <b>.7.</b> 7 | Maintenance Panel                | 3–95 |

| 3.7.7.1        | NORMAL                           | 3-95 |

| 3.7.7.2 | LOCK                              | 3-96  |

|---------|-----------------------------------|-------|

| 3.7.7.3 | MAINT                             | 3-96  |

| 3.7.7.4 | EXAMINE                           | 3-98  |

| 3.7.7.5 | DEPOSIT                           | 3-98  |

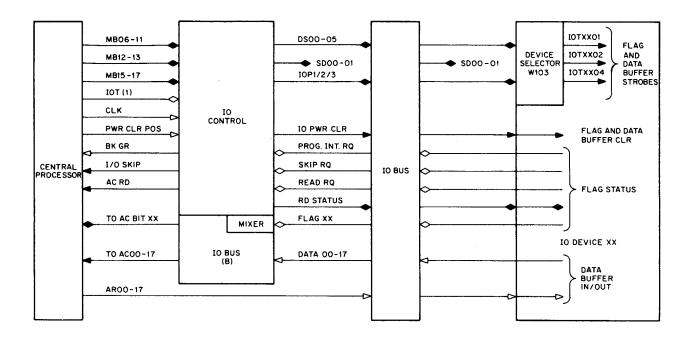

| 3.8     | I/O CONTROL                       | 3-98  |

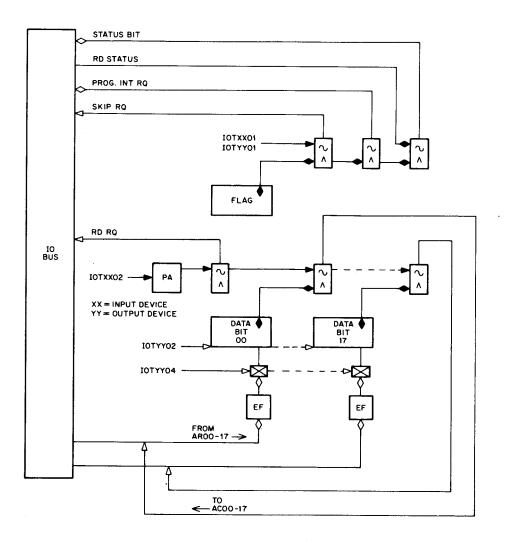

| 3.8.1   | Program-Controlled Data Transfers | 3-99  |

| 3.8.1.1 | I/O Bus Connections               | 3-100 |

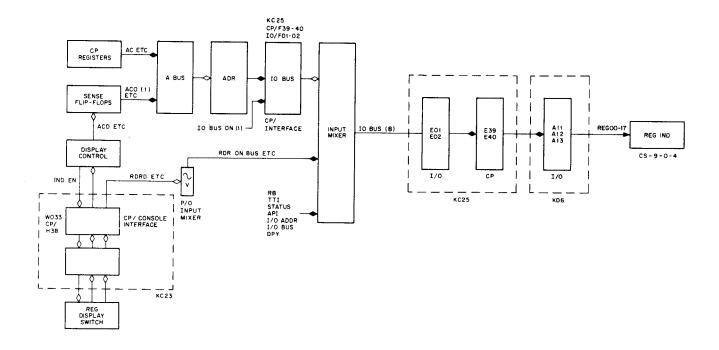

| 3.8.1.2 | Block Diagram Discussion          | 3-100 |

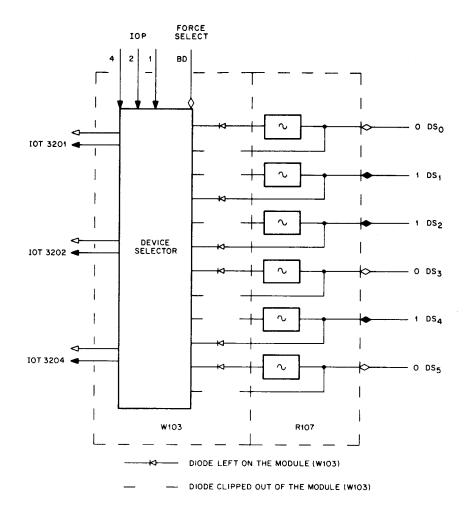

| 3.8.1.3 | Device Selector W103              | 3-103 |

| 3.8.1.4 | Input Transfers                   | 3-103 |

| 3.8.1.5 | Output Transfers                  | 3-105 |

| 3.8.1.6 | I/O Skip Facility                 | 3-105 |

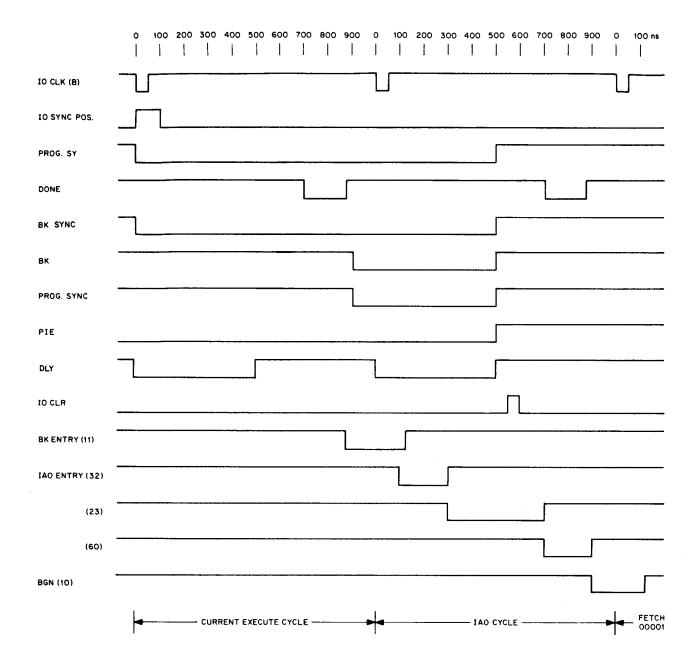

| 3.8.1.7 | Program Interrupt Facility        | 3-106 |

| 3.8.1.8 | I/O Status Check Facility         | 3-110 |

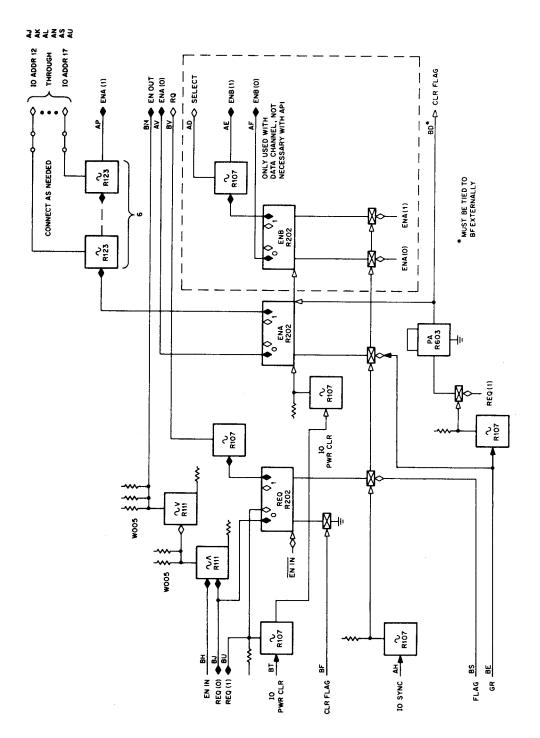

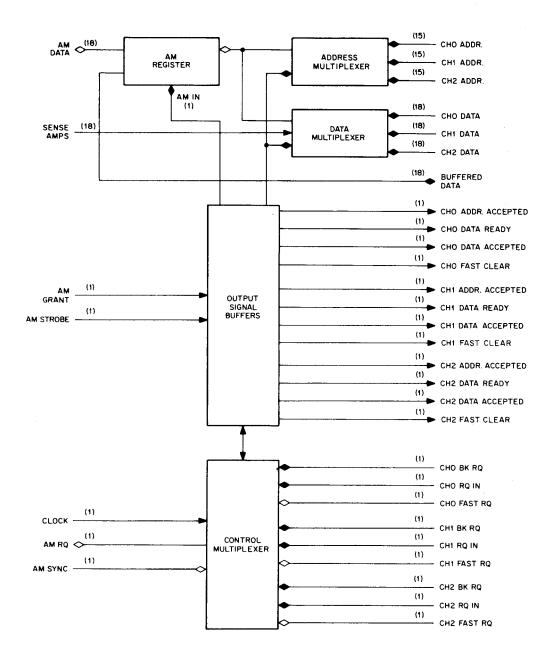

| 3.8.2   | Data Channel Transfers            | 3-111 |

| 3.8.2.1 | I/O Bus Connections               | 3-114 |

| 3.8.2.2 | Multiplexer W104                  | 3-114 |

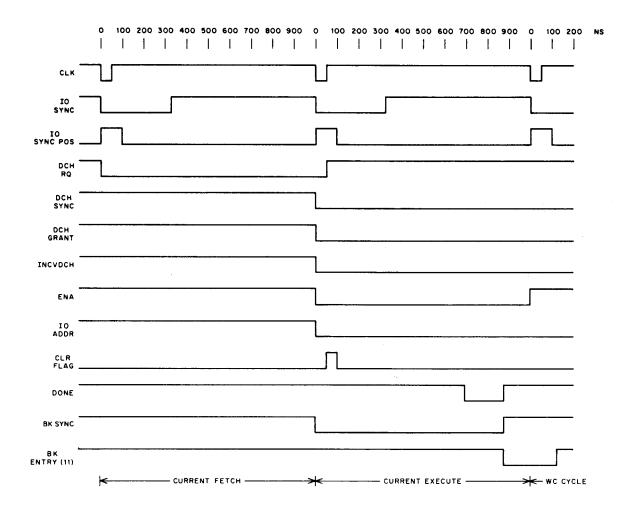

| 3.8.2.3 | Break Synchronization             | 3-114 |

| 3.8.2.4 | WC Cycle                          | 3-117 |

| 3.8.2.5 | CA Cycle                          | 3-118 |

| 3.8.2.6 | Data Input Cycle                  | 3-119 |

| 3.8.2.7 | Data Output Cycles                | 3-120 |

| 3.8.2.8 | Add-to-Memory Facility            | 3-121 |

| 3.8.3   | DMA Channel Transfers             | 3-122 |

| 3.8.3.1 | Interface Connections             | 3-122 |

| 3.8.3.2 | Transfer Operations               | 3-123 |

| 3.8.4   | API Channel Transfers             | 3-125 |

| 3.8.5   | Transfer Priorities               | 3-126 |

| 3.9     | Basic I/O Device Control          | 3-126 |

| 3.9.1   | Teletype                          | 3-126 |

| 3.9.1.1 | Keyboard Control                  | 3-127 |

| 3.9.1.2 | Transfer to AC                    | 3-129 |

| 3.9.1.3 | Skip on Keyboard Flag             | 3-130 |

| 3.9.1.4 | Clear Teleprinter Flag and Load the Buffer | 3-130                  |

|---------|--------------------------------------------|------------------------|

| 3.9.1.5 | Skip on Teleprinter Flag                   | 3-132                  |

| 3.9.1.6 | LINE/OFF/LOCAL Switch                      | 3-132                  |

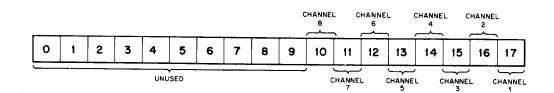

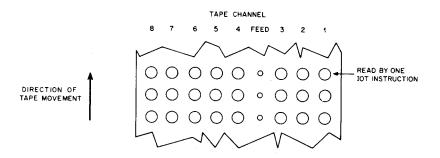

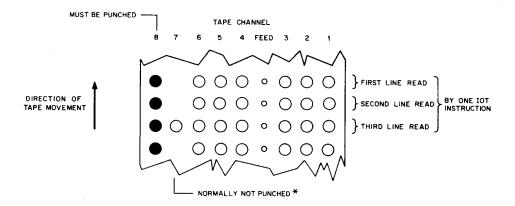

| 3.9.2   | Tape Reader                                | 3-132                  |

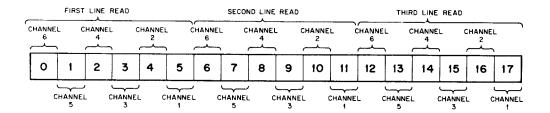

| 3.9.2.1 | Select Reader Binary                       | 3-133                  |

| 3.9.2.2 | Select Reader Alpha                        | 3-136                  |

| 3.9.2.3 | Transfer to AC                             | 3-137                  |

| 3.9.2.4 | Skip on Reader Flag                        | 3 <b>-</b> 1 <i>37</i> |

| 3.9.2.5 | Reader No Tape Logic                       | 3-138                  |

| 3.9.2.6 | FEED Button                                | 3-138                  |

| 3.9.3   | Tape Punch                                 | 3–138                  |

| 3.9.3.1 | Select Punch Binary                        | 3-139                  |

| 3.9.3.2 | Select Punch Alpha                         | 3-141                  |

| 3.9.3.3 | Skip on Punch Flag                         | 3-141                  |

| 3.9.3.4 | Clear Punch Flag                           | 3-141                  |

| 3.9.3.5 | Clear AC, Clear Flag, and Select Punch     | 3-141                  |

| 3.9.3.6 | POWER Button and TAPE Switch               | 3-141                  |

| 3.9.3.7 | FEED Button                                | 3-142                  |

| 3.9.4   | Real-Time Clock                            | 3-142                  |

|         | CHAPTER 4<br>MAINTENANCE                   |                        |

| 4.1     | Maintenance Philosophy                     | 4-1                    |

| 4.2     | Tools and Test Equipment                   | 4-1                    |

| 4.3     | Module Handling                            | 4-2                    |

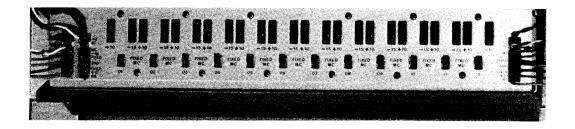

| 4.4     | Marginal Check Switches                    | 4-2                    |

| 4.5     | Preventive Maintenance                     | 4-3                    |

| 4.5.1   | Mechanical Checks                          | 4-3                    |

| 4.5.2   | Power Supply Checks                        | 4-4                    |

| 4.5.3   | Core Memory Current Check                  | 4-5                    |

| 4.5.4   | Sense Amplifier Check                      | 4-5                    |

| 4.6     | Corrective Maintenance                     | 4-5                    |

| 4.6.1   | Marginal Checking with Diagnostic Programs | 4-6                    |

| 4.6.2   | System Troubleshooting                     | 4-1                    |

| 4.6.2.1  | Memory Troubleshooting                     | 4-11 |

|----------|--------------------------------------------|------|

| 4.6.2.2  | 2 Logic Troubleshooting                    |      |

| 4.6.2.3  | .2.3 Signal Tracing                        |      |

| 4.6.2.4  | Aggravation Tests                          | 4-13 |

| 4.6.3    | Circuit Troubleshooting                    | 4-13 |

| 4.6.3.1  | In-Line Dynamic Tests                      | 4-13 |

| 4.6.3.2  | In-Line Marginal Checks                    | 4-13 |

| 4.6.3.3  | Static Bench Tests                         | 4-14 |

| 4.6.3.4  | Dynamic Bench Tests                        | 4-15 |

| 4.6.4    | Tape Reader Adjustments                    | 4-16 |

| 4.6.4.1  | Solenoid Drivers                           | 4-16 |

| 4.6.4.2  | Photo Amplifier                            | 4-16 |

| 4.6.4.3  | Clock and Accelerator                      | 4-17 |

| 4.6.4.4  | Mechanical Adjustments                     | 4-17 |

| 4.6.5    | Module Repair                              |      |

| 4.7      | Replacement Modules                        | 4-17 |

| Appendix |                                            |      |

| Α        | Option List                                | A-1  |

| В        | Basic Instruction Repertoire               | B-1  |

|          | ILLUSTRATIONS                              |      |

| 1-1      | Programmed Data Processor PDP-9            | 1-2  |

| 1-2      | Basic PDP–9 Layout, Front and Rear         | 1-3  |

| 1-3      | PDP-9 System Configuration, Block Diagram  |      |

| 2-1      | Operator Console                           | 2-1  |

| 2-2      | Marginal Check Panel and Maintenance Panel |      |

| 2-3      | Paper Tape Reader/Punch PC09               |      |

| 2-4      | KSR 33 Teletype Unit                       | 2-7  |

| 2-5      | Power Control 841A                         | 2-8  |

| 3-1      | System Block Diagram, Basic PDP-9          | 3-3  |

| 3-2      | Memory Reference Instruction Word Format   | 3-8  |

| 3-3      | OPR Instruction Word Format                |      |

# ILLUSTRATIONS (cont)

| 3-4  | IOT Instruction Word Format              | 3-10         |

|------|------------------------------------------|--------------|

| 3-5  | IOT Instruction Cycles                   | 3-11         |

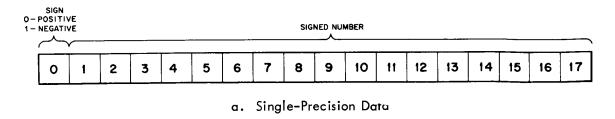

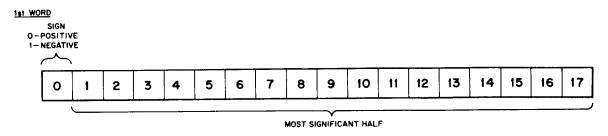

| 3-6  | Data Word Format                         | 3-13         |

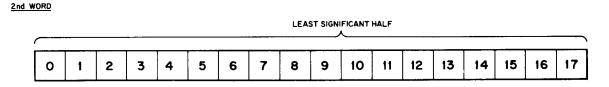

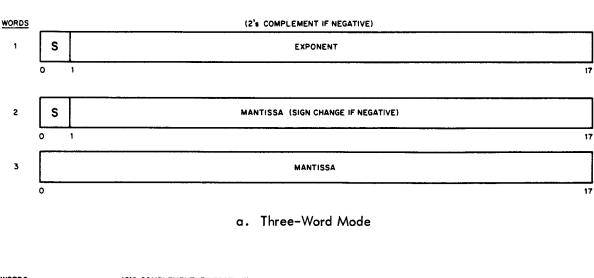

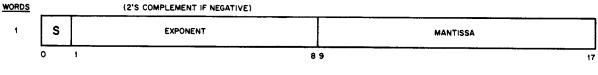

| 3-7  | Floating Point Data Format               | 3-15         |

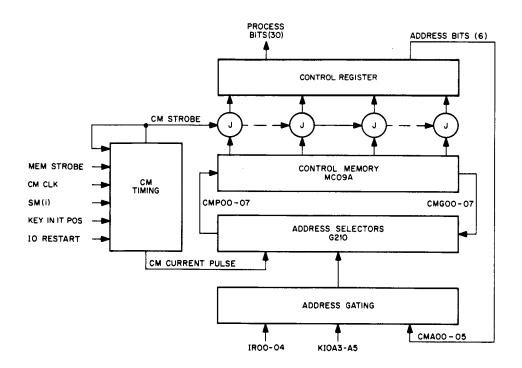

| 3-8  | Control Memory System, Block Diagram     | 3-17         |

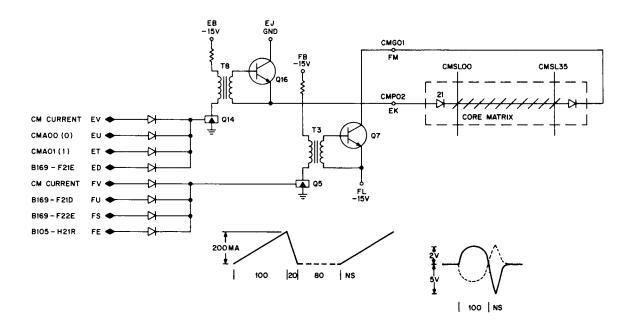

| 3-9  | CM Line Selection, Line 21               | 3-19         |

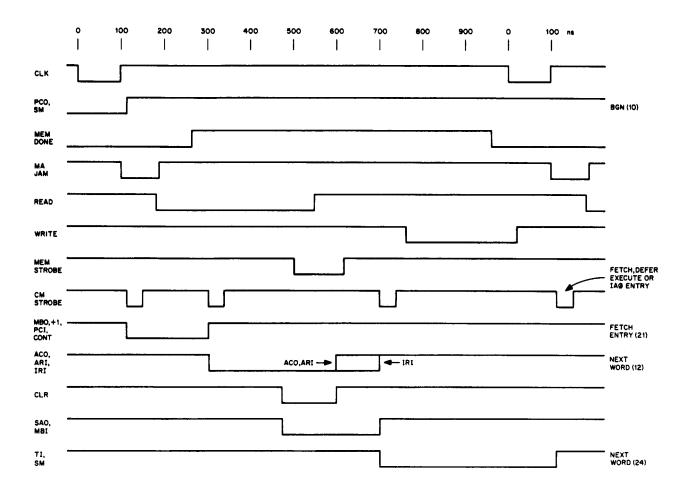

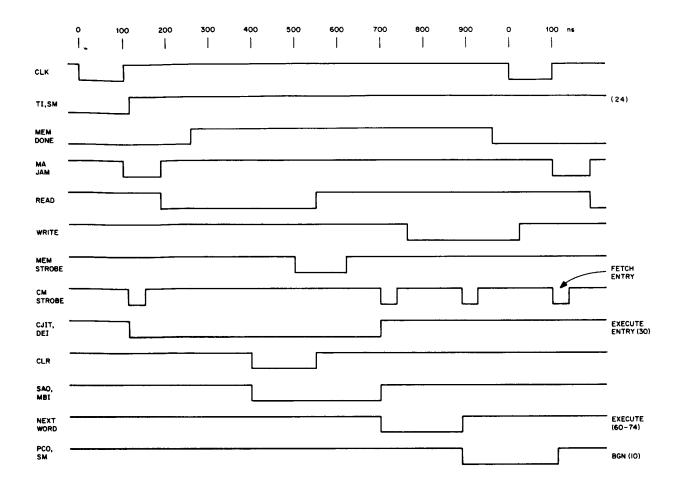

| 3-10 | Fetch Cycle Timing                       | 3-21         |

| 3-11 | Fetch Cycle Flow, Sheet 1<br>Sheet 2     | 3-22<br>3-23 |

| 3-12 | Defer Cycle Timing                       | 3-27         |

| 3-13 | Defer Cycle Flow                         | 3-28         |

| 3-14 | Execute Cycle Timing                     | 3-30         |

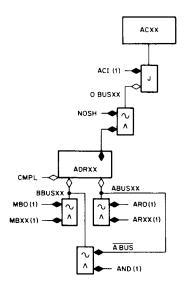

| 3-15 | AND Logic                                | 3-34         |

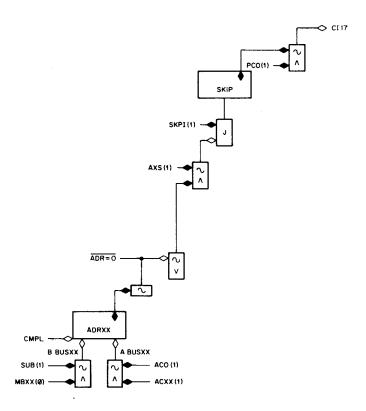

| 3-16 | SAD Logic                                | 3-43         |

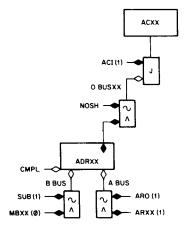

| 3-17 | XOR Logic                                | 3-45         |

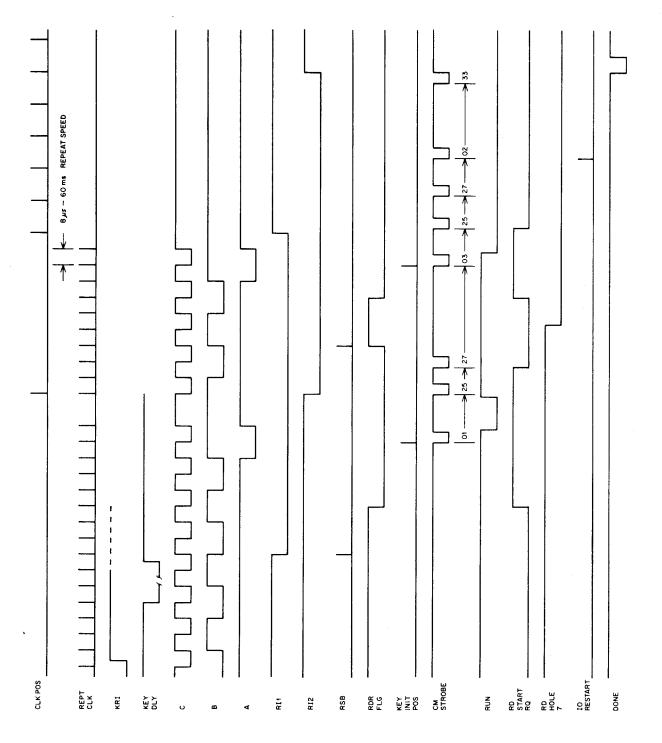

| 3-18 | IOT Timing                               | 3-58         |

| 3-19 | Core Memory System Block Diagram         | 3-61         |

| 3-20 | Planar Array Wiring                      | 3-62         |

| 3-21 | Core Wiring for One Bit Position         | 3-64         |

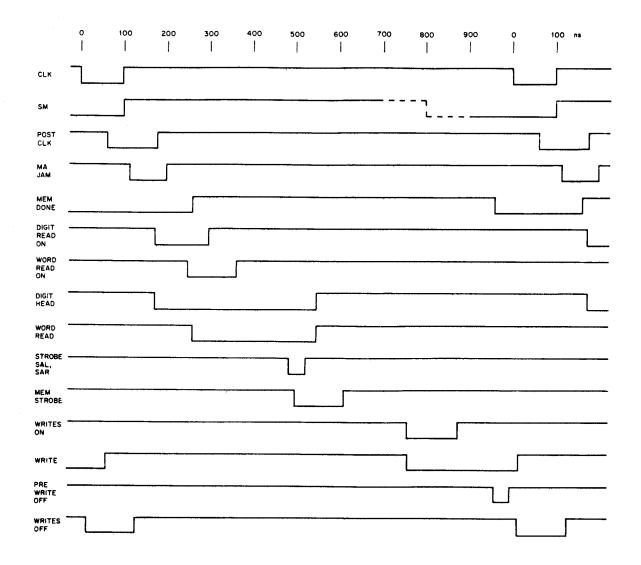

| 3-22 | Core Memory Read/Write Timing            | 3-65         |

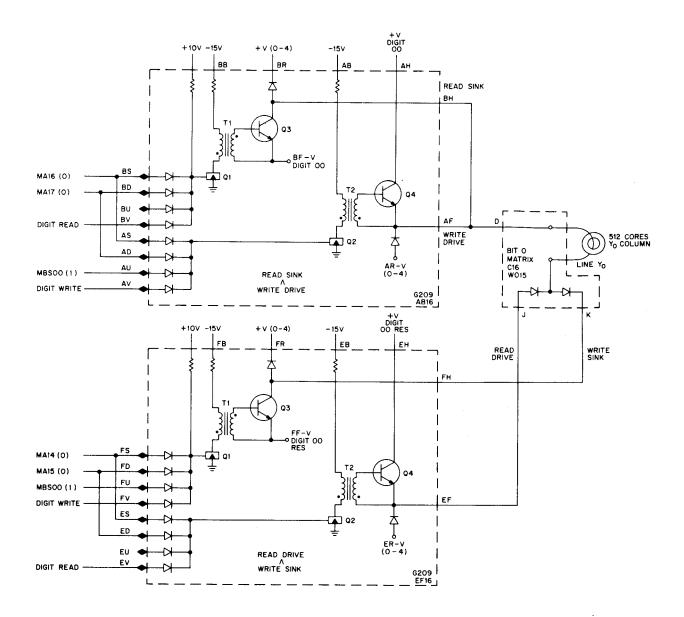

| 3-23 | Digit Drive Selection, Bit O, Line Y     | 3-70         |

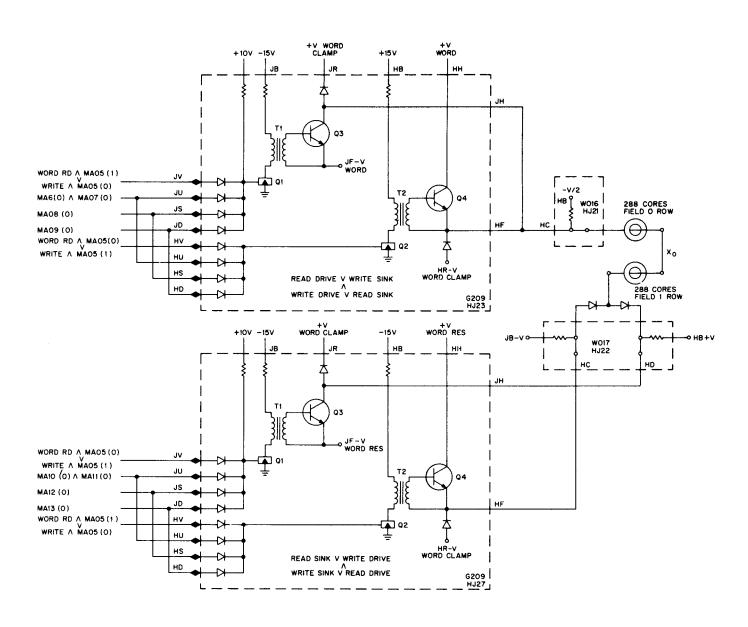

| 3-24 | Word Drive Selection, Line X             | 3-71         |

| 3-25 | Program START Timing                     | 3–78         |

| 3-26 | Initial Set-up DEPOSIT or EXAMINE Timing | 3-82         |

| 3-27 | READ IN Mode Timing                      | 3-86         |

| 3-28 | REGISTER DISPLAY Signal Paths            | 3-92         |

| 3-29 | Program-Controlled I/O Interface         | 3-101        |

| 3-30 | I/O Device Control Logic                 | 3-102        |

| 3-31 | Device Selector W103, Schematic Diagram  | 3-104        |

| 3-32 | Program Interrupt Timing                 | 3-108        |

| 3-33 | Multiplexer W104, Logic Diagram          | 3-115        |

| 3-34 | DCH Break Synchronization                | 3-116        |

# ILLUSTRATIONS (cont)

| 3-35 | Adapter/Multiplexer DM09A, Block Diagram                       | 3-124 |

|------|----------------------------------------------------------------|-------|

| 3-36 | Paper Tape and Reader Buffer Formats                           | 3-134 |

| 4-1  | Marginal Check Switches                                        | 4-3   |

|      | TABLES                                                         |       |

| 1-1  | Related Documents                                              | 1-8   |

| 1-2  | System Program Tapes                                           | 1-9   |

| 1-3  | Maintenance Program Tapes                                      | 1-9   |

| 2-1  | Operator Console, Controls and Indicators                      | 2-2   |

| 2-2  | Marginal Check and Maintenance Panels, Controls and Indicators | 2-5   |

| 2-3  | Tape Reader/Punch, Controls and Indicators                     | 2-7   |

| 2-4  | Teletype Controls                                              | 2-7   |

| 2-5  | Power Control 841A, Controls and Indicators                    | 2-9   |

| 2-6  | Read-In Mode (RIM) Loader Program                              | 2-10  |

| 3-1  | Reserved Core Memory Locations                                 | 3-6   |

| 3-2  | Complementary Numbers                                          | 3-13  |

| 3-3  | I/O Status Bit Assignments                                     | 3-110 |

| 3-4  | Teletype Code (ASCII)                                          | 3-128 |

| 4-1  | Tools and Test Equipment                                       | 4-1   |

| 4-2  | Power Supply Output Checks                                     | 4-4   |

# CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This manual provides operation and maintenance information for the Programmed Data Processor PDP-9, manufactured by Digital Equipment Corporation, Maynard, Massachusetts. The manual consists of two volumes, Volume I containing Chapters 1 through 4, and Volume II containing Chapter 5. Volume I describes the basic computer system (Chapter 1) and discusses the logic circuits in terms of the computer's instruction repertoire (Chapter 3). Manual operations (Chapter 2) and maintenance considerations (Chapter 4) are also included. Volume II contains a complete set of engineering drawings for the basic computer system; customer-ordered options are treated in separate option instruction manuals.

#### 1.2 PURPOSE

This manual is one of several documents related to the PDP-9. It provides the user with a basic understanding of the system capabilities. The levels of discussion assume that the user is familiar with the technology of similar computer systems. For complete and comprehensive coverage in his area of interest, the user should refer to the documents listed in Table 1-1 at the end of this chapter.

#### 1.3 PHYSICAL DESCRIPTION

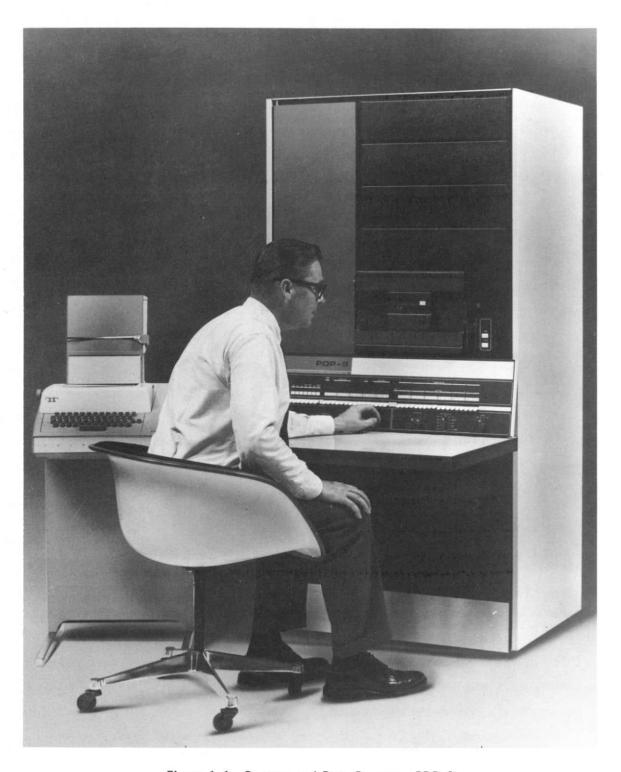

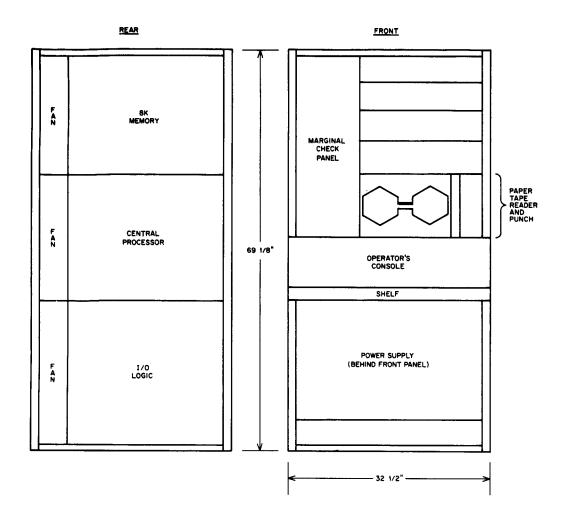

With the exception of the KSR 33 Teletype Unit, the basic PDP-9 (Figure 1-1) is self-contained in a single DEC Type CAB-31 metal cabinet. Four casters permit cabinet mobility. No special power sources, air conditioning or floor bracing are required. The teletype unit is supplied with its own mounting stand. Figure 1-2 shows the front and rear dimensional views of the PDP-9 layout.

Logic modules are mounted in three wings at the rear of the cabinet. These wings, each measuring approximately 22 in. by 30 in., swing out as a single door for module access. The wings also include self-contained cooling fans and marginal-check switches. The top wing holds the 8,192-word core memory system, the middle wing the central processor, and the bottom wing the I/O control section. Each wing has its own switched power-distribution system at the marginal-check switches on the fan housings.

Several commonly-purchased options are prewired into the wings. The core memory wing contains memory parity provisions for use with an optional 19-bit core stack. The central processor wing is prewired for the extended arithmetic element option. The I/O control wing is prewired for the DEC Type 34H Oscilloscope Display Control, the automatic priority interrupt, and the power failure

detection options. Control logic for memory extension, memory parity, and memory protection options is housed in two mounting panels above the paper tape reader/punch. Two remaining panels above these house the DMA multiplexer option.

Figure 1-1 Programmed Data Processor PDP-9

Figure 1-2 Basic PDP-9 Layout, Front and Rear

#### 1.4 FUNCTIONAL DESCRIPTION

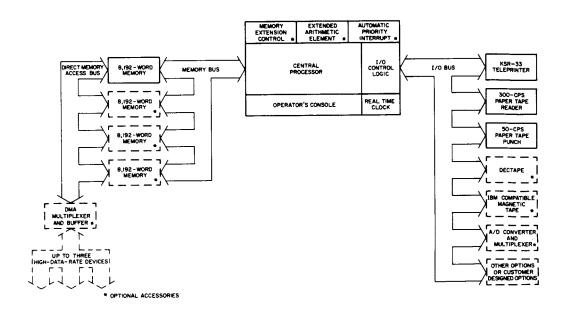

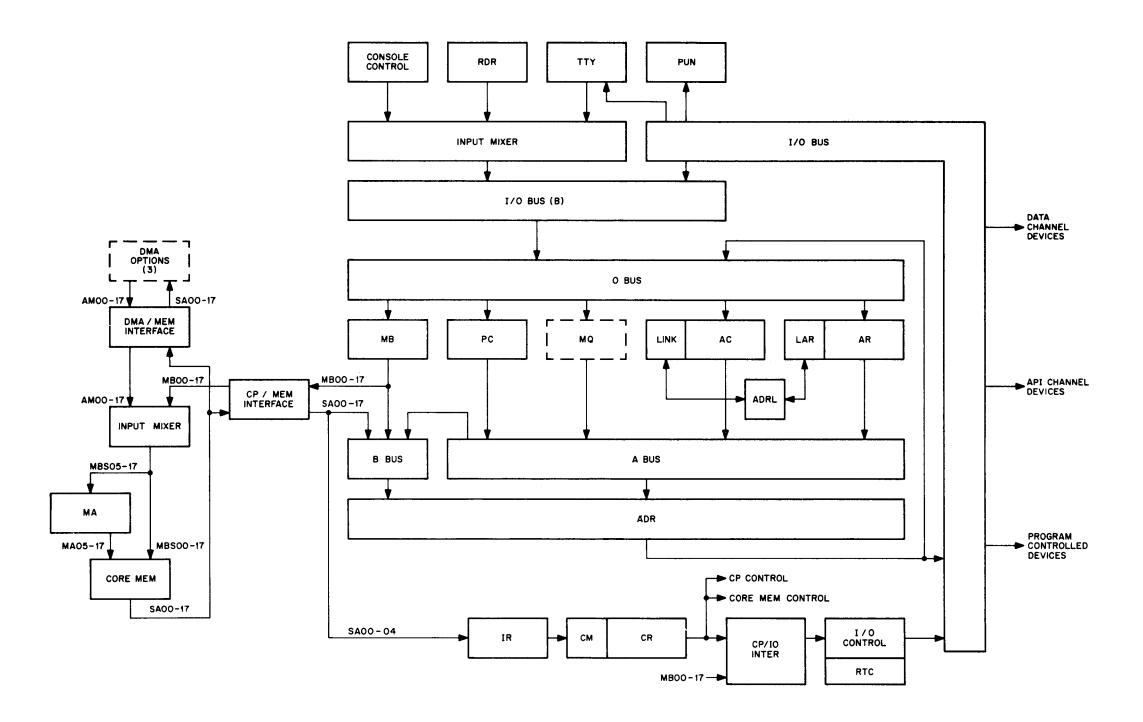

The PDP-9 (Figure 1-3) is a general-purpose, solid-state digital computer designed for data handling in a scientific laboratory, a computation center, or in a real-time process control system. The system is a single-address, 18-bit computer using 1s complement arithmetic which is program-convertible to 2s complement notation to facilitate multiple-precision operations. Indirect addressing to one level and autoindexing features afford programming flexibility. The 8,192-word core memory provides random-access to any word within 1 µs.

The I/O bus system accommodates up to 64 low-speed peripheral devices under program control, up to 8 high-speed devices optionally multiplexed in 8 device-controlled data channels (DCH), and up to 28 devices in an optional 32-channel automatic priority interrupt (API) system. The program-controlled transfer system includes the Teletype, the paper tape reader, the paper tape punch, and the real-time clock as basic furnished equipment. Program-controlled transfer operations include program

interrupt (PI), I/O skip, and I/O status checking facilities. The real-time clock (RTC) is located in the I/O control section of the computer. When turned on, the RTC permits programming of long delays by incrementing a counter in core memory 60 times per second (50 times for 50-cycle powered machines). A program interrupt occurs when the preset count is reached.

Figure 1-3 PDP-9 System Configuration, Block Diagram

The memory bus provides for the addition of up to three memory expansion modules for a total of 32,768 words of memory. The direct memory access (DMA) bus permits direct access to core memory on a cycle-stealing basis for up to three extremely fast (up to 1,000,000 wps) peripheral devices via the DMA channel.

Two DEC Type 709 Power Supplies produce all required dc operating voltages from a single source of 120V or 240V, 60-cycle, single-phase power. The supply input transformers can be tapped for operation with 50-cycle power. The supplies provide +10V and -15V for use throughout the basic PDP-9 system; one supply also provides -30V to the core memory system, and the other provides +10V and -30V to the paper tape punch. A variable 0 to 20V output checks the operation of the computer under marginal power supply limits. By substituting this output for the normal +10V and -15V outputs, the technician can rapidly troubleshoot an existing fault or forecast a future system failure.

Input ac power to the supplies is controlled from a DEC Type 841A Power Control Unit attached to one of the supplies. The 841A contains the ac input power receptacle and associated circuit breaker. The console POWER switch must be ON for application of ac power to the supplies.

#### 1.5 OPTIONS

Appendix A lists all central processor, core memory, and I/O options available for use with the basic PDP-9. Separate manuals on specific options are supplied per individual customer purchases.

#### 1.6 REFERENCE DOCUMENTS AND PROGRAMS

Tables 1-1 through 1-3 at the end of this chapter list the standard documents and program tapes supplied with the basic PDP-9. Others may be furnished as appropriate to customer requirements.

#### 1.7 REFERENCE CONVENTIONS

In the interest of effective text presentation and readability this manual observes certain reference conventions noted below.

- a. Numerical Notation Unless otherwise indicated, all binary number representations are in octal notation.

- b. Circuit References All references to logic signals include the module type designation, module location code, and output pin designation; viz., Pulse Amplifier B602-E26D means that module B602 is located in rack E, slot 26, and the output signal is taken from pin D. All racks are designated alphabetically from left to right as viewed from the module mounting side. All module mounting slots are numbered 01 through 40 from top to bottom. Modules are mounted horizontally in the slots. Dualwidth modules carry dual location designations; e.g., G219-AB16AF, where AF designates pin F in the A slot of dual slot location AB.

- c. Signal Mnemonics Uncommon mnemonics are explained parenthetically the first time that they are mentioned in the discussion; e.g., KDN (key deposit next). A glossary of all signal mnemonics and their logic drawing origins is provided in Chapter 5.

- d. Illustrations References to in-text illustrations include the chapter prefix number--Figure 3-10 is the tenth illustration in Chapter 3.

- e. Drawings Logic drawings are identified in the text by a literal prefix code and a single numeric; e.g., drawing KC20(2), where KC denotes a central processor drawing and the parenthetic portion denotes sheet 2 of a multiple-sheet drawing. Other literals are: MC, core memory drawings, and KD, I/O control drawings. Complete drawing codes appear on the drawings themselves. See also Section 1.9.

#### 1.8 TERMINOLOGY

Terms used frequently throughout the text are defined below. Others are defined within the discussions themselves.

- a. Augmented Instruction An instruction word (OPR,IOT) that does not contain an address of an operand in core memory. The portion of the instruction usually reserved for an address contains micro-coded computer commands. These commands are executed during either normal (OPR) or extended (IOT) computer fetch cycles, as opposed to Memory Reference Instruction.

- b. Control Memory The magnetic storage device in the central processor which issues timed, sequential gating levels to process or execute the instruction. The levels are strobed out of the

read-only control memory in the form of 36-bit process words, each bit representing a gate-on or gate-off condition. Process word storage locations are addressed on the basis of the decoded instruction word op codes and previous processing results. Up to four process words may be extracted within any 1  $\mu$ s computer cycle.

- c. Core Memory The major storage device containing the computer program and the results of program execution. Sometimes referred to as the main memory, as opposed to Control Memory.

- d. Core Memory Cycle The 1 µs read/restore or read/modify/write cycle during which a word is extracted, then restored or modified, and written into core memory. The word may be an instruction word, an effective address word, or a data word (operand).

- e. Computer Fetch Cycle The 1 µs period during which a core memory cycle extracts and restores an instruction word. Instruction words are addressed sequentially by an incrementing program counter (PC) in the central processor, unless otherwise stipulated by program developments.

- f. Computer Defer Cycle The 1 µs period during which a core memory cycle extracts and restores an effective address word. A defer cycle follows a fetch cycle whenever the fetched instruction word contains an indirect address. If the indirect address refers to auto-index locations 10-17 in core memory, the effective address is incremented by 1 during defer; the operand is taken from the location designated by the incremented effective address during the Computer Execute Cycle.

- g. Computer Execute Cycle The 1 µs period during which a core memory cycle extracts and restores an operand addressed by a memory reference instruction word or by an effective address word. The operand is manipulated in the computer in accordance with the op code of the instruction word, and the result is stored in core memory. The result may be the original operand, or may be an operand modified by the manipulating processes. In the latter case, the original operand is lost.

- h. Computer IAO Cycle The 1  $\mu$ s execute period for certain instructions which ignore and replace completely the operands that they address, as opposed to the modifying operations of the normal Computer Execute Cycle.

- i. Direct Address The effective address in a memory reference instruction word of a location in core memory which contains an operand.

- j. Effective Address The actual address of an operand in core memory. The effective address may be a direct address in a memory reference instruction word, or an address in core memory which is addressed by an indirect address in a memory reference instruction word.

- k. Indirect Address The address in a memory reference instruction word of a location in core memory which contains an effective address.

- I. Memory Reference Instruction An instruction word containing a direct address or an indirect address of an operand in core memory, as opposed to Augmented Instruction.

- m. Op Code Operation code. A portion of a memory reference instruction word or an augmented instruction word that defines the operation to be executed.

- n. Program Break An exit from the main program into a device service routine requested by one of several sources below and granted by the central processor upon completion of the current execute cycle, in the following descending order of priority.

DMA channel breaks DCH breaks RTC breaks API breaks PI breaks

# 1.9 ENGINEERING DRAWINGS AND CIRCUIT SCHEMATICS

A complete set of engineering drawings and module circuit schematics is delivered with the PDP-9. Chapter 5 contains a set of reduced engineering drawings applicable to the basic system only indexed by their drawing number codes. Logic symbols used on the drawings are defined in the Logic Handbook, Document C-105.

In isolated cases of custom-design or late design changes, the logic drawings appearing in Chapter 5 may conflict with those furnished with the system. The furnished drawings always reflect the system as delivered, and therefore take precedence over the drawings in Chapter 5.

#### 1.10 SYSTEM SPECIFICATIONS

#### 1.10.1 <u>Dimensions</u>

| Cabinet Height        | 69-1/8 in. |

|-----------------------|------------|

| Cabinet Width         | 32-1/2 in. |

| Cabinet Depth         | 27-3/4 in. |

| Shelf Width           | 32-1/2 in. |

| Shelf Depth           | 22 in.     |

| Door Clearance (Rear) | 31 in.     |

| Cabinet Weight        | 750 lb.    |

| Teletype Height       | 8-3/8 in.  |

| Teletype Width        | 18-5/8 in. |

| Teletype Depth        | 18-1/2 in. |

| Teletype Weight       | 40 lb.     |

#### 1.10.2 Operating Characteristics

| Power Requirements       | 120V±15%, 60 cps±2%, single-phase, 17-30A or 230V±15%, 50 cps±2%, single-phase, 17-30A |

|--------------------------|----------------------------------------------------------------------------------------|

| Power Consumption        | 2 KW                                                                                   |

| Power Receptacle         | Hubbell Twistlock, flush, 250V, 30A                                                    |

| Power Supply outputs     | +10, -15, -30, ±20 Vdc                                                                 |

| Logic Levels             | 0V = logic 0, -3V = logic 1                                                            |

| Tested Temperature Range | 55-122 <sup>o</sup> F                                                                  |

| Relative Humidity Range  | 10-95%                                                                                 |

| Heat Dissipation         | 6830 Btu/hr                                                                            |

#### 1.10.3 Functional Characteristics

Word Length 18 bits plus optional memory parity bit

Cycle Time 1 µs (1.2 µs with parity)

Core Memory Operation Read/restore or read/modify/write cycle

Core Memory Capacity 8,192 words expandable to 32,768 words

Core Memory Access Single direct-addressing in any 8,192-word memory

bank; single indirect-addressing from one bank to

another

Computation Rate 500,000 additions/s

KSR 33 Teletype 10 char/s

DEC PC02 Paper Tape Reader 300 char/s

DEC PC03 Paper Tape Punch 50 char/s

Real-Time Clock 60 pps (50 pps for 50-cycle powered system)

Program-Controlled I/O Capacity Up to 64 devices, 4 mode selections each device

API Channel Capacity

Data Channel Capacity

Up to 28 devices

Up to 8 devices

Direct Memory Access Channel

Up to 3 devices

Capacity

Table 1-1

Related Documents

| Document<br>Number | Title                                             | Publisher         |

|--------------------|---------------------------------------------------|-------------------|

| C-105              | Logic Handbook                                    | DEC               |

| F-95               | PDP-9 User Handbook                               | DEC               |

| DEC-00-IP2A-D      | Paper Tape Reader PC02, Instruction Manual        | DEC               |

| DEC-9A-BSAA-D      | PDP-9 Software Summary                            | DEC               |

| DEC-9A-GSAA-D      | PDP-9 Advanced Software System                    | DEC               |

| DEC-9A-SFA0-D      | PDP-9 FAST System                                 | DEC               |

| DEC-9A-USA0-D      | PDP-9 Multianalyzer Programs                      | DEC               |

| DEC-9B-GSAA-D      | PDP-9 Basic Software System                       | DEC               |

| Bulletin 273B      | KSR 33 Teletype, Technical Manual                 | Teletype Corp.    |

| Bulletin 1184B     | KSR 33 Teletype, Parts                            | Teletype Corp.    |

|                    | Paper Tape Punch Model 500, Maintenance<br>Manual | Royal McBee Corp. |

|                    | Instruction Manuals, Optional Equipment           | DEC               |

Table 1-2 System Program Tapes

| Number* | Program                 | Number*              | Program                          |

|---------|-------------------------|----------------------|----------------------------------|

| ABAA-PU | Symbolic Assembler      | FSDA-PA              | Divide S.P. Signed               |

| AFT1-PU | FORTRAN II Compiler     | FSDB-PA              | Divide S.P. Unsigned             |

| AFT2-PU | FORTRAN II Assembler    | FSMA-PA              | Multiply S.P. Signed             |

| AFT3-PU | FORTRAN II OTS          | FSMB-PA              | Multiply S.P. Unsigned           |

| AFT5-PU | FORTRAN II IO Library   | LFFA-PA              | F.F. Loader                      |

| AFT6-PU | FORTRAN II 6DD Library  | LR1A-PH              | RIM Loader                       |

| AFT7-PU | FORTRAN II 9DD Library  | POT1-PU              | Teletype Octal Dump (SA:22)      |

| CDDA-PU | DDT                     | POT2-PU              | Teletype Octal Dump (SA:17300)   |

| CT1A-PU | Extended Trace          | PT1A-PA              | TIC TOC                          |

| ESSA-PU | Symbolic Editor         | PTMA-PU              | Master Tape Dumplicator          |

| FC2A-PA | CAL Handler Type II     | PYP1-PU              | RIM Puncher (SA: 0100)           |

| FC3A-PA | CAL Handler Type III    | PYP2 <del>-P</del> U | RIM Puncher (SA: 17000)          |

| FCRA-PA | CAL Handler Revised     | QDPA-PA              | Double Precision Integer Test    |

| FCXA-PA | Execute Subroutine      | QF1A-PA              | FORTRAN II Operating Test        |

| FODA-PA | Decimal Integer Print   | QFPA-PA              | Floating Point Test              |

| FOOA-PA | Octal Print Subroutine  | SDPA-PA              | Double Precision Integer Package |

| FOTA-PA | Teletype Output Package | SFPA-PA              | Floating Point Package           |

Table 1-3 Maintenance Program Documents

| Number     | Program                  | · |

|------------|--------------------------|---|

| 9A-D01A-PH | Instruction Test Part I  |   |

| 9A-D02A-PH | Instruction Test Part II |   |

| 9A-D0BA-PH | ISZ Test                 |   |

| 9A-D0CA-PH | Memory Address Test      |   |

| 9A-D0DB-PH | JMP Self Test            |   |

| 9A-D0EA-PH | JMP-Y Interrupt Test     | , |

| 9A-D0FA-PH | JMS-Y Interrupt Test     |   |

<sup>\*</sup>PA - Paper Tape ASCII

PH - Paper Tape Hardware Read-In

PU - Paper Tape Funny Format

Table 1-3 (cont)

Maintenance Program Documents

| Number     | Program                      |  |

|------------|------------------------------|--|

| 9A-DIAA-PH | Basic Memory Checkerboard    |  |

| 9A-DIBA-PH | Extended Memory Checkerboard |  |

| 9A-D2BA-PH | TTY Test                     |  |

| 9A-D2CB-PH | High Speed Reader Test       |  |

| 9A-D2DB-PH | Punch Test                   |  |

| 9A-D7AB-PH | Basic Exerciser              |  |

# CHAPTER 2 OPERATION

#### 2.1 SCOPE

This chapter contains operating information, tabular descriptions of system controls and indicators, and programming considerations for the PDP-9 operator.

#### 2.2 STANDARD CONTROLS AND INDICATORS

The following sections list and define standard manual controls and indicators, arranged as to the system elements: operator console, marginal-check and maintenance panels, paper tape reader/punch, teletype, power control, and core memory banks.

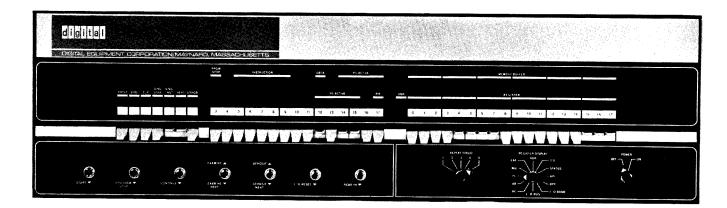

#### 2.2.1 Operator Console

Table 2-1 lists the functions of the standard controls and indicators shown in Figure 2-1. Other controls and indicators are optional and are not listed here. Indicators on the console show the existing states of specific register bits and control flip-flops by illuminating for binary 1s and extinguishing for binary 0s. The console can be electrically locked by a control on the maintenance panel (Figure 2-2) to prevent accidental alteration of the program in progress. While the console is locked, operation of any key or switch (with the exception of the DATA switches) will not be detected by the system.

Figure 2-1 Operator Console

Table 2-1

Operator Console, Controls and Indicators

| Name                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START key                | Three positions: off (center), operate (down, spring-loaded return), and locking (up). Depressing START starts program execution at the location specified by the ADDRESS switches. Up position for MAINT functions, Table 2–2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I/O RESET key            | Two positions: off (center) and operate (down, spring-loaded return). Depressing key clears all I/O device flags, all central processor registers except program counter (PC), and turns off the real-time clock and program interrupt facility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PROGRAM STOP key         | Two positions: off (center) and operate (down, spring-<br>loaded return). Depressing key halts program operation at<br>completion of the current instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CONTINUE key             | Three positions: off (center), operate (down, spring-loaded return), and locking (up). Depressing key resumes program execution from the point at which it stopped. Up position for use with REPT, SING STEP, SING INST switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| EXAMINE/EXAMINE NEXT key | Three positions: off (center), EXAMINE (up, spring-loaded return), and EXAMINE NEXT (down, spring-loaded return). Raising the key to EXAMINE transfers the contents of the memory location specified by the ADDRESS switches to the memory buffer register (MB). After the transfer, the computer stops, and the MB contents can be viewed in the MEMORY BUFFER indicator. The contents of the ADDRESS switches transfer to the arithmetic register (AR) for viewing in the REGISTER indicator. Depressing the key to EXAMINE NEXT increments the contents of the AR by 1 and transfers the contents of the newly addressed memory location to the MB. Using EXAMINE NEXT after EXAMINE facilitates monitoring of sequential memory locations as the ADDRESS switches need only be set the first time to the lowest memory location. |

| DEPOSIT/DEPOSIT NEXT key | Three positions: off (center), DEPOSIT (up, spring-loaded return), and DEPOSIT NEXT (down, spring-loaded return). Raising the key deposits the contents of the DATA switches into the memory location specified by the ADDRESS switches. After the transfer, the contents of the ADDRESS switches appear in the AR as the address of the memory location into which the data was entered. Depressing the key increments the AR contents by I, and deposits the contents of the DATA switches into the memory location specified by the new address. Using DEPOSIT NEXT after DEPOSIT facilitates entering data in sequential memory locations as the ADDRESS switches need only be set the first time to the lowest order address.                                                                                                   |

Table 2–1 (cont)

Operator Console, Controls and Indicators

| Name                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                      | Function                                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| READ IN key                                       | Two positions: off (center) and operate (down, spring-loaded return). Depress the key to initiate read-in of paper tape punched in binary code. (Three 6-bit lines form one 18-bit word.) Storage of words begins at the memory location specified by the ADDRESS switches. At the completion of tape read-in, the computer reads and executes the last word stored. Read-in occurs at the selected repeat speed (see REPEAT SPEED). |                                                                                                                                                                                                                                                                                          |  |

| REPEAT SPEED switch                               | selected spe<br>without oper<br>approximate                                                                                                                                                                                                                                                                                                                                                                                          | With REPT switch up, REPEAT SPEED establishes one of five selected speeds at which certain manual operations repeat without operator intervention. The repeat speeds range from approximately 8 µs (position 5) to 60 ms. Switch must be placed in position 5 during READ IN operations. |  |

| REPT switch and indicator                         | The up position causes operations initiated by START, CONTINUE, SING STEP, SING INST, or READ IN to repeat. REPEAT SPEED establishes the rate of repetition. Also used for MAINT function, Table 2–2. The indicator lights when the switch is up.                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                          |  |

| REGISTER DISPLAY switch<br>and REIGSTER indicator | register to di<br>Display is er                                                                                                                                                                                                                                                                                                                                                                                                      | tion switch. Each position selects a specific isplay its contents in the REGISTER indicator. nabled only when the machine stops. The ister selections are as follows.                                                                                                                    |  |

|                                                   | RDR                                                                                                                                                                                                                                                                                                                                                                                                                                  | Displays contents of paper-tape reader buffer.                                                                                                                                                                                                                                           |  |

|                                                   | TTI                                                                                                                                                                                                                                                                                                                                                                                                                                  | Displays contents of teletype keyboard buffer in the eight least-significant indicator lamps.                                                                                                                                                                                            |  |

|                                                   | STATUS                                                                                                                                                                                                                                                                                                                                                                                                                               | Displays status of I/O device flags connected to status checking facility (Table 3-3).                                                                                                                                                                                                   |  |

|                                                   | I/O ADDR                                                                                                                                                                                                                                                                                                                                                                                                                             | Displays address word from address lines of I/O bus for DCH and optional API operations in the 15 least significant indicator lamps.                                                                                                                                                     |  |

|                                                   | I/O BUS                                                                                                                                                                                                                                                                                                                                                                                                                              | Displays data word on I/O bus to/from any device using the bus.                                                                                                                                                                                                                          |  |

|                                                   | AC                                                                                                                                                                                                                                                                                                                                                                                                                                   | Displays contents of the AC.                                                                                                                                                                                                                                                             |  |

|                                                   | AR                                                                                                                                                                                                                                                                                                                                                                                                                                   | Displays contents of the AR.                                                                                                                                                                                                                                                             |  |

|                                                   | PC                                                                                                                                                                                                                                                                                                                                                                                                                                   | Displays contents of the PC in the 13 least significant indicator lamps, status of LINK, memory extend mode, memory protect mode, EPC in the five most significant lamps.                                                                                                                |  |

Table 2–1 (cont)

Operator Console, Controls and Indicators

| Name                           | Function                                                                                                                                                                                                                   |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER switch                   | Controls application of primary power to power supplies, fans, teletype motor, tape punch motor, and interfaced optional external devices.                                                                                 |

| CLK switch and indicator       | The down position allows the program to enable the real-<br>time clock. The indicator lights when the clock is enabled.                                                                                                    |

| SING STEP switch and indicator | The up position halts the program by preventing the initiation of the next memory cycle (except during DCH operations, which cannot be single-stepped). The indicator lights when the switch is up.                        |

| SING INST switch               | The up position halts the program after completion of one instruction. The indicator lights when the switch is up.                                                                                                         |

| ADDRESS switches (3-17)        | Establish a 15-bit core memory address to be entered in the PC by operation of the START key, or in the AR by operation of the EXAMINE or DEPOSIT key. Up position for a 1 bit, down position for a 0 bit.                 |

| DATA switches (0-17)           | Establish an 18-bit data or instruction word to be entered into memory by DEPOSIT or DEPOSIT NEXT, or to be entered in the AC by a programmed OAS or LAS instruction.  Up position for a 1 bit, down position for a 0 bit. |

| PRGM STOP indicator            | Lights when the program halts.                                                                                                                                                                                             |

| INSTRUCTION indicator          | The five indicator bits reveal the current op code in the IR (instruction register). A lighted indicator lamp denotes a 1 bit, extinguished lamp a 0 bit.                                                                  |

| DATA indicator                 | Lights to indicate that data is being transferred between core memory and a DCH device.                                                                                                                                    |

| PIE indicator                  | Lights when the program interrupt facility has been enabled by program control.                                                                                                                                            |

| LINK indicator                 | Shows the content of the LINK register.                                                                                                                                                                                    |

| MEMORY BUFFER indicator        | Shows the contents of the MB (memory buffer) register.                                                                                                                                                                     |

## 2.2.2 Marginal Check Panel and Maintenance Panel

These panels (Figure 2-2) are concealed behind the hinged red cover on the left of the cabinet. Table 2-2 details the functions of the panel-mounted controls and indicators.

Figure 2–2 Marginal Check Panel and Maintenance Panel

Table 2–2 Marginal Check and Maintenance Panels, Controls and Indicators

| Name                 |                                              | Function                                                                                                                                                                                                                                                                                       |  |

|----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | Marginal Che                                 | ck Panel                                                                                                                                                                                                                                                                                       |  |

| Voltmeter*           | Power Suppl<br>the referenc<br>side of the s | Indicates the marginal-check voltage output of the 709 Power Supply. The center of the scale (0V) equates with the reference voltage selected, +10 or -15 Vdc. The right side of the scale indicates an increase in magnitude beyond the selected voltage. The left side indicates a decrease. |  |

| Selector switch*     | Three position                               | ons:                                                                                                                                                                                                                                                                                           |  |

|                      | OFF                                          | Removes the marginal check voltages from the computer system.                                                                                                                                                                                                                                  |  |

|                      | +10 MC                                       | Selects the +10V marginal check output.                                                                                                                                                                                                                                                        |  |

|                      | -15 MC                                       | Selects the -15V marginal check output.                                                                                                                                                                                                                                                        |  |

| Variac control knob* |                                              | Adjusts the marginal check voltage above or below the selected reference voltage.                                                                                                                                                                                                              |  |

| TOTAL HOURS meter    | "power on"                                   | Indicates to the nearest tenth of an hour the cumulative "power on" time of the system. Meter counts from 00000.0 to 99999.9 hr.                                                                                                                                                               |  |

|                      | Maintenance                                  | Panel                                                                                                                                                                                                                                                                                          |  |

| Selector switch      | Five positions:                              |                                                                                                                                                                                                                                                                                                |  |

|                      | LOCK                                         | Electrically locks the console controls (except DATA switches).                                                                                                                                                                                                                                |  |

|                      | NORMAL                                       | Console is unlocked; all controls effective.                                                                                                                                                                                                                                                   |  |

|                      | MAINT                                        | With the switch in this position and the START key and REPT switch up, the built-in                                                                                                                                                                                                            |  |

<sup>\*</sup>Used with internally-mounted marginal check switches; see Chapter 4.

Table 2–2 (cont)

Marginal Check and Maintenance Panels, Controls and Indicators

| Name                   |                   | Function                                                                                                                                                                                                                                                     |

|------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Maintenance Panel | (cont)                                                                                                                                                                                                                                                       |

| Selector switch (cont) |                   | maintenance test program circulates a self-<br>incrementing count through all active CP<br>registers to verify register operation and in-<br>ternal transfer-path gating. The test pro-<br>ceeds at the rate selected by the console<br>REPEAT SPEED switch. |

|                        | EXAMINE           | With console REPT switch off (down), simulates the console EXAMINE function. With REPT switch up, simulates console EXAMINE-REPT function.                                                                                                                   |

|                        | DEPOSIT           | With console REPT switch off (down), simulates the console DEPOSIT function. With REPT switch up, simulates console DEPOSIT-REPT function.                                                                                                                   |

## 2.2.3 Paper Tape Reader/Punch

The PC09 Tape Reader/Punch appears in Figure 2–3. The PC09 consists of the PC02 Tape Reader (left) and the PC03 Tape Punch (right). Table 2–3 lists the tape reader/punch controls and their functions.

Figure 2-3 Paper Tape Reader/Punch PC09

Table 2–3

Tape Reader/Punch, Controls and Indicators

| Name                       | Location | Function                                                                                                                                                                                                         |

|----------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FEED button                | Reader   | Depressing button advances tape without reading. Spring-<br>loaded release position allows program control or manual<br>control or read-in operations.                                                           |

| POWER button and indicator | Punch    | Off position simulates PUN NO TAPE condition. On position removes the condition. Indicator lights when tape is secured and button is pressed to on position.                                                     |

| FEED button                | Punch    | Depressing button advances tape and punches feed holes.  Off, spring-loaded release position, allows program control of punching operations. POWER indicator extinguishes when button is pressed to on position. |

# 2.2.4 Teletype Unit

The KSR 33 Teletype Unit appears in Figure 2-4. Table 2-4 lists the teletype controls and their functions.

Figure 2-4 KSR 33 Teletype Unit

Table 2–4 Teletype Controls

| Name                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Teletype keyboard     | Supplies input data to the computer and/or the page printer, depending on the setting of the LINE/OFF/LOCAL switch.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LINE/OFF/LOCAL switch | Controls the application of primary power to the Teletype and controls data connection between the Teletype and the central processor. In the LINE position, the Teletype is energized and connected as an I/O device to the computer. In the OFF position the teletype motor is de-energized but the logic circuits remain energized. In the LOCAL position the Teletype is energized for off-line operations, breaking the signal connections to the computer. Use of the Teletype requires that the computer be energized through the console POWER switch. |

# 2.2.5 Power Control 841A

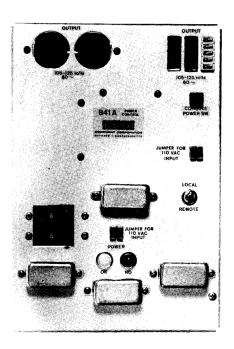

Figure 2-5 illustrates the Power Control 841A. Table 2-5 lists the controls and functions.

Figure 2-5 Power Control 841A

Table 2-5

Power Control 841A, Controls and Indicators

| Name                   | Function                                                                                                                                                                                                                                                                       |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Circuit Breaker CB1    | Protects primary power source from overloads due to failure of 709 Power Supplies.                                                                                                                                                                                             |  |