# PRISM SYSTEMS

Digital Equipment Corporation Confidential and Proprietary

**Restricted Distribution**

# System Reference Manual

# Digital Equipment Corporation Confidential and Proprietary

This is an unpublished work and is the property of Digital Equipment Corporation. This work is confidential and is maintained as a trade secret. In the event of inadvertent or deliberate publication, Digital Equipment Corporation will enforce its rights in this work under the copyright laws as a published work. This work, and the information contained in it may not be used, copied, or disclosed without the express written consent of Digital Equipment Corporation.

# © 1988 Digital Equipment Corporation All Rights Reserved

This Information shall not be disclosed to non-Digital Equipment Corporation personnel or generally distributed within Digital Equipment Corporation. Distribution is restricted to persons authorized and designated by the responsible Engineer or Manager.

This document shall not be left unattended, and, when not in use, shall be stored in a locked storage area.

These restrictions are to be enforced until noted otherwise.

Responsible Engineer/Manager

Date

Revision No: 3.0

**Document Copy:**

Date: 26 April 1988

**Restricted Distribution**

# CONTENTS

| CHAPTER  | 1       | INTRODUCTION                                                            |

|----------|---------|-------------------------------------------------------------------------|

|          | 1.1     | INTRODUCTION                                                            |

|          | 1.2     | DIFFICULTIES IN BUILDING A HIGH PERFORMANCE VAX . 1-1                   |

|          | 1.3     | PRISM ARCHITECTURE OVERVIEW                                             |

|          | 1.3.1   | Instruction Set Characteristics 1-3                                     |

|          | 1.3.2   | Pipelined Processor Model 1-4 ADVANTAGES AND DISADVANTAGES OF PRISM 1-5 |

|          | 1.4     | ADVANTAGES AND DISADVANTAGES OF PRISM 1-5                               |

|          | 1.5     | VAX COMPATIBILITY                                                       |

|          | 1.5.1   | VAX COMPATIBILITY                                                       |

|          | 1.5.2   | Why No VAX Compatibility Mode Is Provided 1-8                           |

|          | 1.6     | TERMINOLOGY AND CONVENTIONS                                             |

|          | 1.6.1   | Numbering                                                               |

|          | 1.6.2   | UNPREDICTABLE And UNDEFINED 1-8                                         |

|          | 1.6.3   | Ranges And Extents 1-9                                                  |

|          | 1.6.4   | Must Be Zero (MBZ)                                                      |

|          | 1.6.5   | Read As Zero (RAZ)                                                      |

|          | 1.6.6   | Should Be Zero (SBZ)                                                    |

|          | 1.6.7   | Tenomo (TCN)                                                            |

|          | 1.6.7   | Read As Zero (RAZ)                                                      |

|          | 1.0.0   | rigure Drawing Conventions                                              |

| CHAPTER  | 2       | BASIC ARCHITECTURE                                                      |

| CHAP IEK | _       |                                                                         |

|          | 2.1     | ADDRESSING                                                              |

|          | 2.2     | DATA TYPES                                                              |

|          | 2.2.1   | Byte                                                                    |

|          | 2.2.2   | Byte                                                                    |

|          | 2.2.3   | Longword                                                                |

| •        | 2.2.4   | Quadword                                                                |

|          | 2.2.5   | F floating                                                              |

|          | 2.2.6   | G IIOating                                                              |

|          | 2.2.7   | Data Types With No Hardware Support 2-7                                 |

|          |         |                                                                         |

| CHAPTER  | 3       | INSTRUCTION FORMATS                                                     |

|          | 3.1     | PRISM REGISTERS                                                         |

| •        | 3.1.1   | Scalar Registers                                                        |

|          | 3.1.2   | Vector Registers                                                        |

|          | 3.1.3   | Program Counter                                                         |

|          | 3.1.4   | Cycle Count Register                                                    |

|          | 3.2     | NOTATION                                                                |

| •        | 3.2.1   | Scalar Operand Values                                                   |

|          | 3.2.2   | Operators                                                               |

|          | 3.2.2   | INSTRUCTION FORMATS                                                     |

|          | 3.3.1   | Memory Instruction Format                                               |

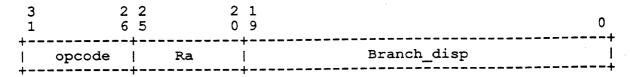

|          | 3.3.1   | Branch Instruction Format                                               |

|          |         |                                                                         |

|          | 3.3.3   |                                                                         |

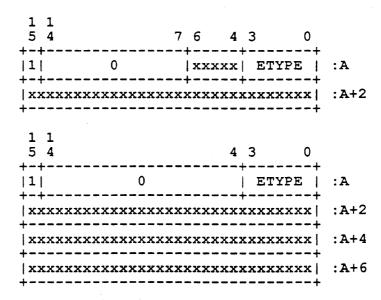

|          | 3.3.3.1 | Masked Vector Arithmetic Operate Instruction Format                     |

|          | 2 2 2 2 |                                                                         |

|          | 3.3.3.2 | Masked Vector Memory Operate Instruction                                |

|          |         | Format                                                                  |

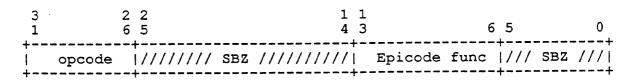

|          | 3.3.4   | Epicode Instruction Format                                              |

| CHAPTER | 4     | INSTRUCTION DESCRIPTIONS                      |

|---------|-------|-----------------------------------------------|

|         | 4.1   | INSTRUCTION SET OVERVIEW AND NOTATION 4-1     |

|         | 4.1.1 | Subsetting Rules 4-2                          |

|         | 4.1.2 | Subsetting Rules                              |

|         | 4.1.3 | Instruction Operand Notation                  |

|         | 4.1.4 | Opcode Qualifiers 4-4                         |

|         | 4.2   | MEMORY LOAD /STORE INSTRUCTIONS 4-9           |

|         |       | Opcode Qualifiers                             |

|         |       | Compare and Swap Quadword, Interlocked 4-8    |

|         |       | Load Address                                  |

|         |       | Load Memory Data into Scalar Register 4-11    |

|         |       | Read, Mask, Add Longword, Interlocked 4-12    |

|         |       | Pead Mask Add Ourdword Interlocked 4-12       |

|         |       | Read, Mask, Add Quadword, Interlocked 4-13    |

|         |       | Store Scalar Register Data into Memory 4-14   |

|         |       | Gather Memory Data into Vector Register 4-15  |

|         |       | Load Memory Data into Vector Register 4-17    |

|         |       | Scatter Vector Register Data into Memory 4-19 |

|         |       | Store Vector Register Data into Memory 4-20   |

|         | 4.3   | INTEGER ARITHMETIC INSTRUCTIONS 4-21          |

|         |       | Integer Add                                   |

|         |       | Integer Signed Compare 4-24                   |

|         |       | Integer Unsigned Compare 4-25                 |

|         |       | Integer Divide 4-26                           |

|         |       | Integer Multiply 4-27                         |

|         |       | Integer Subtract 4-28                         |

|         |       | Integer Subtract                              |

|         |       | Vector Integer Signed Compare 4-30            |

|         | • *   | Vector Integer Unsigned Compare 4-32          |

|         |       | Vector Integer Multiply 4-34                  |

|         |       | Vector Integer Subtract                       |

|         | 4.4   | LOGICAL AND SHIFT INSTRUCTIONS 4-36           |

|         |       | Logical Functions 4-37                        |

|         |       | Shift Logical 4-38                            |

|         |       | Shift Arithmetic 4-39                         |

|         |       | Rotate                                        |

|         |       | Vector Logical Functions 4-41                 |

|         |       | Vector Merge 4-43                             |

|         |       | Vector Shift Logical 4-44                     |

|         | 4.5   | Vector Shift Logical                          |

|         | 4.5.1 | Literals                                      |

|         | 4.5.2 |                                               |

|         | 4.5.3 | Accuracy                                      |

|         |       | Floating Add 4-52                             |

|         |       | Floating Add                                  |

|         |       | Convert F Floating to G Floating 4-54         |

|         |       | Convert G_Floating to F_Floating 4-55         |

|         |       | Convert Floating to Longword 4-56             |

|         |       | Convert Longword to Floating 4-57             |

|         |       | Floating Divide 4-58                          |

|         |       | Floating Multiply 4-50                        |

|         |       | Floating Subtract 4-60                        |

|         |       | Floating Subtract                             |

|         |       | Vector Floating Compare                       |

|         |       |                                               |

|         |       | Vector Convert F Floating to G Floating 4-64  |

|         |       | Vector Convert G Floating to F Floating 4-65  |

|         |       | Vector Convert Floating to Longword 4-66      |

|         |       | Vector Convert Longword to Floating 4-67      |

|         |       | Vector Floating Divide                        |

|         |       | Vector Floating Multiply                      |

|         |       | Vector Floating Subtract 4-70                 |

|         | 4.6          | CONTROL INSTRUCTIONS                                                         |

|---------|--------------|------------------------------------------------------------------------------|

|         |              | Conditional Branch 4-72                                                      |

|         |              | Fault On Low Bit Clear 4-73                                                  |

|         |              | Jump to Subroutine 4-74                                                      |

|         | 4.7          | Jump to Subroutine                                                           |

|         |              | Breakpoint                                                                   |

|         |              | Breakpoint                                                                   |

|         |              | Flush Instruction Cache 4-79                                                 |

|         |              | Generate Compressed Iota Vector 4-80                                         |

|         |              | Move Processor Status 4-81                                                   |

|         |              | Probe Memory Access 4-82                                                     |

|         |              |                                                                              |

|         |              | Read Cycle Count Register                                                    |

|         |              | Read/Write Vector Length Register 4-85                                       |

|         |              | Read/Write Vector Mask Register 4-86                                         |

|         |              | Read/Write Vector Mask Register 4-86 Return from Exception or Interrupt 4-87 |

|         |              | Swap AST Enable                                                              |

|         | 4.8          | Swap AST Enable                                                              |

|         |              | BOOT 4-91                                                                    |

|         |              | BOOT                                                                         |

|         |              | Physical                                                                     |

|         |              | HALT                                                                         |

|         |              | Load Quadword Physical 4-94                                                  |

|         |              | Move From Processor Register                                                 |

|         |              | Move To Processor Register 4-96                                              |

|         |              | Move To Processor Register                                                   |

|         |              | Swap Privileged Context                                                      |

|         |              | Swap IPI                                                                     |

|         |              | Swap IPL                                                                     |

|         |              | Write Cycle Count Register 4-102                                             |

| CHAPTER | 5.1          | MEMORY MANAGEMENT  INTRODUCTION                                              |

|         | 5.2          | VIRTUAL ADDRESS SPACE 5-2                                                    |

|         | 5.2.1        |                                                                              |

|         | 5.3          | PHYSICAL ADDRESS SPACE                                                       |

|         | 5.4          | MEMORY MANAGEMENT CONTROL 5-3                                                |

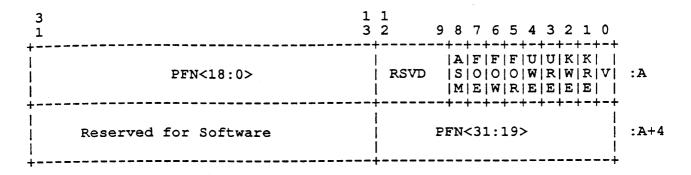

|         | 5.5          | PAGE TABLE ENTRIES                                                           |

|         | 5.5.1        | Changes To Page Table Entries 5-4                                            |

|         | 5.6          | MEMORY PROTECTION                                                            |

|         | 5.6.1        | Processor Modes                                                              |

|         | 5.6.2        | Protection Code                                                              |

|         | 5.6.3        | Access Violation Fault 5-6                                                   |

|         | 5.7          | ADDRESS TRANSLATION                                                          |

|         | 5.8          | TRANSLATION BUFFER                                                           |

|         |              | ADDRESS SPACE NUMBERS                                                        |

|         | 5.10         | MEMORY MANAGEMENT FAULTS 5-8                                                 |

|         |              |                                                                              |

| CHAPTER | 6            | EXCEPTIONS AND INTERRUPTS                                                    |

|         | 6.1          | INTRODUCTION 6-1                                                             |

|         | 6.1.1        | INTRODUCTION                                                                 |

|         | 6.1.2        | Interrupts 6-1                                                               |

|         | 6.1.3        | Exceptions 6-2                                                               |

|         | 6.1.4        | Contrast Between Exceptions And Interrupts 6-3                               |

|         | 6.2          | PROCESSOR STATE                                                              |

|         | 6 2          | INTERRUPTS                                                                   |

|         | 6.3<br>6.3.1 | Asynchronous System Trap (AST) - Level 1 6-7                                 |

|         | 6.3.2   | Software Interrupts - Levels 1 To 3 6                                       |                                              |

|---------|---------|-----------------------------------------------------------------------------|----------------------------------------------|

|         | 6.3.2.1 | Software Tablement Summary Besides                                          |                                              |

|         | 6.3.2.2 |                                                                             | <u>-                                    </u> |

|         | 6.3.3   |                                                                             | - 7                                          |

|         |         | Console Interrupts - Level 4 6- Console Receive Control Status 6-           | - 8                                          |

|         | 6.3.3.1 | Console Receive Control Status 6                                            | - 8                                          |

|         | 6.3.3.2 | Console Transmit Control Status 6-                                          | C                                            |

|         | 6.3.4   | I/O Device Interrupts - Levels 4 And 5 6-                                   | _ 0                                          |

|         | 6.3.5   | Urgent Interrupts - Levels 6 And 7                                          |                                              |

|         | 6.3.5.1 | Urgent Interrupts - Levels 6 And 7 6- Interval Clock Interrupt - Level 6 6- | - 5                                          |

|         | 6.3.5.1 | Interval Clock Interrupt - Level 6 6-1                                      | T C                                          |

|         |         |                                                                             | L C                                          |

|         | 6.3.5.2 | Interprocessor Interrupt - Level 6 6-1                                      | LO                                           |

|         | 6.3.5.2 | Interprocessor Interrupt Enable Register 6-1                                | L C                                          |

|         | 6.3.5.3 | Interprocessor Interrupt Request Register . 6-1                             |                                              |

|         | 6.4     | EXCEPTIONS                                                                  |                                              |

|         | 6.4.1   | Arithmetic Munc                                                             |                                              |

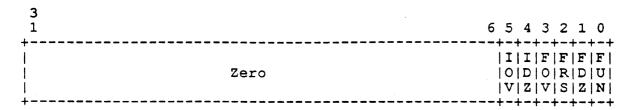

|         | 6.4.2   | Arithmetic Traps 6-1                                                        | 12                                           |

|         |         | Data Alignment Fault 6-1                                                    | . 5                                          |

|         | 6.4.2.1 | Scalar Alignment Fault 6-1                                                  | 5ء                                           |

|         | 6.4.3   | raults Occurring As The Result Of An                                        |                                              |

|         |         | Instruction                                                                 | 6                                            |

|         | 6.4.3.1 | Instruction 6-1 Breakpoint Fault 6-1                                        | 7                                            |

|         | 6.4.3.2 | Fault On Low Bit Clear Fault 6-1                                            | . 7                                          |

|         | 6.4.4   | Tileral On now Bit Clear Fault                                              | . /                                          |

|         |         | rilegal Operand Fault 6-1                                                   | . 8                                          |

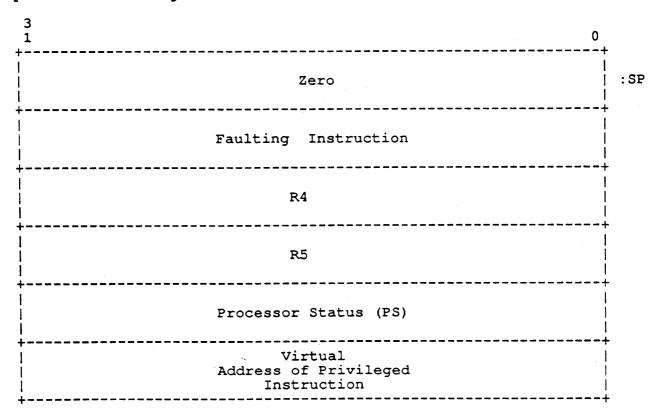

|         | 6.4.4.1 | Illegal Operand Fault 6-1 Privileged Instruction 6-2                        | 20                                           |

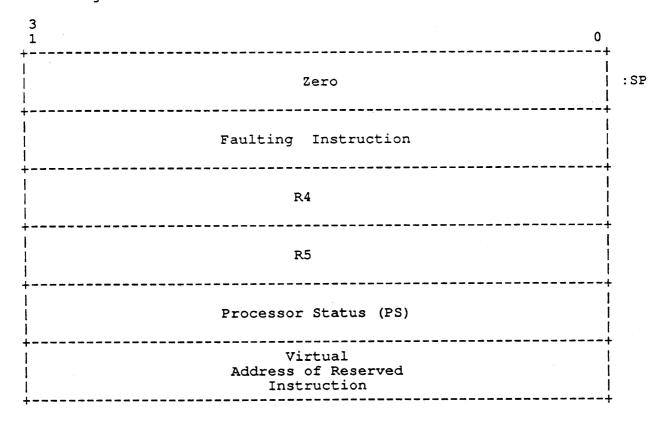

|         | 6.4.4.2 | Reserved Opcode Fault 6-2                                                   | 1:                                           |

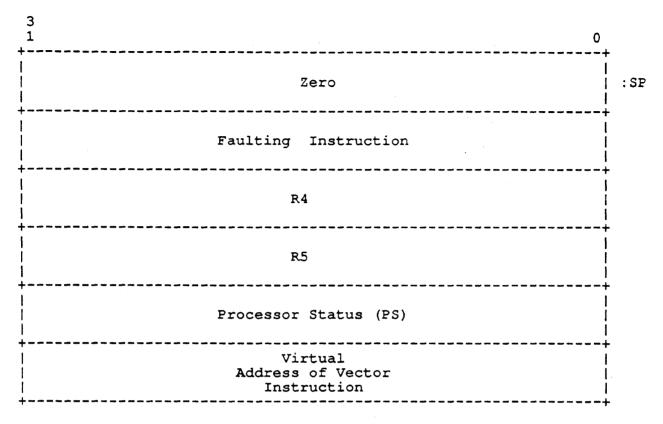

|         | 6.4.4.3 | Vector Enable                                                               | 7                                            |

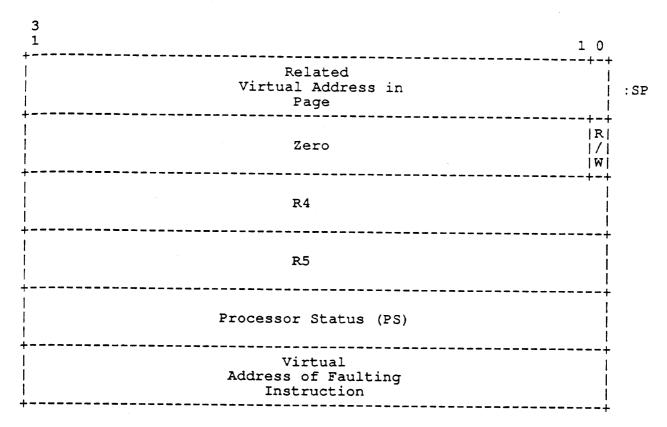

|         | 6.4.5   | Memory Management Faults 6-2                                                | 7                                            |

|         | 6.4.5.1 | Access Violation                                                            | . こ                                          |

|         | 6.4.5.2 | Access Violation 6-2 Translation Not Valid 6-2                              | د.                                           |

|         |         | Transfaction Not Valid 6-2                                                  | . 4                                          |

|         | 6.4.5.3 |                                                                             | 4                                            |

|         | 6.4.5.4 |                                                                             | 4                                            |

|         | 6.4.5.5 | Fault On Write 6-2                                                          | 4                                            |

|         | 6.4.6   | Serious System Failures 6-2                                                 | 5                                            |

|         | 6.4.6.1 | Kernel Stack Not Valid Halt 6-2                                             | , =                                          |

| •       | 6.4.6.2 | Machine Chook About                                                         |                                              |

|         |         | Machine Check Abort 6-2                                                     |                                              |

|         | C 4 7 1 | Vector Exceptions 6-2                                                       | . 7                                          |

|         | 6.4.7.1 |                                                                             | 0                                            |

|         | 6.5     | SERIALIZATION OF EXCEPTIONS AND INTERRUPTS 6-3                              | 0                                            |

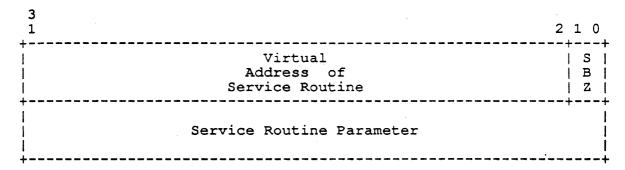

|         | 6.6     | SYSTEM CONTROL BLOCK (SCB) 6-3                                              | 1                                            |

|         | 6.7     | STACKS                                                                      | 1                                            |

|         | 6.7.1   | Stack Writability 6-3                                                       | - TA                                         |

|         | 6.7.2   | Stack Decidence                                                             | 4                                            |

|         | 6.7.3   | Stack Residency 6-3                                                         |                                              |

|         |         | Stack Alignment 6-3                                                         | 4                                            |

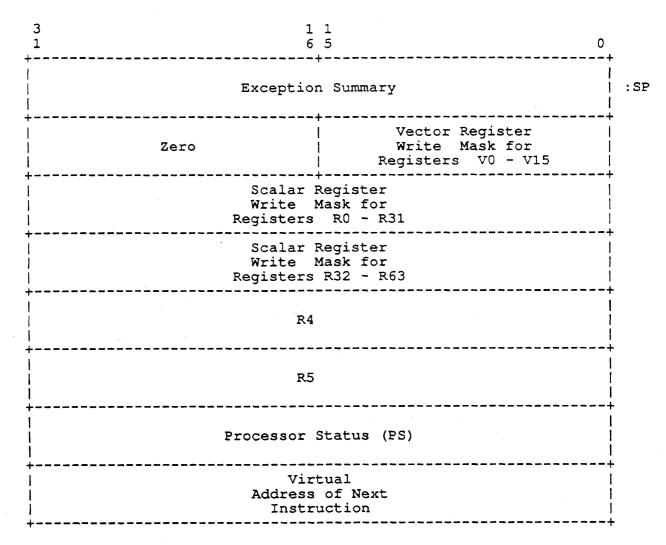

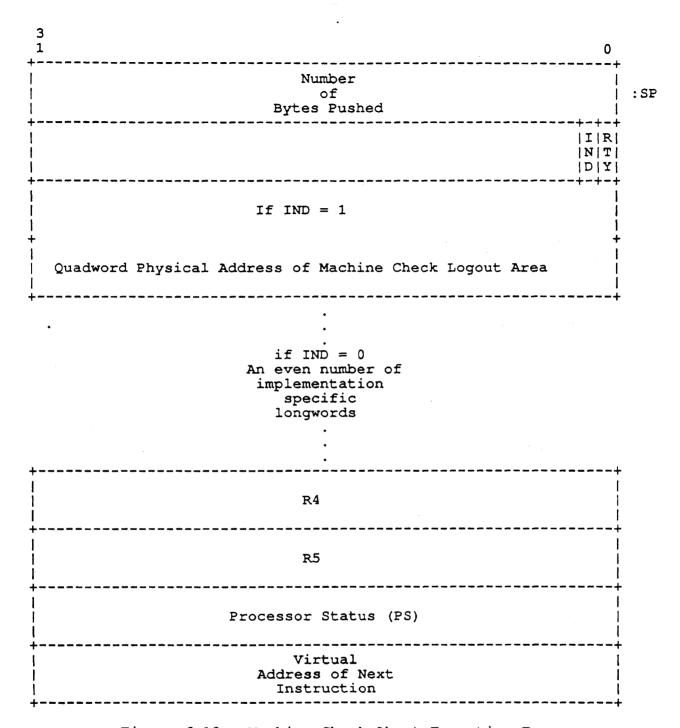

|         | 6.7.4   | Initiate Exception Or Interrupt 6-3                                         | 5                                            |

|         | 6.7.5   | Epicode Interrupt Arbitration 6-3                                           | 7                                            |

|         | 6.7.5.1 | MTPR AST Request Register 6-3                                               | 8                                            |

|         | 6.7.5.2 | MTPR Software Interrupt Request Register 6-3                                | ٥                                            |

|         | 6.7.5.3 |                                                                             | 0                                            |

|         | 6.7.5.4 |                                                                             | ğ                                            |

|         |         |                                                                             | 8                                            |

|         | 6.7.5.5 | Swap Interrupt Priority Level 6-3                                           | 9                                            |

|         | 6.7.6   | Processor State Transition Table 6-3                                        | 9                                            |

|         |         |                                                                             |                                              |

|         |         |                                                                             |                                              |

| CHAPTER | 7       | PROCESS STRUCTURE                                                           |                                              |

|         |         |                                                                             |                                              |

|         | 7.1     | PROCESS DEFINITION                                                          | ٦                                            |

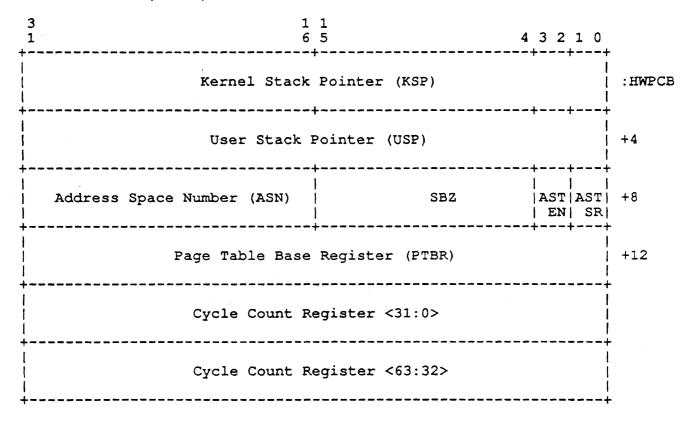

|         | 7.2     | HARDWARE PRIVILEGED PROCESS CONTEXT                                         | 7                                            |

|         | 7.3     | ASYNCHROMOTIC CVCMPM MDADG (ACM)                                            | ~                                            |

|         |         | A Coffee W A A A                                                            | 3                                            |

|         | 7.3.1   | ASYNCHRONOUS SYSTEM TRAPS (AST)                                             | 4                                            |

|         | 7.4     | PROCESS CONTEXT SWITCHING                                                   | 5                                            |

|         | 7.4.1   | A Software Model For Process Context Switching . 7-                         | 6                                            |

|         |         |                                                                             | -                                            |

| CHAPTER | 8                                                                                              | INTERNAL PROCESSOR REGISTERS                                                 |

|---------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

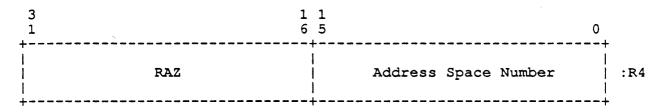

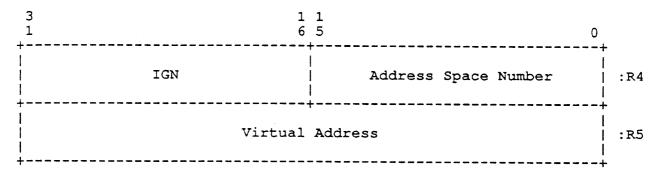

|         | 8.1                                                                                            | Address Space Number (ASN)                                                   |

| CHAPTER | 9                                                                                              | SYSTEM ARCHITECTURE AND PROGRAMMING IMPLICATIONS                             |

|         | 9.1<br>9.2<br>9.2.1<br>9.2.2<br>9.2.2.1<br>9.2.2.2<br>9.2.3<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7 | Interprocessor Signaling And Data Visibility 9-5 Atomicity And Corruption 9- |

| CHAPTER | 10                                                                                             | EXTENDED PROCESSOR INSTRUCTION CODE                                          |

|         | 10.1<br>10.2<br>10.3<br>10.4                                                                   | INTRODUCTION                                                                 |

| CHAPTER  | 11               | SYSTEM BOOTSTRAPPING AND CONSOLE                                                   |            |

|----------|------------------|------------------------------------------------------------------------------------|------------|

|          | 11.1             | BOOTSTRAPPING 11                                                                   | _1         |

|          | 11.1.1           |                                                                                    | -1         |

|          | 11.1.1.          | Memory Testing                                                                     | -2         |

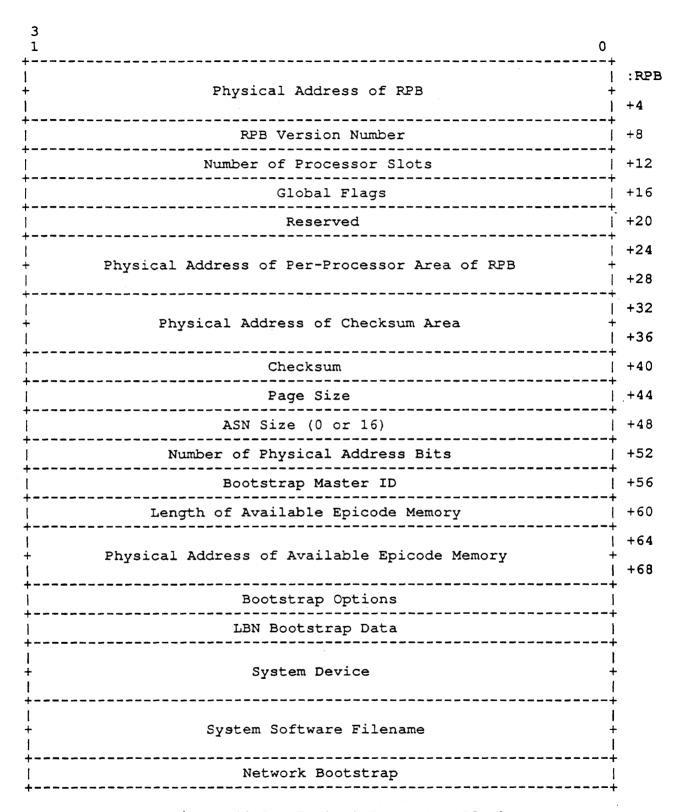

|          | 11.1.1.          | Restart Parameter Block                                                            | -2         |

|          | 11.1.1.3         | Epicode Loading 11                                                                 | -7         |

|          | 11.1.1.4         | Initial Page Tables                                                                | -7         |

|          | 11.1.1.          |                                                                                    | - 8        |

|          | 11.1.1.          | IDAMING OF System Software                                                         | -9         |

|          | 11.1.1.1         | Transfer Of Control To System Software 11                                          | - 9<br>- 9 |

|          | 11.1.2           | Powerfail                                                                          | 10         |

|          | 11.1.3           | Powerfail Recovery                                                                 | 10         |

|          | 11.1.4           | Multiprocessor Bootstrapping 11-                                                   | 11         |

|          | 11.1.4.          | l Initial Synchronization 11-                                                      | 11         |

|          | 11.1.4.2         |                                                                                    | 11         |

|          | 11.1.4.3         |                                                                                    | 12         |

|          | 11.1.4.4         |                                                                                    | 12         |

|          | 11.2             | CONSOLE                                                                            | 13         |

|          | 11.2.1           | CONSOLE                                                                            | 14         |

|          | 11.2.2           | Entering Console Mode                                                              | 14         |

|          | 11.2.3           | Entering Console Mode                                                              | 14         |

|          | 11.3             | CONSOLE LANGUAGE                                                                   | 14         |

|          | 11.3.1           | Control Characters                                                                 | 15         |

|          | 11.3.2<br>11.3.3 | Command Syntax                                                                     | 15         |

|          | 11.3.3           | Commands                                                                           | 17         |

|          |                  | CONTINUE                                                                           | 18         |

|          |                  | DEPOSIT                                                                            | 19         |

|          |                  | EXAMINE                                                                            | 20         |

|          | •                | HALT                                                                               | 24         |

|          |                  | INITIALIZE                                                                         |            |

|          |                  | START                                                                              | 26         |

|          | 11.3.4           | TEST                                                                               | 27         |

|          | 11.3.4           | Error Messages                                                                     | 40         |

|          |                  |                                                                                    |            |

| CHAPTER  | 12               | I/O ARCHITECTURE                                                                   |            |

|          |                  |                                                                                    |            |

|          | 12.1             | SCOPE                                                                              |            |

|          | 12.2             | SYSTEM MEMORY                                                                      |            |

|          | 12.3<br>12.4     | PRISM I/O SPACE AND DEVICE INTERRUPTS 12-<br>GRANULARITY OF I/O SPACE ACCESSES 12- |            |

|          | 12.4             | GRANULARITI OF 1/O SPACE ACCESSES 12                                               | -3         |

| •        |                  |                                                                                    |            |

| APPENDIX | K A              | INSTRUCTION SET SUMMARY                                                            |            |

|          |                  |                                                                                    |            |

|          | A.1              | ENCODING HINTS                                                                     | -1         |

|          | A.2              | FUNCTIONAL GROUP LISTING                                                           |            |

|          | A.3              | MNEMONIC LISTING                                                                   |            |

|          | A.4              | OPCODE LISTING                                                                     | 15         |

| •        |                  |                                                                                    |            |

| APPENDIX | K B              | PROGRAMMING HINTS                                                                  |            |

|          |                  |                                                                                    |            |

|          | B.1              | INTRODUCTION                                                                       |            |

|          | B.2              | INTEGER DIVIDE                                                                     |            |

|          | B.3<br>B.3.1     | FAST INTEGER DIVIDE BY FIXED INTEGERS                                              |            |

|          | 2.2.1            |                                                                                    |            |

Processor Base Register (PRBR) . . . . . . . . . .

Page Table Base Register (PTBR) . . . . . . . . .

System Control Block Base Register (SCBB) . . .

System Identification Register (SID) . . . . .

Software Interrupt Summary Register (SISR) . . .

Software Interrupt Request Register (SIRR) . . . 8-20

8-16

8-17

8-18

8-19

8-14

8-15

8-16

8-17

8-18

8-19

| CONTENTS |      | RESTRICTED DISTRIBUTION                       |         |  |

|----------|------|-----------------------------------------------|---------|--|

|          | 8-20 | System Serial Number Register (SSN)           | . 8-22  |  |

|          | 8-21 | Translation Buffer Check Register (TBCHK)     | . 8-23  |  |

|          | 8-22 | Translation Buffer Invalidate Single Register |         |  |

|          | 0 00 | (TBIS)                                        | . 8-25  |  |

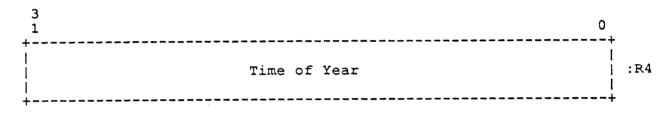

|          | 8-23 | Time of Year Register (TOY)                   | . 8-26  |  |

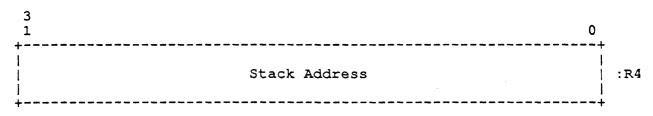

|          | 8-24 | User Stack Pointer (USP)                      | . 8-27  |  |

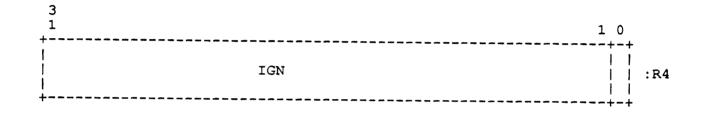

|          | 8-25 | Vector Enable Register (VEN)                  | . 8-28  |  |

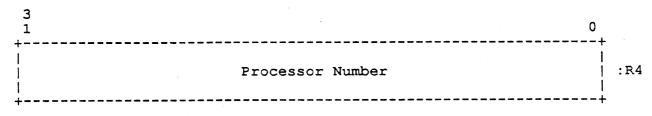

|          | 8-26 | Who-Am-I Register (WHAMI)                     | . 8-29  |  |

|          | 11-1 | Restart Parameter Block                       | . 11-4  |  |

|          | 11-2 | Per-Processor Portion of RPB                  | . 11-5  |  |

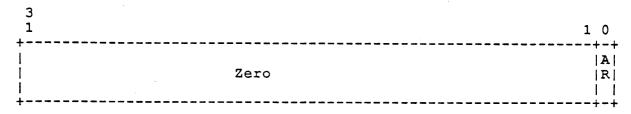

|          | 11-3 | Global Flags                                  | . 11-6  |  |

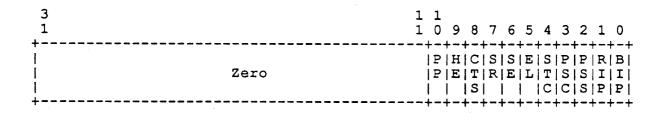

|          | 11-4 | State Longword                                | . 11-6  |  |

|          | 11-5 | Initial Virtual Memory Layout                 | . 11-8  |  |

|          |      |                                               |         |  |

| TABLES   |      |                                               |         |  |

|          | 6-1  | System Control Block Vector Assignments       |         |  |

|          | 6-2  | Processor State Transitions                   | . 6-39  |  |

|          | 8-1  | Internal Processor Register (IPR) Summary     | 8-2     |  |

|          | 9-1  | TB/Cache Invalidation                         | . 9-13  |  |

|          | 9-2  | When DRAINM (M) Or DRAINV (V)                 | . 9-19  |  |

|          | 11-1 | IPR Initialization                            | . 11-9  |  |

|          | 11-2 | Qualifiers for Examine and Deposit            | . 11-21 |  |

RESTRICTED DISTRIBUTION

CONTENTS

#### PREFACE

Several competitors and new start-ups are introducing simplified architecture machines and are claiming superior price/performance over VAX. There are currently about a dozen such companies offering machines with RISC architecture (e.g. SUN, MIPS), vector processing (e.g., Convex, Scientific Computer Systems), symmetric multiprocessing (e.g., Encore, Sequent), and fine-grained parallel processing (e.g., Alliant) capabilities.

Most of these competitors are targeting the high end of the VAX market, which is our most profitable product space. Some are targeting the low end of our product family where simplified architectures offer cheaper and faster custom CMOS implementations than VAX.

Several advanced development and research projects within DIGITAL, and projects elsewhere in the computer industry, have produced results substantiating our competitor's claims and questioning the viability of the VAX architecture to sustain DIGITAL through the 1990's.

In response to this challenge, a strategic effort has been initiated within the company to define a new architecture that will complement our current VAX/VMS and VAX/ULTRIX offerings and provide DIGITAL with a competitive architecture through the 1990's and beyond.

The following lists summarize the assumptions, constraints, goals, and non-goals that have been set for the architecture.

#### Assumptions:

- 1. Simplified architectures show promise for reducing complexity while improving cost/performance and making higher absolute performance possible when compared with VAX.

- 2. Vector processing, multiprocessing, and parallel processing are well enough understood to make them a science (rather than a black art), and therefore, are essential to attaining a competitive architecture.

- 3. Neither DIGITAL nor its customers can afford the resources necessary to support an open architecture philosophy, but rather must be able to leverage software investments across an entire family of compatible products. This implies that any new architecture must be rigid and not allow the instruction set or privileged architecture to be changed from implementation to implementation.

- 4. The design work that must be performed is similar to the VAX architectural effort. An architectural document, at the same level of detail as produced for VAX, must be produced to guide implementations of the new architecture. It is required that this document receive wide review within the technical community and the company in general. When completed and accepted, the architecture will be placed under ECO control and managed by a central architecture group.

- 5. The architecture will be compatibly extended over time, and will allow subsets. Each extension will be subsettable and become a permanent part of the architecture which all implementations must adhere to. Features of the architecture that are subsetted in a particular implementation must be emulated transparently in software.

- 6. VAX compatibility is very important, especially with respect to the way memory is addressed and data is stored. This can be achieved with a combination of software and hardware rather than with just a hardware structure itself.

- 7. A VMS-like operating system environment can be constructed with a compatible file system, network, and user interface, and a functionally compatible set of system services.

- 8. ULTRIX will be ported to the new architecture and remain compatible with both the VAX and PDP-11 implementations. An ongoing effort will be made to ensure that all. implementations of ULTRIX remain compatible.

- 9. Any new architecture must fit into the DIGITAL computing environment and allow connection to local area networks, systems, and clusters.

- 10. The architecture will be extended in the future to accomodate a larger virtual address space.

# Architectural Constraints:

- 1. The architecture must make it possible to efficiently support VAX data types. This support can be achieved with a combination of software and hardware.

- 2. The architecture must support VAX-compatible memory addressing.

- 3. The architecture must provide a VAX-compatible interlock capability so that it is possible to connect VAX processors and I/O peripherals to common memory systems.

- 4. The architecture must support the execution of identical program images on all implementations.

- 5. The scalar architecture must provide greater than a factor of two improvement in cost/performance over a VAX implementation using the same technology.

# Architectural Goals:

- 1. To make it possible to build machines that are as good or better than the competition and have higher absolute performance limits than VAX.

- 2. To define an architecture that is inherently easier to implement than VAX and thus allows shorter development cycles, or alternatively, allows more effort to be expended on performance while holding the development cycle constant.

- 3. To make it attractive to implement the architecture without microcode.

- 4. To allow for easy pipelining and parallel instruction execution directly in the architecture, as opposed to esoteric implementation complexity to gain performance.

- 5. To provide integral vector processing capabilities.

- To allow for symmetric multiprocessing as well as other forms of parallel processing.

- 7. To provide an extensible architecture with rules for subsettability.

- 8. To provide a corporate architecture for the 1990's that is more competitive than VAX and provides more inherent growth capability.

- 9. To remedy anticipated deficiencies and limitations in the VAX architecture (e.g., number of general registers, page size, physical address space, vector processing etc.).

- 10. To provide the functional capabilities of the VAX privileged architecture in a more simplified and easier-to-implement form.

- 11. To make it easy for customers to move applications to the new architecture from VAX.

- 12. To allow unprivileged VMS and ULTRIX layered products that are written in a higher-level language to be moved to the new architecture via recompilation, without loss of language semantics or file and data type compatibility.

- 13. To allow for the implementation of a security kernel.

# Specific Non-Goals:

- 1. To include a VAX compatibility mode.

- 2. To support UNIBUS/QBUS/MASSBUS peripherals.

- 3. To translate VAX macrocode transparently and efficiently.

- 4. To address non-architectural issues such as the implementation of fault tolerant systems.

- To support D\_floating, H\_floating, or decimal data types directly in hardware.

- 6. To support efficient handling of unaligned operands.

# Revision History:

Revision 3.0, 26 April 1988

1. Minor changes.

Revision 2.0, 24 June 1986

1. No changes

Revision 1.0, 22 December 1985

- General rewrite and rephrasing of the introduction, assumptions, architectural constraints, and architectural goals.

- 2. Dropped all references and comparisons with RISC architectures.

- 3. Added assumption that vector processing, multiprocessing, and parallelism are essential for a competitive new architecture.

- 4. Added the assumption that the architecture must allow for competitive and cost effective chip implementations.

- Added a goal to provide integral vector processing capabilities.

Revision 0.0, July 5, 1985

1. First review distribution.

#### RESTRICTED DISTRIBUTION

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 INTRODUCTION

١

The difficulty in building cost-effective, high-performance VAX processors, and the competitive pressure due to recent architectural developments has motivated the design of the PRISM (Parallel Reduced Instruction Set Machine) architecture.

The following sections of this introduction describe:

- 1. Why building a high-end VAX is difficult. \

- An overview of the PRISM architecture.

- 3. The PRISM advantages and disadvantages.

- 4. The constraints and limitations of VAX compatibility on PRISM.

- 5. Terminology and conventions used in this document.

# 1.2 DIFFICULTIES IN BUILDING A HIGH PERFORMANCE VAX

VAX is a complex architecture with a large number of intra-instruction and inter-instruction conflicts, which make it difficult to build cost-effective implementations.

Intra-instruction conflicts, in both decode and execution, make pipelining techniques difficult to use. Some examples are:

- o The variable instruction lengths and complex operand specifiers require a large amount of instruction decode and conflict-detection logic. VAX instructions can range from 1 byte to over 50 bytes in length, depending on the operand specifiers used.

- o The side effects of autoincrement and autodecrement specifiers make pipelining, and the coordinated update of multiple register file copies, difficult.

- o Specifying memory operand requests in the same instruction that operates on the data either degrades performance (because the execution unit must wait for the operand) or increases the cost to buffer the instruction and operands in order to pipeline the operation. Fetching a memory operand requires address calculation, address translation, and cache lookup. This will always be slower than reading a general register. VAX has insufficient registers in which to load memory operands prior to operating on the data; 16 are just not enough, especially when four are dedicated to fixed functions.

- o The indirect specifiers require two memory references to fetch the operand, making the execution unit wait until the operand arrives. Alternatively, other architectures allow these two references to be separated and scheduled.

- o Complex branch instructions, such as Branch on Bit (BBx) and Add Compare and Branch (ACBx), may require several memory references and execution cycles before the branch decision is known. These instructions also have the branch displacement at the end of the instruction requiring several cycles of specifier decode before the branch destination is known.

- o Instructions like POPR and RSB have implied operands and implied register modification.

- o The bit field instructions require special checks to determine whether the operand is in a register or memory and then additional checks to determine reserved operands.

- o Compound instructions, such as CALL and POLY, encounter internal conflicts during execution where the hardware must stall because it has no other work to do. In addition, these instructions must read data operands to determine the semantics of the instruction.

Inter-instruction conflicts make parallel execution and out-of-order completion of VAX instructions very difficult. Some examples are:

- o Virtually every instruction alters the condition codes, so the test or compare instruction can never be separated from the conditional branch instruction with intervening instructions. This means that in a pipelined implementation the conditional branch is stalled waiting for the condition codes from the immediately preceding instruction. Branch prediction could be implemented, but this further complicates the design and increases branch latency when the prediction is wrong.

- o The register interlock and bypass logic is complicated by implied register operands, quadword and octaword register writes starting at an arbitrary register, and byte and word write merges into the general registers.

Most of the general functionality in the VAX architecture is infrequently used. Studies of operand specifier usage have shown that register, short literal, register deferred, and displacement mode operand specifiers constitute 85% to 95% of all operand specifiers used. The bit field instructions can take arbitrary specifiers for

the size and position operands, but in one study over 90% of the size and position specifiers were short literals. \

# 1.3 PRISM ARCHITECTURE OVERVIEW

The design of the PRISM architecture was guided by:

- o The cost/performance and higher absolute performance advantages of simplified instruction set architectures.

- o Advances in compiler technology. In particular, the ability to compile procedures inline, better register allocation algorithms, and instruction scheduling.

- o A processor organization model that allows parallel instruction execution and out-of-order instruction completion.

- o The ability to implement both chip-level and high-end machines.

- o The declining cost of memory.

PRISM has some of the characteristics of the so-called RISC architectures but a better comparison would be the CRAY machines. Below is a brief overview of the PRISM instruction set characteristics followed by a description of how a pipelined processor might be implemented.

# 1.3.1 Instruction Set Characteristics

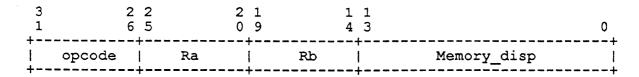

- o All instructions are 32 bits long and have a regular format.

- o There are 64 scalar registers (R0 through R63), each 32 bits wide. R0 reads as zero and writes to R0 are ignored. R1 is the current stack pointer and is referred to as SP.

- o There are 16 vector registers (V0 through V15), each containing 64 elements, 64 bits wide. There is a 7-bit Vector Length register (VL), a 7-bit Vector Count register (VC), and a 64-bit Vector Mask register (VM).

- o All scalar data manipulation is between scalar registers, with up to two register source operands (one may be an 8-bit literal) and one register destination operand.

- o All vector data manipulation instructions get their source operands from one or two vector registers and write their results to a destination vector register.

- o All memory reference instructions are of the load/store type that move data between scalar or vector registers and memory.

- o There are no branch condition codes. Branch instructions test a scalar register value which may be the result of a

previous compare.

- o Integer and logical instructions operate on longwords.

- o Floating-point instructions operate on G\_floating and F\_floating operands.

# 1.3.2 Pipelined Processor Model

The processor model that guided the architecture definition consists of multiple pipelined function units, each of which executes a class of instructions. For example, one function unit for the load/store instructions, one for shifts, one for floating add/subtract, one for integer and floating multiply, and one for integer and floating divide. The multiply and divide units may or may not be pipelined.

The following outline shows one way to organize a pipelined design of the PRISM architecture. It should be emphasized that this is only one model; other implementation models are also possible.

- 1. Instruction fetch The instruction to execute is fetched from the instruction cache.

- 2. Instruction decode and issue The instruction is broken down into its constituent parts and data-independent control and address signals are generated. Before an instruction can begin execution ("issue"), several constraints must be satisfied:

- o All source and destination registers for the instruction must be free, i.e., there must be no outstanding writes to a needed register from prior instructions.

- o The register write path must be available at the future cycle in which this instruction will store its result. Only one result can be stored into the registers per cycle. All instructions, with the exception of loads, have a fixed, data-independent execution time. Loads are predicted on the basis of cache hits.

- o The function unit to be used by the instruction during execution must be free. All units, with the exception of divide, are pipelined and can accept a new scalar instruction each machine cycle. The divide unit is iterative and will accept a new instruction when the previous divide instruction completes. A vector instruction reserves the function unit for the duration of the vector operation.

When a memory load/store instruction experiences a cache miss, at some point the load/store unit busy flag will cause subsequent load/store instructions to hold-issue until the miss completes.

When an instruction does issue, the destination register and write path cycle for the result are reserved.

- 3. Operand setup All instruction-independent register addresses are generated, operands are read and latched, and data-dependent control signals are generated.

- 4. Instruction execution The instruction operands and control signals are passed to a function unit for execution.

- 5. Result store The result from the function unit is stored in the register files or the cache as necessary.

Although this list is sequential, the five activities can be pipelined. For instance, making control signals data-independent and instruction formats regular means that more instruction decode and operand access can be done in parallel, with less logic and greatly simplified control.

Once an instruction is issued, it may take multiple cycles before the result of the calculation is available. Meanwhile, in the next cycle the next instruction can be decoded and, if all its issue conditions are satisfied, it can be issued. Therefore, instructions are decoded and issued in I-Stream order but because of the varying execution times of different operations the results can be stored into the registers out of I-Stream order. This complicates exception handling and hardware retry of failing instructions; however, these are rare events and the substantial performance gain and hardware savings from out-of-order completion of compiler-scheduled code favors this trade-off.

The regular nature of the instruction set and implementation result in a simple set of rules that compilers can use to schedule instructions and thereby increase performance through parallel instruction execution.

#### 1.4 ADVANTAGES AND DISADVANTAGES OF PRISM

The characteristics of the PRISM architecture will allow developers to build processors with substantially more performance than a VAX for the same hardware cost in the same technology. The reasons for this are:

- 1. Fixed-length, quickly decoded instructions.

- 2. 64 scalar registers to reduce memory references and provide more temporary registers for compiler instruction scheduling and procedure use.

- 3. Parallel instruction execution and out-of-order instruction completion.

- 4. No branch condition codes.

- 5. No complex compound instructions with internal data dependencies, e.g., CALL/RET, CASE, ACBx, INSV/EXTV, Decimal. Inline code for complex functions will be better than VAX microcode because:

- A compiler can pick the best code based on the knowledge it has and can eliminate special checks, e.g., string

overlap, procedure entry mask, sign of ACBx loop increment, whether a bit field is in a register or memory.

- VAX microcode must maintain additional state so that in the event of an exception or interrupt it can either backup the instruction or save enough state to continue using First Part Done.

- VAX microcode must make many reserved operand checks that add overhead, e.g., size and position operands in bit field instructions with different checks depending on whether the bit field is in registers or memory.

- 6. No microcode is required for instruction decode or execution.

- 7. A small instruction set emphasizing high frequency operations. Far less logic is spent on functionality that does not contribute to performance.

- 8. A larger branch displacement (22 bits versus 8 bits on VAX) eliminates double branches for conditional branches.

- 9. A larger page size (8 Kbytes) improves Translation Buffer (TB) effectiveness and allows the cache and TB lookup to occur in parallel.

#### The disadvantages of the PRISM architecture are:

- 1. PRISM programs may require 2 to 3 times the code size (in bytes) over VAX with a corresponding increase in instruction stream bandwidth. However, this trade-off is preferred because instruction cache miss rates are low and it is easier to build more instruction stream bandwidth than massive parallel instruction stream decode.

- 2. The 8-Kbyte page size will result in more memory fragmentation. Declining memory costs will help offset this.

- 3. Unaligned references will be slower because they may be implemented by macrocode.

- 4. Context switch time will increase because of the additional scalar registers that must be saved and restored.

#### 1.5 VAX COMPATIBILITY

The PRISM architecture was constrained in a number of ways to support our existing VAX customer base. The goal is to make it both possible and easier for a VAX customer to integrate PRISM with VAX and to move an application to PRISM rather than to a competitor's machine. This goal impacts both the architecture and the system software.

1. The architecture uses VAX data types and allows byte addressing of memory.

The PRISM language compilers will retain their VAX-specific language semantics, e.g., data types and parameter passing, thus allowing customers to recompile most VAX programs without alteration.

#### 1.5.1 Compatibility Limitations

There are some compatibility limitations between PRISM and the VAX architecture that may require changes to some high-level language programs in order to run them on PRISM:

- 1. Floating-point arithmetic There are no PRISM instructions to compute D\_floating and H\_floating results. These operations can be performed by software emulation.

- PRISM has neither VAX POLY nor EMOD instructions. These instructions keep extra quard bits.

- 2. Memory protection granularity PRISM has a page size larger than VAX. Therefore, VAX programs which rely on 512-byte protection granularity will not work.

- 3. Exceptions Instructions may have been executed after an instruction that signals an arithmetic exception. Exception handlers that assume no further instructions have been executed will not work without changes to make the exception precise.

- 4. Dynamic instruction creation Programs which dynamically construct and execute VAX instruction sequences and/or calculate addresses or offsets based on the sizes of VAX instructions will not work.

- 5. Instruction atomicity Programs that rely on the atomicity of VAX instructions may not work, e.g., a multi-threaded application (such as an AST routine) in which shared memory data is guaranteed to be in a consistent state only between VAX instructions with no other means of synchronization being used. Any uninterruptable VAX instruction which makes more than one memory reference, e.g., INCL mem or ADDL3 mem1, mem2, mem3, could be used in this way. On PRISM the operation would require multiple instructions and, depending on where a thread was interrupted, stale data could be used.

- 6. Data structures Code that depends upon VAX architected data structures such as the VAX PSL or call frames will not work.

- 7. PRISM supports a multiprocessing model that is different from VAX. The ordering of writes to memory is not specified by the PRISM architecture except at interlock boundaries. This means that shared data must be accessed only after acquiring a semaphore variable with an interlocked operation.

- 8. The granularity of sharing in a multiprocessor system is a longword on PRISM and byte on VAX.

# 1.5.2 Why No VAX Compatibility Mode Is Provided

VAX compatibility mode is not provided in the PRISM architecture (in the same way that PDP-11 compatibility mode is provided on VAX) for the following reasons:

- 1. The complexity of the VAX architecture would make it very expensive and difficult to provide a VAX compatibility mode with reasonable performance. VAX requires complex instruction decode logic, special data path support, e.g., condition codes, different memory management, and a microcode control store. This would defeat the purpose of a simplified architecture.

- 2. The majority of applications are written in high-level languages and can be recompiled. If programs are not recompiled the performance gain from the additional PRISM scalar registers, vector registers and instruction scheduling is lost.

- 3. The desirable software goal is to network PRISM and VAX processors so customer applications on VAX systems can share data with applications on PRISM. Customers will already own VAX systems on which to run those applications that they don't wish to port to PRISM.

#### 1.6 TERMINOLOGY AND CONVENTIONS

#### 1.6.1 Numbering

All numbers are decimal unless otherwise indicated. Where there is ambiguity, numbers other than decimal are indicated with the name of the base following the number in parentheses, e.g., FF (hex).

#### 1.6.2 UNPREDICTABLE And UNDEFINED

RESULTS specified as UNPREDICTABLE may vary from moment to moment, implementation to implementation, and instruction to instruction within implementations. Software can never depend on results specified as UNPREDICTABLE.

OPERATIONS specified as UNDEFINED may vary from moment to moment, implementation to implementation, and instruction to instruction within implementations. The operation may vary in effect from nothing, to stopping system operation. UNDEFINED operations must not cause the processor to hang, i.e., reach an unhalted state from which there is no transition to a normal state in which the machine executes instructions.

Note the distinction between result and operation. Non-privileged software cannot invoke UNDEFINED operations.

# INTRODUCTION REST TERMINOLOGY AND CONVENTIONS

# 1.6.3 Ranges And Extents

Ranges are specified by a pair of numbers separated by a ".." and are inclusive, e.g., a range of integers 0..4 includes the integers 0, 1, 2, 3, and 4.

Extents are specified by a pair of numbers in angle brackets separated by a colon and are inclusive; e.g., bits <7:3> specify an extent of bits including bits 7, 6, 5, 4, and 3.

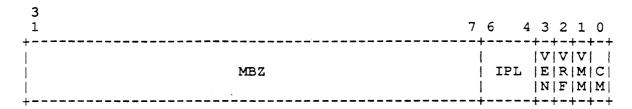

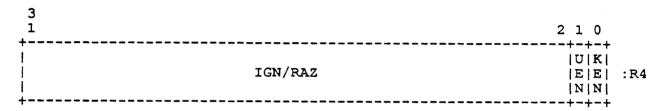

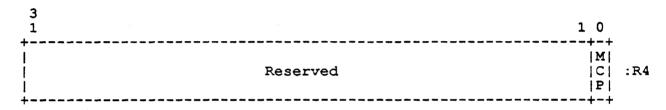

# 1.6.4 Must Be Zero (MBZ)

Fields specified as Must Be Zero (MBZ) must never be filled by software with a non-zero value. If the processor encounters a non-zero value in a field specified as MBZ, an Illegal Operand exception occurs. See Chapter 6, Exceptions and Interrupts, Section 6.4.4.

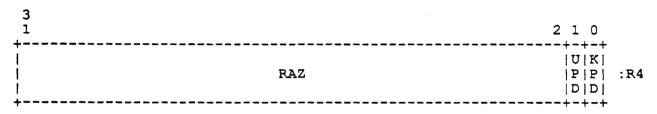

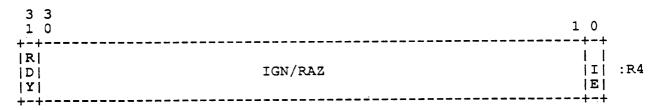

#### 1.6.5 Read As Zero (RAZ)

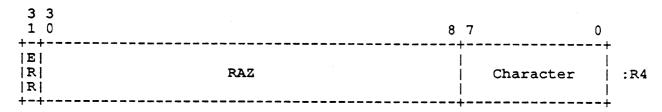

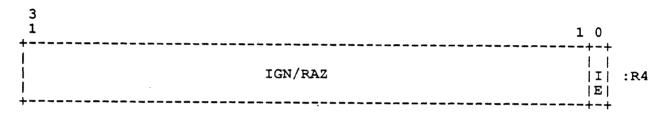

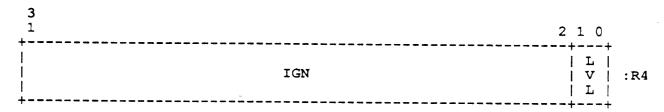

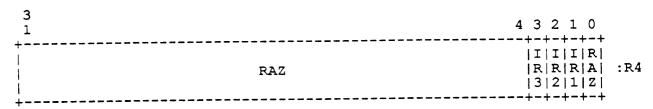

Fields specified as Read As Zero (RAZ) return a zero when read.

#### 1.6.6 Should Be Zero (SBZ)

Fields specified as Should Be Zero (SBZ) should be filled by software with a zero value. These fields may be used at some future time. Non-zero values in SBZ fields produce UNPREDICTABLE results.

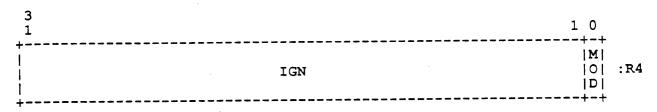

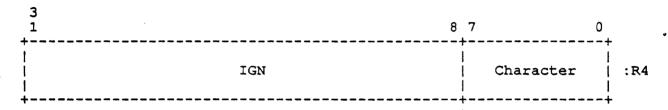

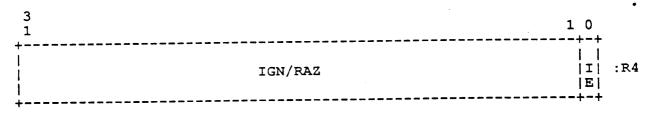

# 1.6.7 Ignore (IGN)

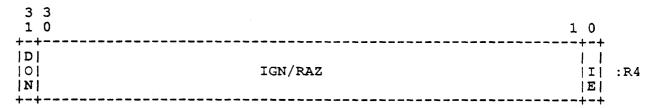

Fields specified as Ignore (IGN) are ignored when written.

# 1.6.8 Figure Drawing Conventions

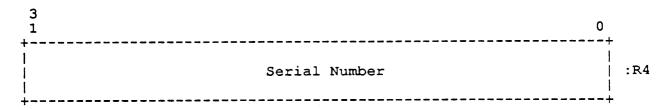

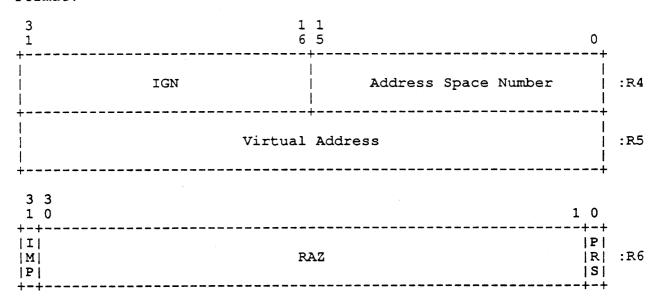

Figures which depict registers or memory follow the convention that increasing addresses run right to left and top to bottom.

#### NOTE

\A note on the manual format: At certain points in the manual, comments on why certain decisions were made, unresolved issues, etc., are between a pair of backslashes. These comments provide additional clarification and will be removed from externally distributed editions.\

# Revision History:

# Revision 3.0, 26 April 1988

1. Minor updates to reflect software strategy for PRISM.

# Revision 2.0, 24 June 1986

- 1. Typographical corrections and clarifications.

- 2. Vector Length register changed from 6 to 7 bits.

# Revision 1.0, 22 December 1985

- 1. Change register width from 64 bits to 32 bits.

- 2. Remove PC from scalar registers.

- 3. Specify R0 reads zero, writes are ignored.

- 4. Specify SP mapped to register R1.

- 5. Add vector registers.

# Revision 0.0, 5 July 1985

1. First review distribution.

#### RESTRICTED DISTRIBUTION

#### CHAPTER 2

#### BASIC ARCHITECTURE

#### 2.1 ADDRESSING

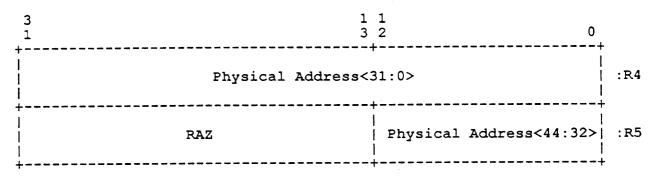

The basic addressable unit in PRISM is the 8-bit byte. Virtual addresses are 32 bits long; hence, the virtual address space is 2\*\*32 (approximately 4.3 billion) bytes. Virtual addresses as seen by the program are translated into physical memory addresses by the memory management mechanism described in Chapter 5, Memory Management.

#### 2.2 DATA TYPES

#### 2.2.1 Byte

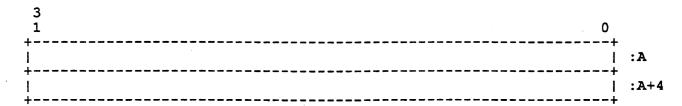

A byte is eight contiguous bits starting on an addressable byte boundary. The bits are numbered from right to left, 0 through 7:

Figure 2-1: Byte Format

A byte is specified by its address A. A byte is an 8-bit value. The byte is only supported in PRISM by zero extended load and store instructions.

#### 2.2.2 Word

A word is two contiguous bytes starting on an arbitrary byte boundary. The bits are numbered from right to left, 0 through 15:

Figure 2-2: Word Format

A word is specified by its address A, the address of the byte containing bit 0. A word is a 16-bit value. The word is only supported in PRISM by zero extended load and store instructions.

#### NOTE

PRISM implementations are likely to impose a significant performance penalty on access to word operands that are not naturally aligned. (A naturally aligned word has zero as the low-order bit of its address.)

#### NOTE

On many of the VAX implementations unaligned operands incurred approximately a 2x performance penalty, i.e., two memory references instead of one. It is expected that most PRISM implementations will implement unaligned accesses via software exceptions with the operating system providing emulation of the load or store of the unaligned data. The performance penalty may be expected to be up to 100x, depending on the particular implementation.

# 2.2.3 Longword

A longword is four contiguous bytes starting on an arbitrary byte boundary. The bits are numbered from right to left 0 through 31:

Figure 2-3: Longword Format

A longword is specified by its address A, the address of the byte containing bit 0. A longword is 32-bit value. When interpreted arithmetically, a longword is a two's complement integer with bits of increasing significance going 0 through 30. Bit 31 is the sign bit. The value of the integer is in the range -2,147,483,648..2,147,483,647. For performing addition, subtraction, multiplication, and comparison, PRISM instructions also provide direct support for the interpretation of a longword as an unsigned integer with bits of increasing significance going 0 through 31. The value of the unsigned integer is in the range 0..4,294,967,295.

#### NOTE

PRISM implementations are likely to impose a significant performance penalty when accessing longword operands that are not naturally aligned. (A naturally aligned longword has zero as the low-order two bits of its address.)

#### 2.2.4 Quadword

A quadword is eight contiguous bytes starting on an arbitrary byte boundary. The bits are numbered from right to left 0 through 63:

Figure 2-4: Quadword Format

A quadword is specified by its address A, the address of the byte containing bit 0. A quadword is a 64-bit value. The quadword is only supported in PRISM by load and store instructions.

#### NOTE

PRISM implementations are likely to impose a significant performance penalty when accessing quadword operands that are not naturally aligned. (A naturally aligned quadword has zero as the low-order three bits of its address.)

## 2.2.5 F\_floating

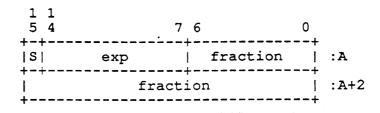

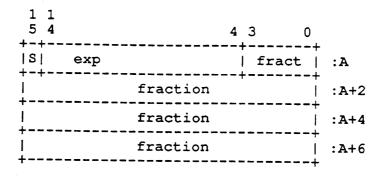

An F\_floating datum is four contiguous bytes starting on an arbitrary byte boundary. The bits are labeled from right to left 0 through 31.

Figure 2-5: F floating Format

An F\_floating datum is specified by its address A, the address of the byte containing bit 0. The form of an F\_floating datum is sign magnitude with bit 15 the sign bit, bits <14:7> an excess 128 binary exponent, and bits <6:0> and <31:16> a normalized 24-bit fraction with the redundant most significant fraction bit not represented. Within the fraction, bits of increasing significance go from 16 through 31 and 0 through 6. The 8-bit exponent field encodes the values 0 through 255. An exponent value of 0, together with a sign bit of 0, is taken to indicate that the F\_floating datum has a value of 2ero, the instruction always produces a datum with a sign bit of 0, an exponent of 0, and all fraction bits of 0. Exponent values of 1.255 indicate true binary exponents of -127.127. An exponent value of 0, together with a sign bit of 1, is taken as reserved. Floating-point instructions processing a reserved operand take an Arithmetic exception (see Chapter 6, Exceptions and Interrupts, Section 6.4.1). The value of an F\_floating datum is in the approximate range 0.29\*10\*\*-38..1.7\*10\*\*38. The precision of an F\_floating datum is approximately one part in 2\*\*23, i.e., typically 7 decimal digits.

#### NOTE

PRISM implementations are likely to impose a significant performance penalty when accessing F floating operands that are not naturally aligned. (A naturally aligned F floating datum has zero as the low-order two bits of its address).

# 2.2.6 G\_floating

A G\_floating datum is eight contiguous bytes starting on an arbitrary byte boundary. The bits are labeled from right to left 0 through 63:

Figure 2-6: G\_floating Format

A G\_floating datum is specified by its address A, the address of the byte containing bit 0. The form of a G\_floating datum is sign magnitude with bit 15 the sign bit, bits <14:4> an excess 1024 binary exponent, and bits <3:0> and <63:16> a normalized 53-bit fraction with the redundant most significant fraction bit not represented. Within the fraction, bits of increasing significance go from 48 through 63, 32 through 47, 16 through 31, and 0 through 3. The 11-bit exponent field encodes the values 0 through 2047. An exponent value of 0, together with a sign bit of 0, is taken to indicate that the G\_floating datum has a value of 0. If the result of a floating point instruction has a value of zero, the instruction always produces a datum with a sign bit of 0, an exponent of 0, and all fraction bits of 0. Exponent values of 1.2047 indicate true binary exponents of -1023.1023. An exponent value of 0, together with a sign bit of 1, is taken as reserved. Floating-point instructions processing a reserved operand take an Arithmetic exception (see Chapter 6, Exceptions and Interrupts, Section 6.4.1). The value of a G floating datum is in the approximate range 0.56\*10\*\*-308.0.9\*10\*\*\frac{3}{3}08. The precision of a G floating datum is approximately one part in 2\*\*52, i.e., typically \frac{15}{15} decimal digits.

#### NOTE

PRISM implementations are likely to impose a significant performance penalty when accessing G\_floating operands that are not naturally aligned. (A naturally aligned G\_floating datum has zero as the low-order three bits of its address.)

# 2.2.7 Data Types With No Hardware Support

The following VAX data types are not directly supported in PRISM hardware, (see the VAX Architecture Standard for detailed information on these data types).

- o Octaword

- o D\_floating

- o H floating

- o Variable Length Bit Field

- o Character String

- o Trailing Numeric String

- o Leading Separate Numeric String

- o Packed Decimal String

- o Queues

Revision History:

Revision 3.0, 26 April 1988

1. Dirty zero cannot be produced as a floating point result.

Revision 2.0, 24 June 1986

1. Minor edits.

Revision 1.0, December 22, 1985

- Removed signed and unsigned descriptions for Byte, Word, and Quadword.

- 2. Changed formatting as per Rev 1.0 format.

Revision 0.0, July 5, 1985

1. First Review Distribution

#### RESTRICTED DISTRIBUTION

#### CHAPTER 3

#### INSTRUCTION FORMATS

#### 3.1 PRISM REGISTERS

## 3.1.1 Scalar Registers

There are 64 scalar registers (R0 through R63), each 32 bits wide. R1 is the stack pointer (SP).

When R0 is specified as a register source operand, a zero valued operand is supplied. When R0 is specified as a register destination, the result of the operation is discarded. If an exception is detected during the execution of an instruction that specifies R0 as the destination, it is UNPREDICTABLE whether or not the exception is actually signaled.

Some instructions read and write quadword register operands. Quadword register operands must be specified in even-odd register pairs. Bits <31:0> of the quadword are in the even register and bits <63:32> are in the odd register. If bit <0> of an instruction register field specifying a quadword operand is not 0, the result of the operation, including exception signaling, is UNPREDICTABLE.

When R0 is specified as a quadword source operand, bits <31:0> are zero and bits <63:32> are UNPREDICTABLE. When R0 is specified as a quadword destination, bits <31:0> are ignored (IGN) and bits <63:32> (the contents of R1) are UNPREDICTABLE.

#### 3.1.2 Vector Registers

There are 16 vector registers, V0 through V15. Each vector register contains 64 elements numbered 0 through 63 and each element is 64 bits wide. A vector instruction that operates on longword or F\_floating data reads bits <31:0> of each source element and writes a result in bits <31:0> of each destination element. Depending on the specific instruction, bits <63:32> of each destination element may receive bits <63:32> of one of the source operands, or may be UNPREDICTABLE.

If the same vector register is used as both a source and a destination in a Vector Gather (VGATH) instruction, the result of the operation is UNPREDICTABLE.

The 7-bit Vector Length register (VL) controls how many vector elements are processed. VL is loaded before executing a vector instruction. The value in VL may range from 0 to 64. A value greater

than 64 produces UNPREDICTABLE results. A value of zero means that no elements are processed. Once loaded, VL specifies the number of elements processed in all subsequent vector instructions until VL is loaded with a new value. Elements beyond VL in the destination vector register are not modified.

The Vector Mask register (VM) has 64 bits, each corresponding to an element in a vector register. Bit 0 corresponds to vector element 0.

The 7-bit Vector Count register (VC) receives the length of the offset vector generated by the IOTA instruction.

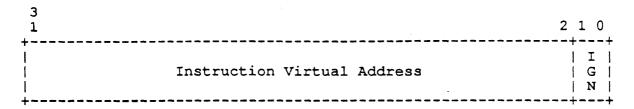

# 3.1.3 Program Counter

The Program Counter (PC) is a special register that addresses the instruction stream. As each instruction is decoded the PC is advanced to the beginning of the next sequential instruction. This is referred to as the "updated PC." Any instruction that uses the value of the PC will use the updated PC. The PC includes only bits <31:2> with bits <1:0> treated as RAZ/IGN. This quantity is a longword aligned byte address. The PC is not mapped to a scalar register, rather it is an implied operand on conditional branch and subroutine jump instructions.

# 3.1.4 Cycle Count Register

The Cycle Count register is a 64-bit register that counts processor cycles. Its resolution is within 128 cycles. It is saved and restored in the Hardware Process Control Block (see Chapter 7) by the Swap Process Context Instruction. It can be read with a Read Cycle Count Register instruction (see page 4-83.). It can be written in kernel mode by the Write Cycle Count Register instruction (see page 4-102.) When the 64-bit count overflows, the counter wraps around to zero.

#### 3.2 NOTATION