# The PRISM Extended Calling Standard

Version 0.7

# March 1988

**DEC Proprietary & Confidential—Do Not Copy**

This document and information contained in it is NOT TO BE DISCLOSED outside Digital Equipment Corporation without written authorization of the PRISM Systems Manager

**Digital Equipment Corporation**

#### Preface

This document summarizes that part of the PRISM Common Software Architecture that corresponds to the calling standard, and describes the conventions governing the run time environment of PRISM programs.

This document defines the run time data structures, constants, algorithms, conventions, methods, and functional interfaces that enable a a user mode procedure to operate correctly in a multilanguage environment on PRISM systems.

All contents of this document apply to both PRISM ULTRIX and MICA. This document specifies the PRISM-specific user mode run time environment which is common and compatible across both operating systems.

Calling standard conventions covered in this document include:

- Register use

- Linkage section

- Invocation descriptors

- Call conventions

- Call stack and frame structure

- Entry and return code sequences

- Exception synchronization and memory synchronization

- Procedure values

- Argument passing mechanisms

- Argument list structure

- Argument descriptors

- Argument data types

- Function value return

- Status codes and condition values

- Rules for FLBC usage and the FLBC displacement field

- Condition handling

- Stack unwinding

- Asynchronous software conditions

- Use of R3 and user mode thread context

- Address values in reserved pages (page zero, page maximum, etc.)

- Stack limit checking

- Alignment rules

- Standard record mappings

This calling standard is a component of the larger PRISM Common Software Architecture, and depends on certain standards and conventions which are not described by this document. Those standards, described by other documents, include:

- Heap memory management and dynamic string management

- Names and naming conventions

- Object language and object file format

- Status values and message definition, formatting, and reporting

- Common Multithread Architecture

## Conventions Used in This Document

The definitions in this standard are presented as follows.

#### Data Structures

Data structures are defined in terms of the physical memory layout that must be used for each structure in the PRISM-32 environment.

#### Constants

Constants are presented symbolically. An appendix provides the symbolic to literal translation for each constant.

# **Algorithms**

Algorithms are presented precisely, as a series of steps, in American language.

#### Conventions

All conventions that are important to correct program execution are presented precisely, in a form appropriate to each convention.

#### Methods

Actual or recommended methods are presented informally, using examples, suggestions, or other appropriate form.

## **Functional Interfaces**

Functional interfaces are presented in precise abstract form. The semantic capabilities of each functional interface are defined. The language-level interface syntax is not defined.

For each high level language, each PRISM system must provide an appropriate concrete interface to each abstract functional interface defined by this standard.

All text enclosed in double backslashes, illustrated by this paragraph, is editorial comment, is not formally a part of the standard, and will not necessarily be in future revisions of this document. 11

# **Revision History**

# Version 0.1: Initial Proposals, July 1985—R. Grove, M.D. MacLaren

Initial proposals.

### Version 0.2: First Distribution, July 1986—C. Nylander

Reflect revision of hardware architecture.

Numerous minor technical revisions and additions.

Cleanup and format for first distribution as Base Document.

# Version 0.3: Internal Working Version, November 1986—C. Nylander

Rewrite and reorganize.

Revise in response to comments on first distribution.

Revise scalar register conventions to provide more argument and scratch registers.

Add vector register conventions.

Revise entry descriptor layout and encoding.

Delete dynamic condition handling.

Add reinvokable condition handlers.

Make condition handler specification self-relative.

Revise scalar register saving algorithm.

Elaborate argument passing mechanisms.

Add argument list structure and algorithms.

Add argument datatypes.

Add argument descriptors.

Add function value return.

Revise stack limit checking technique.

# Version 0.4: Internal Working Version, December 1986—C. Nylander

Delete standard parent frame pointer (R12), move R22 (argument list address) to R12.

Change RTL\_BASE to TEB\_BASE.

Add justification for vector register conventions.

Clarify restrictions on lightweight procedures.

Change Entry Descriptor to Frame Descriptor.

Revise frame descriptors to support vector register save/restore.

Revise rules for FP<2:0>.

Revise call frame layout.

Add procedure synchronization rules.

Clarify argument passing mechanisms.

Clarify argument list structure.

Add vector register saving algorithm.

Revise physical format of descriptors for better uniformity and run time efficiency.

Add bit string descriptors.

Define semantics of text string descriptors.

Define function value return by descriptor.

Add sections describing user mode thread architecture.

Add summary of scope and applicability.

Add guidelines section.

Revise usage of "condition" and "exception" to be as consistent with Working Design Document as possible.

# Version 0.5: Second Distribution, January 1987—C. Nylander

Expand examples.

Cleanup for second distribution as Extended Calling Standard.

# Version 0.6: Internal Working Version, January 1988—C. Nylander

Many miscellaneous clarifications and corrections resulting from review comments.

Minor reorganization.

Add condition handling, signals, and unwinding.

Clarify that entry addresses in invocation descriptors are absolute.

Make R4:R5 destroyable between calling and called routines (e.g. by the auto-loader).

Disallow quadword immediate arguments in standard calls.

Change algorithm for packing procedure arguments in registers.

Disallow descriptors that specify overlapping elements.

Re-do descriptors to unify string and 1 dimensional array descriptors.

Clarify rules for set types in arguments and function value return.

Clarify reference mechanism for returning strings and arrays.

Add new mechanisms for returning function values by descriptor: into fixed buffer, on top of stack, and optionally by dynamic string.

Clarify that pointers are 32 bits.

Add alignment rules.

Add record layout rules.

Remove much of the existing user mode thread architecture section, and rewrite much of what is left.

Change nomenclature around "conditions", "signals", and "exceptions".

Change nomenclature around "Frame Descriptors" (now "Invocation Descriptors") and call frames for heavyweight and lightweight procedure.

# Version 0.7: Internal Working Version, March 1988—C. Nylander

Editorial fixups.

Add linkage pairs.

Specify that FP<1:0> can be dirty when FP<2>=0 as well as when FP<2>=1.

Generalize quadword immediate arguments to large immediate arguments.

Define trailing null or omitted arguments.

Limit maximum natural alignment requirements to quadword.

Remove process environment block and process control region.

Define reserved memory pages.

Add extra level of indirection to function value return by dynamic string descriptor.

Move function value return by dynamic string descriptor to appendix.

Move thread local storage to appendix.

Move thread local context to appendix.

Change literal constants to symbolic constants.

Make functional interfaces abstract.

Make EXTENT undefined for arrays with more than one dimensions.

Specify that procedure invocations are removed from the invocation chain as unwinding proceeds.

Delete condition records.

Reorganize condition vectors.

Rename condition vectors to be condition records.

Redesign mechanism record—remove all CONDITION fields and most ESTABLISHER

Add abstract interfaces for fetching active procedure context removed from the mechanism record.

Extend invalid stack handling to condition stack.

Define abstract functional interfaces for raising conditions, establishing vectored handlers, establishing alternate condition stack, and unwinding.

Add nested unwinds.

Add overlapping unwinds (informal description)

#### 1 Introduction

This standard defines the rules and conventions that govern the user mode run time environment on PRISM systems. It specifically applies to both PRISM ULTRIX and PRISM MICA systems.

This standard defines properties of the run time environment that must apply at various points during program execution. These properties include the contents of key registers, the format and contents of certain data structures, and actions that procedures must perform under certain circumstances.

-Not all of these properties have the same scope. Some properties apply at all points throughout the execution of user mode code, and must therefore be held constant at all times; such properties include those defined for the stack pointer and the frame pointer. Other properties apply only at certain points, such as call conventions that apply only at the point that a JSR to a called procedure is executed.

Furthermore, some of these properties apply under all circumstances; such properties include the call stack structure. Others are optional depending on circumstances; for example, compilers are not obligated to follow the argument list conventions when a procedure and all its callers are in the same module, have been analyzed by an interprocedural analyzer, or have private interfaces (such as language support routines).

Section "Scope and Applicability" summarizes the points at which elements of this standard apply and the circumstances under which they apply.

This standard defines the software implementation architecture for PRISM systems. The conventions described in this standard by definition differ from other software implementation architectures, and programs that depend on properties of this architecture may not be portable to other architectures.

Since source level compatibility and portability between VAX and PRISM is an explicit goal, users should not depend on the properties of this architecture except indirectly through high level language facilities that are portable across architectures.

#### 1.1 Goals

The PRISM calling standard has many of the same goals as the VAX calling standard.

- The standard must be applicable to all intermodule callable interfaces in the PRISM software system. Specifically, the standard must consider the requirements of important compiled languages including ADA, BASIC, BLISS, C, COBOL, FORTRAN, PASCAL, PILLAR, PL/I, and calls to the operating system and library procedures. The needs of other languages that DIGITAL may support in the future must be met by the standard or by compatible revision to it.

- The standard should not include capabilities specifically for lower level components (such as assembler routines) that cannot be invoked from the higher level languages.

- The calling program and called procedure can be written in different languages. The standard attempts to reduce the need for use of language extensions for mixed language programs.

- The standard should contribute to the writing of error free, modular, and maintainable software. Effective sharing and reuse of PRISM software modules are specific goals.

#### Introduction

- The standard should provide the programmer with control over fixing, reporting, and flow of control when software conditions or hardware exceptions occur.

- The standard should provide subsystem and application writers with the ability to override system messages to provide a more suitable application oriented interface.

- The standard should add no space or time overhead to procedure calls and returns that do not establish condition handlers and should minimize time overhead for establishing handlers at the cost of increased time overhead when exceptions occur.

# New goals for the PRISM calling standard include:

- Provide a common, compatible user mode run time environment on both the PRISM ULTRIX and PRISM MICA operating systems.

- Maintain high level language source level compatibility with VAX procedure calls. In particular, provide immediate value, reference and descriptor mechanisms for passing arguments.

- Provide a compatible calling standard architecture for a future 64-bit extension of the PRISM architecture.

- Effectively use a large number of registers.

- Pass some arguments in registers to improve performance.

- Provide an efficient mechanism for calling lightweight procedures that do not need a stack call frame because they do not modify preserved registers.

- Use the same calling sequence to invoke lightweight procedures that maintain only a

register call frame and and heavyweight procedures that maintain a stack call frame.

From the caller's point of view, this unifies the VAX concepts of JSB and CALL linkages.

The compiler determines whether to use a stack frame based on the complexity of the

called procedure, but this does not require any recompilation of callers.

- Provide condition handling, traceback, and debugging for lightweight procedures that

do not have a stack frame.

# 2 Register Usage Conventions

### 2.1 Scalar Register Conventions

| R0     | Hardware defined: binary zero as a source operand, sink (no effect) as a result operand.                                                                                                                                                                                                          |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1     | SP, the stack pointer. Used by hardware. Must be quadword aligned.                                                                                                                                                                                                                                |

| R2     | FP, the frame pointer. Defined by call stack conventions. Must be quadword aligned                                                                                                                                                                                                                |

| R3     | TEB_BASE, the thread environment block pointer. Contains the address of a data structure used by compiled code and the run time library to maintain thread local context.                                                                                                                         |

| R4R5   | Scratch registers which may be modified after the caller has executed the JSR to effect the call, but before the called procedure is invoked. That is, R4R5 are destroyable between calling and called procedures (e.g. by the auto-loader), before they can be accessed by the called procedure. |

| R8R9   | In a standard call that returns a function result in a register, the result is returned in R8 (result size $\leq$ 32 bits), or R8R9 (33 bits $\leq$ result size $\leq$ 64 bits).                                                                                                                  |

| R10    | In a standard call, R10 contains the address of the called procedure's invocation descriptor.                                                                                                                                                                                                     |

| R11    | In a standard call, R11 contains the return address.                                                                                                                                                                                                                                              |

| R12    | In a standard call to a procedure with more than eight longwords in the argument list, R12 contains the quadword aligned memory address of the remainder of the argument list.                                                                                                                    |

| R13    | In a standard call, R13 contains the number of longwords in the argument list.                                                                                                                                                                                                                    |

| R14R21 | In a standard call, the first eight longwords of the argument list are passed in R14R21.                                                                                                                                                                                                          |

| R4R31  | Scratch registers in standard call, which may be modified by the called procedure without being saved and restored.                                                                                                                                                                               |

| R32R63 | No conventional use. If a standard-conforming procedure modifies one of these registers, it must save and restore it.                                                                                                                                                                             |

# 2.2 Vector Register Conventions

| V0V15 | Scratch registers in standard call. |  |

|-------|-------------------------------------|--|

| VL    | Scratch register in standard call.  |  |

| VC    | Scratch register in standard call.  |  |

| VM    | Scratch register in standard call.  |  |

The PRISM calling standard specifies no conventions for preserved vector registers, vector argument registers, or vector function value return registers. All such conventions are by agreement between the calling and called procedures.

Although no vector registers are preserved in a standard call, the entry descriptors defined by this standard include specification of the vector registers saved by a procedure. This so that, when vector registers are preserved by agreement between the calling and called procedure, the condition handling facility will restore them on unwind.

Any condition handler that disturbs the vector state must save and restore it.

These conventions for vector register use, particularly the absence of preserved registers, reflect our current best judgement. The rationale for these decisions includes the following assumptions:

<sup>1.</sup> Nearly all vector arguments will be passed between cooperating procedures, such as math library routines and compiler generated code, that will establish interface-specific agreements for vector register use.

## **Register Usage Conventions**

- 2. Nearly all use of vector operations will be in bottom level procedures (procedures that do not call other procedures), and these procedures should have as many scratch registers as possible available to them without the necessity of saving and restoring vector registers.

- 3. In those cases where vector registers are used in a calling procedure and there are no agreements with the called procedure, values in the vector registers either do not need to be saved across calls or else can be saved equally well by the calling procedure.

These conventions are subject to change when we have more experience with the use of vector registers in calling and called procedures.  $\$

### 3 Invocation Descriptors

An Invocation Descriptor is a quadword aligned data structure that provides basic information about a procedure. This data structure is used in calls between procedures and in interpreting the call stack that exists at any point in a thread's execution.

Some PRISM procedures allocate call frames on the stack, others maintain their call frame entirely in registers (although they may use the stack), and very simple procedures do not necessarily allocate any stack storage at all. The calling procedure need not distinguish these cases. The invocation descriptor for the current procedure contains a field that indicates whether the procedure allocates a call frame on the stack.

As illustrated in the subsequent subsections, the form of an invocation descriptor depends on whether or not a procedure requires a call frame on the stack.

## 3.1 Invocation Descriptor—Procedures With a Register Frame

A procedure which does not allocate a call frame on the stack (sometimes referred to as a "lightweight procedure") saves it's invocation context in registers.

Such a procedure cannot save and restore nonscratch registers. Because a procedure without a stack frame must therefore use scratch registers to maintain invocation context, such a procedure cannot make a standard call to any other procedure.

A procedure with a register frame can have condition handlers and can handle conditions in the normal way. Such a procedure can also allocate local stack storage in the normal way. although it will not necessarily do so.

|                       |                       |                     | Quadword       | Aligned      |

|-----------------------|-----------------------|---------------------|----------------|--------------|

|                       | CODE_ADI              |                     |                |              |

| RA_SAVE  <br>(8 bits) | SP_SAVE  <br>(8 bits) | FP_SAVE<br>(8 bits) | FLAGS<br>  (5) | FMT<br>  (3) |

| +                     | CONDITION<br>(32 bi   | -                   | +              |              |

CODE\_ADDRESS is the absolute address of the first instruction of the entry code sequence for the procedure.

FMT = INVDESCR\$C REGISTER\_FRAME for an invocation descriptor denoting a procedure with a register frame.

**FLAGS** is a set of flag bits defined as follows.

- FLAGS<HAS\_HANDLER> is 1 if this procedure has a condition handler. If FLAGS<HAS\_ HANDLER> is 1, then the CONDITION\_HANDLER field must denote a condition handler.

- FLAGS<HANDLER\_REINVOKABLE> is 1 if the condition handler is a reinvokable handler, that is, one which can be reinvoked should another condition occur while the handler is already active. If FLAGS<HANDLER REINVOKABLE> is 0 then the condition handler is not reinvokable.

FLAGS<HANDLER\_REINVOKABLE> must be 0 unless FLAGS<HAS\_HANDLER> is 1.

• FLAGS<2:4> must be 000.

\\\ : ... <u>----</u> . ......

FP\_SAVE is the number of the register in which the value of FP at entry to this procedure is maintained.

SP\_SAVE is the number of the register in which the value of SP at entry to this procedure is maintained. SP\_SAVE will specify R1 if this procedure does not modify SP.

RA\_SAVE is the number of the register in which the return address is maintained. If this procedure uses the standard call conventions and does not modify R11, then RA\_SAVE will specify R11.

CONDITION\_HANDLER is a signed self-relative pointer to the invocation descriptor for a run time static condition handling procedure. This field is *not* defined unless FLAGS specifies that there is a condition handler.

Lightweight procedures have more freedom than might be apparent. By use appropriate agreements with procedures that call a lightweight procedure, by appropriate agreements with procedures that a lightweight procedure calls, and by use of unwind handlers, a lightweight procedure may modify nonscratch registers, and may call other procedures.

Such agreements may be by convention (as in the case of language support routines in the RTL) or by interprocedural analysis. Calls employing such agreements are, however, not standard calls.

Since such agreements must be permanent (for upwards compatibility of object code), lightweight procedures should in general follow the normal restrictions.

# 3.2 Invocation Descriptor—Procedures With a Stack Frame

A procedure which allocates a call frame on the stack (sometimes referred to as a "heavy-weight procedure") can save and restore nonscratch registers, and may make standard calls to other procedures. A standard heavyweight procedure maintains the invocation context in stack storage as defined in section "The Call Stack".

|                                   | Quadword Aligned                                     | d.              |

|-----------------------------------|------------------------------------------------------|-----------------|

|                                   | ADDRESS<br>bits)                                     | +<br> <br> -    |

| FP_SP_DIFFERENCE (16 bits)        | MUST BE ZERO   FLAGS   FMT<br>  (8 bits)   (5)   (3) | +<br> <br> <br> |

|                                   | CONDITION_HANDLER   (32 bits)                        |                 |

| VECTOR REGISTER MASK<br>(16 bits) | REGISTER_OFFSET<br>  (16 bits)                       | <br> <br> -     |

| PECTO                             | TER MASK                                             | т<br> <br>      |

|                                   | bits)                                                | i               |

CODE\_ADDRESS is the absolute address of the first instruction of entry code sequence for the procedure.

FMT = INVDESCR\$C\_STACK\_FRAME for an invocation descriptor denoting a procedure with a stack frame.

**FLAGS** is a set of flag bits defined as follows.

- FLAGS<HAS\_HANDLER> is 1 if this procedure has a condition handler. If FLAGS<HAS\_ HANDLER> is 1, then the CONDITION\_HANDLER field must denote a condition han-

- FLAGS<HANDLER REINVOKABLE> is 1 if the condition handler is a reinvokable handler, that is, one which can be reinvoked should another condition occur while the handler is already active. If FLAGS<HANDLER\_REINVOKABLE> is 0 then the condition handler is not reinvokable.

- FLAGS<HANDLER\_REINVOKABLE> must be 0 unless FLAGS<HAS\_HANDLER> is

- FLAGS<VECTOR\_CONTEXT\_SAVE> is 1 if this procedure saves VL, VC, and VM in the register save area on entry to the procedure.

- FLAGS<3:4> must be 00.

FP\_SP\_DIFFERENCE is the distance in bytes between the stack frame base (this procedure's FP value) and the stack's top (SP value) at entry to the procedure (see section "Stack Frame Layout"). FP\_SP\_DIFFERENCE must be a multiple of 8 so as to maintain quadword-alignment of the stack.

CONDITION\_HANDLER is a signed self-relative pointer to the invocation descriptor for a run time static condition handling procedure. This field is present in all invocation descriptors with FMT = INVDESCR\$C\_STACK\_FRAME, but is not defined unless FLAGS specifies that there is a condition handler.

REGISTER\_OFFSET is the difference in bytes between the stack frame base (this procedure's FP value) and the register save area (see section "Stack Frame Layout"). REGISTER\_ OFFSET must be a multiple of 8 such that REGISTER\_OFFSET(FP) yields a quadword aligned address.

**REGISTER\_MASK** is a bit vector (0..63) specifying the scalar registers that are saved in the register save area on entry to the procedure.

**VECTOR\_REGISTER\_MASK** is a bit vector (0..15) specifying the vector registers that are saved in the register save area on entry to the procedure.

Dynamic condition handling is not defined by this calling standard; it is language-defined. Compilers will set up language-specific static condition handlers, and these static condition handlers will provide the dynamic condition handling semantics of each language.

Users should not write static condition handlers, as they are part of the software implementation architecture and are not necessarily portable to other architectures.

Users should utilize the dynamic condition handling mechanisms provided by the language in which they are coding, which are implemented and invoked via compiler and RTL mechanisms, and are portable.

11

# 4 The Linkage Section

Since a PRISM instruction cannot contain a full virtual address, PRISM is a base register architecture. All memory references are displacements relative to the contents of a base register (or implicitly, the program counter), and all external references must be indirect through address constants.

The fundamental table of address constants that a procedure can use to access static storage and external procedures and variables is called a linkage section. A register that is used to access the contents of the linkage section is a linkage pointer.

A procedure's linkage section includes the invocation descriptor for that procedure and the addresses of all external constants, variables, and procedures referenced by the procedure.

When a separately compiled procedure is called, the caller must provide a pointer (in R10) to the called procedure's invocation descriptor. R10, the linkage pointer, may be used by the called procedure as a base register to access address constants in its linkage section.

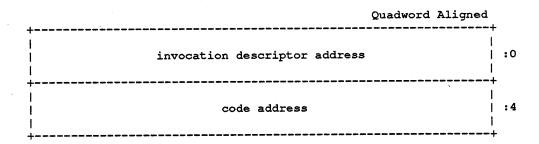

Linkages to external procedures are represented in the calling procedure's linkage section as a linkage pair. A linkage pair, which must be quadword aligned, consists of two longwords.

Invocation descriptor address is the absolute address of the invocation descriptor of the called procedure.

Code address is the absolute address of the first instruction of the called procedure's entry code sequence.

Although, because the invocation descriptor also contains the absolute code address, only the invocation descriptor address is strictly required in the linkage section, the absolute code address is placed in the linkage section to provide better performance for external procedure calls. Although the absolute code address in the invocation descriptor is used under certain circumstances (see section "Procedure Values"), this structure of linkage pairs in the linkage section is required by this standard—the second longword must always be present.

The linkage section is part of the called procedure, and the layout of a linkage section is determined by the compiler. Procedures compiled together (belonging to a single object module) will share a linkage section, which will contain an invocation descriptor for each procedure in the module. Offsets for invocation descriptors and address constants within the linkage section are assigned by the compiler when the module is compiled.

In practice, the linkage section will be allocated in a read-only PSECT. This read-only linkage PSECT could also contain all read-only constants defined by the module. However, when an image is activated and the fixups on the linkage section are performed, all the read-only constants in that PSECT become non-shared between processes. If there are more than a page or two of read-only constants, this may significantly increase physical memory usage; thus, caution must be exercised.

In general, an object module contains an invocation descriptor for each entry point contained by the module. The descriptors are allocated in a linkage PSECT. For each external procedure, Q, referenced in a module, the module's linkage PSECT also contains a linkage pair denoting Q, that is, a pointer to Q'sinvocation descriptor and entry code address.

As an example of typical code to call an external procedure, Q, suppose that LP is a register currently containing the address of the current procedure's invocation descriptor (LP is not a fixed register). Q can be called by:

```

Q OFFSET(LP), R10

; Q's linkage pair into R10..R11

; Jump to Q. Return address in R11

JSR

R11, (R11)

```

Because Q's invocation descriptor is in Q's linkage section, Q can use the value in R10 as a base address for accessing data in its linkage PSECT. Q accesses external procedures and data in other PSECTs through pointers in its linkage PSECT. Therefore, R10 serves as the root pointer for access to all static data.

The following example illustrates the layout and use of linkage sections. (This example does not presume to represent how a compiler might actually layout a linkage section, or to represent actual PRISM assembler notation, and the code fragments presented do not presume to do anything useful.)

#### MODULE X

```

; Linkage section for Module X

$LINK

.psect

; Invocation descriptor for heavyweight procedure X1

X1::

.address

X1 ENTRY

; Address of entry code sequence for X1

; X1 has stack frame but no condition handler

1

.byte

; MBZ

0

.byte

; FP_SP_DIFFERENCE = 32

32

.word

0

; No condition handler

.long

; REGISTER_OFFSET = 16

.word

16

.word

0

; No saved V0..V15

7

; Save R61..R63

.quad

Y1 PROCVAL:

; Procedure value for procedure Y1

; Value is Yl's invocation descriptor address

.address Y1

; Read-only table of powers of 2

POWER 2 TABLE:

.long 1,2,4,8,16,32,64,128,256,512,1024,2048,4096,8192

; External static variables

Y_DATA_1_ADDR:

; Address of Y DATA 1

.address

Y DATA 1

Y DATA_2_ADDR:

.address

Y_DATA_2

; Address of Y DATA 2

; Code for Module X

$CODE

.psect

; Entry code sequence for procedure X1

```

```

X1 ENTRY:

; Address of X1's invocation descriptor is in R10

; on standard call, and return address is

; in R11

; Allocate stack space for X1 stack frame

-32(SP), SP

LDA

; Save invocation descriptor address and return address

R10, (SP)

STO

; Save caller's frame pointer

STL

FP,8(SP)

STQ

R62, 16 (SP)

; Save R62..R63

STL

R61,24(SP)

; Save R61

; X1 is now the current procedure

RO, SP, FP

OR

OR

R0,R10,R61

; Move own invocation descriptor address to preserved

; register R61

; Calculate 2 raised to power of first argument and store in Y_DATA_1

POWER 2 TABLE-X1 (R61), R4

LDA

; R4 <- address of powers of 2 table

#2,R14,R5

SLL

; R4 <- address of value of 2**first argument

; R4 <- 2**first argument

R4,R5,R4

ADD

LDL

(R4),R4

LDL

Y DATA 1 ADDR-X1 (R61), R5

; R5 <- address Y DATA 1

; Y DATA 1 <- R4

STL

R4, (R5)

; Preserve arguments across call to Y1

; R62 <- first argument

R0,R14,R62

OR

; R63 <- second argument

OR

RO,R15,R63

; CALL procedure Y1

Y1 PROCVAL-X1(R61),R10

LDO

; R10 <- address of Y1's invocation descriptor

; R11 <- address Y1's entry code sequence

; R11 <- return address and call Y1

JSR

R11, (R11)

; Store first+second argument in external Y_DATA_2 and return sum

; as X1 value

; R8 <- sum

ADD

R62, R63, R8

Y_DATA_2_ADDR-X1 (R61),R4

LDL

; R4 <- address Y_DATA_2

; Y DATA 2 <- R8

STL

R8, (R4)

; Return sum to caller.

; Restore R61

24 (FP),R61

LDL

; Restore R62..R63

LDO

16(FP),R62

; Get return address and caller's frame pointer

LDQ

4 (FP),R4

; Restore caller's frame pointer. Caller is once

OR

RO,R5,FP

; again the current procedure.

; Restore caller's SP

32 (R5),SP

LDA

JSR

RO, (R4)

; Return to caller

MODIILE Y

; Linkage section for Module Y

SLINK

.psect

; Invocation descriptor for lightweight procedure Y1

Y1::

Y1 ENTRY

; Address of entry code sequence for Y1

.address

; Y1 has register frame and a nonreinvokable handler

.byte

8

; Save caller's FP in R7

7

.byte

; Leave caller's SP undisturbed in R1

.byte

1

; Leave return address undisturbed in R11

.byte

11

Y1_HND-.

; Y1 HND is condition handler

.long

```

```

; Invocation descriptor for condition handler

Y1 HND:

Y1 HND ENTRY; Address of entry code sequence for Y1_HND.

.address

; (Y1 HND ENTRY is not shown in this example.)

-0

; Y1 HND has register frame and no condition handler

.byte

; Save caller's FP in R4

.byte

4

; Leave caller's SP undisturbed in R1

.byte

1

.byte

; Leave return address undisturbed in R11

11

; No condition handler

.long

; address of base of static Y data

Y STATIC DATA:

Y DATA PSECT

.address

.psect

SDATA

; static data psect

Y DATA PSECT:

Y DATA 1::

; global static variable Y_DATA_1

.long

; global static variable Y_DATA_2

Y DATA 2::

1

.long

.psect

$CODE

; Code for Module Y

; Entry code sequence for procedure Y1

; Address of Y1's invocation descriptor is in R10

Y1 ENTRY:

; on standard call, and return address is

; in R11

RO, FP, R7

; Save caller's frame pointer

OR

; Force pending exceptions to be raised

DRAIN

; Y1 is now the current procedure

#4,R10,FP

OR

; Compute product of global static Y_DATA_1 and Y_DATA_2.

; Store product in Y_DATA_1.

Y STATIC DATA-Y1 (R10), R4

; R4 <- base of static data psect

T.DT.

Y DATA 1-Y DATA PSECT(R4), R5; R5 <- Y DATA 1 value

LDL

LDL

Y DATA 2-Y DATA PSECT(R4), R6 ; R6 <- Y DATA 2 value

R5, R6, R5

; Calculate product

MUL

; Synchronize exceptions

DRAIN

STL

R5,Y DATA 1-Y DATA PSECT(R4) ; Y_DATA_1 <- product

; return to caller

; Restore caller's frame pointer. Caller is once

OR

RO, R7, FP

; again the current procedure.

; Return to caller

JSR

RO, (R11)

```

#### The PRISM Call Conventions

The PRISM call conventions determine the methods used to communicate certain data between the caller and the called procedure during invocation and return. Elements of these conventions may be optional, depending on the properties of the called procedure.

The register or stack location used for an element in standard calls is specified as part of the calling standard.

### **Invocation Descriptor Address**

This is the address of the invocation descriptor of the called procedure. This address is required in standard calls and is contained in register R10.

#### Return Address

In a normal return from the called procedure, the return address is the address of the instruction to which control is transferred. In a standard call, this address is contained in register R11.

### **Argument Count**

This is the number of longwords in the argument list. This count is required in a standard call and is contained in register R13.

#### **Argument List**

The argument list in a PRISM call is an ordered set of zero or more argument items, which together comprise a logically contiguous structure known as the argument item sequence. This logically contiguous sequence is in practice mapped to registers and memory in a fashion that may produce a physically discontiguous argument list. In a standard call, the first N items are passed in registers R14..R21. (See section "Argument Lists" for details of argument-to-register correspondence). The remaining items are collected in a memory argument list, which is a quadword aligned array of longwords. In a standard call, the address of this list (if present) is contained in register R12.

#### **Function Result**

If a standard-conforming procedure is a function, and the function result is to be returned in a register, then the result is returned in R8 or R8..R9. Otherwise, the function result is returned via the first argument item. (See section "Function Value Return").

#### **Scratch Registers**

These are registers that the called procedure is allowed to modify without saving and restoring their contents. In a standard call, these are R4..R31.

## 6 The Call Stack

# 6.1 Stack Usage, FP, and SP

The PRISM treatment of condition handling, unwinding (nonlocal GOTOs), trace back, and debugging depends on conventions governing the use of R1 (SP, the stack pointer register) and R2 (FP, the frame pointer register). SP is used by the hardware in raising exceptions and asynchronous software conditions.

SP must denote a quadword aligned address, that is, SP<2:0> must be 000.

The contents of the stack located at addresses lower than (SP) are continually and unpredictably modified. The contents of the stack located at addresses higher than FP\_SP\_DIFFERENCE(FP) belong to the calling procedure; they should not be read or written by the called procedure, except as specified in the argument list or by language-controlled up level references.

Additional rules for FP are more complex. Its value in a thread denotes the invocation context of the current procedure in that thread, which is the root of a chain of procedure invocation contexts, including a (possibly null) set of register values saved by each invocation. The first procedure in the invocation chain is the current procedure, the next is its predecessor (the procedure that invoked the current procedure), and so forth. The current and saved register values associated with each procedure invocation define the values of all registers at the moment of that invocation, excluding registers that are scratch registers for that procedure. The invocation chain information is thus sufficient to analyze a thread at any moment and to implement stack unwinding.

Given the current register values for a procedure invocation, that invocation can be interpreted by examining the value of FP.

If FP<2> is 0 then the current procedure has a stack frame, and FP<31:3> contains the address of the quadword aligned stack frame base. The standard stack frame layout specifies the location of key information in the frame, including the location of the address of the current procedure's invocation descriptor and the register values saved by that procedure. From this information the register values and context of the preceding invocation can be determined.

If FP<2> is 1 then the current procedure has a register frame, and FP<31:3> contains the address of the quadword aligned invocation descriptor. Information in the invocation descriptor specifies which current registers maintain the return address and the predecessor's FP and SP values; these are the only registers needed to determine the register values and context for the predecessor.

Compilers may use FP<1:0> for other flags. That is, FP<2:0> must always be masked to obtain the stack frame or invocation descriptor address.

Compilers are allowed to optimize high level language procedure calls in such a way that they do not appear in the invocation chain; in-line procedures, for example, never appear in the invocation chain.

### 6.2 Stack Frame Layout

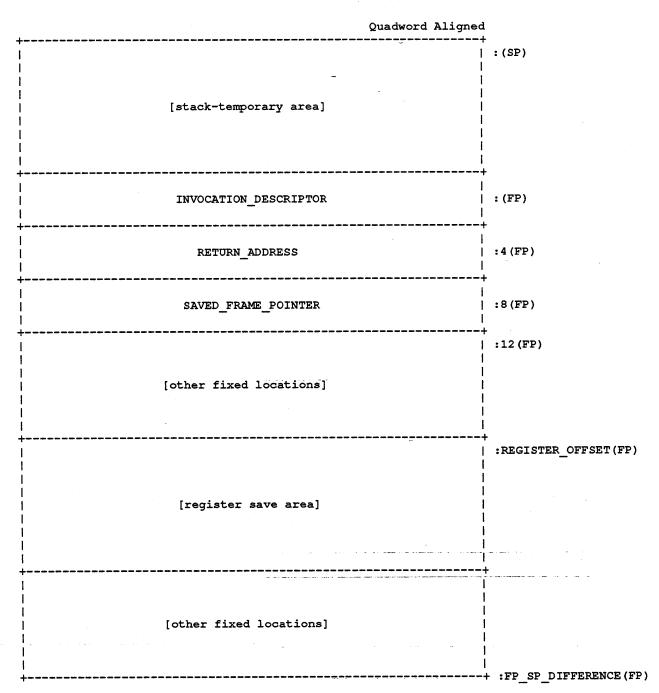

The following figure illustrates the layout of the PRISM stack frame for procedures that have stack frames. Some parts of the stack frame are optional and occur only as required by the particular procedure. Brackets surrounding a field's name indicate the field is optional.

The information needed to interpret the calling chain is at locations (FP), 4(FP), and 8(FP); these locations must be maintained as defined this calling standard. The stack frame must be allocated and initialized by the entry code sequence of a called procedure with a stack frame.

**INVOCATION\_DESCRIPTOR** contains the address of the invocation descriptor of the current procedure.

**RETURN\_ADDRESS** contains the address of the instruction to which control is to be transferred on a normal return.

SAVED\_FRAME\_POINTER contains the caller's FP.

Other fixed locations are optional sections of the stack frame that contain language-specific locations required by the procedure context of some high level languages. This may include, for example, register spill area, language-specific condition handling context, fixed temporaries, etc.

```

\\

Since REGISTER_OFFSET(FP) must be quadword aligned, it can't be at 12(FP), so 12(FP) must either be a fixed compiler temporary or unused.

\\

```

Register save area is a set of consecutive longwords in which nonscratch registers modified by the current procedure are saved. The register save area begins at REGISTER\_OFFSET(FP), where REGISTER\_OFFSET is specified in the procedure's invocation descriptor. REGISTER\_OFFSET(FP) must yield a quadword aligned address. The set of registers saved is specified in the invocation descriptor, by the REGISTER\_MASK and VECTOR\_REGISTER\_MASK fields and by FLAGS<VECTOR\_CONTEXT\_SAVE>.

The high-address end of the stack frame is defined by the value FP\_SP\_DIFFERENCE in the procedure's invocation descriptor. The high-address end is used to determine the value of SP for the predecessor procedure in the calling chain.

A compiler may use the stack-temporary area for fixed local variables, such as constant-sized data items and program state, as well as for dynamically sized local variables. The stack temporary area may also be used for dynamically sized items with a limited lifetime, for example, a dynamically sized function result or string concatenation that can't be directly stored in a target variable. When a procedure uses this area, the compiler must keep track of its base and reset SP to the base to reclaim storage used by temporaries.

#### 6.3 The Register Save Area

The algorithm for packing saved registers in the quadword aligned register save area is

- 1. All even-odd saved scalar register pairs are stored, in register-number order, in consecutive quadwords.

- 2. All even or odd saved scalar registers whose paired register is not being saved are stored, in register-number order, in consecutive longwords following the even-odd register pairs.

- 3. If an odd number of scalar registers are being saved, an additional longword must be allocated following the last saved scalar register.

- 4. All saved vector registers V0..V15 are stored, in register-number order, in consecutive quadwords beginning at the first quadword following the saved scalar registers.

- 5. If VM, VL, and VC are being saved,

- 1. VM is stored in the first quadword following the last saved register.

- 2. VL is stored in the longword following the saved VM.

3. VC is stored in the longword following the saved VL.

For example, if registers R40, R42, R43, R50, and R54 were to be saved, they would be packed in the register save area as follows.

|   | Quadword Aligned | ·<br>•                |

|---|------------------|-----------------------|

|   | R42              | :REGISTER_OFFSET (FP) |

|   | R43              |                       |

|   | R40              | _                     |

|   | R50 I            | _                     |

| ! | R54 I            | _                     |

|   | scratch          | ·                     |

If R51 had also been saved, the contents of the register save area would instead be

|                       | Quadword Aligned                       |

|-----------------------|----------------------------------------|

| :REGISTER_OFFSET (FP) | R42                                    |

|                       | R43                                    |

|                       | R50                                    |

|                       | R51                                    |

|                       | R40                                    |

|                       | R54                                    |

|                       | †===================================== |

# 7 Entry and Return Code Sequences

When a procedure is called, the code at the entry address must

- 1. Allocate and initialize a stack frame (if a procedure with stack frame).

- 2. Initialize RA\_SAVE, SP\_SAVE, and FP\_SAVE (if a procedure with a register frame)

- 3. Store all saved registers (if any).

- 4. Execute a DRAIN instruction (if the procedure has a condition handler)

- 5. Set FP in a manner consistent with the register conventions that define the calling chain.

The current procedure (as defined by the conventions) is the calling procedure until the called procedure's entry code sequence sets FP.

When a procedure returns, the return code sequence must

- 1. Restore saved registers (if any).

- 2. Execute a DRAIN instruction (if the procedure has a condition handler)

- 3. Restore FP to the value it had on entry to the procedure.

- 4. Reset SP (if modified by the procedure).

SP will normally be reset to the value it had on entry to the procedure; however, in some cases the returning procedure must leave SP pointing to a lower stack address than it had on entry to the procedure (see section "Function Value Return").

In addition, if the called procedure executes vector loads and stores it must under certain circumstances execute a DRAINM to synchronize memory with the calling procedure or with procedures it calls (see section "Interprocedural Synchronization").

The examples below illustrate entry and return code sequences; there are many other possible code sequences depending on the called procedure's register use and frame layout, and the compiler's optimization methods.

All the examples assume that procedure Q is invoked by a standard call from procedure P.

#### 7.1 Entry Code Sequence—Register Frame

For convenience, this example assumes that Q has no static condition handler, RA\_SAVE specifies R11, and SP\_SAVE specifies R1 (that is, the procedure allocates no local stack storage).

```

OR RO, FP, FP_SAVE; FP_SAVE is specified in Q's invocation descriptor.

OR #4, R10, FP; FP = address (Q's invocation descriptor) OR 4

; Q is now the current procedure.

```

#### 7.2 Return Code Sequence—Register Frame

```

OR RO, FP_SAVE, FP; Restore P's FP value.

; P is once again the current procedure.

JSR RO, (R11); Return to P's code.

```

# Entry Code Sequence—Stack Frame

For convenience, this example assumes that the regions for language-specific fixed locations are empty, so that REGISTER\_OFFSET = 16 and when the entry code sequence is complete FP = SP.

```

-Q FP SP DIFFERENCE (SP), SP

LDA

; Allocate space for new stack frame.

; Save address of invocation descriptor and

STQ

R10, (SP)

; return address

; Save caller's FP.

STL

FP, 8(SP)

Rx, 16(SP)

; Save first register.

STL

; Force any pending hardware exceptions

DRAIN

; to be raised. Required if Q has a

; condition handler so that a pending exception

; caused by the caller will not be raised in the

; context of Q.

; Q is now the current procedure.

RO, SP, FP

OR

```

Note that if this code sequence is interrupted by an asynchronous software condition, SP will have a different value than it did at entry, but the calling procedure will still be current.

At that point, it would not be possible to determine the original value of SP by the register frame conventions. If actions by the condition handler result in a nonlocal GOTO to a location in the procedure, P, that called Q, then it will not be possible to restore SP to the correct value in P.

Therefore, any procedure that contains a label which can be the target of a non-local GOTO must reset SP at that label.

# 7.4 Return Code Sequence—Stack Frame

This is the return code sequence for the preceding example. The example below assumes the return address is still in R11.

```

; Restore saved registers.

; Restore first register saved.

LDL 16(FP), Rx

; Force any pending hardware exceptions

DRAIN

; to be raised. Required if Q has a

; condition handler so that a pending exception will

; be raised in the context of Q.

; Remove temporary stack storage.

OR - RO, FP, SP

LDL 8(FP), FP

; Restore FP. P is once again the current procedure.

LDA Q_FP_SP_DIFFERENCE(SP), SP

; Restore SP.

; Return to P.

JSR RO, (R11)

```

Interruption of this code sequence by an asynchronous software condition can result in P being the current procedure but with SP not yet restored to its value in P. The discussion of that situation in entry code sequences applies here as well.

#### Procedure Values

PRISM procedure values utilize the properties of invocation descriptors.

A PRISM procedure value is not a procedure's entry address, and it is not necessarily the address of an actual invocation descriptor. Rather, a procedure value is a pointer that can be treated as the address of an invocation descriptor. That is, a procedure value points to a data structure whose first longword contains the address to which the calling procedure must jump. The procedure value itself must be passed as part of the calling sequence.

Suppose register R32 contains a procedure value. An example of the code to call the procedure is:

```

RO, R32, R10; Procedure value to R10

LDL (R32), R11 ; Entry address to scratch register

JSR R11, (R11) ; Jump to entry address; return address goes in R11

; The use of R10 and R11 to is specified by the calling standard.

; R11 is also used here as a temporary.

```

If a procedure Q is not nested within another procedure, then a procedure value for Q is simply the address of Q's invocation descriptor, and the code sequence above calls Q.

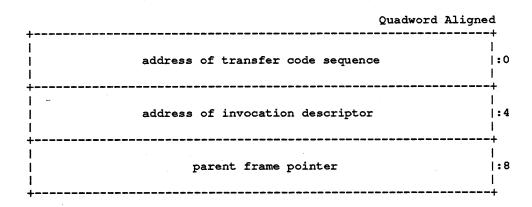

If Q is a subprocedure of a procedure P, then a procedure value for Q must be a bound procedure value. The bound procedure value is a data structure of three longwords that provides a parent frame pointer, the address of an invocation descriptor, and the address of a transfer code sequence.

When the transfer code sequence addressed by the first longword is called (by a call sequence such as the one above), the procedure value will be in R10, and the transfer code must finish setting up the elements of the standard call.

An example of a such a transfer code sequence, for a target procedure that expects the parent frame pointer to be passed in R30, is:

```

LDL

8(R10), R30

; Parent frame pointer to R30

LDL 4(R10), R10

; Invocation descriptor address to R10

; Entry address to scratch register

LDL

(R10), R4

JSR RO, (R4)

; Jump to entry address.

; Return address was already in R11, and this code

; sequence preserves the return address in R11.

```

Here, when control is transferred to Q's entry address, R10 contains the address of Q's invocation descriptor, R11 contains the return address, and R30 contains the parent frame pointer (which is the parent call frame pointer, FP, for the invocation of P to which Q is bound in this procedure value).

The parent frame pointer is needed by Q's code for such things as references to variables in P, and nonlocal GOTOs to points in P. When a bound procedure value such as this is needed, the data structure will normally be allocated in the parent frame.

Procedure values as defined here are typically not used to manage a call within a module; in that situation the call may be done by a PC-relative JSR instruction.

11 Note that bound procedure values must be generated at run-time. The parent frame pointer is not known until the parent has been invoked. In addition, if a bound procedure value were to be statically initialized, then the PRISM Common Software Architecture would require it to be four longwords, with the absolute address of the target procedure's entry code sequence in the third longword -- that is, a bound procedure value would have to have a linkage pair embedded within it. 11

### 9 Argument Passing Mechanisms

The term argument item means an item passed by PRISM call conventions, representing an argument to be associated with a corresponding parameter in the called procedure.

The PRISM calling standard distinguishes among three classes of argument items according to the mechanism used to pass the argument:

- Immediate value

- Reference

- Descriptor

The standard permits any combination of these mechanisms in an argument list. Argument items are not self-defining: interpretation of each argument item depends on agreement between the calling and called procedures.

#### 9.1 Immediate Value

An *immediate value* argument item contains the value of the data item. The argument item, or the value contained in it, is to be directly associated with the parameter.

An argument may be passed by immediate value only if

• it is a scalar data type with known size  $\leq 32$  bits,

or

• it is a record with known size  $\leq 32$  bits.

or

• it is a set with known size  $\leq 32$  bits.

No form of string or array may be passed by immediate value.

A standard immediate argument item must be a longword. (This standard also defines the rules for passing immediate arguments > 32 bits, but such arguments may not be used in standard calls).

The unused high-order bits of all data types (including records) must be zero-extended or sign-extended, to the next longword boundary, as appropriate.

#### 9.2 Reference

A reference argument item contains the address of a data item such as a scalar, string, array, record, or procedure. That data item, or the value contained in it, is to be associated with the parameter.

A reference argument item must be a longword.

#### 9.3 Descriptor

A descriptor argument item contains the address of a descriptor, which contains structural information about the argument's type (such as array bounds) and the address of a data item. That data item, or the value contained in it, is to be associated with the parameter.

A descriptor argument item must be a longword, and the descriptor to which it points must be quadword aligned.

The rules that determine how high level language arguments are mapped to these argument passing mechanisms are language defined. In general, languages should use the same rules as those used on VAX, in order to avoid pertubations in the user-visible programming environment from VAX to PRISM, and to maintain interlanguage compatibility.

In practice, this means by reference except when descriptor is required.

System implementation languages (PILLAR and C) will, however, use immediate whenever possible. 11

# 10 Argument Lists

#### 10.1 Argument List Structure

The argument list in a PRISM call is an ordered set of zero or more argument items, which together comprise a logically contiguous structure known as the argument item sequence.

An argument item in a standard procedure call must be a longword. A longword argument item may be used to pass immediate arguments  $\leq 32$  bits, arguments by reference, and arguments by descriptor.

Although the longword argument items form a logically contiguous sequence, they are in practice mapped to registers and memory in a fashion that may produce a physically discontiguous argument list. Registers R14..R21 are used to pass the first eight longwords of the argument item sequence. Additional argument items must be passed in a quadword aligned memory argument list, the address of which must be passed in R12.

Argument items are assigned to registers R14 to R21 and to longwords in the memory argument list according to the following rules:

- 1. Argument items are assigned in order to increasing argument registers, beginning with R14.

- 2. If there is one or more unassigned argument items after argument register R21 has been allocated, then all remaining argument items are assigned to the memory argument list in order from the lowest-addressed longword to the highest-addressed longword.

- The address of the memory argument list must be passed in R12.

- The memory argument list must be quadword aligned.

- 3. Argument items must not be directly assigned to R12.

That is, the order of the arguments in registers and memory is R14 < R21 < (R12) < (R12) + N.

The memory portion of the argument list must be treated as read-only data by the called procedure, and may be allocated in read-only memory at the option of the calling procedure (except by agreement between the calling and called procedure, such as for output parameters).

#### 10.2 Large Immediate Arguments

Certain languages will pass immediate arguments > 32 bits as large immediate arguments.

Such arguments are *not* standard, cannot be used for interlanguage procedure calls, and must *not* be used in public interfaces callable by multiple languages. However, this standard defines how large immediate arguments must be passed by languages that support them.

Large immediate arguments are treated as a sequence of longwords, and are assigned to argument registers and memory as though they were a sequence of different argument items. This means that large immediate argument is not necessarily quadword aligned, and may be split between R21 and (R12).

Large immediate arguments that are not a multiple of 32 bits in length must be zero-extended or sign-extended to the next multiple of 32 bits.

The sequence of longwords comprising a long immediate argument is assigned to registers and memory according to the algorithm in the preceeding section, where the lowest addressed longword of the immediate argument is the first argument item contributed by the immediate argument, the next-lowest addressed longword of the immediate argument is the next argument item contributed by the immediate argument, and so on.

Large immediate arguments are treated as a number of separate longword arguments when computing the argument count to be stored in R13.

## 10.3 Argument Lists and High Level Languages

High level language functional notations for procedure calls are mapped into PRISM argument item sequences according to the following rules:

- 1. Arguments are mapped from left to right to increasing offsets in the argument item sequence. R14 is allocated to the first argument, and the last longword of the memory argument list (if any) is allocated to the last argument.

- 2. Each source language argument corresponds to a single PRISM argument item, except for certain parameterized types.

- For parameterized types, if the source language argument is not being passed by a single standard descriptor, then the address of the argument value is passed in a single argument item (that is, the argument value is passed by reference) and the type parameter values are passed in consecutive argument items immediately following the argument value item in the argument item sequence.

- 3. Each argument item is a longword.

- This may require zero-extension or sign-extension.

- 4. A null or omitted argument, for example CALL SUB(A,,B), is represented by a longword argument item containing 0.

- No arguments passed by the immediate mechanism may be omitted unless a default value is supplied by the language. (This is to enable called procedures to distingish an omitted immediate argument from an immediate argument with the value 0).

- Trailing null or omitted arguments, for example CALL SUB(A,,), are passed by the same rules as embedded null or omitted arguments.

# 10.4 Order of Argument Evaluation

Since most higher level languages do not specify the order of evaluation (with respect to side effects) of arguments, those language processors can evaluate arguments in any convenient order. The choice of argument evaluation order and code generation strategy is constrained only by the definition of the particular language. Programs should not be written that depend on the order of evaluation of arguments.

# 11 Procedure Argument Descriptors

#### 11.1 Goals

• Support high level languages

Support passing parameters between procedures that conform to the PRISM calling standard. Thus, they are designed to support high level language (HLL) procedures calling procedures which are:

- written in a HLL (same language or a different language)

- part of the Run Time Library

- part of a callable utility

- Provide architectural extensibility

Two variants of the PRISM architecture are anticipated, 32-bit and 64-bit. Because of this, the logical and physical attributes of descriptors must be separated.

- The information found in a PRISM descriptor will be the same across all variants of the PRISM architecture, and the user's view of PRISM descriptors should not be sensitive to the variants of the architecture. This is termed the *logical view* of the architecture.

- The physical view of a descriptor includes the order and the size of each field. The size and order of the fields will not necessarily be the same across all variants of the PRISM architecture.

Definitions of descriptors at both the logical and physical level are provided. Only routines using the logical view will work across all variants of the architecture. Routines using the physical view will *not* work across all variants of the architecture.

Software that needs to view descriptor fields should use the logical view wherever possible so that it remains invariant across the PRISM architecture. High level language users should utilize descriptors via mechanisms such as %DESCR, attributes on variables, and macros or lightweight procedures for accessing and manipulating descriptor attributes.

VAX compatibility

VAX programs that use descriptors via mechanisms such as %DESCR will continue to work on PRISM (except those programs that pass atomic data by %DESCR).

Make descriptors self defining

Given the starting address, it is possible to determine what fields exist in a descriptor.

• Minimize time of access to data.

Descriptors frequently need to trade off size of the descriptor for speed of access to descriptor data. PRISM descriptors favor improving the speed of access to data.

Avoid redundant information

Several VAX descriptors contain fields that can be derived from other fields in the descriptor. PRISM descriptors are designed to avoid that redundant information.

Avoid redundant forms.

Due to evolution of the VAX calling standard, there are multiple ways of describing some objects with a descriptor. PRISM descriptors avoid redundant forms.

- Support 8-bit and multibyte character sets PRISM descriptors support 8-bit character sets and multibyte character sets.

- Avoid unsupported combinations of fields.

- PRISM Descriptors are designed to avoid unsupported combinations of fields. VAX descriptors have 2 fields, CLASS and DTYPE, that are not entirely orthogonal to one another. Combinations that seem quite feasible are not supported and often go undetected by DIGITAL software. A crisper definition of descriptors was applied to PRISM.

- Provide uniform descriptors for procedure arguments, function return values, and condition arguments.

- Provide uniform array descriptors

- On VAX, FORTRAN will create a contiguous array descriptor for an array of real values whereas PASCAL will create a noncontiguous array descriptor for the same array. This problem is resolved on PRISM by avoiding special descriptor classes for contiguous arrays. Noncontiguous array descriptors can describe both contiguous arrays and cross sections of arrays that cannot be described by a contiguous array descriptor.

- Provide uniform bit descriptors Languages can check whether a bit string or array is aligned by testing the lowest three bits of the POSITION field in the descriptor.

- Provide uniformity descriptors for sequences of bits and characters.

- On VAX, some languages pass strings using string class descriptors, and expect string class descriptors for input arguments; other languages use one dimensional array descriptors. This problem is resolved on PRISM by having one form of descriptor for linear, one-dimensional data.

- Avoid addressing calculations in called procedures.

- The addressing fields in the PRISM array descriptors are optimized for compiled code referencing an array element.

#### 11.2 Non-Goals

- Descriptors are not designed to describe objects to the degree needed by tools such as the PRISM Debugger or PRISM CDD.

- These tools should use their own data structures, such as DSTs, to describe objects. The calling standard will not encompass all the requirements of such utilities.

- VAX and PRISM descriptors are not identical.

- PRISM descriptors support high level language use of descriptors. Code that explicitly declares and references fields in VAX descriptors is unlikely to work on PRISM.

### 11.3 Use of Descriptors for Procedure Arguments

Standard descriptors are defined for passing argument information between high level languages.

Unless explicitly stated otherwise in this standard, the calling procedure must fill in all fields in a descriptor. This is true whether the descriptor is generated by default or by a language extension. The fields must be filled in even if a called procedure written in the same language would ignore the contents of some of the fields.

Unless explicitly stated otherwise in this standard, all fields of a PRISM descriptor represent unsigned quantities. Descriptors are read-only from the point of view of the called procedure, and may be allocated in read-only storage at the option of the calling procedure (except by agreement between the calling and called procedure, such as dynamic text string descriptors).

Descriptors must be quadword aligned.

Procedure argument descriptors are divided into two broad categories, each of which is discussed in a following subsection:

- descriptors for byte addressable data

- descriptors for bit addressable data

#### 11.4 Descriptors for Byte Addressable Data

The broad class of descriptors for byte addressable data contains the following specific descriptor classes:

- Fixed text

- Varying text

- Dynamic text

- Byte addressable array

PRISM byte addressable array descriptors may be used to pass arrays where each array element starts and ends on a byte boundary. The storage of the array elements is allocated with a fixed (possibly zero) number of bytes separating logically adjacent elements.

The four byte addressable data descriptor classes support all the types of text strings understood in the PRISM software architecture. Each of the languages with a concept of text string must map it to one of these forms. Utility routines that accept text string arguments by descriptor should anticipate receiving text strings in any of these forms, and only these forms.

#### 11.4.1 Logical Attributes of Byte Addressable Data Descriptors

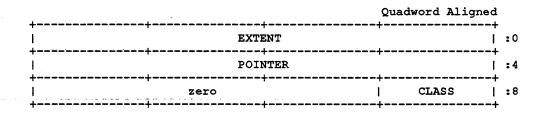

**CLASS** is the descriptor class attribute:

DESCR\$C\_FIXED\_TEXT DESCR\$C\_DYNAMIC\_TEXT DESCR\$C\_VARYING\_TEXT DESCR\$C\_BYTE\_ARRAY POINTER is the address of the first byte of storage occupied by the data. This is the address of the first byte of the string or, for an array, the address of element (low\_bound(1), . . . low\_ bound(n)).

**EXTENT** specifies the number of bytes of contiguous storage occupied by the data.

When CLASS = DESCR\$C\_FIXED\_TEXT or CLASS = DESCR\$C\_DYNAMIC\_TEXT, EXTENT is an integer  $0..2^{31} - 1$  specifying the length in bytes of the string.

When CLASS = DESCR $C_VARYING_TEXT$ , EXTENT is an integer  $0...2^{16}-1$  specifying the maximum length in bytes of the varying string.

When CLASS = DESCR\$C\_BYTE\_ARRAY, and DIMENSIONS = 1, and STRIDE = EL-EMENT\_SIZE, then EXTENT is an integer 0..231 - 1 specifying the length in bytes of the storage occupied by the array.

For all other cases, EXTENT is undefined.

**DIMENSION** is an unsigned integer 1..255 specifying the number of dimensions in an array. If CLASS is not DESCR\$C\_BYTE\_ARRAY, then DIMENSION must be zero.

ELEMENT\_SIZE specifies the number of bytes of storage occupied by each element of a character array, and is present if and only if CLASS = DESCR\$C\_BYTE\_ARRAY.

For arrays of fixed length text strings, ELEMENT\_SIZE is an integer 0..231-1 specifying the length in bytes of each element of the array.

For arrays of varying text strings, ELEMENT\_SIZE is an integer  $0..2^{16} - 1$  specifying the maximum length in bytes of each element of the array.

For all other data types, ELEMENT\_SIZE is undefined.

**VIRTUAL\_ORIGIN** is the address of element  $(0, \ldots, 0)$ , and is present if and *only* if CLASS = DESCR\$C BYTE ARRAY. This address is not necessarily within the storage of the array.

If, and only if, CLASS = DESCR\$C\_BYTE\_ARRAY, then the following fields occur once per dimension:

LOW\_BOUND(i) is a signed integer specifying the lower bound of the ith dimension of the

HIGH BOUND(i) is a signed integer specifying the upper bound of the ith dimension of the array.

STRIDE(i) is a signed integer specifying the difference in bytes between the addresses of successive elements of the ith dimension of the array.

### 11.4.2 Data Type Conventions for Byte Addressable Data Descriptors

Byte addressable data descriptors do not specify the data type contained by a string or array. This must be established by agreement between calling and the called procedures.

All characters in a fixed, varying, or dynamic string must be of the same size, and the character size cannot be determined by inspecting the descriptor; the calling and called procedures must agree on the character size.

### 11.4.3 Run Time Conventions for Byte Addressable Data Descriptors

The conventions controlling the use of byte addressable data descriptors are determined by the class of the descriptor.

#### DESCR\$C\_FIXED\_TEXT

A fixed text string is sequence of  $0..^{31} - 1$  bytes with a fixed extent.

EXTENT specifies the number of bytes (not characters) occupied by the string.

When a fixed text string is written, the contents of the descriptor must not be modified.

### DESCR\$C\_VARYING\_TEXT

A varying text string is an unsigned 16-bit integer immediately followed by a fixed length area containing  $0..2^{16} - 1$  bytes. The varying string is left justified within this fixed length area.

EXTENT, which must be  $\leq 2^{16} - 1$ , specifies the length in bytes (not characters) of the fixed length area.

POINTER specifies the address of the unsigned 16-bit integer count which preceeds the fixed length area. This integer, which must be  $\leq$  EXTENT, specifies the current length in bytes of the varying string.

When a varying text string is written, the contents of the descriptor must not be modified. If a text string is copied to a varying text string of smaller extent, the string must be truncated. When a varying text string is modified, the new current length of the string is written to the 16-bit count.

#### DESCR\$C DYNAMIC\_TEXT

A dynamic text string is a sequence of  $0..2^{31} - 1$  bytes.

An uninitialized DYNAMIC\_TEXT descriptor, and a descriptor for a null dynamic string, has an EXTENT of zero.

The EXTENT and POINTER fields of a DYNAMIC\_TEXT descriptor may be changed when the associated dynamic string is modified. These fields are volatile across external procedure calls, and descriptors for DYNAMIC\_TEXT strings must be allocated in read/write memory.

The system supplies functions for allocating and deallocating memory for dynamic strings. These functions may modify the EXTENT and POINTER fields of the descriptor. With one exception, these system supplied functions are the *only* procedures that may modify to these fields.

The only exception to this rule is that a procedure with knowlege that the descriptor has not yet been used must zero the extent field to mark it as being uninitialized. A procedure with this knowlege is typically the procedure that allocated the descriptor.

### DESCR\$C BYTE\_ARRAY

A byte addressable array is a ordered sequence of elements, where all elements of any array must be the same byte addressable PRISM data type.

All elements of an array must reside in distinct storage. That is, a PRISM array descriptor must not specify that any array elements overlap one another.

When an array is written, the contents of the descriptor must not be modified.

The address of element (i,j,k) of a byte addressable array can be computed as follows.

```

address = VIRTUAL_ORIGIN + i*STRIDE(1) + j*STRIDE(2) + k*STRIDE(3)

```

The address of the first byte of a byte addressable array is:

```

address =

VIRTUAL_ORIGIN +

LOW_BOUND(1)*STRIDE(1) +

LOW_BOUND(2)*STRIDE(2) +

LOW BOUND(3)*STRIDE(3)

```

or

address = POINTER

### 11.4.4 Physical Format of PRISM-32 Byte Addressable Data Descriptors

|                 |                   |                  | Quadword Aligned |        |

|-----------------|-------------------|------------------|------------------|--------|

|                 | EXTE              | INT              | <br>             | •      |