# MSV11-J MOS Memory

User's Guide

1. 1 1. - 1

## MSV11-J MOS Memory

User's Guide

Prepared by Educational Services of Digital Equipment Corporation

1st Edition, May 1985 Copyright <sup>©</sup> May 1985 by Digital Equipment Corporation. All Rights Reserved. Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts 01754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| digita(   | DIBOL        | Rainbow | VAX            |

|-----------|--------------|---------|----------------|

| DEC       | MASSBUS      | RSTS    | VMS            |

| DECmate   | PDP          | RSX     | VT             |

| DECUS     | P/OS         | RT      | Work Processor |

| DECwriter | Professional | UNIBUS  |                |

## CONTENTS

## CHAPTER 1 GENERAL DESCRIPTION AND SPECIFICATIONS

| 1.1     | Introduction 1-1                                                |

|---------|-----------------------------------------------------------------|

| 1.2     | Description 1-3                                                 |

| 1.2.1   | Error Correction 1-3                                            |

| 1.2.2   | Battery Backup 1-3                                              |

| 1.2.3   | ECC Initialization 1-3                                          |

| 1.2.4   | Control and Status Register (CSR) 1-3                           |

| 1.2.5   | Bus Cycles 1-3                                                  |

| 1.2.6   | Refresh 1-4                                                     |

| 1.2.7   | Simplified Block Diagram Description 1-4                        |

| 1.3     | Error Correction Code (ECC) 1-6                                 |

| 1.3.1   | Advantage of ECC 1-6                                            |

| 1.3.2   | ECC Operation 1-7                                               |

| . 1.3.3 | Example of ECC-Implementation 1-7                               |

| 1.4     | Specifications 1-7                                              |

| 1.4.1   | General Specifications 1-7                                      |

| 1.4.2   | Environmental Specifications 1-8                                |

| 1.4.3   | Electrical Specifications 1-9                                   |

| 1.4.3.1 | Power Supply Requirements 1-9                                   |

| 1.4.4   | Interface Specifications 1-10                                   |

| 1.4.4.1 | P-Bus Interface 1-10                                            |

| 1.4.4.2 | Q-Bus Interface 1-10                                            |

| 1.4.4.3 | Signal AC/DC Loading 1-10                                       |

| 1.4.5   | Performance Specifications 1-10                                 |

| 1.4.5.1 | P-Protocol Access and Cycle Times (All MSV11-J Variations) 1-11 |

| 1.4.5.2 | Q-Protocol Access and Cycle Times (MSV11-JD and MSV11-JE        |

|         | Variations Only) 1-12                                           |

|         |                                                                 |

## CHAPTER 2 DATA FLOW

| 2.1   | Introduction                       | 2-1 |

|-------|------------------------------------|-----|

| 2.2   | Address Portion of Bus Cycle       | 2-1 |

| 2.3   | Data Transfer Portion of Bus Cycle |     |

| 2.3.1 | Read Data Transfer                 |     |

| 2.3.2 | Write Data Transfer                |     |

| 2.3.3 | Write Byte                         |     |

## CHAPTER 3 MEMORY CYCLES

| Bus Cycles                   | 3-1                                                                                                                                                                                                                                                                                                                                    |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                        |

| Write Byte Cycle             | 3-2                                                                                                                                                                                                                                                                                                                                    |

| Block Mode Read Cycles       | 3-2                                                                                                                                                                                                                                                                                                                                    |

|                              |                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                        |

| Read-Modify-Write Byte Cycle | 3-3                                                                                                                                                                                                                                                                                                                                    |

|                              |                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                        |

|                              | Introduction<br>Bus Cycles<br>Read Cycles<br>Memory Read Cycle<br>CSR Read Cycles<br>Write Word Cycles<br>Memory Write Word Cycles<br>CSR Write Word Cycles<br>CSR Write Word Cycles<br>Block Mode Read Cycles<br>Block Mode Read Cycles<br>Read-Modify-Write Cycle<br>Read-Modify-Write Byte Cycle<br>Refresh Cycle<br>ECC INIT Cycle |

## CHAPTER 4 CONFIGURATION AND CSR OPERATION

| Introduction                              |                                     |

|-------------------------------------------|-------------------------------------|

| Module Installation                       | 4-1                                 |

| Jumper Configurations and Switch Settings | 4-1                                 |

|                                           |                                     |

|                                           |                                     |

|                                           |                                     |

|                                           |                                     |

|                                           |                                     |

|                                           |                                     |

| Bit Descriptions of CSR                   | 4-7                                 |

|                                           |                                     |

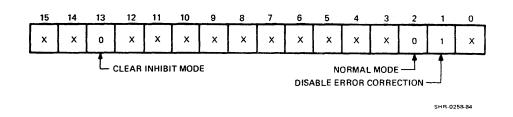

| Normal Mode (ECC Enabled)                 | 4-14                                |

| Normal Mode (ECC Disabled)                | 4-15                                |

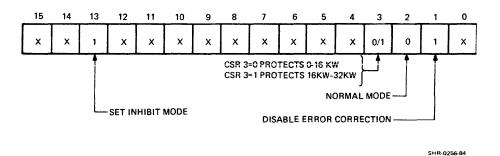

| Normal Protected Mode (ECC Disabled)      | 4-17                                |

|                                           |                                     |

|                                           |                                     |

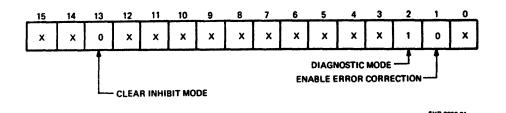

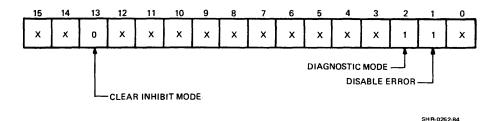

| Protected Diagnostic Mode (ECC Enabled)   | 4-21                                |

|                                           |                                     |

| Operating Modes Summary                   | 4-23                                |

|                                           |                                     |

|                                           | Introduction<br>Module Installation |

## CHAPTER 5 DIAGNOSTICS

| 5.1     | General                                              | 5-1 |

|---------|------------------------------------------------------|-----|

| 5.2     | Preventive Maintenance                               | 5-1 |

| 5.3     | Diagnostic Testing                                   | 5-1 |

| 5.3.1   | Introduction                                         | 5-1 |

| 5.3.2   | Operational Switch Settings 5                        |     |

| 5.3.3   | CVMJA0 Diagnostic Operation                          | 5-3 |

| 5.3.3.1 | Example 1 – Error Free Printout                      |     |

| 5.3.3.2 | Example 2 – Printout Containing Memory Errors        |     |

| 5.3.3.3 | Example 3 – Printout Showing Non-Contiguous Memory 5 |     |

| 5.4     | Digital's Services                                   |     |

| 5.4.1   | Digital Repair Service 5                             |     |

|         |                                                      |     |

## **FIGURES**

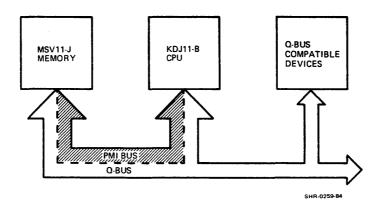

| 1-1 | Q-Bus/PMI Bus Interface                 | 1-1 |

|-----|-----------------------------------------|-----|

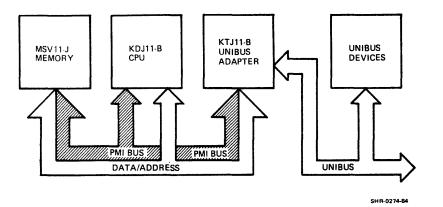

| 1-2 | ÙNIBUS/PMI Bus Interface                | 1-2 |

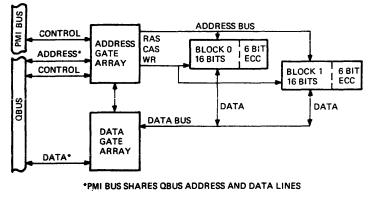

| 1-3 | MSV11-J Simplified Block Diagram        | 1-5 |

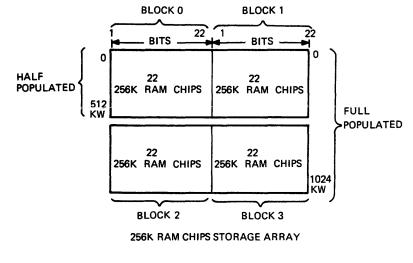

| 1-4 | MOS Storage Array Architecture          |     |

| 2-1 | Address Flow (Read, Write, Write Byte)  | 2-2 |

| 2-2 | Read Cycle Data Flow                    | 2-3 |

| 2-3 | Write Cycle Data Flow                   | 2-4 |

| 2-4 | Write Byte Cycle Data Flow              | 2-5 |

| 2-5 | Byte Selection for Write Byte Operation | 2-6 |

| 3-1 | Odd/Even Memory Request for Block Mode  | 3-3 |

| 4-1 | MSV11-J Jumpers                         | 4-2 |

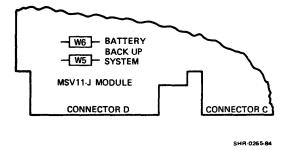

| 4-2 | Battery Backup Jumper Connection        | 4-3 |

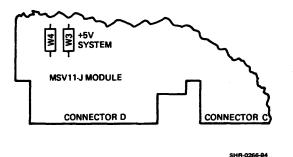

| 4-3 | +5 V Jumper Connections                 | 4-3 |

| 4-4 | CSR Bit Assignments                     | 4-8 |

## **TABLES**

| 1-1 | O-Bus Cycle – MSV11-JD and -JE Only                 | 1-4  |

|-----|-----------------------------------------------------|------|

| 1-2 | PMI Bus Cycle                                       | 1-4  |

| 4-1 | Starting Memory Address Selection                   | 4-4  |

| 4-2 | CSR Address Selection                               | 4-6  |

| 4-3 | Backplane Pin Utilization                           | 4-7  |

| 4-4 | CSR Bit Descriptions                                | 4-8  |

| 4-5 | Operating Modes                                     | 1-14 |

| 4-6 | Error Condition Summary for Various Operating Modes | 1-24 |

| 4-7 | Error Logging                                       | 1-26 |

| 5-1 | Switch Settings                                     | 5-2  |

## CHAPTER 1 GENERAL DESCRIPTION AND SPECIFICATIONS

#### **1.1 INTRODUCTION**

The MSV11-J is a metal oxide semiconductor, random access memory. It uses error detection and correction (ECC), a control and status register (CSR) to store status and error information, and has starting addresses on 8 kW boundaries. The board can be configured half or fully populated with 256K dynamic RAMs. Maximum memory capacity is 2 Mb.

The memory is designed for Q-bus systems and supports the private memory interconnect (PMI) protocol of the KDJ11-B processor. The PMI bus is specifically designed for and used in the PDP-11/83 Q-bus System and the PDP-11/84 UNIBUS System.

A PDP-11/83 Q-bus system uses the KDJ11-B CPU module, one or more MSV11-J memory modules and a selection of Q-bus compatible devices. Data transfers between the KDJ11-B CPU and MSV11-J memory use the PMI protocol. All other communications, whether originated by the CPU or other bus master, occur via Q-bus protocol (Figure 1-1).

NOTE: The location of the MSV11-J in the PDP-11/83 backplane determines the protocol used between the KDJ11-B and the MSV11-J. For PMI protocol, the MSV11-Js must be located immediately in front (lower slot number) of the CPU; otherwise the memory and CPU communicate with the Q-bus protocol. There should be no open slot between memory and the CPU.

Figure 1-1 Q-Bus/PMI Bus Interface

A PDP-11/84 UNIBUS system uses the KDJ11-B CPU module, one or two MSV11-J memory modules, the KTJ11-B UNIBUS adapter (UBA) module, and a selection of UNIBUS compatible devices. The KDJ11-B, MSV11-J, and KTJ11-B modules communicate via PMI protocol. All communication between UNIBUS devices and the KTJ11-B occur via UNIBUS protocol. The KTJ11-B provides the appropriate interface between PMI and UNIBUS protocols (Figure 1-2).

Figure 1-2 UNIBUS/PMI Bus Interface

The MSV11-J memory provides the following features.

- Starting addresses on 8 kW boundaries

- Can be half or fully populated

- Executes normal Q-bus protocol and the faster PMI protocol. Q-bus protocol is possible only with the MSV11-JD and MSV11-JE variations.

- Uses two gate arrays (VLSI technology)

- Uses advanced Schottky TTL logic

- Battery backup can be configured on board

- Green LED on module to indicate the presence of +5 volts (+5 VBB when configured for battery backup)

- On-board refresh of RAMs is transparent to CPU

- Compatible with 18- or 22-bit address backplane

- Error correction logic (ECC) to detect and correct single-bit errors and to detect double-bit errors

- Red LED on module to indicate detection of an uncorrectable error

- Contains control and status register which can be assigned one of 16 addresses

- Error correction code (ECC) operation can be controlled via CSR

- CSR operating modes facilitate diagnostic testing

- Memory compatible with Q-CD backplanes (not compatible with Q-Q backplanes)

NOTE: Insertion of the MSV11-J in a Q-Q backplane may damage other components or the memory itself. The PMI bussing on the MSV11-J's CD connectors is not compatible with the +12 V bussing on the Q-Q backplane.

#### **1.2 DESCRIPTION**

The MSV11-J is an LSI-11 Q-bus quad-height module. It uses error correction (ECC) for increased reliability and is available in the following configurations.

| Option<br>Number | Module<br>Designation | Description                                                 |

|------------------|-----------------------|-------------------------------------------------------------|

| MSV11-JB         | M8637-B               | 1 Mb ECC using 256K dynamic RAMs-<br>PDP-11/84 ONLY         |

| MSV11-JC         | M8637-C               | 2 Mb ECC using 256K dynamic RAMs-<br>PDP-11/84 ONLY         |

| MSV11-JD         | M8637-D               | 1 Mb ECC using 256K dynamic RAMs-<br>PDP-11/84 or PDP-11/83 |

| MSV11-JE         | М8637-Е               | 2 Mb ECC using 256K dynamic RAMs-<br>PDP-11/84 or PDP-11/83 |

NOTE: Modules designated MSV11-JB and MSV11-JC may be used in the PDP-11/84 (UNIBUS) system only. Modules designated MSV11-JD and MSV11-JE may be used in both the PDP-11/84 and PDP-11/83 (Q-bus) systems.

The memory starting address can be set at any 8 kW boundary within the 2048 kW extended address space. (The extended address space contains 22 address lines.)

#### **1.2.1 Error Correction**

The MSV11-J contains ECC logic which detects and corrects single-bit errors and detects double-bit errors. Detecting and correcting single-bit errors is transparent to the master device accessing the memory.

#### **1.2.2 Battery Backup**

MOS storage devices are volatile (data is not retained when power is lost). Therefore, during an ac power failure, dc power is available to MOS memory for a limited time only. The MSV11-J memory module has inputs for two sources of +5 V power. These inputs are designated +5 VBB and +5 V. The +5 VBB module input can be connected to a battery backed-up power system; the +5 V input is not battery supported. In battery support mode, power is used only to refresh the MOS storage array so that battery backup time, and therefore data retention time, is maximized. A green LED on the module stays on as long as +5 VBB is available. Modules are shipped in a non-battery backed-up configuration; the module needs a jumper change to configure it for battery backed up applications.

The PDP-11/84 system can be shipped in a battery backup system configuration or in a non-battery backup system configuration. In a battery backup system configuration, the memory is tied to the battery backup supply through the backplane and power connector. Therefore, the MSV11-J modules should not be configured for battery backup mode in either of the above mentioned system configurations.

#### **1.2.3 ECC Initialization**

The MSV11-J performs an error correction initialize (ECC INIT) operation after the power-up (+5 BBU power up in battery backed up systems). For an ECC INIT operation, a pattern is written into all memory locations in the MOS storage array. All MOS RAMs on the module are written sequentially during initialization. The circuitry senses the presence of 5 VBB and DCOK before starting the initialization sequence. Signal BPOK is deasserted by memory while ECC INIT is in progress.

#### 1.2.4 Control and Status Register (CSR)

The control and status register in the MSV11-J allows program control of certain ECC functions, and stores diagnostic information if an error occurs. The CSR has its own address in the I/O peripheral page, and can be read or written into by any device designated as bus master.

#### 1.2.5 Bus Cycles

The MSV11-J supports the following Q-bus and PMI bus cycles (Tables 1-1 and 1-2). These bus cycles, executed by bus master devices, transfer 16-bit words or 8-bit bytes to or from slave devices.

| Bus Cycle<br>Mnemonic | Description                 | Function (with Respect to Bus Master) |

|-----------------------|-----------------------------|---------------------------------------|

| DATI                  | Data word input             | Read                                  |

| DATO                  | Data word output            | Write                                 |

| DATOB                 | Data byte output            | Write byte                            |

| DATIO                 | Data word input/output      | Read-modify-write                     |

| DATIOB                | Data word input/byte output | Read-modify-write byte                |

| DATBI                 | Block mode input            | Block Read                            |

| DATBO                 | Block mode output           | Block Write                           |

#### Table 1-1 Q-Bus Cycle - MSV11-JD and -JE Only

#### Table 1-2 PMI Bus Cycle

| Bus Cycle<br>Mnemonic | Description          | Function (with Respect to Bus Master) |

|-----------------------|----------------------|---------------------------------------|

| (P) DATI*             | Data input (2 words) | Read                                  |

| (P) DATBI*            | Block mode input     | Block mode read                       |

| (P) DATO*             | Data word output     | Write                                 |

| (P) DATOB*            | Data byte output     | Write byte                            |

\* The P in parentheses preceding the cycle type denotes PMI cycle.

#### 1.2.6 Refresh

The MSV11-J refresh circuitry guarantees that the data stored in the MOS RAMs is valid for extended periods of time. The interval between refresh cycles is set to about 14  $\mu$ s to guarantee accessing all 128 rows in 2 ms (128 cycle refresh) or 256 rows in 4 ms (256 cycle refresh).

Refresh requests are initiated every 14.0  $\mu s \pm 5$  percent from an asynchronous oscillator on the module. These single refresh cycles are initiated at the end of a bus memory access. If the memory does not receive a bus memory access request within 9  $\mu s$  of a single refresh request, it changes that request to a double refresh request, appending two refreshes to the end of the next bus memory access. Double refresh is not valid on the MSV11-JB or MSV11-JC memories.

A refresh priority cycle is enabled if a bus memory access has not occurred within two refresh periods (i.e., 28  $\mu$ s) and the refresh request cycles have not been peformed. During a refresh priority cycle, the next memory cycle is preceded by two refresh cycles. If a memory cycle is not initiated within 3  $\mu$ s of the assertion of refresh priority cycle, the refresh logic initiates its own refresh demand cycle.

#### 1.2.7 Simplified Block Diagram Description

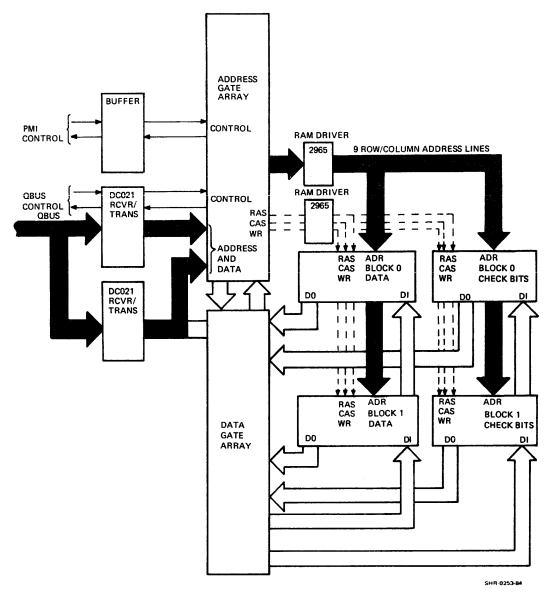

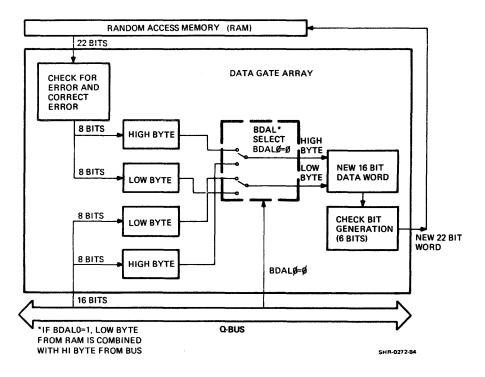

Figure 1-3 is a simplified block diagram of the memory. The bus interface, address gate array, data gate array, and MOS storage array are shown. The address gate array contains the ECC initialization circuitry, memory refresh circuitry, and the timing and control for PMI and Q-bus cycle types.

The data gate array contains the ECC logic, generates check bits for write cycles, and uses the check bits during read cycles to detect and correct single-bit errors and to detect double-bit errors.

The half-populated MOS storage array consists of two blocks – block 0 and block 1. The fully populated MOS storage array consists of four blocks – blocks 0, 1, 2, and 3. Each block is 22 bits wide and 256K deep (see Figure 1-4).

SHR-0264-84

Figure 1-3 MSV11-J Simplified Block Diagram

SHR-0271-84

Figure 1-4 MOS Storage Array Architecture

The 22-bit words in memory consist of 16 data bits and 6 check bits. The check bits are generated by the data gate array for each 16-bit data word. Although the MSV11-J memory word is 22 bits long, the bus master transactions are 16-bit words. The 6 check bits are internal to the memory.

The control and status register (CSR) performs the following major functions.

- It disables or enables error reporting to the CPU.

- It allows diagnostic programs to be run without having the diagnostic interfere with the check bits in the protected diagnostic area.

- It disables ECC, if desired. MSV11-J detects but does not correct errors.

- It flags single- or double-bit errors. If ECC is enabled, single-bit errors are corrected.

- The address of the error is latched in the CSR unless higher priority (double-bit error) is present.

- In diagnostic mode, syndrome or check bits can be returned to the processor if desired.

#### **1.3 Error Correction Code (ECC)**

ECC is a technique used to increase reliability of MOS memory. This is done by correcting single-bit errors. The use of ECC with MOS memory requires additional logic to generate check bits used in the detection and correction process.

ECC is practical not only due to the low cost of memory and logic, but also because the predominant failure mode in dynamic RAMs is single cell failures, distributed randomly. These failures occur at a low rate and the probability of two such failures (or one such failure and a soft bit error) occurring in coincidence is extremely small.

#### 1.3.1 Advantage of ECC

MOS RAM technology is constantly evolving and the RAM density quadruples for each new RAM introduction. Larger memory arrays make the probability of errors slightly higher even though the reliability of RAMs is improving.

Some advantages of using ECC with MOS RAM technology are:

- MOS RAMs, unlike core, are more susceptible to noisy power supplies.

- Soft errors due to inherent radiation traces (alpha particles) occasionally cause an individual bit in the RAM to lose its data. These soft errors are overwritten during the next WRITE to that location. ECC prevents a system failure until the overwriting can occur.

- Most hard errors (due to aging or premature defect of the RAM) occurring in a desired (by CPU) address cause a failed bit.

These three types of failures cause a system failure in parity memory but are transparent in ECC memory. ECC makes single-bit failure in the RAM transparent to the CPU by correcting single-bit errors "on the fly" before the CPU receives it. It thereby increases the effective MTBF (mean time between failures) of main memory. Also the memory failure rate doesn't proportionally increase as memory capacity increases.

#### **1.3.2 ECC Operation**

A check bit code is generated on each memory write cycle. This code is written into memory along with the 16-bit data word. On a memory read cycle, the check bits are read from memory along with the 16-bit data word. New check bits are generated and compared with the check bits read from memory. If the two groups of check bits are alike, no error is detected. If they are different, the difference between the two groups of check bits (syndrome bits) determines the failed bit, provided there is only one error. The ECC circuitry corrects the bit in the word and sends the word to the CPU.

In the case of a multiple error, the word is not corrected and is sent to the CPU with an asserted signal line warning the CPU that this data is invalid. This signal has the same effect as a parity flag in parity memory, at the occurrence of a single-bit error.

#### **1.3.3 Example of ECC-Implementation**

A fully populated MSV11-J is a 2 Mb memory. The memory storage consists of 22-bit words, (16 data bits plus 6 check bits) each bit position being in a different memory chip (RAM). However, the CPU reads from memory, or writes to memory, in 16-bit words.

For a write cycle (DATO function), the memory receives (from the CPU) the 16-bit word and generates the 6 check bits. This new 22-bit word is stored in the memory array.

For a read cycle (DATI function), the 22-bit word is fetched from memory and divided into two; the original 16-bit word (data) and 6 check bits. New check bits from the 16-bit data word are generated and compared with the check bits read from memory. If a single-bit error occurs, the ECC circuitry in memory corrects the data word containing the error. The corrected word is then transferred to the CPU. The data in the original memory location remains uncorrected.

For a DATOB function, only a byte is written into memory. To accomplish this function, the entire 16-bit data word and 6 check bits residing in memory must be read and checked for errors. Any single-bit error in the word is corrected. Assume, for example, that the CPU desires to write the lower byte. The new lower byte is combined with the high byte to form a new 16-bit data word. Check bits are generated on the new word and the entire word (16 data bits plus 6 check bits) is written back to memory.

The sequence of events is:

- 1. 22 bits read from memory.

- 2. Single-bit error corrected, if required.

- 3. New byte combined with old byte.

- 4. 6 check bits generated on new 16-bit word.

- 5. New 22-bit word written to memory.

#### **1.4 SPECIFICATIONS**

This paragraph describes the various MSV11-J specifications including access and cycle times for the Q-bus and P-bus protocol.

#### **1.4.1 General Specifications**

| Height<br>Width<br>Length | 10.436 inch quad height<br>0.5 inch<br>8.94 inch bottom of fingers to<br>top of handle, extended |

|---------------------------|--------------------------------------------------------------------------------------------------|

| Etch                      | 8 mil multilayer                                                                                 |

1-7

#### **User Options**

Starting addressStarting address = 08 kW boundariesCSR addressCSR addressCSR = 0 (17772100)(1 of 16)Q22Q18 or Q22Q22

#### New Technologies

| Drams                 | 256K dynamic RAMs     |

|-----------------------|-----------------------|

| Gate arrays           |                       |

| Advanced Schottky TTL | F series (fast) logic |

#### **Battery Backup**

5 VCC for bus support logic 5 VBB for MOS RAMs and refresh

#### Refresh

Interval between refresh cycles (guarantees accessing all 128 rows in 2 ms or 256 rows in 4 ms)

#### Error Correction Code Detects single and double-bit errors and corrects single-bit errors

1.4.2 Environmental Specifications

#### Temperature

Storage Temperature Range

-40 to +66 degrees Celsius

$14.0 \ \mu s \pm 5\%$

Default (All Switches Off)

Before operating a module which is at a temperature beyond the operating range, that module must first be brought to an environment within the operating range and then must be allowed to stabilize for a minimum of five minutes.

Operating Temperature Range

+5 to +60 degrees Celsius

De-rate the maximum operating temperature by one degree Celsius for each 1000 feet of altitude above 8000 feet.

#### **Relative Humidity**

| Storage   | 10 to 90%, noncondensing |

|-----------|--------------------------|

| Operating | 10 to 90%, noncondensing |

#### **Operating Airflow**

When the inlet temperature is +60 degrees Celsius, adequate airflow must be provided to limit the inlet to outlet temperature rise across the module to 5 degrees Celsius. For operation below +55 degrees Celsius, airflow must be provided to limit the inlet to outlet temperature rise across the module to 10 degrees Celsius maximum.

#### Altitude

MOVII IC IE

- Storage The module will not be mechanically or electrically damaged at altitudes up to 50,000 feet (90 MM mercury).

- 2. Operating Up to 50,000 feet (90 MM mercury).

NOTE: De-rate the maximum operating temperature by one degree Celsius for each 1000 feet of altitude above 8000 feet.

#### **1.4.3** Electrical Specifications

**1.4.3.1** Power Supply Requirements – The module operates on +5 V only, with provisions made for operating in a battery backup mode for long term data retention.

#### Current, Amps

| MSV11-JB, JD | Standby<br>Typ | Max  | Active<br>Typ | Max  | ECC Init<br>Typ | Max  |

|--------------|----------------|------|---------------|------|-----------------|------|

| +5 V only    | 0.5            | 0.56 | 0.5           | 0.57 | 0.5             | 0.57 |

| +5 V BBU     | 0.8            | 1.41 | 1.0           | 3.37 | 1.0             | 2.54 |

|              |                |      |               |      |                 |      |

| +5 V Total   | 1.3            | 1.97 | 1.5           | 3.94 | 1.5             | 3.11 |

#### Current, Amps

| MSV 11-JC, JE | Standby<br>Typ Max |      | Active<br>Typ Max |      | ECC Init<br>Typ Max |             |

|---------------|--------------------|------|-------------------|------|---------------------|-------------|

| +5 V only     | 0.5                | 0.56 | 0.5               | 0.57 | 0.5                 | 0.57        |

| +5 V BBU      | 1.0                | 1.72 | 1.2               | 3.72 | 1.25                | 4.00        |

|               |                    |      | <u></u>           |      |                     | <del></del> |

| +5 V Total    | 1.5                | 2.28 | 1.7               | 4.29 | 1.75                | 4.57        |

The 5 VCC and 5 VBB power supplies must not exceed the range minus 1.0 V to plus 7.0 V to avoid permanent stress damage to the MOS RAMs. Operating voltage range is 5 V  $\pm$  5 percent.

#### 1.4.4 Interface Specifications

**1.4.4.1 P-Bus Interface** – The memory communicates with the KDJ11-B processor via an enhanced protocol (p-protocol). Essentially, reads are two word transfers which take advantage of the KDJ11-B restart overhead to load a second 16-bit word into the cache on the CPU module. Write operations are initiated just after addresses are valid.

**1.4.4.2** Q-Bus Interface – In addition to the p-protocol, the memory is compatible with the LSI-11 bus (Q-bus). All signals are one bus load.

NOTE: MSV11-JB and MSV11-JC cannot perform Q-Bus protocol.

#### 1.4.4.3 Signal AC/DC Loading -

| 2.5 | ac loads | (1  ac load = 9.35 pF)                                           |

|-----|----------|------------------------------------------------------------------|

| 0.5 | dc loads | $(1 \text{ dc load} = 105 \text{ u}^{\text{A}} \text{ nominal})$ |

#### 1.4.5 Performance Specifications

This paragraph lists the access and cycle times for the P-bus and for the Q-bus.

#### NOTES:

- 1. Memory performance is the time measured from the output of the bus receivers to the input of the bus drivers.

- 2. This assumes PWTSTB occurs within 145 ns of PBCYC. Longer time to PWTSTB extends cycle time an equivalent amount of time.

- 3. Correction of single errors extend the access time of PMI DATI or DATBI cycles by 116 ns maximum.

- 4. R PBCYC to T PRD STB trailing edge.

- 5. T PRD STB trailing edge to second word valid.

- 6. R PBCYC to memory BUSY de-asserted.

- 7. T PRD STB trailing edge to next T PRD STB trailing edge with minimum PBLK response from bus master (240 ns).

- 8. R DAL (address) valid to T PSSEL.

- 9. R SYNC to TRPLY with minimum time from R SYNC to RDIN/RDOUT (25 ns/50 ns).

- 10. R SYNC to memory BUSY de-asserted.

- 11. DATO (B) cycles assume 50 ns from R SYNC to RDOUT.

- 12. The first transfer in a DATBI is the same as a DATI. Subsequent word access times are measured from R DIN de-asserted to TRPLY asserted with minimum bus timing (i.e., TRPLY negated to RDIN asserted = 150 ns). DATBI access time alternates between these two values due to the two word read architecture of the memory. Even word accesses (as determined by DAL 01) have a longer access and cycle time. Subsequent odd transfers realize the faster access and cycle time.

- 13. Minimum bus timing from T RPLY de-asserted to R DOUT asserted.

- 14. R PBCYC to memory BUSY de-asserted after 8 double-word transfers (16 words transferred) assuming minimum P BLK response from master (240 ns).

- 15. R QSYNC to memory BUSY de-asserted after 16 word transfers assuming minimum TRPLY, R DIN bus master timing.

#### Refresh

All access and cycle times are extended whenever a refresh conflict occurs.

| Maximum (ns) |

|--------------|

| 538          |

| 1006         |

| 1483         |

| 1483         |

|              |

#### 1.4.5.1 P-Protocol Access and Cycle Times (All MSV11-J Variations)

| Memory Performance (1)          |        |          |     |     |         |                     |         |      |

|---------------------------------|--------|----------|-----|-----|---------|---------------------|---------|------|

|                                 | Access | Time (ns | )   |     | Cycle T | <b>`ime (ns)</b> (6 | 5)      |      |

|                                 | Min    | Тур      | Max |     | Min     | Тур                 | Max     |      |

| DATI (3) 1st word<br>(no error) | 390    | 417      | 444 | (4) | 538     | 568                 | 597     |      |

| 2nd word                        | 35     | 58       | 80  | (5) | -       | -                   | <u></u> |      |

| DATBI (3)                       | 518    | 531      | 545 | (7) | 3794    | 4166                | 4539    | (14) |

| DATO                            | 30     | 38       | 45  | (8) | 538     | 568                 | 597     | (2)  |

| DATOB (3)                       | 30     | 38       | 45  | (8) | 746     | 788                 | 829     | (2)  |

| DATI CSR access                 | 390    | 417      | 444 | (4) | 538     | 568                 | 597     |      |

| DATO CSR access                 | 30     | 38       | 45  | (8) | 538     | 568                 | 597     |      |

\* Refresh requests are added to the end of a bus memory cycle. The next bus memory cycle is postponed until this refresh cycle is completed. Double refresh is not valid on MSV11-JB and MSV11-JC.

† Refresh priority cycles precede a memory cycle and delay access and cycle times.

**‡** Refresh demand cycles are self-initiated and may delay memory access and cycle times up to this length of time.

|                         | Access | Time (ns) | )   |                   | Cycle T | ' <b>ime (ns)</b> (1 | 0)    |      |

|-------------------------|--------|-----------|-----|-------------------|---------|----------------------|-------|------|

|                         | Min    | Тур       | Max |                   | Min     | Тур                  | Max   |      |

| DATI                    | 269    | 327       | 386 | (9)               | 556     | 605                  | 654   |      |

| DATBI<br>Even           | 268    | 324       | 381 | (12) <sup>.</sup> | 7261    | 8032                 | 8802  | (15) |

| Odd                     | 212    | 269       | 325 |                   | -       | -                    | -     |      |

| DATO (11)               | 88     | 135       | 182 | (9)               | 606     | 655                  | 704   |      |

| DATBO (11) (13)         | 88     | 135       | 182 |                   | 9423    | 9805                 | 10187 | (15) |

| DATOB (11)              | 88     | 135       | 182 | (9)               | 772     | 850                  | 929   |      |

| DATIO (13)              | 269    | 327       | 384 | (9)               | 1208    | 1333                 | 1457  |      |

| DATIOB (13)             | 269    | 327       | 384 | (9)               | 1415    | 1553                 | 1691  |      |

| DATI CSR access         | 269    | 327       | 386 | (9)               | 556     | 605                  | 654   |      |

| DATO CSR<br>Access (11) | 88     | 135       | 182 | (9)               | 606     | 655                  | 704   |      |

Memory Performance (1)

## CHAPTER 2 DATA FLOW

#### 2.1 INTRODUCTION

This chapter describes the basic data flow for read, write, and write byte cycles. Other bus cycle types are basically combinations of these. For example, block mode read cycles are similar to a succession of read cycles.

Each bus cycle contains an address portion and data transfer portion. The address portion of the various bus cycle types are similar in that the processor is addressing the slave device. The data transfer portion of each bus cycle type differs since the data flows in different directions for different cycle types. For example, a read cycle transfers data from memory to the processor while a write cycle transfers data from the processor to memory.

#### 2.2 ADDRESS PORTION OF BUS CYCLE

Figure 2-1 shows the address flow portion of the bus cycle. In the PMI bus protocol, if the address specified by the processor is within the address of the memory, the memory responds with a control signal to indicate that it has been selected.

In the Q-bus protocol, if the address specified by the processor is within the address range of the memory, the memory executes the requested cycle.

The address portion of the bus cycle is initiated when the processor places a 22-bit address on the bus. The address is received and compared with the memory's starting address to determine if the addressed location resides on that memory board. Nine of the address bits specify the row address and nine specify the column address.

After the row address becomes stable, row address strobe (RAS) is asserted.

The address gate array then switches from row address to column address. After the column address becomes stable, column address strobe (CAS) is asserted. Note that the nine address lines at the output of the address gate array are multiplexed and supply the row address followed by the column address.

The RAMs have multiplexed address inputs. Eighteen address bits (9 row address and 9 column address bits) are required to supply a unique address for each memory location.

There are 22 RAMs in each data word (88 RAMs on a fully populated board). There is one RAM for each bit of the 16-bit data word and one for each of the 6 check bits.

Each set of 22 RAM chips makes up a block of memory. A fully populated board has 4 blocks or a total of 88 RAM chips (see Figure 1-4).

Figure 2-1 Address Flow (Read, Write, Write Byte)

The row and column address bits specify the same address in all blocks. Therefore, two additional bits are required to uniquely define one of the blocks. One bit (BDAL1) defines odd/even word selection for a read or write cycle. In other words, BDAL1 selects the left (even) block or the right (odd) block (Figure 1-4). The second bit is BDAL20 which selects the upper block or the lower block.

For a write cycle, the processor must specify which block the word is to be written to. This is accomplished by BDAL1 and BDAL20.

#### 2.3 DATA TRANSFER PORTION OF BUS CYCLE

The following paragraphs describe the data transfer portion of the read cycle, write cycle, and write byte cycle in terms of data flow.

Figure 2-2 Read Cycle Data Flow

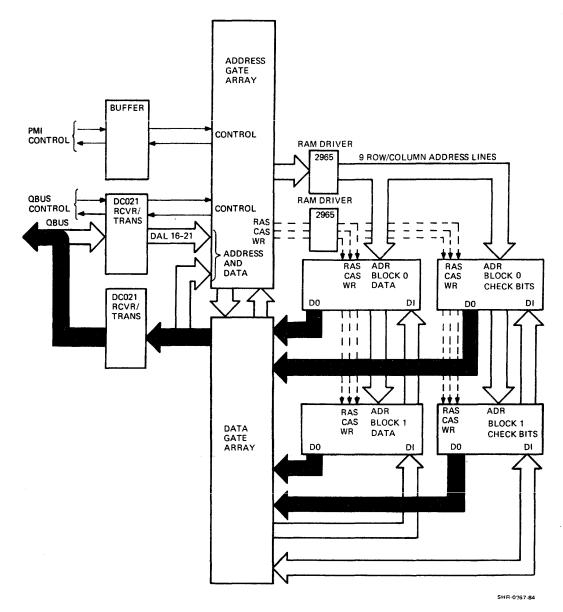

#### 2.3.1 Read Data Transfer (Figure 2-2)

Read cycles are executed as two-word reads from two different locations – one word from block 0 and one word from block 1.

When CAS goes low, the RAM output drivers are turned on. After data becomes valid, the two 22-bit words are transferred to the data gate array and latched in this array under control of the address gate array.

For a Q-bus read cycle, the processor specifies which word is to be transferred. For a PMI-bus read cycle, the processor specifies which word is transferred to the bus first. This is accomplished by BDAL1.

If Q-bus protocol is used, only one word is placed on the bus. BDAL1 selects the word to be placed on the bus. If an error occurs in the first word, the error is corrected and no loss in access time occurs.

If PMI protocol is used, both words are placed on the bus serially. BDAL1 selects the word to be placed on the bus first. If an error occurs in the first word of the two-word read, the data is stalled while the error correction takes place. If an error occurs in the second word instead of the first word, the error is corrected with no loss of cycle time.

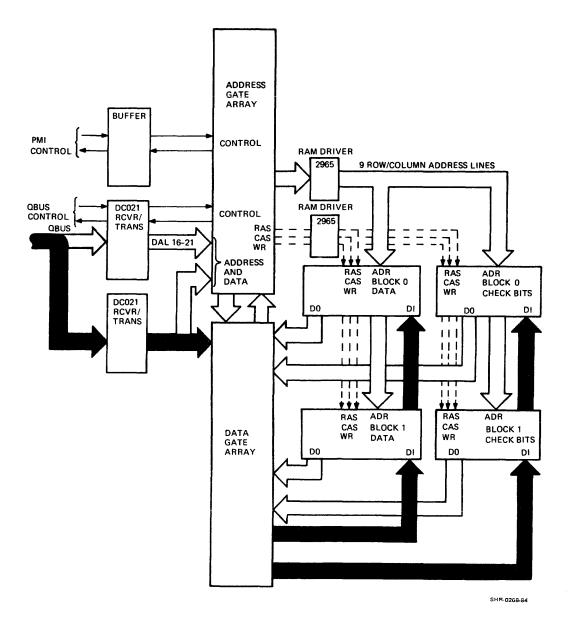

#### 2.3.2 Write Data Transfer (Figure 2-3)

Write cycles are single-word writes to RAM. The processor places a 16-bit data word on the bus thus initiating the data transfer portion of this bus cycle. The data is received by two DC021 transceivers and then the data gate array. The data gate array generates 6 check bits from the 16-bit data word. The address gate array determines which block of memory is written and asserts the write signal. The 22-bit word is then written in the appropriate block.

The state of BDAL1 determines in which block of memory the word is written. If BDAL1=0, the word is written in block 0 and if BDAL1=1, the word is written in block 1.

Figure 2-3 Write Cycle Data Flow

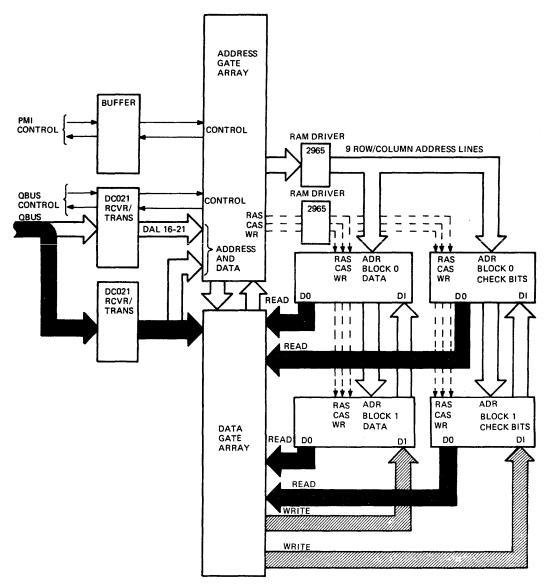

#### 2.3.3 Write Byte (Figure 2-4)

The write byte data transfer is actually a read-modify-write to the RAMs. In ECC memory, the check bits are encoded on a 16-bit word basis. Therefore, it is necessary to read the whole word (16 data bits plus 6 check bits) from memory. The word is transferred to the data gate array and checked for errors. If there is a single-bit error, it is corrected.

The processor places a 16-bit word (two bytes) on the Q-bus. One of the two bytes is the byte to be written to memory. This byte is combined in the data gate array with the appropriate byte from memory and a new 16-bit word is formed.

Check bits are calculated on the new 16-bit word resulting in a 22-bit data word. The 22-bit word is then written back to memory.

SHR-0270-84

Figure 2-4 Write Byte Cycle Data Flow

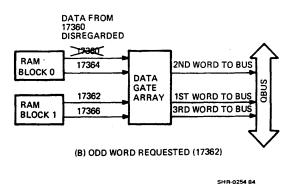

Figure 2-5 shows how the write byte operation is performed. The figure assumes the low byte is to be modified. The low byte from the bus is combined in the data gate array with the high byte from memory and a new 16-bit data word is formed. BDAL0 determines the appropriate byte from the bus and the appropriate byte from memory.

If BDAL0=0, the high byte from memory is combined with the low byte from the bus. If BDAL0=1, the low byte from memory is combined with the high byte from the bus.

Figure 2-5 Byte Selection for Write Byte Operation

1

## CHAPTER 3 MEMORY CYCLES

#### 3.1 INTRODUCTION

This chapter describes the following types of MSV11-J memory cycles.

- O-bus (MSV11-JD and MSV11-JE only)

- PMI bus

- Refresh

- ECC initialization (ECC INIT)

Bus cycles are categorized as read, write word, write byte, block mode read, block mode write, read-modify-write, and read-modify-write byte cycles.

Refresh and ECC INIT cycles are internal to the memory. The following paragraphs in this chapter provide additional detail on bus cycles and internal cycles.

#### 3.2 BUS CYCLES

This paragraph describes the basic differences between the Q-bus and PMI bus protocols for the various cycle types.

#### 3.2.1 Read Cycles

Read cycles may be memory read cycles where data is read from RAM, or CSR read cycles where data is read from CSR.

**3.2.1.1 Memory Read Cycle** – Memory read cycles are two-word reads from RAM. Each word consists of 16 data bits plus 6 check bits.

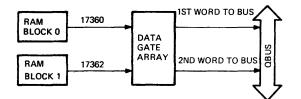

For Q-bus memory read cycles, two data words are latched into the data gate array. However, only one word is placed on the Q-bus.

For PMI bus memory read cycles, two data words are latched into the data gate array and both words are placed on the bus. Either word may be selected to be placed on the bus first. If the odd word is placed on the bus first, it is followed by the preceding even word. For example, if a word at address 17362 is selected to be placed on the bus first, the next word transferred will be from address 17360. If the even word is selected to be placed on the bus first, the next odd word is then transferred second. For example, if a word at address 17360 is selected to be placed on the bus first, the next odd word is then transferred second. For example, if a word at address 17360 is selected to be placed on the bus first, the next odd word is then transferred will be at address 17362.

**3.2.1.2** CSR Read Cycles – CSR read cycles on the Q-bus and PMI bus are single-word read cycles. No error detection/correction occurs for CSR data.

#### 3.2.2 Write Word Cycles

Write word cycles may be memory write word cycles where data is written in RAM or CSR write word cycles where data is written in the CSR.

**3.2.2.1** Memory Write Word Cycles – Memory write word cycles are single-word cycles. After memory receives the data word it generates 6 check bits. The 22 bits are then written to memory.

**3.2.2.2** CSR Write Word Cycles – CSR write word cycles on the Q-bus and PMI bus are single write word cycles. Check bits are not generated for CSR write word cycles.

#### 3.2.3 Write Byte Cycle

Q-bus and PMI bus write byte cycles are similar. The check bits for each cycle type are generated by memory on the basis of a 16-bit word. The write byte cycle is executed as a read cycle followed by a write word cycle. The sequence of events is as follows.

- 1. The word containing the byte to be modified is read from memory and is latched in the data gate array.

- 2. Error correction occurs if required.

- 3. The 16-bit data word on the bus containing the new byte is latched in the data gate array.

- 4. The new byte is combined with the old byte from the memory to form a new 16-bit data word.

- 5. New check bits are generated for this 16-bit word.

- 6. The new 22-bit data word is written to RAM.

NOTE: A single-bit error is corrected if one occurs. If a double error occurs, the word cannot be corrected and is written back to memory. No write byte cycle occurs. During subsequent reads of that location, the errors are detected and reported back to the processor.

#### 3.2.4 Block Mode Read Cycles

Q-bus block mode read cycles are successive 16-bit word transfers. Two 16-bit words are read from memory and latched into the data gate array on read cycles. The address gate array takes advantage of this fact during Q-bus block mode read cycles.

During Q-bus block mode transfer, the gate array accesses RAM and a two-word internal read occurs. Both words are latched in the data gate array. Error correction is performed if there is an error. Either one of the two words may be placed on the bus first.

If the processor requests an even word, the even word is placed on the bus. On the next cycle, the odd word, which is already latched in the gate array, is placed on the bus. A second RAM access is not necessary, in this case, as the odd word is already latched in the data gate array (Figure 3-1A).

For example, if the processor requests the data in address 17360, the data in address 17360 and 17362 is latched into the data gate array and the data in address 17360 is placed on the bus. On the next bus cycle, the data in address 17362 (which is latched in the data gate array) is placed on the bus (Figure 3-1A).

If the processor requests an odd word be placed on the bus, that word and the preceding word are latched in the data gate array, and the odd word is placed on the bus. The even word is disregarded as addresses are incremented for block mode read cycles. The next bus cycle causes two more words to be transferred from RAM to the data gate array. The even word is placed on the bus. The odd word is transferred to the bus during the next bus cycle.

(A) EVEN WORD REQUESTED (17360)

Figure 3-1 Odd/Even Memory Request for Block Mode

For example, if the data in address 17362 is requested to be placed on the bus, the data in address 17360 is disregarded (Figure 3-1B). The next bus cycle causes the data in addresses 17364 and 17366 to be latched in the data gate array. The data in 17364 is placed on the bus. The next cycle causes the data in 17366 to be placed on the bus. Since the data in 17366 was already latched in the data gate array, a RAM access for this data was not required.

PMI bus block mode read cycles always start on even word boundaries and consist of double-word transfers. Two words are placed on the bus during each successive read cycle.

#### 3.2.5 Block Mode Write Cycles

Q-bus block mode write cycles are a succession of single write word cycles to successive memory locations. In the Q-bus write word cycle, there is overhead time between cycles. By using Q-bus block mode write cycles, this overhead is minimized (i.e., no address required in protocol between successive writes).

There are no PMI bus block mode write cycles. In PMI bus write word cycles, the processor can execute the write word cycles very quickly. Therefore, it is not necessary to implement PMI bus block mode write cycles.

#### 3.2.6 Read-Modify-Write Cycle

Memory executes a Q-bus read-modify-write cycle as a read cycle followed by a write cycle to the same location. Memory executes this single-bus cycle as two internal cycles.

There are no read-modify-write cycles in the PMI protocol. A read-modify-write cycle is executed as two bus cycles – a read cycle followed by a separate write cycle to the same location.

#### 3.2.7 Read-Modify-Write Byte Cycle

Memory executes the Q-bus read-modify-write byte as a read cycle followed by a write byte cycle to the same location. Memory executes this single-bus cycle as two internal cycles.

There are no read-modify-write byte cycles in the PMI protocol. A read-modify-write byte cycle is executed as two bus cycles – a read cycle followed by a separate write byte cycle to the same location.

#### 3.3 REFRESH CYCLE

Each memory cell slowly loses its charge so a refresh cycle is needed to restore the contents of memory. Each row of memory must be refreshed every 4 msec.

Refresh is an asynchronous operation whose period is determined by an on-board oscillator. The refresh logic is contained in the address gate array. The array also contains a refresh address counter which keeps track of the rows that are refreshed.

#### 3.4 ECC INIT CYCLE

The ECC INIT cycle is an internal cycle executed only during power up. Its purpose is to write known data into all memory locations soon after power up. Memory writes zeroes in all cells and generates the check bits associated with the cleared memory cells.

A memory location that has not been written to since power up contains unknown random data. If a write byte cycle was performed at that location, an error would most likely occur. In this case, the word read from memory is written back to memory and the write byte cycle aborts. No error indication is flagged. Subsequent read cycles at that same location inform the processor of the error condition.

ECC INIT eliminates the error condition for write byte cycles by clearing the memory cells of invalid data.

For systems without battery backup, ECC INIT occurs when +5 V appears during power up. For systems with battery backup, ECC INIT occurs when the battery backup voltage (+5 VBB) occurs. When +5 V reappears on battery backup systems, ECC INIT is not executed since the data is valid and was not lost.

## CHAPTER 4 CONFIGURATION AND CSR OPERATION

#### 4.1 INTRODUCTION

This chapter describes the module installation, control and status register (CSR) operation, operating modes, and error reporting log.

The module installation description includes switch and jumper configurations, memory addressing, CSR addressing, and backplane placements.

The CSR description includes CSR bit format, and descriptions of each bit.

The description of operating modes includes normal modes of operation and various diagnostic modes.

The error reporting description includes error logging performed during PMI bus and Q-bus cycles for single-bit and double-bit errors. From a module viewpoint, errors occurring during read and write byte cycles are latched in the CSR. From the system viewpoint, only uncorrectable errors occurring during read cycles are reported to the central processor. Errors during write byte cycles are not reported.

#### 4.2 MODULE INSTALLATION

Before you remove or replace an MSV11-J memory module, exercise the following cautions.

CAUTION: Static charges can damage the MOS memory chips. Be careful how you handle the module and where you lay it down.

When you install or remove the memory module, make sure there is no dc voltage applied to the module.

If the green LED is on, the module is receiving +5 V from the power supply or battery backup. The power source must be off before you remove or replace a memory module.

#### 4.2.1 Jumper Configurations and Switch Settings

The MSV11-J has jumpers installed at the factory to establish the configuration of the module.

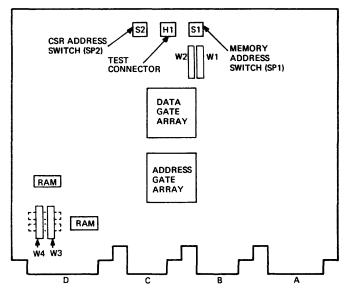

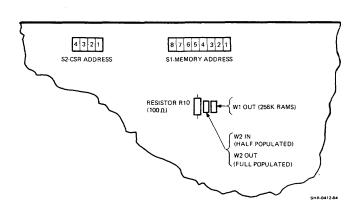

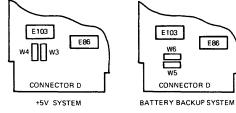

The MSV11-J contains two switchpacks – one is an 8-switch DIP (dual in-line package) and one is a 4switch DIP. The 8-switch DIP selects the starting memory address on an 8Kword boundary. The 4-switch DIP selects the CSR starting address. One of 16 possible CSR addresses may be selected. 4.2.1.1 Jumper Installation – The following chart summarizes the MSV11-J jumpers (see Figure 4-1).

| Jumper                                             | Description                                     |

|----------------------------------------------------|-------------------------------------------------|

| W1 Out                                             | 256K dynamic RAMs                               |

| W2 In<br>W2 Out                                    | Half populated module<br>Fully populated module |

| W5, W6 mounted<br>horizontally<br>(see Figure 4-2) | Battery backup system                           |

| W3, W4 mounted<br>vertically<br>(see Figure 4-3)   | +5 V system                                     |

NOTE: PDP-11/84 systems are available in a battery backup configuration. In these systems, +5 V BBU is bussed to the +5 V pins in the two slots reserved for the MSV11-J. These memories must NOT be changed to the battery backup configuration.

SHR-0269-84

Figure 4-1 MSV11-J Jumpers

Figure 4-2 Battery Backup Jumper Connection

Figure 4-3 +5 V Jumper Connections

**4.2.1.2** Memory Address Switch Settings – The memory address switch settings are shown in Table 4-1. The table is divided into 3 columns – the decimal switch settings in 8Kword increments, the octal equivalent, and the actual switch settings shown in binary. The memory address switch (SP1 in Figure 4-1) is an 8-switch DIP (dual in-line package). The least four significant switch settings (5 through 8) of the memory address switch (SP1) represent 8Kword increments as shown in the upper half of the table. For example, if these switch settings (5 through 8) are 0s, a memory address of 0 is represented (assuming switches 1 through 4 are also 0). If switch setting 8 is a 1 (all others being 0s), the memory address is incremented by 8Kwords. If switch setting 7 is a 1, with all other switch settings set to 0, the memory address is incremented by another 8Kwords. The upper half of the table shows the effect of switch settings 5 through 8. Note that switch settings 1 through 4 are all 0s in the upper half of the table and do not come into play until 128Kwords are reached.

The lower half of the table represents increments of 128K until 2 M is reached. Note that switch settings 4 through 1 come into play here. Each increment of these switch settings represents an increase of 128K. For example, if switch setting 4 is a 1 and switch settings 3 through 1 are 0s, a starting address range of 128K to 248K is selected. The specific memory starting address selected within that range is determined by switch settings 8 through 5 (indicated by Xs in the lower half of the table).

| Table 4-1 | Starting | Memory     | Address  | Selection |

|-----------|----------|------------|----------|-----------|

|           | Starting | Tracinoi y | 71001033 | Selection |

| Decimal (Kwords) | Octal             | Switch Setting (SP1)<br>1 2 3 4 5 6 7 8 |  |

|------------------|-------------------|-----------------------------------------|--|

| 0                | 0000000           | 0000000                                 |  |

| 8                | 00040000          | 0000001                                 |  |

| 16               | 00100000          | 0000010                                 |  |

| 24               | 00140000          | 0000011                                 |  |

| 32               | 00200000          | 00000100                                |  |

| 40               | 00240000          | 00000101                                |  |

| 48               | 00300000          | 00000110                                |  |

| 56               | 00340000          | 00000111                                |  |

| 64               | 00400000          | 00001000                                |  |

| 72               | 00440000          | 00001001                                |  |

| 80               | 00500000          | 00001010                                |  |

| 88               | 00540000          | 00001011                                |  |

| 96               | 00600000          | 00001100                                |  |

| 104              | 00640000          | 00001101                                |  |

| 112              | 00700000          | 00001110                                |  |

| 120              | 00740000          | 00001111                                |  |

| 000-120          | 0000000-00740000  | 0 0 0 0 X X X X                         |  |

| 128-248          | 0100000-01740000  | 0 0 0 1 X X X X                         |  |

| 256-376          | 0200000-02740000  | 0 0 1 0 X X X X                         |  |

| 384-504          | 0300000-03740000  | 0 0 1 1 X X X X                         |  |

| 512-632          | 0400000-04740000  | 0 1 0 0 X X X X                         |  |

| 640-760          | 0500000-05740000  | 0 1 0 1 X X X X                         |  |

| 768-888          | 0600000-06740000  | 0 1 1 0 X X X X                         |  |

| 896-1016         | 0700000-07740000  | 0 1 1 1 X X X X                         |  |

| 1024-1144        | 1000000-10740000  | 1000XXXX                                |  |

| 1152-1272        | 1100000-11740000  | 1 0 0 1 X X X X                         |  |

| 1280-1400        | 1200000-12740000  | 1010XXXX                                |  |

| 1408-1528        | 1300000-13740000  | 1011XXXX                                |  |

| 1536-1656        | 1400000-14740000  | 1 1 0 0 X X X X                         |  |

| 1664-1784        | 1500000-15740000  | 1 1 0 1 X X X X                         |  |

| 1792-1912        | 1600000-16740000  | 1 1 1 0 X X X X                         |  |

| 1920-2040        | 17000000-17740000 | 1 1 1 1 <b>X X X X</b>                  |  |

NOTE: I = Switch on 0 = Switch off X = Switch can be either on or off

Several examples are provided below to help you understand the table.

Example 1 – Desired starting memory address = 144K

Switch 1234 0001 Selects 128K-248K range (see lower half of Table 4-1) 144K -128K 16K 5678 0010 represents 16K (see upper half of Table 4-1) Starting memory address of 144K = switchsettings of: Switch 12345678 00010010 Setting Example 2 – Desired starting memory address = 1.576 M Switch 1234 1100 Selects 1536K to 1656K range (see lower half of Table 4-1) 1576K -1536K 40K 5678 0101 represents 40K (see upper half of Table 4-1) Starting memory address of 1.576 M = switch settings of: Switch 12345678 Setting 11000101

**4.2.1.3** CSR Address Switch Settings – The CSR address switch (Figure 4-1) is a 4-switch DIP (dual inline package) which allows selection of one of 16 CSR addresses. Table 4-2 shows the possible CSR addresses for 18-bit and 22-bit systems. The switch setting for a particular CSR address is the same whether the CSR is in an 18-bit or 22-bit system. For example, the switch setting is 1110 for a 22-bit CSR address of 17772134 or an 18-bit CSR address of 772134.

| 22-Bit CSR<br>Address | 18-Bit CSR<br>Address | Switch<br>Setting<br>1 2 3 4 |  |

|-----------------------|-----------------------|------------------------------|--|

| 17772100              | 772100                | 0000                         |  |

| 17772102              | 772102                | 0001                         |  |

| 17772104              | 772104                | 0010                         |  |

| 17772106              | 772106                | 0011                         |  |

| 17772110              | 772110                | 0100                         |  |

| 17772112              | 772112                | 0101                         |  |

| 17772114              | 772114                | 0110                         |  |

| 17772116              | 772116                | 0111                         |  |

| 17772120              | 772120                | 1000                         |  |

| 17772122              | 772122                | 1001                         |  |

| 17772124              | 772124                | 1010                         |  |

| 17772126              | 772126                | 1011                         |  |

| 17772130              | 772130                | 1100                         |  |

| 17772132              | 772132                | 1101                         |  |

| 17772134              | 772134                | 1110                         |  |

| 17772136              | 772136                | 1111                         |  |

#### Table 4-2 CSR Address Selection

NOTE:

1 = Switch on

0 = Switch off

#### 4.2.2 Backplane Placements

The PDP-11/83 and PDP-11/84 system backplanes are designed for the MSV11-J memory which incorporate Q-bus and PMI-bus protocols. The MSV11-JB and MSV11-JC memory variations can only be used in PDP-11/84 systems. The MSV11-JD and MSV11-JE variations can be used in PDP-11/84 or PDP-11/83 systems.

As a cross-product, the MSV11-J memory can be installed in a Q-CD backplane. However, you must not install an option in a slot adjacent to the MSV11-J that uses pins in the CD connector. Instead, leave an empty slot between the MSV11-J and this option. An option which does not use pins in the CD connector may be placed adjacent to the MSV11-J.

NOTE: Do not install the MSV11-J in a Q-Q backplane since this backplane shorts Q-bus signals to PMI bus signals and the system will not operate. This can also result in damage to the MSV11-J and other modules in a Q-Q backplane.

The location of the MSV11-J memories in a PDP-11/83 system determine the protocol to be used between memory and CPU. For PMI protocol, the MSV11-Js must be located immediately in front (lower slot number) of the CPU; otherwise the memory and CPU will communicate with the Q-bus protocol.

Table 4-3 shows the backplane pin assignments. Connectors A through D are shown across the top and pin numbers A through V (excluding G, I, O, and Q) are listed down the side. Backplane pins are designated first by slot, then by pin number, and then by the side of the module. A typical example is shown below.

|                                                                             | C A |

|-----------------------------------------------------------------------------|-----|

| Connector (A through D)                                                     |     |

| Connector (A through D)                                                     |     |

| Pin (A through V except G, I, O, and Q) ——————————————————————————————————— |     |

| side $1 = \text{component side},$                                           |     |

| Table 4-3 Backplane Pin Util | tilization |

|------------------------------|------------|

|------------------------------|------------|

| Pin | Connector A<br>Side 1 | Side 2       | Connector<br>Side 1 | B<br>Side 2 | Connector (<br>Side 1 | Side 2 | Connector<br>Side 1 | D<br>Side 2 |

|-----|-----------------------|--------------|---------------------|-------------|-----------------------|--------|---------------------|-------------|

| Α   |                       | 5V           | BDCOK               | 5V          | S RUN                 | 5V     | PBYT                | 5V          |

| В   |                       |              | BPOK                |             | PSSEL                 | PSSEL  | PWTSTB              | PWTSTB      |

| С   | BDAL16                | GND          | BDAL18              | GND         | S RUN                 | GND    | PBYT                | GND         |

| D   | BDAL17                |              | BDAL19              |             | PUBMEM                | PUBMEM | PMAPE               | PMAPE       |

| Ε   |                       | BDOUT        | BDAL20              | BDAL2       | PBCYC                 | PBCYC  |                     |             |

| F   |                       | BRPLY        | BDAL21              | BDAL3       | PUBSYS                | PUBSYS |                     |             |

| Н   |                       | BDIN         |                     | BDAL4       | PHBPAR                | PHBPAR |                     |             |

| J   | GND                   | BSYNC        | GND                 | BDAL5       | <b>PSBFUL</b>         | PSBFUL |                     |             |

| Κ   | <b>REF KILL</b>       | BWTBT        |                     | BDAL6       | PLBPAR                | PLBPAR |                     |             |

| L   |                       |              |                     | BDAL7       |                       |        |                     |             |

| Μ   | GND                   | BIAKI        | GND                 | BDAL8       | PRDSTB                | PRDSTB |                     |             |

| Ν   |                       | BIAKO        |                     | BDAL9       |                       |        |                     |             |

| Р   |                       | BBS7         |                     | BDAL10      | PBLKM                 | PBLKM  |                     |             |

| R   | BREF                  | BDMGI        |                     | BDAL11      | PBSY                  | PBSY   |                     |             |

| S   |                       | BDMG0        |                     | BDAL12      |                       |        | BBSY                | BBSY        |

| Т   | GND                   | BINIT        | GND                 | BDAL13      | GND                   |        | GND                 |             |

| U   |                       | <b>BDAL0</b> |                     | BDAL14      |                       |        | 5VBBU               | 5VBBU       |

| V   | 5VBBU                 | BDAL1        | 5V                  | BDAL15      | PUBTMO                | PUBTMO | 5VBBU               | 5VBBU       |

#### NOTES:

- 1. CAl is connected to CCl on the module

- 2. DA1 is connected to DC1 on the module

- 3. All PMI signals except PBYT have the connectors on side 1 etched to the respective signal on side 2 of the module

- 4. AM2 is connected to AN2 on the module

- 5. AR2 is connected to AS2 on the module

- 6. Side 1 is component side

- 7. Side 2 is back side

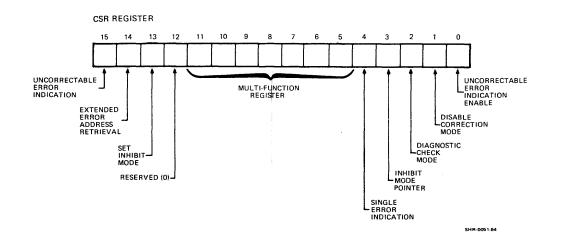

#### 4.3 CONTROL AND STATUS REGISTER (CSR)

The control and status register in the MSV11-J allows program control of certain ECC functions and contains diagnostic information if an error has occurred. The CSR is a 16-bit register and has an assigned address – it can be accessed via the Q-bus, or PMI protocol.

There is one CSR per memory module. Each CSR can be assigned to one of 16 predetermined addresses which range from 772100 to 772136 for 18-bit systems and from 17772100 to 17772136 for 22-bit systems (refer to Table 4-2).

ECC is performed only on memory accesses and is not used when accessing the CSR.

#### 4.3.1 Bit Format of CSR

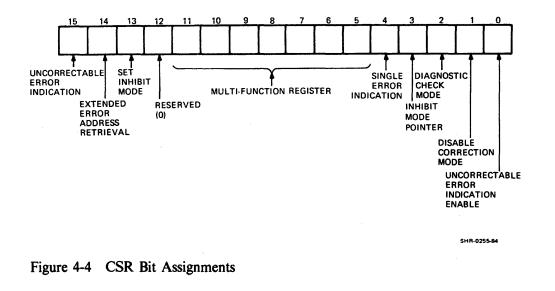

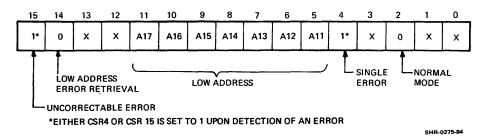

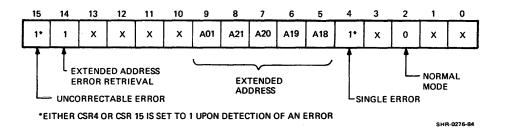

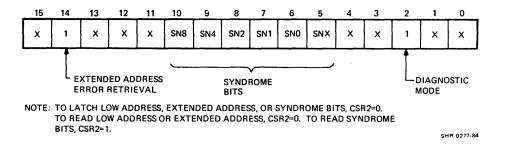

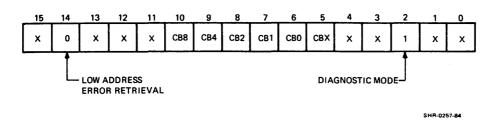

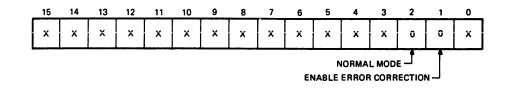

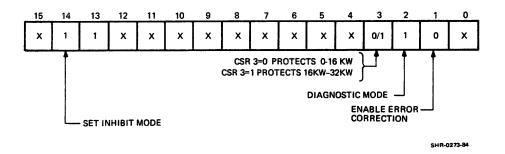

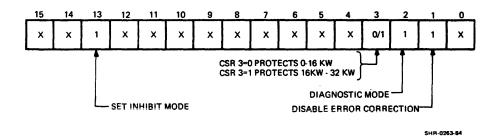

Figure 4-4 shows the bit assignments of the CSR. Unused bits are read as 0.

#### 4.3.2 Bit Descriptions of CSR

Table 4-4 describes each of the CSR bits shown in Figure 4-4.

Table 4-4 CSR Bit Descriptions

| Bit | Name                                                         | Set By<br>Cleared By                                              | Remarks                                                                                                                                                                                                                                                                                                                                         |

|-----|--------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00  | Uncorrectable<br>error<br>indication<br>enable<br>read/write | Set/cleared by<br>software<br>Cleared by power<br>up and BUS INIT | Does not affect CSR. BDAL17 is<br>driven directly by CSR00 at same<br>time as data during a DATI(O)<br>cycle. BDAL16 is not affected by<br>CSR00.                                                                                                                                                                                               |

|     |                                                              |                                                                   | CSR00=0 Inhibit Error Indication<br>Will not allow a system parity<br>(uncorrectable error) trap; i.e.,<br>BDAL17 is not asserted with data<br>on DATI(O) cycles during<br>uncorrectable error detection.<br>CSR04 and CSR15 still indicates<br>errors. BDAL16 is asserted with<br>data on DATI(O) cycle when an<br>uncorrectable error occurs. |

|     |                                                              |                                                                   | CSR00=1 Active Error Indication<br>This bit causes assertion of<br>BDAL17 with data during all<br>DATI(O) cycles.                                                                                                                                                                                                                               |

| Bit | Name                                        | Set By<br>Cleared By                                              | Remarks                                                                                                                                                                                                                                                                                                                                         |

|-----|---------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01  | Disable<br>correction<br>mode<br>read/write | Set/cleared by<br>software<br>Cleared by power<br>up and BUS INIT | Serves as a diagnostic aid to allow<br>reading data from memory without<br>interference from the error<br>correction logic.                                                                                                                                                                                                                     |

|     |                                             |                                                                   | CSR01=0 Enable Error Correction<br>Single error sets CSR04 and latches<br>error address and syndrome bits.<br>Double error sets CSR15 and latches<br>error address and syndrome bits.<br>Once a double error is detected, a<br>single error is flagged through<br>CSR04, but does not cause the address<br>and syndrome bits to be overwritten. |