VT220

**Technical Manual**

### **VT220**

**Technical Manual**

1st Edition, November 1984

Copyright 6 1984 by Digital Equipment Corporation All Rights Reserved Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts  $\emptyset1754$ .

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| d i g i t a I | DECUS     | P/OS         | VAX            |

|---------------|-----------|--------------|----------------|

| DEC           | DECwriter | Professional | VMS            |

| DECmate       | DIGITAL   | Rainbow      | VT             |

| DECnet        | LA        | RSTS         | Work Processor |

| DECSsystem-10 | MASSBUS   | RSX          |                |

| DECSYSTEM-20  | PDP       | UNIBUS       |                |

This equipment has been certified to comply with the limits for a Class B computing device, pursuant to Subpart J of Part 15 of FCC Rules. Only peripherals (computer input/output devices, terminals, printers, etc.) certified to comply with the Class B limits may be attached to this computer. Operation with noncertified peripherals is likely to result in interference to radio and television reception. It has been type tested and found to comply with the limits for a Class B computing device in accordance with the specifications in Subpart J of part 15 of FCC Rules, which are designed to provide reasonable protection against such interference in a residential installation. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the difference by one or more of the following measures:

reorient the receiving antenna relocate the computer with respect to the receiver move the computer away from the receiver plug the computer into a different outlet so that computer and receiver are on different branch circuits.

If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions. The user may find the following booklet prepared by the Federal Communications Commission helpful:

"How to Identify and Resolve Radio-TV Interference Problems".

This booklet is available from the US Government Printing Office, Washington, DC 20402, Stock No. 004-000-00345-4.

### **CONTENTS**

#### INTRODUCTION

| CHAPTER 1                                                                                      | SYSTEM INTRODUCTION |                                                                     |

|------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------|

| 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.3<br>1.4<br>1.5<br>1.6.1<br>1.6.2<br>1.6.3<br>1.6.4 | VT52 Mode           | 1-1<br>1-2<br>1-2<br>1-3<br>1-3<br>1-4<br>1-4<br>1-5<br>1-5         |

| CHAPTER 2 2.1 2.2 2.3 2.3.1 2.3.2 2.3.3 2.3.4 2.3.5 2.3.6 2.3.6.1 2.3.6.2 2.3.7 2.4            |                     | 2-1<br>2-3<br>2-5<br>2-6<br>2-6<br>2-8<br>2-8<br>2-9<br>2-9<br>2-10 |

| CHAPTER 3                                                                                      | SYSTEM OVERVIEW     |                                                                     |

| 3.1<br>3.2<br>3.2.1<br>3.2.2                                                                   | Operating States    | 3-1<br>3-1<br>3-1<br>3-2                                            |

| 3.2.3<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7                                                               | System Architecture  CPU Logic  Video Logic  System Communication Logic  Modem Option (VT22X-AA)  Power Supply  Keyboard  Monitor Components | 3-2<br>3-2<br>3-3<br>3-4<br>3-5<br>3-5<br>3-5<br>3-6<br>3-6                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| CHAPTER 4                                                                                                                                 | CPU LOGIC                                                                                                                                    |                                                                                                       |

| 4.1<br>4.2<br>4.2.1<br>4.2.1.1<br>4.2.1.2<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>4.3<br>4.4 | Attribute RAM                                                                                                                                | 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13<br>4-14<br>4-15<br>4-16 |

| CHAPTER 5                                                                                                                                 | SYSTEM COMMUNICATION LOGIC                                                                                                                   |                                                                                                       |

| 5.1<br>5.2<br>5.2.1<br>5.2.1.1<br>5.2.1.2<br>5.2.1.3<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.3<br>5.4<br>CHAPTER 6                       | EIA Host Interface (I/F)                                                                                                                     |                                                                                                       |

| 6.1<br>6.2<br>6.2.1<br>6.2.1.1                                                                                                            | General                                                                                                                                      | 6-1<br>6-2<br>6-4<br>6-5                                                                              |

| 6.2.1.3                                 | 9007 VPAC Transactions                 | 6-8  |

|-----------------------------------------|----------------------------------------|------|

| 6.2.2                                   | Timing Generator                       | 6-11 |

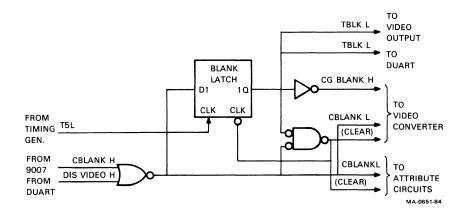

| 6.2.3                                   | Blank Circuits                         | 6-15 |

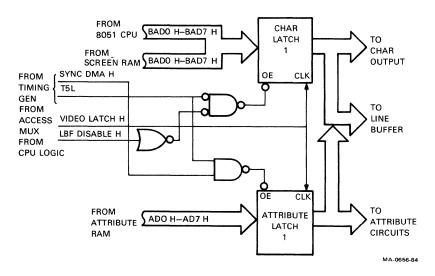

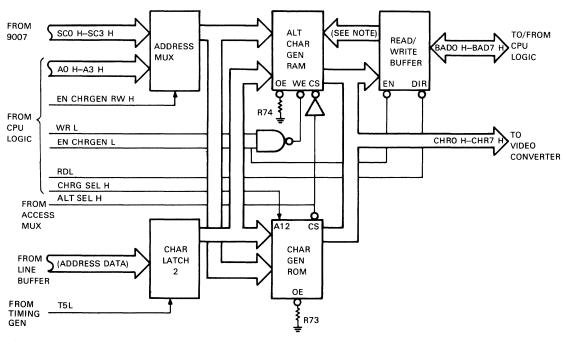

| 6.2.4                                   | Character Generator                    | 6-15 |

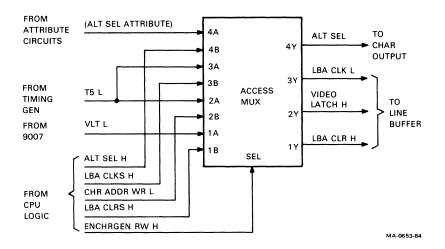

| 6.2.4.1                                 | Access Mux                             | 6-17 |

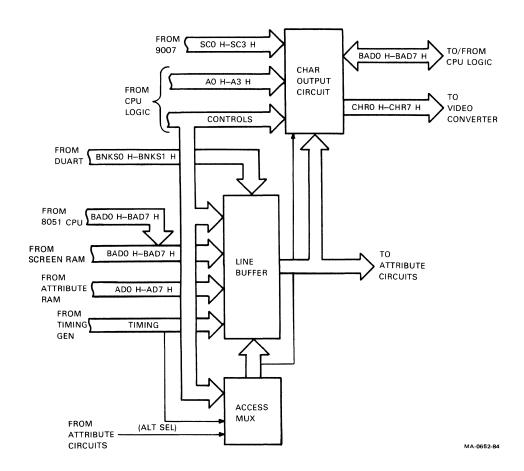

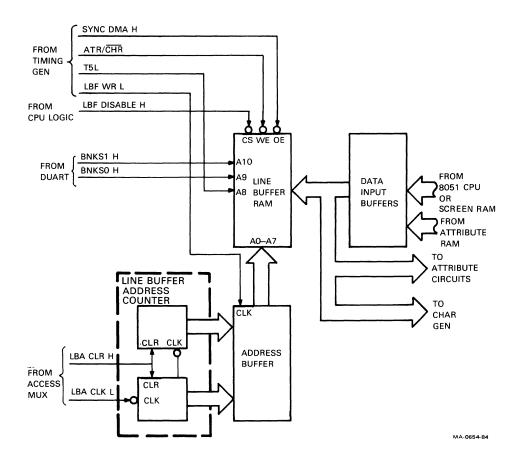

| 6.2.4.2                                 | Line Buffer                            | 6-18 |

| 6.2.4.3                                 | Character Output Circuit               | 6-21 |

| 6.2.5                                   | Attribute Circuits                     | 6-24 |

| 6.2.6                                   | Video Converter                        | 6-26 |

| 6.2.6.1                                 | Conversion Control                     |      |

| 6.2.6.2                                 | Parallel-to-Serial (P/S) Converter     | 6-28 |

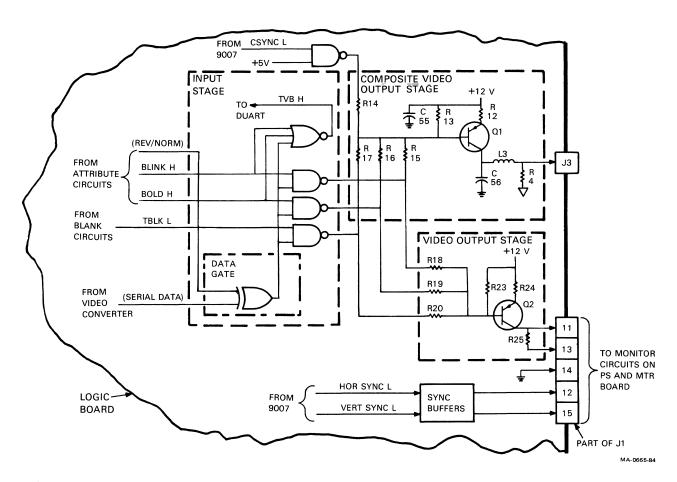

| 6.2.7                                   | Video Output                           | 6-30 |

| 6.3                                     | Signal Descriptions                    |      |

| 6.4                                     | Cahamatia Deference Information        |      |

| 0.4                                     | Schematic Reference Information        | 0-41 |

| CHAPTER 7                               | 7 KEYBOARD (LK201)                     |      |

| 7.1                                     | Introduction                           | 7-1  |

| 7.2                                     | Physical Description                   | 7-2  |

| 7.3                                     | Functional Description                 | 7-4  |

| 7.3.1                                   | Keyboard Operation Overview            | 7-4  |

| 7.3.1.1                                 | Keyboard Scanning                      | 7-5  |

| 7.3.1.2                                 | Control of Audio Transducer and        |      |

| , , , , , , , , , , , , , , , , , , , , | Indicators                             | 7-5  |

| 7.3.2                                   | Keyboard Firmware Functions            | 7-5  |

| 7.3.2.1                                 | Functions Not Changed by CPU           | , ,  |

| 7.5.2.1                                 | Instructions                           | 7-5  |

| 7.3.2.2                                 | Functions Changed by CPU Insructions   | 7-6  |

| 7.3.2.3                                 | Firmware Functions Changed By CPU      | , 0  |

|                                         | Instructions                           | 7-6  |

| 7.4                                     | Detailed Keyboard Circuit Description  | 7-7  |

| 7.4.1                                   | Keyboard Matrix Scanning               | 7-7  |

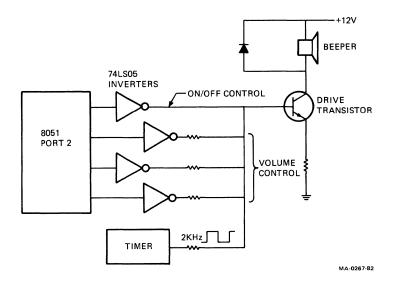

| 7.4.2                                   | Audio Transducer Control Circuit       | 7-14 |

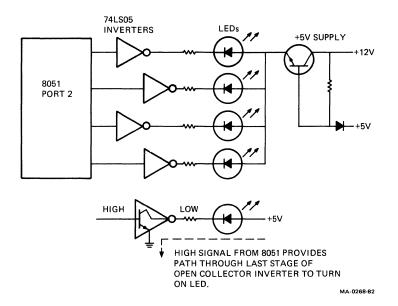

| 7.4.3                                   | Indicator (LED) Control Circuit        | 7-14 |

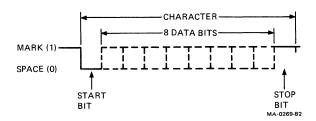

| 7.4.4                                   | Keyboard Communication                 | 7-16 |

| 7.4.4.1                                 | Keyboard Transmit Mode                 | 7-16 |

| 7.4.4.2                                 | Keyboard Receive Mode                  | 7-16 |

| 7.4.5                                   | Reset Signal for 8051 Microprocessor   | 7-17 |

| 7.4.6                                   | Hardware Keyboard Identification (ID)  | 7-17 |

| 7.4.7                                   |                                        | 7-17 |

| 7.5                                     | Voltage Supplies                       |      |

| 7.5.1                                   | Keyboard Programming                   | 7-17 |

|                                         | Keyboard Layout and Key Identification | 7-17 |

| 7.5.2                                   | Modes                                  | 7-23 |

| 7.5.2.1                                 | Special Considerations Regarding       |      |

|                                         | Autorepeat                             | 7-23 |

| 7.5.2.2                                 | Special Considerations Regarding       |      |

|                                         | Down/Up Mode                           | 7-25 |

| 7.5.2.3                                 | Autorepeat Rates                       | 7-25 |

| 7.5.3                                   | Keyboard Peripherals                   | 7-25 |

| 7.5.3.1                                 | Audio                                  | 7-25 |

| 7.5.3.2                                 | Indicators (LEDs)                      | 7-26 |

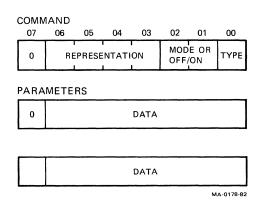

| 7.5.4                                   | Keyboard-to-System Module Protocol     | 7-26 |

| 7.5.4.1                                 | Keycode Transmission                   | 7-26 |

|                                         |                                        |      |

| 7.5.4.2 7.5.4.3 7.5.5 7.5.5.1 7.5.5.2 7.5.5.3 7.5.5.4 7.5.6.1 7.5.6.2 7.5.6.3 7.5.6.4 7.5.6.5 7.5.7 7.5.7               | Parameters Peripheral Commands Mode Set Commands Special Considerations Error Handling Keyboard Locked Condition Reserved Code Test Mode Future Expansion Default Conditions Audio Volume                                                                                                                                                  | 7-26<br>7-28<br>7-29<br>7-30<br>7-30<br>7-35<br>7-37<br>7-37<br>7-37<br>7-38<br>7-38<br>7-38<br>7-38<br>7-38 |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| CHAPTER 8                                                                                                               | MONITOR CIRCUITS                                                                                                                                                                                                                                                                                                                           |                                                                                                              |

| 8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.2.2.1<br>8.2.2.2<br>8.2.2.3<br>8.2.3<br>8.2.4<br>8.2.4.1<br>8.2.4.2<br>8.2.5<br>8.2.5 | General Major Circuits and Components  Video Amplifier (Amp) Circuit Horizontal Deflection Circuit Horizontal Processor Circuit Horizontal Driver Circuit Horizontal Output Circuit Flyback Transformer Circuit Vertical Deflection Circuit Vertical Processor Circuit Vertical Output Circuit Dynamic Focus Brightness Control CRT Device | 8-16                                                                                                         |

| CHAPTER 9                                                                                                               | POWER SUPPLY                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

| 9.1<br>9.2<br>9.2.1<br>9.2.2<br>9.2.2.1<br>9.2.2.2<br>9.2.2.3<br>9.2.2.4<br>9.2.2.5<br>9.2.3                            | General Major Circuits and Components  AC Input Components  AC Conversion Circuits  +12 V Start Up Circuit  Input Rectification Circuit  DC Output Circuits  Overcurrent Protect Circuit  Pulse Width Modulator Circuit  DC OK Circuit  DC Input Components                                                                                | 9-1<br>9-2<br>9-3<br>9-4<br>9-6<br>9-7<br>9-8<br>9-11<br>9-12<br>9-13                                        |

| APPENDICE                                                                                                               | s                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |

| A<br>B<br>C                                                                                                             | SPECIFICATIONS                                                                                                                                                                                                                                                                                                                             | A-1<br>B-1<br>C-1                                                                                            |

#### FIGURES

| 1-1          | VT220 Series Terminals                                                                    | 1-1          |

|--------------|-------------------------------------------------------------------------------------------|--------------|

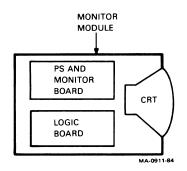

| 1-2          | Monitor Assembly Major Components                                                         | 1-2          |

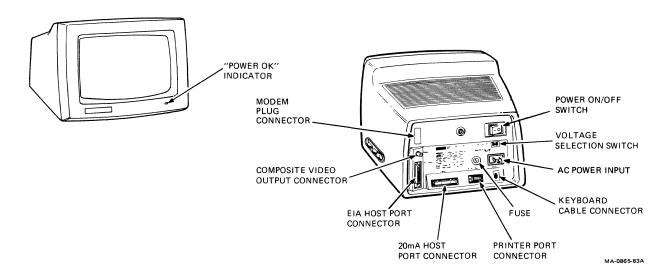

| 2-1          | Monitor Assembly Controls, Indicators,                                                    |              |

|              | and Connectors                                                                            | 2-1          |

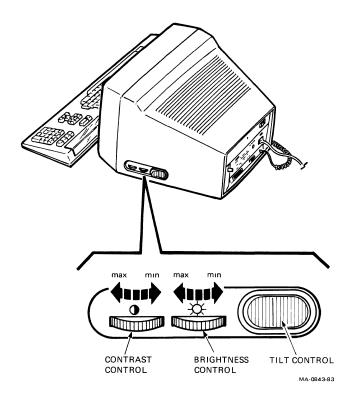

| 2-2          | Display Controls and Tilt Leg Release Button                                              | 2-2          |

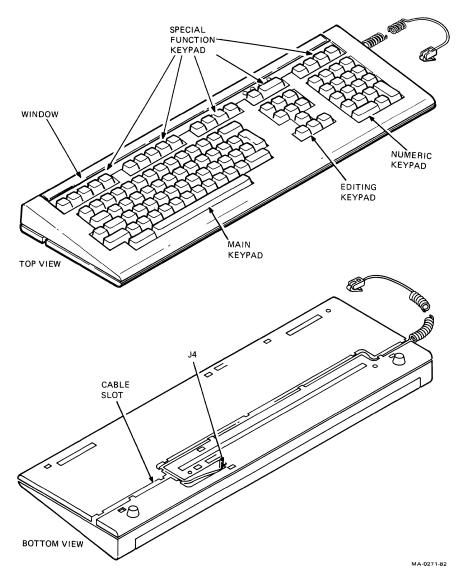

| 2-3          | LK201 Keyboard Module                                                                     | 2-4          |

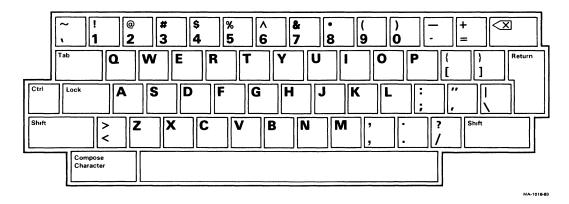

| 2-4          | Main Keypad                                                                               | 2-5          |

| 2-5          | Editing Keypad                                                                            | 2-6          |

| 2-6          | Auxiliary Keypad                                                                          | 2-6          |

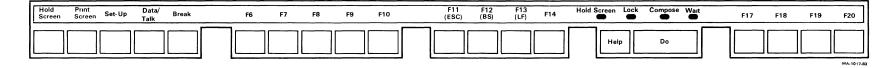

| 2-7          | Top-Row Function Keys                                                                     | 2-7          |

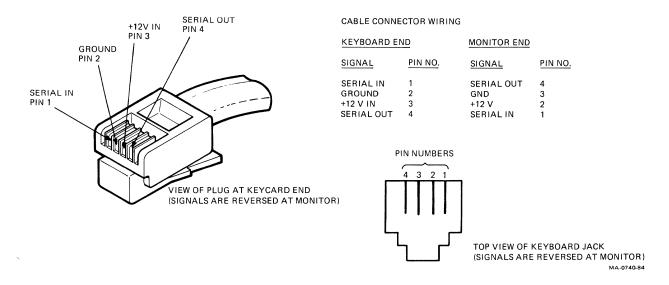

| 2-8          | BCC01 Cable Connector (Keyboard End)                                                      | 2-9          |

| 2-9          | Modem Module Controls, Indicators, and                                                    |              |

|              | Connectors                                                                                | 2-10         |

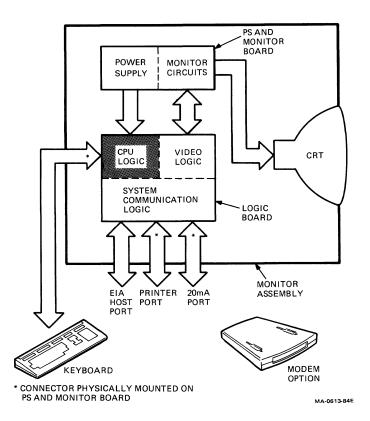

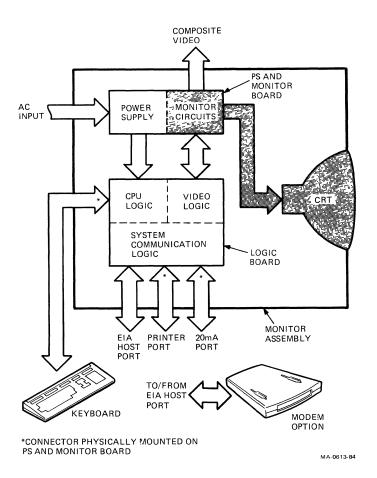

| 3-1          | VT220 Series Terminal Functional Block Diagram                                            | 3-3          |

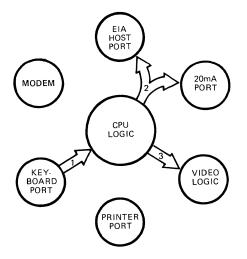

| 3-2          | System Interaction in Set-Up                                                              | 3-6          |

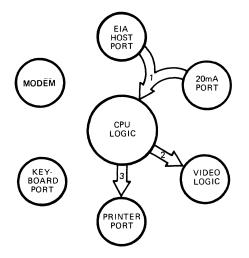

| 3-3          | System Interaction in Local                                                               | 3-7          |

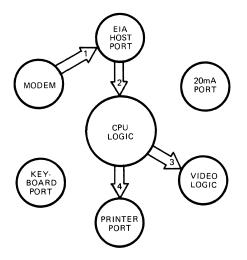

| 3-4          | System Interaction On-Line: Data to Host                                                  |              |

|              | (Null-Modem)                                                                              | 3-7          |

| 3-5          | System Interaction On-Line: Data from Host                                                | 3-8          |

| 3-6          | System Interaction On-Line: Data to Host (Modem)                                          | 3-8          |

| 3-7          | System Interaction On-Line: Data from Host                                                |              |

|              | (Modem)                                                                                   | 3-9          |

| 4-1          | VT220 Series Terminal Functional Block Diagram                                            | 4-1          |

| 4-2          | CPU Logic Block Diagram                                                                   | 4-2          |

| 4-3          | CPU Block Diagram                                                                         | 4-3          |

| 4 – 4        | 8051 CPU Internal Block Diagram                                                           | 4-4          |

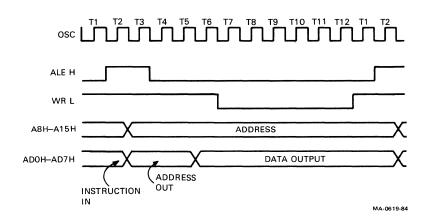

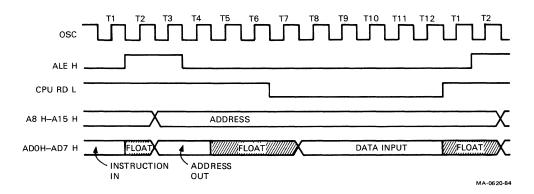

| 4-5          | 8051 CPU Instruction Fetch Timing Diagram                                                 | 4-6          |

| 4-6          | 8051 CPU Read Transaction Timing Diagram                                                  | 4-6          |

| 4-7          | 8051 CPU Write Transaction Timing Diagram                                                 | 4-6          |

| 4-8          | 8051 CPU Address Map: ROM                                                                 | 4-7          |

| 4-9          | 8051 CPU Address Map: Non-ROM                                                             | 4-7          |

| 4-10         | Address Latch Block Diagram                                                               | 4-8          |

| 4-11<br>4-12 | ROM Block Diagram                                                                         | 4-8          |

|              | Data Buffer Block Diagram                                                                 | 4-9          |

| 4-13         | Screen RAM Block Diagram                                                                  | 4-10         |

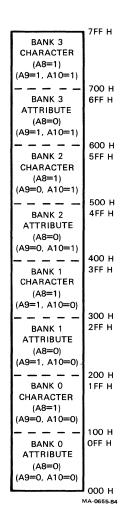

| 4-14         | Attribute RAM Block Diagram                                                               | 4-11         |

| 4-15<br>4-16 | Select Decoder Block Diagram                                                              | 4-12         |

|              | Keyboard I/F Block Diagram                                                                | 4-14<br>4-15 |

| 4-17<br>4-18 | NVR Block Diagram                                                                         | 4-16         |

| 5-1          |                                                                                           | 5-1          |

| 5-1<br>5-2   | VT220 Series Terminal Functional Block Diagram  System Communications Logic Block Diagram | 5-3          |

| 5-3          | DUART Block Diagram                                                                       | 5-4          |

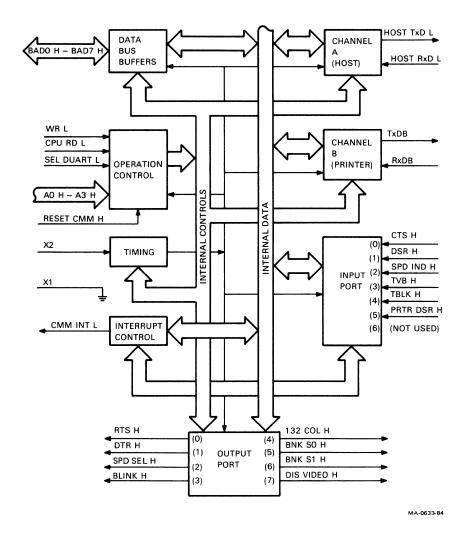

| 5-4          | 2681 DUART Internal Circuits Block Diagram                                                | 5-5          |

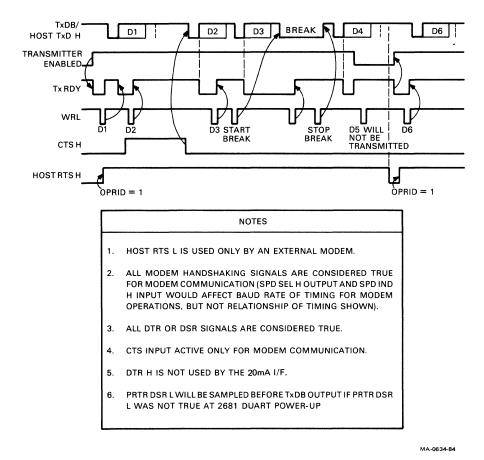

| 5 <b>-</b> 4 | 2681 DUART: Transmit Data Timing Diagram                                                  | 5-8          |

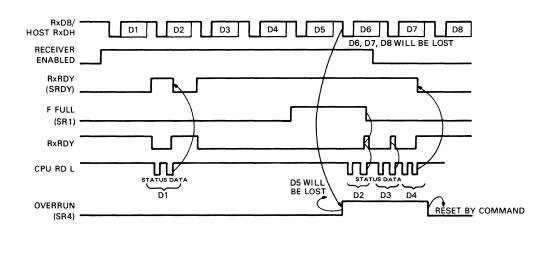

| 5 <b>-</b> 6 | 2681 DUART: Receive Data Timing Diagram                                                   | 5-9          |

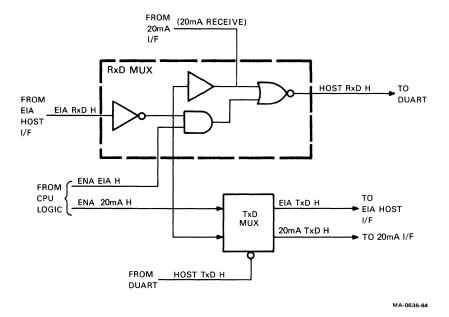

| 5 <b>-</b> 7 | Host Data Mux Block Diagram                                                               | 5-9          |

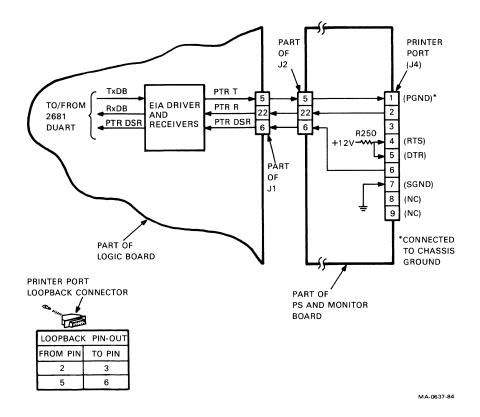

| 5 <b>-</b> 7 | Printer I/F Block Diagram                                                                 | 5-10         |

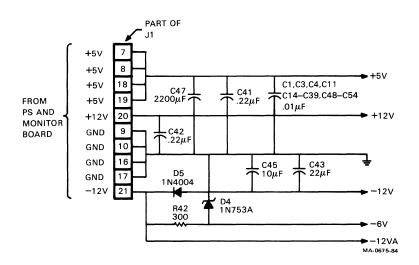

| 5 <b>-</b> 9 | Logic Board (J1)/PS and Monitor Board (J2)                                                | J 1 K        |

| J-J          | Interconnection Diagram                                                                   | 5-11         |

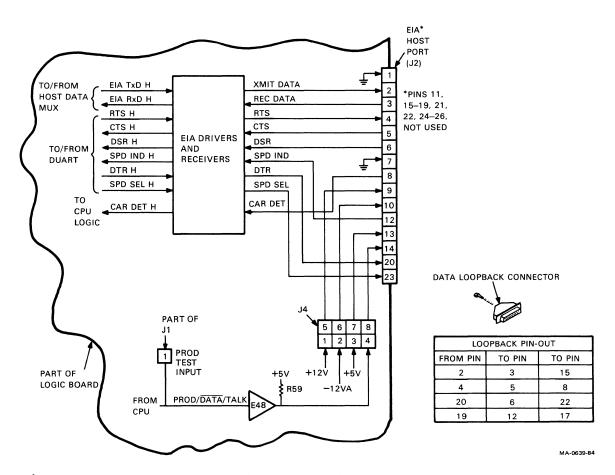

| 5-10         | FIA Host I/F Block Diagram                                                                | 5-11         |

|              |                                                                                           |              |

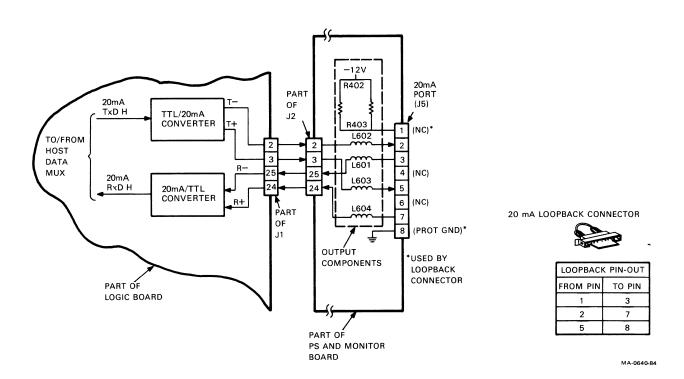

| 5-11          | 20 mA I/F Block Diagram                        | 5-13 |

|---------------|------------------------------------------------|------|

| 6-1           | VT220 Series Terminal Functional Block Diagram | 6-1  |

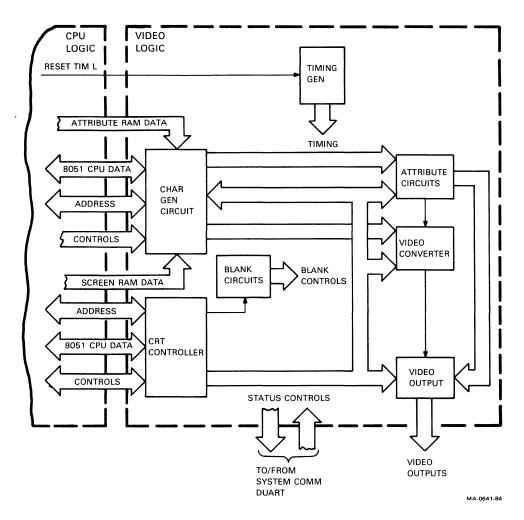

| 6-2           | Video Logic Block Diagram                      | 6-3  |

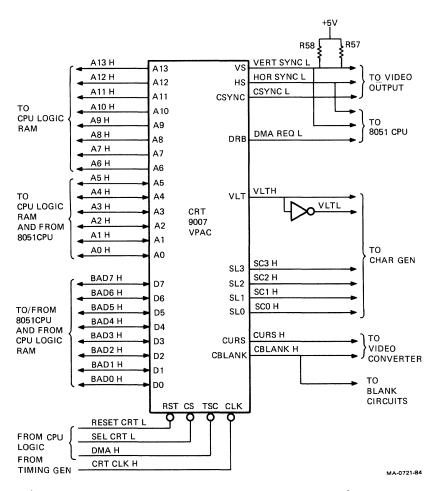

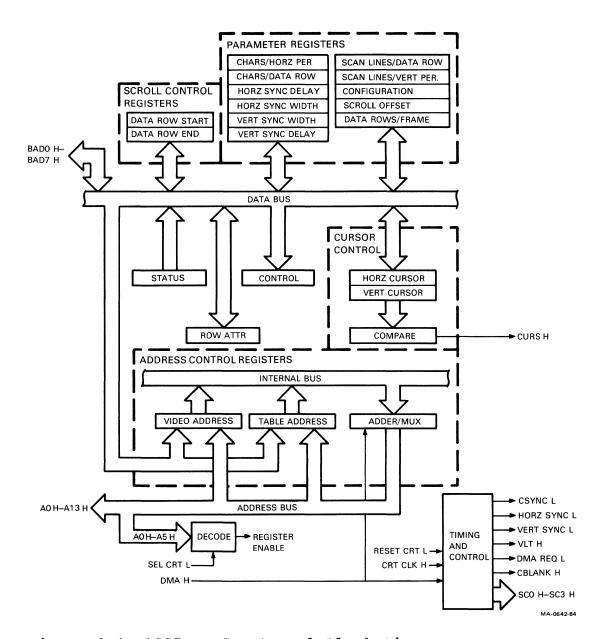

| 6-3           | CRT Controller Block Diagram                   | 6-4  |

| 6-4           | 9007 VPAC Internal Block Diagram               | 6-5  |

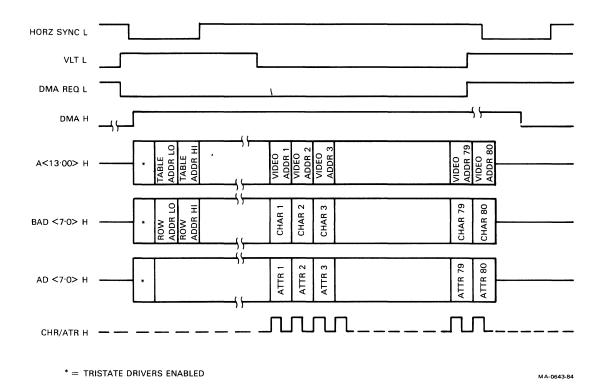

| 6-5           | 9007 VPAC: DMA Transaction Diagram             | 6-9  |

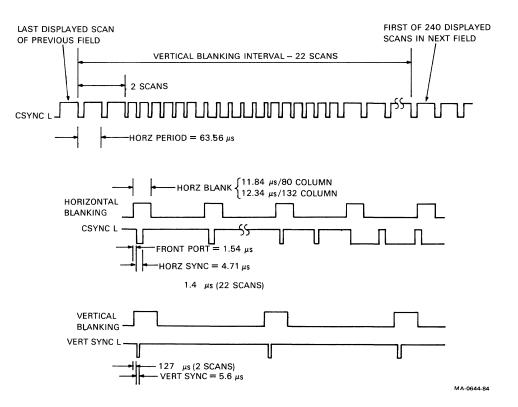

| 6-6           | 9007 VPAC: Composite Sync and Blanking Timing  |      |

|               | Diagram                                        | 6-9  |

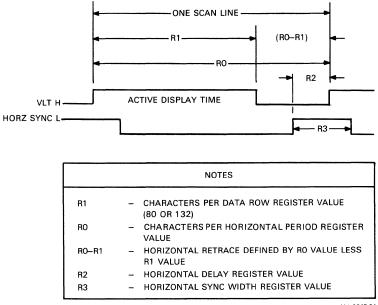

| 6-7           | 9007 VPAC: Horizontal Timing                   | 6-10 |

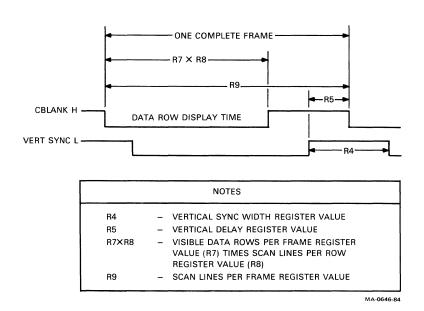

| 6-8           | 9007 VPAC: Vertical Timing                     | 6-10 |

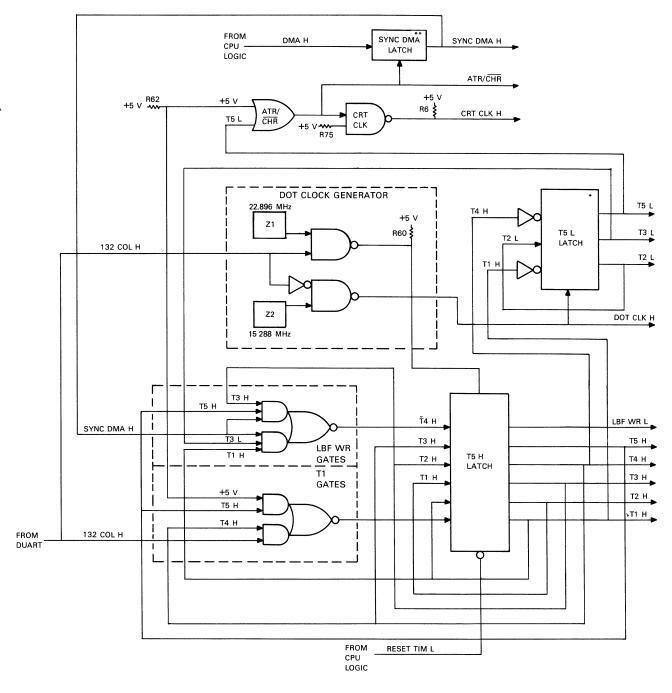

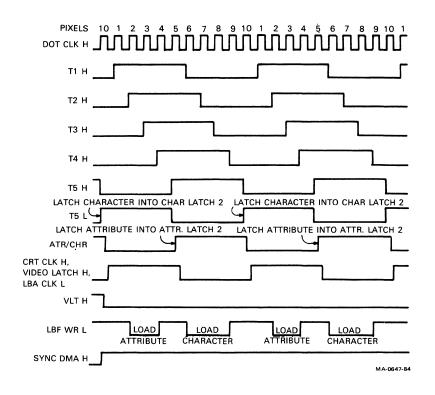

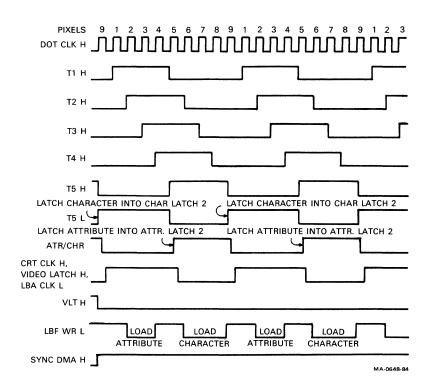

| 6-9           |                                                | 6-12 |

| 6 <b>-</b> 10 |                                                | 6-13 |

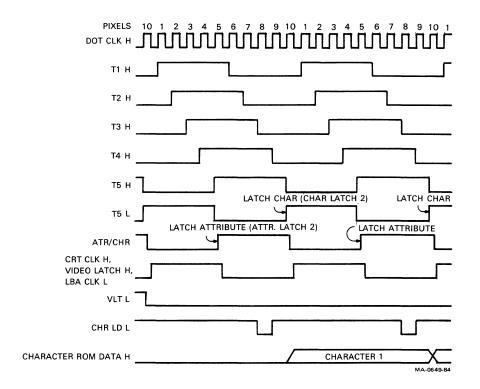

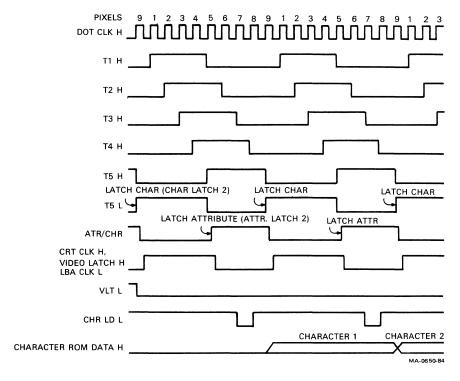

| 6-11          |                                                | 6-15 |

| 6-12          |                                                | 6-16 |

| 6-13          | Access Mux Block Diagram                       | 6-17 |

| 6-14          |                                                | 6-18 |

| 6-15          |                                                | 6-20 |

| 6-16          | Data Input Buffers Block Diagram               |      |

| 6-17          | <u> </u>                                       | 6-21 |

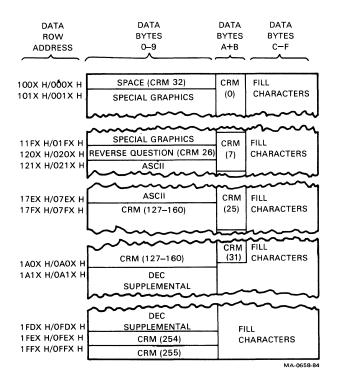

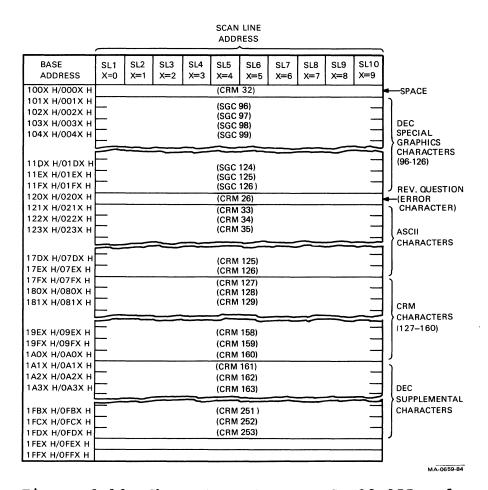

| 6-18          | Character ROM Map: Overview                    | 6-22 |

| 6-19          | Character ROM Map: CRM32-255 and               |      |

|               |                                                | 6-23 |

| 6-20          | Character ROM Map: CRMØ-31                     |      |

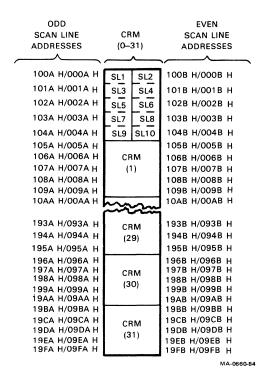

| 6-21          | Attribute Circuits Block Diagram               |      |

| 6-22          | <b>,</b>                                       | 6-27 |

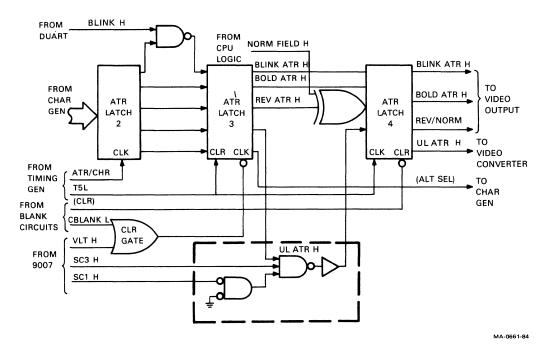

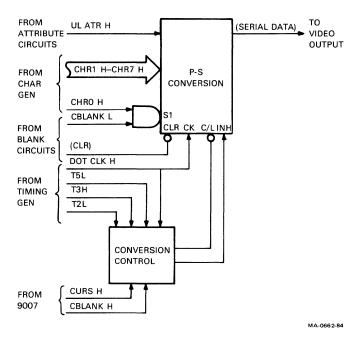

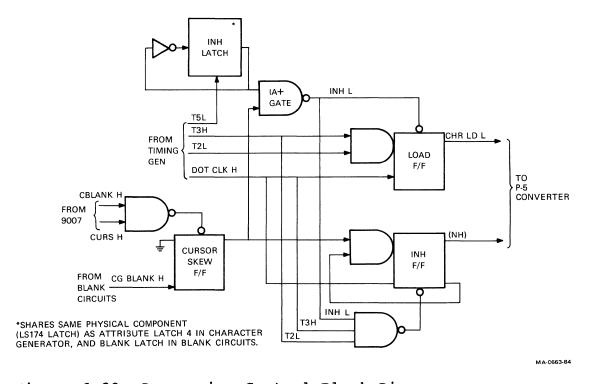

| 6-23          | Conversion Control Block Diagram               | 6-27 |

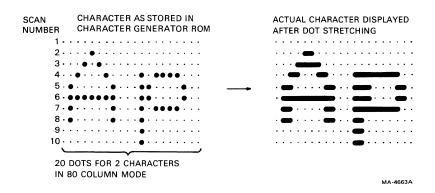

| 6-24          | Dot Matrix Display and Dot Stretching          | 6-28 |

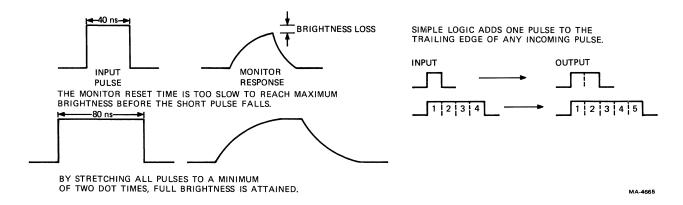

| 6-25          | Effects of Dot Stretching                      | 6-28 |

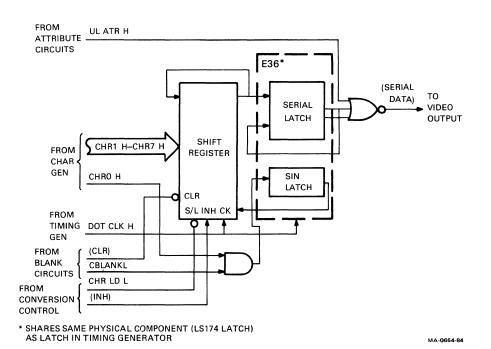

| 6-26          | P-S Conversion Block Diagram                   | 6-29 |

| 6-27          | Video Output Block Diagram                     | 6-30 |

| 7-1           | VT220 Series Terminal Functional Block Diagram | 7-1  |

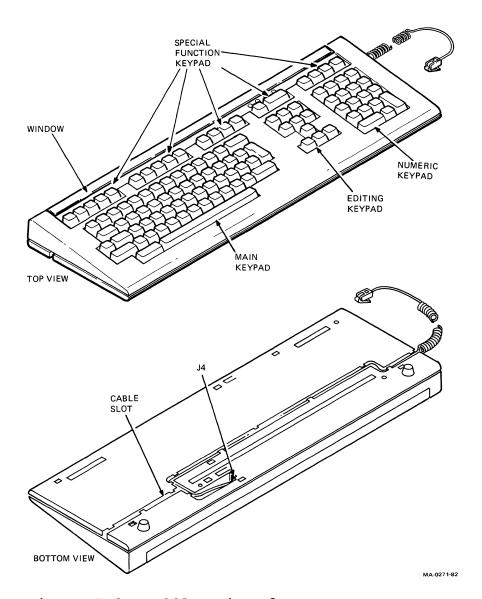

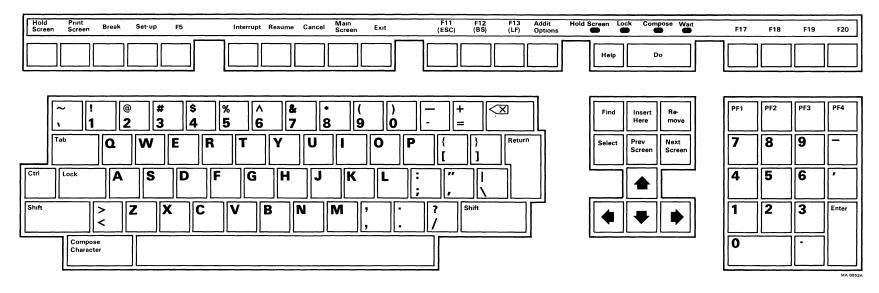

| 7-2           | LK201 Keyboard                                 | 7-2  |

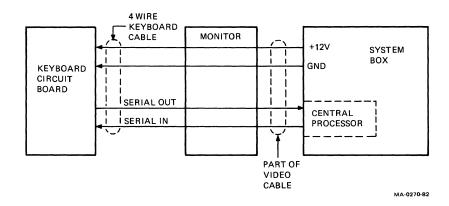

| 7-3           | Keyboard Cable Connections                     | 7-3  |

| 7-4           | LK201 Keyboard Block Diagram                   | 7-4  |

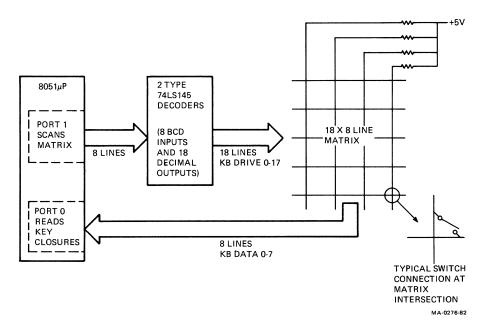

| 7-5           | Matrix Scanning Block Diagram                  | 7-7  |

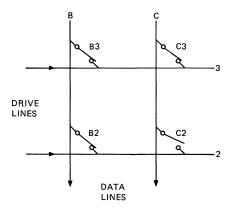

| 7-6           | Example of Ghost Key Generation                | 7-8  |

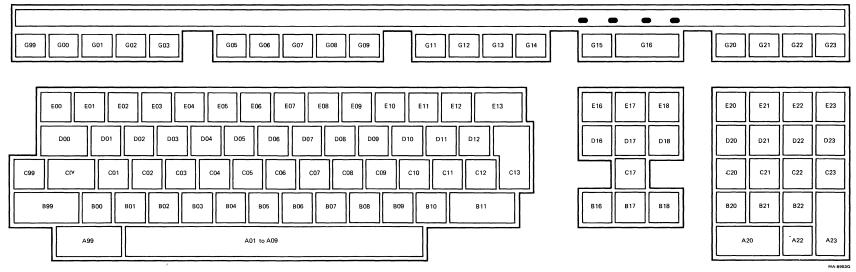

| 7-7A          | LK201-AA Keyboard Layout                       | 7-12 |

| 7-7B          | LK201-AA Keyboard Layout                       | 7-13 |

| 7-8           | Beeper Control Circuit                         | 7-15 |

| 7-9           | Indicator (LED) Control Circuit                | 7-15 |

| 7-10          | Keyboard Transmit and Receive Character Format | 7-16 |

| 7-11          | System Module to Keyboard Protocol             | 7-29 |

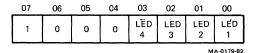

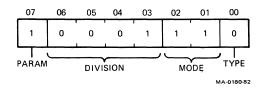

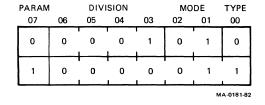

| 7-12          | Indicator (LED) Parameter                      | 7-33 |

| 7-13          | Indicator (LED) Layout                         | 7-33 |

| 7-14          | Audio Volume Parameter                         | 7-33 |

| 7-15          | Set Main Array to Down/Up Example              | 7-35 |

| 7-16          | Set Main Array to Autorepeat Example           | 7-35 |

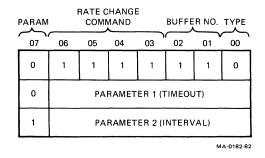

| 7-17          | Change Rates in Buffer 3 Example               | 7-36 |

| 8-1           | VT220 Series Terminal Functional Block Diagram | 8-1  |

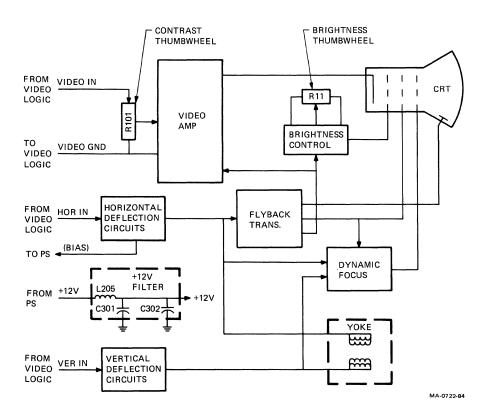

| 8-2           | Monitor Circuits Block Diagram                 | 8-2  |

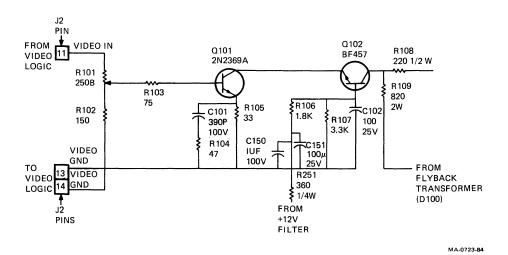

| 8-3           | Video Amplifier Circuit Diagram                | 8-3  |

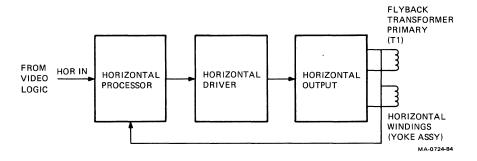

| 8-4           | Horizontal Deflection Circuit Block Diagram    | 8-5  |

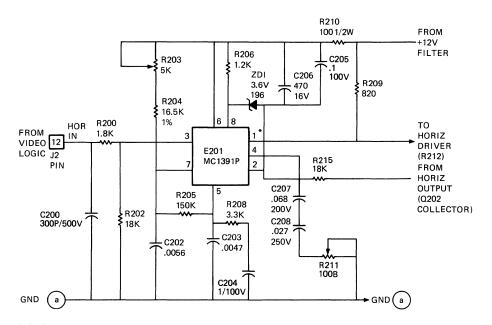

| 8-5           | Horizontal Processor Circuit Diagram           | 8-5  |

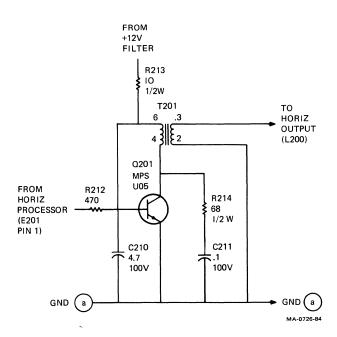

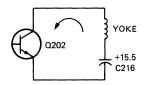

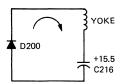

| 8-6  | Horizontal Driver Circuit Diagram              | 8-6  |

|------|------------------------------------------------|------|

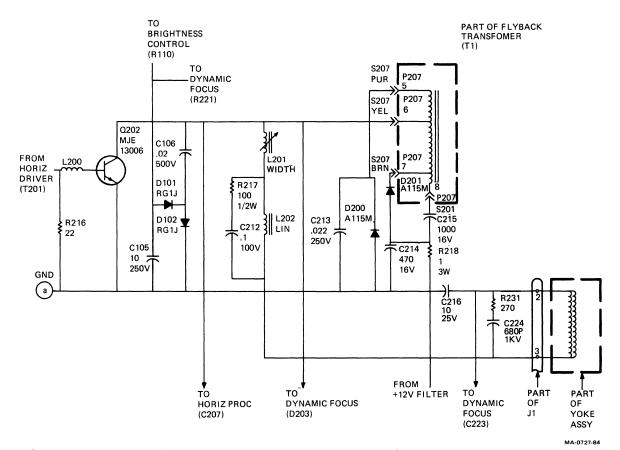

| 8-7  | Horizontal Output Circuit Diagram              | 8-7  |

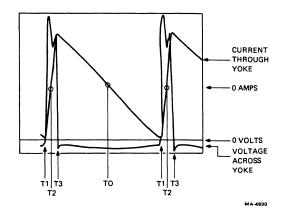

| 8-8  | Horizontal Deflection Waveform                 | 8-8  |

| 8-9  | Horizontal Trace: Scan from Center to Right    |      |

|      | Side of Screen (TØ Time)                       | 8-9  |

| 8-10 | Horizontal Retrace: Move to Center from        |      |

|      | Right Side (Tl Time)                           | 8-9  |

| 8-11 | Horizontal Retrace: Move to Left Side from     |      |

|      | Center (T2 Time)                               | 8-10 |

| 8-12 | Horizontal Trace: Scan to Center from Left     |      |

|      | Side of Screen (T3 Time)                       | 8-10 |

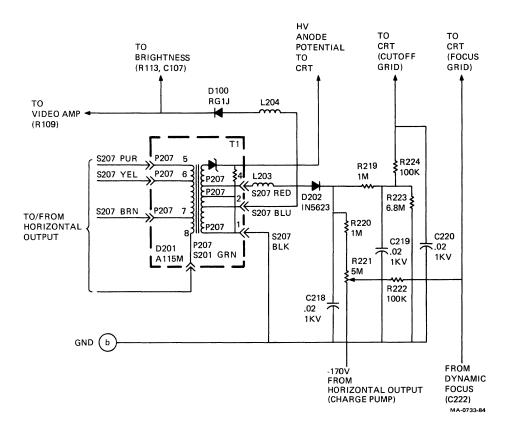

| 8-13 | Flyback Transformer Circuit Diagram            |      |

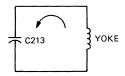

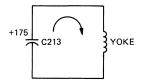

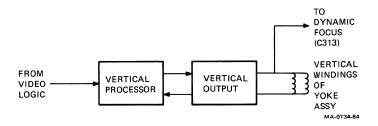

| 8-14 | Vertical Deflection Circuit Block Diagram      | 8-13 |

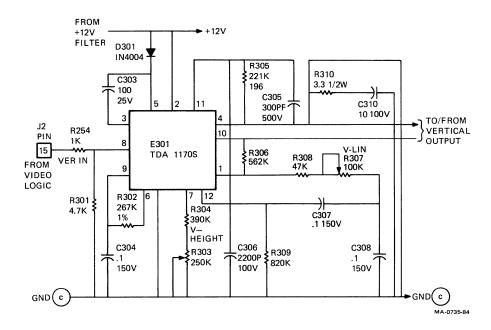

| 8-15 | Vertical Processor Circuit Diagram             |      |

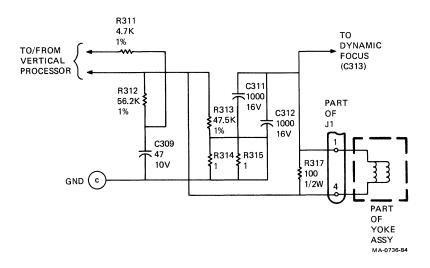

| 8-16 | Vertical Output Circuit Diagram                | 8-14 |

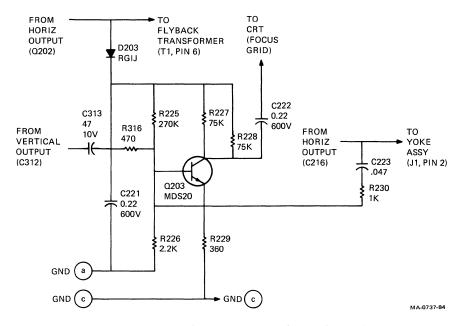

| 8-17 | Dynamic Focus Circuit Diagram                  | 8-15 |

| 8-18 | Brightness Control Circuit Diagram             | 8-16 |

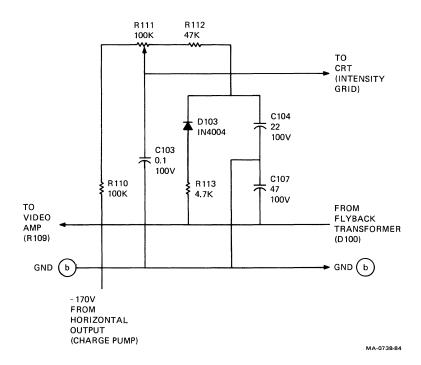

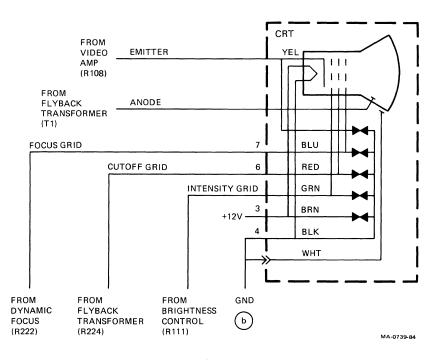

| 8-19 | CRT Device                                     | 8-17 |

| 9-1  | VT220 Series Terminal Functional Block Diagram | 9-1  |

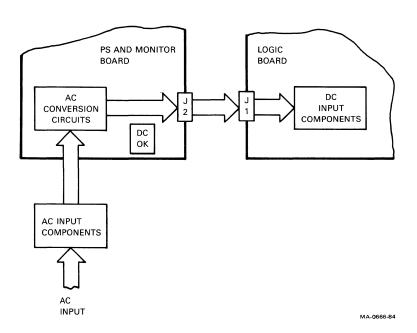

| 9-2  | Power Supply Block Diagram                     | 9-2  |

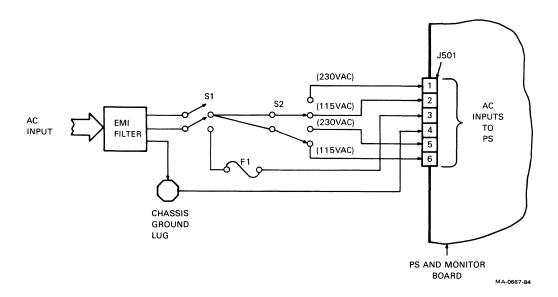

| 9-3  | AC Input Components Block Diagram              | 9-3  |

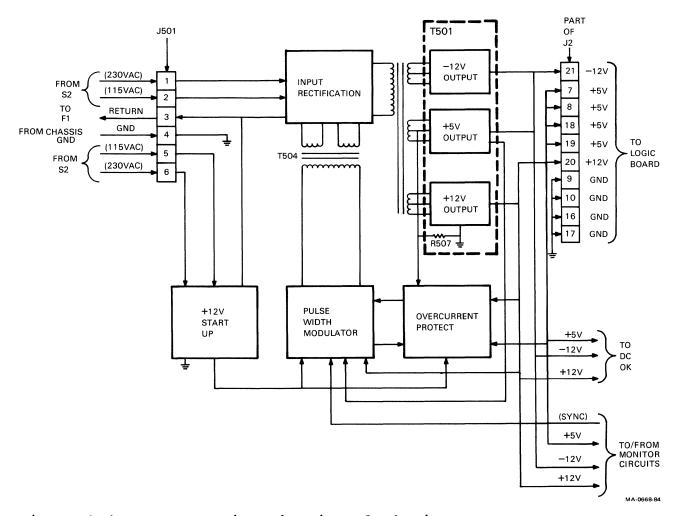

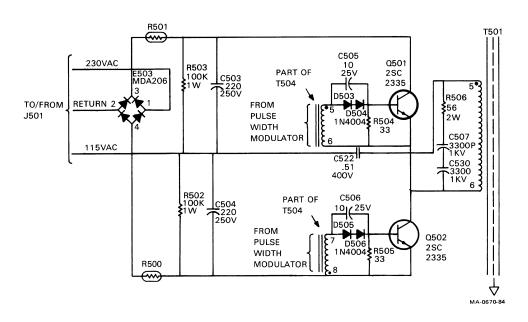

| 9-4  | AC Conversion Circuits Block Diagram           | 9-4  |

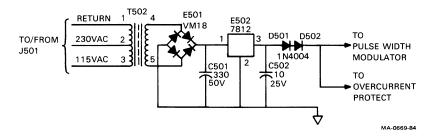

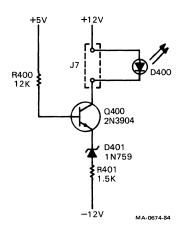

| 9-5  | +12 V Start Up Circuit Diagram                 | 9-7  |

| 9-6  | Input Rectification Circuit Diagram            | 9-7  |

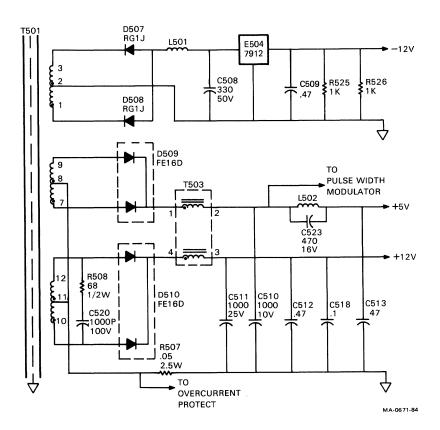

| 9-7  | DC Output Circuits Diagram                     | 9-8  |

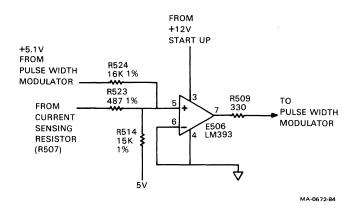

| 9-8  | Overcurrent Protect Circuit Diagram            | 9-11 |

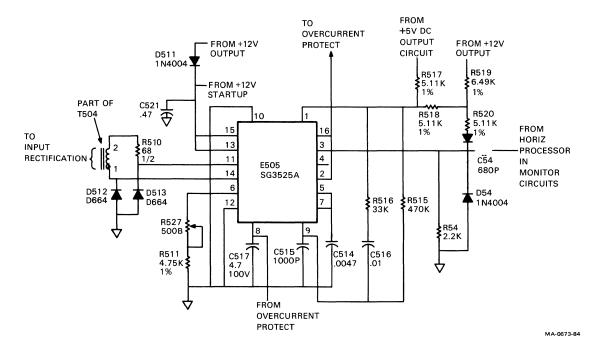

| 9-9  | Pulse Width Modulator Circuit Diagram          | 9-12 |

| 9-10 | DC OK Circuit Diagram                          | 9-13 |

| 9-11 | DC Input Circuits Diagram                      | 9-14 |

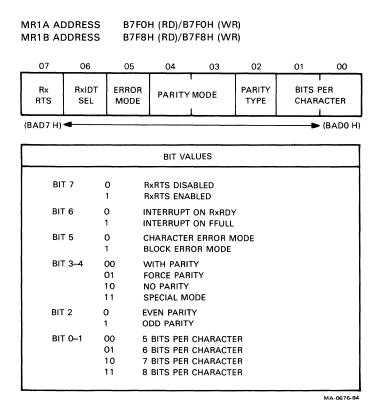

| C-1  | 2681 DUART: Mode Register 1 (MR1)              |      |

|      | (Channel A and B)                              | C-1  |

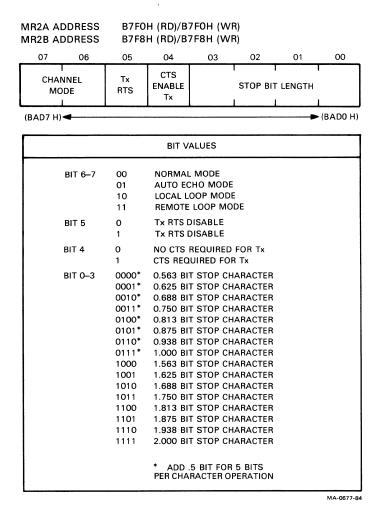

| C-2  | 2681 DUART: Mode Register 2 (MR2)              |      |

|      | (Channel A and B)                              | C-2  |

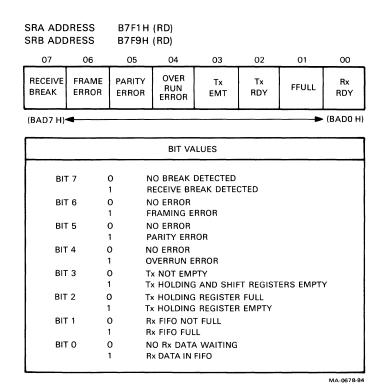

| C-3  | 2681 DUART: Status Register (SR)               |      |

|      | (Channel A and B)                              | C-3  |

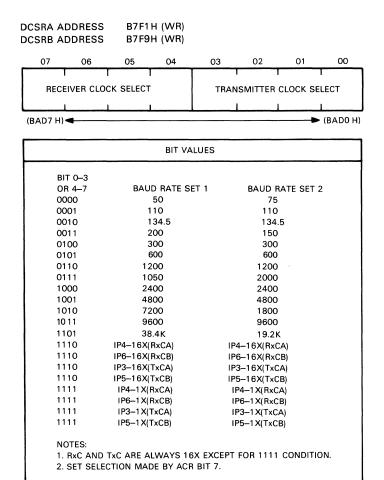

| C-4  | 2681 DUART: Data Clock Selection Register      |      |

|      | (DCSR) (Channel A and B)                       | C-4  |

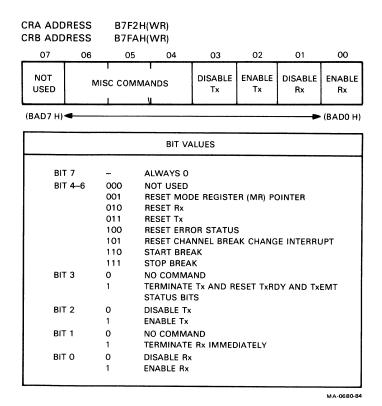

| C-5  | 2681 DUART: Command Register (CR)              |      |

|      | (Channel A and B)                              | C-5  |

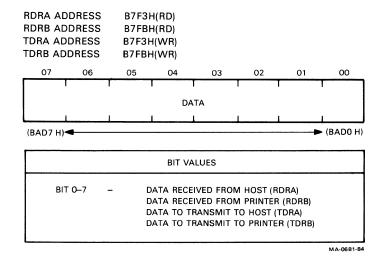

| C-6  | 2681 DUART: Receive/Transmit Data Registers    |      |

|      | (RDR/TDR) (Channel A and B)                    | C-5  |

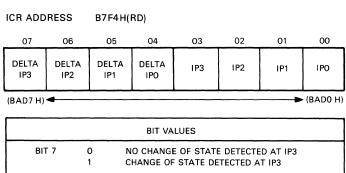

| C-7  | 2681 DUART: Input Change Register (ICR)        | C-6  |

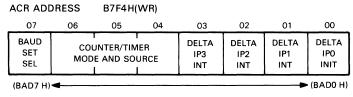

| C-8  | 2681 DUART: Auxiliary Control Register (ACR)   | C-7  |

| C-9  | 2681 DUART: Interrupt Status Register (ISR)    | C-8  |

| C-10 | 2681 DUART: Interrupt Mask Register (IMR)      | C-8  |

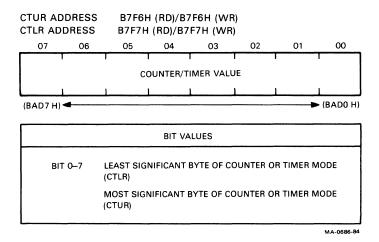

| C-11 | 2681 DUART: Counter Timer/Upper (CTUR)         |      |

|      | and Lower (CTLR) Registers                     | C-9  |

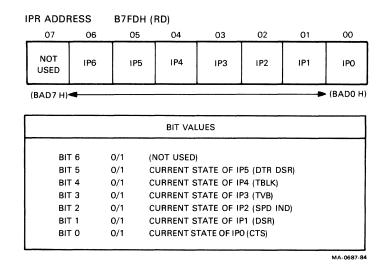

| C-12 | 2681 DUART: Input Port Register (IPR)          | C-9  |

| C-13 | 2681 DUART: Output Port Configuration Register |      |

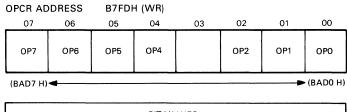

|      | (OPCR)                                         | C-10 |

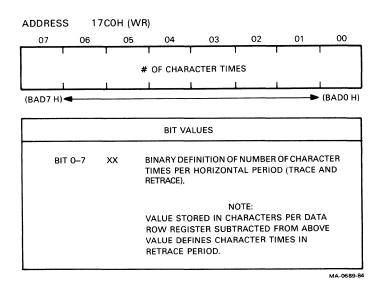

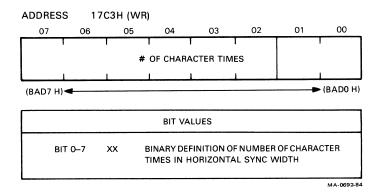

| C-14 | 9007 VPAC: Characters Per Horizontal           |      |

|      | Period Register                                |      |

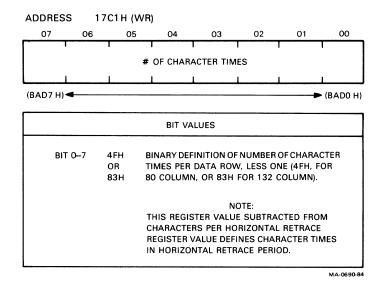

| C-15 | 9007 VPAC: Characters Per Data Row Register    | C-11 |

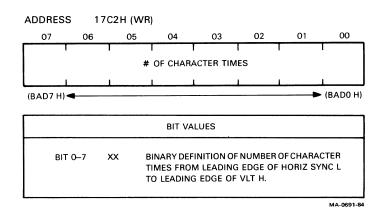

| C-16   | 900/ VPAC: Horizontal Sync Delay Register       |        |

|--------|-------------------------------------------------|--------|

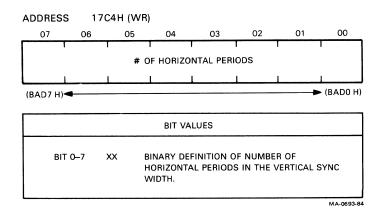

| C-17   | 9007 VPAC: Horizontal Sync Width Register       |        |

| C-18   | 9007 VPAC: Vertical Sync Width Register         |        |

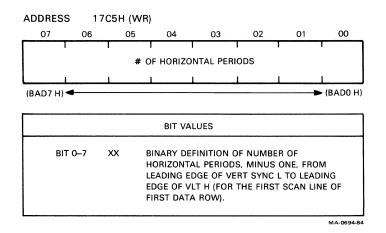

| C-19   | 9007 VPAC: Vertical Sync Delay Register         | C-12   |

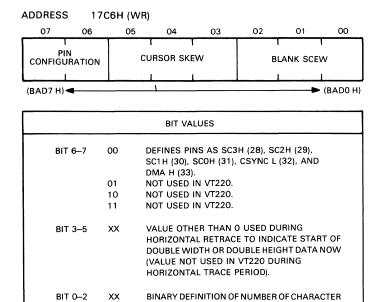

| C-20   | 9007 VPAC: Configuration/Skew Register          | C-13   |

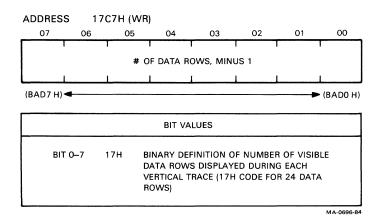

| C-21   | 9007 VPAC: Data Rows Per Frame Register         | C-13   |

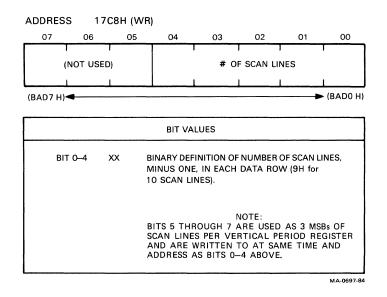

| C-22   | 9007 VPAC: Scan Lines Per Data Row Register     | C - 14 |

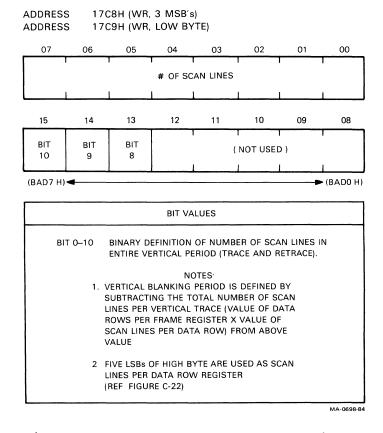

| C-23   | 9007 VPAC: Scan Lines Per Vertical Period       |        |

|        | Register                                        | C - 14 |

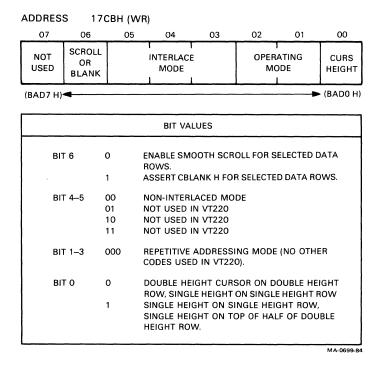

| C-24   | 9007 VPAC: Control Register                     |        |

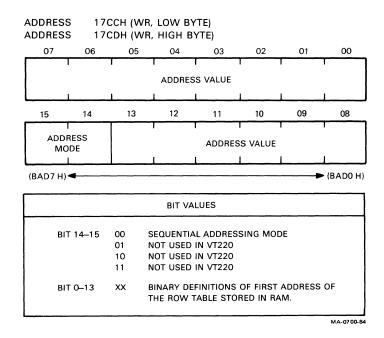

| C-25   | 9007 VPAC: Table Address Register               | C-15   |

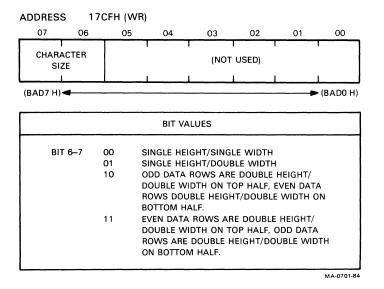

| C-26   | 9007 VPAC: Row Attribute Register               | C-16   |

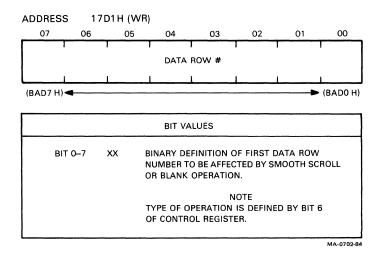

| C-27   | 9007 VPAC: Data Row Start Register              | C-16   |

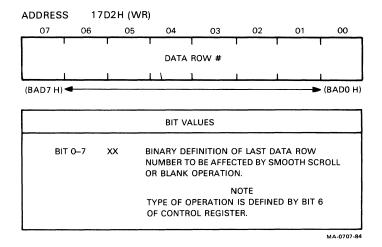

| C-28   | 9007 VPAC: Data Row End Register                |        |

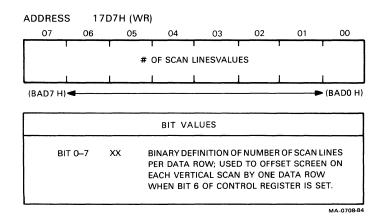

| C-29   | 9007 VPAC: Smooth Scroll Offset Register        | C-17   |

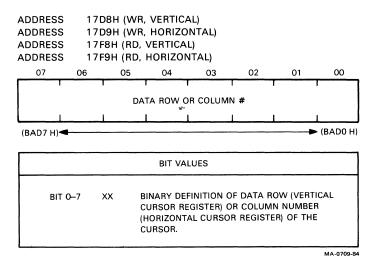

| C-3Ø   | 9007 VPAC: Vertical/Horizontal Cursor Registers |        |

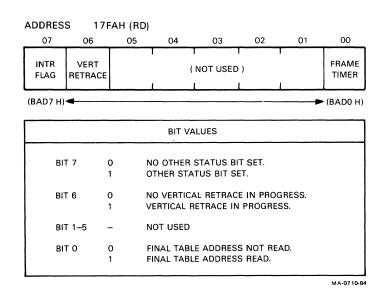

| C-31   | 9007 VPAC: Status Register                      | C-18   |

| TABLES |                                                 |        |

| 4-1    | 8051 CPU Addresses (Non-ROM)                    | 4-13   |

| 4-2    | CPU Logic Signal Descriptions                   |        |

| 4-3    | CPU Logic Schematic References                  | 4-22   |

| 5-1    | 2681 DUART Addresses                            | 5-7    |

| 5-2    | System Communication Logic Signal Descriptions  | 5-14   |

| 5-3    | System Communication Logic Schematic References | 5-20   |

| 6-1    | 9007 VPAC Internal Addresses                    | 6-7    |

| 6-2    | Video Logic Signal Descriptions                 | 6-32   |

| 6-3    | Video Logic Schematic References                | 6-42   |

| 7-1    | Keyboard Matrix                                 | 7-9    |

| 7-2    | Keyboard Functional Divisions                   | 7-18   |

| 7-3    | Keycode Translation Table                       | 7-19   |

| 7-4    | Peripheral Commands in Hexadecimal              | 7-32   |

| 7-5    |                                                 | 7-39   |

| 7-6    |                                                 | 7-39   |

| 9-1    | Input Voltage Specifications                    | 9-5    |

| 9-2    | Output Voltage Specifications                   | 9-9    |

#### INTRODUCTION

#### GENERAL

This manual provides information to aid field service engineers and other personnel trained by Digital Equipment Corporation in the isolation of VT220 Series terminal malfunctions. To this end, this manual identifies the major circuits within the VT220 Series terminal and provides functional descriptions of those circuits.

Where appropriate, only summarized discussions of operating and programming information is presented; and only to the extent necessary to understand how a specific hardware component or circuit functions.

#### MANUAL ORGANIZATION

The first three chapters of this manual provide an introduction to the VT220 Series terminal.

Chapter 1 provides a brief introduction to the VT220 Series terminal.

Chapter 2 provides brief descriptions of all VT220 Series terminal controls, indicators, and connectors.

Chapter 3 provides an overview of the VT220 Series terminal system interactions.

Chapters 4 -- 9 provide a functional breakdown and description of the major logic circuits that comprise the VT220 Series terminal.

Chapter 4 explains the CPU logic, responsible for overall control of VT220 Series terminal operation.

Chapter 5 explains the system communication logic, responsible for communication with host and auxiliary devices.

Chapter 6 explains the video logic, responsible for developing output to monitor circuits.

Chapter 7 explains the LK201 keyboard module, responsible for operator input.

Chapter 8 explains the monitor circuits and the cathode ray tube (CRT), responsible for visual output to the operator.

Chapter 9 explains the power supply, responsible for converting ac input to dc potentials needed for terminal operation.

The final part of this manual is made up of appendices which provide specification, differences information, and programming reference data.

Appendix A describes specifications for the VT220 Series terminal.

Appendix B describes differences between the VT220 Series terminal and the VT102 terminal.

Appendix C provides summary of bit values for register devices.

#### RELATED DOCUMENTATION

The following is a list of related documents for the VT220 Series terminal.

#### VT220 Series Documentation

Pocket Service Guide - EK-VT220-PS

Programmer Reference Manual - EK-VT220-RM

Programmer Pocket Guide - EK-VT220-HR

Owner's Manual - EK-VT220-UG

Installation Guide - EK-VT220-IN

Video Terminal IPB - EK-VT220-IP

Modem User's Guide - EK-VT22M-UG

#### Maintenance Print Sets

VT220 (terminal assembly) - MP-01732-01 LK201 (keyboard module) - MP-01395-00 VT22X-AA (modem module) - 70-21205-01

## CHAPTER 1 SYSTEM INTRODUCTION

#### 1.1 GENERAL

The VT220 Series terminal is a 1/4-page (up to 24 displayable lines of text) conversational terminal that uses ANSI standard functions to create, store, and edit text.

#### 1.2 PHYSICAL DESCRIPTION

The VT220 terminal (Figure 1-1) consists of up to three units: a monochrome monitor/terminal module, a keyboard, and an optional modem module.

NOTE

Specifications for the VT220 Series terminal are provided in Appendix A.

Figure 1-1 VT220 Series Terminals

Figure 1-2 Monitor Assembly Major Components

#### 1.2.1 Monitor Assembly (VT220)

The monitor assembly is the center of the terminal. Figure 1-2 shows the major monitor assembly components.

- Logic board -- contains the components needed to control terminal operation.

- Power supply (PS) and monitor board -- contain the components used to convert ac input to the dc voltages required by the terminal, as well as circuits used to drive the cathode ray tube (CRT).

- Cathode Ray Tube (CRT) -- provides visual output to terminal operator.

- Communication ports -- provide for cable connection between the monitor assembly and a local host (EIA or 20 mA connection), remote host (via a modem), keyboard, and printer.

#### 1.2.2 Keyboard (LK201)

The VT220 terminal uses the LK201 keyboard with the following features.

- Four LEDs -- provide visual indication of operational conditions.

- Typewriter-Style keypad -- contains 57 keys for text entry.

- Auxiliary keypad -- contains 18 keys, including 4 keys which have their function assigned by application programming.

- Editing keypad -- contains 6 screen function keys, and 4 cursor movement keys.

- Top-Row function keys -- are 20 keys aligned across the top of the keyboard which are provided for various functions.

A description of controls and indicators (Chapter 2) explains in greater detail how the LK201 keyboard functions when used with the VT220 terminal.

#### 1.2.3 Modem Module Option (VT22X-AA)

The optional modem provides telephone line communication with a remote host. The module mounts beneath the monitor assembly, raising the actual height of the monitor by about 1 1/2 inches.

#### 1.3 DISPLAY CHARACTERISTICS AND CAPABILITIES

The VT220 terminal's display capabilities are upward compatible with the text capabilities of the VT102 terminal.

The terminal has four text modes. Three modes execute standard ANSI functions (VT100 mode, VT200 mode with 7-bit controls, and VT200 mode with 8-bit controls), and one mode executes Digital private functions (VT52 mode). The following major text capabilities are available within these various modes.

- 24 rows of text with either 80 or 132 characters per row (characters are formed within a 7 X 9 dot matrix in a 10 X 10 cell for 80 characters per row, and within a 7 X 9 dot matrix in a 9 X 10 cell for 132 characters per row)

- Hard character set of 288 characters, with set made up of 256 characters in Digital's control representation mode (CRM) set, 31 characters from Digital's special graphics set, and one character, the reverse question mark, used as an error character

- Down-Line loadable character set

- Reverse video

- Underline

- Double height/width characters, on a line-to-line basis

- Bold/normal intensity

- Character blinking

- ANSI compatible control functions

#### 1.4 COMMUNICATION ENVIRONMENT

The major communications features of the terminal include the following.

- Asynchronous communications at up to 19.2K bits per second

- EIA RS232C host port

- 20 mA host port for passive only 20 mA loop communications

- 9-pin EIA RS232C printer port

- 7- or 8-bit character formats

- BNC connector for composite video output to an optional slave monitor

NOTE

The composite video output is an RS170-like output; however, the use of dc coupling is not in strict agreement with RS170 specifications.

#### 1.5 MAJOR OPERATING STATES

The VT220 Series terminal has three major operating states.

- Set-Up

- On-Line

- Local

The operating states are described in greater detail in the system overview (Chapter 3).

#### 1.6 OPERATING MODES

The VT220 Series terminal has four major operating modes which can be selected either from the keyboard (while in set-up), or by the host (via control codes).

- VT100 mode

- VT200 mode, 7-bit controls

- VT200 mode, 8-bit controls

- VT52 mode

#### 1.6.1 VT100 Mode

The VT100 mode executes standard ANSI functions and emulates the text mode functionality of Digital's VT102 terminal. (VT102/VT220 differences are described in Appendix B).

The VT100 mode provides some backward compatibility with existing software written for the VT102 terminal (when in VT100 mode, the VT220 responds as a service level, class 2 terminal, and VT100 programs which do not recognize this class of terminal functionality will not execute on the VT220). This mode restricts use of the keyboard to those keys which have a direct functional counterpart at the VT102's keyboard. All data is restricted to 7-bit format, and only ASCII, UK, or special graphics characters are generated.

#### 1.6.2 VT200 Mode, 7-Bit Controls

This mode supports Digital Multinational Characters or National Replacement Character sets, depending on the character set mode selected. Both character groups can be accessed via the keyboard or from the host computer via control codes. This operating mode also provides some backward compatibility for existing VT100 software.

#### 1.6.3 VT200 Mode, 8-Bit Controls

This mode supports Digital Multinational Characters or National Replacement Character sets, depending upon the character set mode selected. As in the VT200 mode, 7-bit controls, both character groups can be accessed via the keyboard or programmed control codes.

#### 1.6.4 VT52 Mode

The VT52 mode is a text mode that executes Digital private functions, but not ANSI. This mode has a degree of compatibility with a VT102 operating in that terminal's VT52 mode.

The VT52 mode restricts use of the keyboard to those keys which have a direct functional counterpart at the VT102's keyboard when the VT102 is in VT52 mode. All data is restricted to 7-bit format, and only ASCII, UK, or special graphics characters are generated.

# CHAPTER 2 CONTROLS, INDICATORS, AND CONNECTORS

#### 2.1 GENERAL

This chapter provides information about the terminal's controls, indicators, and connectors, including those for the VT22X-AA modem option. It also includes information on the various keypads and special function keys of the LK201 keyboard.

#### 2.2 MONITOR ASSEMBLY (VT220)

The monitor assembly controls, indicators, and connectors (Figures 2-1 and 2-2) are as follows.

Power controls, indicators, and connectors

- Power on/off switch -- turns the terminal on or off.

- "Power OK" indicator -- lights to indicate power is applied to the terminal and all dc voltages are present.

Figure 2-1 Monitor Assembly Controls, Indicators, and Connectors

Figure 2-2 Display Controls and Tilt Leg Release Button

- AC power input -- connects the power cord to the monitor assembly.

- Fuse -- protects the monitor assembly from electrical damage.

- Voltage selection switch -- matches the input voltage selected to the voltage supplied by the ac source.

#### CAUTION

An incorrect setting of the voltage select switch can damage the monitor assembly.

#### Communication connectors

- EIA host port connector -- connects the terminal to a local host computer, or an external modem for remote host communication.

- 20 mA host port connector -- connects the terminal to a local host computer via a passive only 20 mA loop.

- Composite video output connector -- provides a complete composite video output signal for an additional slave monitor; (composite video output is an RS170-like output using dc coupling not in strict agreement with RS170 specifications).

- 9-pin printer port connector -- connects a printer to the terminal.

- Keyboard cable connector -- connects the keyboard to the monitor assembly.

- Modem plug connector -- connects shorting plug portion of modem connection cable to monitor assembly.

#### CRT display controls

- Contrast control -- adjusts the degree of contrast on the screen.

- Brightness control -- adjusts the degree of brightness on the screen.

- Tilt control -- releases a tilt leg that drops to provide a -5 to +15 degree tilt range for adjusting the angle of the monitor.

#### 2.3 KEYBOARD (LK201)

The LK201 keyboard (Figure 2-3) consists of the following components.

- Main keypad

- Editing keypad

- Auxiliary keypad

- Top-Row function keys

- Visual indicators

- Audible indicators

- Connector cable

Figure 2-3 LK201 Keyboard Module

Figure 2-4 Main Keypad

#### 2.3.1 Main Keypad

The main keypad (Figure 2-4) operates like a standard typewriter keyboard. These special function keys are located on the main keypad.

- TAB key -- generates a horizontal tab, normally moving the cursor to the next tab stop.

- CTRL (Control) key -- when pressed with another key, generates a control code to tell the system to perform a predefined function (such as CTRL -- <X, which generates a CANCEL control character).

- LOCK key -- function determined by set-up feature so that when pressed, it can serve as either a SHIFT LOCK (all keys to generate their shifted value), or a CAPS LOCK (alphabetic keys generate uppercase characters), until LOCK key is pressed again.

- SHIFT key -- when pressed with another key, generates either the key's shifted value (for alphanumeric and two-symbol keys), or, in the case of some function keys, generates a predefined control function.

- RETURN key -- generates a CR (or a CR and LF, as selected in General Set-Up), or, in some cases, moves the cursor to the next line when editing text. In other cases, it is a signal to the system that a particular operation is finished.

- <X (Delete) key -- generates a DEL character, normally moving cursor one character to the left and erasing character at the new cursor position.

- COMPOSE CHARACTER key -- generates characters that do not exist as standard keys.

Figure 2-5 Editing Keypad

Figure 2-6 Auxiliary Keypad

#### 2.3.2 Editing Keypad

The editing keypad (Figure 2-5) is normally used to control the cursor, and edit data already entered. In a typical editing operation, the four arrow keys move the cursor in the direction indicated by the arrow. The six editing keys can have functions corresponding to their legends, or can be defined for special functions, depending on the application program in effect.

#### 2.3.3 Auxiliary Keypad

The auxiliary keypad (Figure 2-6) is used primarily to enter numeric data. However, some of this keypad's keys (PF1, PF2, PF3, and PF4) can have functions assigned to them by the application software in use. The ENTER key causes a CR (or a CR and LF, as selected in General Set-Up), and is also used while in set-up mode to activate selected features.

#### 2.3.4 Top-Row Function Keys

Most of the top-row function keys (Figure 2-7), have functions assigned to them by the application software in use. The following top-row function keys have predetermined values.

- HOLD SCREEN key -- freezes the display and stops new characters from being displayed until pressing HOLD SCREEN again returns the terminal to normal operation.

- PRINT SCREEN key -- sends the text on the screen to the printer (CTRL-PRINT SCREEN sets or resets auto print mode).

- SET-UP key -- causes terminal to enter or exit set-up.

Figure 2-7 Top-Row Function Keys

- DATA/TALK key -- controls use of a switched telephone line when the optional modem is installed.

- BREAK key -- transmits a BREAK control character to the host if BREAK generation is enabled in set-up (SHIFT-BREAK initiates a disconnect, while CTRL-BREAK sends the answerback message to the host).

- F11 (ESC) -- generates an ESC character in either VT100 or VT52 modes (function is determined by application programs in either of the VT200 modes).

- F12 (BS) -- generates a BS character in either VT100 or VT52 modes (function is determined by application programs in either of the VT200 modes).

- F13 (LF) -- generates a LF character in either VT100 or VT52 modes (function is determined by application programs in either of the VT200 modes).

#### 2.3.5 Visual Indicators

The keyboard has four visual indicators to show the present status or operation in progress.

- HOLD SCREEN indicator -- on when display is frozen (refer to HOLD SCREEN key description in section 2.3.4)

- LOCK indicator -- on when keyboard's LOCK key is depressed (see LOCK key description in para. 2.3.1)

- COMPOSE indicator -- on to indicate a compose sequence is in progress

- WAIT indicator -- on when keyboard is prevented from transmitting information (in effect, locked out of the system)

#### 2.3.6 Audible Indicators

The keyboard generates two sounds, both of which can be enabled or disabled in set-up.

- Keyclick

- Bell

2.3.6.1 Audible Keyclick -- sounds each time a key is pressed, with the following exceptions.

- When the SHIFT or CTRL keys are depressed, because these keys do not generate characters, but only modify characters generated by other keys

- When the WAIT indicator is on (characters from the keyboard will be lost)

- When the keyclick is disabled in set-up

- When an inactive key is pressed

- 2.3.6.2 Bell -- sounds in each of the following cases.

- During the power-up self-test

- When the terminal receives a BEL character from the host

- When a composing error is made

- When the margin is approached (unless bell is disabled in set-up)

#### 2.3.7 Connector Cable

The keyboard module connects to the system via a BCC01 cable. Figure 2-8 shows the connector for the BCC01 cable.

Figure 2-8 BCC01 Cable Connector (Keyboard End)

#### 2.4 MODEM OPTION (VT22X-AA)

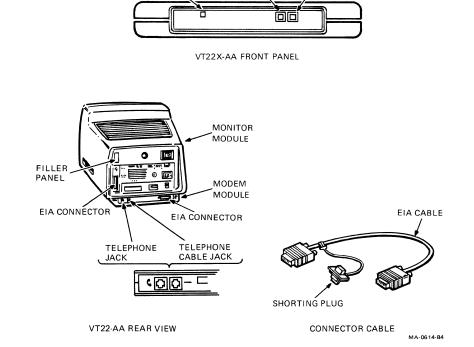

The VT22X-AA modem controls, indicators, and connectors (Figure 2-9) are as follows.

Front panel controls and indicators

- Test LED -- when lit, provides visual indication of either on-going analog or remote loop test condition.

- Analog loop test button -- puts modem into test of local loop when depressed.

- Remote loop test button -- puts modem into test of remote loop when depressed.

ANALOG LOOP

TEST BUTTON

TEST LED

REMOTE LOOP

TEST BUTTON

Figure 2-9 Modem Module Controls, Indicators, and Connectors

#### Rear panel connectors

- Connector cable -- consists of shorting plug (which connects to receptacle covered by filler panel) and EIA cable (which routes host communication between the EIA connectors on the monitor and the modem).

- Filler panel -- is a removable panel covering monitor assembly receptacle for shorting plug of modem connector cable.

- EIA connector -- is a 25-pin connector on both monitor assembly and modem with host communications routed between the two EIA connectors by the connector cable.

- Telephone jack -- connects telephone device to the modem.

- Telephone cable jack -- connects telecommunications line to the modem.

## CHAPTER 3 SYSTEM OVERVIEW

#### 3.1 GENERAL

This chapter provides an overview of system interactions during each of the possible operating states of the VT220 Series terminal.

#### 3.2 OPERATING STATES

The terminal functions in any one of three operating states.

- Set-Up

- Local

- On-Line

#### 3.2.1 Set-Up

Set-Up is selectable from the keyboard (SET-UP key) for performing the following functions.

- Examining or changing terminal operating characteristics (such as transmit and receive speeds)

- Transferring from on-line to local, or from local to on-line

While in set-up, the terminal is functionally disconnected from the host. Only the keyboard is enabled as an input device, and only the monitor is enabled for output. Any data received from the host is buffered until the terminal is placed in an on-line operating state.

#### 3.2.2 Local

Local is selectable while in set-up. This operating state disables terminal-to-host communications. Any data received from the host while in local is buffered until the terminal is placed on-line.

While in local, the keyboard serves as an input device, with displayable data input from this device sent to the screen. In addition, information can be output from the terminal (either screen or keyboard data), to the printer (via printer port).

#### 3.2.3 On-Line

On-line is selectable while in set-up. This operating state lets the terminal communicate with a host. This communications link-up can take the following two forms.

- Null modem -- communication is through a direct line link with the host, either through the EIA host port, or the 20 mA port

- External modem -- communication with a remote host, via EIA host port connection with the modem option

When the terminal is on-line, data entered at the keyboard is transmitted to the host. A local-echo feature (selectable in set-up) routes keyboard data to the monitor, as well as to the host.

Both the monitor and the printer can receive information from the host, but not both at the same time. However, data received for the monitor can be subsequently transferred to the printer.

The printer port can be placed in controller mode while on-line (via set-up feature). When the printer port is selected for controller mode, the terminal is essentially a buffer for host to printer communications. In such a case, no output is made to the monitor, and no keyboard input is transferred to the host.

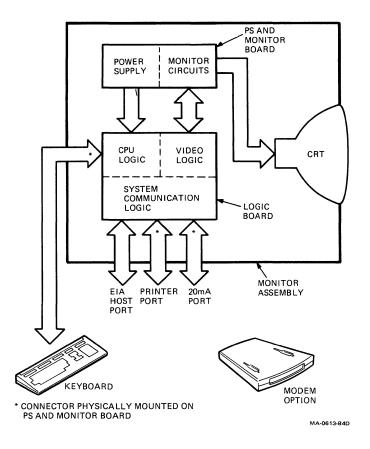

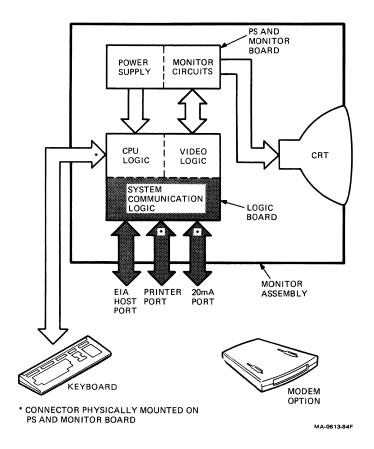

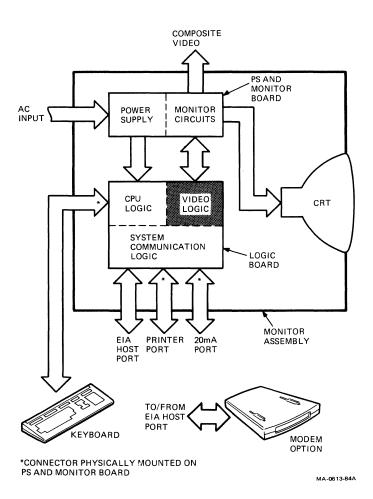

#### 3.3 SYSTEM ARCHITECTURE

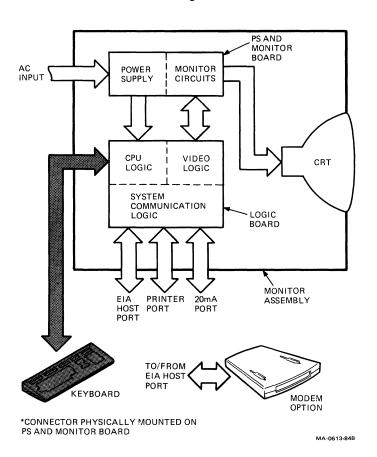

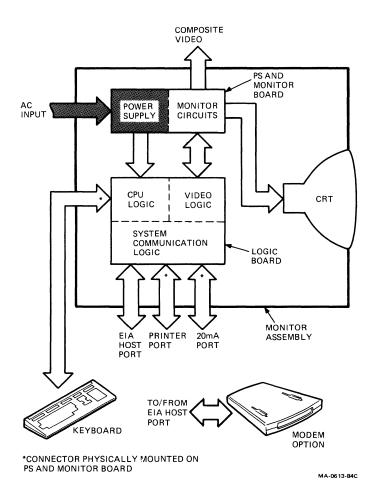

Figure 3-1 provides a functional block diagram of the terminal that identifies the terminal's major components or logics.

- CPU logic

- Video logic

- System communication logic

- Modem option

- Power supply

- Keyboard

- Monitor (monitor circuits and CRT)

Figure 3-1 VT220 Series Terminal Functional Block Diagram

#### 3.3.1 CPU Logic

The CPU logic controls the overall operation of the terminal. It interprets host and keyboard input and directs terminal functions. The CPU logic contains the following major components/circuits.

- 8051 microprocessor with internal RAM (128 bytes) and ROM (4K), directly responsible for terminal operation, including direct interface with the keyboard module

- Associated decoding logic

- 256 byte nonvolatile RAM for storing terminal set-up information

- 24K byte of ROM containing firmware for all terminal control functions, such as keyboard handling, screen data handling, set-up, self-test, VT100 and VT52 modes, and printer control

- 8K of volatile screen RAM used for storage of characters to be displayed, as well as for data buffering, and scratch pad operations

- 8K of volatile atribute RAM used for storage of attribute data associated with characters stored in the screen RAM

#### NOTE

The volatile screen and attribute RAMs are also accessed by the video logic to obtain character and attribute values stored in these RAMs.

# 3.3.2 Video Logic

The video logic develops the video output signals required to drive the terminal monitor. The video logic consists of the following major components/circuits.

- A 9007 video processor that performs DMA transfers (character and attribute transfers from CPU logic RAMs to the video converting circuit), and generation of basic video timing signals

- A video converting circuit that transforms display data into video output to the monitor circuits, and composite video output to a slave monitor

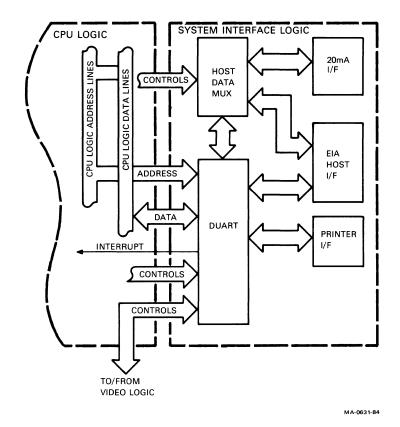

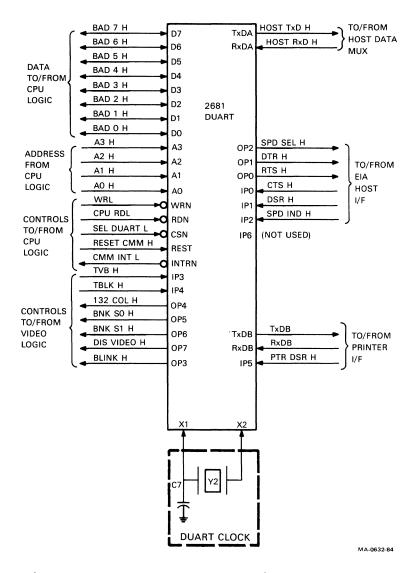

# 3.3.3 System Communication Logic

The system communication logic interfaces the terminal with external devices. The system communication logic consists of the following major components/circuits.

- Connectors for physical connection with the printer, host (EIA host port or 20 mA port connectors), and modem option (via EIA host port)

- DUART for control of communication as programmed by the CPU

- Interface components responsible for input and output of data from the various connectors

# 3.3.4 Modem Option (VT22X-AA)

When installed, the modem interfaces the terminal with a switched or dedicated telephone line for communication with a remote host. The VT22X-AA modem consists of the following major circuits/components.

- Two four-pin telephone jack connectors for interfacing with the telephone line

- EIA connector for interfacing with the monitor assembly

- Handshake circuits to control the communication between the terminal and the remote host

# 3.3.5 Power Supply

The power supply generates the operational voltages required by the monitor assembly, keyboard, and the modem module option. The power supply contains the following major components/circuits.

- AC input circuits

- +5 V development circuits

- +12 V development circuits

- -12 V development circuits

- Pulse modulation and feedback control circuits

- Overcurrent protect circuit

#### 3.3.6 Keyboard

The keyboard enables operator input to the system. The keyboard consists of the following major components/circuits.

- 8051 microprocessor for control of keyboard operations

- Serial interface for communication with the monitor assembly

- Key matrix scanning circuits for determining when a key is being pressed

- Audio circuits for generating bell tones and key clicks

- LED drivers for enabling the keyboard's visual indicators

# 3.3.7 Monitor Components

The monitor components convert separate video and sync input signals from the video logic into visual output to the operator. The monitor contains the following major components/circuits.

- CRT device for presenting the visual output

- Monitor circuits for developing drive potentials for the CRT

- BNC connector for composite video output to a slave monitor

- Brightness and contrast controls

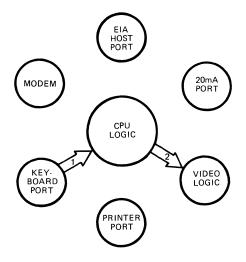

#### 3.4 SYSTEM INTERACTION

Figures 3-2 through 3-7 provide an overview of the information flow within the terminal for various system configurations during the different operating states (set-up, local, and on-line).

- 1. DATA IS TRANSFERED FROM THE KEYBOARD TO THE CPU LOGIC DEFINING PARAMETERS TO BE AFFECTED.

- 2. IF SCREEN DISPLAY IS TO BE AFFECTED, CPU LOGIC DIRECTS VIDEO LOGIC TO ALTER DISPLAY.

MA-1443-83A

Figure 3-2 System Interaction in Set-Up

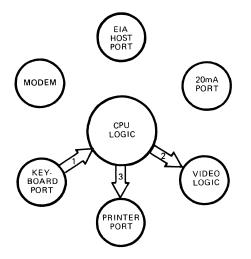

- 1 DATA IS TRANSFERRED FROM THE KEYBOARD TO THE CPU LOGIC

- 2. IF SCREEN DISPLAY IS TO BE AFFECTED, CPU LOGIC DIRECTS VIDEO LOGIC TO ALTER DISPLAY.

- 3. IF DATA IS TO OUTPUT TO A PRINTER, CPU LOGIC DIRECTS TRANSFER OF DATA AND CONTROLS TO PRINTER VIA PRINTER PORT PORTION OF SYSTEM INTERFACE LOGIC.

MA-1445-83A

Figure 3-3 System Interaction in Local

- 1 DATA IS TRANSFERRED FROM THE KEYBOARD TO THE CPU LOGIC

- 2. DATA IS TRANSFERRED FROM THE CPU LOGIC TO THE HOST, VIA EITHER EIA HOST PORT, OR 20 mA PORT PORTIONS OF THE SYSTEM COMMUNICATION LOGIC

- 3. IF LOCAL-ECHO IS ENABLED, AND SCREEN DISPLAY IS TO BE AFFECTED, CPU LOGIC DIRECTS VIDEO LOGIC TO ALTER DISPLAY.

MA-1447-83A

Figure 3-4 System Interaction On-Line: Data to Host (Null-Modem)

- DATA IS TRANSFERRED TO THE CPU LOGIC FROM THE HOST, VIA EITHER EIA HOST PORT, OR 20 MA PORT PORTIONS OF THE SYSTEM COMMUNICATION LOGIC.

- 2. IF SCREEN DISPLAY IS TO BE AFFECTED, CPU LOGIC DIRECTS VIDEO LOGIC TO ALTER DISPLAY.

- 3. IF DATA IS TO BE OUTPUT TO THE PRINTER DEVICE, CPU LOGIC DIRECTS TRANSFER OF DATA AND CONTROLS TO PRINTER DEVICE VIA PRINTER PORT PORTION OF SYSTEM COMMUNICATION LOGIC.

MA-1450-83A

Figure 3-5 System Interaction On-Line: Data from Host

- 1. DATA IS TRANSFERRED FROM THE KEYBOARD TO THE CPU LOGIC.

- 2. DATA IS TRANSFERRED FROM THE CPU LOGIC TO THE HOST EIA

- 3. DATA IS ROUTED FROM EIA HOST PORT TO MODEM OPTION.

- IF LOCAL-ECHO IS ENABLED, AND SCREEN DISPLAY IS TO BE AFFECTED, CPU LOGIC DIRECTS VIDEO LOGIC TO ALTER DISPLAY.

MA-1452-83A

Figure 3-6 System Interaction On-Line: Data to Host (Modem)

- 1. DATA IS ROUTED TO EIA HOST PORT BY MODEM OPTION.

- 2. DATA IS TRANSFERRED TO THE CPU LOGIC FROM THE EIA HOST

- 3. IF SCREEN DISPLAY IS TO BE AFFECTED, CPU LOGIC DIRECTS VIDEO LOGIC TO ALTER DISPLAY.

- 4. IF DATA IS TO BE OUTPUT TO THE PRINTER DEVICE, CPU LOGIC DIRECTS TRANSFER OF DATA AND CONTROLS TO PRINTER DEVICE VIA PRINTER PORT PORTION OF SYSTEM COMMUNICATION LOGIC.

MA-1455-83A

Figure 3-7 System Interaction On-Line: Data from Host (Modem)

# CHAPTER 4 CPU LOGIC

# 4.1 GENERAL

The CPU logic (shaded area in Figure 4-1) directs VT220 activity in response to either operator input (via keyboard), or host input (via system communication logic). In general, the CPU performs the following functions.

- Defines operational parameters for other logic components

- Directs system communication logic, video logic, and keyboard module operation

Figure 4-1 VT220 Series Terminal Functional Block Diagram

- Manages screen and attribute RAMs

- Initializes system at power up, and executes self-test programs

# 4.2 MAJOR CIRCUITS AND COMPONENTS

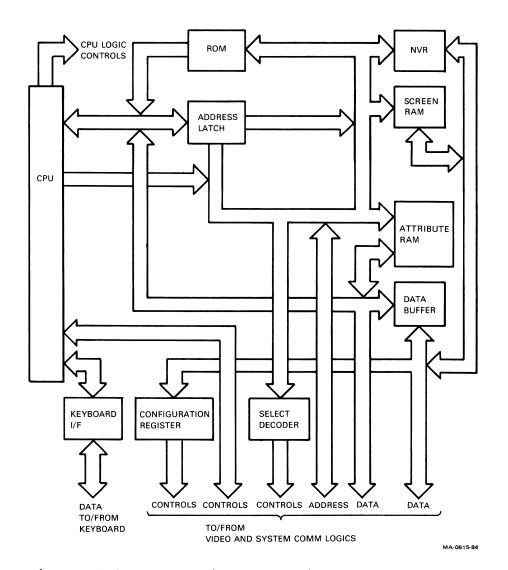

Figure 4-2 provides a block diagram identifying the major circuits and components that make up the central processing unit (CPU) logic.

- Central processing unit (CPU)

- Address latch

- Program ROM

- Data buffer

- Screen RAM

- Attribute RAM

- Select decoder

- Keyboard I/F

- Nonvolatile RAM (NVR)

- Configuration register

Figure 4-2 CPU Logic Block Diagram

# 4.2.1 Central Processing Unit (CPU)

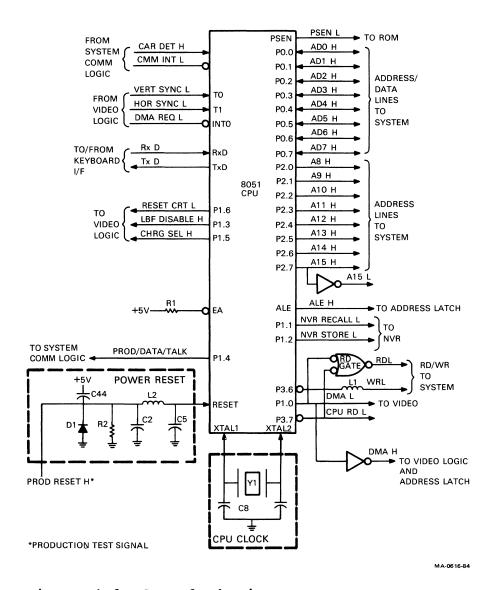

The CPU (Figure 4-3) consists of the following components.

- 8051 microprocessor -- services interrupt and DMA requests, interprets host and keyboard data, generates address and read/write controls for system components, and initializes system on power up.

- RD gate -- generates RD L from either CPU RD L, when CPU is attempting to read from an I/O device or RAM, or from DMA L, when character and attribute data is to be transferred out of the RAMs over to the video logic.

Figure 4-3 CPU Block Diagram

- Power reset -- resets the 8051 on power up.

- CPU clock -- provides 11.0592 MHz input to 8051 CPU for basic timing.

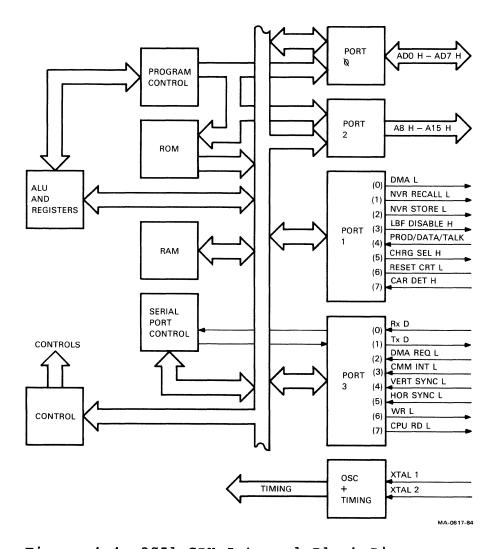

- 4.2.1.1 8051 CPU Internal Circuits -- Figure 4-4 provides a block diagram showing the major 8051 CPU internal circuits.

- Port Ø -- is eight bidirectional lines used for output of lower byte of address and for input and output of data.

- Port 1 -- is eight quasi-bidirectional lines used for input of status information and output of controls.

- Port 2 -- is eight lines used for output of high byte of address.

Figure 4-4 8051 CPU Internal Block Diagram

- Port 3 -- is eight lines used for input of status, output of controls, and transfer of serial data between the 8051 and the keyboard I/F.

- Oscillator (OSC) and timing -- generates 8051 timing signals based on 11.0592 MHz input from external CPU clock.

- Program control -- controls sequence of program memory execution (internal ROM and external ROM).

- Control -- interprets instructions and generates controls to 8051 circuits based on that interpretation.

- Serial port control -- provides full-duplex UART functionality for serial data communications with the keyboard.

- ROM -- provides 4K bytes of internally stored programming.

- RAM -- provides 128K bytes of memory for scratch pad and register/stack functions.

- ALU and registers -- provide processing logic, including special function registers.

Later in this chapter, Table 4-2 describes the signals shown in Figures 4-3 and 4-4.

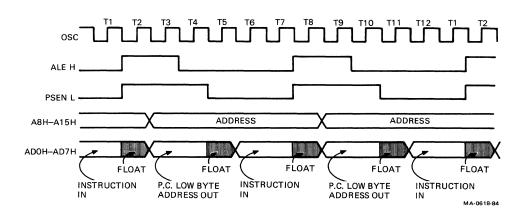

# 4.2.1.2 8051 CPU Transactions -- The 8051 performs the following transactions.

- Instruction fetch -- reads internal or external ROM.

- Read/write transaction -- reads or writes data for system

I/O devices, screen RAM, or attribute RAM.

- DMA transaction -- grants control of the data buses to enable video logic access of CPU logic RAMs, for access of character and attribute values.

Figures 4-5 through 4-7 provide timing diagrams for instruction fetch, read, and write transactions. No diagram is provided concerning DMA transactions, as DMA transactions are described in greater detail in the video logic description (refer to the CRT controller description in Chapter 6).

Figure 4-5 8051 CPU Instruction Fetch Timing Diagram

Figure 4-6 8051 CPU Read Transaction Timing Diagram

Figure 4-7 8051 CPU Write Transaction Timing Diagram

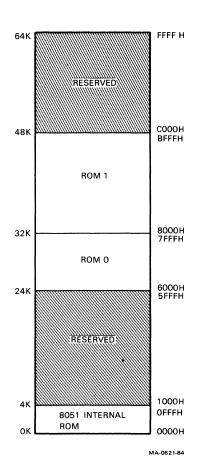

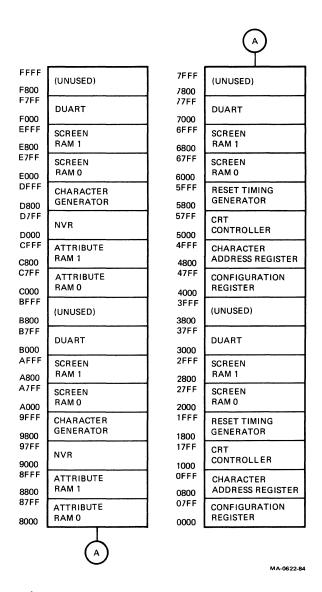

Figure 4-8 provides an address map for instruction fetch transactions (ROM access). Figure 4-9 provides an external data memory map for system non-ROM read/write transactions. As shown in Figure 4-9, several address ranges are mapped for each specific device or transaction. This is due to a "don't care" condition for some bits when addressing these devices. The addresses actually used are identified in Table 4-1 in conjunction with the select decode description (section 4.2.8).

Figure 4-8 8051 CPU

Address Map: ROM

Figure 4-9 8051 CPU Address Map: Non-ROM

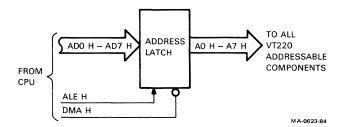

### 4.2.2 Address Latch

The address latch (Figure 4-10), is used by the 8051 for storing the lower byte of address to be used for access of any 8051 addressable component, including external ROM. Address is input to the latch by ALE H and enabled as output as long as DMA H is false. The address latch is inhibited during DMA transactions to prevent any value stored in the latch from affecting the address being generated by the video logic for access of the RAM.

Definitions of the signals identified in Figure 4-10 are provided in Table 4-2.

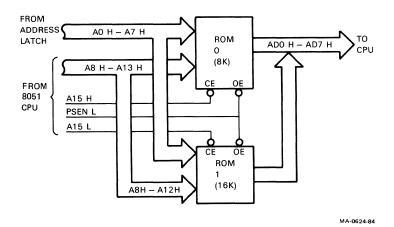

# 4.2.3 Read Only Memory (ROM)

ROM provides storage for the firmware required for terminal operation. The ROM (Figure 4-11) consists of two ROM devices, ROM  $\emptyset$ , containing 8K bytes of firmware, and ROM 1, containing 16K bytes.

ROM access occurs when PSEN L is true, with ROM  $\emptyset$  enabled for Al5 L true, and ROM 1 enabled for Al5 H true.

Figure 4-10 Address Latch Block Diagram

Figure 4-11 ROM Block Diagram

Later in this chapter, Table 4-2 describes the signals shown in Figure 4-11.

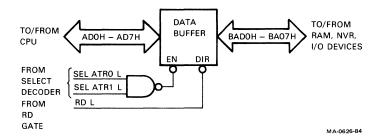

#### 4.2.4 Data Buffer

The data buffer provides isolation between the ADØ H-AD7 H lines used by the 8051 CPU for program memory, addressing, and access of either of the two attribute RAMs in the video logic (refer to Chapter 6), and the BADØ H-BAD7 H lines used for all other read, write, and DMA transactions.

The isolation between the ADØ H-AD7 H bus and the BADØ H-BAD7 H bus provided by the data buffer enables the video logic to use both buses during DMA transactions. The BADØ H-BAD7 H lines are used for accessing character address data stored in the screen RAM, while the ADØ H-AD7 H lines are used for accessing attribute data stored in the attribute RAM.

As shown in Figure 4-12, the data buffer is a bidirectional device enabled whenever the attribute RAM is not being accessed (SEL ATRØ L and SEL ATRI L both false), with the direction of data transfer determined by RD L (out as BAD signals when RD L is false, and in as AD signals when true). The data buffer is disabled either during 8051 CPU access of the attribute RAM, or during DMA transactions, when the video logic is accessing the stored attribute data.

Later in this chapter, Table 4-2 describes the signals shown in Figure 4-12.

Figure 4-12 Data Buffer Block Diagram

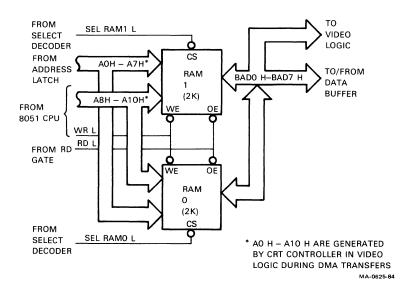

#### 4.2.5 Screen RAM

The 8051 uses the screen RAM to store character address data for output to the video logic and for scratch pad operations. Character address data stored in the screen RAM is transferred to the video logic during DMA transactions (along with attribute values associated with the defined character address, as stored in attribute RAM). It also defines an address value for a character generator within the video logic, with that address defining the character to be processed for display (refer to the video logic description in Chapter 6).

The screen RAM (Figure 4-13) consists of two static RAM devices, each providing 2K bytes of RAM space. Each is selected by separate select signals (SEL RAMØ L or SEL RAM1 L), and enabled for 8Ø51 write by WR L, or enabled for read output by RD L (with RD L generated either from CPU RD L, for CPU access, or from DMA L, for DMA transfer to the video logic).

Later in this chapter, Table 4-2 describes the signals shown in Figure 4-13.

Figure 4-13 Screen RAM Block Diagram

# 4.2.6 Attribute RAM

The 8051 CPU loads attribute values for specific characters into attribute RAM at addresses directly corresponding to character address values loaded into the screen RAM. Whenever character address values are loaded into the screen RAM, the 8051 CPU will write attribute values associated with those character address values into the attribute RAM.

During DMA transactions, the video logic generates a single address which is applied to both the attribute and screen RAMs. The attribute data is output from attribute RAM and sent to the video logic in conjunction with the character address being output from the screen RAM on the same DMA transaction (attribute value on the AD data lines, and character data on the BAD data lines).

The attribute RAM (Figure 4-14) consists of two static RAM devices, each providing 2K bytes of RAM space. Each is selected by separate select signals (SEL ATRØ L or SEL ATRI L), and enabled for 8051 write by WR L, or enabled for read output by RD L (with RD L generated either from CPU RD L, for CPU access, or from DMA L, for DMA transfer to the video logic).

Later in this chapter, Table 4-2 describes the signals shown in Figure 4-14.

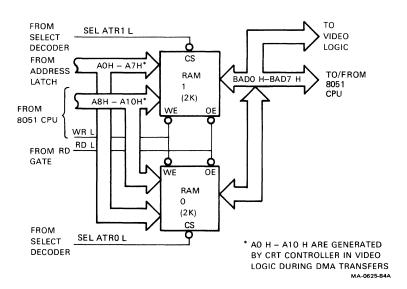

Figure 4-14 Attribute RAM Block Diagram

#### 4.2.7 Select Decoder

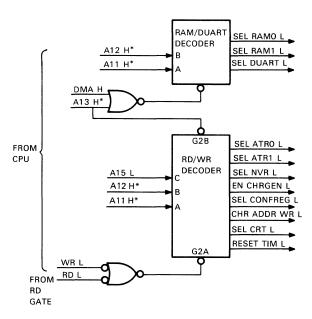

The select decoder generates access enables for 8051 CPU read/write transactions, and for video logic DMA transactions. The select decoder (Figure 4-15) consists of the following components.

- RAM/DUART decoder -enabled by Al3 H true, during is 8051CPU read/write transactions to decode All H-Al2 H inputs into enable of either the screen RAM (SEL RAMØ SEL RAM1 L) or the DUART in or(SEL DUART); it is also enabled by communication logic H true during DMA transactions for selecting screen (address input for DUART is not to be accessed presented during DMA transactions).

- RD/WR decoder -- is enabled by RD L or WR L for 8051 CPU read/write transactions, when Al3 H is false, to decode Al5 L, All H-Al2 H into access output to NVR (SEL NVR L), configuration register (SEL CONF REG L), attribute RAM (SEL ATRØ L or SEL ATRI L), or to various video logic components (EN CHR GEN L, CHR ADDR WR L, SEL CRT L, and RESET TIM L); it is also enabled by RD L, during DMA transactions (Al3 H false during DMA, with address value for either of two attribute RAMs presented to decoder).

\* A11 H -A13 H ARE GENERATED BY CRT CONTROLLER IN VIDEO LOGIC DURING DMA TRANSACTIONS.

MA-0627-84

Figure 4-15 Select Decoder Block Diagram

During DMA transactions, the RD/WR decoder and the RAM/DUART decoder will both be enabled for output of corresponding screen RAM and attribute RAM select signals, as these two RAM circuits are read simultaneously by the video logic.

Table 4-1 identifies the address values for all of the access enable signals. Later in this chapter, Table 4-2 describes the signals shown in Figure 4-15.

Table 4-1 8051 CPU Addresses (Non-ROM)

| Enable Signal  | Hex Address(es)    | Device (Logic)                     |

|----------------|--------------------|------------------------------------|

| SEL RAMØ L     | A000-A7FF          | RAM Ø (CPU)                        |

| SEL RAM1 L     | A800-AFFF          | RAM 1 (CPU)                        |

| SEL DUART L    | B7F0-87FF          | DUART (system communication)       |

| SEL ATRØ L     | 8000-87FF          | Attribute RAM Ø (video)            |

| SEL ATR1 L     | 8800-8FFF          | Attribute RAM l (video)            |

| SEL NVR L      | 9700-97FF          | NVR                                |

| EN CHR GEN L   | 9FF <b>Ø-</b> 9FFF | Character generator (video)        |

| SEL CONF REG L | Ø7FF               | Configuration register (CPU)       |

| CHR ADDR WR L  | ØFFF               | Character address register (video) |

| SEL CRT L      | 1700-17FF          | CRT controller (video)             |

| RESET TIM L    | 1FFF               | Timing control (video)             |

# 4.2.8 Keyboard Interface (I/F)

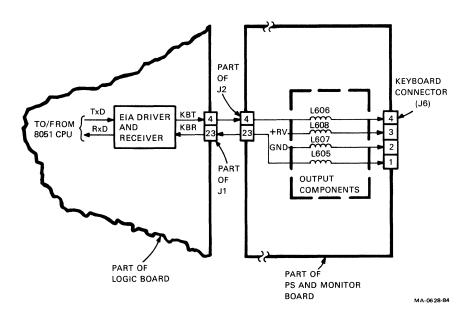

The keyboard I/F buffers communication between the keyboard module and the 8051 CPU. Serial data is output to the keyboard as KBT (originating at 8051 as TxD), and input to the 8051 as RxD (originating at keyboard as KBR).

Keyboard I/F components are physically located on both of the terminal PCBs. Figure 4-16 provides a breakdown of the keyboard I/F.

- EIA driver and receiver -- interface TTL level logic with EIA level communication lines.

- Jl (logic board)/J2 (PS and monitor board) -- are 26-pin connectors used for routing signals between the two system PCBs.

- Output components -- are ferrite beads tied to keyboard connector pins that are used for radiation suppression.

- J6 -- is a 4-pin telephone plug-type connector that provides direct connection between the keyboard cable and the monitor assembly.

Figure 4-16 Keyboard I/F Block Diagram

Figure 4-16 provides a pin-out for the keyboard connector (J6) and identifies the J1/J2 pins used for keyboard I/F functions. A complete pin-out of J1/J2 is provided in the system communication logic description presented in Chapter 5 (refer to Figure 5-9).

Later in this chapter, Table 4-2 describes the signals shown in Figure 4-16.

# 4.2.9 Nonvolatile RAM (NVR)

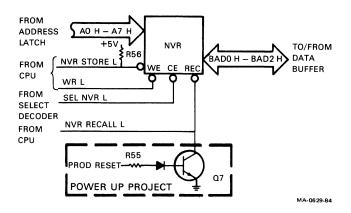

The NVR combines a 256  $\chi$  4 bit static RAM with a 256  $\chi$  4 bit electrically alterable ROM (EAROM) to provide memory for storing terminal operational parameters, and allowing those parameters to be manipulated by the operator.

During a power-up sequence, data is transferred from the EAROM to the NVR RAM portion (NVR RECALL L), and then to the CPU logic RAM for use in defining terminal parameters. While in the CPU logic RAM, the data stored can be altered. Operator keyboard input defines new parameters, with the 8051 directing a write to alter the data stored in the CPU logic RAM. During a save parameters operation, the data stored in the CPU logic RAM is written to the NVR RAM by the 8051 (SEL NVR L and WR L), and then stored as new parameter values in the NVR EAROM by NVR STORE L from the 8051.

Figure 4-17 NVR Block Diagram

The NVR circuit (Figure 4-17) consists of the following components/circuits.

- NVR device -- contains the RAM and EAROM memories for storing and transferring of parameter values.

- Power up protect -- prevents inadvertant write to NVR device by the 8051 during a power up sequence by forcing NVR RECALL L low until full dc power is applied and all circuits operational (NVR RECALL L places NVR in recall mode and prevents a low at NVR STORE L from being acted on).

Later in this chapter, Table 4-2 describes the signals shown in Figure 4-17.

# 4.2.10 Configuration Register

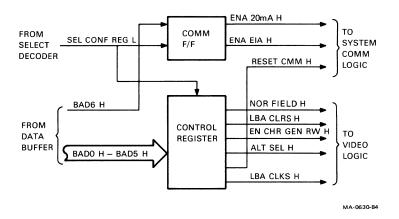

The configuration register is programmed by the 8051 with control values to affect system communication and video logic operations. The configuration register (Figure 4-18) consists of two devices, both loaded by SEL CONF REG L: A F/F device for controlling which host communications port is to be enabled (reset for ENA EIA H, set for ENA 20 mA H), and a register for generating miscellaneous video logic controls (NOR FIELD H, LBA CLRS H, EN CHR GEN RW H, ALT SEL H, and LBA CLKS H), as well as a reset to the DUART in the system communications logic (RESET CMM H).

Descriptions of the signals identified in Figure 4-18 follow in Table 4-2.

Figure 4-18 Configuration Register Block Diagram

# 4.3 SIGNAL DESCRIPTIONS

Table 4-2 provides descriptions of all the signals identified in this chapter. These descriptions are provided for reference, and are listed alphabetically by mnemonic, with numeric mnemonics listed last.

# 4.4 SCHEMATIC REFERENCE INFORMATION

Table 4-3 identifies the logic board component coordinate, and the schematic page and coordinates for each of the CPU logic circuits and components identified in this chapter.

#### NOTE

The reference information is based on Rev. A of the logic board schematics (CS  $5415653-\emptyset-1$ ), and Rev. A of the PS and monitor board schematics (CS  $5415651-\emptyset-1$ ).

Table 4-2 CPU Logic Signal Descriptions

| Mnemonic      | Signal                         | Description                                                                                                                                          |

|---------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| A8 H-A15 H    | Address bits<br>8-15 high      | High order byte of address                                                                                                                           |

| A15 L         | Address bit 15 low             | Inverted most significant bit of address used as enable for ROM 1, and for decode input to select decoder                                            |