RF11/RS11 DECdisk system manual

1st Edition March 1971 2nd Printing (Rev) August 1971

Copyright © 1971 by Digital Equipment Corporation

The material in this manual is for informa-tion purposes and is subject to change with-

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

**FOCAL**

FLIP CHIP DIGITAL

COMPUTER LAB

UNIBUS

# **CONTENTS**

|            |                                                  | Page            |         |                                              | Page |

|------------|--------------------------------------------------|-----------------|---------|----------------------------------------------|------|

| СНАРТЕ     | R 1 RF11/RS11 GENERAL DESCRIPTION                |                 | 4.2.1   | Read/Write Heads                             | 4-1  |

|            |                                                  | 1.1             | 4.2.2   | Digital Recording Techniques                 | 4-2  |

| 1.1        | Introduction                                     | 1-1             | 4.2.3   | The Read/Write Head Electronics              | 4-3  |

| 1.2        | Functional Description                           | 1-1             | 4.2.4   | The RS11 Signal Format                       | 4-4  |

| 1.2.1      | RS11 Disk Unit                                   | 1-1             | 4.3     | Track Signal Error Detection Logic           | 4-5  |

| 1.2.2      | RF11 Control Unit                                | 1-2             | 4.3.1   | Error Detection Logic for the A Timing Track | 4-5  |

| 1.3        | Specifications                                   | 1-3             | 4.3.2   | Error Detection Logic for the B and C Tracks | 4-5  |

| 1.3.1      | Physical Description                             | 1-4             | 4.3.3   | Error Detection Logic for the Data Tracks    | 4-6  |

| 1.3.2      | Environmental Limits                             | 1-4             | 4.4     | The Control Section Logic                    | 4-7  |

| 1.3.3      | Logic Format                                     | 1-4             | 4.4.1   | Initialization                               | 4-7  |

| 1.3.4      | Timing Format                                    | 1-4             | 4.4.2   | Unibus Receivers and Drivers                 | 4-7  |

| 1.3.5      | Power Requirements                               | 1-4             | 4.4.3   | Output Gating                                | 4-7  |

| 1.3.6      | Power Dissipation                                | 1-4             | 4.4.4   | Selection Logic                              | 4-7  |

| 1.4        | Related Documents                                | 1-4             | 4.4.5   | NPR (Non-Processor Request) Logic            | 4-7  |

|            |                                                  |                 | 4.4.6   | Interrupt Logic                              | 4-8  |

| CHAPTE     | ER 2 RF11/RS11 OPERATION                         |                 | 4.4.7   | Function Register Logic                      | 4-8  |

| 2.1        | Introduction                                     | 2-1             | 4.4.8   | Timing Generation Logic                      | 4-8  |

| 2.2        | Controls and Indicators                          | 2-1             | 4.4.9   | Self-Clocking Logic                          | 4-11 |

| 2.2.1      | RS11 Controls                                    | 2-1             | 4.4.10  | Bit Counter                                  | 4-11 |

| 2.2.2      | RF11 Indicators                                  | 2-1             | 4.4.11  | Unlock Sequence Logic                        | 4-11 |

| 2.2.3      | 855 Power Control                                | 2-3             | 4.4.12  | Disk Addressing Logic                        | 4-12 |

| 2.2.3      | 655 Towor Control                                |                 | 4.4.13  | Current Memory Address Register Logic        | 4-12 |

| СНАРТЕ     | ER 3 PROGRAMMING                                 |                 | 4.4.14  | Word Count Register Logic                    | 4-13 |

|            |                                                  |                 | 4.5     | System Data Transfer Logic                   | 4-13 |

| 3.1        | Introduction                                     | 3-1             | 4.5.1   | The Buffer and Shift Register Logic          | 4-13 |

| 3.2        | Device Registers                                 | 3-1             | 4.5.2   | Write Operation Logic                        | 4-13 |

| 3.2.1      | Disk Control Status Register (DCS - 777460)      | 3-1             | 4.5.3   | Read Operation Logic                         | 4-15 |

| 3.2.2      | Word Count Register (WC = 777462)                | 3-2             | 4.5.4   | Write Check Logic                            | 4-15 |

| 3.2.3      | Current Memory Address Register (CMA = 777464)   | 3-2             | 4.5.5   | Data Transfer Error Condition Logic          | 4-15 |

| 3.2.4      | Disk Address Register (DAR = 777466)             | 3-2             | 4.5.5.1 | Write Check Error                            | 4-15 |

| 3.2.5      | Disk Address Ext & Error Register (DAE = 777470) | 3-3             | 4.5.5.2 | Error and FReeZe                             | 4-16 |

| 3.2.6      | Disk Data Buffer Register (DBR = 777474)         | 3-3             | 4.5.5.3 | Address Parity Error                         | 4-16 |

| 3.2.7      | Maintenance Register (MAR = 777474)              | 3-3             | 4.5.5.4 | Missed Transfer Error                        | 4-16 |

| 3.2.8      | Address of Disk Segment Register (ADS = 777476)  | 3-4             | 4.5.5.5 | Data Parity Error                            | 4-16 |

| 3.3        | Addresses                                        | 3-4             | 4.5.5.6 | Write Lockout Error                          | 4-16 |

| 3.4        | Data Format                                      | 3-4             | 4.5.5.7 | Nonexistent Disk Error (PSLER)               | 4-17 |

| 3.5        | Programming Examples                             | 3-4             | 4.5.5.8 | Nonexistent Disk (SEQ ER)                    | 4-17 |

|            |                                                  |                 | 4.5.5.9 | Data Request Late Error                      | 4-17 |

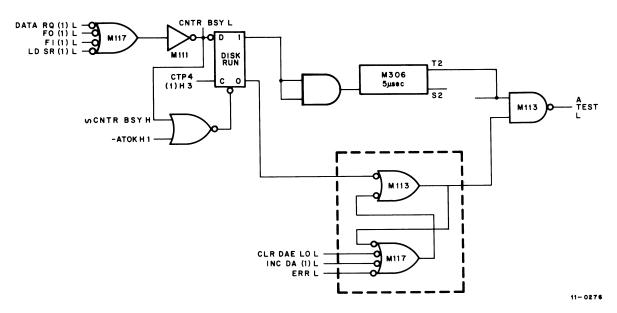

| CHAPT      | ER 4 DETAILED DESCRIPTION                        |                 | 4.5.6   | The A TEST and Read Disable Signal           | 4-17 |

| <i>1</i> 1 | Introduction                                     | 4-1             | 4.5.7   | The Gap                                      | 4-19 |

| 4.1        |                                                  | 4-1<br>4-1      | 4.6     | The Maintenance Logic                        | 4-19 |

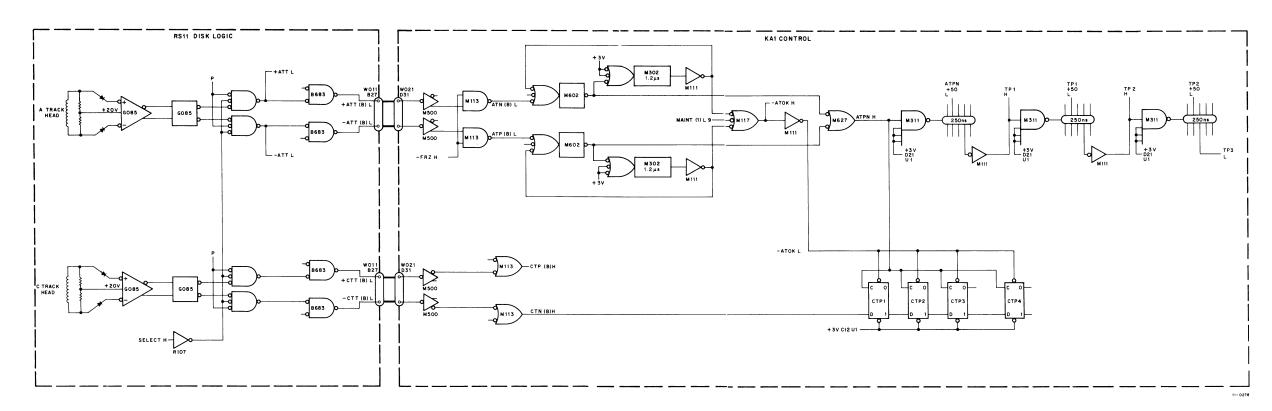

| 4.2        | RS11 Disk Logic                                  | <del>4-</del> 1 | 7.0     | The Maintenance Dogie                        |      |

# **CONTENTS** (cont.)

|          |                                                          | Page |         |                                          | Page |

|----------|----------------------------------------------------------|------|---------|------------------------------------------|------|

| CHAPTER  | 5 MODULE DESCRIPTIONS                                    |      | СНАРТЕ  | R 6 RF11/RS11 INSTALLATION               |      |

| 5.1      | Introduction                                             | 5-1  | 6.1     | Introduction                             | 6-1  |

| 5.2      | DEC Logic                                                | 5-2  | 6.2     | System Configuration                     | 6-1  |

| 5.3      | Measurement Definitions                                  | 5-2  | 6.3     | Installation Planning                    | 6-1  |

| 5.4      | Loading                                                  | 5-2  | 6.3.1   | Power Requirements                       | 6-1  |

| 5.5      | Module Modifications                                     | 5-2  | 6.3.2   | Space Requirements                       | 6-2  |

| 5.6      | Module Characteristics                                   | 5-2  | 6.3.3   | Environmental Requirements               | 6-3  |

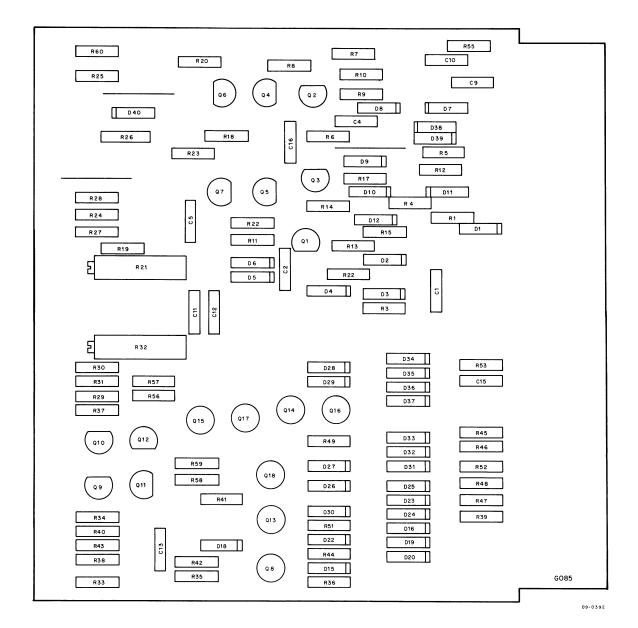

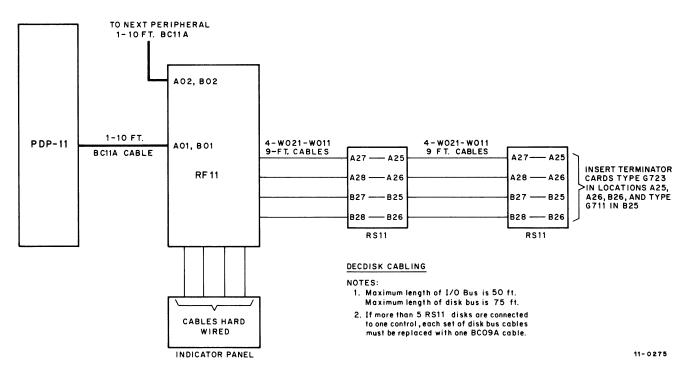

| 5.6.1    | G085 Disk Read Amplifier                                 | 5-2  | 6.3.4   | Cable Requirements                       | 6-3  |

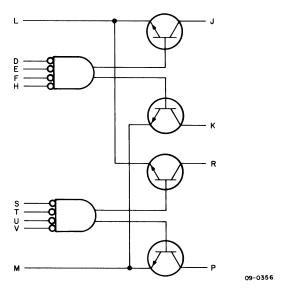

| 5.6.2    | G285 Series Switch                                       | 5-3  | 6.4     | Installation Procedure                   | 6-3  |

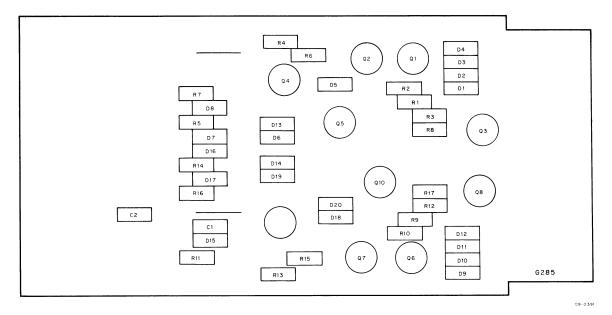

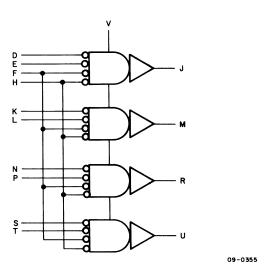

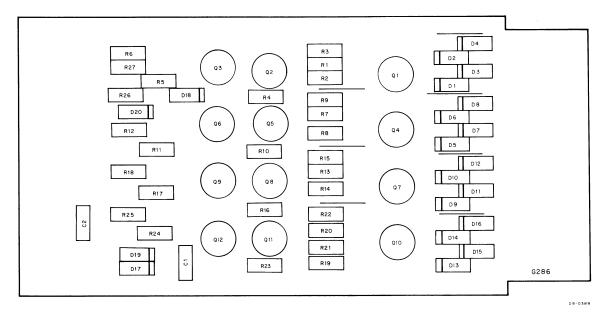

| 5.6.3    | G286 Centertap Selector                                  | 5-4  | 6.4.1   | Cabinet Unpacking                        | 6-3  |

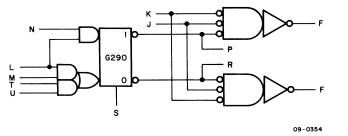

| 5.6.4    | G290 Writer Flip-Flop                                    | 5-4  | 6.4.2   | Cabinet Installation                     | 6-5  |

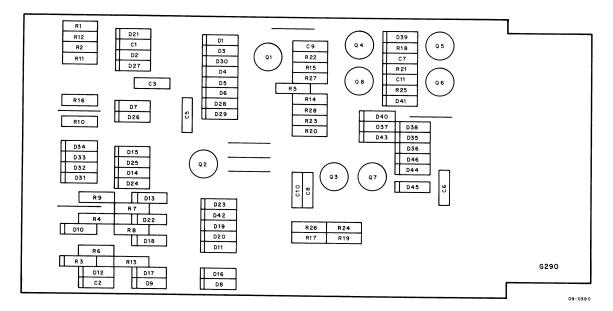

| 5.6.5    | G681 B Track Matrix                                      | 5-5  | 6.4.3   | RF11 Controller Installation             | 6-5  |

| 5.6.6    | G789 Signal Simulator Connector                          | 5-5  | 6.4.4   | RS11 Unpacking                           | 6-5  |

| 5.6.7    | G790 Signal Simulator Generator                          | 5-5  | 6.4.5   | RS11 Installation                        | 6-6  |

| 5.6.8    | G821 Regulator Control                                   | 5-5  | 6.4.6   | Power-Up Sequence                        | 6-6  |

| 5.6.9    | G711 Terminator Board                                    | 5-5  | 6.5     | Installation Testing                     | 6-6  |

| 5.6.10   | G723 Negative Bus Terminator                             | 5-5  | 6.5.1   | Diagnostics                              | 6-7  |

| 5.6.11   | G736 Priority Select Module                              | 5-5  | 6.5.2   | System Software                          | 6-7  |

| 5.6.12   | G740 Disk Selection Module                               | 5-5  |         |                                          |      |

| 5.6.13   | G775 Indicator Panel                                     | 5-6  | CHAPTE  | R 7 RF11/RS11 MAINTENANCE                |      |

| 5.6.14   | M106 Dot NOR Gates                                       | 5-6  | 7.1     | Introduction                             | 7-1  |

| 5.6.15   | M149 9 x 2 NAND Wired or Matrix                          | 5-6  | 7.2     | Organizational Maintenance               | 7-1  |

| 5.6.16   | M205 5 D Flip-Flops                                      | 5-6  | 7.2.1   | Preventive Maintenance                   | 7-1  |

| 5.6.17   | M216 Six D Flip-Flops                                    | 5-6  | 7.2.2   | RS11 Maintenance Adjustments             | 7-1  |

| 5.6.18   | M306 Integrating One-Shot                                | 5-6  | 7.2.2.1 | Read Amplifier Adjustment Procedure      | 7-1  |

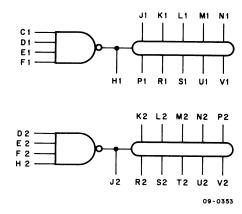

| 5.6.19   | M311 Tapped Delay Line                                   | 5-6  | 7.2.2.2 | G085 Adjustment                          | 7-2  |

| 5.6.20   | Negative Input Converter                                 | 5-7  | 7.2.3   | Changing The Timing Tracks               | 7-3  |

| 5.6.21   | M632 Positive Input-Converter Driver                     | 5-7  | 7.2.4   | Diagnostics                              | 7-4  |

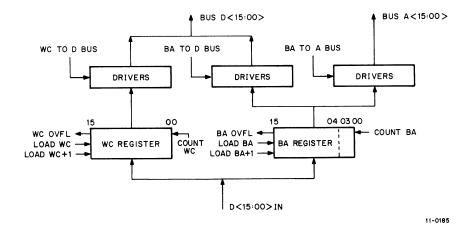

| 5.6.22   | M795 Word Count & Current Memory Address Module (WC&CMA) | 5-8  | 7.3     | Field-Level Maintenance                  | 7-4  |

| 5.6.22.1 | Theory of Operation                                      | 5-8  | 7.3.1   | On-Line Check                            | 7-4  |

| 5.6.22.2 | Functional Description                                   | 5-8  | 7.3.2   | Disk Assembly Repairs                    | 7-5  |

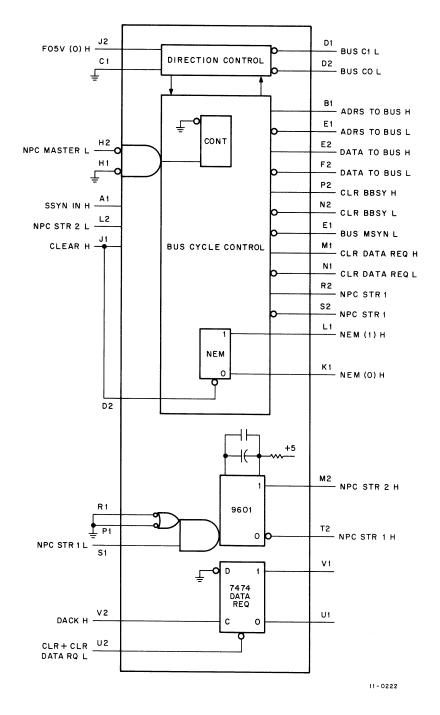

| 5.6.23   | M796 Unibus Master Control Module                        | 5-9  | 7.3.2.1 | Removing the Disk Assembly               | 7-5  |

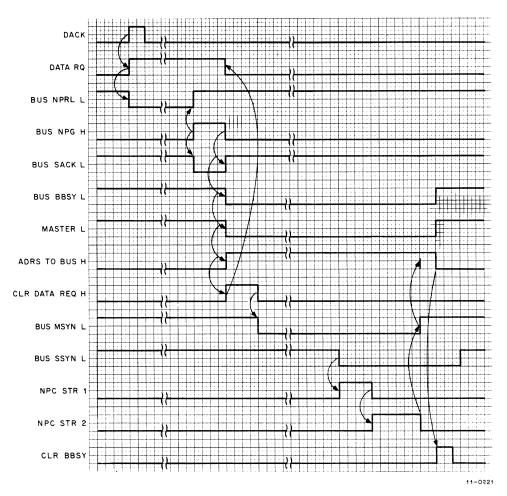

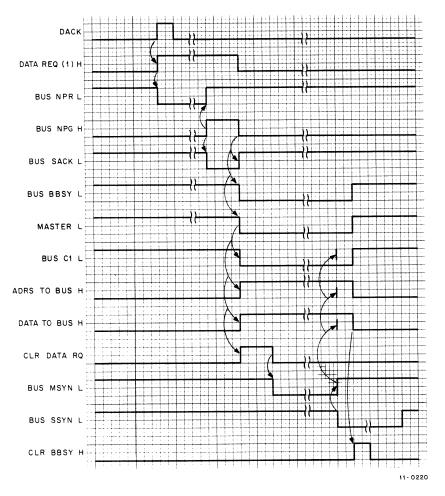

| 5.6.23.1 | Theory of Operation                                      | 5-9  | 7.3.2.2 | Removing the Disk Surface                | 7-8  |

| 5.6.23.2 | Functional Description                                   | 5-9  | 7.3.2.3 | Replacing the Shoes                      | 7-8  |

| 5.6.24   | M797 Register Selection Module                           | 5-10 | 7.3.2.4 | Replacing and Cleaning the Disk Surface  | 7-8  |

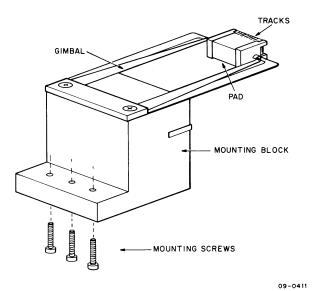

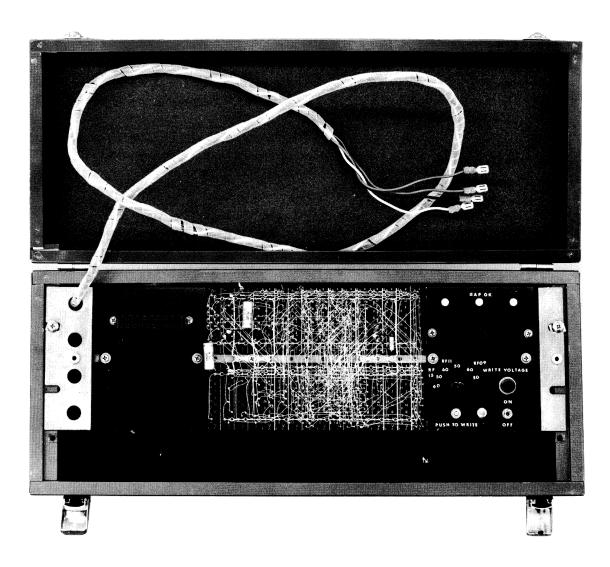

| 5.6.24.1 | Theory of Operation                                      | 5-11 | 7.3.2.5 | Timing Track Writer                      | 7-10 |

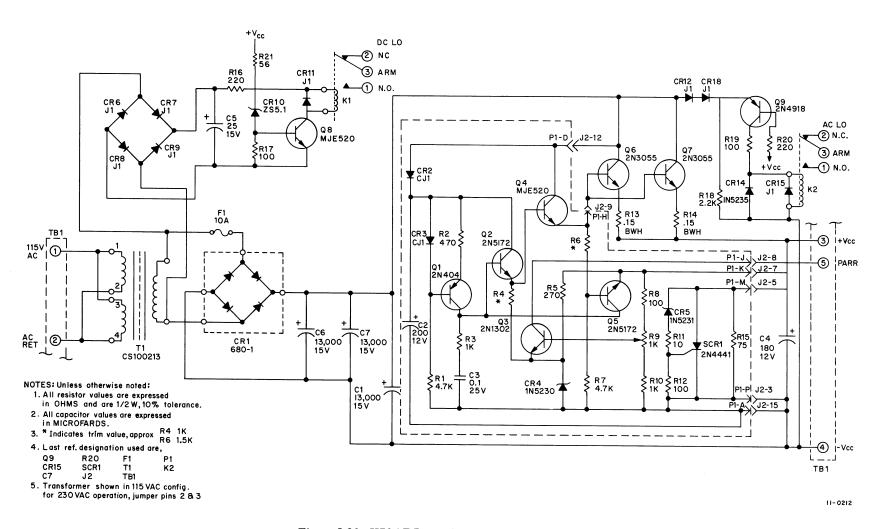

| 5.6.25   | M798 Unibus Drivers                                      | 5-11 | 7.3.3   | RS11 Calibration                         | 7-11 |

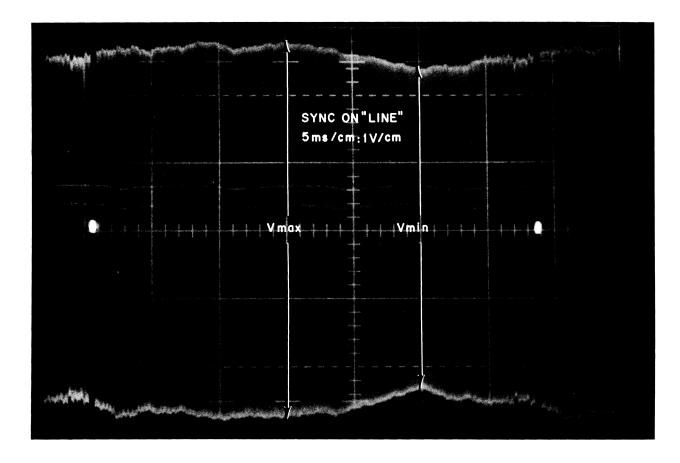

| 5.6.26   | W021 RF11/RS11 Interface Cable                           | 5-11 | 7.3.3.1 | Measuring Surface Modulation             | 7-11 |

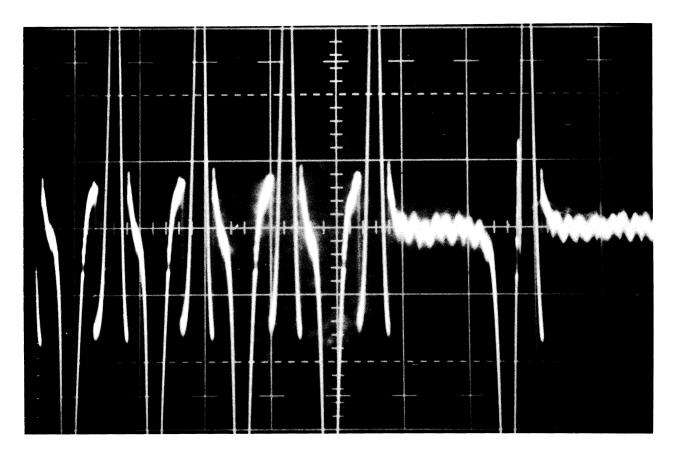

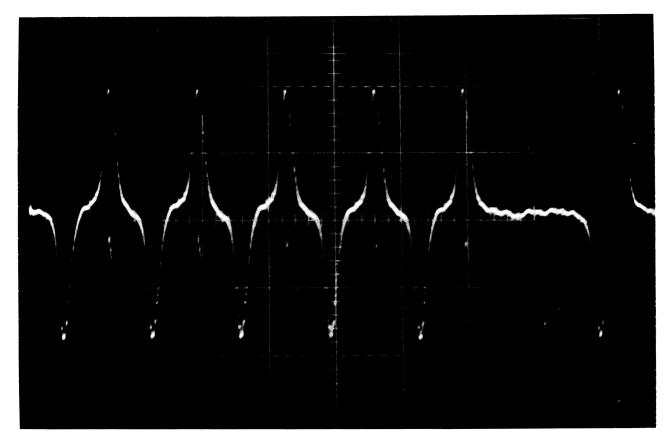

| 5.7      | RF11/RS11 Power Supplies                                 | 5-11 | 7.3.3.2 | Analyzing the Gain of the Data Tracks    | 7-12 |

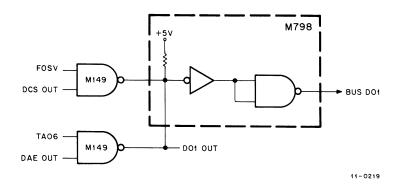

| 5.7.1    | 705B Power Supply                                        | 5-11 | 7.3.3.3 | Calibrating the Gain of the Data Readers | 7-13 |

| 5.7.2    | 716 Indicator Supply                                     | 5-12 | ,       |                                          | ,    |

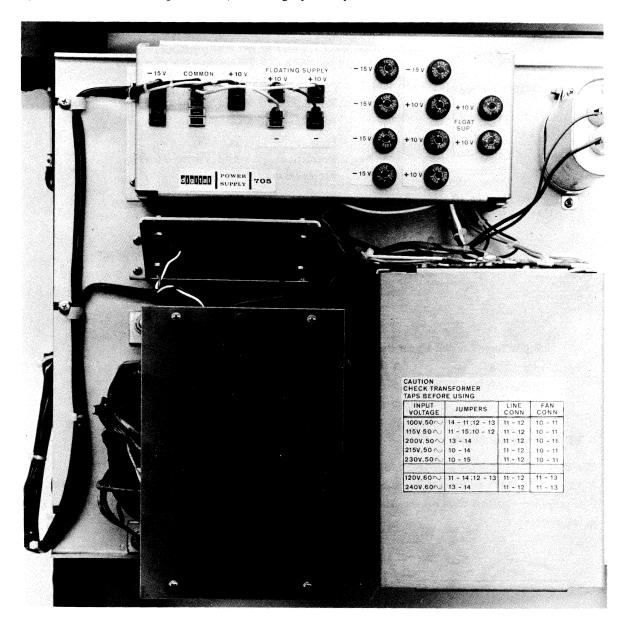

| 5.7.3    | H726A-2 Power Supply                                     | 5-12 | APPEND  | IX A RF11/RS11 SIGNAL SUMMARY            | A-1  |

# **ILLUSTRATIONS**

| Figure No.       | Title                                                | Art No.            | Page              | Figure No. | Title                                                 | Art No. | Page       |

|------------------|------------------------------------------------------|--------------------|-------------------|------------|-------------------------------------------------------|---------|------------|

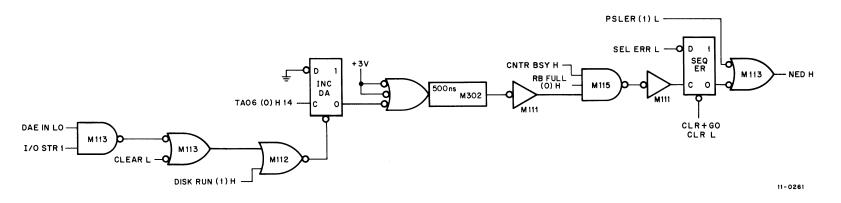

| 1-1              | RF11/RS11 DECdisk Interface Block Diagram            | 11-0243            | 1-1               | 4-30       | Nonexistent Disk by Sequence Error                    | 11-0261 | 4-18       |

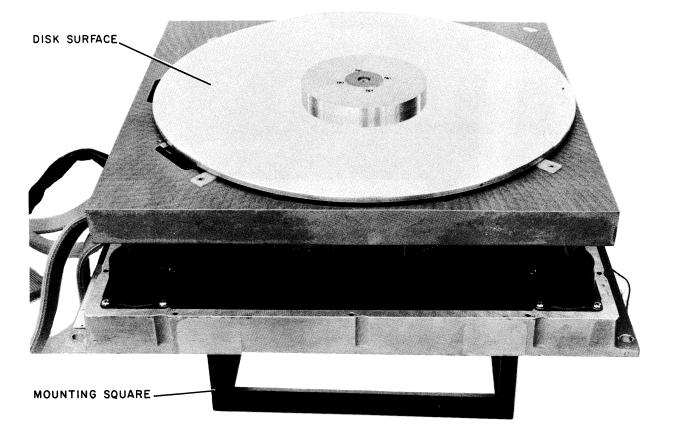

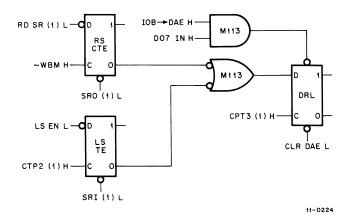

| 1-2              | RS11 Disk Unit                                       |                    | 1-1               | 4-31       | Data Request Late Error                               | 11-0224 | 4-18       |

| 1-3              | RS11 Disk Surface                                    | 11-0242            | 1-2               | 4-32       | Disk Run Logic                                        | 11-0276 | 4-18       |

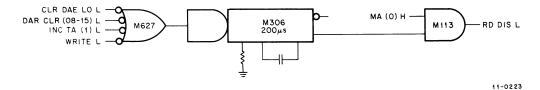

| 1-4              | RS11 Disk Surface Recording Format                   | 11-0273            | 1-2               | 4-33       | Read Disable Logic                                    | 11-0223 | 4-19       |

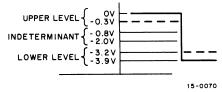

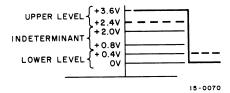

| 1-5              | RF11 Control Unit                                    |                    | 1-3               | 5-1        | Voltage Spectrum of Negative Logic Systems            | 15-0070 | 5-2        |

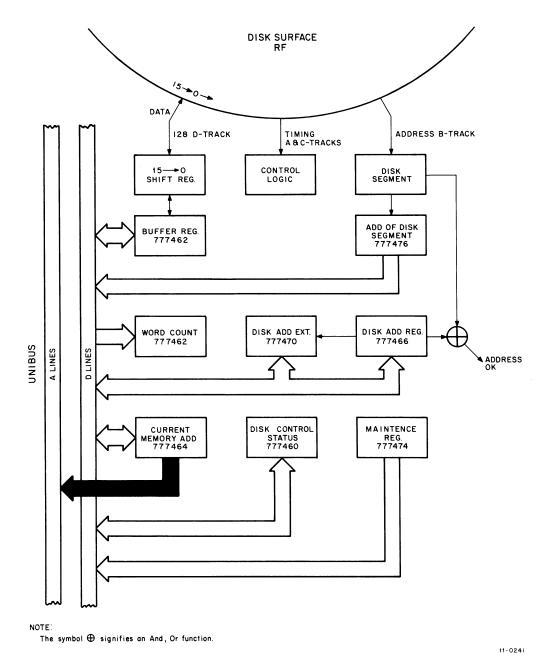

| 1-6              | RF11/RS11 System, Block Diagram                      | 11-0241            | 1-3               | 5-2        | Voltage Spectrum of TTL Logic                         | 15-0070 | 5-2        |

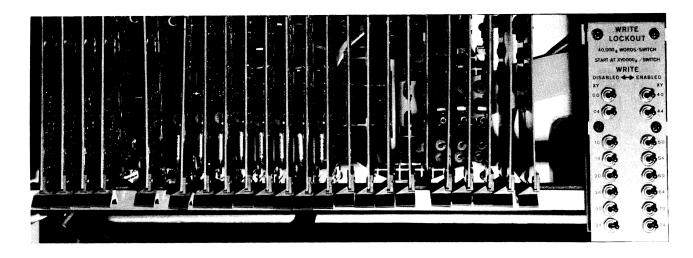

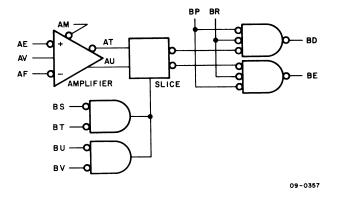

| 2-1              | Write Lockout Switches                               |                    | 2-1               | 5-3        | G085 Disk Read Amplifier and Slice, Block Schematic   | 09-0357 | 5-2        |

| 2-2              | RF11 Indicators                                      | 11-0240            | 2-3               | 5-4        | Disk Read Amplifier and Slice, Parts Location Diagram | 09-0392 | 5-3        |

| 2-3              | 855 Power Control                                    |                    | 2-3               | 5-5        | G285 Series Switch, Block Schematic                   | 09-0356 | 5-3        |

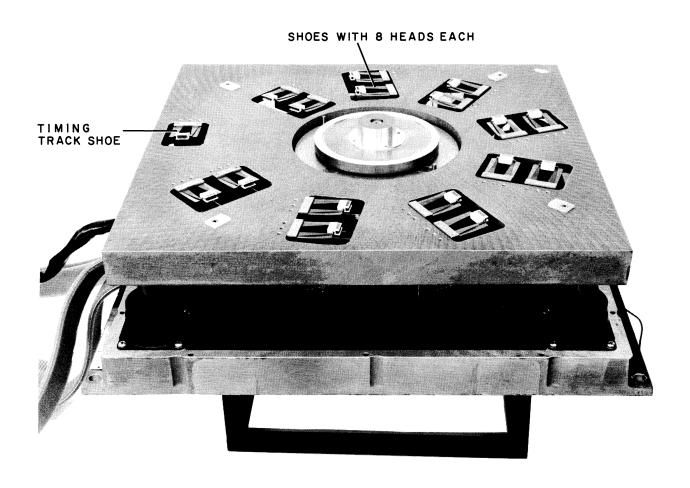

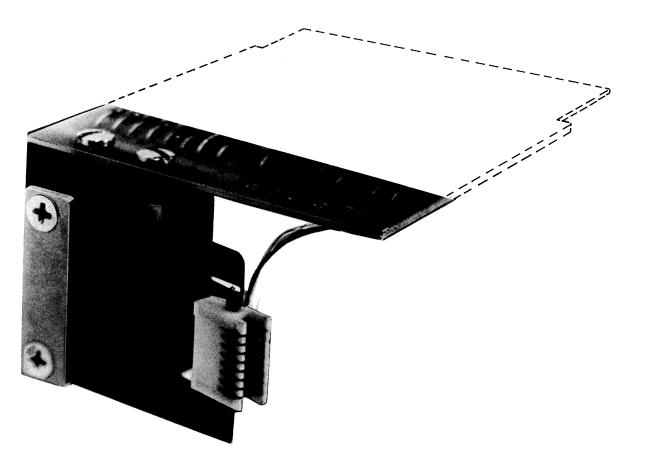

| 4-1              | Disk Assembly with Cover Removed                     |                    | 4-1               | 5-6        | G285 Series Switch, Parts Location Diagram            | 09-0391 | 5-4        |

| 4-2              | Disk Assembly with Cover and Surface Removed         |                    | 4-2               | 5-7        | Centertap Selector, Block Schematic                   | 09-0355 | 5-4        |

| 4-3a             | RS11 Head Assembly                                   |                    | 4-2               | 5-8        | G286 Centertap Selector, Parts Location Diagram       | 09-0389 | 5-4        |

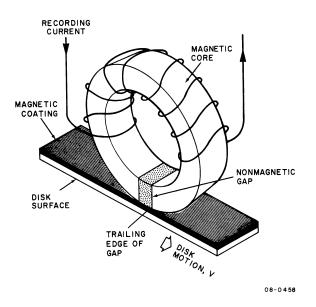

| 4-3b             | Simplified Diagram of the Magnetic Recording Process | 08-0458            | 4-2               | 5-9        | G290 Writer Flip-Flop, Block Schematic                | 09-0354 | 5-4        |

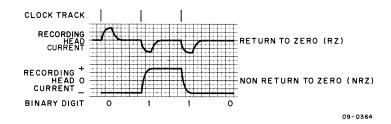

| 4-4              | NRZ and RZ Recording Formats                         | 09-0364            | 4-3               | 5-10       | G290 Writer Flip-Flop, Parts Location Diagram         | 09-0390 | 5-5        |

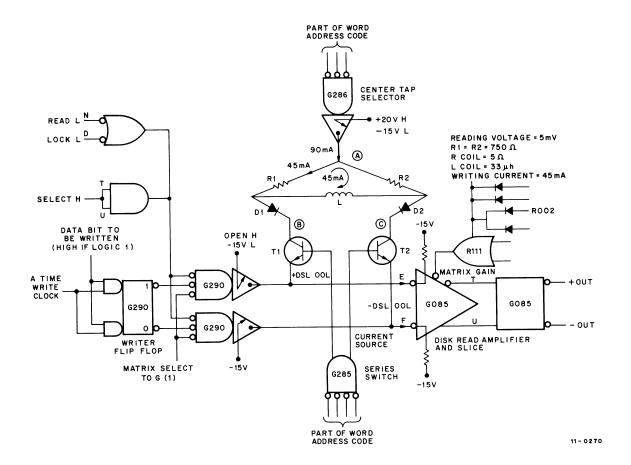

| 4-5              | RS11 Read/Write Electronics                          | 11-0270            | 4-3               | 5-11       | M311 Tapped Delay, Block Schematic                    | 09-0353 | 5-7        |

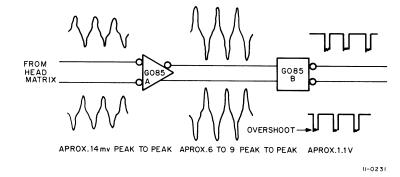

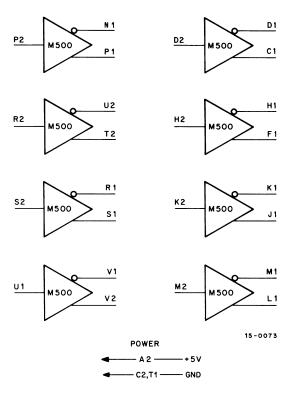

| 4-6              | G085 Slicing Rectifier                               | 11-0231            | 4-3               | 5-12       | M500 Negative Receiver, Block Schematic               | 15-0073 | 5-7        |

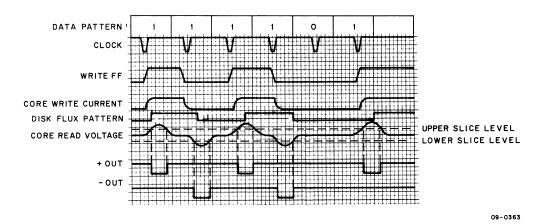

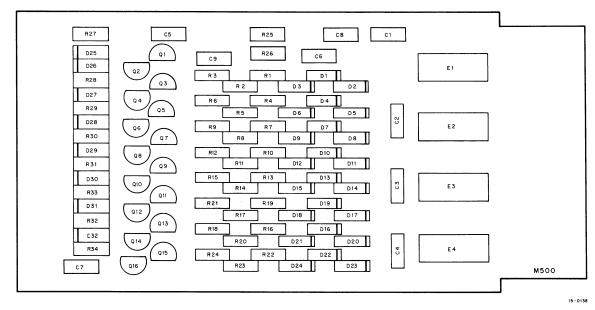

| 4-7              | Read/Write Electronics Waveforms                     | 09-0363            | 4-4               | 5-13       | M500 Negative Receiver, Parts Location Diagram        | 15-0138 | 5-7        |

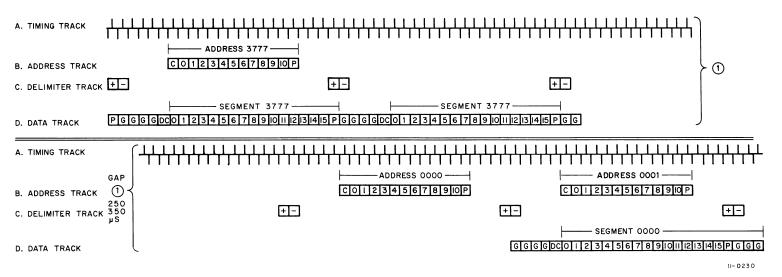

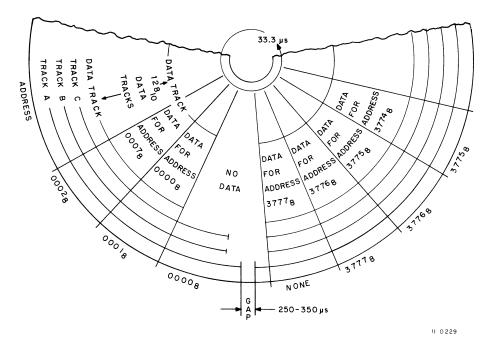

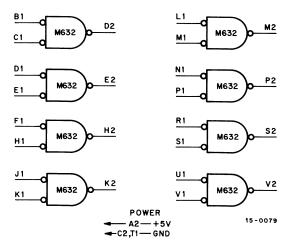

| 4-8              | RS11 Disk Format                                     | 11-0230            | 4-4               | 5-14       | Negative Driver, Block Schematic                      | 15-0079 | 5-8        |

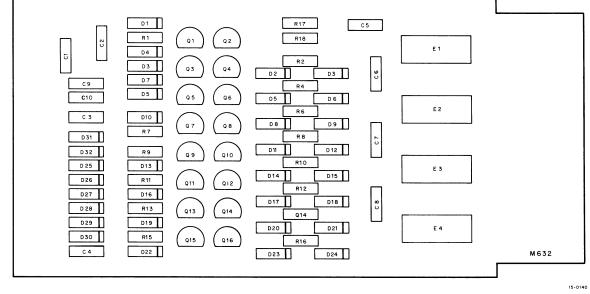

| 4-9              | RS11 Track Layout                                    | 11-0229            | 4-5               | 5-15       | M632 Negative Driver, Parts Location Diagram          | 15-0140 | 5-8        |

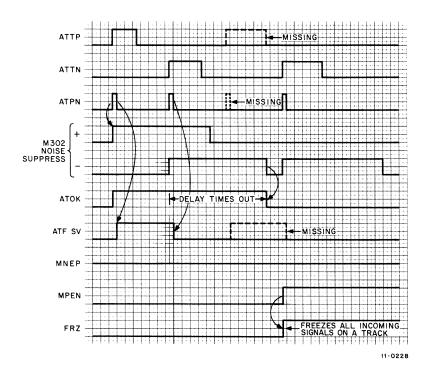

| 4-10             | A Track Error Detection, Timing Diagram              | 11-0228            | 4-5               | 5-16       | M795 Word Count and Bus Address, Block Diagram        | 11-0185 | 5-8        |

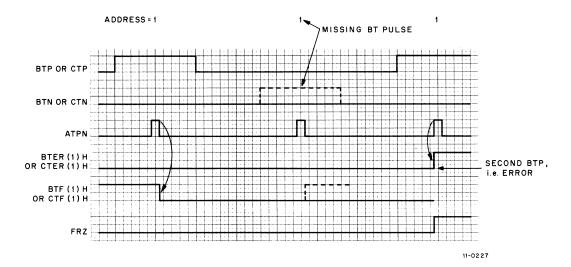

| 4-11             | B and C Track Error Detection, Timing Diagram        | 11-0227            | 4-6               | 5-17       | M796 Block Diagram                                    | 11-0222 | 5-9        |

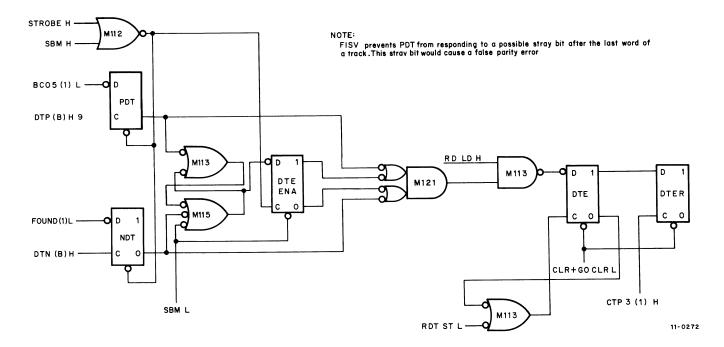

| 4-12             | Data Track Error Detection Logic                     | 11-0272            | 4-6               | 5-18       | DATI Operation                                        | 11-0221 | 5-10       |

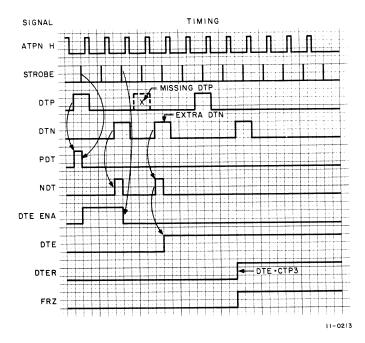

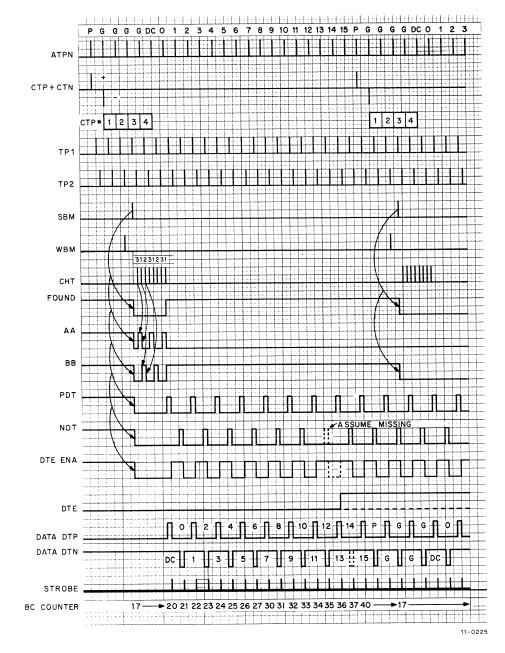

| 4-13             | Data Track Timing Diagram                            | 11-0213            | 4-7               | 5-19       | DATO Operation                                        | 11-0220 | 5-10       |

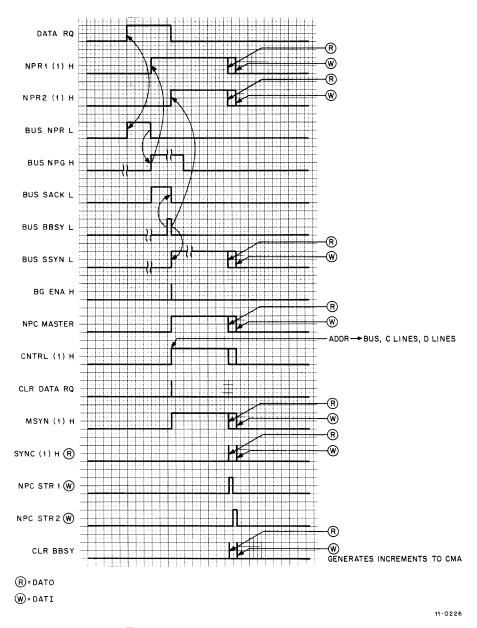

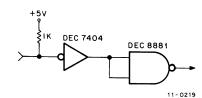

| 4-14             | NPR Logic, Timing Diagram                            | 11-0226            | 4-8               | 5-20       | Noninverting Unibus Driver                            | 11-0219 | 5-11       |

| 4-15             | Timing Generator                                     | 11-0278            | 4-9               | 5-21       | Internal Wire-ORed Bus                                | 11-0219 | 5-11       |

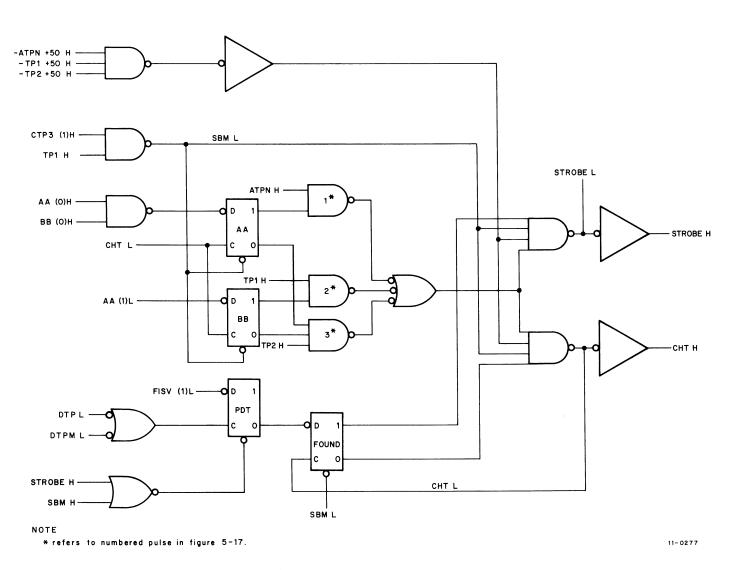

| 4-16             | Self-Clocking Logic                                  | 11-0277            | 4-10              | 5-22       | 705B Power Supply                                     |         | 5-11       |

| 4-17             | Self-Clocking Logic, Timing Diagram                  | 11-0225            | 4-11              | 5-23       | H726A-2 Power Supply, Circuit Schematic               | 11-0212 | 5-13       |

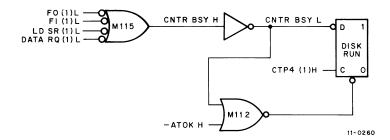

| 4-18             | Unlock Sequence Logic                                | 11-0260            | 4-12              | 6-1        | System Configuration                                  | 11-0218 | 6-1        |

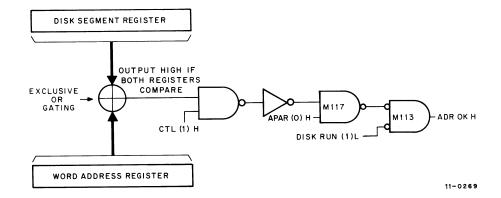

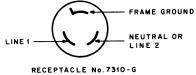

| 4-19             | Equal Comparison Gating                              | 11-0269            | 4-12              | 6-2        | Hubbell Wall Receptacle Connector Diagram             | 09-0414 | 6-2        |

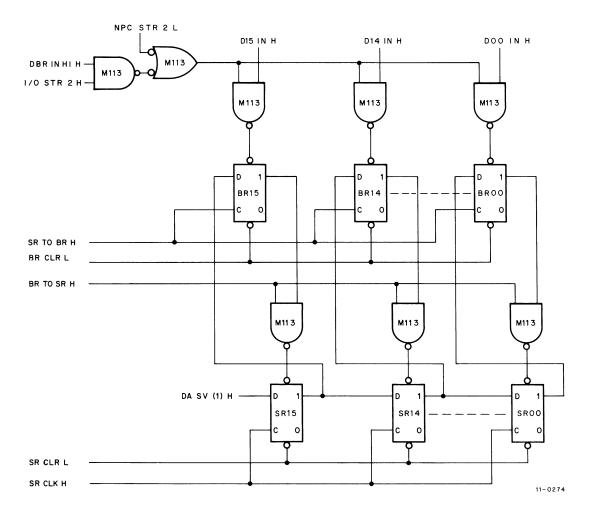

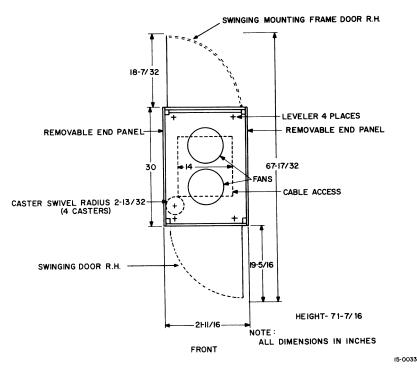

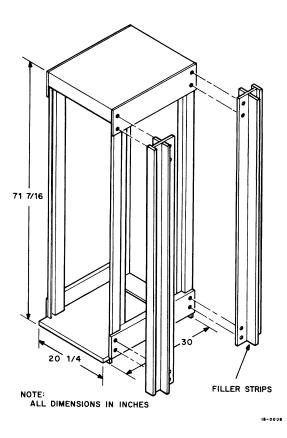

| 4-20             | Buffer Register and Shift Register Interconnections  | 11-0274            | 4-13              | 6-3        | The RF11 Cabinet                                      | 15-0033 | 6-2        |

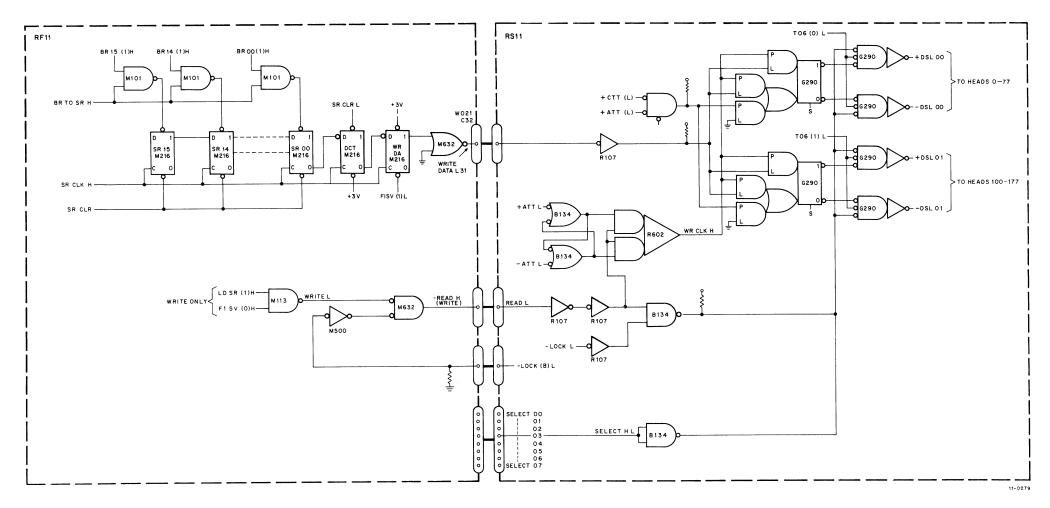

| 4-21             | WRITE Circuitry to RS11                              | 11-0279            | 4-14              | 6-4        | RF11/RS11 Disk System                                 | 11-0275 | 6-4        |

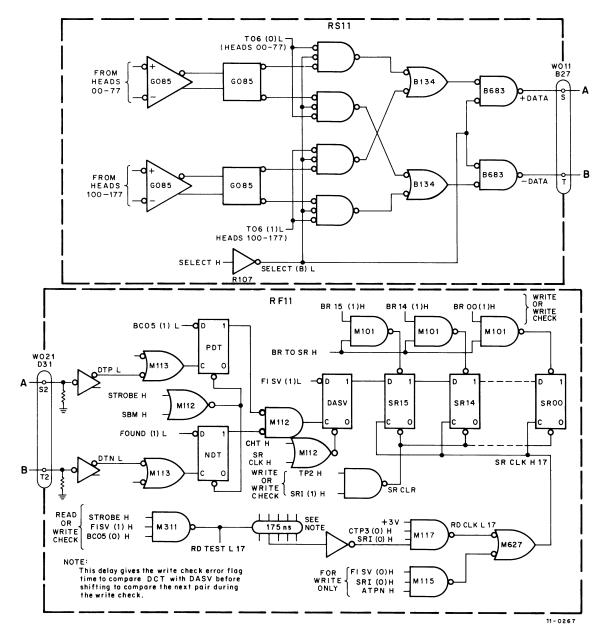

| 4-22             | Read and Write Check SR and RS11 Logic               | 11-0267            | 4-15              | 6-5        | Cabinet Bolting Diagram                               | 15-0098 | 6-5        |

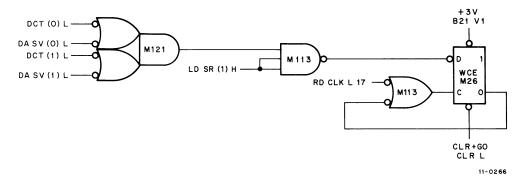

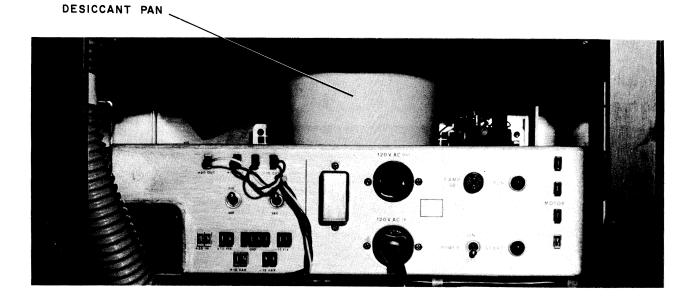

| 4-23             | Write Check Error                                    | 11-0266            | 4-16              | 6-6        | The Disk Assembly with Desiccant Pan                  |         | 6-5        |

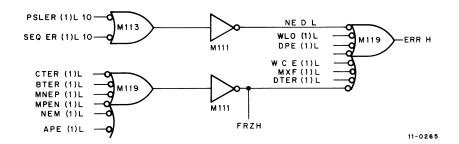

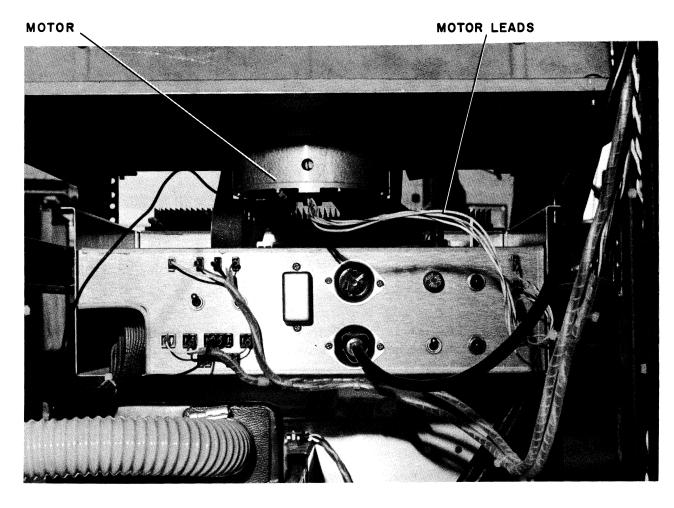

| 4-24             | Error and Freeze                                     | 11-0265            | 4-16              | 6-7        | Disk Assembly with Pan Removed and Motor Leads Con-   |         | 6-6        |

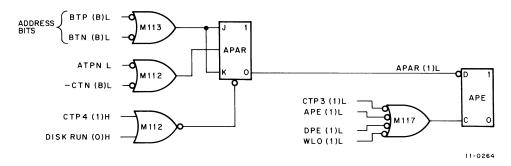

| 4-24<br>4-25     | Address Parity Error                                 | 11-0264            | 4-16              | 0-7        | nected                                                |         | 0-0        |

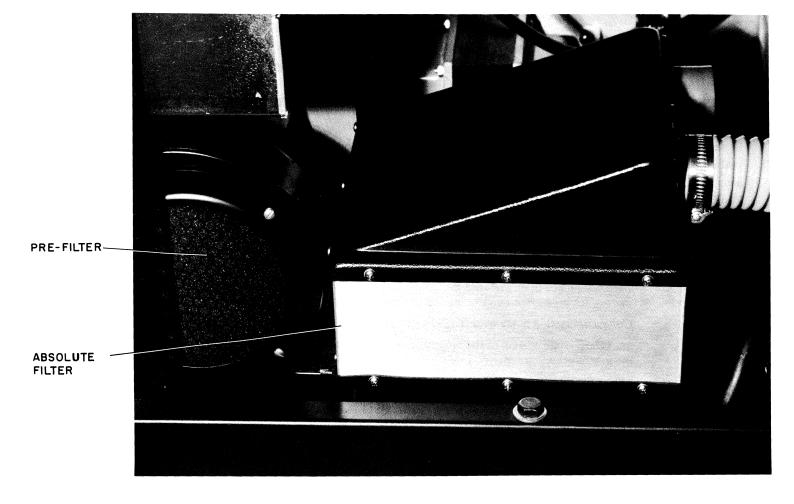

|                  | Missed Transfer Error                                |                    |                   | 7.1        | Purge Unit and Filters                                |         | 7-2        |

| 4-26<br>4-27     | Data Parity Error                                    | 11-0262<br>11-0263 | 4-16<br>4-16      | 7-1<br>7-2 | Average Gain Measurement                              | 11-0217 | 7-2<br>7-2 |

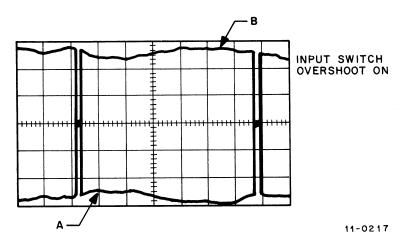

| 4-27             | Write Lockout Error                                  | 11-0203            | 4-10<br>4-17      | 7-2<br>7-3 | Slice Overshoot                                       | 11-0217 | 7-3        |

| 4-28<br>4-29     | Nonexistent Disk by Program Selector Error           | 11-0271            | 4-17<br>4-17      | 7-3<br>7-4 | Average Slice Measurement                             | 11-0216 | 7-3<br>7-3 |

| <del>4-</del> 43 | Moneyigient Disk of Hogiani scienti Elloi            | 11-0239            | <del>7</del> -1 / | /          | Avoiage office measurement                            | 11 0213 | , 3        |

# ILLUSTRATIONS (cont.)

# **TABLES**

| Figure No. | Title                                        | Art No. | Page | Table No. | Title                               | Page |

|------------|----------------------------------------------|---------|------|-----------|-------------------------------------|------|

| 7-5        | Slice Measurement                            | 11-0214 | 7-3  | 1-1       | RF11 Hardware Registers             | 1-2  |

| 7-6        | RS11 Electronics Showing Posted Data         |         | 7-3  | 2-1       | RS11 Controls                       | 2-1  |

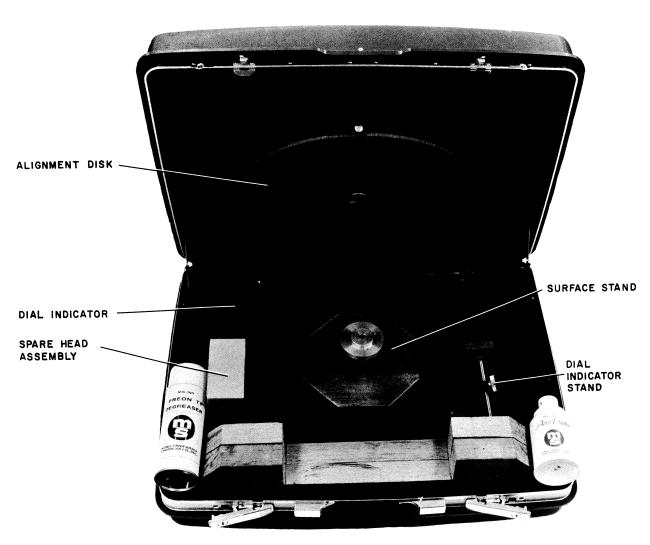

| 7-7        | Disk Assembly Dismantling Kit                |         | 7-5  | 2-2       | RF11 Indicators                     | 2-1  |

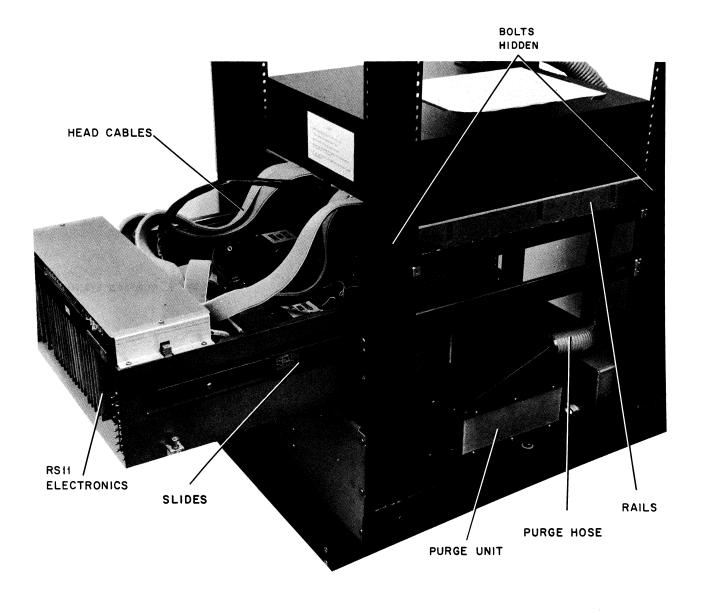

| 7-8        | Removing the Disk Assembly from the Cabinet  |         | 7-6  | 3-1       | Function Code                       | 3-2  |

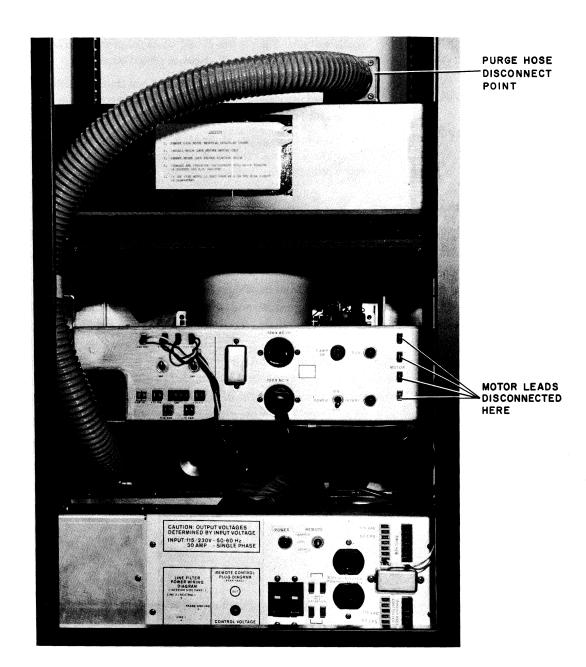

| 7-9        | Disconnecting Motor Leads and Purge Hose     |         | 7-6  | 5-1       | Module Utilization                  | 5-1  |

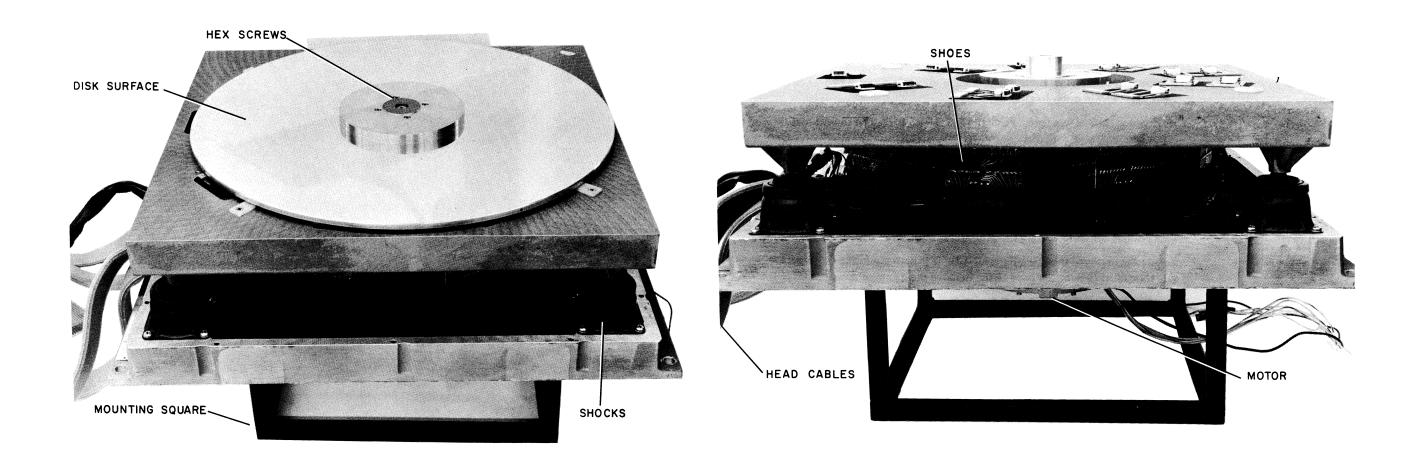

| 7-10       | Disk Assembly with Cover Removed             |         | 7-7  | 5-2       | M795 Input Signals                  | 5-9  |

| 7-11       | Disk Assembly with Cover and Surface Removed |         | 7-7  | 5-3       | M795 Output Signals                 | 5-9  |

| 7-12       | Shoe Assembly Removed                        |         | 7-8  |           |                                     | 6-1  |

| 7-13       | Aligning the Heads                           | 09-0411 | 7-9  | 6-1       | Disk Options                        |      |

| 7-14       | Aligning the Heads                           | 09-0412 | 7-9  | 6-2       | Power Configurations                | 6-2  |

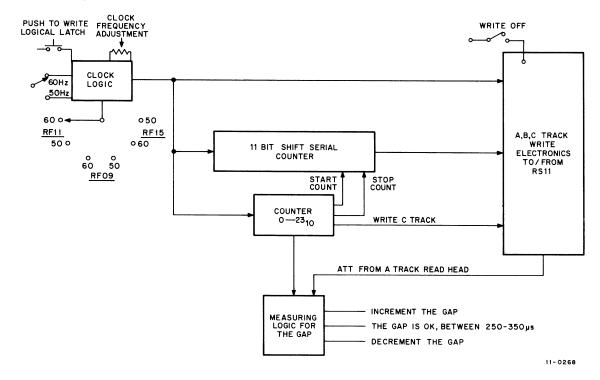

| 7-15       | Timing Track Writer, Block Diagram           | 11-0268 | 7-10 | 6-3       | Weight Configurations               | 6-3  |

| 7-16       | Timing Track Writer                          |         | 7-11 | 6-4       | Modules Required                    | 6-3  |

| 7-17       | Measuring Surface Modulation on the A Track  |         | 7-12 | 7-1       | Visual Inspection Checklist         | 7-1  |

| 7-18       | Maximum Gain, Minimum Slice                  |         | 7-14 | 7-2       | Processor Register Bit Positions    | 7-2  |

| 7-19       | Minimum Gain, Maximum Slice                  |         | 7-14 | 7-3       | On-Line Static Program Requirements | 7-4  |

| 7-20       | RS11 Test Data Sheet                         |         | 7-15 | 7-4       | Jumpers to Increase Gain            | 7-13 |

# **FOREWORD**

This manual provides the user with the theory of operation and logic diagrams necessary to understand and maintain the RF11/RS11 DECdisk System. General and detailed descriptions of the RF11 Control and the RS11 Disk are included. It is assumed that the reader is familiar with basic PDP-11 operation.

Although control signals and data are transferred between the RF11 Control and the Unibus , it is beyond the scope of this manual to cover the operation of the Unibus. A detailed description of the Unibus is presented in the *PDP-11 Unibus Interface Manual* (DEC-HIAA-D).

The manual is divided into 6 major sections: general description, installation, operation, programming, detailed description and maintenance. The appendix contains the RF11/RS11 signal designations and definitions.

A complete set of engineering drawings is provided with each RF11/RS11 DECdisk System. These drawings are contained in a separate volume entitled RF11/RS11 DECdisk System, Engineering Drawings and reflect the latest print revisions which correspond to the specific system shipped to the user.

Unibus is a trademark of Digital Equipment Corporation.

|  | , |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

# CHAPTER 1 RF11/RS11 GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

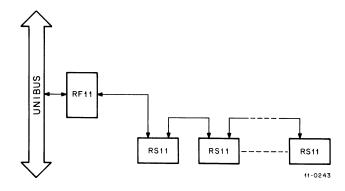

The RF11/RS11 DECdisk System is a PDP-11 Computer peripheral. The RF11/RS11 serves as an additional random access memory unit to the PDP-11 System. Each RF11/RS11 Disk System consists of an RF11 Controller and from one to eight optional RS11 Disk units. The RF11 Controller interfaces the RS11 Disk unit or units to the Unibus. The RF11 also converts the serial data off the RS11s to parallel data on the Unibus and vice versa. Therefore, the RF11/RS11 Disk System reads and writes serial memory information in parallel transfer to or from the PDP-11 Unibus.

#### 1.2 FUNCTIONAL DESCRIPTION

The RF11 Control and the RS11 Disk combine as a fast, low-cost, random access, bulk storage package for the PDP-11 Computer. The system stores digital data on fixed-head rotating disks in a serial format. The data can be randomly accessed and, when necessary, protected from overwriting. One RS11 and the RF11 provide 262,144 (2<sup>18</sup>) 17-bit words (16 data bits and one parity bit) of storage. Up to eight RS11 disks can be controlled by one RF11 for a total of 2,097,152 (2<sup>21</sup>) words of storage. The RS11 units are interfaced with the RF11 by the parallel disk bus that carries both control and data information (see Figure 1-1).

Figure 1-1 RF11/RS11 DECdisk Interface Block Diagram

## 1.2.1 RS11 Disk Unit

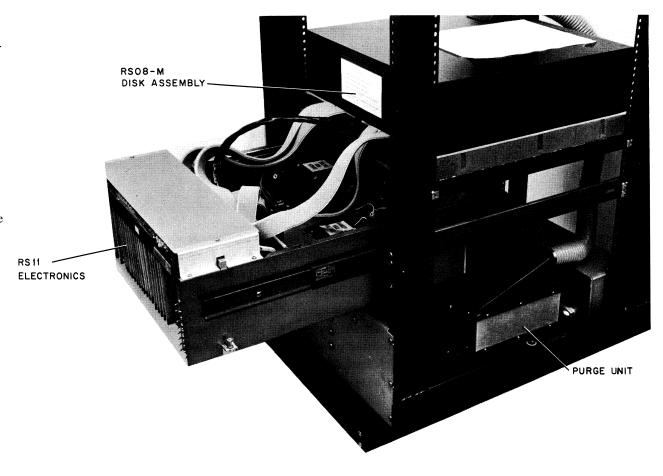

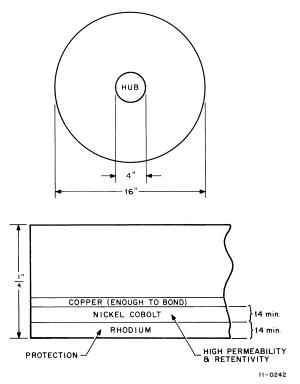

The RS11 Disk unit contains a nickel-cobalt-plated disk that is driven by a hysterisis synchronous motor (see Figure 1-2). Data is recorded on a single rotating disk surface by 128 fixed read/write heads. Each read/write head covers a separate track on the nickel-cobalt surface (see Figure 1-3); thus disk action is similar to the operation of

Figure 1-2 RS11 Disk Unit

many circular tapes running simultaneously in continuous loops. Each track on the disk can store 2048 16-bit words. As a track fills, the system automatically moves to the next track. The disk rotates at 1800 rpm (60-Hz power) and, therefore, can transfer a word every  $16 \mu s$ . To achieve random access storage, each disk is logically segmented into 2048 slices or words; each slice is preassigned a number or address from 1 to  $3777_8$ . Therefore, the RF11 Control, in response to the computer, can select, at random, any track of a disk and any address along that track to read or write a word.

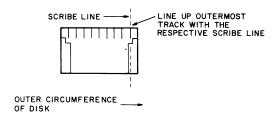

Figure 1-3 RS11 Disk Surface

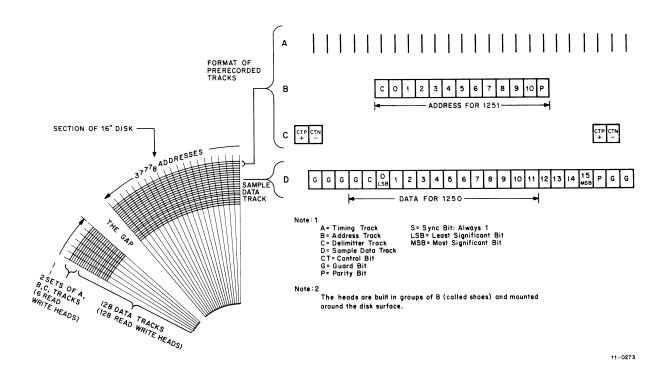

The RS11 Disk surface recording format (see Figure 1-4) consists of 2048 22-bit segments or addresses per track. A 16-bit word is stored in a 22-bit segment. A 2049th segment, called a gap, is provided to give the track selection matrix time to switch tracks. This segment has no address and stores no data or timing; it is used as a marker to notify the RF11 Control after a complete revolution. In addition to storing one 16-bit word, each data segment includes four guard bits, a parity bit, and a sync bit or control bit that operates the self-clocking logic of the RS11 Disk logic for reliable data recovery. The control bit adjusts the timing of the data strobing to ensure proper recovery of each word of data. Each 16-bit word is identified by an address that is prerecorded at the factory on a special track on the disk's surface. This address is recorded serially on the B track, exactly one word before the data word with which it is associated (see Figure 1-4). The word address can then be assembled and identified before the heads reach the word itself. Each address is 13-bits long: 11 bits supply addressing data, one bit is a control bit, and one bit is a parity bit. There are five additional prerecorded tracks on the disk surface. The A track is a prerecorded track that consists of timing pulses 720-ns apart; these pulses are used to develop a strobe to clock data into or out of the data tracks. The C track is used to delimit each word unit. The RF11 Control uses the C track to see when a word has been assembled or written. This enables the RF11 to communicate with the Unibus for data transfer at the proper time. Each of the three prerecorded tracks described – the A, B, and C tracks – are copied on three spare tracks that are used if one of the original tracks is accidentally erased. If the spare tracks are damaged, all the timing tracks can be rewritten in the field with a special timing track writer (see Paragraph 7.3.3.5). The remaining 128 data tracks on the RF11 Disk unit are used for data serially formatted in 22-bit word format.

#### 1.2.2 RF11 Control Unit

The RF11 Control unit (see Figure 1-5) serves as the interface between the RS11 disks and the PDP-11 Unibus. Basically, the RF11 performs five functions: error detection, data conversion (serial-to-parallel for a disk Read

Figure 1-4 RS11 Disk Surface Recording Format

and parallel-to-serial for a disk Write), Unibus data transfer supervision, disk position monitoring, and system maintenance. The RF11 directly connects to the Unibus and communicates with the processor for status and control information. For data information, the RF11 communicates directly with memory without processor supervision. This is called a non-processor request (NPR) data transfer.

The RF11 contains eight 16-bit hardware registers for communication with the processor and memory. These registers and their respective address assignments are listed in Table 1-1. These device registers initiate all software control of the RF11 and can be read or written into using software instructions that refer to their address. A detailed description of the registers and their bit assignments is presented in Chapter 4. Figure 1-6 shows the functional block diagram of the RF11/RS11 System.

Table 1-1 RF11 Hardware Registers

| Register                        | Address |

|---------------------------------|---------|

| Disk Control Status (DCS)       | 777460  |

| Word Count (WC)                 | 777462  |

| Current Memory Address (CMA)    | 777464  |

| Disk Address (DAR)              | 777466  |

| Disk Address Ext. & Error (DAE) | 777470  |

| Disk Data Buffer (DBR)          | 777472  |

| Maintenance (MA)                | 777474  |

| Address of Disk Segment (ADS)   | 777476  |

The MA register is provided as a maintenance tool.

Figure 1-5 RF11 Control Unit

Through the data transfer control function, the software operating system initializes the RF11 Control by selecting the RS11 Disk to be used, the track address within that disk (Data Track Matrix) to be used, and the first address within the track to be used. Also, it initializes the number of words to be transferred (WC) and the location in core that the transfer is to be made (CMA). One of three operations is then selected: Read the disk; Write on the disk; or Write Check what has already been written. The data conversion function assembles the word off the selected track for a Read operation, or writes the word bit by bit onto the track during a Write operation. When called for by the software system, a Write Check operation compares data in memory with corresponding data on the disk to check for a discrepancy in a Write operation. The data conversion function also notifies the control

Figure 1-6 RF11/RS11 System, Block Diagram

logic when it needs control of the Unibus (NPR) after it has assembled a word or needs another word to write, and the data is transferred to the Unibus. The system maintenance function simulates either the disk surface head signals or the RS11 output signals and is used exclusively for testing the RF11/RS11 System. Detailed coverage of the maintenance function is found in Chapter 7.

#### 1.3 SPECIFICATIONS

The RF11/RS11 System specifications are grouped into six general areas: physical description, environmental limits, logic format, timing format, power requirements, and heat output.

#### 1.3.1 Physical Description

RF11/RS11 System housing is provided by a cabinet designed to accommodate one RF11 and up to two RS11s and a power supply. Six additional RS11s can be mounted in two additional cabinets without additional power supplies. Other equipment should not be mounted in the RS11 Disk System cabinets.

Cabinet Dimensions: Height: 71-7/16 in.

Width: 21-11/16 in. Depth: 30 in.

Shipping Information: Weight of RF11, one RS11, power supply, and cabinet.

590 lbs (crated) 500 lbs (uncrated)

Weight of RF11, two RS11's, power supply, and cabinet.

690 lbs (crated) 600 lbs (uncrated)

(The RF11/RS11 systems are shipped mounted in cabinets.)

#### 1.3.2 Environmental Limits

The environmental limits required for proper operation of the RF11/RS11 System are listed below.

Temperature: (Operating) 65° to 90°F

Relative Humidity: (Operating) 20% to 55% Condensation: (Operating or Storage) None

Vibration/Shock: (Operating) Good isolation is provided. To prevent data errors, extreme vibra-

tions should be avoided while the RS11 is transferring information.

#### 1.3.3 Logic Format

The logic format pertaining to data transfer and data storage in the RF11/RS11 System is listed below.

Disks: Eight RS11 Disks may be controlled by one RF11 for 2,097,152 16-bit words.

Tracks: Each RS11 has 128 data tracks and six timing tracks.

Words: Each data track includes 2048 data words.

Word Format: Data words are recorded in 22 bits.

Bits: Each word contains 16 data bits, four guard bits, one parity bit, and one sync bit. The guard bits are always 0 and the sync bit is always 1.

·

Recording Method: NRZI

Density: Maximum recording density is 1900 bpi.

Words per Disk: 262,144

Control Tracks: Each disk contains three timing tracks plus three spares (spares can be used to re-

cover data on disk). The three tracks are the A track (timing), B track (address-

ing), and the C track (delimiter or control).

Data Transfer Path: Unibus (When the RF11 is bus master, direct memory access (DMA) is per-

formed.)

Priority Interrupt: The RF11/RS11 has a priority level of BR5 and a interrupt vector address of

204. (However, the priority level is selectable.)

## 1.3.4 Timing Format

The various operation times and timing features of the RF11/RS11 System are listed below.

Data Transfer Rate: (DMA) 16 \mu s per word (60-Hz power) 19.2 \mu s per word (50-Hz power)

Access Time: For 60-Hz power:

Minimum Access Time:  $258 \mu s$ Average Access Time: 16.9 msMaximum Access Time: 33.6 ms

For 50-Hz power:

Minimum Access Time: 258 μs Average Access Time: 20.3 ms Maximum Access Time: 40.3 ms

NPR Transfers: Maximum Latency: 12 μs

Maximum Delay: 3 disk revolutions at 1800 rpm

Self-Clocking: The RF11 employs self-clocking keyed by the control bit in a data word on a data

track for reliable data recovery.

#### 1.3.5 Power Requirements

The power requirements pertaining to the logic and the RS11 motor in the RF11/RS11 system are listed below.

Power Requirements:  $115/230 \pm 10\%$  Vac, single phase,  $50 \pm 2$  or  $60 \pm 2$  Hz; for a one disk system,

starting current of 14A, nominal current of 6.5A; for a eight disk system, starting current of 81A, nominal current of 21A. Power starting currents

can be realized if disks are in sequence.

RS11 Motor Power Requirements: Specifications are the same as those for logic power, except

additional line current is required. Motor start, 5.5A for 20 ±3 s. Motor run, 4.0A continuous at 115 Vac. (A stepdown autotransformer is provided for 230 Vac operation.)

Line Frequency Stability: Maximum line frequency drift is 0.1 Hz/s. A constant frequency

motor-generator set or static ac/ac inverter should be provided for in-

stallations with unstable power sources.

Motor Bearing Life: Expected operating life of at least 20,000 hours, under standard computer

environment.

Power Supplies: One H726A-2 Power Supply for RF11 logic. One 705B Power Supply for level

converters and up to eight RS11 disk logic sets. One 716 power supply for in-

dicator panel.

One 855 Line Filter for disk motors.

# 1.3.6 Power Dissipation

Power dissipation is dependent on the number of disks in the system; it varies from 0.75 kW (2550 btu/hr) for a one disk system to 2.42 kW (8230 btu/hr) for an eight disk system.

#### 1.4 RELATED DOCUMENTS

This section provides a list of documents, related to the RF11/RS11 System, that pertain to its use as a peripheral of the PDP-11 Computer.

| Title                                       | Number                  | Description                                                                                                                                                                                                                      |

|---------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             |                         | General                                                                                                                                                                                                                          |

| PDP-11 Handbook                             | Second Edition,<br>1970 | Discussion of overall system, addressing modes, and basic instruction set from a programming point of view. Some interface and installation data.                                                                                |

| Instruction List                            | None                    | Pocket-size list of instructions. Lists group names, functions codes, and bit assignments. Includes ASCII codes and the bootstrap loader.                                                                                        |

| Logic Handbook                              | DEC, 1970               | Presents functions and specifications of the M-series logic modules and accessories used in PDP-11 interfacing. Includes other types of logic produced by DEC but not used with the PDP-11.                                      |

|                                             |                         | Hardware                                                                                                                                                                                                                         |

| Unibus Interface Manual                     | DEC-11-HIAB-D           | Used in conjunction with this manual; provides detailed theory, flow, and logic descriptions of Unibus and external device logic. Discusses methods of interface construction and provides examples of typical interfaces.       |

| PDP-11/20 System                            | DEC-11-HR1A-D           | Introduction, general description, specifications of entire PDP-11/20 system. Also contains operating procedures and controls and indicators for both PDP-11 and Teletype.                                                       |

| KA11 Processor                              | DEC-11-HR2A-D           | Block diagram discussion, detailed theory of operation related to flow diagrams, instruction set, module descriptions and related logic diagrams, maintenance and adjustments.                                                   |

| MM11-E Core Memory                          | DEC-11-HR3A-D           | General discussion, detailed theory of operation, bus transactions, adjustments, maintenance aids, and logic drawings.                                                                                                           |

| KL11 Teletype Control                       | DEC-11-HR4A-D           | Theory of operation, adjustment and calibration, programming data, maintenance aids, and logic drawings.                                                                                                                         |

| H720 Power Supply & Mounting Box            | DEC-11-HR5A-D           | Power supply block diagram discussion, theory of operation, circuit diagrams.                                                                                                                                                    |

|                                             |                         | Mounting box description and specifications for all models and cabinets. Includes installation information.                                                                                                                      |

| KY11-A Programmer's<br>Console              | DEC-11-HR7A             | General description, flow diagram discussion, module description and related logic diagram. Operation and controls & indicators covered in <i>PDP-11/20 System Manual</i> .                                                      |

| PDP-11 Conventions                          | DEC-11-HR6A-D           | <ul> <li>a. General Maintenance</li> <li>b. Logic Symbology</li> <li>c. Drawing Set Explanation</li> <li>d. Processor Signals</li> <li>e. Product Identification Codes</li> <li>f. Glossary</li> <li>g. Abbreviations</li> </ul> |

|                                             |                         | Software                                                                                                                                                                                                                         |

| Paper Tape Software<br>Programming Handbook | DEC-11-GGPA-D           | Detailed discussion of the PDP-11 software system used to load, dump, edit, assemble and debug PDP-11 programs.  Also includes discussion of input/output programming and the floating-point and math package.                   |

# CHAPTER 2 RF11/RS11 OPERATION

## 2.1 INTRODUCTION

Basic operation of the RF11/RS11 Disk System is accomplished through the PDP-11 software and the RF11 device registers. However, only the operation of the RF11/RS11 is pertinent to this manual.

# 2.2 CONTROLS AND INDICATORS

The RF11/RS11 controls and indicators consist of RS11 controls and RF11 indicators, respectively. The RS11 controls are the WRITE LOCK SWITCHES of the RS11 Disk unit. The RF11 indicators are located on the indicator panel of the master cabinet. The 855 Power Control contains the controls for the system's power supplies.

## 2.2.1 RS11 Controls

Each RS11 Disk unit contains a set of sixteen switches designated WRITE LOCK SWITCHES. These switches are capable of locking out any combination of sixteen 16,384 word blocks (8 tracks) (refer to Table 2-1). Each switch can inhibit the computer from overwriting on eight separate tracks (see Figure 2-1). A write locked-out disk will cause an error flag (WLO) to be set when an attempt is made to write on a locked-out section.

Table 2-1

RS11 Controls

|                                              | Track                                                                       |                                                                                                      |          |  |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------|--|--|--|

| Switch                                       | Decimal                                                                     | Octal                                                                                                |          |  |  |  |

| 00<br>04<br>10<br>14<br>20<br>24<br>30<br>34 | 0-7<br>8-15<br>16-23<br>24-31<br>32-39<br>40-47<br>48-55<br>56-63           | $ \begin{pmatrix} 0-7 \\ 10-17 \\ 20-27 \\ 30-37 \\ 40-47 \\ 50-57 \\ 60-67 \\ 70-77 \end{pmatrix} $ | Matrix O |  |  |  |

| 40<br>44<br>50<br>54<br>60<br>64<br>70<br>74 | 64-71<br>72-79<br>80-87<br>88-95<br>96-103<br>104-111<br>112-119<br>120-127 | 100-107<br>110-117<br>120-127<br>130-137<br>140-147<br>150-157<br>160-167<br>170-177                 | Matrix I |  |  |  |

Figure 2-1 Write Lockout Switches

#### 2.2.2 RF11 Indicators

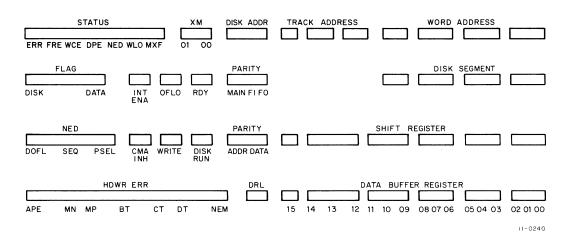

The RF11 indicator panel shows the states of most of the register bits, along with some flip-flop states. These indicators are divided into address and error indicators (refer to Table 2-2) and are labeled on the panel (see Figure 2-2) as to the bit and the register, or to what the bit or flip-flop defines.

Table 2-2 RF11 Indicators

| Indicator Function |                                                                                                                                                            |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Address Indicators |                                                                                                                                                            |  |  |  |

| Disk Segment       | The dynamic shift register that assembles the serial address from the disk. If these indicators are dimly lit, the disk is communicating with the control. |  |  |  |

| Word Address       | Displays bits 00 through 10 of the DAR register and indicates the segment on the disk a transfer is to be made to or from.                                 |  |  |  |

| Track Address      | Displays bits 11 through 15 of the DAR and bits 00 and 01 of the DAE registers.  (continued on next page)                                                  |  |  |  |

Table 2-2 (Cont) RF11 Indicators

| Indicator | Function                                                                                                                                                                                                                                                                         |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Address Indicators (Cont)                                                                                                                                                                                                                                                        |

| Disk ADDR | Displays bits 02 through 04 of the DAE register and indicates the disk unit selected.                                                                                                                                                                                            |

| XM        | EXtended Memory bits. Indicates A16 and A17 on the Unibus when the control is Bus Master.                                                                                                                                                                                        |

|           | Error Indicators                                                                                                                                                                                                                                                                 |

| ERR       | ERRor. Indicates that an error exists in the control. If FRZ is not lit, it is a "soft" error.                                                                                                                                                                                   |

| WCE       | Write Check Error. Indicates that the control was performing a WRITE CHECK command and the word read from the disk did not compare with the word taken from core. Causes ERR to light.                                                                                           |

| DPE       | Data Parity Error. Indicates that the data being read from the disk did not compare with the computed parity. Causes ERR to light.                                                                                                                                               |

| DT        | Data Timing Error. Indicates that the data word has missing or extra bits. Causes ERR to light.                                                                                                                                                                                  |

| NED       | NonExisting Disk. Causes ERR to light.                                                                                                                                                                                                                                           |

| DOFL      | Disk OverFLow. Indicates that the control sequenced into disk $10_8$ .                                                                                                                                                                                                           |

| SEQ       | SEQuence Error. Indicates the control sequenced into a non-existing disk in the system.                                                                                                                                                                                          |

| PSEL      | Program SELect Error. Indicates the program selected a non-existing disk.                                                                                                                                                                                                        |

| WLO       | Write LockOut. Indicates the control tried to write into a write-protected area of the disk. A WLO switch on the RS11 chassis is enabled. Causes ERR to light.                                                                                                                   |

| MXF       | Missed XFer. Indicates the control was unable to perform a transfer for three revolutions of the disk. Caused by the processor halting or ignoring an NPR request, failure of the control to find the disk address, or failure of the control to find data. Causes ERR to light. |

| DRL       | Data Request Late. Indicates the control is ready to transfer data and the previous data has not been taken. Does not stop the current function or cause an error.                                                                                                               |

| FRZ       | FReeZe. Indicates a "hard" error occurred in the control. Causes ERR to light.                                                                                                                                                                                                   |

| APE       | Address Parity Error. Indicates that the address being read from the disk did not compare with the computed parity.  Causes FRZ to light.                                                                                                                                        |

Table 2-2 (Cont) RF11 Indicators

| Indicator                                                               | Function                                                                                                                                                                                   |  |  |  |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                         | Error Indicators (Cont)                                                                                                                                                                    |  |  |  |

| MN                                                                      | Missing Negative or extra positive pulses from the A Timing Track. Causes FRZ to light.                                                                                                    |  |  |  |

| MP                                                                      | Missing Positive or extra negative pulse from the A Timing Track. Causes FRZ to light.                                                                                                     |  |  |  |

| ВТ                                                                      | B Timing Track error. Indicates that there was an extra or missing pulse from the B Track. Causes FRZ to light.                                                                            |  |  |  |

| СТ                                                                      | C Timing Track error. Indicates that there was an extra or missing pulse from the C Track. Causes FRZ to light.                                                                            |  |  |  |

| NEM                                                                     | NonExisting Memory. Indicates the control put an address on the Unibus for which no Slave Sync returned for 20 $\mu$ s. Causes FRZ to light.                                               |  |  |  |

|                                                                         | Additional Indicators                                                                                                                                                                      |  |  |  |

| FCTN                                                                    | FunCTioN register. Indicates the functions being performed                                                                                                                                 |  |  |  |

|                                                                         | by the control; for maintenance functions, the disk signals must be simulated by the program. Fo lit indicates a Write. Fo and F1 lit indicates a Write Check. F1 lit indicates a Read.    |  |  |  |

| PARITY                                                                  |                                                                                                                                                                                            |  |  |  |

| ADDR                                                                    | Indicates the parity of the disk addresses read from the disk surface.                                                                                                                     |  |  |  |

| DATA Indicates the parity of the data word being read from the surface. |                                                                                                                                                                                            |  |  |  |

| FLAG                                                                    |                                                                                                                                                                                            |  |  |  |

| DISK                                                                    | Indicates that an error condition exists in the control or that the control is ready to execute a function. If INT ENA is set, the control raises an Interrupt on the BR-5 level.          |  |  |  |

| DATA                                                                    | Indicates that the control is making an NPR request.                                                                                                                                       |  |  |  |

| INT ENA                                                                 | INTerrupt ENAble. Indicates that the control is conditioned to raise an Interrupt when Disk Flag is asserted.                                                                              |  |  |  |

| CMA INH                                                                 | Current Memory Address INHibit. Indicates that the program has selected a one-word transfer location in core. This prevents the CMA register from incrementing by two after each transfer. |  |  |  |

| OFLO                                                                    | OverFLOw. Indicates that the control has completed a block of transfers and that the Word Count register has gone to 0.                                                                    |  |  |  |

| WRITE                                                                   | Indicates that the control is turning on the writers in the RS11.                                                                                                                          |  |  |  |

| DISK RUN                                                                | Indicates that the control is performing a transfer with the disk.                                                                                                                         |  |  |  |

| RDY                                                                     | ReaDY. Indicates the control is ready to perform a function.  RDY is the complement of the CONT BUSY signal in the control.                                                                |  |  |  |

Figure 2-2 RF11 Indicators

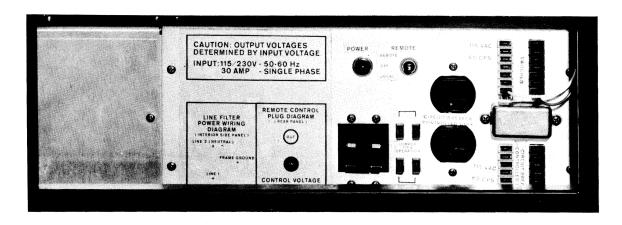

# 2.2.3 855 Power Control

The 855 Power Control accepts a 30A power cord at either 115 or 230 Vac, filters the voltage, and delivers the voltage to either a switched or an unswitched output. A circuit breaker at the input controls all power. The switched output can be controlled locally or remotely by setting the LOCAL REMOTE, OFF switch. Both sides of the ac line are switched. Figure 2-3 shows the unit and drawing C-CS-855-0-1 shows its circuit schematic. Descriptions of the power supplies are contained in Chapter 5.

Figure 2-3 855 Power Control

| • |  |  |  |  |  |

|---|--|--|--|--|--|

|   |  |  |  |  |  |

|   |  |  |  |  |  |

|   |  |  |  |  |  |

|   |  |  |  |  |  |

|   |  |  |  |  |  |

|   |  |  |  |  |  |

|   |  |  |  |  |  |

|   |  |  |  |  |  |

# CHAPTER 3 PROGRAMMING

# 3.1 INTRODUCTION

This chapter presents the software interface of the RF11; this includes the device registers and the data format. Finally, programming examples are included to illustrate basic RF11 operation and the functions of the software interface.

## 3.2 DEVICE REGISTERS

All RF11 software control is done with the eight device registers. These registers are assigned memory addresses and can be read or written into (with the exceptions noted) using instructions that refer to the respective register address. The eight device registers and their bit assignments are listed in the following paragraphs. Unassigned and write only bits are always read as 0's. Loading unassigned or read only bits has no affect on the bit. The INIT signal refers to the initialization signal issued by the processor.

# 3.2.1 Disk Control Status Register (DCS – 777460)

| Bit |                                                | Description and Operation                                                                                                                                                                                                                                                                                                                                                      |

|-----|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | ERROR (ERR) Read Only. Interrupts if INT ENA=1 | Logical OR of status bits 09–14 of DCS register. Set if any of the above bits are 1. Cleared if all of the above bits are 0. Causes the control to terminate present function. Will interrupt the program if INT ENA (bit 6 of DCS) is set. Status bits 09–13 indicate recoverable errors ("soft errors"). The program can continue from this condition by setting the GO bit. |

| 14  | FREEZE (FRZ) Read Only. Sets ERROR (Bit 15)    | Logical OR of status bits 10 and 12–15 of DAE register. Set if any of the above bits are 1. Cleared when all of the above bits are 0. Causes the control to terminate present function and disables the disk timing within the control. Freezes the control for further evaluation and sets ERROR (DCS bit 15).                                                                |

|    |                                                        | •                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13 | WRITE CHECK ERROR (WCE) Read Only. Sets ERROR (Bit 15) | Set when a comparison error exists between the word read from memory and the word read from the disk during WRITE CHECK. Cleared by INIT, DISK CLEAR or GO. The disk address of the word in error is the contents of the DAR (bits 00–10) minus one. The word in error is found in memory location CMA-4 or CMA-2 if the error occurred in the last word transferred.                                       |

| 12 | DATA PARITY ERROR (DPE) Read Only. Sets ERROR (Bit 15) | Set when the data parity does not agree with the computed parity of the data word just read. The control transfers the word containing the parity error and sets the error flag. Cleared by INIT, DISK CLEAR, or GO. The disk address of the word in error is the contents of the DAR (bits 00–10) minus one. The word in error is found in memory location CMA-2.                                          |

| 11 | NONEXISTENT DISK (NED) Read Only. Sets ERROR (Bit 15)  | Set when any disk called for or sequenced into does not exist. Cleared by INIT and DISK CLEAR, or if a new disk address is loaded the operation can be continued by setting GO. The address of the nonexisting disk is found in the DAE (bits 02–04). If bit 05 of the DAE is set, disk 10 <sub>8</sub> was sequenced into.                                                                                 |

| 10 | WRITE LOCKOUT (WLO) Read Only. Sets ERROR (Bit 15)     | Set when attempting to write into a Write Protected address. Cleared by INIT, DISK CLEAR, or GO. The memory location of the word not written is CMA-2. DAR (bits 00–10) contains the disk address of the word not written. Reading or Write Check in a write protected area is permitted. Protection is provided by each disk, in increments of 16,384 words, via 16 toggle switches on each disk assembly. |

| 09 | MISSED TRANSFER (MXF) Read Only. Sets ERROR (Bit 15)   | Set when disk was busy and missed transferring data twice in succession from the same address. (More than one disk revolution occurred without a transfer.) Cleared by INIT, DISK CLEAR, or GO. Indicates failure in control or an overloaded NPR facility.                                                                                                                                                 |

| 08 | DISK CLEAR<br>Write Only                               | This bit initializes (power clear) the disk control when set.                                                                                                                                                                                                                                                                                                                                               |

|    |                                                        | (continued on next page)                                                                                                                                                                                                                                                                                                                                                                                    |

Bit

(continued on next page)

3-1

**Description and Operation**

| Bit   |                                         | <b>Description and Operation</b>                                                                                                                                                                                               |

|-------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07    | CONTROL READY (RDY) Read Only           | Indicates that the control is ready to perform a function. Cleared when the control is executing transfers between the disk and the Unibus. Set by INIT, DISK CLEAR, or when disk function is terminated.                      |

| 06    | INTERRUPT ENABLE<br>Read/Write          | When set, this bit allows the control ready signal (RDY) or error (DCS bit 07 or 15) to interrupt the program. Set by program, cleared by INIT, DISK CLEAR, or the program.                                                    |

| 05    | EXTENDED MEMORY 1 (XM 1) Read/Write     | MSB of Current Memory Address (extension of the CMA register). Can be loaded by the program. Cleared by INIT or DISK CLEAR.                                                                                                    |

| 04    | EXTENDED MEMORY 0 (XM 0)<br>Read/Write  | Second MSB of Current Memory Address (extension of<br>the CMA Registers). Can be loaded by the program.<br>Cleared by INIT or DISK CLEAR.                                                                                      |

| Note  | Option and a memory larger than 32k     | 4-5) are intended for systems equipped with the KT11-A K words, and will cause the Nonexistent Memory bit (DAE the CMA or selected by program, when the system has 32K                                                         |

| 03    | MAINTENANCE (MA)<br>Read/Write          | When set, this bit indicates that a maintenance function is in process. Loaded by the program. Cleared by INIT, DISK CLEAR, or the program.                                                                                    |

| 01-02 | FUNCTION REGISTER (FR1, FR0) Read/Write | The function register (FR) selects the operation to be performed by the disk control when a GO command is given. (DCS bits $00-1$ ). The function code is described in Table 3-1.                                              |

|       |                                         | The FR is loaded by the program and is cleared by INIT or DISK CLEAR. The FR retains the function until altered by the program or cleared, thus enabling the user to continue from a "soft error" condition with a GO command. |

| 00    | GO BIT (GO)<br>Write Only               | When set, the GO bit will cause the disk control to carry out the function contained in the FR. The GO bit and the FR can be loaded simultaneously.                                                                            |

Table 3-1

Function Code

| FR01 | FR00 | Mode             | Operation   |

|------|------|------------------|-------------|

| 0    | 0    | NORMAL<br>NORMAL | NOP<br>READ |

| 0    | 1    | NORMAL           | WRITE       |

| 1    | 1    | NORMAL           | WRITE CHECK |

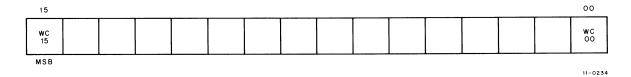

# 3.2.2 Word Count Register (WC = 777462)

Bit

00 - 15

WORD COUNT (WC)

Read/Write

**Description and Operation**

Counts the number of data transfers to and from the disk. The WC register can be loaded and read from the bus, and shall be loaded with the 2's complement of the number of data transfers desired. The register will be incremented by the disk control before each data transfer. Cleared by INIT or DISK CLEAR.

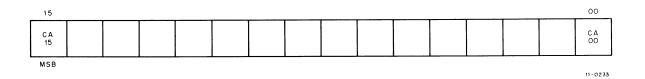

# 3.2.3 Current Memory Address Register (CMA = 777464)

Bit

Description and Operation

00 - 15

Holds the core address of the data to be transferred next. Addressing will only be permitted on word boundaries. Thus CA00 must always be loaded with a 0.

The register will be set to the starting address. The disk control will increment the register by 2 after each data transfer. The register will carry into the extended memory bits (DCS bits 03-04). Register range:  $000000_8 - 177776_8$ . Cleared by INIT or DISK CLEAR.

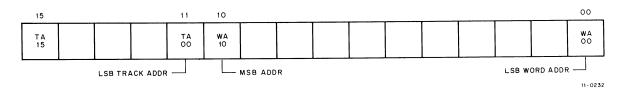

## 3.2.4 Disk Address Register (DAR = 777466)

Bit

**Description and Operation**

00–10 WORD ADDRESS (WA)

Read/Write

Selects one of 2048 words on a disk track. The word address will carry into the track address, thus allowing spiral read or write.

(continued on next page)

# Bit Description and Operation

11-15 TRACK ADDRESS (TA)

Read/Write Selects one of 128 tracks per disk with bits 00-01 of DAE register. Bit 15 carries into bit 00 of the DAE (Disk Address Ext & Error Register).

GENERAL: The DAR is incremented by the disk control when the disk data is transferred into the Data Buffer Register (DBR) during a Read operation, or when the disk data is transferred from the DBR during Write. The register can be loaded and read from the bus and is cleared by INIT or DISK CLEAR.

#### 3.2.5 Disk Address Ext & Error Register (DAE = 777470)

14

13

12

11

10

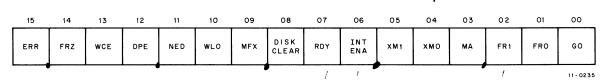

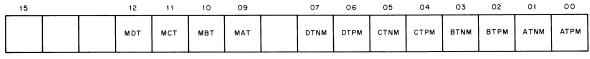

| 15  |      |      | 12   | 11 | 10  | <br>08     | 07  |         | 05        | 04       |          | 02        | 01       | 00        |   |

|-----|------|------|------|----|-----|------------|-----|---------|-----------|----------|----------|-----------|----------|-----------|---|

| APE | ATER | BTER | CTER |    | NEM | CMA<br>INH | DRL |         | D A<br>03 | DA<br>02 | DA<br>O1 | D A<br>00 | TA<br>06 | T A<br>05 |   |

|     |      |      |      |    |     |            | D   | A OVFLO | ,         |          | MSB OF D | А         | L        | MSB OF T  | A |

|     |      |      |      |    |     |            |     |         |           |          |          |           |          | 11-023    | 9 |

Bit Description and Operation

15 ADDRESS PARITY ERROR This bit is set when the disk control detects an address

(APE) parity error. Allowed any time the disk is busy. This error will cause a FREEZE (FRZ) condition. Cleared by INIT or DISK CLEAR.

A TIMING TRACK ERROR

(ATER)

Read Only. Sets FREEZE (FRZ)

- (DCS Bit 14)

Detects missing or extra bits from the A Timing Track

(clock). Causes a FREEZE (FRZ) condition when set.

(See description of FRZ.) Set by the control upon detection of an error, cleared by INIT or DISK CLEAR.

B TIMING TRACK ERROR

(BTER)

Read Only. Sets FREEZE (FRZ)

- (DCS Bit 14)

Detects missing or extra bits from the B Timing Track

(ADDR). Causes a FREEZE (FRZ) condition when set.

(See description of FRZ.) Set by the control upon detection of an error, cleared by INIT or DISK CLEAR.

C TIMING TRACK ERROR

(CTER)

Read Only. Sets FREEZE (FRZ)

- (DCS Bit 14)

Detects missing or extra bits from the C Timing Track

(SECTOR). Causes a FREEZE (FRZ) condition when

set. (See description of FRZ.) Set by the control upon

detection of an error, cleared by INIT or DISK CLEAR.

Unused.

NONEXISTENT MEMORY (NEM) Set when the control fails to receive SSYN after asserting MSYN to the memory (time out after 20  $\mu$ s. Cleared by INIT and DISK INIT. CMA contains address of NEM. Bit 14)

Unused.

CURRENT MEMORY ADDRESS

INHIBIT (CMA INH)

Read/Write

Unused.

When set, this bit prevents the Current Memory Address

Counter from incrementing. Set by program, cleared by

INIT, DISK CLEAR, or the program.

DATA REQUEST LATE

Read/Write

This status bit is set when the processor has failed to allow an NPR transfer to be executed when the disk control was ready to transfer data. This status bit is intended as an overload warning and does not set ERROR (DCS bit 15). Cleared by INIT, DISK CLEAR, or the program.

Unused.

DISK ADDRESS -10<sub>8</sub> (DA14)

This bit is set if we sequence into disk 10<sub>8</sub>, which does

DISK ADDRESS -10<sub>8</sub> (DA14)

Read/Write

This bit is set if we sequence into disk 10<sub>8</sub>, which does not exist. This will set NED (DCS bit 11) which sets ERROR to signal the program. Cleared by INIT, DISK CLEAR, or when a new disk ADDR is loaded.

04-02 DISK ADDRESS (DA) Selects one of eight disks that can be controlled from Read/Write one disk control. The track address (DAE bit 01) carries into the disk address enabling automatic data trans-

fers across disks.

TRACK ADDRESS (TA)

These are the two most significant bits of the track ad-

dress. The least significant bits are found in the DAR register (bits 11-15). Together they select one of 128

**Description and Operation**

tracks per disk.

GENERAL: The disk address and the track address bits are cleared by INIT or DISK CLEAR.

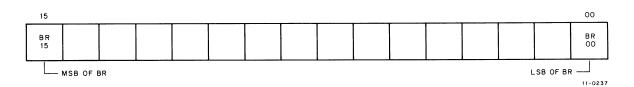

#### 3.2.6 Disk Data Buffer Register (DBR = 777474)

Read/Write

Bit

01 - 00

Bit

Bit

Description and Operation

00–15 BUFFER REGISTER (BR) This register is provided mainly as a maintenance tool and can be loaded and read from the bus. Cleared by INIT and DISK CLEAR.

#### 3.2.7 Maintenance Register (MAR = 777474)

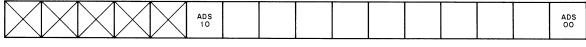

11-0238

Description and Operation

00-01 A TIMING MAINTENANCE Simulated A Timing Track disk interface.

(ATM) Write Only

(continued on next page)

| Bit      |                                                                                                                                                                     | Description and Operation                                      |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| 02-03    | B TIMING MAINTENANCE (BTM) Write Only                                                                                                                               | Simulated B Timing Track disk interface.                       |  |  |  |  |

| 04-05    | C TIMING MAINTENANCE (CTM) Write Only                                                                                                                               | Simulated C Timing Track disk interface.                       |  |  |  |  |

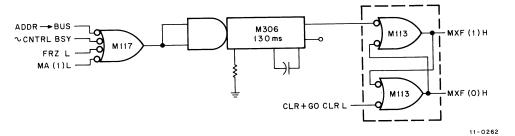

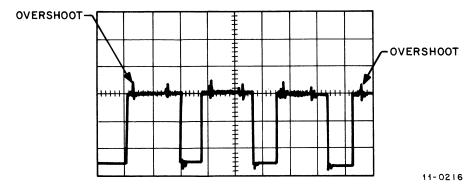

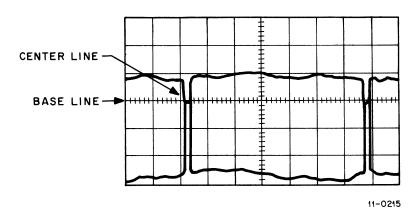

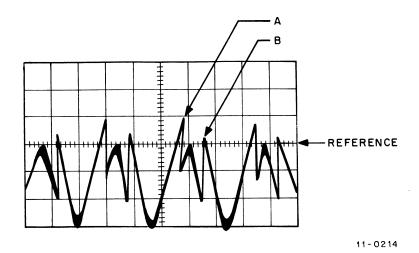

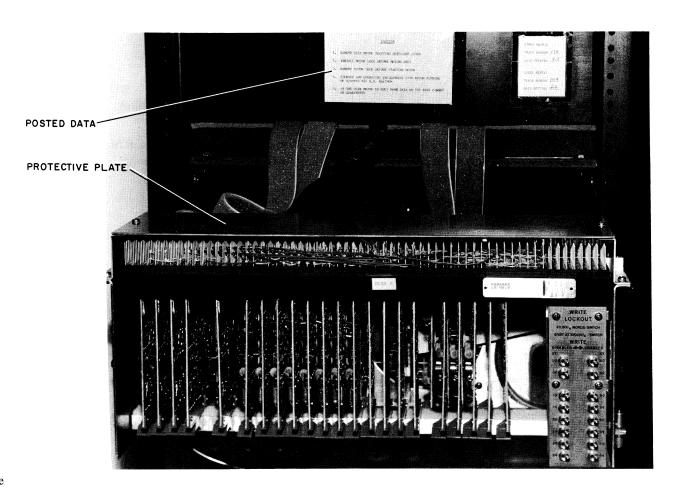

| 06-07    | DATA TRACK MAINTENANCE (DTM) Write Only                                                                                                                             | Simulated Data Track disk interface.                           |  |  |  |  |