# DR11-W Direct Memory Access Interface User's Guide

Prepared by Educational Services of Digital Equipment Corporation

# © Digital Equipment Corporation 1987 All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

#### Printed in U.S.A.

# This document was set on a DIGITAL DECset Integrated Publishing System.

• Class A Computing Devices:

**Notice:** This equipment generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference in which case the user at his own expense may be required to take measures to correct the interference.

The following are trademarks of Digital Equipment Corporation:

| d i g i t a l ™ | DECwriter    | RSX            |  |  |

|-----------------|--------------|----------------|--|--|

| anannan         | DIBOL        | Scholar        |  |  |

| DEC             | MASSBUS      | ULTRIX         |  |  |

| DECmate         | PDP          | UNIBUS         |  |  |

| DECset          | P/OS         | VAX            |  |  |

| DECsystem-10    | Professional | VMS            |  |  |

| DECSYSTEM-20    | Rainbow      | VT             |  |  |

| DECUS           | RSTS         | Work Processor |  |  |

#### CONTENTS

#### **PREFACE CHAPTER 1** GENERAL INFORMATION INTRODUCTION..... 1.1 1.2 MODULE LAYOUT..... 1.3 BASIC BLOCK DIAGRAM ..... DATA TRANSFER TECHNIQUES..... 1.4 1.4.1 Programmed I/O..... 1-5 1.4.2 Interrupt Driven I/O..... Direct Memory Access I/O..... 1.4.3 1-5 1.5 BURST MODES..... 1-9 DATA TRANSFER RATES TO USER DEVICES..... 1.6 1.7 DATA TRANSFER RATES ACROSS A LINK ..... 1-9 1.8 SPECIFICATIONS..... 1-9 **CHAPTER 2** SETUP, INSTALLATION, AND TESTING GENERAL 2.1 2-1 2.2 UNPACKING ..... 2-1 2.3 ANTI-STATIC PRECAUTIONS..... 2.4 SETUP..... 2-1 Selecting the UNIBUS Address 2.4.1 Selecting the Interrupt Vector Address..... 2.4.2 2.4.3 Setting the E105 Switchpack..... 2-3 Selecting the Correct BUSY Signal ..... 2.4.3.1 2-3 Setting UNIBUS Address Bit <00> Suppression..... 2-3 2.4.3.2 Selecting Error and Information Register (EIR)Suppression..... 2.4.3.3 2-5 2.4.4 Setting the Burst-Size Toggle Switch 2-5 2.4.5 Selecting the Burst Release Time-Out Value ..... 2-7 2.4.6 Selecting the UNIBUS Interrupt Priority ..... 2-8 2.4.7 INSTALLATION AND CHECKOUT ...... 2-8 2.5 Installing the DR11-W in a Compliant System ...... 2-10 2.5.1 2.5.2 Installing the DR11-W in a Non-Compliant System ...... 2-11 2.5.3 2.5.4 Installation Without the Bulkhead Pane...... 2-11 CABLE WRAP-AROUND TESTING ...... 2-12 2.6 2.7 LOGIC WRAP-AROUND TESTING ...... 2-14 LINK-MODE TESTING...... 2-15 2.8

2.9

FINAL INSTALLATION...... 2-17

#### **CHAPTER 3** USER DEVICE INTERFACING INTRODUCTION..... 3-1 3.1 PHYSICAL 3.2 3.3 ELECTRICAL 3.3.1 Output Circuit..... 3.3.2 Input Circuit..... 3-1 Terminators ..... 3-1 3.3.3 3-1 Cable Characteristics..... 3.3.4 3.3.5 Logic Levels ..... 3-5 Logic Polarity..... 3.3.6 Logic Reference 3-53.3.7 Transmission Distance..... 3-5 3.3.8 3.4 DATA FORMAT..... DIRECTION OF DATAFLOW DURING PROGRAMMED I/O..... 3-8 3.5 DIRECTION OF DATAFLOW DURING DIRECT MEMORY ACCESS 3.6 (DMA) I/O..... INPUT SIGNAL FUNCTIONAL DESCRIPTION ...... 3-11 3.7 3.7.1 Data Inputs 3-12 3.7.2 3.7.3 3.7.4 OUTPUT SIGNAL FUNCTIONAL DESCRIPTION...... 3-14 3.8 Data Outputs 3-15 3.8.1 3.8.2 3.8.3 Miscellaneous 3-15 3.8.4 3.9 DMA CYCLES IN GENERAL ...... 3-15 3.10 3.11 3.12 3.12.1 3.12.1.1 3.12.1.2 3.12.1.3 3.12.2 Writing Bytes ...... 3-23 3.12.2.1 Simplest and Slowest ...... 3-24 3.12.2.2 3.12.2.3 PROCESSOR CONTROL OF TRANSFER DIRECTION ...... 3-24 3.13 PROCESSOR CONTROL OF BURST MODE ...... 3-25 3.14 3.15 PROGRAMMING THE DR11-W **CHAPTER 4** INTRODUCTION..... 4.1 4.2 REGISTERS..... Word Count Register.... 4.2.14-2 4.2.2Bus Address Register Shared Address 772 414..... 4.2.3 4-3 Control and Status Register..... 4-3 4.2.4 Error and Information Register..... 4.2.5 4-8

| 4.2.6                                                                                       | Input Data Register                                                                                                                                                                                                                                                                                                                                            | 4-9                                                                                                                        |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 4.2.7                                                                                       | Output Data Register                                                                                                                                                                                                                                                                                                                                           | 4-10                                                                                                                       |

| 4.3                                                                                         | DATA DESKEW                                                                                                                                                                                                                                                                                                                                                    | 4-10                                                                                                                       |

| 4.4                                                                                         | USING PROGRAMMED I/O                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| 4.5                                                                                         | USING INTERRUPT DRIVEN I/O                                                                                                                                                                                                                                                                                                                                     | 4-13                                                                                                                       |

| 4.6                                                                                         | STARTING A DMA TRANSFER                                                                                                                                                                                                                                                                                                                                        | 4-14                                                                                                                       |

| 4.7                                                                                         | DEVICE DRIVERS                                                                                                                                                                                                                                                                                                                                                 | 4-14                                                                                                                       |

| CHAPTER 5                                                                                   | LINKS                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            |

| 5.1                                                                                         | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 5-1                                                                                                                        |

| 5.2                                                                                         | LINKING TWO DR11-Ws                                                                                                                                                                                                                                                                                                                                            | 5-1                                                                                                                        |

| 5.3                                                                                         | LINKING A DR11-W TO A DRV11-B OR DRV11-W                                                                                                                                                                                                                                                                                                                       | 5-3                                                                                                                        |

| 5.4                                                                                         | REDEFINITION OF SIGNALS AND CSR BITS                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| 5.5                                                                                         | REDEFINITION OF BAR BIT <00>                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| 5.6                                                                                         | SPECIAL INTERRUPT CONDITIONS                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| 5.7                                                                                         | BASIC PROGRAMMING TECHNIQUES                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                          |

| 5.7.1                                                                                       | Programmed I/O                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

| 5.7.2                                                                                       | Interrupt Driven I/O                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| 5.7.3                                                                                       | DMA I/O                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| 5.8                                                                                         | LINK ARBITRATION                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

| 5.9                                                                                         | INITIATING-END VERSUS SENDING-END                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

| 5.10                                                                                        | STARTING A DMA TRANSFER                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| 5.11                                                                                        | STARTING A DMA TRANSPER  STARTING ORDER                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| 5.12                                                                                        | UNIBUS BANDWIDTH CONSUMPTION                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| 5.12                                                                                        | BURST MODE                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| 3.13                                                                                        | DURST MODE                                                                                                                                                                                                                                                                                                                                                     | 5-0                                                                                                                        |

|                                                                                             |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                            |

| CHAPTER 6                                                                                   | DMA OPERATION IN DETAIL                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

|                                                                                             | DMA OPERATION IN DETAIL  INTRODUCTION                                                                                                                                                                                                                                                                                                                          | 6-1                                                                                                                        |

| CHAPTER 6                                                                                   |                                                                                                                                                                                                                                                                                                                                                                | 6-1<br>6-1                                                                                                                 |

| <b>CHAPTER 6</b> 6.1                                                                        | INTRODUCTIONOVERVIEW                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| CHAPTER 6 6.1 6.2 6.3                                                                       | INTRODUCTIONOVERVIEWREADY LOGIC                                                                                                                                                                                                                                                                                                                                | 6-1                                                                                                                        |

| <b>CHAPTER 6</b> 6.1 6.2 6.3 6.4                                                            | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1                                                                                                                 |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5                                                              | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1                                                                                                          |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6                                                          | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-2                                                                                                   |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7                                                      | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-2<br>6-3                                                                                            |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8                                                  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4                                                                                     |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9                                              | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5                                                                              |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9 6.10                                         | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5                                                                       |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9 6.10 6.11                                    | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6                                                                |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12         | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6<br>6-7<br>6-10                                                 |

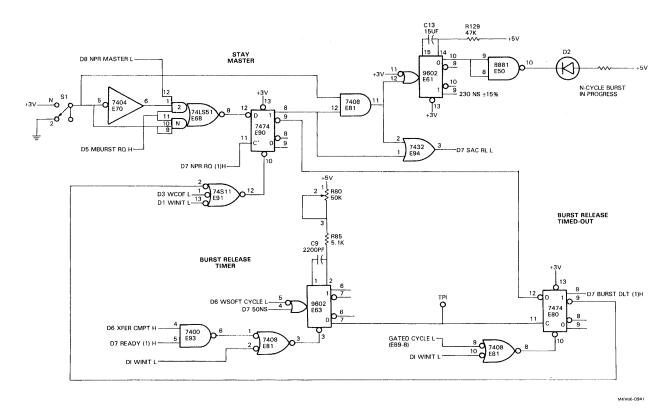

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9 6.10 6.11 6.12 6.13                          | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6<br>6-7<br>6-10<br>6-10                                         |

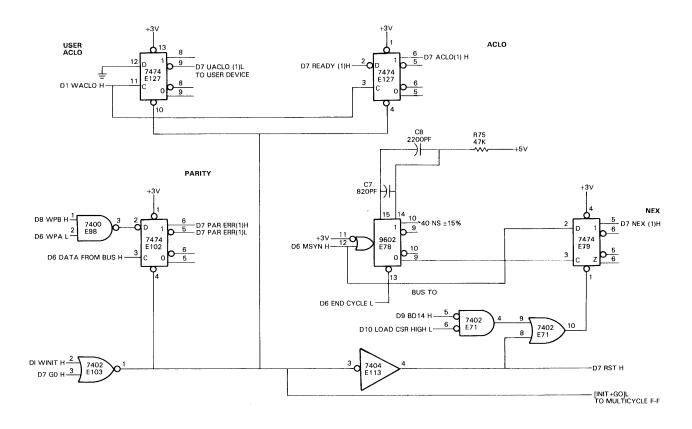

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9 6.10 6.11 6.12 6.13 6.14                     | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6<br>6-7<br>6-10<br>6-11                                         |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9 6.10 6.11 6.12 6.13 6.14 6.15                | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6<br>6-7<br>6-10<br>6-11<br>6-11                                 |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9 6.10 6.11 6.12 6.13 6.14 6.15 6.16           | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6<br>6-7<br>6-10<br>6-11<br>6-11<br>6-12                                |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9 6.10 6.11 6.12 6.13 6.14 6.15 6.16 6.17      | INTRODUCTION OVERVIEW READY LOGIC WORD COUNT OVERFLOW CYCLE AND BUSY LOGIC MULTICYCLE REQUEST THE CYCLE DELAY LINE CYCLE INHIBIT FLIP-FLOP THE NPR REQUEST FLIP-FLOP THE NPR ARBITRATOR UNIBUS TIMING LOGIC SLAVE SYNC FOR WRITE OPERATIONS SLAVE SYNC FOR READ OPERATIONS BURST OPERATION N-CYCLE LED BURST RELEASE TIMER ERRORS                              | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6<br>6-7<br>6-10<br>6-11<br>6-11<br>6-12<br>6-12                 |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9 6.10 6.11 6.12 6.13 6.14 6.15 6.16 6.17 6.17 | INTRODUCTION  OVERVIEW  READY LOGIC  WORD COUNT OVERFLOW  CYCLE AND BUSY LOGIC  MULTICYCLE REQUEST  THE CYCLE DELAY LINE  CYCLE INHIBIT FLIP-FLOP  THE NPR REQUEST FLIP-FLOP  THE NPR ARBITRATOR  UNIBUS TIMING LOGIC  SLAVE SYNC FOR WRITE OPERATIONS  SLAVE SYNC FOR READ OPERATIONS  BURST OPERATION  N-CYCLE LED  BURST RELEASE TIMER  ERRORS  AC LO Error | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6<br>6-7<br>6-10<br>6-11<br>6-11<br>6-12<br>6-12<br>6-12         |

| CHAPTER 6  6.1 6.2 6.3 6.4 6.5 6.6 6.7 6.8 6.9 6.10 6.11 6.12 6.13 6.14 6.15 6.16 6.17      | INTRODUCTION OVERVIEW READY LOGIC WORD COUNT OVERFLOW CYCLE AND BUSY LOGIC MULTICYCLE REQUEST THE CYCLE DELAY LINE CYCLE INHIBIT FLIP-FLOP THE NPR REQUEST FLIP-FLOP THE NPR ARBITRATOR UNIBUS TIMING LOGIC SLAVE SYNC FOR WRITE OPERATIONS SLAVE SYNC FOR READ OPERATIONS BURST OPERATION N-CYCLE LED BURST RELEASE TIMER ERRORS                              | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6<br>6-7<br>6-10<br>6-11<br>6-11<br>6-12<br>6-12<br>6-12<br>6-13 |

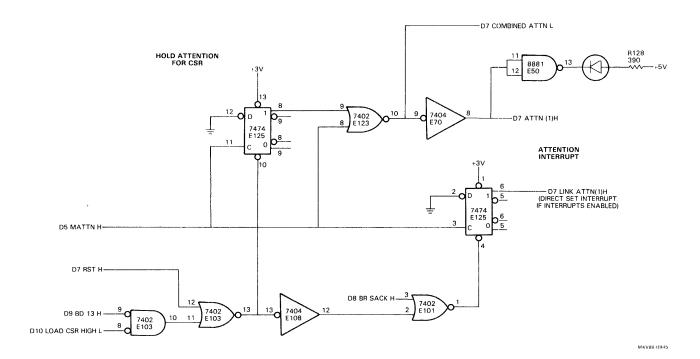

| 6.17.4     | Attention                                                              | 6-14       |

|------------|------------------------------------------------------------------------|------------|

| 6.17.4.1   | Attention to the CSR                                                   |            |

| 6.17.4.2   | Attention Causing an Interrupt                                         | 6-15       |

| 6.18       | INTERRUPT LOGIC                                                        | 6-15       |

| APPENDIX A | THE VAX/VMS XADRIVER                                                   |            |

| FIGURES    |                                                                        |            |

|            | DD11 W DL 1 D' O                                                       | 1 1        |

| 1-1        | DR11-W Block Diagram Overview                                          | 1-1<br>1-2 |

| 1-2        | Overview Block Diagrams of DR11-W Links                                |            |

| 1-3        | DR11-W Module Physical Layout                                          |            |

| 1-4        | DR11-W Basic Block Diagram                                             |            |

| 1-5        | Single-Cycle UNIBUS Transfer Timing Block Diagram                      |            |

| 1-6        | Two-Cycle UNIBUS Transfer Timing Block Diagram                         | 1-6        |

| 1-7        | N-Cycle UNIBUS Transfer Timing Block Diagram                           | 1-7        |

| 2-1        | Burst Release Time Waveform                                            | 2-8        |

| 2-1        | Installing the DR11-W in an FCC-Compliant System (Showing a PDP-11/24  | 20         |

| 2 2        | or a PDP-11/44 and a BA11-A in an H9642 Cabinet)                       | 2-10       |

| 2-3        | Installing the DR11-W in a Non-Compliant System (H9642 Cabinet, 871-C  |            |

|            | Power Controller, and Add-On Picture Frame)                            | 2-11       |

| 2-4        | Installing the DR11-W Without the Bulkhead Panel (H9642 Cabinet, 871-C |            |

|            | Power Controller, and User Device)                                     | 2-12       |

| 2-5        | Cable Wrap-Around Testing Configuration                                | 2-13       |

| 2-6        | Logic Wrap-Around Testing Configuration                                | 2-15       |

| 2-7        | Link Testing Configuration                                             | 2-16       |

| 2 1        | Typical DR11-W Output Circuit Diagram                                  | 3-2        |

| 3-1        |                                                                        | 3-2        |

| 3-2        | Typical Dr11-W Input Circuit Diagram                                   |            |

| 3-3        | Unused Input Configurations                                            |            |

| 3-4        | The UNIBUS Address Space Map for a Series of 8-Bit Bytes               | 3-6        |

| 3-5        | UNIBUS Address Space Map for a Series of 16-Bit Words                  | 3-6        |

| 3-6        | Eighteen-Bit UNIBUS Address Configuration                              | 3-7        |

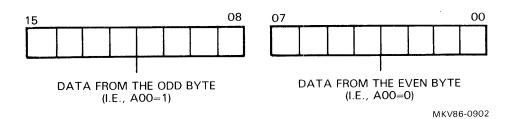

| 3-7        | UNIBUS Data Interpreted as a Word                                      | 3-7        |

| 3-8        | UNIBUS Data Interpreted as Two Bytes                                   | 3-7        |

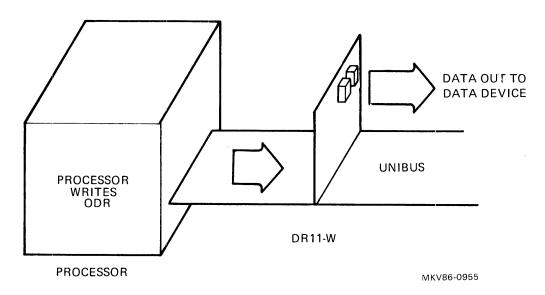

| 3-9        | Processor Writing Output Data Register Diagram                         | 3-8        |

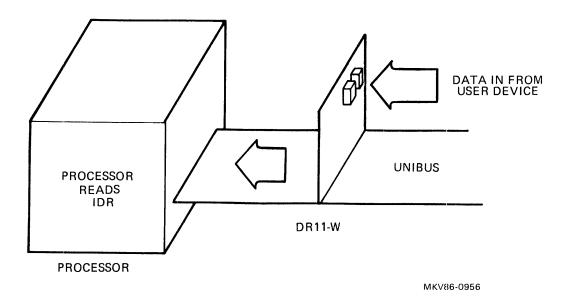

| 3-10       | Processor Reading Input Data Register Diagram                          | 3-8        |

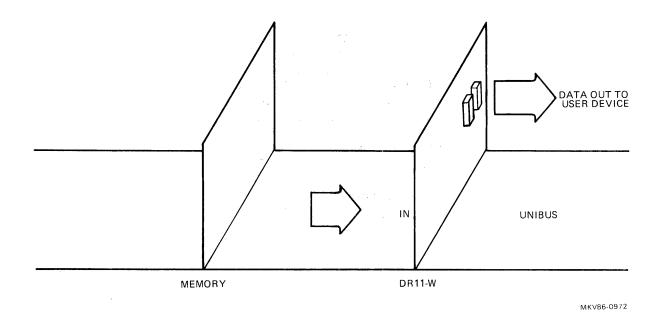

| 3-11       | Data from Memory to User (DATI) Diagram                                | 3-9        |

| 3-12       | Data from User to Memory (DATO) Diagram                                |            |

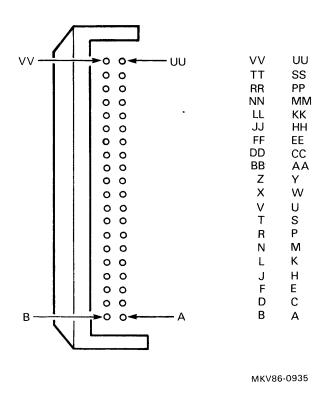

| 3-13       | J1 and J2 Connector Pin Identification                                 | 3-12       |

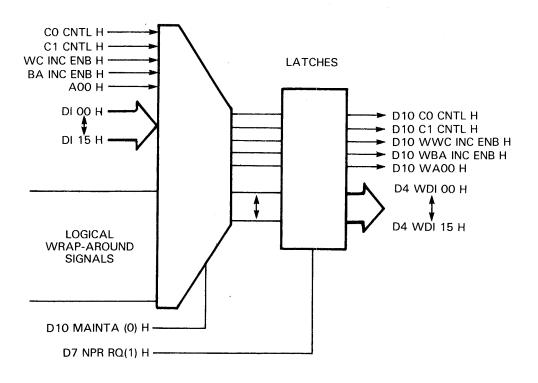

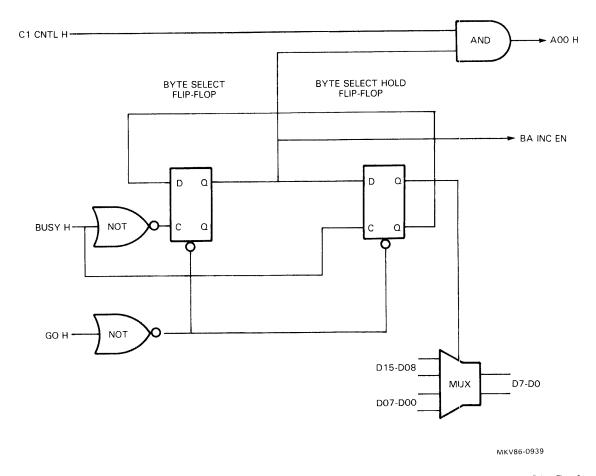

| 3-14       | DR11-W Input MUX and Latch Block Diagram                               |            |

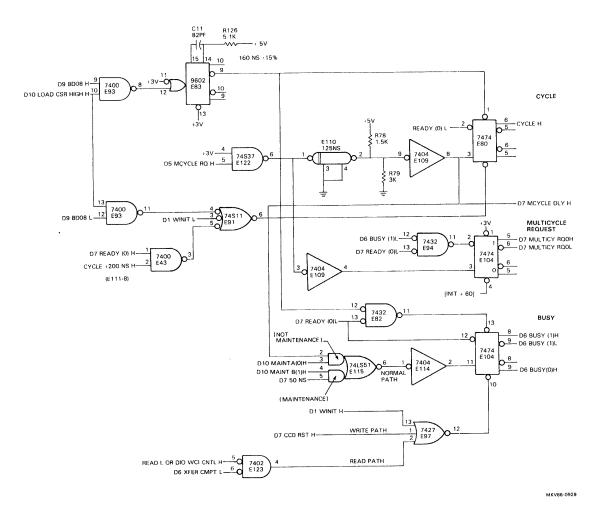

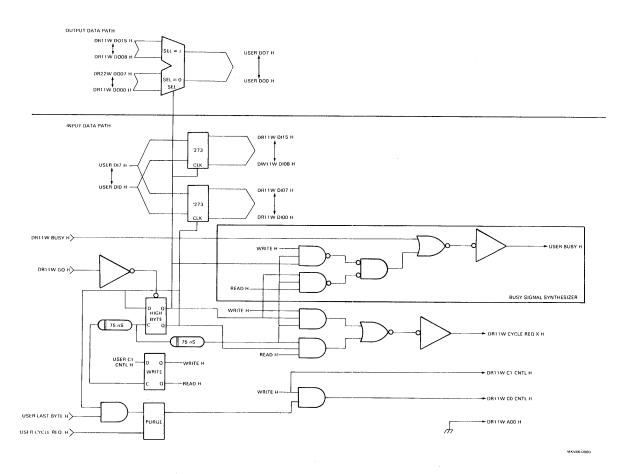

| 3-15       | Cycle and Busy Logic Diagram                                           | 3-18       |

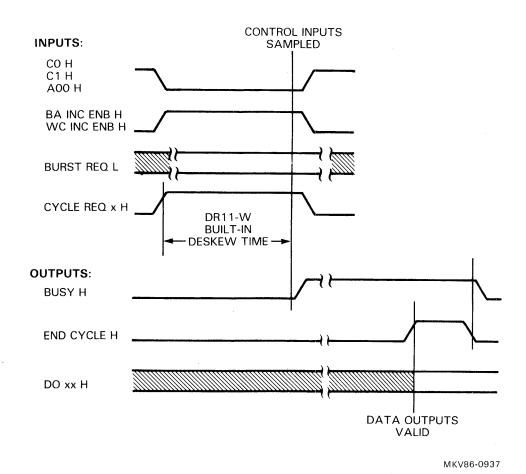

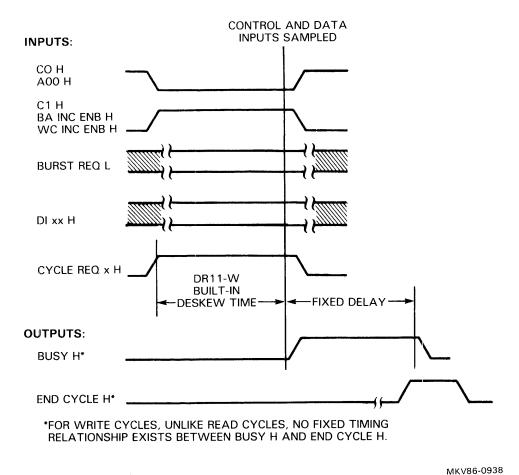

| 3-16       | Simplified Read-Cycle Timing Diagram                                   | 3-19       |

| 3-17       | Simplified Write-Cycle Timing Diagram                                  |            |

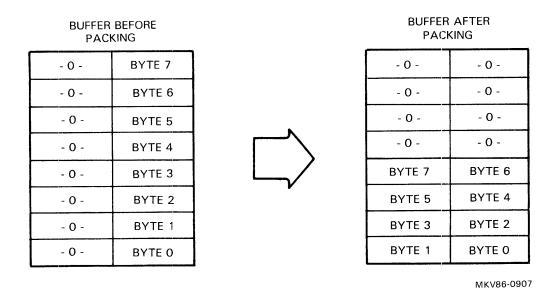

| 3-18       | Unpacking a Buffer Prior to Reading Bytes from Memory                  |            |

| 3-19       | Logic Diagram of User-Supplied Hardware to Read One Byte               |            |

|            | per DMA Cycle                                                          | 3-22       |

|            |                                                                        |            |

| 3-20        | Logic Diagram of User Supplied Hardware to Read Two Bytes per    | 2.22   |

|-------------|------------------------------------------------------------------|--------|

| 2.21        | DMA Cycle                                                        | . 3-23 |

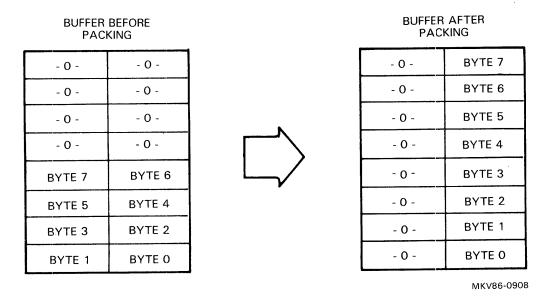

| 3-21        | Packing a Buffer After Writing Bytes to Memory                   | . 3-24 |

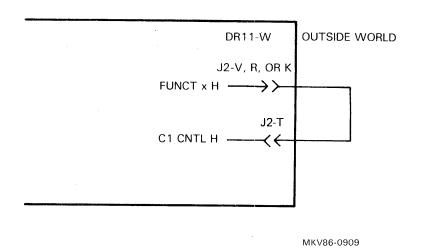

| 3-22        | Connections for Processor Control of Transfer Direction          |        |

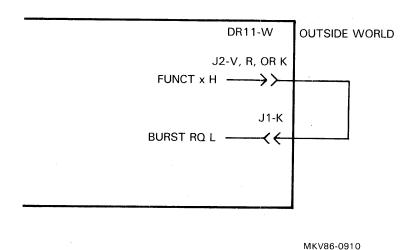

| 3-23        | Connections for Processor Control of Burst Mode                  |        |

| 3-24        | Circuit for a User Device Which Never Uses Burst Mode            |        |

| 3-25        | Circuit for a User Device Which Always Uses Burst Mode           |        |

| 3-26        | Circuit for a User Device Which Dynamically Uses Burst Mode      | . 3-27 |

| 4-1         | Word Count Register                                              |        |

| 4-2         | Bus Address Register                                             | . 4-2  |

| 4-3         | Formation of an 18-Bit UNIBUS Address                            | . 4-2  |

| 4-4         | CSR/EIR Flip-Flop                                                | . 4-3  |

| 4-5         | Control and Status Register                                      | . 4-4  |

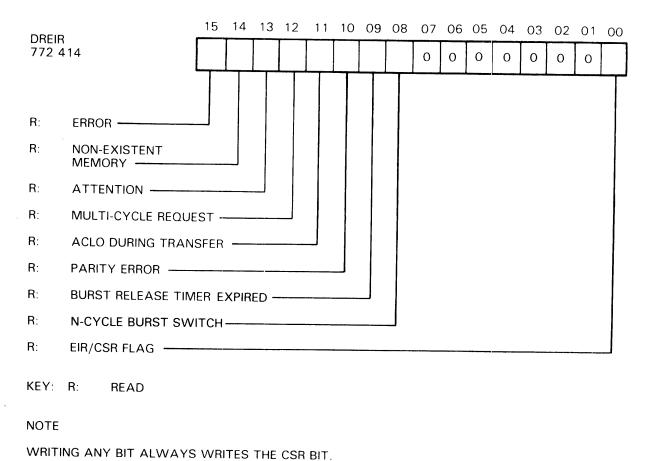

| 4-6         | Error and Information Register                                   |        |

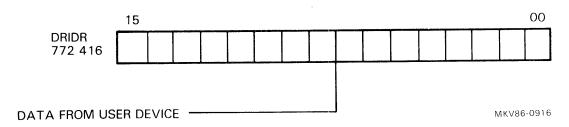

| 4-7         | Input Data Register                                              |        |

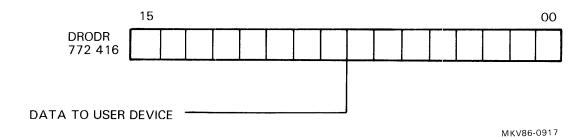

| 4-8         | Output Data Register                                             |        |

| 4-9         | Shewing of Signals                                               |        |

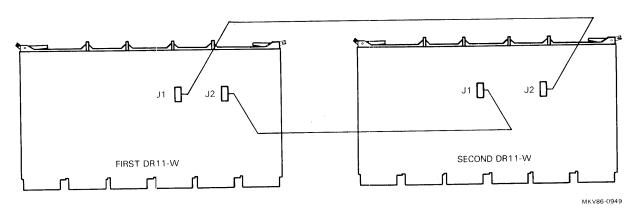

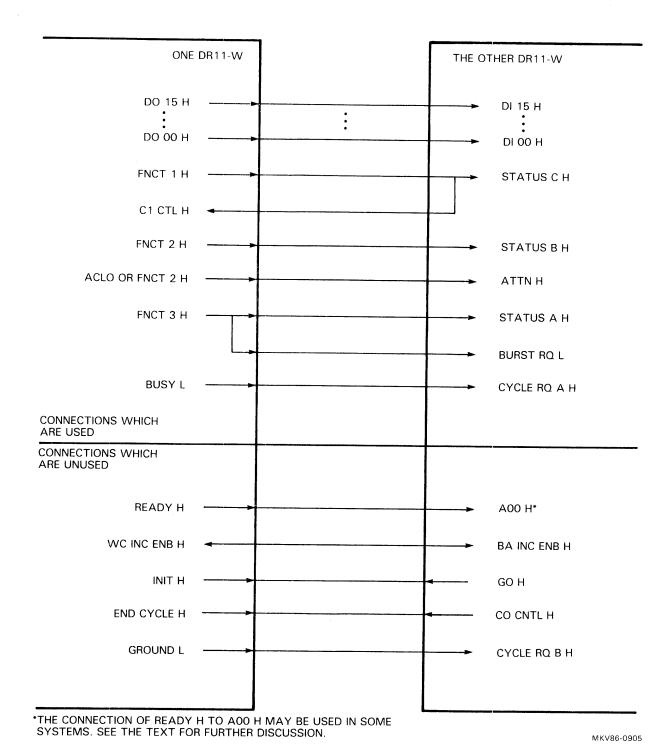

| 5-1         | Configuration for Cross-Cabling Two DR11-Ws to Create a Link     | . 5-1  |

| 5-1<br>5-2  | Connection Diagram for Half of a DR11-W Link                     |        |

| 5-2<br>5-3  |                                                                  |        |

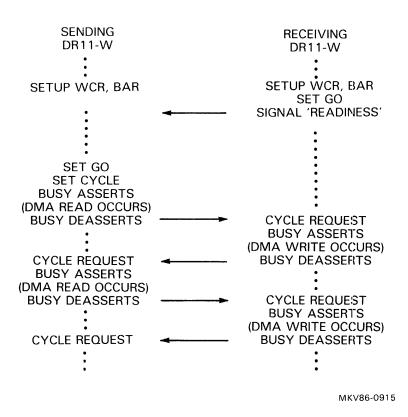

|             | Link DMA Operation Flow Diagram                                  |        |

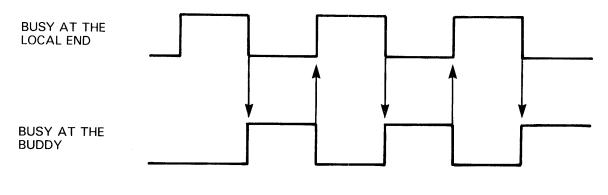

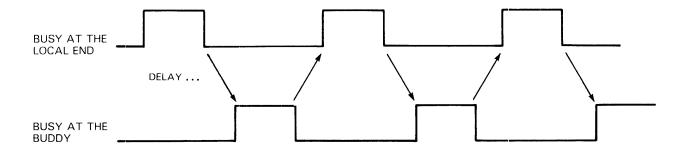

| 5-4         | Busy Signal Relationship During Link DMA Operation               |        |

| 5-5         | Busy Signal Relationship During Link Operation with Added Delays | . 5-8  |

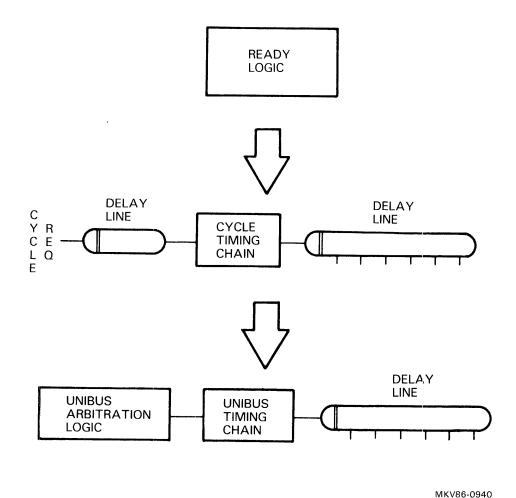

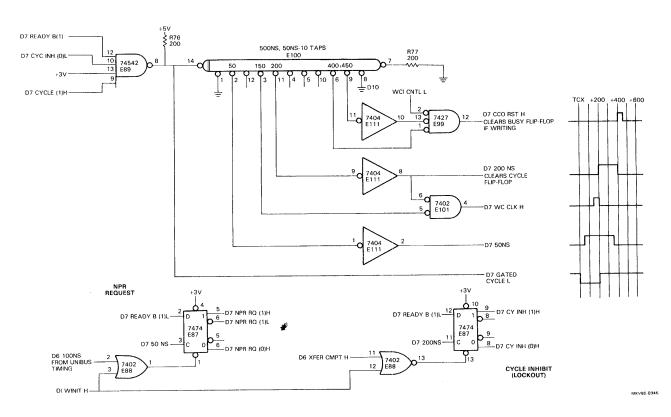

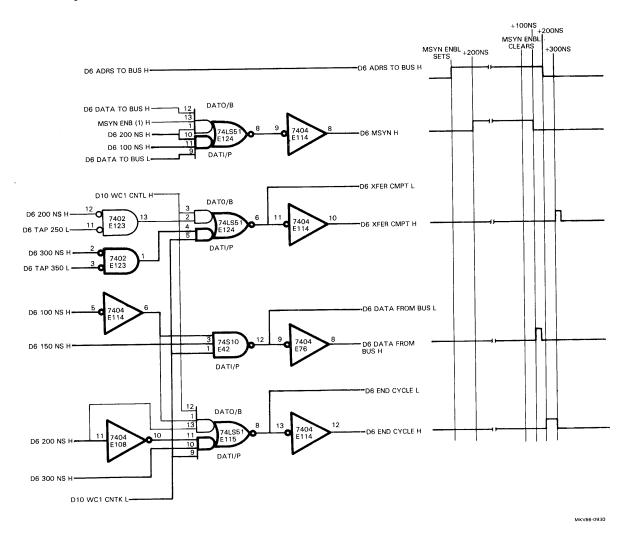

| 6-1         | DMA Cycle Logic                                                  |        |

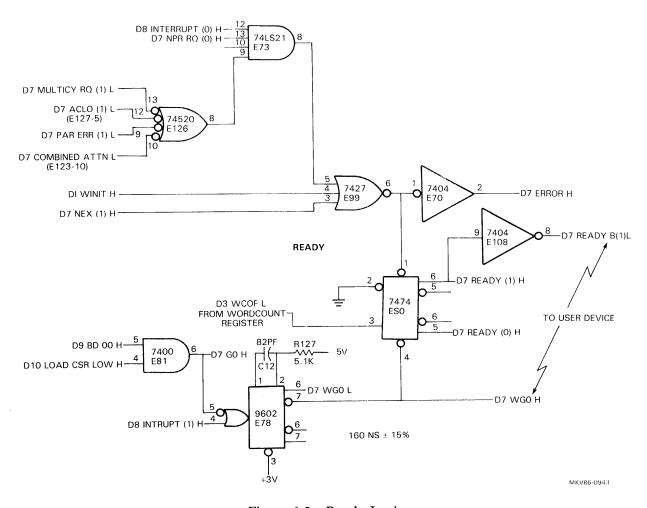

| 6-2         | Ready Logic                                                      | . 6-3  |

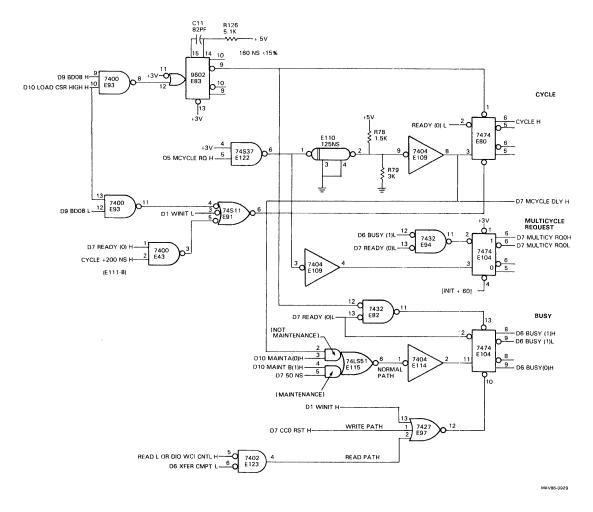

| 6-3         | Cycle Request and Busy Logic Diagram                             | . 6-4  |

| 6-4         | Cycle Delay Line Logic                                           | . 6-5  |

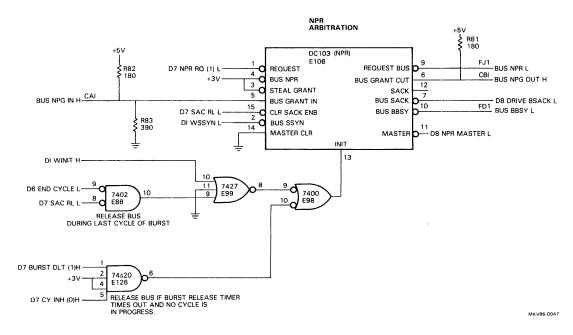

| 6-5         | NPR Arbitration Logic                                            |        |

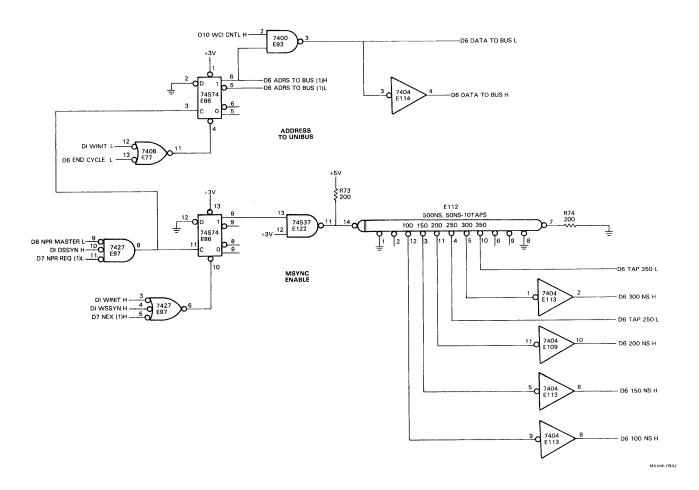

| 6-6         | UNIBUS Timing Logic                                              | . 6-7  |

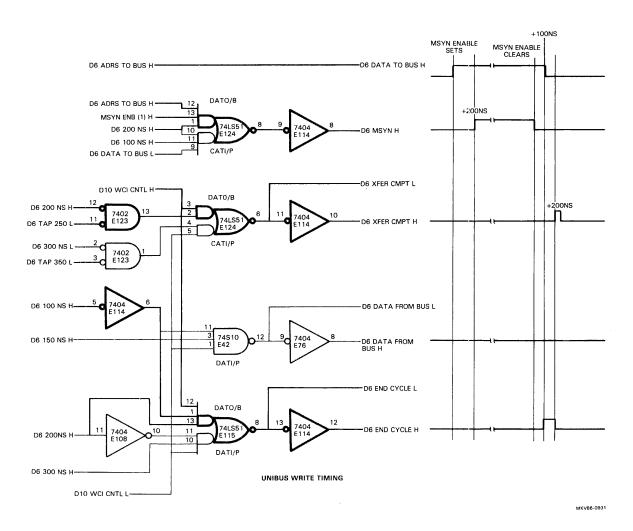

| 6-7         | UNIBUS Write Logic and Timing Diagram                            |        |

| 6-8         | UNIBUS Read Logic and Timing Diagram                             |        |

| 6-9         | Burst Logic                                                      |        |

| 6-10        | Error Logic                                                      |        |

| 6-11        | Attention Logic                                                  |        |

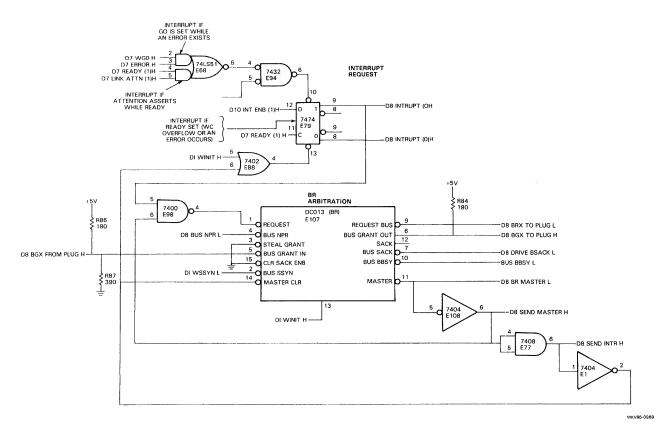

| 6-12        | Interrupt Arbitration Logic                                      |        |

|             | TAI                                                              | BLES   |

| 1-1         | DR11-W DMA Speed in Various Computers                            | . 1-8  |

| 2-1         | Address Selection                                                | . 2-2  |

| 2-1         | Interrupt Vector Address Selection                               |        |

| 2-2         | Busy Signal Selection                                            |        |

| 2-3         | A00 Suppression                                                  |        |

| 2-4         | Error and Information Register Suppression                       |        |

| <b>4-</b> 3 | Error and information register Suppression                       | . 4-5  |

| 2-6 | Burst Size Selection             | 2-6  |

|-----|----------------------------------|------|

| 2-7 | Slave Sync Time-Out Selection    | 2-7  |

| 2-8 | Burst Release Timer Adjustment   | 2-9  |

| 2-9 | BR Level Plug Part Numbers       | 2-9  |

| 3-1 | Cable Stock Part Numbers         | 3-4  |

| 3-2 | Locic Voltage Level Requirements |      |

| 3-3 | DMA Data Flow Directions         | 3-10 |

| 3-4 | DR11-W User Input Signals        |      |

| 3-5 | UNIBUS Cycle Selection           |      |

| 3-6 | DR11-W User Output Signals       |      |

#### **PREFACE**

The DR11-W Direct Memory Access Interface User's Guide describes the installation, testing, and use of the DR11-W in both the PDP-11 and VAX-11 environments.

Chapter 1 describes the DR11-W in general and cites its specifications.

Chapter 2 describes the configuration, installation, and testing of the DR11-W.

Chapter 3 describes the physical interface presented to a user device connected to the DR11-W.

Chapter 4 describes DR11-W programming in general, and the specific programming considerations which exist when the DR11-W is connected to a user device.

Chapter 5 describes the additional hardware and software considerations which exist when two DR11-Ws are cross-connected to form a high-speed, computer-to-computer data link.

Chapter 6 describes in detail those inner workings of the DR11-W which may be of concern to the system implementer.

Appendix A provides a listing of the Macro-32 source for the VAX/VMS XADRIVER.

The manual assumes that you have a basic knowledge of the UNIBUS as well as PDP-11 or VAX-11 assembly language. All programming examples are given using PDP-11 code since that should be intelligible to both the PDP-11 and the VAX-11 programmer.

The UNIBUS is described in detail in the 1985 UNIBUS Processor Handbook; other details of the processors may be found in either the PDP-11 Architecture Handbook (EB-23657-18) or the VAX-11 Architecture Handbook (EB-26115-46).

This, the fourth edition, is all new and supersedes the previous three editions. A few terms have been redefined. Most are self-evident but two changes should be noted in particular.

#### **Operating Modes**

The first through third editions referred to three operating modes for the DR11-W:

- 1. Word mode

- 2. Block mode

- 3. Burst mode (either two-cycle or n-cycle)

In the fourth edition, block mode refers to the various DMA modes: one-cycle burst (also known as non-burst), two-cycle burst, and n-cycle burst modes. The fourth edition defines the following operating modes:

## 1. Word mode

- a. Using programmed I/O

- b. Using interrupt I/O

#### 2. Block Mode

- a. Using one-cycle bursts

- b. Using two-cycle bursts

- c. Using n-cycle bursts

This form is in keeping with the rest of the DR11-W related documentation, in particular, the VAX/VMS XADRIVER description contained in the Guide to Writing a Device Driver for VAX/VMS (AA-Y511A-TE).

#### **Burst Data Late**

Additionally, all references to burst data late have been changed to burst release. This is to eliminate confusion with the data-late error (which a burst release does not represent).

# CHAPTER 1 GENERAL INFORMATION

## 1.1 INTRODUCTION

The DR11-W is a general-purpose module used whenever a UNIBUS PDP-11 or VAX-11 computer must be interfaced to another device or computer and transfer parallel binary information. The DR11-W provides the logic to interface this binary data to the UNIBUS.

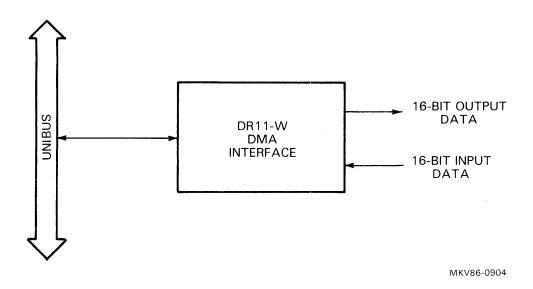

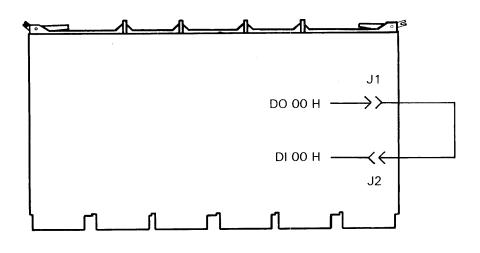

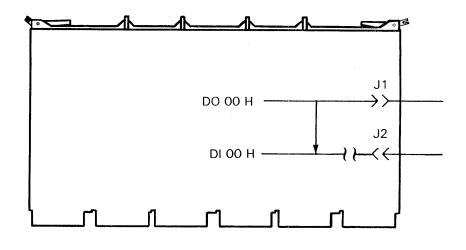

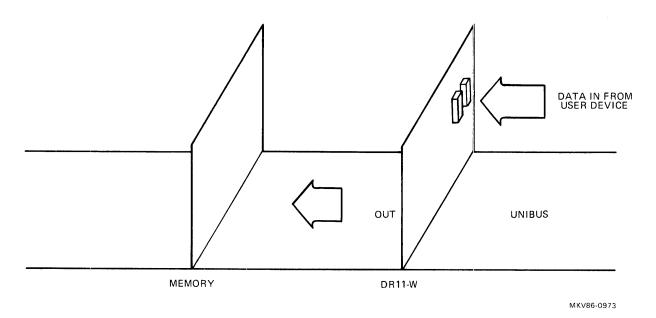

Data is transferred on the UNIBUS as 8-bit bytes or 16-bit words. The user device may connect to between 1 and 16 bits of this data. Separate lines are used for data input and data output (see Figure 1-1).

Figure 1-1 DR11-W Overview Block Diagram

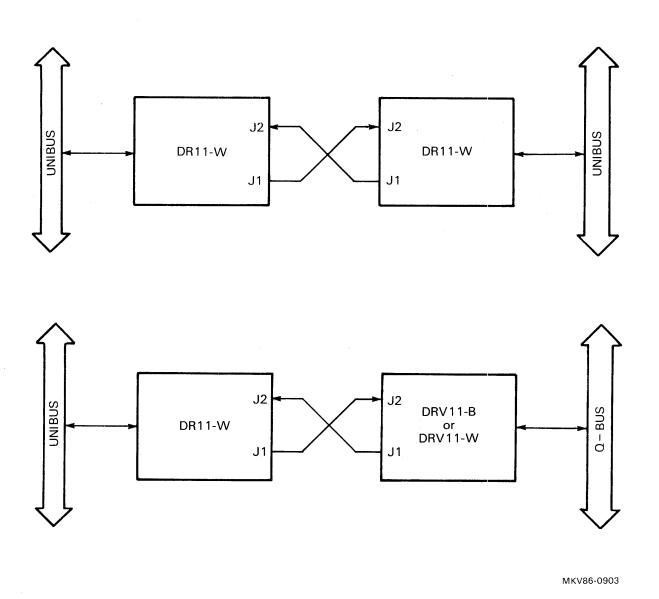

Two DR11-Ws may be cross-connected to form a high-speed link between two UNIBUS computers. The DR11-W may also be cross-connected with the DRV11-B or DRV11-W, used on the Q-bus. Together, these devices allow any PDP-11, VAX-11, or MicroVAX systems to be linked together (see Figure 1-2).

Figure 1-2 Overview Block Diagrams of DR11-W Links

## 1.2 MODULE LAYOUT

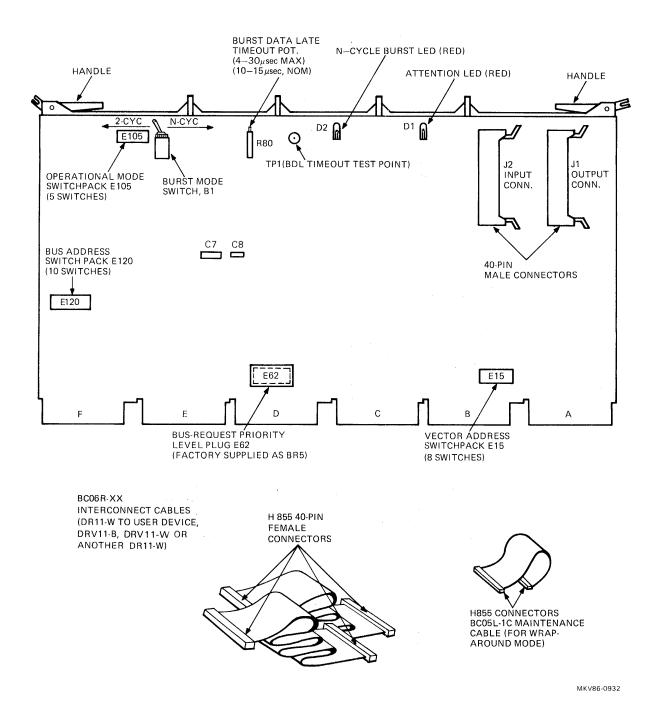

Figure 1-3 shows a DR11-W module. All of the user-interface features are called out.

Figure 1-3 DR11-W Module Physical Layout

# 1.3 BASIC BLOCK DIAGRAM

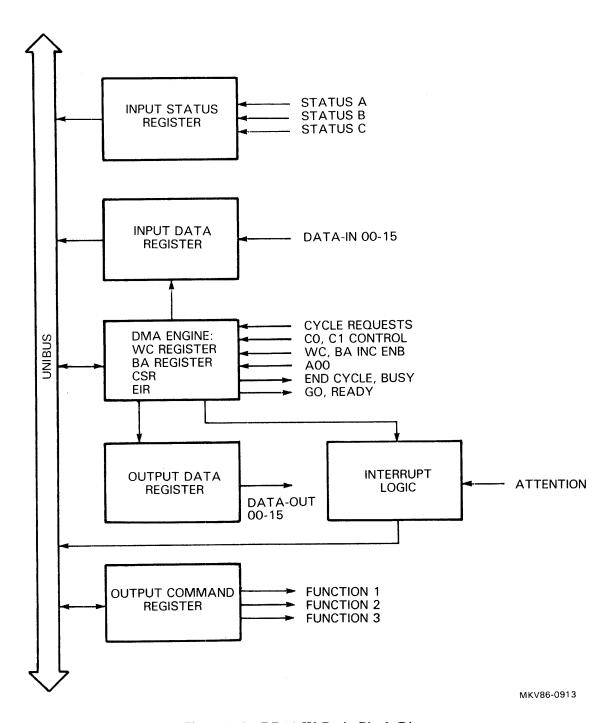

The basic block diagram of the DR11-W is illustrated in Figure 1-4.

Figure 1-4 DR11-W Basic Block Diagram

#### 1.4 DATA TRANSFER TECHNIQUES

The DR11-W may transfer data between the computer and the user device using:

- Programmed I/O

- Interrupt-driven I/O

- Direct memory access (DMA) I/O

The first two techniques are collectively referred to as word mode since the processor must participate in the transfer of every individual word. The third technique is referred to as block mode since the processor need only participate to set up the transfer of an entire block of data. These three techniques vary in speed and programming complexity. A typical application uses a mix of techniques.

## 1.4.1 Programmed I/O

Using this technique, a program simply moves data to the output data register or reads data from the input data register. Some means must be provided for synchronizing the movement of the data with the operation of the user device. This is often done using the function outputs and status inputs.

This technique can be quite fast and powerful, particularly for short transfers. However, it can consume up to 100 percent of the processor's time.

# 1.4.2 Interrupt-Driven I/O

Using this technique, the DR11-W transfers one word in or out each time an interrupt is generated by the user device. For relatively slow data rates, this causes much less processor overhead than programmed I/O, while maintaining the same flexibility.

Interrupt I/O typically has the lowest transfer rate of the three techniques.

#### 1.4.3 Direct Memory Access I/O

This is the principal application of the DR11-W. Using this technique, the DR11-W is pointed at a block of the PDP-11 or VAX-11 memory. Then, without further interaction by the processor, the DR11-W can read words out of this memory and transfer them to the user device, or take words supplied by the user device and transfer them into memory. At the end of the block, an interrupt is usually generated.

For mid- to large-sized blocks of data, this is the fastest transfer method.

#### 1.5 BURST MODES

The right to use the UNIBUS for a data transfer is decided by a priority-arbitration process. Before a DMA device (such as the DR11-W) can transfer data on the UNIBUS, it must first win this priority arbitration. While the UNIBUS arbitration process is concurrent with data transfers (so that the overall throughput of the UNIBUS is improved), the need to arbitrate does increase the latency for any one UNIBUS device.

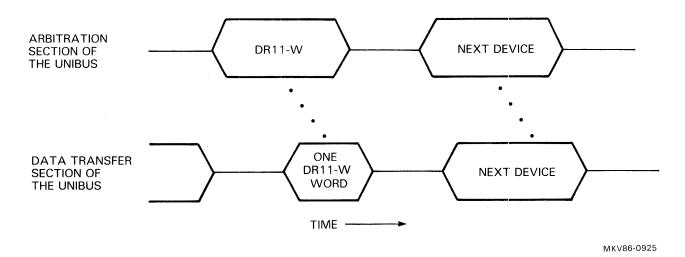

Normally, a DMA device arbitrates for use of the UNIBUS, transfers one word of data, and then releases the UNIBUS (see Figure 1-5).

Figure 1-5 Single-Cycle UNIBUS Transfer Timing Block Diagram

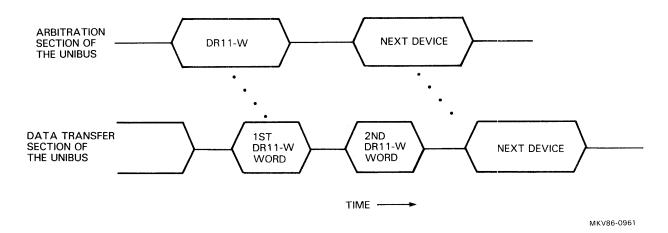

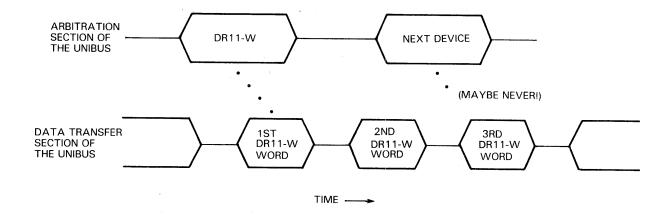

If a device has a lot of data to move quickly, it often helps to transfer more than one word each time the device becomes the master of the UNIBUS. In DR11-W terminology, this is called burst mode. The DR11-W hardware supports the transferring of two words per UNIBUS mastership. This is called two-cycle burst mode (see Figure 1-6). The DR11-W can also be configured to transfer an unlimited number of words per UNIBUS mastership. This is referred to as n-cycle burst mode (see Figure 1-7). In n-cycle burst mode, the DR11-W can use the entire UNIBUS forever, to the exclusion of all other prospective users. This mode is sometimes referred to as bus hog mode.

Figure 1-6 Two-Cycle UNIBUS Transfer Timing Block Diagram

MKV86-0962

Figure 1-7 N-Cycle UNIBUS Transfer Timing Block Diagram

Table 1-1 DR11-W DMA Speed in Various Computers

|                                                            | Bandwidt<br>Kilobytes |      |

|------------------------------------------------------------|-----------------------|------|

| Configuration                                              | Burst Siz             | e 2  |

| PDP-11/34 with MS11-L Memory:                              |                       |      |

| DATI (reading memory)                                      | 993                   | 1192 |

| DATO (writing memory words)                                | 1394                  | 1748 |

| DATOB(writing memory bytes)                                | 697                   | 874  |

| PDP-11/44 with MS11-P Memory:                              |                       |      |

| DATI (reading memory)                                      | 936                   | 1057 |

| DATO (writing memory words)                                | 1192                  | 1598 |

| DATOB(writing memory bytes)                                | 607                   | 728  |

| PDP-11/44 with MS11-M Memory:                              |                       |      |

| DATI (reading memory)                                      | 943                   | 1032 |

| DATO (writing memory words)                                | 1202                  | 1394 |

| DATOB(writing memory bytes)                                | 601                   | 697  |

| PDP-11/84 with MSV11-R Memory, UBMAP Off or DMA Cache Off: |                       |      |

| DATI (reading memory)                                      | 799                   | 936  |

| DATO (writing memory words)                                | 1024                  | 1394 |

| DATOB(writing memory bytes)                                | 512                   | 697  |

| PDP-11/84 with MSV11-R Memory, UBMAP and DMA Cache On:     |                       |      |

| DATI (reading memory)                                      | 862                   | 1024 |

| DATO (writing memory words)                                | 1024                  | 1394 |

| DATOB(writing memory bytes)                                | 512                   | 697  |

| VAX-11/780,<br>Direct Data Path (DDP):                     |                       |      |

| •                                                          | 427                   | 479  |

| DATI (reading memory) DATO (writing memory words)          | 427<br>528            | 602  |

| DATO (writing memory words)  DATOB(writing memory bytes)   | 264                   | 30   |

#### 1.6 DATA TRANSFER RATES TO USER DEVICES

Direct memory access programming techniques generally provide the fastest possible transfer rate. In this mode, the maximum speed of the DR11-W is largely determined by the speed of the memory that the DR11-W is accessing.

Table 1-1 documents the fastest observed rates on various UNIBUS processor and memory combinations, using optimum programming and the fastest possible user device.

#### **NOTE**

The speeds listed in Table 1-1 are actual speeds measured on hardware systems – your system may vary  $\pm 5\%$  or more from the values shown in the table.

#### 1.7 DATA TRANSFER RATES ACROSS A LINK

When operating as a cross-connected link with no additional buffering, the transfer rate is about one-half of the rate obtained by averaging the speed of each individual end. The exact formula is indicated below. For example, if the link is reading words from a PDP-11/24 and writing them to a PDP-11/44, the maximum transfer rate is:

$$\frac{1}{R_{\text{PDP-11/24 READ}}} + \frac{1}{R_{\text{PDP-11/44 WRITE}}}$$

MKV86-0963

#### 1.8 SPECIFICATIONS

The general specifications for the DR11-W are listed below.

• Data format presented to the user:

Binary parallel words of up to 16 bits

• Data format presented to the UNIBUS:

Binary parallel 8-bit bytes or 16-bit words

• Transfer methods:

Programmed I/O

Interrupt-driven I/O

Direct memory access I/O

#### • UNIBUS characteristics:

Capable of DMA to the full 256K byte UNIBUS address range

Maximum single transfer of 64K bytes or words

All UNIBUS data cycles supported:

- DATI (read)

- DATO (write word)

- DATOB (write byte)

- DATIP (read with write intent)

Three jumper (capacitor) selectable time-out values:

- Twelve microseconds

- Thirty-three microseconds

- Forty-five microseconds (as shipped from factory)

Four plug-selectable UNIBUS interrupt priority levels:

- BR7

- BR6

- BR5 (as shipped from factory)

- BR4

Three user-selectable burst DMA modes:

- One word transfers

- Two word bursts

- N word bursts

Automatic release of UNIBUS if transfers stop in mid-burst

User interface characteristics:

Two, 40-pin, flat-cable connectors:

- Twenty-five output lines, plus grounds

- Twenty-eight input lines, plus grounds

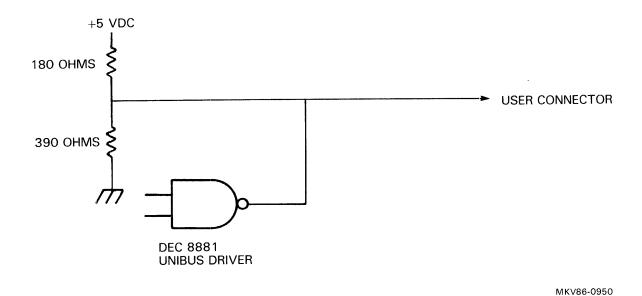

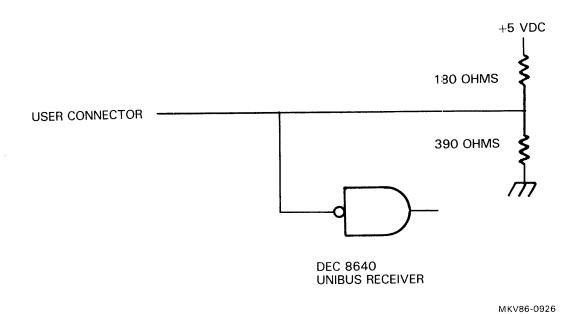

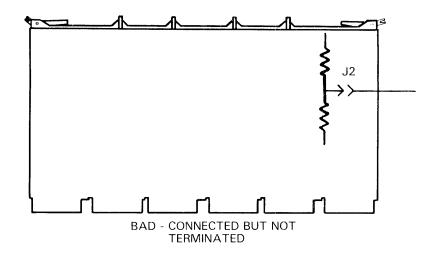

All signals driven with UNIBUS drivers or received with UNIBUS receivers for maximum noise immunity

All signals terminated into 120 ohms and 3.3 volts

Sixteen-bit parallel data inputs and outputs

Three-bit parallel control outputs

Three-bit parallel status inputs

User-selectable logic-high or logic-low busy signal

#### Physical characteristics:

Single hex module – 21.6 cm  $\times$  38.1 cm (8.5 in  $\times$  15.0 in)

Powered by 3.7 A (nominal) of +5 Vdc

Temperature range:

- 5° to 50°C (41° to 122°F) operating

- -40° to 66°C (-40° to 151°F) storage

# Humidity range:

- 10 to 90%, allowing no condensation

Two indicator LEDs:

- ATTN (interrupt)

- N-cycle burst transfer in progress

## • Programming characteristics:

Six registers occupying four addresses in the I/O page:

- Bus address register

- Word (or byte) count register

- Control and status register

- Error and information register

- Input data buffer register

- Output data buffer register

Some program compatibility with DR11-B

Errors detected by the DR11-W:

- UNIBUS time-out

- Memory parity error

- User data overrun/underrun error

- Power failure during transfer

#### • Software available:

PDP-11 stand-alone diagnostic program - CZDRL

PDP-11 stand-alone link diagnostic – CZDRK

VAX-11 stand-alone diagnostic program (includes link tests) – ESDRE

VAX-11 on-line confidence check - ESDRB

VAX/VMS sample device driver - XADRIVER

## • Related documentation:

DR11-W Field Maintenance Print Set (MP00693)

PDP-11 UNIBUS Processor Handbook (EB-26077-41)

PDP-11 Architecture Handbook (EB-23657-18)

RSX11-M Guide to Writing an I/O Driver (AA-2600E-TC)

RSX11-M+ Guide to Writing an I/O Driver (AA-H267B-TC)

VAX-11 Architecture Handbook (EB-26115-46)

Guide to Writing a Device Driver for VAX/VMS (AA-Y511A-TE)

# CHAPTER 2 SETUP, INSTALLATION, AND TESTING

#### 2.1 GENERAL

The DR11-W is installed and tested like most other modules. Off-line diagnostic programs are provided for both the PDP-11 and VAX-11 families of processors. In addition, the VAX-11 family provides an on-line confidence check program, which uses the VMS sample driver program (XADRIVER).

#### 2.2 UNPACKING

The DR11-W may have been factory installed in your system. If so, go to Section 2.6. If the DR11-W has not already been installed in your system, it is shipped in a corrugated cardboard carton. To unpack the DR11-W, perform the following procedure.

- Check that the carton is sealed and undamaged. Report any damage to Digital Equipment Corporation or to the shipping carrier.

- Remove the sealing tape that holds the carton closed. Be careful not to damage the module as you do this.

- Remove the DR11-W module from the carton, keeping it in its anti-static bag. Do not remove the module from the anti-static bag until you are at an anti-static workstation.

- Inspect the DR11-W module for visible damage. Report any damage to Digital Equipment Corporation.

#### 2.3 ANTI-STATIC PRECAUTIONS

Like most computer modules, the DR11-W contains components which can be damaged by static electricity. As long as the module remains inside its plastic bag, it is protected.

Outside of its protective plastic bag, the module should only be handled at an approved static-free workstation. A wrist strap connected to earth ground through a safety resistor should be worn by the user whenever handling the DR11-W.

#### **2.4 SETUP**

The DR11-W must be set up for each individual application. For each DR11-W module in the system, this setup consists of:

- Selecting the UNIBUS address of the registers.

- Selecting the interrupt vector address.

- Setting the E105 switches.

- Setting the burst-size toggle switch.

Three other setups may or may not matter, depending upon the application:

- Selecting the UNIBUS time-out value.

- Setting the burst release time-out value.

- Selecting the UNIBUS interrupt priority.

#### 2.4.1 Selecting the UNIBUS Address

Each DR11-W in the system contains six registers which the software uses to control the operation of the DR11-W. Every DR11-W in the system must have a unique address for this group of registers and this address must match the address expected by the software. This address is selected on each DR11-W module by the E120 switchpack on that module. See Figure 1-3 for the location of E120.

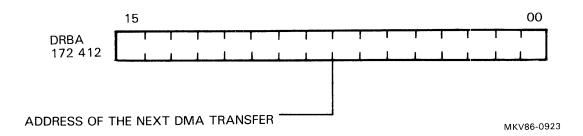

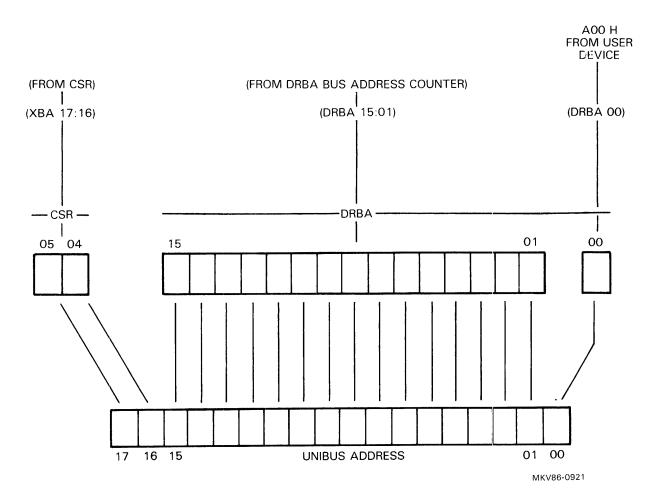

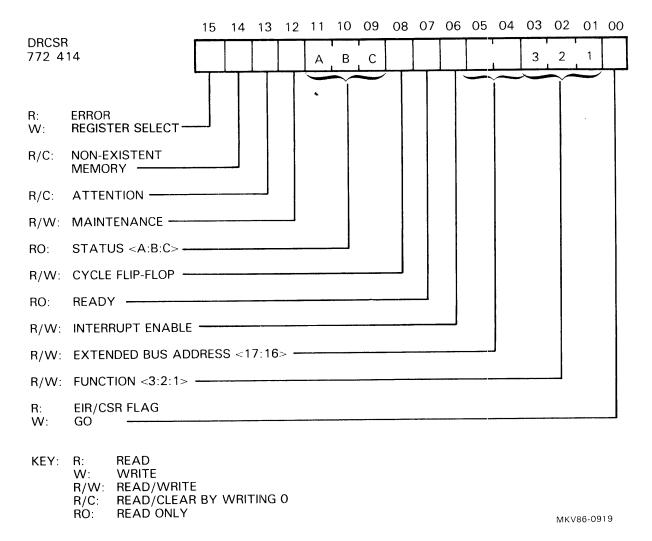

The address of the DR11-W is actually the address of the first register in the group of six. The other registers follow in ascending order. By convention, the first DR11-W in the system is assigned to UNIBUS address 772 410. This is actually the address of the DR11-W word count register. For this DR11-W, the bus address register is found at address 772 412, and so forth.

Table 2-1 documents the relationship between the E120 switches and the address assigned to the DR11-W. Note that each switch selects one bit of the UNIBUS address that this particular DR11-W will respond to. A switch set to OFF corresponds to a 1 in the UNIBUS address. The conventional settings for the first two DR11-Ws are also shown. Additional DR11-Ws are assigned addresses from the floating address space (as shown in the PDP-11 and VAX-11 architecture handbooks).

Table 2-1 Address Selection

| UNIBUS<br>Address Bit   | 17 | 16 | 15 | 14 | 13                                    | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|-------------------------|----|----|----|----|---------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|

| E120 Switch             |    |    |    |    | · · · · · · · · · · · · · · · · · · · | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |    |    |    |

| First DR11-W (772 410)  |    |    |    |    |                                       | _  | On | _  | On | _  | On | On | On | On | _  |    |    |    |

| Second DR11-W (772 430) |    |    |    |    |                                       | _  | On | _  | On | _  | On | On | On |    | _  |    |    |    |

Key: On = Switch ON - = Switch OFF

# 2.4.2 Selecting the Interrupt Vector Address

Each DR11-W in the system also uses one unique address that contains a pointer to the interrupt service routine for that DR11-W, if any exists. By convention, these vector addresses are also unique to each DR11-W, although it is not mandatory that they be so. Once again, this vector address must match that expected by the software. The vector address is selected on each DR11-W module by the E15 switchpack on that module. See Figure 1-3 for the location of E15.

Only the first DR11-W in the system is assigned a fixed vector address. By convention, it is UNIBUS address 000 124. Any other DR11-Ws are assigned vectors from the floating vector space (also described in the PDP-11 and VAX-11 architecture handbooks).

Table 2-2 documents the relationship between the E15 switches and the interrupt vector address assigned to the DR11-W. Note that each switch selects one bit of the interrupt vector address assigned to the DR11-W. A switch set to OFF corresponds to a 1 in the interrupt vector address. Switch 1 of the E15 switchpack is used in link-mode applications. In link mode, switch 1 should be OFF (open).

Table 2-2 Interrupt Vector Address Selection

| Interrupt<br>Vector<br>Address Bit | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| E15 Switch                         |    |    |    |    |    |    |    | 8  | 7  | 6  | 5  | 4  | 3  | 2  |    |    |

| First DR11-W (000 124)             |    |    |    |    |    |    |    | On | On | _  | On | _  | On | _  |    |    |

Key:

On = Switch ON - = Switch OFF

# 2.4.3 Setting the E105 Switchpack

The E105 switchpack selects three independent features:

- The polarity of the BUSY signal.

- Whether or not UNIBUS address bit (00) is suppressed.

- Whether or not the error and information register is suppressed.

Each of these features is described on subsequent pages.

**2.4.3.1** Selecting the Correct BUSY Signal – Three switches on the E105 switchpack select from three different versions of the DR11-W BUSY signal. Figure 1-3 shows the location of E105 and Table 2-3 lists the settings of switches S1, S2, and S3.

For connection to a user device, either the BUSY H or BUSY L signal can be selected, as required by the particular user device.

For connection to another DR11-W, the BUSY L signal must be selected. Whenever the cable wrap-around test is performed, the BUSY L signal setting must also be used.

Finally, special timing is required for the DR11-W to participate as one end of a DR11-W to DRV11-B, or DR11-W to DRV11-W link. This special timing is provided by the third setting.

**2.4.3.2** Setting UNIBUS Address Bit (00) Suppression – By itself, the DR11-W is capable of performing only word transfers on the UNIBUS. A small amount of additional logic within a user device allows the DR11-W to transfer bytes on the UNIBUS.

Table 2-3 Busy Signal Selection

|                 | E105 s | witches |     |                                                                                                                                                  |

|-----------------|--------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Busy Signal     | 1      | 2       | 3   | Use                                                                                                                                              |

| BUSY H          | On     | Off     | Off | Asserts the busy signal as a logic-high signal.                                                                                                  |

| BUSY L          | Off    | On      | Off | Asserts the busy signal as a logic-low signal. This setting is always used for DR11-W to DR11-W links and cable wrap-around testing.             |

| D7 CYC INH(1) L | Off    | Off     | On  | Asserts the busy signal using the particular timing required by the DRV11-B. This setting is always used for DR11-W to DRV11-B or DRV11-W links. |

Memories attached to the UNIBUS are always word-oriented. During UNIBUS DATOB (write byte) operations, these memories use UNIBUS address line 00 (A00) to indicate which of the two bytes of the memory word should be updated. During all other UNIBUS operations, A00 should be ignored by the memory. A00 is directly supplied by the user device, not the DR11-W.

If you are using a memory which fails to ignore A00 for word operations, the A00 H input to the DR11-W may be disabled by placing switch 4 of the E105 switchpack in the ON position. See Figure 1-3 for the location of E105 and Table 2-4 for the switch settings. Normally, E105-4 is left in the OFF position.

Table 2-4 A00 Suppression

| UNIBUS Address<br>Bit <00> | E105 Switch 4 |

|----------------------------|---------------|

| Enabled                    | Off           |

| Forced to 0                | On            |

If you are running the cable wrap-around diagnostics, E105-4 must be in the OFF position.

If you are connecting your DR11-W as part of a DR11-W to DR11-W (or DRV11-B or DRV11-W) link, you may leave E105-4 in either position. Placing the switch in the OFF position allows bus address bit  $\langle 00 \rangle$  to follow the status of the ready bit within the DR11-W at the far end of the link. This allows the program at the near end of the link to tell whether the DR11-W at the far end of the link is ready simply by reading BAR  $\langle 00 \rangle$ . Placing the switch in the ON position disables this indication.

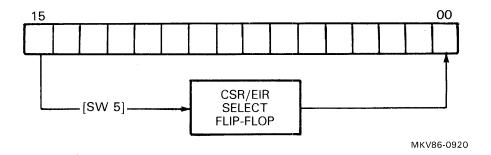

**2.4.3.3** Selecting Error and Information Register (EIR) Suppression – Certain older software packages are not programmed to handle the error and information register of the DR11-W. Setting switch 5 of E105 to OFF allows this register to be turned off (that is, it becomes invisible to the program). See Figure 1-3 for the location of E105 and Table 2-5 for the switch settings.

Table 2-5 Error and Information Register Suppression

| EIR        | E105 Switch 5 |

|------------|---------------|

| Suppressed | Off           |

| Enabled    | On            |

Operation with switch 5 off is loosely named DR11-B mode, since the DR11-B does not contain an error and information register. This position, however, does not provide exact software compatibility with the DR11-B.

Setting switch 5 on E105 to ON allows this register to be used by the program. This is named DR11-W modes. It is recommended that all new software be developed to run in DR11-W mode.

## 2.4.4 Setting the Burst-Size Toggle Switch

Arbitrating for the use of the UNIBUS requires some finite time, so the UNIBUS specification allows a device to transfer more than one word each time it becomes the UNIBUS master. Without additional (external) logic, the DR11-W is capable of transferring one, two, or an unlimited number of words each time it becomes the master of the UNIBUS. This is referred to as the burst size.

When the DR11-W is transferring one word per UNIBUS mastership, it is said to be operating in one-cycle or non-burst mode.

When the DR11-W is transferring more than one word per UNIBUS mastership, it is said to be operating in burst mode. The DR11-W internal logic implements two distinct types of burst mode:

- Two-cycle burst mode (two transfers per UNIBUS mastership).

- N-cycle burst mode (unlimited transfers per UNIBUS mastership).

The user device selects between burst and non-burst mode. If burst mode is selected, a toggle switch on the DR11-W further selects between two-cycle and n-cycle modes. See Figure 1-3 for the switch location and Table 2-6 for the switch settings. Placing the switch handle towards the edge of the module selects two-cycle burst. Placing the handle towards the middle of the module selects n-cycle burst.

#### NOTE

Allowing the DR11-W to transfer an unlimited number of words may lock out all other users of the UNIBUS, so n-cycle mode is also known as bus hog mode. For this reason, n-cycle bursts are not supported on the VAX-11/780, VAX-11/782, VAX-11/785, VAX 8600, and VAX8650. However, n-cycle bursts will operate under certain restricted conditions (for example, if the DR11-W is the only device connected to the UNIBUS adapter and the UNIBUS).

Table 2-6 Burst Size Selection

| Burst Size | Toggle<br>Switch Handle<br>Towards: |

|------------|-------------------------------------|

| Two-Cycle  | Edge of board                       |

| N-Cycle    | Middle of board                     |

## 2.4.5 Selecting the UNIBUS Time-Out Value

The UNIBUS is an asynchronous bus. This means that transactions on the UNIBUS are not synchronized by any master clock. Within certain limits, a device can operate as quickly or as slowly as necessary.

All UNIBUS interfaces which perform direct memory access must contain a feature known as UNIBUS slave-sync time-out. This feature sets the maximum time that the interface will wait for a slave device to respond on the UNIBUS. Without it, accessing a non-existent device could stall the UNIBUS indefinitely.

The DR11-W allows you to select from three different values of slave-sync time-out. This is done by optionally cutting out either capacitor C7 or capacitor C8. See Figure 1-3 for C7 and C8 locations and Table 2-7 for their values. The DR11-W is shipped set to the longest setting (that is, both capacitors installed). Normally, C8 should be removed (so as to use the shortest setting). Systems where the DR11-W is connected to a VAXBI bus through a DWBUA require the middle setting. Finally, if the system makes use of multiported memory, it may be necessary to select one of the longer time-out settings in order to avoid a false indication of a non-existent memory (NXM) error.

If the three supplied settings do not provide a long enough time-out, you can add a larger capacitor to the DR11-W module, parallel with either C7 or C8.

**Table 2-7** Slave Sync Time-out Selection

| Timeout in<br>Microseconds | Used With        | C8  | <b>C7</b> |

|----------------------------|------------------|-----|-----------|

| <unused></unused>          | Nothing          | Out | Out       |

| 12                         | Most systems     | Out | In        |

| 33                         | VAXBI systems    | In  | Out       |

| 45                         | Multiport memory | In  | In        |

#### NOTE

Use the shortest setting which provides error-free operation.

If the system is a VAX-11/780, VAX-11/782, VAX-11/785, VAX 8600, or VAX 8650 the timeout value must be less than 50 microseconds. Longer values will cause the VAX UNIBUS adapter to falsely report a hung UNIBUS.

# 2.4.6 Selecting the Burst Release Time-Out Value

The DR11-W is capable of transferring one, two, or n words each time it becomes the master of the UNIBUS. This is referred to as the burst size.

Burst mode is used to increase the overall UNIBUS throughput. It is only effective if the user device can deliver data rapidly (so that the UNIBUS does not sit idle while the DR11-W waits for the user's data).

If the DR11-W has become the UNIBUS master and has transferred at least one word of a two- or n-cycle burst, a timer is started. If the user device supplies the next word of data before the timer expires, the timer is started again. If, however, the user device fails to supply the data and the timer expires, then the DR11-W releases the UNIBUS.

This situation is harmless. The time-out ensures that the DR11-W does not continue to occupy the UNIBUS if the user device fails or momentarily stalls.

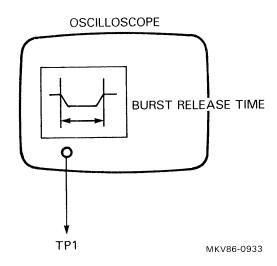

The burst release timer is adjustable by means of a trimpot, R80. See Figure 1-3 for the R80 location and Table 2-8 for timing adjustments. The minimum setting of the timer is 4 microseconds while the maximum setting is 30 microseconds. Like the slave-sync timer, additional capacitance can be added in parallel with the timing capacitor (C9), if needed.

Both the PDP-11 and VAX-11 off-line diagnostic programs contain a specific routine used to adjust the burst-release timer. For the VAX system, this is done using EVDRE Test 32. The correct command to invoke the test is:

#### DS> STA/SEC:BURST

For the PDP-11 system, this is done using CZDRL routine BRSTDL, invoked by answering YES to the question asking whether you wish to do burst data-late calibration.

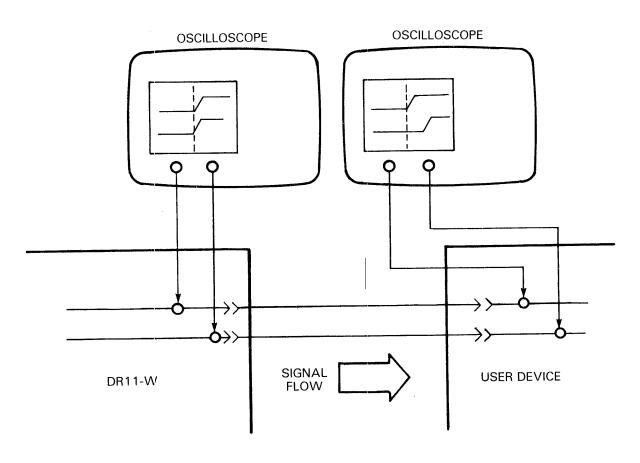

In both cases, an oscilloscope should be connected to test point 1 (TP1). See Figure 1-3 for the location of TP1. The burst release time is the time during which the TP1 waveform is logic-low. Figure 2-1 shows the waveform viewed with an oscilloscope connected to TP1.

Figure 2-1 Burst Release Time Waveform

# 2.4.7 Selecting the UNIBUS Interrupt Priority

Every device on the UNIBUS that can generate interrupts has a specific interrupt priority level. The overall priority scheme is described in the UNIBUS chapter of the *PDP-11 Architecture Handbook*. In general, it is a combination of the device's bus request level (BR level) and the device's position along the UNIBUS.

The specific BR level of the DR11-W is set by a jumper plug installed at E62. See Figure 1-3 for the location of the BR plug. The DR11-W is shipped from the factory with a BR5 plug installed. Other plugs may be ordered and installed to select BR7, BR6, or BR4. BR7 is the highest priority; BR4 is the lowest priority (see Table 2-9).

# 2.5 INSTALLATION AND CHECKOUT

Once the module setup is complete, the DR11-W may be installed in the system. Before installing, check that:

- A hex SPC slot is available in which to mount the module.

- At least 3.7 A of +5 Vdc are available from the power supply powering that SPC slot.

- The NPG jumper wire has been removed from backplane pins CA1 and CB1 of that slot. This is usually a short blue wire. It may already have been removed.

- The grant continuity card (G727, G7270, or G7273) has been removed from that slot.

The system that you are installing the DR11-W in may or may not be FCC compliant. (The United States Federal Communications Commission has established rules and regulations regarding the amount of radio and television interference which a computer may legally emit.) The installation of the DR11-W into your system varies depending upon whether or not your system is FCC compliant.

Table 2-8 Burst Release Timer Adjustment

| Timer<br>(Microseconds) | R80 Position          |

|-------------------------|-----------------------|

| 4 30                    | Fully CCW<br>Fully CW |

Table 2-9 BR Level Plug Part Numbers

| BR Level       | Plug Part<br>Number | Other Devices<br>Normally at<br>This Level      |

|----------------|---------------------|-------------------------------------------------|

| BR7            | 54-08782            | None                                            |

| BR6            | 54-08780            | Real-time clocks                                |

| BR5 (standard) | 54-08778            | Disks, tapes,<br>multi-line<br>synchronous comm |

| BR4            | 54-08776            | Single-line asynchronous comm, printers         |

#### 2.5.1 Installing the DR11-W in a Compliant System

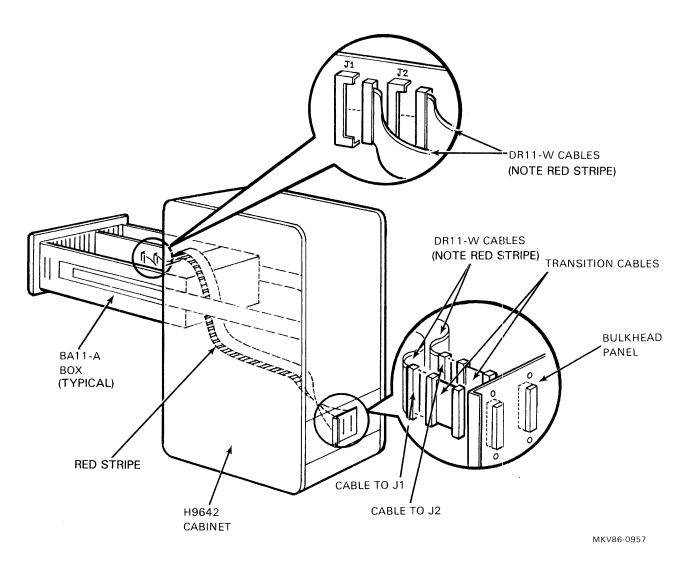

If your system is already FCC compliant, you must install the DR11-W in such a fashion so as to maintain this compliance. This is done by routing the DR11-W user cables through a bulkhead panel at the rear of the mounting cabinet (see Figure 2-2). This bulkhead panel filters the DR11-W signal lines in order to contain the high frequencies within the computer cabinet. The bulkhead connector also provides a more convenient place to connect the user cables, resulting in a neater, more maintainable installation.

The interface presented at the outside of the bulkhead panel is identical to the interface presented at the DR11-W module itself.

Figure 2-2 Installing the DR11-W in an FCC-Compliant System (Showing a PDP-11/24 or a PDP-11/44 and a BA11-A Box in an H9642 Cabinet)

#### 2.5.2 Mounting the Bulkhead in the Existing Picture Frame

Locate an unused opening in the picture frame. Remove the screws which hold the cover plate in place, then remove the cover plate itself.

Ensure that both the picture frame opening and the bulkhead connector that you are about to install are each clean and free of corrosion.

Dress the BC06-R cables (which connect to the DR11-W) out through the opening in the picture frame. Connect each cable to an adapter (part number 70-21988), then connect the adapter to one of the connectors in the bulkhead panel.

When you have connected both cables and adapters to the bulkhead panel, and have verified that the connections are correct and secure, place the bulkhead panel in the opening and install and tighten the mounting screw. Ensure that the screws are tight (so that the best possible ground connection is made).

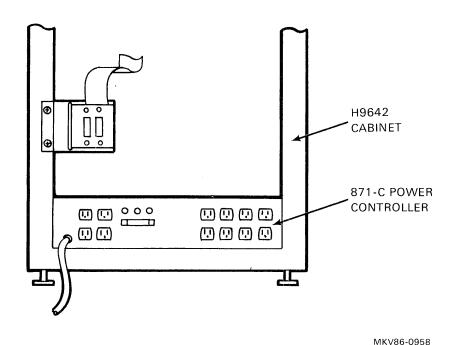

# 2.5.3 Installing the DR11-W in a Non-Compliant System

If your system is not FCC compliant, you can still take advantage of the convenience gained by use of the bulkhead panel (see Figure 2-3). In this case, the system may not already contain the picture frame which holds the bulkhead panels. Figure 2-3 shows the use of a single-hole picture frame which allows the bulkhead to be mounted. This **does not** make the system FCC-compliant.

Figure 2-3 Installing the DR11-W in a Non-Compliant System (H9642 Cabinet, 871-C Power Controller, and Add-On Picture Frame)

Once again, the interface presented at the outside of the bulkhead panel is identical to the interface presented at the DR11-W module itself.

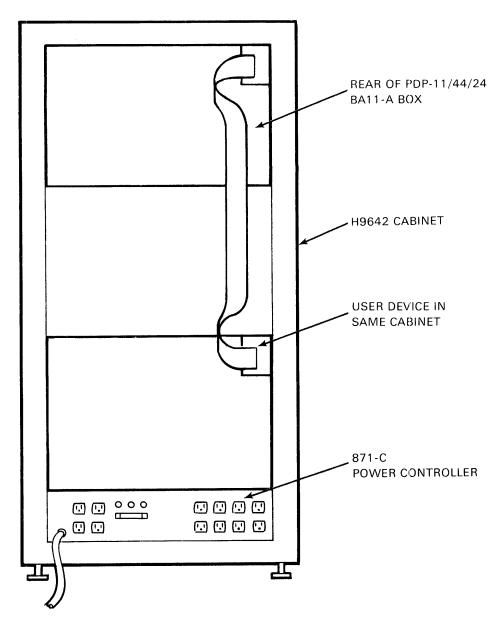

# 2.5.4 Installation Without the Bulkhead Panel

It is also possible to install the DR11-W without using the bulkhead panel. In this case, the cables are run directly from the connectors on the DR11-W module to the user device (see Figure 2-4).

This is only possible if your system is exempt from the FCC regulations.

MKV86-0959

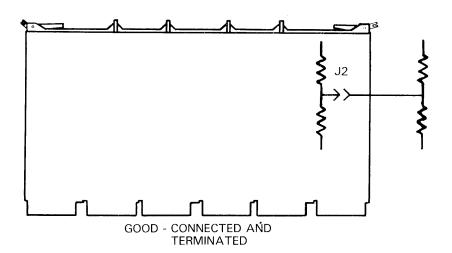

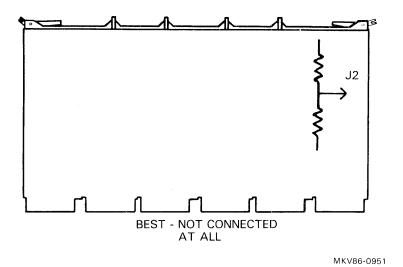

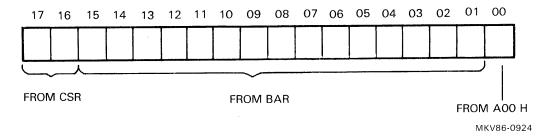

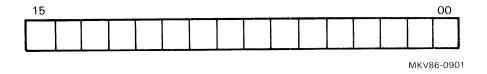

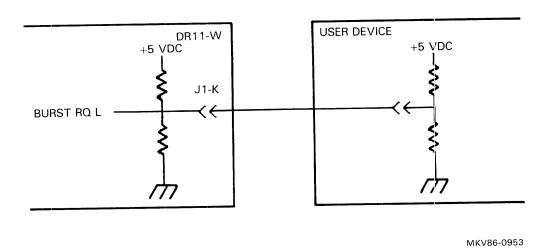

Figure 2-4 Installing the DR11-W Without the Bulkhead Panel (H9642 Cabinet, 871-C Power Controller, and User Device)