Unibus Troubleshooting user's manual

EK-FS002-OP-001

# **COMPANY CONFIDENTIAL**

digital equipment corporation • maynard, massachusetts

Copyright © 1977 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

This manual is intended for use by authorized DIGITAL personnel only. The information contained in this manual is intended to be used for analyzing product performance.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

# **CONTENTS**

|                |                                               | Page   |

|----------------|-----------------------------------------------|--------|

| CHAPTER 1      | INTRODUCTION                                  |        |

| 1.1            | SYSTEM OVERVIEW                               | . 1-1  |

| 1.2            | UNIBUS TROUBLESHOOTING TECHNIQUES             | . 1-2  |

| 1.3            | HI/LO TERMINATOR MARGIN CARDS                 | . 1-2  |

| 1.4            | UNIBUS VOLTAGE MARGIN TESTER BOX              | . 1-2  |

| 1.5            | SINGLE-ENDED MARGINING TECHNIQUE              | . 1-2  |

| CHAPTER 2      | UNIBUS CONFIGURATION                          |        |

| 2.1            | GENERAL                                       | . 2-1  |

| 2.2            | UNIBUS DEFINITIONS                            | . 2-1  |

| 2.2.1          | Bus Segment                                   | . 2-1  |

| 2.2.2          | Bus Cable                                     | . 2-2  |

| 2.2.3          | Bus Element                                   | . 2-2  |

| 2.2.4          | Lumped Load                                   | . 2-2  |

| 2.2.5          | Bus Jumper                                    | . 2-2  |

| 2.2.6          | Bus Terminator                                | . 2-4  |

| 2.2.7          | Semi-Lumped Load                              | . 2-4  |

| 2.2.8          | AC Unit Load                                  | . 2-5  |

| 2.2.9          | DC Unit Load                                  | . 2-6  |

| 2.2.10         | Unibus Length and Loading                     | . 2-6  |

| 2.3            | UNIBUS CONFIGURATION RULES                    | . 2-7  |

| 2.3.1          | Maximum Cable Length (Rule No. 1)             | . 2-8  |

| 2.3.2          | Maximum dc Loading (Rule No. 2)               | . 2-8  |

| 2.3.3          | Maximum Lumped Loading (Rule No. 3)           | . 2-8  |

| 2.3.4          | Skewed Cable Lengths (Rule No. 4)             | . 2-11 |

| 2.3.5          | Skewed Cable Lengths, Supplement (Rule No. 5) | . 2-13 |

| 2.3.6          | Rule Violations (Rule No. 6)                  | . 2-10 |

| 2.3.7          | System Acceptance (Rule No. 7)                | . 2-10 |

| 2.3.8          | Actual Bus Loading                            | . 2-17 |

| 2.4            | UNIBUS LATENCY                                | . 2-19 |

| 2.4.1          | Device Categories                             | . 2-22 |

| 2.4.2          | NPR Calculations for T1                       | . 2-22 |

| 2.4.3          | Latency Tolerance Calculations                | . 2-23 |

| 2.4.4          | BR Devices                                    | . 2-23 |

| 2.4.5          | Unibus Loading Rules                          | . 2-23 |

| 2.4.3<br>2.5   | BUS BUSY TEST TECHNIQUES                      | . 2-24 |

|                | Bus Busy and Latency Tolerance                | . 2-24 |

| 2.5.1<br>2.5.2 | Calculating Nominal Bus Busy Times            | . 2-25 |

| 2.5.2<br>2.5.3 | Measuring Bus Busy Times                      | . 2-27 |

| 2.5.3<br>2.5.4 | Configuration Tables                          | . 2-30 |

# CONTENTS (Cont)

|           |                                                            | Page   |

|-----------|------------------------------------------------------------|--------|

| CHAPTER 3 | TROUBLESHOOTING                                            |        |

| 3.1       | GENERAL                                                    | 3-1    |

| 3.2       | TIMING CONSIDERATIONS                                      |        |

| 3.2.1     | DATO-DATOB                                                 |        |

| 3.2.2     | DATI-DATIP                                                 |        |

| 3.2.3     |                                                            |        |

|           | Interrupt Transactions                                     |        |

| 3.2.4     | High-Frequency Cable Losses                                |        |

| 3.2.5     | Peripheral Data Rate                                       |        |

| 3.3       | PROPAGATION DELAY                                          |        |

| 3.3.1     | Line Termination Technique                                 | 3-11   |

| 3.4       | CABLE AND CONTACT RESISTANCE LOSSES                        | 3-12   |

| CHAPTER 4 | BUS MARGINING                                              |        |

| 4.1       | GENERAL                                                    | . 4-1  |

| 4.2       | BUS QUIESCENT LEVELS                                       | . 4-1  |

| 4.2.1     | Quiescent Conditions                                       |        |

| 4.2.2     | Multiple Bus System Considerations                         |        |

| 4.2.3     | Grant Line Termination                                     |        |

| 4.3       | HI/LO TERMINATOR BUS MARGINING                             |        |

| 4.4       | UNIBUS VOLTAGE MARGIN TESTER BOX                           |        |

| 4.4.1     | Functional Description                                     |        |

| 4.4.2     | UVM-TA Operation and Test Procedures                       | 4-13   |

| 4.5       | SINGLE-ENDED MARGINING                                     |        |

| 4.5.1     | Setup and Operation (Using M9308 Single-Ended Margin Head) |        |

| 4.5.2     | Single-Ended Circuit Consideration                         |        |

| 4.5.3     | SACK Timeout                                               |        |

| 4.6       | MODIFYING M930 TERMINATOR CARD                             |        |

|           |                                                            |        |

| 4.6.1     | Equipment Required                                         |        |

| 4.6.2     | Modifying the M930                                         |        |

| 4.6.3     | Procedure for Use                                          | . 4-23 |

| CHAPTER 5 | UVM-TA TESTER                                              |        |

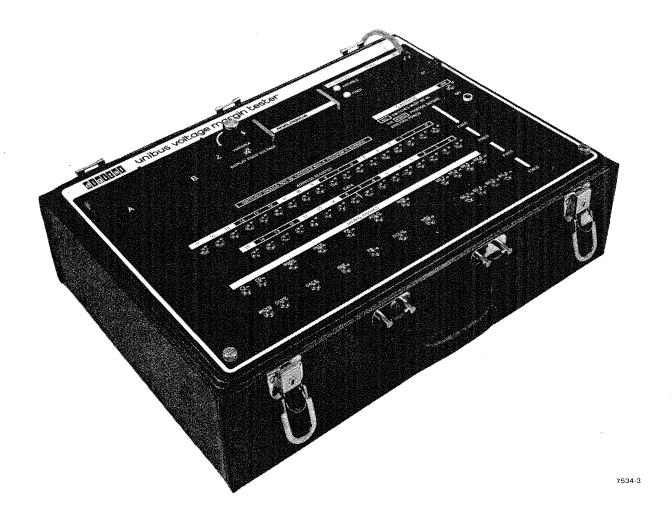

| 5.1       | UVM-TA OVERVIEW                                            | . 5-1  |

| 5.2       | TESTER KIT COMPONENTS                                      | . 5-1  |

| 5.3       | TESTER SPECIFICATIONS                                      | . 5-2  |

| 5.4       | UNPACKING PROCEDURE                                        | . 5-3  |

| 5.5       | ACCEPTANCE TEST                                            |        |

| 5.6       | CONTROLS AND INDICATORS                                    |        |

| 5.7       | OPERATING PROCEDURE                                        |        |

| 5.8       | MAINTENANCE PHILOSOPHY                                     |        |

| i.9       | PREVENTIVE MAINTENANCE                                     |        |

| 5.10      | CORRECTIVE MAINTENANCE                                     |        |

| .11       | DISASSEMBLY/ASSEMBLY                                       |        |

|           | DIDADDLIMDLI/ADDLIMDLI                                     | . 50   |

# CONTENTS (Cont)

APPENDIX A ECO HISTORY AND REWORK

| APPENDIX B | M9202-2 UNIBUS JUMPER INSTALLATION                  |            |

|------------|-----------------------------------------------------|------------|

| APPENDIX C | AC AND DC LOAD TABLE                                |            |

| APPENDIX D | BUS LOADS                                           |            |

|            |                                                     |            |

|            | FIGURES                                             |            |

| Figure No. | Title                                               | Page       |

| 2-1        | Lumped Loads (Example A)                            | 2-3<br>2-4 |

| 2-2        | Lumped Loads (Example B)                            |            |

| 2-3        | Semi-Lumped Loads (Example C)                       | 2-5        |

| 2-4        | Bus Load Example                                    | 2-7        |

| 2-5        | Rule No. 3 Violation (Block Diagram)                | 2-8        |

| 2-6        | Rule No. 3 Violation (Waveform Example)             | 2-9        |

| 2-7        | Rule No. 3 Implementation (Block Diagram)           | 2-9        |

| 2-8        | Rule No. 3 Implementation (Waveform Example)        | 2-10       |

| 2-9        | Multiple Bus System Example                         | 2-10       |

| 2-10       | Rule No. 4 Violation (Block Diagram)                | 2-11       |

| 2-11       | Rule No. 4 Implementation (Example A) Block Diagram | 2-11       |

| 2-12       | Rule No. 4 Implementation (Example B) Block Diagram | 2-12       |

| 2-13       | Rule No. 4 Violation (Waveform Example)             | 2-12       |

| 2-14       | Rule No. 4 Implementation (Waveform Example)        | 2-13       |

| 2-15       | Skewed Cable Length Violation                       | 2-14       |

| 2-16       | Skewed Cable Length Violation (Waveform Example)    | 2-14       |

| 2-17       | Violation of Rule No. 5 (Waveform Example)          | 2-15       |

| 2-18       | Implementation of Rule No. 5 (Waveform Example)     | 2-15       |

| 2-19       | Actual Bus Loads Example                            | 2-1/       |

| 2-20       | Algorithm to Determine NPR Sequence                 | 2-20       |

| 2-21       | Unibus Length Between Device and Memory             | 2-28       |

| 2-22       | Single-Cycle Transaction                            | 2-29       |

| 2-23       | Double-Cycle Transaction                            | 2-30       |

| 2-24       | DLT Configurations                                  | 2-31       |

| 3-1        | Unibus Troubleshooting Flowchart                    | 3-2        |

| 3-2        | System Cabling Configuration Example                | 3-5        |

| 3-3        | Transmission Line Circuit Example                   | 3-7        |

| 3-4        | BC11-A Unibus Cable Delay Example                   | 3-7        |

| 3-5        | BC11 Unibus Cable Impedance Example                 | 3-8        |

| 3-6        | Impedance Mismatch Example                          | 3-9        |

| 3-7        | Impedance (Low Resistance) Mismatch Example         | 3-9        |

| 3-8        | Mismatch Reflection Curve Example                   | 3-10       |

# FIGURES (Cont)

| Figure No. | Title                                                    | Page   |

|------------|----------------------------------------------------------|--------|

| 3-9        | BC11 Unibus Cable Mismatch (Waveform Example)            | . 3-10 |

| 3-10       | System Device Impedance Example                          | . 3-11 |

| 3-11       | Line Termination Technique Example                       | . 3-12 |

| 3-12       | Cable Resistance Problems Example                        | . 3-13 |

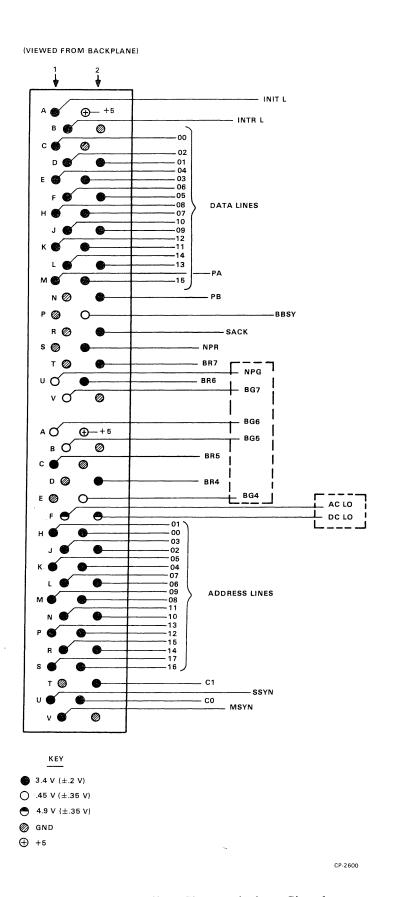

| 4-1        | Unibus Slot Backplane Signals                            | . 4-3  |

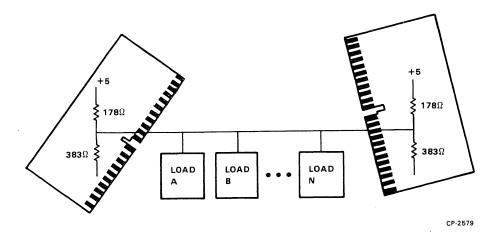

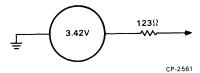

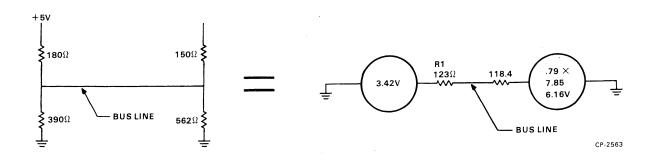

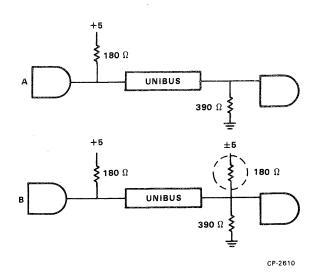

| 4-2        | Low True Unibus Line                                     | . 4-4  |

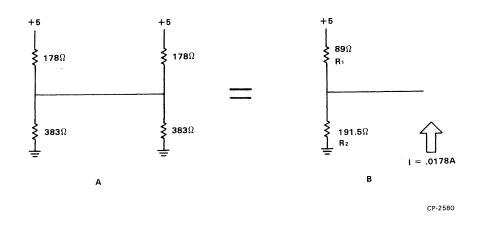

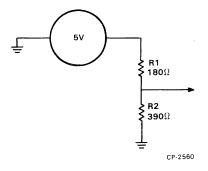

| 4-3        | Equivalent Unibus Line Circuit                           | . 4-4  |

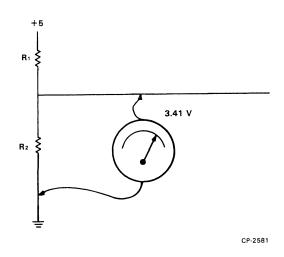

| 4-4        | Quiescent dc Level Example                               | . 4-5  |

| 4-5        | Load Current Leakage Example                             | . 4-5  |

| 4-6        | Ouiescent Level vs. Bus Loading (Worst Case)             | . 4-6  |

| 4-7        | Margining Multiple Bus Systems                           | . 4-7  |

| 4-8        | Grant Line Bus Margining Technique                       | . 4-8  |

| 4-9        | Margining Cards                                          | . 4-5  |

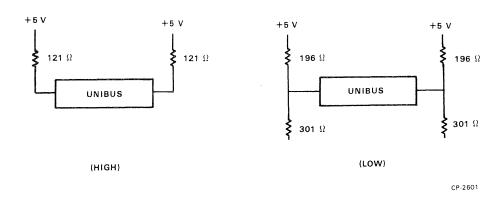

| 4-10       | Hi/Lo Terminator Circuit Example                         | . 4-10 |

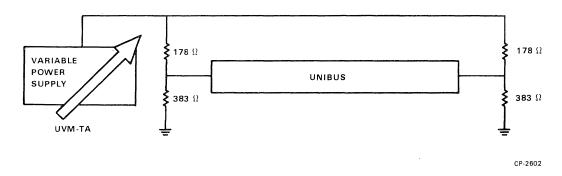

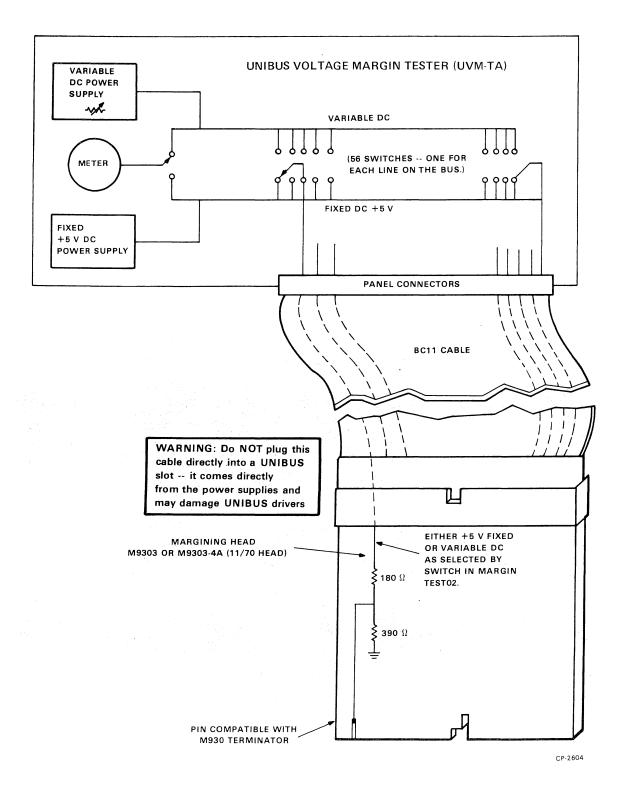

| 4-11       | UVM-TA Circuit Representation                            | . 4-11 |

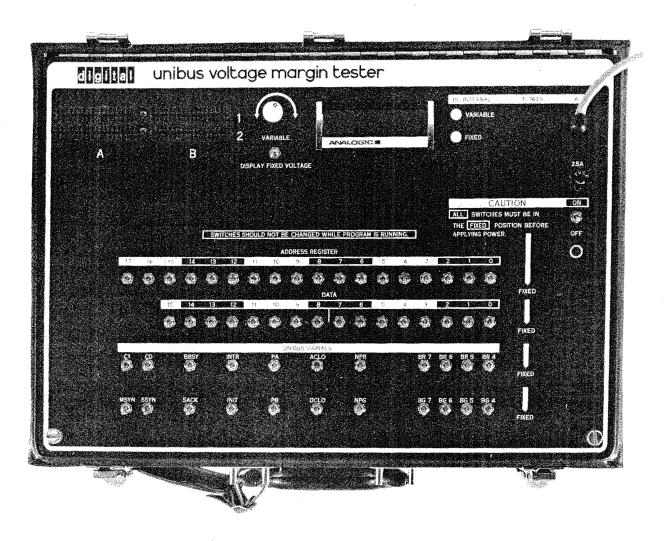

| 4-12       | Controls and Indicators                                  | . 4-11 |

| 4-13       | UVM-TA Block Diagram                                     | . 4-12 |

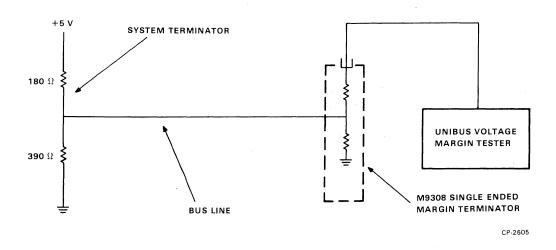

| 4-14       | Single-Ended Circuit Example                             | . 4-15 |

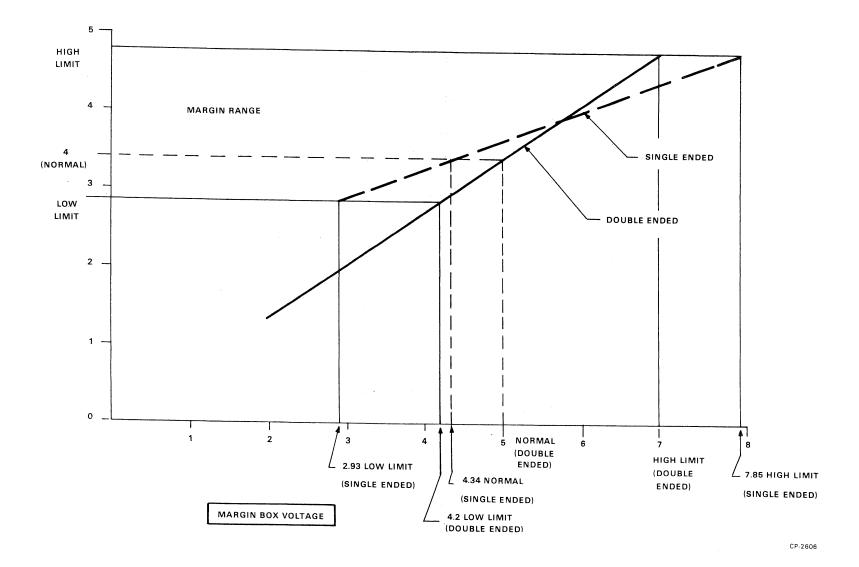

| 4-15       | Ouiescent Voltage vs UVM-TA Voltage                      | . 4-18 |

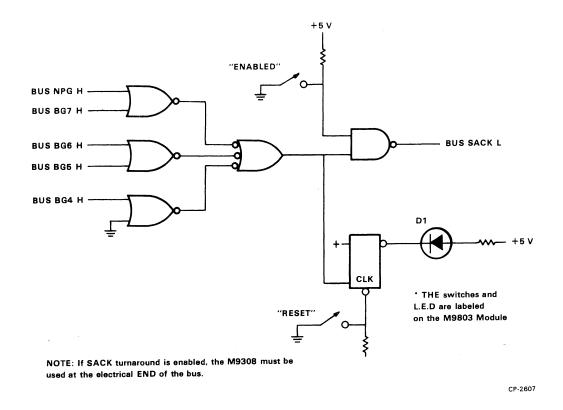

| 4-16       | M9308 Termination Circuit Example                        | . 4-20 |

| 4-17       | M9308 SACK Turnaround Logic                              | . 4-22 |

| 4-18       | M930 Modification Example                                | . 4-23 |

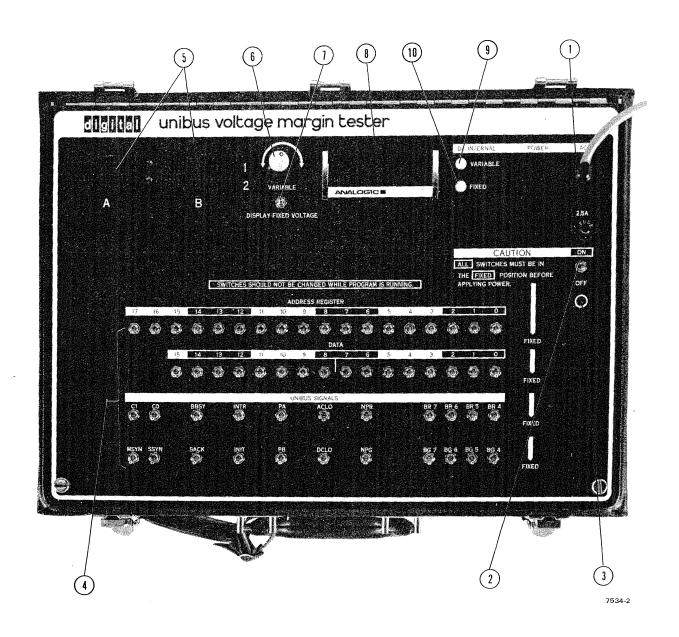

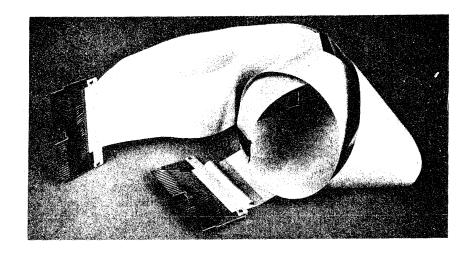

| 5-1        | Unibus Voltage Margin Tester Box                         | . 5-2  |

| 5-2        | Controls and Indicators (Indexed)                        | . 5-4  |

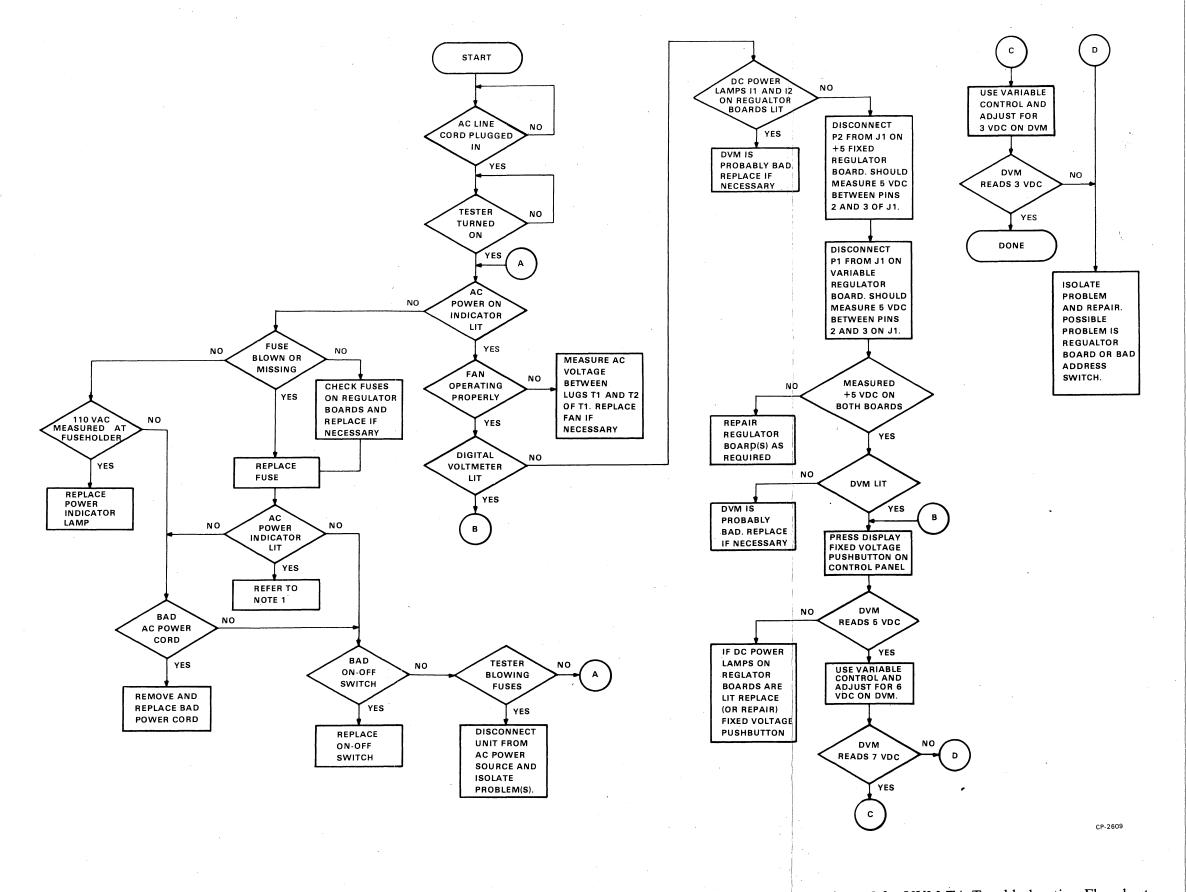

| 5-3        | UVM-TA Troubleshooting Flowchart                         | . 5-7  |

|            |                                                          |        |

|            | TABLES                                                   |        |

| Table No.  | Title                                                    | Page   |

| 2-1        | Realistic Load Values                                    | . 2-18 |

| 2-2        | Maximum NPR Rates of the NPR Devices with Variable Speed | . 2-19 |

| 2-3        | Device Delay (Ddy)                                       | . 2-26 |

| 2-4        | Memory Access Delay (Dma)                                | . 2-26 |

| 2-5        | Transmitter/Receiver Delay (Dtr)                         | . 2-26 |

| 4-1        | Bus Quiescent Levels                                     | . 4-1  |

| 4-2        | Terminator Application Data                              | . 4-19 |

| 5-1        | Tester Kit Components                                    | . 5-1  |

| 5-2        | Controls and Indicators (Indexed)                        | . 5-5  |

| 5-3        | Preventive Maintenance Schedule                          | . 5-6  |

|            |                                                          |        |

This user's manual is a detailed troubleshooting and reference guide for isolating Unibus problems related to (a) systems which are inoperative and (b) systems which are marginal.

Due to the complexities and terminology associated with the Unibus, this manual also contains descriptions, definitions and reference material relative to the Unibus and associated hardware.

#### NOTE

This manual does not define the optimum system configurations for throughput or latency tolerence which may be dependent on customer usage and applications environment.

This manual supersedes Unibus Margin Tester user's guide, document number EK-FS002-OP-PRE.

#### **NOTE**

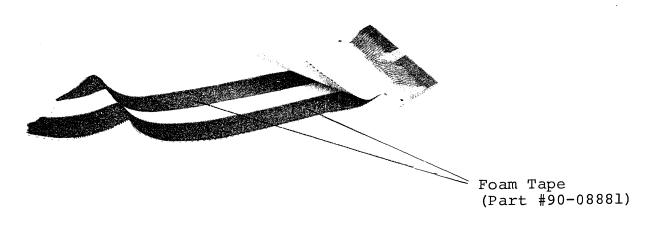

The M9308 Margin Heads are direct replacements for the M9303 Margin Heads. However, the M9308 allows for greater margining voltage (2.93 to  $7.85~\rm V$ ) than the M9303 (4.2 to  $7.0~\rm V$ ).

•

# CHAPTER 1 INTRODUCTION

## 1.1 SYSTEM OVERVIEW

Most of the PDP-11's internal electronic components and system peripherals are connected to and communicate with each other through the Unibus. There are 56 lines on the bus that handle such signals as address, data and control information. Each device, including memory locations and peripheral device registers, is assigned one address on the Unibus.

#### NOTE

This manual is intended for use by authorized DIG-ITAL EQUIPMENT CORPORATION personnel only. Information contained in this manual is neither intended to be a product specification nor to supersede or replace any other published information that is available to customers or users of DIGITAL products.

Some PDP-11 system configurations experience permanent and intermittent bus failures due to improper signal termination and loading techniques. (These problems can exist even when the proper guidelines and rules for system configurations are followed.) This manual will assist in the proper procedures for isolating configuration and Unibus problems, and corrective action that can be implemented for better system operation.

Due to complexity of system configuration and operation, all Unibus systems are subject to additional electrical and mechanical factors which may become even more relevant when, and if, these factors interact. If this interaction becomes large enough, it can cause false signal levels that can seriously effect system operation. Some of the signal conditions that can occur because of these additional electrical and mechanical factors follow.

- 1. Signal caused by dc loading of receivers and drivers

- 2. Signal loss caused by nonzero resistance of BC11 jumper cable

- 3. Signal loss caused by connector contact resistance

- 4. Standing wave reflections from devices on the line

- 5. Increased propagation delay caused by devices on the line and high frequency cable losses

- 6. Crosstalk on bus lines caused by the cable or by devices attached to the bus

- 7. Signal skew caused by multiple high-frequency loading on different lines by a device

## 1.2 UNIBUS TROUBLESHOOTING TECHNIQUES

Currently, there are three troubleshooting aids that can be used to troubleshoot and isolate Unibus problems.

- 1. Hi/Lo Terminator Margin Cards

- 2. Unibus Voltage Margin Tester Box

- 3. Single-Ended Margining Technique

A fourth troubleshooting aid is the flowchart (refer to Chapter 3) which is organized into a general flow and reference diagram which points out particular sections that contain troubleshooting techniques and supportive information. The supportive information will aid in the understanding of, and provide background for, the use of the Unibus Troubleshooting techniques outlined in Chapter 3 of this manual.

#### 1.3 HI/LO TERMINATOR MARGIN CARDS

The Hi/Lo Terminator Margin Cards are used to replace the M930 bus terminator in the PDP-11 system for margining purposes. The Hi/Lo Terminator Cards are used as a go/no go test and are not to be installed in the system on a permanent basis. (Refer to Chapter 4 for additional operational procedures and descriptions.)

## 1.4 UNIBUS VOLTAGE MARGIN TESTER BOX

The Unibus Voltage Margin Tester Box is designed to test Unibus driver and receiver terminating networks for the PDP-11 system. The tester is connected to the Unibus through special terminator cards called margining heads. When the tester is cabled to the Unibus, the operator can select which signal(s) (single, groups, or all) is to be tested. (Refer to Chapter 4 for additional operational procedures and descriptions.)

#### 1.5 SINGLE-ENDED MARGINING TECHNIQUE

For some PDP-11 processors (e.g., PDP-11/04 and PDP-11/34), it is not possible to use the M930 margining heads with the Unibus Voltage Margin Tester Box. This is due to additional hardware on the terminator module (boot strap function, sack turnaround, etc.) which must be present in order for the processor to operate normally. It is for these processors that the Unibus Tester Box single-ended margining technique has been developed. However, this technique can be used with any Unibus processor. (Refer to Chapter 4 for additional operational procedures and techniques.)

# CHAPTER 2 UNIBUS CONFIGURATION

#### 2.1 GENERAL

After the Unibus option configuration (based on NPR latency, physical location, etc.) is determined, these options must be interconnected using the correct procedure and techniques.

The definitions, rules and guidelines outlined in this section are designed to aid you in configuring an electrically reliable Unibus. These rules and guidelines are intended for new systems and are not to be considered as a justification for any changes in existing systems, unless Unibus related problems are encountered and cannot be resolved in any other way.

The configuration rules (Paragraph 2.3) ensure, with reasonable confidence, that Unibus segments will be electrically reliable, i.e., resulting dc bus levels will guarantee an adequate noise margin, and reflections from lumped loads will not be excessive.

To configure a Unibus system, the required order of options on the Unibus, based on NPR latency, physical location, etc., should first be determined. The rules will then determine the length the Unibus cable interconnecting the options and the number and location of bus repeaters. If the number of bus repeaters is excessive, total cable length can sometimes be reduced by rearranging the order of options on the bus (again, paying close attention to NPR latency, etc.). Then, after reapplying the rules in this guide, one or more bus repeaters may be eliminated or located further down the bus to optimize system speed. For large systems, more than one pass of this procedure may be necessary to achieve satisfactory results.

A reasonable effort should always be made to ensure total cable length is as short as possible, particularly if one or more bus repeaters can be eliminated in the process. Bus repeaters are costly and slow down the system. Before implementing configuration rules, the user should carefully read and understand the definitions that follow.

#### 2.2 UNIBUS DEFINITIONS

Prior to configuring the Unibus, review the definitions outlined in Paragraphs 2.2.1 through 2.2.10.

# 2.2.1 Bus Segment

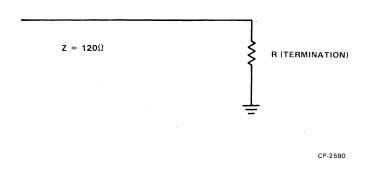

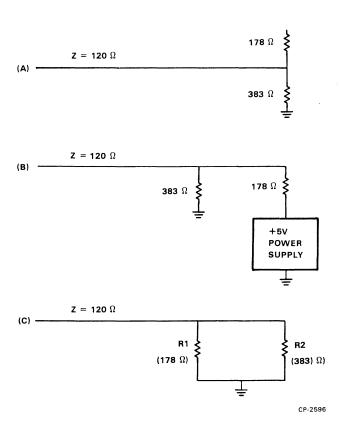

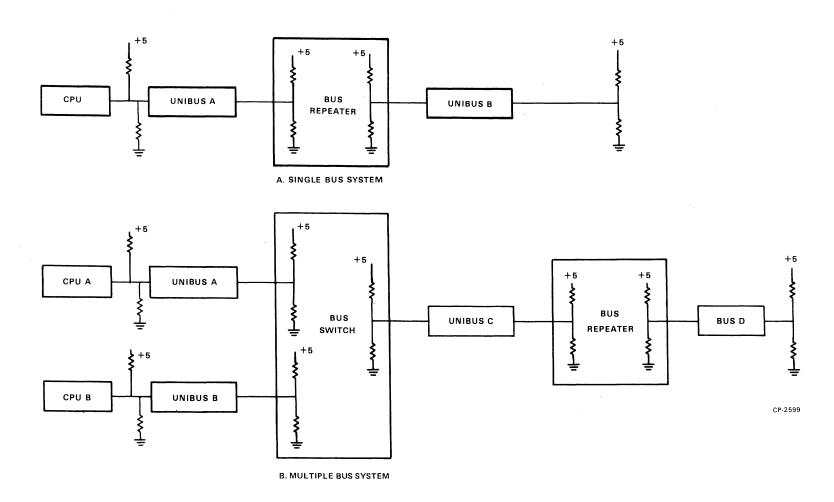

The Bus Segment is defined as that portion of a Unibus system between and including two terminators. A bus segment consists of: a terminator, a 120 ohm transmission path (cable) with options containing drivers and receivers attached to it, and another terminator in that order. A single bus system is one which has one bus segment. A multiple bus system is one which has more than one bus segment, usually separated by bus repeaters (DB11s) or bus switches (DT03s – which contain bus repeaters).

2.2.2 Bus Cable

A Bus Cable is defined as cable connecting two backplanes which acts as a 120 ohm transmission line with a length of two feet or more. A BC11A cable is defined to be both a cable and a bus element. For our purposes, the cable is a subset of the bus element and should be treated as such. The following bus elements are Unibus cables:

```

2-foot Unibus cable (60.96 cm)

BC11A-2

3-foot Unibus cable (91.44 cm)

BC11A-3

5-foot Unibus cable (1.52 m)

BC11A-5

6-foot Unibus cable (1.82 m)

BC11A-6

8.5-foot Unibus cable (2.59 m)

BC11A-8F

10-foot Unibus cable (3.04 m)

BC11A-10

15-foot Unibus cable (4.57 m)

BC11A-15

20-foot Unibus cable (6.07 m)

BC11A-20

25-foot Unibus cable (8.60 m)

BC11A-25

30-foot Unibus cable (9.14 m)

BC11A-30

24-inch folded Unibus cable (60.96 m)

M9202

```

The M9202 is considered to be a cable (for the purposes of this manual) because it contains 2 feet of 120 ohm cable.

#### 2.2.3 Bus Element

A Bus Element is defined as any module, backplane, cable or group of these items that has a common designation which has a direct electrical connection to one or more Unibus signal lines (other than AC LO L or DC LO L). For example, an M930 terminator, an M7821 module, a BB11 backplane, a BC11 cable, and an RK11 controller are Unibus elements. An H720 power supply, an LA36 DECwriter and a BA11 expander box are not Unibus elements.

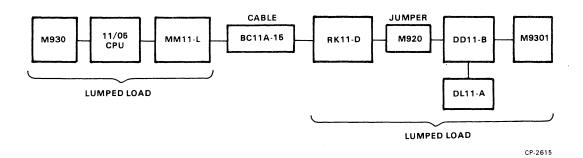

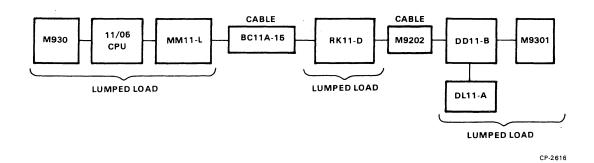

2.2.4 Lumped Load

A Lumped Load is defined as a group of Unibus elements, other than cables or jumpers, which are interconnected via Unibus jumpers and direct wiring (backplane wire, PC etch) only. The group is not a lumped load if it uses a Unibus cable to interconnect the Unibus elements or if the elements are separated by a bus repeater. (Be certain the difference between "jumper" and "cable" is understood see Figures 2-1 and 2-2.)

2.2.5 Bus Jumper

A Bus Jumper is defined as a Unibus element connecting two backplanes which contains less than two feet of cable. The following elements are Unibus jumpers:

```

M920

jumper

jumper with boards 1.27 cm (0.5 in) apart

M9200

jumper/terminator

M981

6-inch cable (15.24 cm)

BC11A-0

```

The BC11A-0 is considered to be a jumper (for the purposes of this manual) because it contains less than 60.96 cm (2 feet) of 120 ohm cable.

In this system, there are two lumped loads:

- 1. M930, 11/05 CPU, and MM11-L

- 2. RK11-D, DD11-B, DL11-A, and M9301

Suppose the M920 is replaced by an M9202:

Now there are three lumped loads:

- 1. M930, 11/05 CPU, and MM11-D

- 2. RK11-D

DD11-B, DL11-A, and M9301

Figure 2-1 Lumped Loads (Example A)

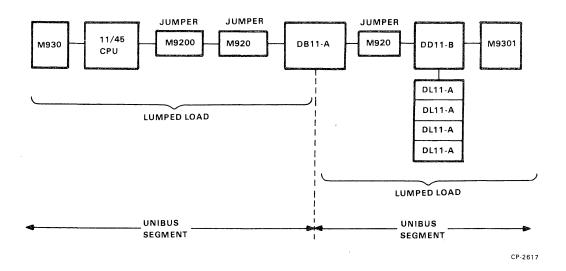

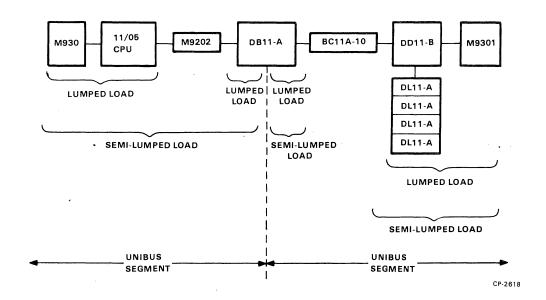

This system has two Unibus segments separated by a bus repeater, so the system has two lumped loads:

- 1. M930, 11/45 CPU, DB11-A (left side)

- 2. DB11-A (right side), DD11-B, four DL11-As, M9301

#### **NOTE**

These examples are for illustrative purposes only and do not represent practical configurations.

Figure 2-2 Lumped Loads (Example B)

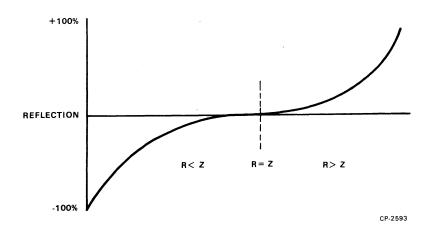

### 2.2.6 Bus Terminator

A Bus Terminator is defined as a Unibus element or part of an element containing a resistive network which connects to the end of a Unibus segment and matches the 120 ohm characteristic impedance of the Unibus transmission path. The M930 and M9306 are Unibus terminators if they connect to the Unibus. The following bus elements *contain* Unibus terminators:

| M981      | jumper/terminator                               |

|-----------|-------------------------------------------------|

| M9300     | Unibus B terminator (M930 + NPR logic)          |

| M9301     | bootstrap/terminator                            |

| M9302     | M930 with SACK return                           |

| DT03      | bus switch                                      |

| DB11-A    | bus repeater                                    |

| PDP-11/04 | CPU (NOTE: other CPUs also contain terminators) |

A Unibus segment must always have a Unibus terminator at each end of its 120 ohm transmission path.

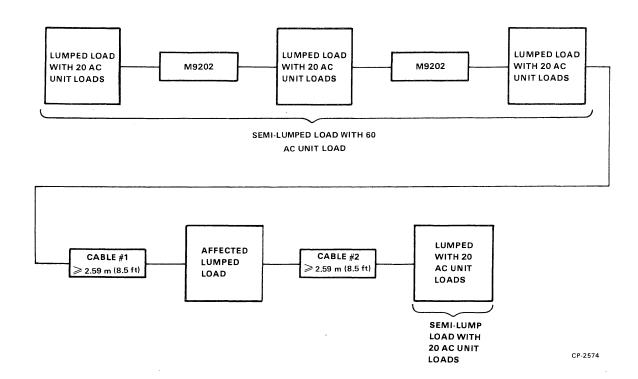

#### 2.2.7 Semi-Lumped Load

A semi-lumped load is defined as a group of lumped loads interconnected by 91.44 cm (3 ft) or less of cable (M9202, BC11-2 or BC11-3) and not separated by a bus repeater. Refer to Figure 2-3.

This system has two Unibus segments, with a total of four lumped loads and three semi-lumped loads.

#### Lumped loads:

- 1. M930, 11/45 CPU

- 2. DB11-A (left side)

- 3. DB11-A (right side)

- 4. DD11-B, four DL11s, M9301

#### Semi-lumped loads:

- 1. M930, 11/45 CPU, DB11-A (left side)

- 2. DB11-A (right side)

- 3. DD11-B, four DL11s, M9301

Figure 2-3 Semi-Lumped Loads (Example C)

#### 2.2.8 AC Unit Load

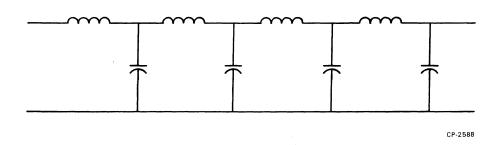

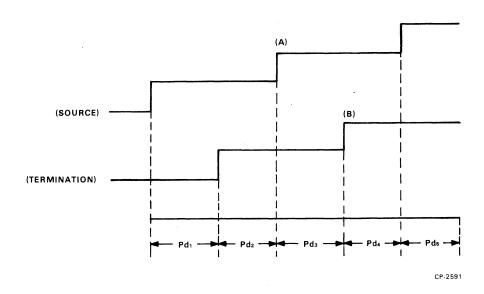

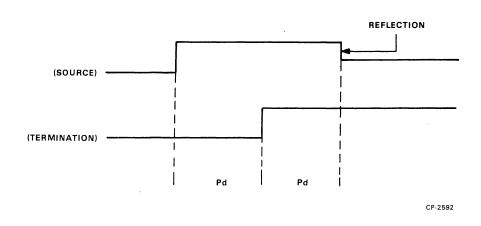

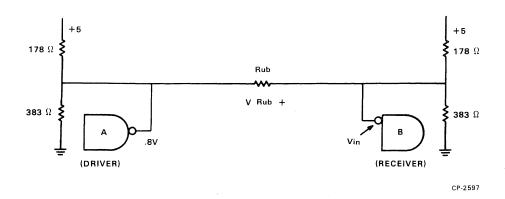

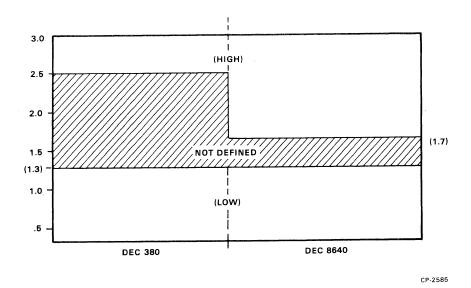

An ac unit load is defined as a number related to the impedance that a Unibus element presents to a Unibus signal line (due to backplane wiring, PC etch runs, receiver input loading, and driver output loading). This impedance load on a transmission line causes a "reflection" to occur when a step is sent down the line. This reflection shows up on an oscilloscope as a spike occurring shortly after asserting or unasserting edge. An ac unit load is nominally 9.35 pF of capacitance. Nine lumped ac loads reflect 20 percent and 20 lumped ac loads reflect 40 percent of a 25 ns risetime step. AC loads must be distributed on the Unibus in the manner described by the rules in this manual in order to provide bus operation with reflections guaranteed to be at or less than a tolerable level.

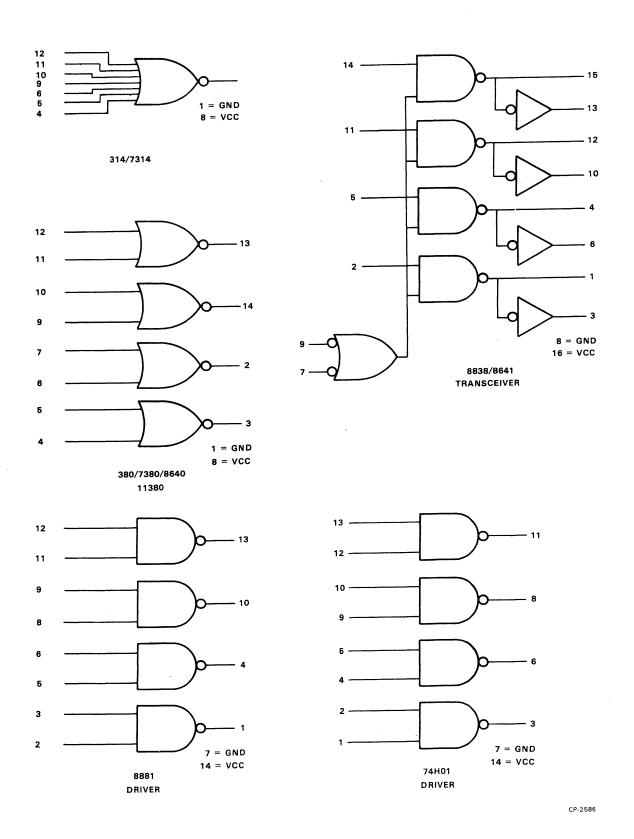

The ac unit load rating of Unibus elements is usually based on the greatest of the capacitances that the element presents to the BBSY, SSYN, and MSYN Unibus signal lines. Appendix C contains the ac loading specifications of the Unibus elements. If the element is customer-designed, its ac unit loading must be determined from a reasonable estimate of the equivalent capacitance presented to the Unibus.

#### 2.2.9 DC Unit Load

A dc unit load is defined as a number related to the amount of dc leakage current that a Unibus element presents to a Unibus signal line which is high (undriven). A dc unit load is nominally  $105~\mu A$  ( $80~\mu A$  – receiver plus  $25~\mu A$  – driver). However, the dc unit load rating of a bus element is not strictly based on the element's signal line that has the greatest leakage, (e.g., dc leakage is less important on D lines than it is on SSYN). The dc unit loading of an element should always be obtained from the specification for that element (see Appendix D). It should not be obtained from a calculation of the receiver and driver leakage current, unless the element is custom-designed and is not listed in the applicable documentation.

#### 2.2.10 Unibus Length and Loading

The Unibus is a transmission line on which data transfers are asynchronous and interlocked. Significant electrical delay affecting system operation may, therefore, be imposed through unnecessarily long Unibus cables.

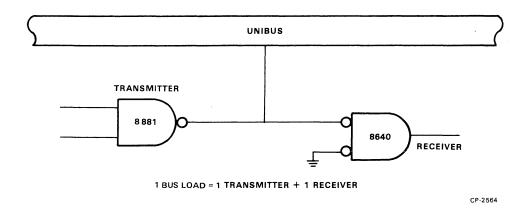

With ribbon cable the maximum length is 15.24 m (50 ft). For proper operation, the length of taps or stubs must be minimized. The Unibus signals should have receivers and transmitters in one place (near the Unibus cable) to act as a buffer between the Unibus and the signal lines carrying Unibus signals within the equipment. The maximum length of ribbon cable is obtainable only if the individual tap lengths are less than 5.08 cm (2 in), including printed circuit etches and if the loading is not more than one standard bus load. One bus load is defined as one transmitter and one receiver (see Figure 2-4).

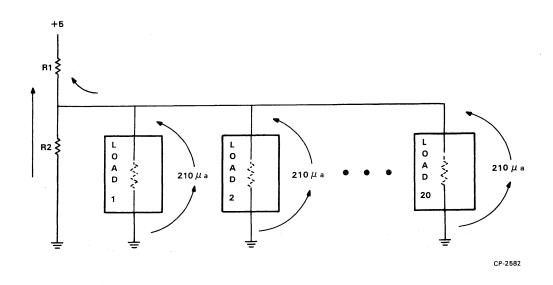

The Unibus is limited to a maximum of 20 bus loads. This limit is set to maintain a sufficient noise margin. For more than 20 bus loads, a Unibus repeater option (DB11-A) is used.

Figure 2-4 Bus Load Example

#### 2.3 UNIBUS CONFIGURATION RULES

The following rules and guidelines are intended to be used for new systems and/or existing systems that experience Unibus problems. The seven rules are listed below for quick reference. A more detailed description, comments, and suggestions are described in the following paragraphs.

Rule No. 1 (Maximum cable length) – The total length of Unibus cable in a Unibus segment should not exceed 15.24 m (50 ft).

Rule No. 2 (Maximum dc loading) – The total number of dc unit loads on a Unibus signal line should not exceed 20. (See Appendix D.)

Rule No. 3 (Maximum lumped loading) – No lumped load on a Unibus segment should contain more than 20 ac unit loads unless the entire segment consists of one lumped load.

Rule No. 4 (Skewed cable lengths) – If (a) a lumped load (called the "affected lumped load") has 2.59 m (8.5 ft) or longer cables connected to both bus in and bus out and (b) the sum of the ac unit loads in the two *lumped loads* connected to the opposite ends of the cables exceeds 18, or (c) the sum of the ac unit loads in the two semi-lumped loads connected to the opposite ends of the cables exceeds 36, then the lengths of these cables should differ by 1.52 m (5 ft) or more with the longer cable being on the end with the greatest number of ac unit loads (if there is a practical choice).

Rule No. 5 (Skewed cable lengths, supplement) – If the length of one of the cables connected to the affected lumped load in Rule No. 4 must be increased because of that rule, then the longer cable should have at its opposite end of the semi-lumped load with the greater number of ac unit loads. This rule should be implemented only if it is practical to do so, i.e, in cases where its implementation will not increase total cable length more than 1.52 m (5 ft).

Rule No. 6 (Violation of Rules No. 1 through No. 5) – Rules No. 1 through No. 5 should not be grossly violated. If a bus segment violates a rule slightly, and for practical reasons reconfiguring is undesirable, then the segment *must* pass voltage-margin tests (a) when the system is originally configured and (b) when any Unibus element is added, deleted, or swapped (including the swapping of a defective module or backplane).

Rule No. 7 (System acceptance) – Even if rules No. 1 through No. 5 are implemented, all Unibus segments of a system should be voltage margined after the system is configured.

# 2.3.1 Maximum Cable Length (Rule No. 1)

If Rule No. 1 is violated, (a) the dc drop across the bus, when driven at one end and received at the other, may be excessive, and (b) far-end crosstalk may be excessive. In calculating lengths, the M920 should be considered as zero feet, the M9202 as 60.96 cm (2 ft), and the BC11A-0 as 15.24 cm (6 in).

If the length of a segment exceeds 15.24 m (50 ft), reconfiguring (changing the order of bus elements) may reduce the length. If that fails, a DB11-A bus repeater will be necessary.

### 2.3.2 Maximum dc Loading (Rule No. 2)

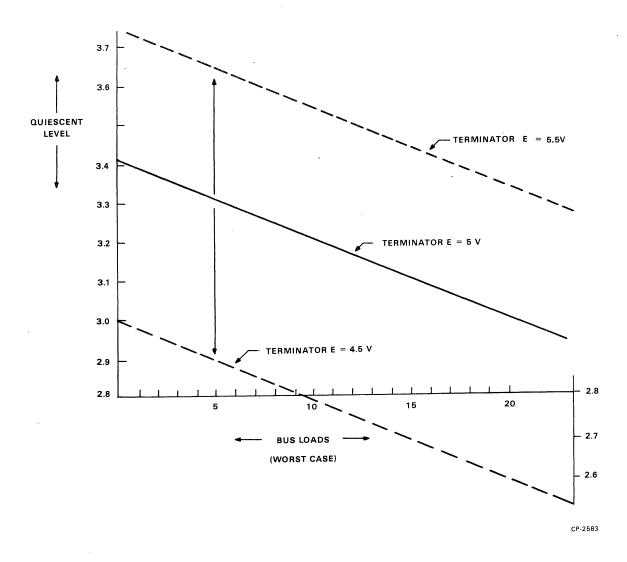

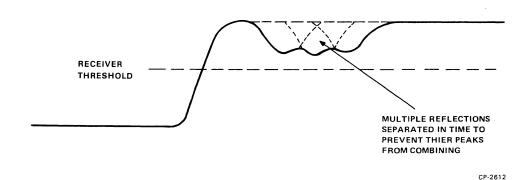

If too many dc loads are put on a Unibus segment, the quiescent undriven voltage may be lowered to a level where bus receivers become susceptible to reflections from lumped loads and the overall noise margin on the high end (bus undriven) may become too small. DB11 bus repeaters should be used (as required) to implement this rule.

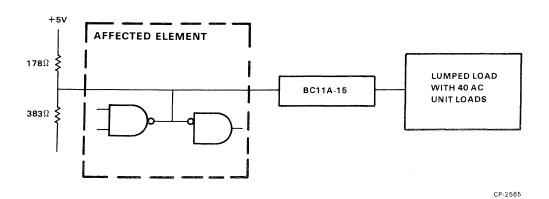

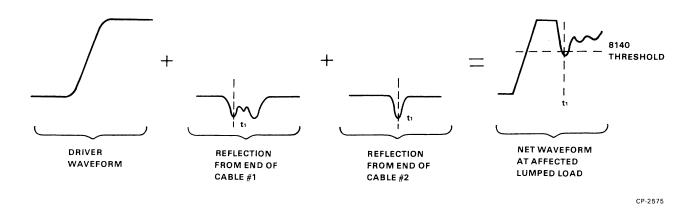

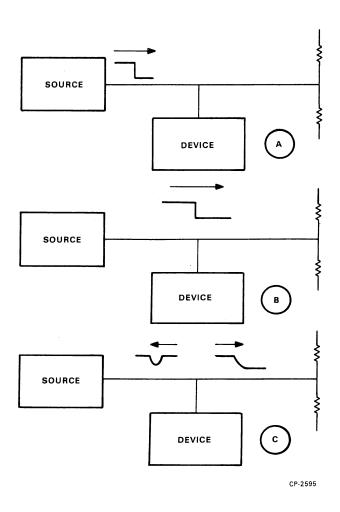

#### 2.3.3 Maximum Lumped Loading (Rule No. 3)

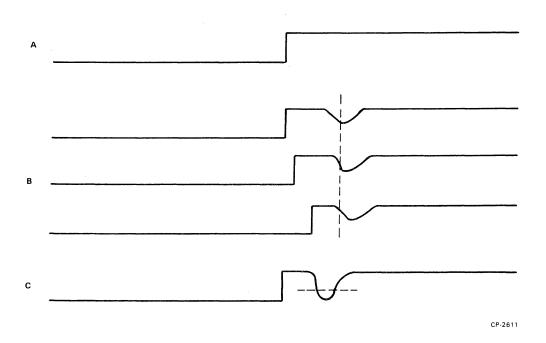

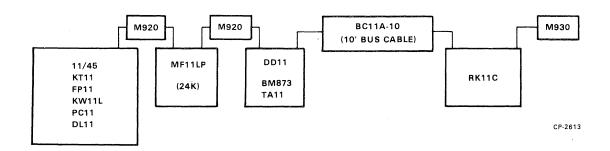

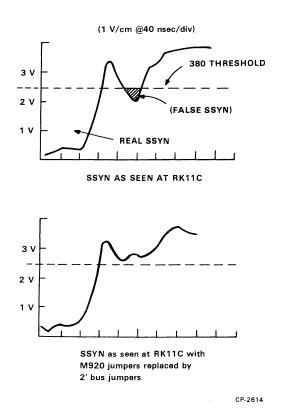

If a lumped load is too large, it may generate a reflection on the Unibus large enough to create a false logic signal and cause a failure (see Figures 2-5 and 2-6). M9202 folded cables (or BC11A-2s, if M9202 is unavailable) should be used in place of M920s in order to separate large lumped loads. The effect of the M9202 is to cause the peak reflections from the lumped loads it separates to occur at slightly different times. The following examples (see Figures 2-7 and 2-8) illustrate implementation of Rule No. 3.

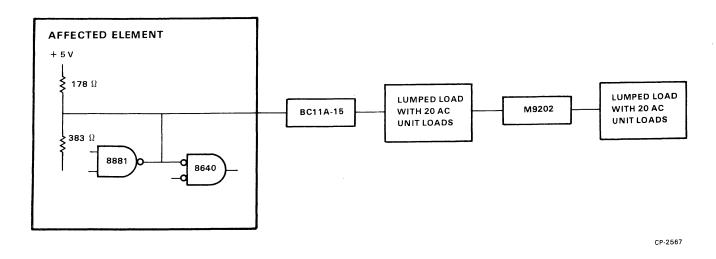

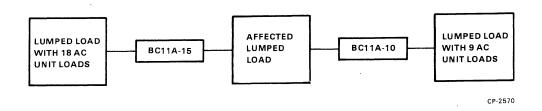

Figure 2-5 Rule No. 3 Violation (Block Diagram)

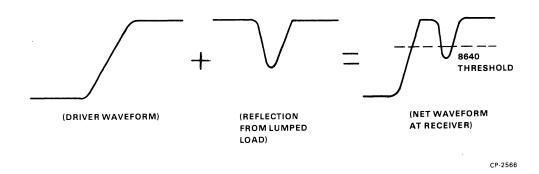

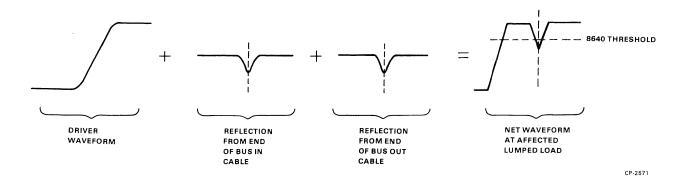

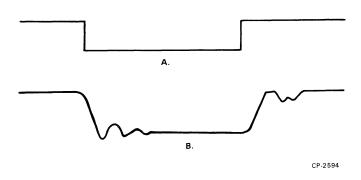

The system shown in Figure 2-5 violates Rule No. 3. When the driver in the affected bus element unasserts the bus, the receiver in that element will see the following waveform:

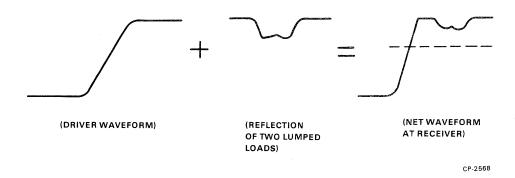

Figure 2-6 Rule No. 3 Violation (Waveform Example)

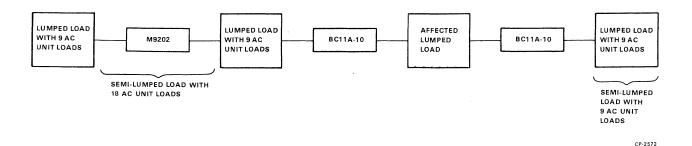

The reflection may cause the threshold of the 8640 receiver to be crossed a second time, and a failure may result. To implement Rule No. 3, the lumped load must be split into two equal loads by adding an M9202 in place of an M920 (see Figure 2-7).

Figure 2-7 Rule No. 3 Implementation (Block Diagram)

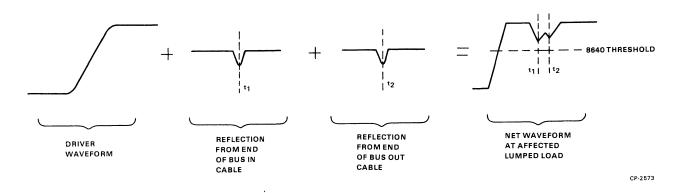

The conditions to satisfy Rule No. 3 are now implemented. When the driver in the affected bus element unasserts the bus, the receiver in that element will see the following waveform (Figure 2-8).

Figure 2-8 Rule No. 3 Implementation (Waveform Example)

Now the 8640 threshold is not crossed and the danger of a failure is reduced.

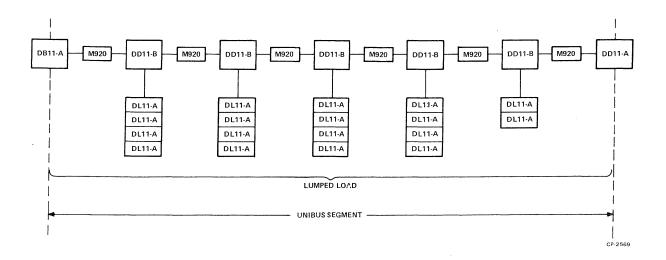

Rule No. 3 states that there is no limit to the number of ac unit loads on a Unibus segment (unless the entire segment consists of one lumped load). The reason for this statement is that there is no 120 ohm cable in the segment on which reflections can travel. The following segment (Figure 2-9) is an example.

Figure 2-9 Multiple Bus System Example

Variable (September 1997)

This segment obeys all configuration rules. It has zero (0) feet of cable, 20 dc unit loads, and an irrelevant number of ac loads. In this configuration none of the M920s have to be replaced by M9202s.

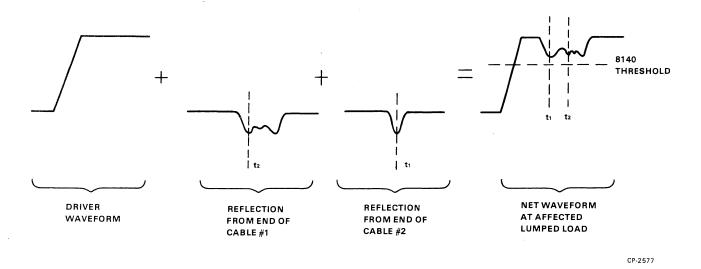

### 2.3.4 Skewed Cable Lengths (Rule No. 4)

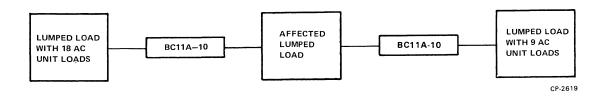

There may be several ways to implement Rule No. 4. Consider the following bus segment (Figure 2-10).

Figure 2-10 Rule No. 4 Violation (Block Diagram)

This segment violates Rule No. 4 because the sum of the lumped loads that are connected to the opposite ends of the cables exceed 18 unit loads. AC unit loads equal 27 (18 + 9 = 27) lumped at the ends of the BC11As of equal length. One way to implement Rule No. 4 is to increase the length of one cable to 4.57 m (15 ft) (see Figure 2-11).

Figure 2-11 Rule No. 4 Implementation (Example A) Block Diagram

Another way is to split the lumped load on the left into two lumped loads using an M9202 (see Figure 2-12).

Figure 2-12 Rule No. 4 Implementation (Example B) Block Diagram

When this rule is violated and when a driver in the affected lumped load unasserts the bus, reflections from the ends of its bus in and bus out cables will arrive at the affected lumped load simultaneously and superimpose. The net reflection may cross the 8640 threshold and cause a failure (see Figure 2-13).

Figure 2-13 Rule No. 4 Violation (Waveform Example)

When the rule is implemented by making the lengths of the bus in and bus out cables different, the reflections will arrive at slightly different times (see Figure 2-14):

Figure 2-14 Rule No. 4 Implementation (Waveform Example)

Now the reflection does not cross the 8640 threshold and the danger of a failure is reduced.

The configuration in Figure 2-12 does not violate Rule No. 4 because the sum of the ac unit loads lumped at the ends of the BC11A-10 cables is 18 (9 + 9 = 18) and the sum of ac unit loads in the semi-lumped loads at the BC11A-10's ends of the cables is 9 plus the lumped loads (18) for a total of 27 unit loads (9 + 18 = 27).

Either of these methods could be used to implement Rule No. 4 but the second is more desirable in this example because it minimizes the total cable length of the segment.

#### 2.3.5 Skewed Cable Lengths, Supplement (Rule No. 5)

To understand why this rule is necessary, consider the following example (Figure 2-15).

Figure 2-15 Skewed Cable Length Violation

Suppose that the length of cable no. 1 equals the length of cable no. 2. This violates Rule No. 4. In this case, the affected lumped load will see the following waveform (Figure 2-16) when its driver unasserts the bus.

Figure 2-16 Skewed Cable Length Violation (Waveform Example)

The reflection in this waveform crosses the 8640 threshold and may cause a failure. The best way to implement Rule No. 4 in this example is to increase the length of either cable no. 1 or cable no. 2 by 1.52 m (5 ft). Suppose the length of cable no. 2 is increased by 1.52 m (5 ft). (This violates Rule No. 5 because this is the end with the smaller lumped load.) In this case, the affected lumped load will see the following waveform (Figure 2-17) when its driver unasserts the bus.

Figure 2-17 Violation of Rule No. 5 (Waveform Example)

The reflection in this waveform also crosses the 8640 threshold and may cause a failure.

Now suppose the length of cable no. 1 is increased by 1.52 m (5 ft) instead of cable no. 2. This will implement Rule No. 5 correctly. In this case, the affected lumped load will see the following waveform (Figure 2-18) when its driver unasserts the bus.

Figure 2-18 Implementation of Rule No. 5 (Waveform Example)

The reflection from the ends of cables no. 1 and no. 2 do superimpose somewhat, but not much. As a result, the 8640 threshold is not crossed.

#### 2.3.6 Rule Violations (Rule No. 6)

Rules No. 1 through No. 5 should be implemented if possible. On rare occasions it may not be practical to do so. For example, the last bus segment on a system may exceed the 15.24 m (50 ft) maximum length rule by 1.52 m (5 ft), and implementing Rule No. 1 may require another DB11-A repeater, which may require another BA11-ES expander box, which may require another H960 cabinet. In this case, it is acceptable to violate Rule No. 1, providing that the system is tagged so that Rule No. 6 is always followed when the system undergoes change or corrective maintenance. Common sense has to be exercised if any of Rules No. 1 through No. 5 is violated.

The voltage margining procedure follows.

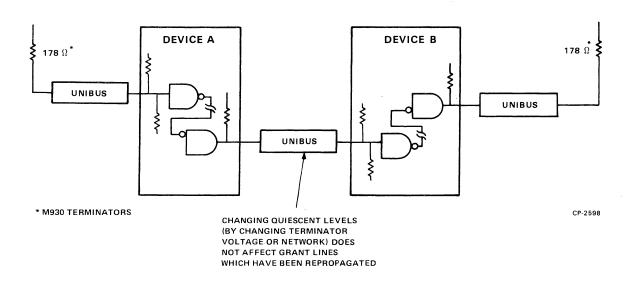

- 1. Replace the two terminators of the segment (M930, M9300, M9301, M9302, M981) with the appropriate low-margin cards (M9304, M9305).

- 2. Run complete diagnostics and system exercisers.

- 3. Replace the two low-margin cards by the corresponding high-margin cards (M9304-YA, M9305-YA).

- 4. Run complete diagnostics and system exercisers.

- 5. Replace the two high-margin cards with the original terminators.

If any diagnostic or system exerciser fails during this procedure, the system has a problem. It may be necessary to implement a rule violation in order to correct the problem. A Unibus voltage margining tester box (Chapter 4) may be necessary to isolate the problem. To determine if there is a margin problem, failures during margining must correspond with (or compared to) no failures when not margining.

#### 2.3.7 System Acceptance (Rule No. 7)

On rare occasions, Rules No. 1 through No. 5 may not be sufficient to eliminate all reflection problems. On these occasions, a Unibus voltage margin tester box (UVM-TA) should be used (along with common sense) to isolate the problem and implement solutions. When an option fails (gives data errors, hangs the bus, etc.) during a margining test, particularly the low-margining test, be suspicious of reflections from surronding options after eliminating weak drivers, leaky receivers, etc. The solution may be to replace an additional M920 in those surrounding options with an M9202 (or even a BC11A-3) in order to further spread out and reduce reflections. If Rules No. 1 through No. 5 do not eliminate a reflection problem, please consult F.S.11 Product Support in Maynard.

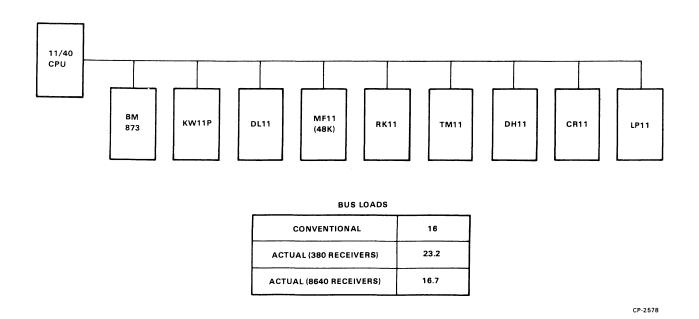

#### 2.3.8 Actual Bus Loading

PDP-11 systems are configured to have no more than twenty loads or 15.24 m (50 ft) of Unibus cable on a given bus. Most devices are specified in terms of whole number loads but in fact this is not always the case. Table 2-1 lists realistic numbers for various options and using the system shown (Figure 2-19), it is seen how loading may differ from that determined by conventional configuration guidelines.

# NOTE If quiescent voltages are correct, then dc loading is probably not a problem.

Figure 2-19 Actual Bus Loads Example

Caution must be exercised in customer situations – the published loading specifications for each device (as listed in Appendix D) must be used in discussions with non-DEC personnel. Table 2-1 is included only for your information. (Refer to Chapter 3, Paragraph 3.3)

Table 2-1 Realistic Load Values

| Option | No. of<br>Drivers | Driver<br>Type | No. of<br>Revrs       | Max. No.<br>unit<br>loads if<br>Rcvrs<br>are 380s | Max. No. unit loads if Revrs are 8640s |

|--------|-------------------|----------------|-----------------------|---------------------------------------------------|----------------------------------------|

| AA11A  | 5                 | 8881           | 2                     | 1.52                                              | .76                                    |

| AA11B  | 5                 | 8881           | 2<br>2<br>2<br>2<br>2 | 1.52                                              | .76                                    |

| AA11C  | 5                 | 8881           | $\overline{2}$        | 1.52                                              | .76                                    |

| AA11D  | 5                 | 8881           | 2                     | 1.52                                              | .76                                    |

| AA11E  | 5<br>5            | 8881           | $\bar{2}$             | 1.52                                              | .76                                    |

| AD01   | 3                 | 8881           | 1                     | 1.119                                             | .7380                                  |

| AFC11  | 2                 | 8881           | î                     | 1                                                 | .6190                                  |

| BM792Y | 1                 | 8881           | î                     | .8809                                             | .5                                     |

| BM873  | 0                 | NONE           | $\frac{1}{2}$         | 1.523                                             | .7619                                  |

| CB11   |                   | 8881           | ĩ                     | 1                                                 | .6190                                  |

| CD11   | 2 3               | 8881           | i i                   | 1.119                                             | .7380                                  |

| CM11   | 4                 | 8881           | 1                     | 1.238                                             | .8571                                  |

| CR11   |                   | 8881           | 1                     | 1.238                                             | .8571                                  |

| DA11B  | 7                 | 8881           | i                     | 1                                                 | .6190                                  |

| DAIIF  | 4<br>2<br>2       | 8881           | Î                     | Ī                                                 | .6190                                  |

| DB11A  | 1                 | 8881           | lî                    | .8809                                             | .5                                     |

| DC11   | 3                 | 8881           | l î                   | 1.119                                             | .7380                                  |

| DH11   | 1                 | 8881           | 3                     | 2.404                                             | 1.261                                  |

| DJ11   |                   | 8881           | 1                     | 1                                                 | .6190                                  |

| DK11   | 2 2               | 8881           | Î                     | 1                                                 | .6190                                  |

| DL11   | 4                 | 8881           | Î                     | 1.238                                             | .8571                                  |

| DM11BB | 1 7               | 8881           | Î                     | 1                                                 | .6190                                  |

| DN11   | 2 2               | 8881           | Î                     | 1                                                 | .6190                                  |

| DP11   | $\frac{2}{3}$     | 8881           | Î                     | 1.119                                             | .7380                                  |

| DR11A  | 4                 | 8881           | Î                     | 1.238                                             | .8571                                  |

| DR11B  | 2                 | 8881           | Î î                   | 1                                                 | .6190                                  |

| DR11C  | 4                 | 8881           | 1                     | 1.238                                             | .8571                                  |

| DT03F  | 7                 | 8881           | Î                     | 1                                                 | .6190                                  |

| DX11   | 2 2               | 8881           | 1                     | 1                                                 | .6190                                  |

| GT40   | 3                 | 8881           | 1                     | 1.119                                             | .7380                                  |

| KE11A  | 1                 | 8881           | 1                     | .8809                                             | .5                                     |

| KG11   | 2                 | 8881           | 1                     | 1                                                 | .6190                                  |

| KW11L  | 1                 | 8881           | ĺ                     | .8809                                             | .5                                     |

| KW11P  | 3                 | 8881           | li                    | 1.119                                             | .7380                                  |

| LC11A  | 4                 | 8881           | î                     | 1.238                                             | .8571                                  |

| LP11   |                   | 8881           | 1                     | 1                                                 | .6190                                  |

| LPS11  | 2<br>2<br>2<br>2  | 8881           |                       | 1.52                                              | .76                                    |

| LS11   | 2                 | 8881           | 2                     | 1                                                 | .6190                                  |

| LVII   | 2                 | 8881           | 1                     | 1                                                 | .6190                                  |

| M792   | 1                 | 8881           | 1                     | .8809                                             | .5                                     |

| ME11   | 1                 | 74H01-1        | 1                     | 1.952                                             | 1.571                                  |

| MF11   | 1                 | 74H01-1        | 1                     | 1.952                                             | 1.571                                  |

| MM11   | 1                 | 74H01-1        | 1                     | 1.952                                             | 1.571                                  |

Table 2-1 Realistic Load Values (Cont)

| Option | No. of<br>Drivers | Driver<br>Type | No. of<br>Revrs | Max. No. unit loads if Revrs are 380s | Max. No.<br>unit<br>loads if<br>Rcvrs<br>are 8640s |

|--------|-------------------|----------------|-----------------|---------------------------------------|----------------------------------------------------|

| MR11   | 1                 | 8881           | 1               | .8809                                 | .5                                                 |

| MS11   | 2                 | 8881           | 1               | 1                                     | .6190                                              |

| PC11   | 4                 | 8881           | 1               | 1.238                                 | .8571                                              |

| PR11   | 4                 | 8881           | 1               | 1.238                                 | .8571                                              |

| RC11   | 3                 | 8881           | 1               | 1.119                                 | .7380                                              |

| RF11   | 2                 | 8881           | 1               | 1                                     | .6190                                              |

| RK11C  | 2<br>2            | 8881           | 1               | 1                                     | .6190                                              |

| RK11D  | 2<br>2            | 8881           | 1               | 1                                     | .6190                                              |

| RP11   | 2                 | 8881           | 1               | 1 .                                   | .6190                                              |

| TA11   | 3                 | 8881           | 1               | 1.119                                 | .7380                                              |

| TC11   | 2 2               | 8881           | 1               | 1 1                                   | .6190                                              |

| TM11   | 2                 | 8881           | 1               | 1 1                                   | .6190                                              |

| UDC11  |                   | 8881           | 2               | 1.52                                  | .76                                                |

#### 2.4 UNIBUS LATENCY

This section is designed to familiarize the Field Service Engineer with the recommended NPR Device Sequence on the Unibus and also provide the ability to determine and minimize possible "Data Late" errors.

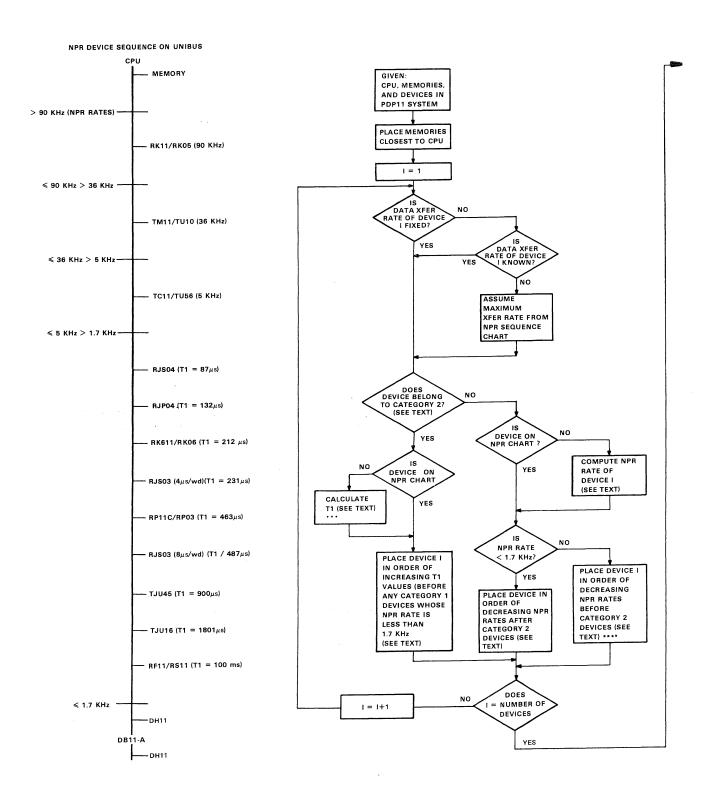

The device sequences for a given PDP-11 System (CPU, memories, and devices) can be obtained by applying the algorithm given in Figure 2-20 and Table 2-2.

Table 2-2 Maximum NPR Rates of the NPR Devices with Variable Speed

| Device        | Maximum Data<br>Transfer Rate | Maximum<br>NPR Rate |

|---------------|-------------------------------|---------------------|

| CD11-E        | 1000 card/min                 | 1.33 kHz            |

| CD11-A        | 1200 card/min                 | 1.6 kHz             |

| DA11-B/DR11-B | 500,000 word/s                | 500 kHz             |

| DH11          | 16 × 9600 Baud                | 15.4 kHz            |

| DQ11-DA       | 10,000 Baud                   | 1 kHz               |

| DQ11-EA       | 1 Megabaud                    | 100 kHz             |

| GT40          | 20 µs/point                   | 50 kHz              |

Figure 2-20 Algorithm To Determine NPR Sequence (Sheet 1 of 2)

- \* If only one BUS REPEATER, this means between the CPU and the BUS REPEATER.

- \*\* Or the least frequently used category 1 device.

- \*\*\* T1 = Maximum tolerance between bus cycles

- \*\*\*\*Except asyncheonous communication devices (e. g., DH11) which have great latency tolerance capacity. DH11 can be placed in rear of all other devices.

#### NOTES:

- Throughput is conditional and is well studied at the CPU. I/O bandwidth is more difficult to determine but has been investigated by Engineering.

- BR device can be put behind repeaters or behind NPR device. BR device should be placed in front of asynchronous devices. (i.e. NPR11 - DMC11, DVM11 -DC11)???

CP-2686

Figure 2-20 Algorithm To Determine NPR Sequence (Sheet 2 of 2)

Using the procedure outlined in Figure 2-20 and the maximum NPR rates specified in Table 2-2, the following steps should be used to approach a DATA LATE problem.

- 1. Determine the correct sequence of devices on the Unibus. If the configuration is incorrect, correct it.

- 2. Determine from the configuration tables whether or not the system is expected to experience DLTs due to Unibus bandwidth (refer to Figure 2-24).

- 3. If the system is not expected to experience DLTs but nevertheless does, isolate the hardware malfunction with the bus busy measurement technique.

In some cases, it may be useful to apply the Bus Busy measurement technique to systems which may experience Data Lates due to Unibus bandwidth. In such instances, the technique helps to demonstrate that the hardware is functioning correctly.

#### NOTE

For the purposes of this manual, bandwidth is defined as the number of bus cycles that can be accommodated and still provide successful execution of the application software.

#### 2.4.1 Device Categories

All existing NPR devices that are connected to the Unibus are considered to be in one of the two defined categories. Note the fact that all communication devices are considered to be in category 1 classification even though some devices have data buffers of more than six words (usually, these devices multiplex more than one line).

Category 1 – Devices whose controllers have six or fewer words of data buffer (excluding RF11/RS11 which, although it has only a one-word data buffer, falls more closely into category 2 simply because it can wait for a maximum of three disk revolution time or 100 ms without getting "data late" errors). Other devices in this category are: CD11, DA11, DH11, DQ11, DR11, GT40, RK11/RK05, TM11/TU10, and TC11/TU56.

Category 2 – Devices whose controllers have more than six words of data buffer (including RF11/RS11 as described under category 1). Devices included in this category are: RJS04, RJP04, RK611/RK06, RJS03, RP11C/RP03, TJU45, TJU16, and RF11/RS11.

### 2.4.2 NPR Calculations for T1

NPR rates of category 1 devices can be computed in one of the following ways.

NPR RATE = baud rate /10 (may be different for different devices), or

= word/s, or

$= card/min \times 1.33$

Within Category 1, devices with higher NPR rates should be placed before devices with lower NPR rates.

#### 2.4.3 Latency Tolerance Calculations\*

The process of determining category 2 device sequence can be simplified by comparing T1 (maximum tolerance between bus cycles) of each device, which can be computed as follows:

$$T1 = TDBS - TBBLUP \times 2$$

where: TDBS = Time to transfer DBS words to/from the device (in  $\mu$ s)

DBS = Data buffer size of the device controller (for RH11, DBS = 66)

TBBLUP = Typical data bubble up time of the device controller (for RH11, TBBLUP = 16

Please note the following information carefully.

- 1. If the sector size of a device is larger than DBS, TDBS is simply the product of the instantaneous data transfer rate of the device and the DBS of the device controller. For example, the sector size of RP04 is 256 words (DBS = 66 words), and the instantaneous data transfer rate is  $2.48 \mu s/word$ , so TDBS =  $2.48 \times 66 = 164 \mu s$ .

- 2. If the sector size of a device is smaller than DBS, the sector gap and interleaved sector and gap (if any) must be accounted for to compute TDBS. The situation can be clarified better with the examples that follow. RS03 has sectors of 64 words, sector gaps of 25.6  $\mu$ s and an instantaneous data transfer rate of 3.6  $\mu$ s/word. Its DB (or silo) has two more words than a sector; therefore, two words must be gotten to/from the next sector.

Sector-noninterleaved (4ls/wd): TDBS =  $3.6 \times 64 + 25.6 + 3.6 \times 2 = 263 \mu s$ Sector-interleaved (8  $\mu s$ /wd): TDBS =  $(3.6 \times 64 + 25.6) \times 2 + 3.6 \times 2 = 519 \mu s$

#### **NOTE**

Within category 2, devices with greater T1 should be placed after devices with smaller T1. All category 2 devices should be placed before category 1 devices with NPR rate less than 1.7 kHz, except for asynchronous communication devices (e.g., DH11) which have great latency tolerance capacity. DH11 can be placed in rear of all other devices.

#### 2.4.4 BR Devices

All the BR devices should be placed after NPR devices. However, sometimes for convenience sake some BR devices may be put before NPR devices (e.g., a DECwriter may be placed next to the CPU).

#### 2.4.5 Unibus Loading Rules

- 1. Maximum loading before the first bus repeater is 19 dc bus loads; between two adjacent bus repeaters is 18 dc bus loads.

- 2. Maximum Unibus cable length between the first bus repeater and the CPU or between the adjacent bus repeaters is 15.24 m (50 ft). For example, configure a system with 11/45, 128K of MF11-UP, DL11-A/LA30, KW11-L, RK11/RK05, RJS04, RJP04, DH11, DQ11-EA (at 12.5K baud), RF11/RS11, TJU16, GT40, CD11-E.

<sup>\*</sup>Latency tolerance capacities of devices in category 2 are defined and computed using "Latency Tolerance Capacities of NPR Controllers/Devices and Configuration Guidelines". 4/23/75.

After going through Figure 2-20 and Table 2-2, the following sequence results.

| Device             | <b>Unibus Loads</b> |

|--------------------|---------------------|

| ** / * *           | •                   |

| 11/45              | 2                   |

| KW11-L             | 1                   |

| DL11A/LA30         | 1                   |

| 128K MF11-UP       | 8                   |

| RK11/RK05 (90 kHz) | 1                   |

| GT40 (50 kHz)      | 1                   |

| RJS04              | 1                   |

| RJP04              | 1                   |

| TJU16              | 1                   |

| RF11/RS11          | 1                   |

| DH11 (15.4 kHz)    | 2                   |

| CD11-E (1.33 kHz)  | . 1                 |

| DQ11-EA (1.25 kHz) | _1_                 |

| TOTAL              | 22 UNIT LOADS       |

There are a total of 22 unit loads. Therefore, a DB11-A is added at the end and DH11, DQ11-EA and CD11-E are repositioned after DB11-A.

#### NOTE

The NPR device sequence algorithm does not take into account the measures of the usage of the devices. For example, suppose that in the system given above GT40 is seldom used. GT40 may be placed behind RF11/RS11 to improve system throughput.

#### 2.5 BUS BUSY TEST TECHNIQUES

The following description is designed to aid in determining "nominal" device bus busy times for PDP-11 system configurations. It is intended for use in cases where a system under test is configured correctly, but is still incurring Unibus "Data Late" errors.

Almost every PDP-11 I/O device, transferring data at the NPR level, has a period of time in which a word or byte of data can remain in its data buffer before the next incoming word displaces it. This period of time is known as a device's latency. If, during this period of time, the device is unable to complete a Unibus transfer, the word in the data buffer will be displaced and lost. A data late error will result and the transfer operation must be aborted and restarted. This is obviously an undesirable condition.

Latency, or Data Late, errors may occur as a result of many factors, e.g., device and memory types, Unibus configurations, software in use, and hardware malfunction. This document will address hardware malfunctions.

### 2.5.1 Bus Busy and Latency Tolerance

In many instances stand-alone diagnostics and system exercisers will provide sufficient information to allow the problem to be identified and isolated. This generally leads to a traditional troubleshooting approach.

Sometimes, however, the malfunction will be more subtle, eluding even the most rigorous diagnostics. In the past, large devices were slow (by today's standards) and there was little concern about how long a device took to complete a transaction on the Unibus. As systems have expanded in size and devices have become faster and software more stringent in its I/O demands, the need for NPR devices to complete their transactions and release the Unibus to another device as soon as possible has become imperative.

If an NPR device holds BBSY asserted on the Unibus for an abnormally long period of time, that device (in some configurations) could "crowd out" another NPR device competing for Unibus time forcing an error condition to occur. It should be evident, then, that Data Lates being reported by one device may be caused by another device on the system being a "bus hog".

The following paragraphs will show how to predict nominal BBSY time for a given configuration and how to measure the actual BBSY times. Guidelines are included to help determine whether or not the measured BBSY times fall within an acceptable range around the predicted value.

# 2.5.2 Calculating Nominal Bus Busy Times

# NOTE

It doesn't matter if the calculations necessary to predict a BBSY time are performed first or if the measurements are made first. In some cases however it is necessary to determine if a device is conducting "single cycle" or "double cycle" transactions, as this will affect the calculations that must be made. This will be true of some Massbus devices (RH11). If in doubt, proceed to Paragraph 2.4.3 and make this determination.

This section deals with calculating or predicting a BBSY time for a device within a given configuration. Component tolerances throughout the system make exact calculations impossible, but typically a device should fall within a plus-or-minus 30 percent range of the predicted value. If, after measuring the real BBSY time, it exceeds the predicted value by more than 30 percent, a potential problem area has been found and steps should be taken to bring the offending device nearer to specification.

For the purposes of this manual, BBSY can be thought of as composing four separate components:

- 1. Ddy

- This is the internal timing delay of the device itself. The figure can be obtained from Table 2-

- 2. Dma

This is memory access time or the time it takes memory to assert SSYN after it sees MSYN. This figure can be obtained from Table 2-4.

- 3. Dtr

- This is the delay associated with Unibus transmitters and receivers. This figure may be obtained from Table 2-5.

- 4. Dp

This is the propagation delay of the Unibus itself, taking into account its length and loading properties. This must be calculated from a formula.

Table 2-3 Device Delay (Ddv)

| Controller<br>Type                                         | Ddv (in nanoseconds)<br>Single<br>Cycle | Double<br>Cycle   |

|------------------------------------------------------------|-----------------------------------------|-------------------|

| TC, TM, RP11-C, RK11-C, RF11<br>DH11<br>RK11-D<br>RH11 680 | 1100<br>1350<br>935<br>1355             | N/A<br>N/A<br>N/A |

Table 2-4 Memory Access Delay (Dma)

| Memory<br>Type | Dma (in nanoseconds) Single Cycle | Double<br>Cycle |

|----------------|-----------------------------------|-----------------|

| 8K MF11-L      | 365                               | 730             |

| 8K MF11-LP     | 430                               | 860             |

| 16K MF11-U     | 375                               | 740             |

| 16K MF11-UP    | 460                               | 920             |

| Other Core     | 410                               | 820             |

Table 2-5 Transmitter/Receiver Delay (Dtr)

| Transmitter/Receiver<br>Type | Dtr (in nanoseconds) Single Cycle | Double<br>Cycle |

|------------------------------|-----------------------------------|-----------------|

| Dt 8881                      | 60                                | 120             |

| Dt 8838                      | 40                                | 80              |

| Dt 380                       | 40                                | 80              |

| Dt 8640                      | 40                                | 80              |

Single Cycle =  $Dp = (3.4 \times UL) + (3.5 \times dc \text{ unit loads})$ Double Cycle =  $Dp = (6.8 \times UL) + (7 \times dc \text{ unit loads})$

The summation of these four components yields a BBSY value unique to particular device and configuration.

$$BBSY = Ddv + Dma + Dtr + Dp$$

The first three components of the formula (Ddv, Dma and Dtr) are easily obtained by referring to the referenced tables. Locate in the table the appropriate device, memory type or transmitter/receiver type and extract the number from either the "single cycle" or "double cycle" column as it pertains to the device. Determining "single cycle" or "double cycle" is explained in Paragraph 2.5.3.

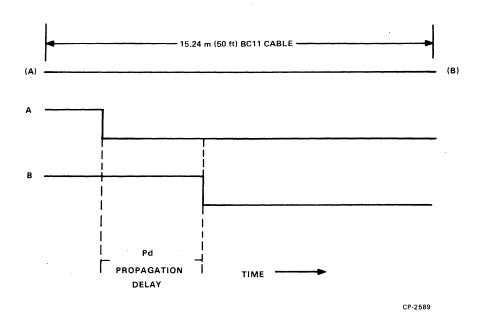

The fourth component of the formula (Dp) may be derived in the following manner.

Single Cycle

$Dp = (3.4 \times U1) + (3.5 \times dc unit loads)$

or

**Double Cycle**

$Dp = (6.8 \times U1) + (7 \times dc unit loads)$

where:

U1 = Unibus length in meters (feet) between the device and memory

DC Unit Loads = the number of DC Unit Loads between the devices and memory, *including* the dc unit loads presented by memory itself.

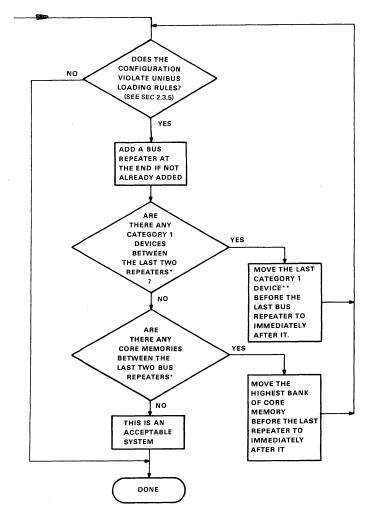

To illustrate this, look at the sample configuration shown in Figure 2-21. If the device under test were the RK11-D the value of U1 would be 60.96 cm (2 ft) and the dc unit loads would be 3 (1 dc unit load for each 16K bank of memory). If the device under test were the TM11, U1 would equal 2.13 m (7 ft) and dc unit loads would equal 4.

### NOTE

If the device under test is located behind one or more DR11 bus repeaters add 375 ns (for devices doing "single cycle" transfers) or 750 ns (for devices doing "double cycle" transfers) to the calculations for each bus repeater between the device and memory.

2.5.3 Measuring Bus Busy Times

A dual-trace oscilloscope with three probes will be needed to conduct the following tests. The third probe will be used to monitor MSYN in order to determine if some of the NPR devices (such as RH11s) are doing "double cycle" transactions. If it is certain that all the devices to be tested will be conducting "single cycle" transfers only, the third probe may be eliminated and all calculations will be made from figures extracted from the "single cycle" columns in Tables 2-3, 2-4, and 2-5.

Figure 2-21 Unibus Length Between Device and Memory

Set up the oscilloscope as follows:

Coupling = dc Trigger = External positive Mode = Alternate Vols/Div = .1 (with X10 probes) Time/Div = .5 microseconds.

Now locate a convenient access to the Unibus. The TC11 (DECtape) is a good access point if available, otherwise any backplane with Unibus-in or Unibus-out will do.

Connect the probe corresponding to external trigger to SACK L at pin AR2.

Connect the probe corresponding to channel 1 to BBSY L at pin AP2.

Connect the probe corresponding to channel 2 to MSYN L at pin BV1.

The software to be run during these tests will be DEC/X11. Before proceeding, note that Table 2-4 (Dma) doesn't include data on MOS or bi-polar memory systems. For this reason, ensure that DEC/X11 doesn't use MOS or bi-polar as write buffer space. If the system under test is an all core system this will not be of any concern. If the system does include MOS or bi-polar it will be necessary to lock the run-time exerciser in memory (via the RUNL command) so that the beginning of DEC/X11s write buffer space (which coincides with the last address + 2 or the last module) is in core. It is acceptable if the DEC/X11 code exercises from MOS or bi-polar as long as the write buffer space is in core. Finally, inhibit write buffer rotation via the ROTOFF command.

Before issuing the RUNL command, DESelect all modules and SELect the module corresponding to the first device to be tested.

## NOTE

By testing only one device at a time and by triggering the scope from SACK, it is ensured that the signals seen will be those issued by the device under test.

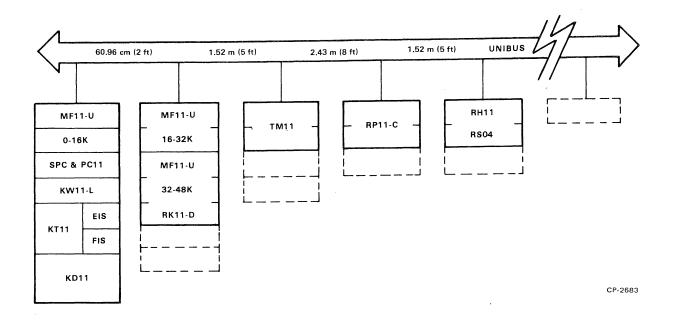

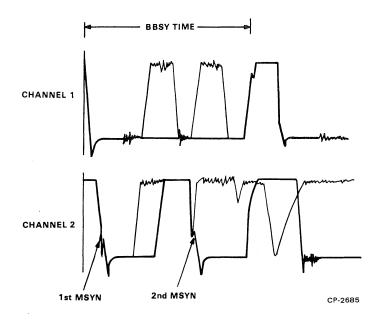

Once DEC/X11 has been started and the scope trigger has been properly adjusted, the brace should correspond to one of the two figures shown in Figures 2-22 and 2-23. Figure 2-22 shows a device doing single-cycle transaction, and Figure 2-23 shows a device performing double cycle transactions.

The key here is the channel 2 trace displaying MSYN. If MSYN is seen being asserted once during the BBSY time displayed on channel 1, the device is performing single-cycle transfers and the "single cycle" column in Tables 2-3, 2-4 and 2-5 should be used. If MSYN is seen being asserted twice during the BBSY time the device is performing double cycles and the "double cycle" column in the tables should be used for the calculations on that device.

The BBSY time being displayed on channel 1 is the time to be ultimately concerned with. This is the value that should coincide (plus-or-minus 30 percent) with the calculated value.

Once the measurements have been taken for a device, issue a control C from the keyboard to stop the run-time exerciser. When DEC/X11 is ready to accept new commands DESelect the device just tested and SELect the module corresponding to the next device to be tested and repeat these procedures until all NPR devices on the system have been measured.

Figure 2-22 Single-Cycle Transaction

Figure 2-23 Double-Cycle Transaction

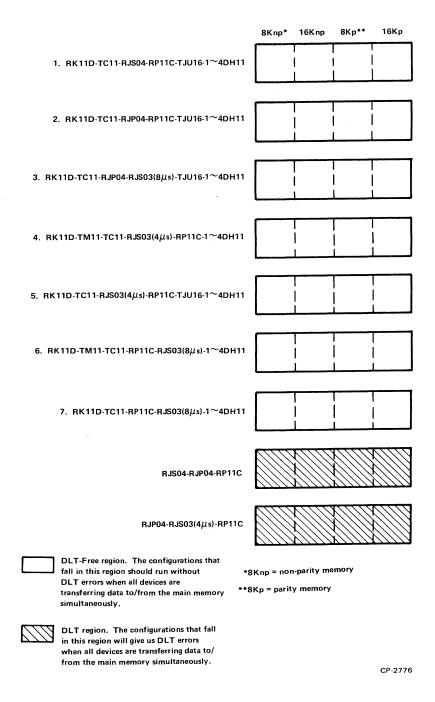

2.5.4 Configuration Tables

The configuration table (Figure 2-24) is presented here to familiarize the user with Data Late (DLT) occurrence possibilities of some common PDP-11 systems. No attempt is made in this manual to cover all possible configurations because of the complexity of the problems that could be encountered.

In all configurations, the general rules are:

- 1. If a configuration runs DLT-free, then a subset of the configuration should also run DLT-free.

- 2. If a configuration runs with DLT, adding more devices to the system should also give DLT.

Figure 2-24 DLT Configurations

2-31

# CHAPTER 3 TROUBLESHOOTING

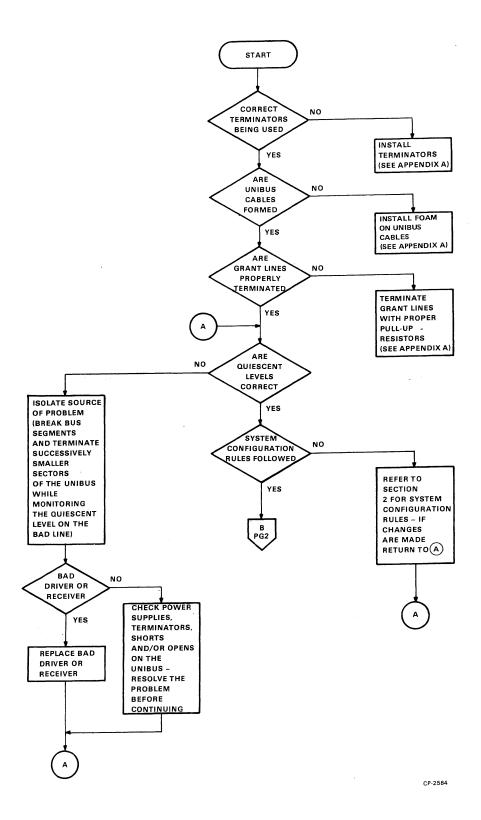

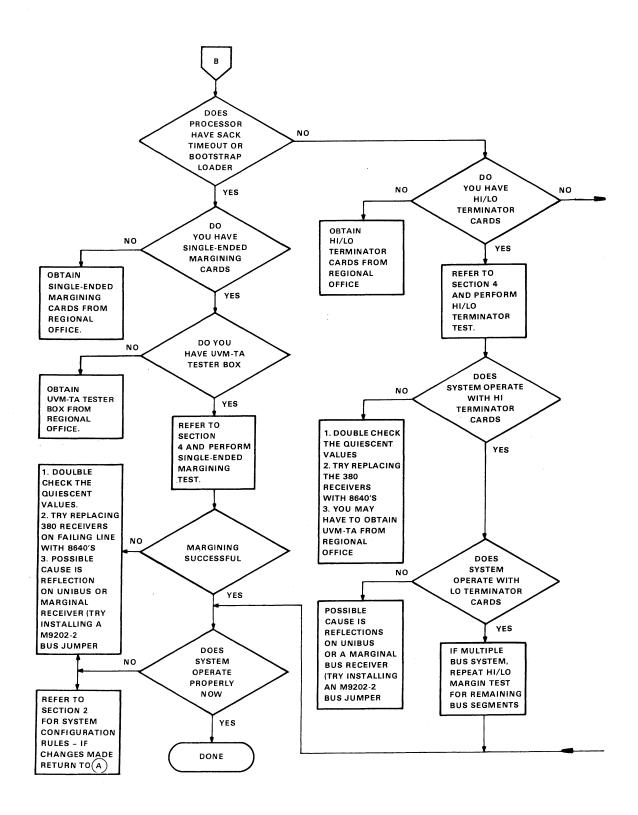

# 3.1 GENERAL

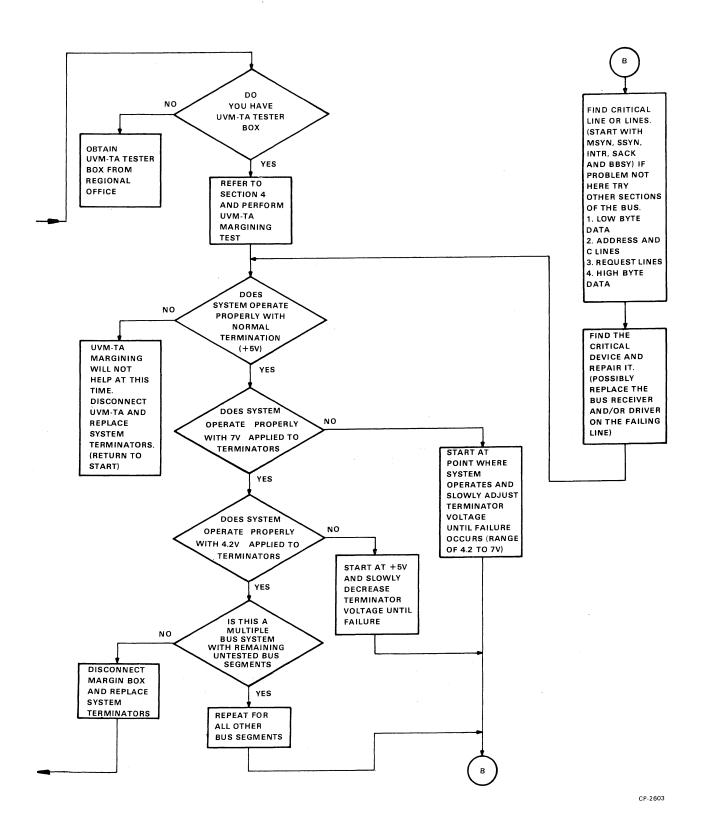

This section is designed to aid in isolating and troubleshooting Unibus failures. The Unibus Trouble-shooting Flowchart (Figure 3-1) is designed to provide a step-by-step procedure for checking and correcting Unibus problems. The flowchart references chapters and paragraphs (which contain additional information and possible solutions to solve Unibus problems) are included for reference.

# 3.2 TIMING CONSIDERATIONS\*

Some system failures such as address errors, missing data, illegal traps and system halts can occur because of bus timing relationships.

# 3.2.1 DATO-DATOB

The Unibus specification states that MSYN must be asserted 150 ns (minimum) after the address, control, and data (for DATO and DATOB transactions). This delay includes 75 ns to allow internal logic in the slave device to decode the address. If MSYN is asserted before 150 ns, insufficient deskew and signal decoding at the slave may result in errors. An 8881 driver and an 8640 receiver combination can cause up to 60 ns of skew leaving as little as 15 ns as the allowable skew because of the Unibus transmission media. The most timing-sensitive lines have been found to be BBSY, MSYN, SSYN and INTR. Cable length and configuration can be a noticeable factor in these lines.

# 3.2.2 DATI-DATIP

For a DATI or DATIP operation, the slave puts requested data on the D lines and then asserts SSYN. The slave should not assert SSYN at the driver input before the data and enable lines are valid at the data driver inputs. The critical point seems to be around 35-40 ns skew in SSYN vs. DATA at which point it is possible for high-speed systems (such as the 11/45 which allows only the 75 ns maximum skew) to clock in erroneous data.

Some memories have a potential problem with this timing relationship in certain systems. When a system is upgraded from an 11/05 or 11/20 to an 11/45 or when more of this memory is added in an extended cabinet by a longer Unibus cable, the risk factor for problems becomes greater. If problems are experienced with these memories (MM11-L, MM11-S, MM11-E, MM11-F) in high-speed systems, consult F.S. Product Support.

<sup>\*</sup>Refer to the 1975 Peripherals Handbook for Unibus timing information.

Figure 3-1 Unibus Troubleshooting Flowchart (Sheet 1 of 3)

Figure 3-1 Unibus Troubleshooting Flowchart (Sheet 2 of 3)

Figure 3-1 Unibus Troubleshooting Flowchart (Sheet 3 of 3)

# 3.2.3 Interrupt Transactions

A typical 11/45 system will experience problems if the data lags the INTR line on the cable by more than 30-40 ns. Most DEC interfaces assert the vector address and INTR at exactly the same time and Unibus skew times may cause a timing problem if the bus is long. Experiments with a typical system show the vector address lagging INTR on the cable by as much as 30 ns with 9.14 m (30 ft) of Unibus cable and a TC11 or 45 ns with 9.44 m (31 ft) of bus and a DL11. The electrical configuration rules as listed in Chapter 2 will minimize these problems when properly applied.

# 3.2.4 High-Frequency Cable Losses

The increase in transmission line conductor resistance at high frequencies, known as skin effect, may be a factor in bus analysis. This function exhibits a very fast rise time to 50 percent of the input, but a very slow dribble up from 50 percent to 90 percent of the input.

A 15.24 m (50 ft) bus cable could theoretically have a dribble up noticeable for up to 170 ns in response to a step function at the input.

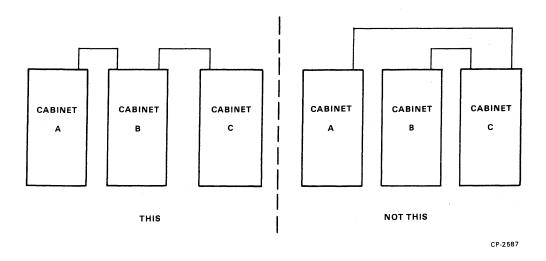

The bus should, therefore, be kept as short as possible to avoid potential timing problems. The published (i.e., allowable) Unibus length is 15.24 m (50 ft), but it is desirable to use as little cable as possible for a given configuration (see Figure 3-2). Devices should be physically arranged in the same order as they are electrically connected, if possible. (If M9202 folded cables are needed due to physical arrangement, they should not be replaced by M920s in order to decrease bus length.)

Figure 3-2 System Cabling Configuration Example

# 3.2.5 Peripheral Data Rate

It is possible to support only a certain rate of data transfer on the Unibus – beyond this rate, data late situations will occur. A method for roughly determining permissible combinations of simultaneous peripheral device activity (such as would occur when executing DECX11) follows.

1. Determine a window for a given system based on the slowest NPR device transfer rate ( $\mu$ s).4 If you have an RK11, RP11, TM11 and TC11, the slowest device will be the TC11 with a transfer rate of 200  $\mu$ s/word.

Window =  $200 \mu s$  (in this case)

2. Determine how many transfers the faster devices will perform in the window time.

(Window Time)/(Transfer Rate)

| RK11 (11.1 $\mu$ s/word) | 200/11.1 = 18.02 |

|--------------------------|------------------|

| TM11 (27.7 $\mu$ s/word) | 200/27.7 = 7.22  |

| RP11 (7.5 $\mu$ s/word)  | 200/7.5 = 26.66  |

3. Calculate the *total* number of transfers occurring within the window.

$$TC11 = 1$$

$RK11 = 18.02$

$RP11 = 26.66$

$TM11 = 7.22$