## IEU11-A/IEQ11-A

User's Guide

### IEU11-A/IEQ11-A

User's Guide

Prepared by Computer Special Systems

Digital Equipment Corporation • Nashua, NH 03062

#### © Digital Equipment Corporation 1985 All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

| digital TM     |  |

|----------------|--|

| DEC            |  |

| <b>DECmate</b> |  |

| DECset         |  |

| DECsystem-10   |  |

| DECSYSTEM-20   |  |

|                |  |

| DECUS        | RSTS           |

|--------------|----------------|

| DECwriter    | RSX            |

| DIBOL        | UNIBUS         |

| MASSBUS      | VAX            |

| PDP          | VMS            |

| P/OS         | VT             |

| Professional | Work Processor |

| Rainbow      |                |

#### CONTENTS

|           | Pag                                         |

|-----------|---------------------------------------------|

| PREFACE   |                                             |

| CHAPTER 1 | GENERAL DESCRIPTION                         |

| 1.1       | INTRODUCTION                                |

| 1.2       | PHYSICAL DESCRIPTION                        |

| 1.2.1     | IEU11-A Option Components                   |

| 1.2.2     | IEQ11-A Option Components                   |

| 1.3       | APPLICATION EXAMPLES                        |

| 1.4       | FUNCTIONAL DESCRIPTION                      |

| 1.4.1     | IEC/IEEE Interface Messages                 |

| 1.4.1.1   | Address Command Group (ACG)                 |

| 1.4.1.2   | Universal Command Group (UCG)               |

| 1.4.1.4   | Listener Address Group (LAG)                |

| 1.4.2     | Talker Address Group (TAG)                  |

| 1.4.3     | Secondary Command Group (SCG)               |

| 1.4.4     | Types of Functional Devices                 |

| 1.4.5     | IEEE 488-1978 Interface Functions           |

| 1.5       | GENERAL SPECIFICATIONS                      |

|           |                                             |

| CHAPTER 2 | INSTALLATION                                |

| 2.1       | INTRODUCTION 2-1                            |

| 2.2       | IEU11-A OPTION UNPACKING AND INSPECTION 2-1 |

| 2.3       | IEU11-A SITE REQUIREMENTS                   |

| 2.4       | M8648 MODULE CONFIGURATION                  |

| 2.4.1     | M8648 Module Configuration Procedure 2-3    |

| 2.5       | M8648 MODULE INSTALLATION                   |

| 2.5.1     | M8648 Module Installation Procedure 2-4     |

| 2.6       | VERIFYING M8648 MODULE OPERATION            |

| 2.6.1     | M8648 Module Operation Verified in a PDP-11 |

|           | System 2-5                                  |

| 2.6.2     | M8648 Module Operation Verified in a VAX-11 |

| 2.7       | System 2-5                                  |

| 2.7.1     | FIELD SERVICE AND CUSTOMER ACCEPTANCE 2-5   |

| 2.7.1     | Field Service and Customer Acceptance       |

| 2.7.2     | Procedure (PDP-11 System)                   |

| 2.1.2     | Field Service and Customer Acceptance       |

| 2.8       | Procedure (VAX-11 System)                   |

| 2.8.1     | IEC/IEEE BUS INTERCONNECTION                |

| 2.8.2     | IEEE/IEC Bus Interconnect Procedure 2-9     |

| 2.9       | Testing the IEC/IEEE Bus Cables             |

| 2.10      | IEQ11 SITE REQUIREMENTS 2-14                |

| 2.11      | M8634 MODULE CONFIGURATION                  |

#### CONTENTS (Cont)

|           | Pa                                        | ag e |

|-----------|-------------------------------------------|------|

| 2.11.1    | M8634 Module Configuration Procedure 2-   | -16  |

| 2.12      | M9634 MODITE INSTALLATION                 | -T 8 |

| 2.12.1    | M8634 Module Installation Procedure 2-    | -18  |

|           | VERIFYING M8634 MODULE OPERATION2-        | -20  |

| 2.13      | FIELD SERVICE AND CUSTOMER ACCEPTANCE 2-  | -2Ø  |

| 2.14      | IEEE/IEC BUS INTERCONNECTION              | -22  |

| 2.15      | IEEE/IEC Bus Interconnection Procedure 2- | -22  |

| 2.15.1    | Testing the IEC/IEEE Bus Cables 2-        | -25  |

| 2.15.2    | Testing the IEC/ILLE Bus Cables           |      |

| CHAPTER 3 | PROGRAMMING                               |      |

| 3.1       | INTRODUCTION                              | 3-1  |

| 3.1.1     | UNIBUS Addresses                          | 3-1  |

| 3.1.2     | Register Bit Abbreviations                | 3-2  |

| 3.2       | TEU11-A DEVICE REGISTERS                  | 3-2  |

| 3.2.1     | IEEE Status Register (ISR)                | 3-4  |

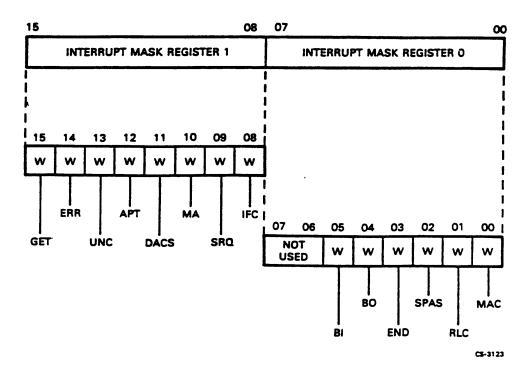

| 3.2.1.1   | Interrupt Mask Register 0 and Interrupt   |      |

| 3.2       | Status Register Ø                         | 3-4  |

| 3.2.1.2   | Interrupt Mask Register 1 and Interrupt   |      |

| 3.2.2.2   | Status Register 1                         | 3-8  |

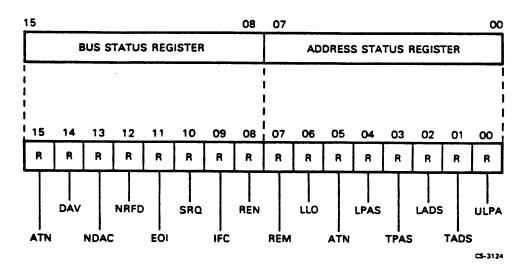

| 3.2.1.3   | Address Status Register                   | -10  |

| 3.2.1.4   | Bus Status Register                       | -10  |

| 3.2.2     | IEEE Interrupt Register (IIR)3-           | -1Ø  |

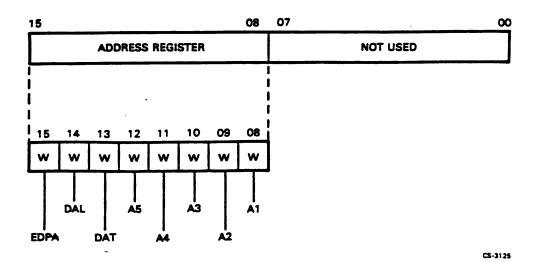

| 3.2.2.1   | Address Register                          | -10  |

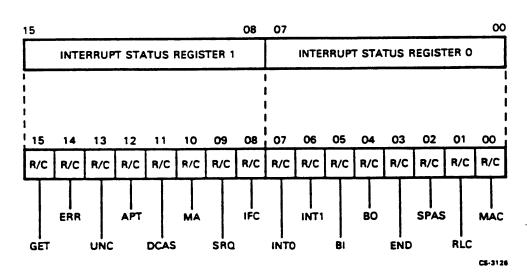

| 3.2.2.2   | Interrupt Status Register 0               | -12  |

| 3.2.2.3   | Interrupt Status Register 1               | -12  |

| 3.2.3     | IEEE Command Register (ICR)               | -12  |

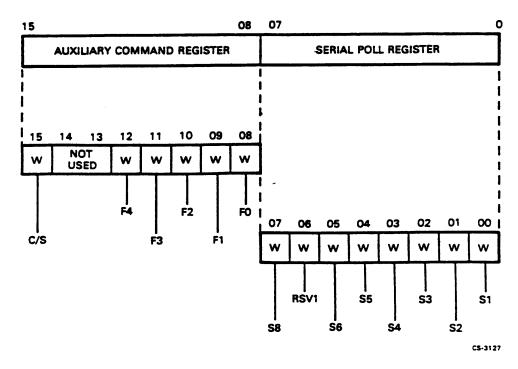

| 3.2.3.1   | Auxiliary Command Register 3              | -12  |

| 3.2.3.2   | Auxiliary Commands                        | -15  |

| 3.2.3.3   | Serial Poll Register 3                    | -2Ø  |

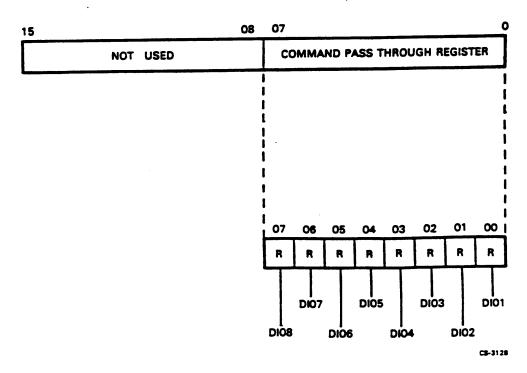

| 3.2.3.4   | Command Pass Through Register 3           | -21  |

| 3.2.4     | IEEE Data Register (IDR)                  | -21  |

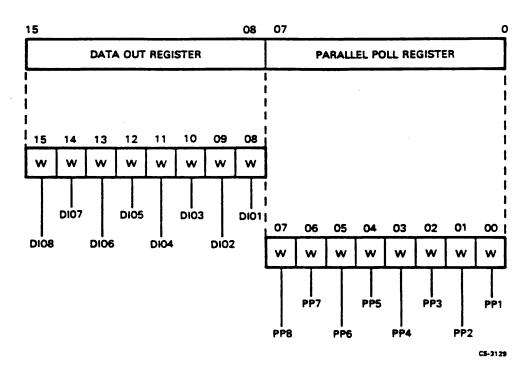

| 3.2.4.1   | Data Out Register 3                       | -22  |

| 3.2.4.2   | Parallel Poll Register                    | -23  |

| 3.2.4.2   | Data In Register                          | -24  |

|           |                                           | -25  |

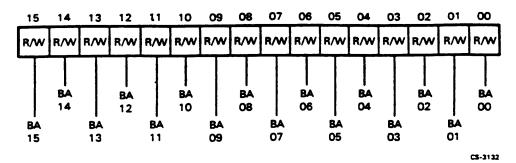

| 3.2.5     | Bus Address Register (BAR)                |      |

| 3.2.6     | Byte Count Register                       | -30  |

| 3.2.7     | Match Character Register                  | -31  |

| 3.2.8     |                                           | -32  |

| 3.3       |                                           | -33  |

| 3.3.1     |                                           | -34  |

| 3.3.2     | Acceptor nandamake                        | -36  |

| 3.3.3     |                                           | -40  |

| 3.3.4     | Idiket did bibeciel tallocione interest   | -45  |

| 3.4       | SERVICE REGULD! LONGITOR                  | -48  |

| 3.5       | REMOTE LONGITOR                           | -49  |

| 3.6       | PARALLEL POLL FUNCTION 3                  | -45  |

#### CONTENTS (Cont)

|                                                        | 1                                                                                                                                                                                                                                                  | Page                                   |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3.6.1<br>3.7<br>3.7.1<br>3.7.2<br>3.7.3<br>3.8<br>3.9  | Remote Configured Parallel Poll  CONTROLLER FUNCTION  Controller Self-Addressing  Passing Control  System Controller  GENERAL OPERATION  PROGRAMMING EXAMPLE                                                                                       | 3-51<br>3-51<br>3-55<br>3-57<br>3-60   |

| CHAPTER 4                                              | MAINTENANCE                                                                                                                                                                                                                                        |                                        |

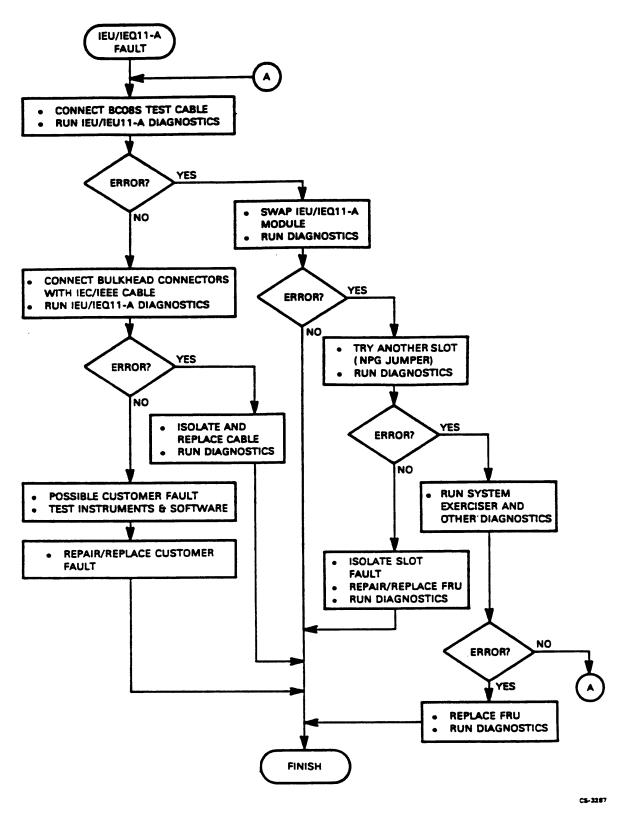

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4.1                      | INTRODUCTION  REQUIRED TOOLS AND EQUIPMENT  CORRECTIVE MAINTENANCE  IEU11-A/IEQ11-A DIAGNOSTIC SOFTWARE  Diagnostic Software (PDP-11 and LSI-11  Systems)  Diagnostic Software (VAX-11 Systems)                                                    | 4-1<br>4-1<br>4-3                      |

| APPENDIX A                                             | STANDARD CONNECTIONS                                                                                                                                                                                                                               |                                        |

| APPENDIX B                                             | REMOTE MESSAGE CODING                                                                                                                                                                                                                              |                                        |

| APPENDIX C                                             | HANDSHAKE PROCESS TIMING SEQUENCE                                                                                                                                                                                                                  |                                        |

| C.1<br>C.2                                             | GENERAL COMMENTSLIST OF EVENTS FOR HANDSHAKE PROCESS                                                                                                                                                                                               |                                        |

| APPENDIX D                                             | MULTILINE INTERFACE MESSAGES; 150-7 BIT CODE REPRESENTATION                                                                                                                                                                                        |                                        |

|                                                        | FIGURES                                                                                                                                                                                                                                            |                                        |

| Figure No.                                             | Title                                                                                                                                                                                                                                              | Page                                   |

| 1-1A<br>1-1B<br>1-2<br>1-3<br>1-4<br>2-1<br>2-2<br>2-3 | IEU11-A Option Components IEQ11-A Option Components Interprocessor Link Multiple Processor Link Example Devices on an IEC/IEEE Bus M8648 Module Configuration (UNIBUS) BCØ8S-Ø1 Test Cable Installed (M8648 Module) IEC Cable Connections (UNIBUS) | 1-4<br>1-5<br>1-6<br>1-7<br>2-6<br>2-7 |

#### FIGURES (Cont)

| Figure No.    | Title                                         | Page  |

|---------------|-----------------------------------------------|-------|

| 2-4           | IEEE Cable Connections (UNIBUS)               | 2-11  |

| 2-5           | IEC Cable Test Configuration (UNIBUS)         | 2-12  |

| 2-6           | IEEE Cable Test Configuration (UNIBUS)        | 2-13  |

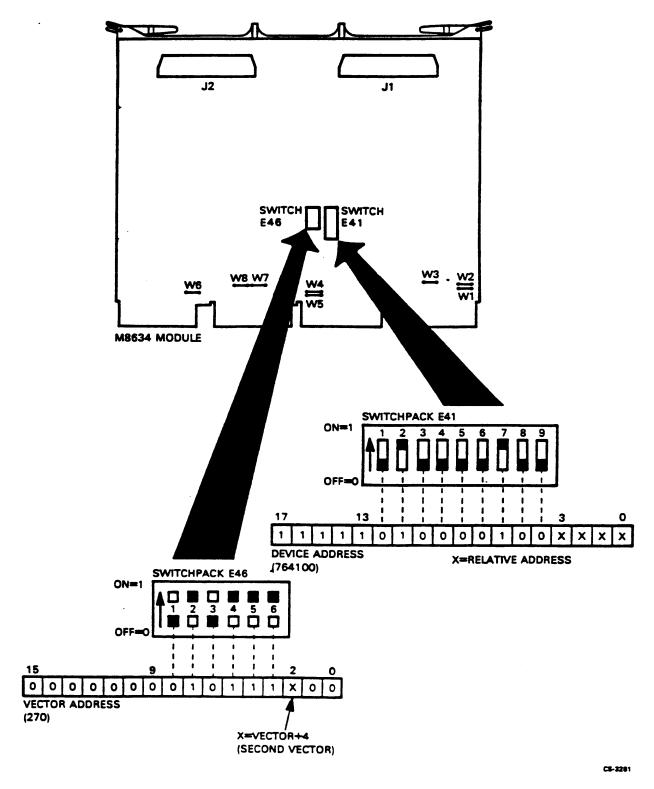

| 2-0           | M8634 Module Configuration (Q-Bus)            | 2-17  |

| <del></del> - | BC08S-01 Test Cable Installed (M8634)         | 2-21  |

| 2-8<br>2-9    | IEC Cable Connections, IEQ11-AA               | 2-23  |

| <del></del> - | IEEE Cable Connections, IEQ11-AB              | 2-24  |

| 2-10<br>2-11  | IEC Cable Test Configuration, IEQ11-AA        | 2-26  |

| 2-11          | IEEE Cable Test Configuration, IEQ11-AB       | 2-26  |

| 2-12          | IEC Cable Test Configuration, IEQ11-AC        | 2-27  |

| 2-13          | IEEE Cable Connections, IEQ11-AD              | 2-28  |

| 2-14          | IEC Cable Connections, IEQ11-AC               | 2-29  |

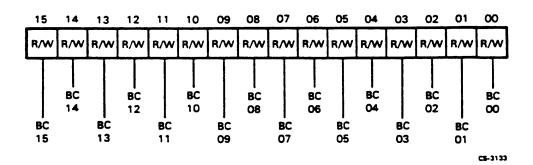

| 3-1           | IEEE Status Register (Write Only)             | 3-5   |

| 3-2           | IEEE Status Register (Read Only)              | 3-5   |

| 3-3           | IEEE Interrupt Register (Write Only)          | 3-11  |

| 3-4           | IEEE Interrupt Register (Read Only)           | 3-12  |

| 3-5           | IEEE Command Register (Write Only)            | 3-13  |

| 3-6           | IEEE Command Register (Read Only)             | 3-22  |

| 3-7           | IEEE Data Register (Write Only)               | 3-23  |

| 3-8           | IEEE Data Register (Read Only)                | 3-24  |

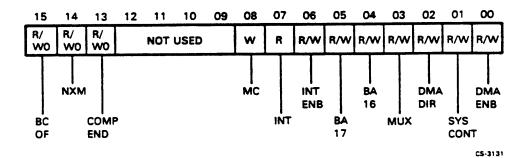

| 3-9A          | Control and Status Register                   | 3-25  |

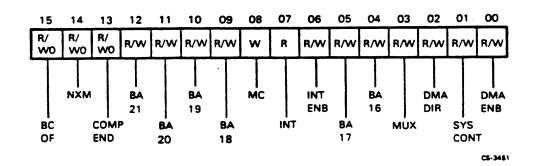

| 3-9B          | Control and Status Register (IEQ11-A Only)    | 3-25  |

| 3-10          | Bus Address Register                          | 3-30  |

| 3-10          | Byte Count Register                           | 3-30  |

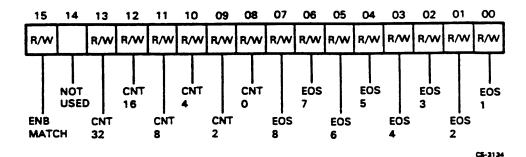

| 3-12          | Match Character Register                      | 3-31  |

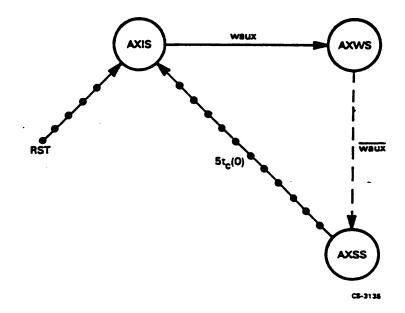

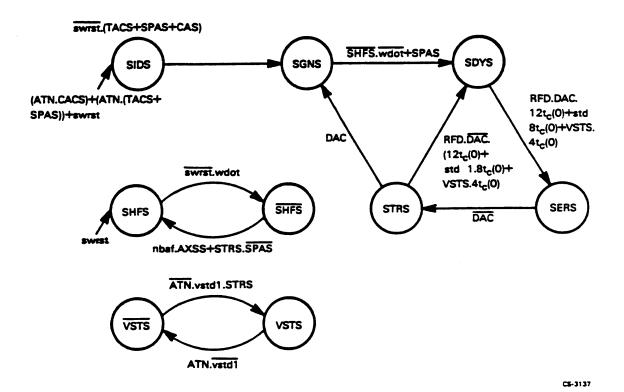

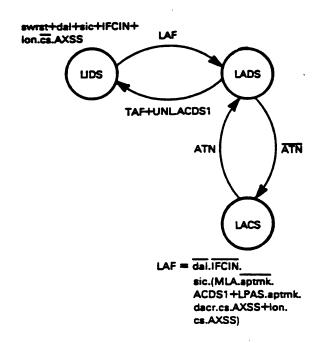

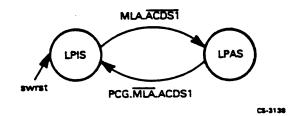

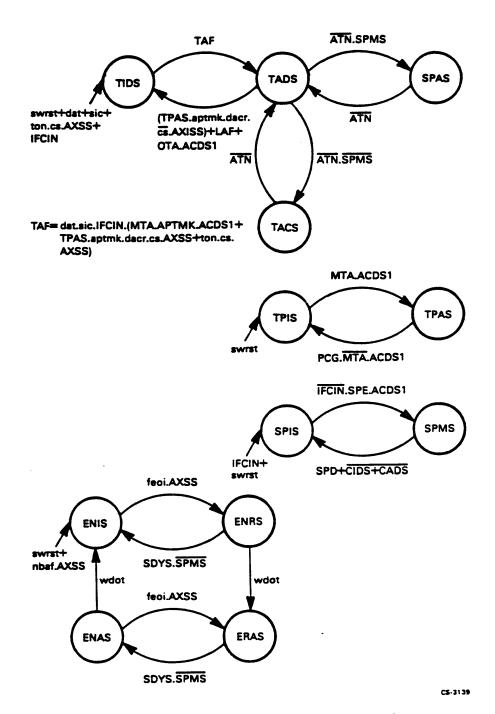

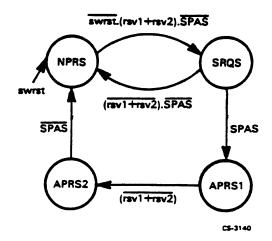

| 3-13          | TMS 9914A Auxiliary Command State Diagram     | 3-34  |

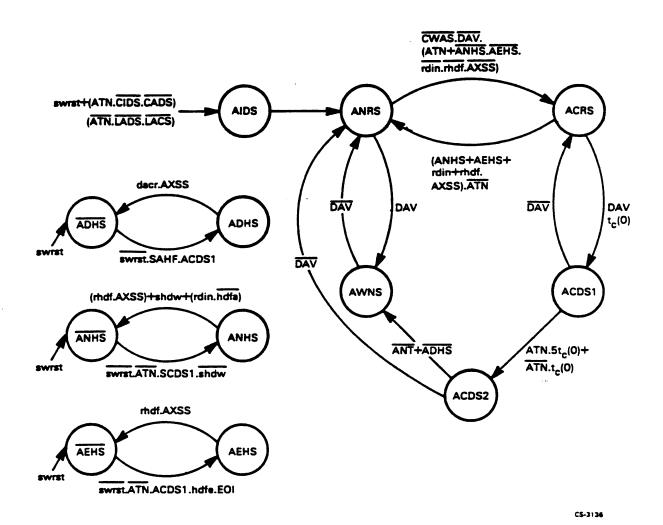

| 3-14          | TMS 9914A Acceptor Handshake State Diagram    | 3-35  |

| 3-15          | TMS 9914A Source Handshake State Diagram      | 3-39  |

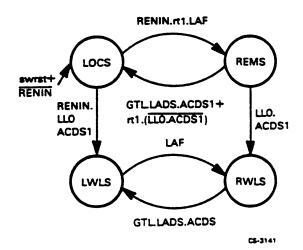

| 3-16          | TMS 9914A Listener State Diagram              | 3-42  |

| 3-17          | TMS 9914A Talker State Diagram                | 3-43  |

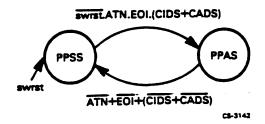

| 3-18          | Service Request State Diagram                 | 3-46  |

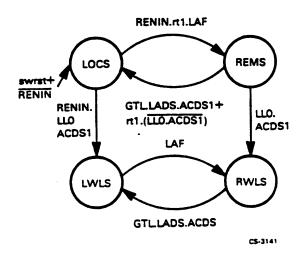

| 3-19          | TMS 9914A Remote Local State Diagram          | 3-48  |

| 3-20          | TMS 9914A Parallel Poll State Diagram         | 3-50  |

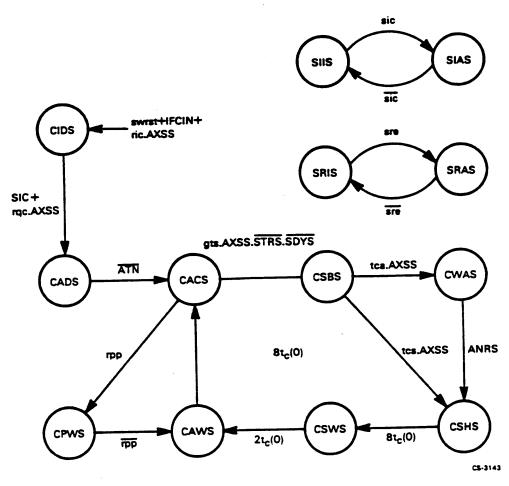

| 3-21          | TMS 9914A Controller State Diagram            | 3-52  |

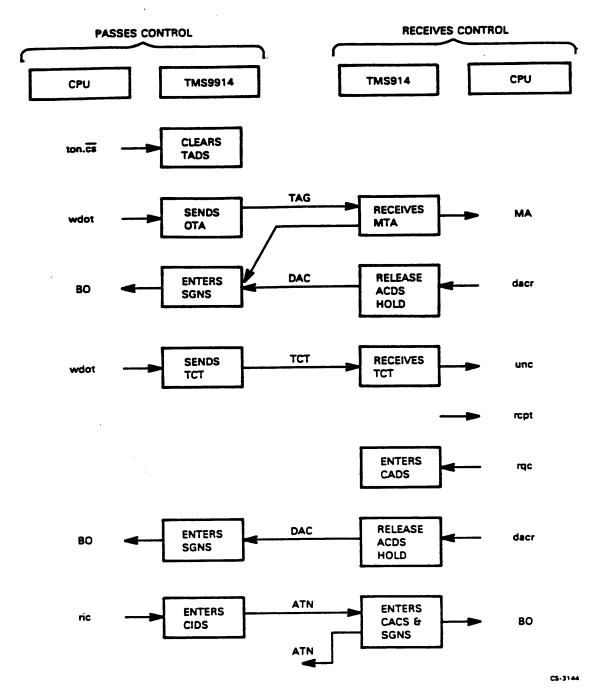

| 3-22          | Passing Control Between TMS 9914s             | 3-56  |

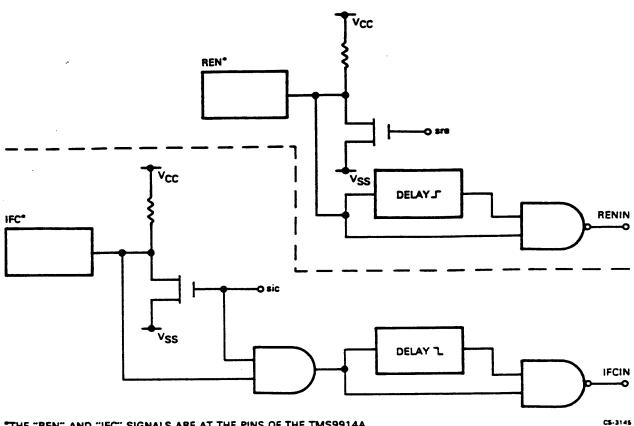

| 3-23          | IFC and REN Pins                              | 3-58  |

| 4-1           | IEU11-A and IEQ11-A Troubleshooting Flowchart | 4-2   |

| c-1           | Handshake Process Timing Diagram              | . C-2 |

| C-2           | Handshake Process Flow Diagram                | . C-3 |

| <b>.</b>      |                                               |       |

|               | TABLES                                        |       |

| Table No.     | Title                                         | Page  |

| 1-1           | Data Line                                     | . 1-8 |

| 1-2           | Interface Management Signal Lines             |       |

| 1-3           | Handshaking Lines                             | . 1-9 |

#### TABLES (Cont)

| Table No. | Title                                          | Page  |

|-----------|------------------------------------------------|-------|

| 1-4       | Address Command Group (ACG)                    | 1-10  |

| 1-5       | Universal Command Group (UCG)                  | 1-10  |

| 1-6       | Listener Address Group (LAG)                   | 1-11  |

| 1-7       | Talker Address Group (TAG)                     | 1-11  |

| 1-8       | Secondary Command Group                        | 1-12  |

| 1-9       | Functional Types of Devices                    | 1-13  |

| 1-10      | IEEE 488-1978 Interface Functions              |       |

| 1-11      | Environment Specifications                     | 1-15  |

| 1-12      | Electrical Specifications                      | 1-15  |

| 1-13      | Performance Parameters                         |       |

| 1-14      | IEC/IEEE Bus Parameters                        | 1-16  |

| 2-1       | IEUll-AA Option Shipping List (IEC Bus)        | 2-2   |

| 2-2       | IEUll-AB Option Shipping List (IEEE Bus)       |       |

| 2-3       | IEUll-A Site Requirements                      |       |

| 2-4       | IEQ11-AA Option Shipping List (IEC Bus)        |       |

| 2-5       | IEQ11-AB Option Shipping List (IEEE Bus)       | 2-14  |

| 2-6       | IEQ11-A Option Site Requirements               | 2-15  |

| 2-7       | BR Level Jumpers                               | 2-16  |

| 2-8       | System-Dependent Jumper Scheme                 | 2-19  |

| 2-9       | IEQ11-A Installation Cables                    | 2-27  |

| 3-1       | UNIBUS Addresses                               |       |

| 3-2       | Register Bit Abbreviations                     | 3-2   |

| 3-3       | TMS 9914A Read Registers                       |       |

| 3-4       | TMS 9914A Write Registers                      | . 3-3 |

| 3-5       | Interrupt Mask Register Ø and Interrupt Status |       |

|           | Register Ø Bit Description                     | 3-6   |

| 3-6       | Interrupt Mask Register 1 and Interrupt Status |       |

|           | Register 1 Bit Description                     |       |

| 3-7       | Address Status Register Bit Description        |       |

| 3-8       | Address Register Bit Description               |       |

| 3-9       | Auxiliary Commands                             |       |

| 3-10      | Software Reset Conditions                      |       |

| 3-11      | Control and Status Register Bit Format         | 3-28  |

| 3-12      | Match Character Register Bit Descriptions      | 3-32  |

| 3-13      | Auxiliary Command State Diagram Mnemonics      | 3-34  |

| 3-14      | Acceptor Handshake Mnemonics                   | 3-36  |

| 3-15      | Acceptor Handshake Message Outputs             |       |

| 3-16      | Source Handshake Mnemonics                     |       |

| 3-17      | Source Handshake Message Outputs               | 3-40  |

| 3-18      | Talker and Listener Mnemonics                  | 3-44  |

| 3-19      | Talker Function Message Outputs                | 3-45  |

| 3-20      | Service Request Mnemonics                      | 3-47  |

| 3-21      | Service Request Message Outputs                | 3-47  |

| 3-22      | Remote/Local Mnemonics                         | 3-48  |

| 3-23      | Parallel Poll Mnemonics                        | 3-50  |

| 3-24      | Parallel Poll Message Outputs                  | 3-5Ø  |

| 3-25      | Controller Function Mnemonics                  |       |

| 3-26      | Controller Function Message Outputs            | 3-54  |

| 3-27      | Multiline Interface Messages                   | 3-59  |

#### INTENDED AUDIENCE

The IEU11-A/IEQ11-A User's Guide is for either the field service engineer or the user who must install, program, or maintain either the IEU11-A option or the IEQ11-A option down to the Field Replaceable Unit (FRU) level.

#### DOCUMENT DESIGN

Chapter 1 provides general information about the IEU11-A option and the IEU11-A option. This chapter contains a physical description, application examples, functional description, and general specifications.

Chapter 2 contains the installation procedure for both the IEU11-A option and the IEQ11-A option. There are two separate installation procedures: one for the IEU11-A option, which is installed in UNIBUS systems (VAX-11 and PDP-11), and another for the IEQ11-A option which is installed in Q-Bus systems (LSI-11, MICRO/PDP-11 and MICRO/VAX).

Chapter 3 provides programming information for both the IEU11-A option and the IEU11-A option. This chapter defines the register bits for both the IEU11-A option and IEQ11-A option. Much of this chapter is taken from the TMS 9914A General Purpose Interface Bus (GPIB) Controller manual (published by Texas Instruments).

Chapter 4 contains guidelines in troubleshooting the IEU11-A option and the IEU11-A option. There is a troubleshooting flowchart and references to the required diagnostics for both options.

#### RELATED DOCUMENTATION

The following documents contain information that is relevant to both the IEU11-A option and the IEQ11-A option.

| Title                                                               | Document Number | Source                          |

|---------------------------------------------------------------------|-----------------|---------------------------------|

| PDP-11 Bus Handbook                                                 | EB-17525-20     | Available in hardcopy           |

| IEUll-A Print Set                                                   | MP-Ø1179        | Shipped with the IEU11-A option |

| IEQ11-A Print Set                                                   | MP-01180        | Shipped with the IEQ11-A option |

| PDP-11 Diagnostic<br>Listing                                        | AC-T064C-MC     | Distributed by SDC              |

| IEX11-A IEC/IEEE Bus<br>Interfaces (A Service<br>Information Guide) | EY-1064E-SG-001 | Available in hardcopy           |

Document Number

Source

Title

\*TMS 9914A General Purpose Interface Bus (GPIB) Controller Published by Texas Instruments

DIN IEC625 Part 1

Published by DIN Deutsches Inst.fuer Normung E.V.

\*IEEE Standard 488-1975-78 Published by The Institute of Electrical and Electronic Engineers

Additional copies of this document and printed copies of the documents listed above (except those documents marked with an {\*}) may be obtained from:

Digital Equipment Corporation 444 Whitney Street Northboro, Massachusetts Ø1532

ATTN: Printing and Circulation Services (NR2/Ml5)

Customer Services Section

#### IMPORTANT NOTICE

Texas Instruments reserves the right to make changes at any time to the TMS 9914A General Purpose Interface Bus (GPIB) Controller (IC chip) in order to improve design and to supply the best product possible.

TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

Copyright 1982

Texas Instruments Incorporated

In accordance with the Copying License Agreement, Texas Instruments has granted Digital Equipment GmbH publishing rights for Chapter 3 of this document.

#### 1.1 INTRODUCTION

This manual describes two similar but distinct options: the IEU11-A option, and the IEQ11-A option. The IEU11-A option is a DMA controller that interfaces a UNIBUS system to two independent instrument buses (IEC/IEEE). The IEQ11-A option is a DMA controller that interfaces a Q-bus system to two independent instrument buses (IEC/IEEE). In both options the instrument buses conform to both the European Standard IEC 625-1 and the U.S. Standard IEEE 488-1978. Each instrument bus can have up to fifteen devices in a sequential configuration. The total of fifteen devices includes the option itself.

#### NOTE

The designation IEU11-A/IEQ11-A option is used to refer to both the IEU11-A option and IEQ11-A option simultaneously. This designation is used in this manual for convenience only, since the IEU11-A option and the IEQ11-A option are two distinct options.

Software drivers control and communicate with the IEU11-A/IEQ11-A option through programmed I/O transfers, DMA transfers, and interrupts. Programmed transfers are normally used for command bytes. DMA transfers are used for data bytes.

#### 1.2 PHYSICAL DESCRIPTION

There are two kinds of options: the IEUll-A option, and the IEQll-A option. The IEUll-A option is used in UNIBUS systems, such as the PDP-ll and VAX-ll systems. The IEQll-A option is used in the Q-BUS systems, such as the LSI-ll, MICRO/PDP-ll and MICRO/VAX systems.

#### NOTE

MICRO/PDP-11 systems and MICRO/VAX systems (both Q22-BUS and BA23 boxes) will, in the following document, be referred to as MICRO systems.

Figure 1-1A IEU11-A Option Components

#### 1.2.1 IEU11-A Option Components

The IEU11-A option consists of one M8648 module and a BC08S-01 test cable. The type of cable and bulkhead panel depends on whether the option is used with an IEC bus or an IEEE bus. In an IEC bus installation, the IEC-625 bulkhead will hold an IEC bus cable (BN11C-02). Although it is shipped with only one cable, a second cable (17-00384-02) is optional. In an IEEE bus installation, the IEEE-488 bulkhead attaches to only one IEEE bus cable (BN11D-02). A second IEEE-488 bulkhead panel and IEEE bus cable combination (BN11D-02) is optional. The BC08S-01 test cable connects J1 and J2 connectors on the M8648 module when diagnostics are run to test the IEU11-A option. Refer to Figure 1-1A for the IEU11-A option components.

#### 1.2.2 IEQ11-A Option Components

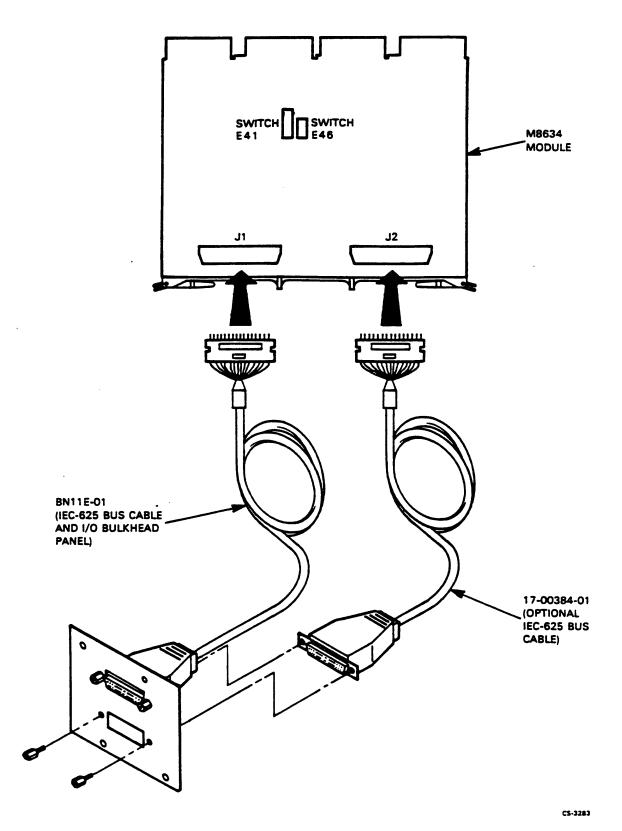

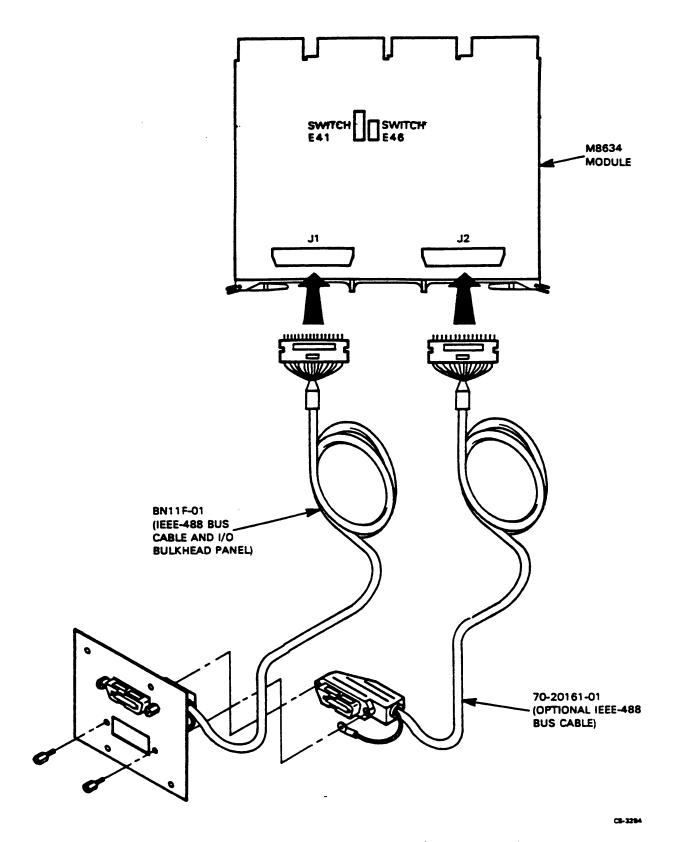

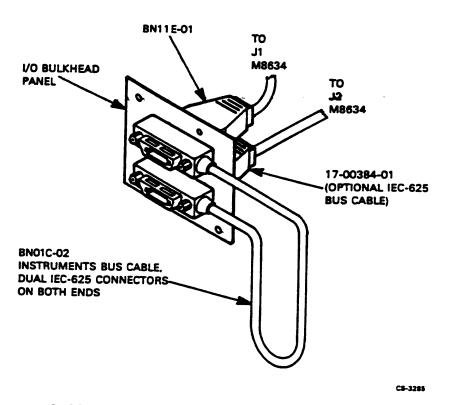

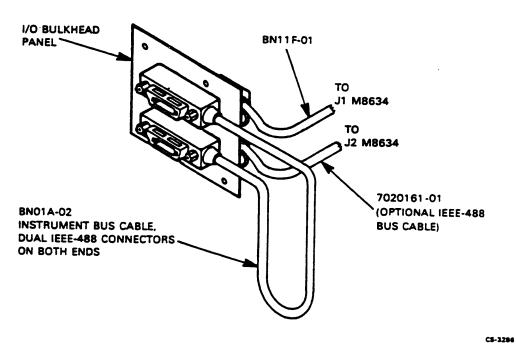

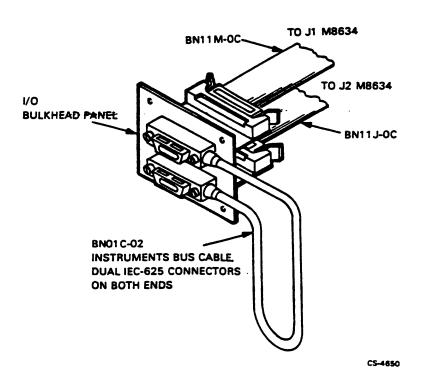

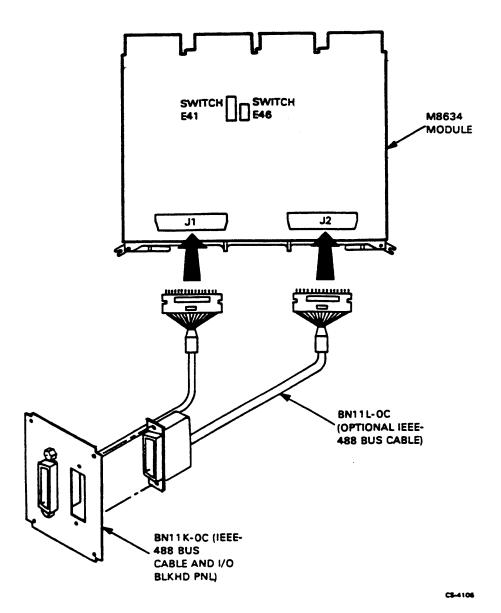

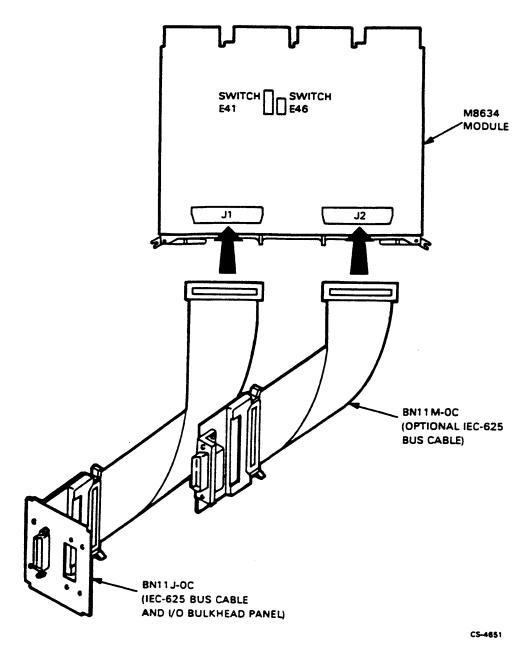

The IEQ11-A option consists of one M8634 module and a BC08S-01 test cable. The type of cable used with the bulkhead panel depends on whether the option is used with an IEC bus or IEEE bus. In an IEC bus installation, the C size IEC-625 bulkhead panel is used with one IEC bus cable (BN11E-Ø1). The second bus cable (17-00384-01) is optional. In an IEEE bus installation, a C size IEEE-488 bulkhead panel is used with one IEEE-488 bus cable (BN11F-Ø1). The second cable (7Ø-2Ø161-Ø1) is optional. For the MICRO systems, a B-size IEEE-488 bulkhead panel is used with one IEEE-488 bus cable (BN11K-0C). The second cable (BN11L-ØC) is optional. For IEC Bus applications, a B-size IEC 625-1 bulkhead panel is used with one IEC 625-1 bus cable (BN11J-0C). The second cable (BN11M-0C) is optional. The BC08S-01 test cable connects J1 and J2 connectors on the M8634 module when diagnostics are run to test the IEQ11-A option.

Refer to Figure 1-1B and Figure 2-13 for the IEQ11-A option components.

Figure 1-1B IEQ11-A Option Components

#### 1.3 APPLICATION EXAMPLES

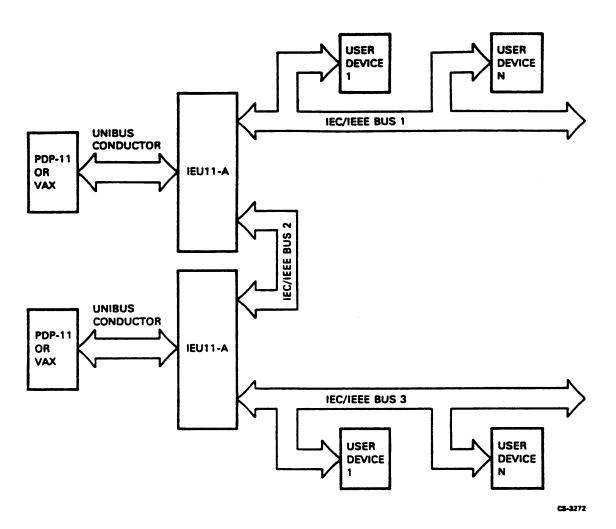

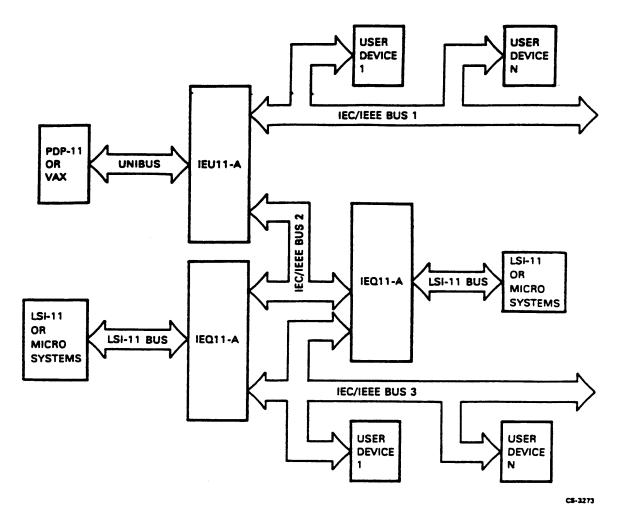

The IEU11-A/IEQ11-A option can be configured in numerous ways. Figure 1-2 shows an interprocessor link, while Figure 1-3 shows a multiple processor link.

Figure 1-2 Interprocessor Link

Figure 1-3 Multiple Processor Link

#### 1.4 FUNCTIONAL DESCRIPTION

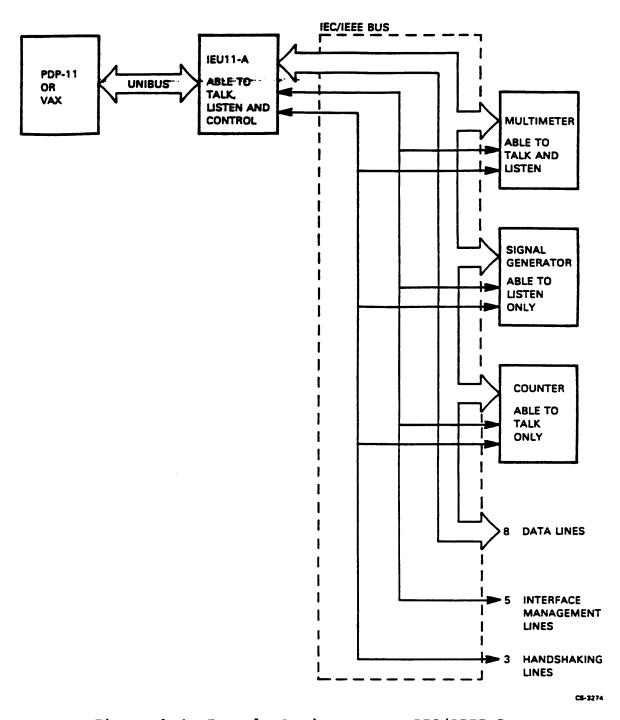

The IEC/IEEE bus, a standardized instrumentation bus, transfers digital data between a group of instruments and a computer system (see Figure 1-4). The data is transmitted in bit-parallel/byte-serial format. The data can consist of either interface messages or device dependent messages.

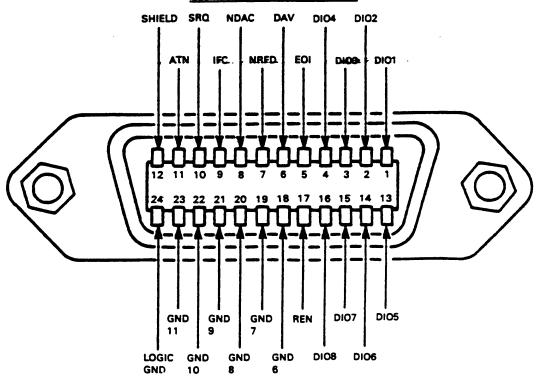

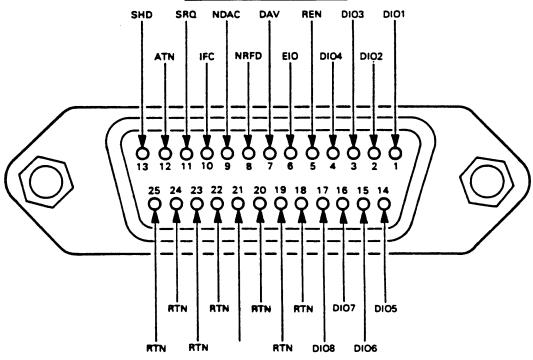

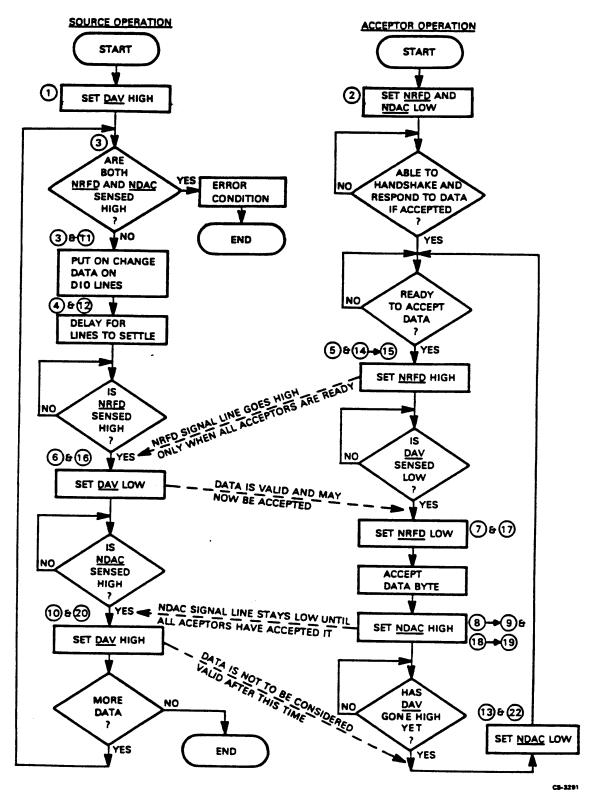

There are sixteen lines that are used to control and transmit messages between the devices. These lines are as follows: eight data lines, five interface management lines, and three handshaking lines. All data is transferred by means of the data lines (DIO <8:1>). Refer to Table 1-1 for data lines parameters. The interface management signal lines control the overall bus operations (Table 1-2 describes these signal lines). The three handshaking lines operate in a three-wire interlocked handshake process to transfer each data byte by means of the DIO data lines (Table 1-3 describes the function of these lines, while Appendix C describes the handshaking process itself).

1 -6

Figure 1-4 Example Devices on an IEC/IEEE Bus

Table 1-1 Data Line

| Signal Name       | Mnemonic  | Function                                                                                                                                                        |  |  |

|-------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data Input/Output | DIO (8:1) | DIO <8:I7 lines are the data input/output lines to the IEC/IEEE bus. These data lines are connected to the IEC/IEEE bus by means of non-inverting transceivers. |  |  |

Table 1-2 Interface Management Signal Lines

| Signal Name     | Mnemonic | Function                                                                                                                                            |

|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Attention       | ATN      | Sent by the controller in charge. When true (low), interface commands are being sent over the DIO lines. When false (high), these lines carry data. |

| Interface Clear | IFC      | Sent by the system controller to set the interface system into a known quiescent state. The system controller becomes the controller in charge.     |

| Service Request | SRQ      | Set true (low) by a device to in-<br>dicate a need for service.                                                                                     |

| Remote Enable   | REN      | Sent by system controller to select control either from the front panel or from the IEC/IEEE bus.                                                   |

| End Or Identify | EOI      | If ATN is false (high), this indicates the end of a message block. If ATN is true (low), the controller is requesting a parallel poll.              |

Table 1-3 Handshaking Lines

| Signal Name       | Mnemonic | <b>Punction</b>                                                                  |

|-------------------|----------|----------------------------------------------------------------------------------|

| Data Valid        | DAV      | Controlled by source to show acceptors when valid data is presented to the bus.  |

| Not Ready For Dat | a NRFD   | Sent by acceptor to indicate read-<br>iness for next byte.                       |

| Not Data Accepted | ndac     | Acceptor sets this false (high) when it has latched the data from the I/O lines. |

- 1.4.1 IEC/IEEE Interface Messages

This section describes the messages that may be sent by means of

the IEC/IEEE Bus by a controller-in-charge. A controller-incharge is an IEU11-A/IEQ11-A option that is active (CACS). The

messages can be divided into five groups.

- Address Command Group (ACG)

- Universal Command Group (UCG)

- 3. Listener Address Group (LAG)

- 4. Talker Address Group (TAG)

- 5. Secondary Command Group (SCG)

- 1.4.1.1 Address Command Group (ACG) -- These commands are effective only in devices which have been addressed as a Listener or a Talker. Table 1-4 list the ACG commands.

Table 1-4 Address Command Group (ACG)

| Mnemonic | Octal       | ASCII | Punction  | Command                        | Description                                                                                                                                                                                                                                                                          |

|----------|-------------|-------|-----------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GTL      | 961         | SOB   | Listener  | Go To Local                    | Causes addressed listeners to go from Remote mode to Local mode. When local is true, a device is controlled by its front or back panel controls.                                                                                                                                     |

| SDC      | 564         | ECT   | Listeners | Selected<br>Device Clear       | Causes the addressed listeners to be reset (initialization).                                                                                                                                                                                                                         |

| PPC      | <b>66</b> 5 | 20    | Listener  | Perallel Poll<br>Configuration | Causes the addressed listeners to enter the Perallel Poll Configuration mode so that the addressed listeners are able to perticipate in a parallel poll. The next command must be PPE from the Secondary Command Group to allow the listener to respond to ATN or EDI becoming true. |

| ट्या     | <b>616</b>  | BS    | Listener  | Group<br>Execute<br>Trigger    | Causes the addressed listeners to<br>start basic operation of the<br>device of which the listener is<br>a part.                                                                                                                                                                      |

| TCT      | <b>811</b>  | HT    | Talker    | Take Control                   | Causes a device which has been addressed as the talker to enable its controller to become the controller-in-charge after the current controller-in-charge unasserts ATN.                                                                                                             |

1.4.1.2 Universal Command Group (UCG) -- These commands affect all devices which are able to respond without having to be previously addressed. The UCG commands are listed in Table 1-5.

Table 1-5 Universal Command Group (UCG)

| Mnemonic | Octal | ASCII | Command                      | Description                                                                                                                                 |

|----------|-------|-------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| то       | 621   | OC.1  | Local Lockout                | Causes all devices to ignore their local message RTL (Return To Local).                                                                     |

| DCL      | 624   | 004   | Device Clear                 | Causes all devices to be reset (initialization).                                                                                            |

| PPU      | 625   | NAK   | Parallel Poll<br>Unconfigure | Causes all parallel poll configurations co become unconfigured.                                                                             |

| SPE      | 838   | CAN   | Serial Poll<br>Enable        | Causes all talkers to enter the serial poll mode to allow a talker to send a status byte after being addressed by the controller-in-charge. |

| SFD      | 631   | 234   | Serial Poll<br>Disable       | Causes all talkers to exit the serial poll mode and return to the normal data mode.                                                         |

1.4.1.3 Listener Address Group (LAG) -- These commands may be used to address one or more listeners or to address all listeners at once. Addressed listeners become active when the controller-in-charge unasserts ATN. The LAG commands may be followed by a secondary address (MSA) to address an extended listener. Table 1-6 lists the LAG addresses.

Table 1-6 Listener Address Group (LAG)

| Mnemonic | Octal       | ASCII | Address                 | Description                                                                                                                                                                    |

|----------|-------------|-------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIA 86   | 646         | SP    | My Listen<br>Address 8  | Any listener that recognizes its own address becomes an addressed listener, and is able to receive data bytes from a talker as soon as the controller-in-charge unasserts ATN. |

| MIA 61   | <b>941</b>  | 1     | My Listen<br>Address 1  | •                                                                                                                                                                              |

| MIA 38   | <b>87</b> 6 | >     | My Listen<br>Address 38 | •                                                                                                                                                                              |

| UNL      | 677         | 7     | Unlisten                | Causes all listeners to become unaddressed.                                                                                                                                    |

1.4.1.4 Talker Address Group (TAG) -- These commands are used to address or unaddress one talker. An addressed talker becomes active when the controller-in-charge unasserts ATN. The commands in the TAG may be followed by a secondary address (MSA) to address an extended talker.

Table 1-7 Talker Address Group

| Mnemonic | Octal | ASCII | Address               | Description                                                                                                                                                                     |

|----------|-------|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MTDA 96  | 166   | ę     | My Talk<br>Address 8  | A talker that recognizes its own address becomes an addressed talker, whereas all other talkers becomes unaddressed. Only one talker is able to send data via the IEC/IEEE Bus. |

| MIDA 81  | 161   | A     | My Talk<br>Address 1  | •                                                                                                                                                                               |

| MTA 30   | 136   | •     | My Talk<br>Address 30 | •                                                                                                                                                                               |

| UNT      | 137   | -     | Untalk                | Causes the addressed talker to become un-<br>addressed.                                                                                                                         |

1.4.2 Secondary Command Group (SCG)

The meaning of these commands is defined by the preceeding primary command of the Primary Command Group (PCG= ACG UCG LAG TAG). Table 1-8 list the SCG commands.

Table 1-8 Secondary Command Group

| Mnemonic            | Octal | ASCII | Command                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|-------|-------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PPE 61              | 145   |       | Parallel Poll<br>Enable #1 | Each PPE command must follow a PPC (Parallel Poll Configure) command which forces currently addressed listemers into their Parallel Poll Configuration state. The PPE command indicates to a device how to respond to a parallel poll request from the controller-in-charge. A device responds by sending one status bit on one of the eight DIO lines. The second digit of the PPE command memonic specifies that line, whereas the first digit specifies which state of the devices status bit should activate the DIO line. For example, PPE 12 instructs the device to activate the DIO line 2 when the device status bit is "1", and PPE 62 instructs the device to activate that line if the status bit is "5". A Parallel Poll Request is issued by the controller-in-charge by activating the EDI line together with the ATN line. |

| PPE 82              | 141   | •     | Parallel Poll<br>Enable 2  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PPE 67              | 146   | f ·   | Parallel Poll<br>Enable 97 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PPE 98              | 147   | g     | Parallel Poll<br>Enable #8 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PPE 11              | 150   | h     | Parallel Poll<br>Enable 11 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PPE 12              | 151   | i     | Perallel Poll<br>Enable 12 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PPE 17              | 156   | n     | Parallel Poll<br>Enable 17 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PPE 18              | 157   | •     | Parallel Poll<br>Enable 18 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PPD                 | 165   | P     | Perallel Poll<br>Disable   | This command must follow its associated PPC command and inhibits devices from responding to the Parallel Poll Request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MSA <sub>.</sub> 60 | 146   |       | My Secondary<br>Address 8  | An MSA Command must follow a Talker or Listener Address. Devices that use extended addressing will not become addressed as long as the associated Secondary Address follows the Primary Address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MSA (II)            | 141   | •     | My Secondary<br>Address 1  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MSA 29              | 175   | 3     | My Secondary<br>Address 29 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MSA 30              | 176   | -     | My Secondary<br>Address 30 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### 1.4.3 Types of Functional Devices There are four functional types of devices that can be used on the IEC/IEEE bus. These functional types are the following:

- Talk only devices

- Listen only devices

- Talk and listen devices

- Talk, listen, and control devices

Table 1-9 describes these functional types of devices.

Table 1-9 Functional Types of Devices

| Device Type                  | Function                                                                                                                                            | Example Device            |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Talk Only                    | When signaled, this device applies its output to the DIO lines in a fixed configuration. The configuration may be altered by a front panel control. | Counter                   |

| Listen Only                  | Responds to data from the DIO lines.                                                                                                                | Printer, signal generator |

| Listens and<br>Talks         | This device is configured by signals from the controller, receives the requested reading, and returns the results to the IEC/IEEE bus.              | Digital<br>multimeter     |

| Talks, Listens, and Controls | Not only can talk and listen,<br>but also controls all opera-<br>tions on the IEC/IEEE bus.                                                         | IEU11-A or<br>IEQ11-A     |

# 1.4.4 IEC/IEEE Bus System Each IEC/IEEE Bus system must have three basic functional elements to be able to organize and manage the information exchanged between devices. The three functional devices are the following:

- Controller device

- Listener device

- Talker device

When acting as a controller, the IEU11-A/IEQ11-A option can be the controller-in-charge, as well as the system controller. An IEC/IEEE Bus System can have multiple devices which contain the controller interface function. However, only one device at a time can be the controller, and this device is known as the controller-in-charge. The system controller is the controller that is able to send IFC and REN messages (see Table 1-2 for the definition of IFC and REN). Only one device can be assigned as system controller.

An IEU11-A/IEQ11-A option becomes a listener when the controller-in-charge sends its listen address over the IEC/IEEE bus, or by loading its own Auxiliary Command Register with the Listen Only command (LON). When active, the listener receives data bytes from the IEC/IEEE bus to the IEU11-A/IEQ11-A option. Multiple listeners may be configured simultaneously.

An IEUll-A/IEQll-A option becomes a talker when the controller-incharge applies its talk address by means of the IEC/IEEE bus, or by loading its own Auxiliary Command Register with the Talk Only command (TON). When active, the talker sends data bytes from the IEUll-A/IEQll-A option to the IEC/IEEE bus. Only one device at a time acts as a talker.

1.4.5 IEEE 488-1978 Interface Functions

The IEU11-A/IEQ11-A option provides the IEEE 488-1978 interface

functions listed in Table 1-10.

Table 1-10 IEEE 488-1978 Interface Functions

| Function Name                                                | Mnemonic       |

|--------------------------------------------------------------|----------------|

| Automatic Source Handshake                                   | SH1            |

| Automatic Acceptor Handshake                                 | AH1            |

| Talker and Extended Talker (includes serial poll capability) | T5, TE5        |

| Listener and Extended Listener                               | L3, LE3        |

| Service Request                                              | SR1            |

| Remote Local                                                 | RL1            |

| Parallel Poll                                                | PP1, PP2       |

| Device Clear                                                 | DC1            |

| Device Trigger                                               | DT1            |

| Controller                                                   | Cl, 2, 3, 4, 5 |

#### 1.5 GENERAL SPECIFICATIONS

This section contains information on environmental specifications, electrical specifications, performance parameters, and IEC/IEEE bus parameters. Refer to Table 1-11 through Table 1-14 for the information.

Table 1-11 Environment Specifications

| Environmental Parameter | Specification            |

|-------------------------|--------------------------|

| Operating Temperature   | 5° to 50° C              |

| Relative Humidity       | 10% to 90% noncondensing |

Table 1-12 Electrical Specifications

| Electrical Parameter   | Specification                                                     |  |  |  |

|------------------------|-------------------------------------------------------------------|--|--|--|

| Required Voltage(s)    | +5 V dc ( <u>+</u> 5%)                                            |  |  |  |

| Current Requirement(s) | 3.5A @ +5 volts (IEU11-A Option) 3.0A @ +5 volts (IEQ11-A Option) |  |  |  |

| UNIBUS/LSI Bus Load    | 1                                                                 |  |  |  |

| Logic Levels           | TTL                                                               |  |  |  |

| IEC/IEEE Bus Load      | l on each bus                                                     |  |  |  |

Table 1-13 Performance Parameters

| Parameter                   | Specifications                                                                                                                      |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Operating Mode(s)           | 1. Programmed I/O transfers with interrupt.                                                                                         |

|                             | <ol><li>DMA data transfer, byte addressing, and<br/>interrupt.</li></ol>                                                            |

| Transfer Rate               | Up to 150K bytes per second (DMA transfer). Transfer rates dependent on the hardware configuration and operating system being used. |

| Maximum Block<br>Length     | 64K bytes                                                                                                                           |

| Addressable<br>Memory Range | 256 KB (4MB on Q-22)                                                                                                                |

| Interrupt                   | Vector A (channel 1) is selectable, while Vector B (channel 2) depends on Vector A. Vector A is set at A+4.                         |

| Priority Level              | BR6 (selectable). BR4 is used on Q-bus CPUs.                                                                                        |

Table 1-14 IEC/IEEE Bus Parameters

| Parameter                | Specification  Two independent IEC/IEEE buses                                               |  |  |

|--------------------------|---------------------------------------------------------------------------------------------|--|--|

| Communication<br>Channel |                                                                                             |  |  |

| Number of Devices        | Up to 15 devices on each bus (includes IEU11-A/IEQ11-A)                                     |  |  |

| Maximum Cable<br>Length  | Two meters (6.56 ft) times the number of devices, or 20 meters (65.6 ft), whichever is less |  |  |

|                          | NOTE                                                                                        |  |  |

| Individual exceed four   | cable length should not meters between devices.                                             |  |  |

#### 2.1 INTRODUCTION

The IEUll-A option can be installed in either a PDP-11 or a VAX-II system, while the IEQ11-A option can be installed in either a LSI-11 or a MICRO system. The installation procedure for LSI-11 and MICRO systems is different from the PDP-11 and VAX-11 systems, since a different module is used.

An installation consists of the following six major steps.

- 1. Unpacking and inspection

- 2. Module configuration

- 3. Module installation

- 4. Verifying module operation

- 5. Field service and customer acceptance

- 6. IEC/IEEE bus interconnection

To do an IEU11-A/IEQ11-A option installation, perform the following:

- PDP-11 or VAX-11 system installation Sections 2.2 through 2.8.

- LSI-11 or MICRO systems installation Sections 2.9 through 2.15.

#### 2.2 IEU11-A OPTION UNPACKING AND INSPECTION

The IEUll-A option is packed according to commercial packing practices. Remove all packing materials and check the equipment against the shipping list. Table 2-1 lists the items contained in the IEUll-AA option (IEC bus), while Table 2-2 lists the items contained in the IEUll-AB option (IEEE bus).

Table 2-1 IEU11-AA Option Shipping List (IEC Bus)

| Qty. | Part Number | Description                                                            |

|------|-------------|------------------------------------------------------------------------|

| 1    | M8648       | Dual IEC/IEEE bus controller (UNIBUS)                                  |

| I    | BCØ8S-Ø1    | Test cable                                                             |

| 1    | BN11C-02    | IEC 625-1 bus system cable with PDP-11 bulkhead panel assembly         |

| 1    | BNØ1C-Ø2    | Instrument bus cable, dual IEEE-488 connectors on both ends (optional) |

Table 2-2 IEUll-AB Option Shipping List (IEEE Bus)

| Qty. | Part Number | Description                                                            |

|------|-------------|------------------------------------------------------------------------|

| 1    | M8648       | Dual IEC/IEEE bus controller (UNIBUS)                                  |

| 1    | BCØ8S-Ø1    | Test cable                                                             |

| 1    | BN11D-02    | IEEE 488 bus cable with PDP-11 bulk-head panel assembly                |

| 1    | BNØ1A-02    | Instrument bus cable, dual IEEE-488 connectors on both ends (optional) |

Inspect all items and carefully check the module for cracks, loose components, and breaks in the etched paths. Report damages or missing items to the shipper immediately, and inform the DIGITAL representative.

2.3 IEU11-A SITE REQUIREMENTS

Table 2-3 lists the site requirements for the IEU11-A option.

Table 2-3 IEUll-A Site Requirements

| Parameter                  | Requirements                                             |

|----------------------------|----------------------------------------------------------|

| Module Environment         | DD11 backplane; one hex SPC-slot with NPR jumper removed |

| Voltage Requirements       | 5V dc @ 3.5 A                                            |

| Bulkhead Panel Size        | One 2-insert unit                                        |

| Location of Bulkhead Panel | Anywhere in bulkhead frame                               |

Table 2-3 IEU11-A Site Requirements (Cont)

| Parameter                | Requirements                                                                                                                                                                                                             |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Address           | The factory installed address is 764100. The IEU11-A requires an assignment of eight consecutive device addresses in the UNIBUS I/O page. The factory installed address is assigned to the first register (ISR 1 and 2). |

| Interrupt Vector Address | The factory installed Interrupt Vector address is 270. The Interrupt Vector Address requires a block of two interrupt vectors (four words) at the beginning of an address where bits <2:0> must equal 0.                 |

| Interrupt Priority Level | BR6 (bus grant jumper plug).                                                                                                                                                                                             |

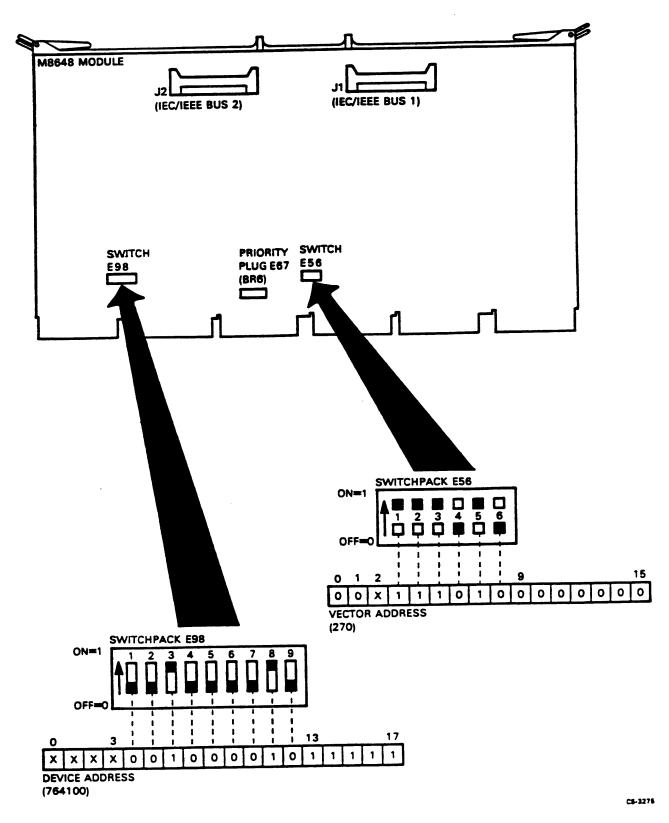

#### 2.4 M8648 MODULE CONFIGURATION

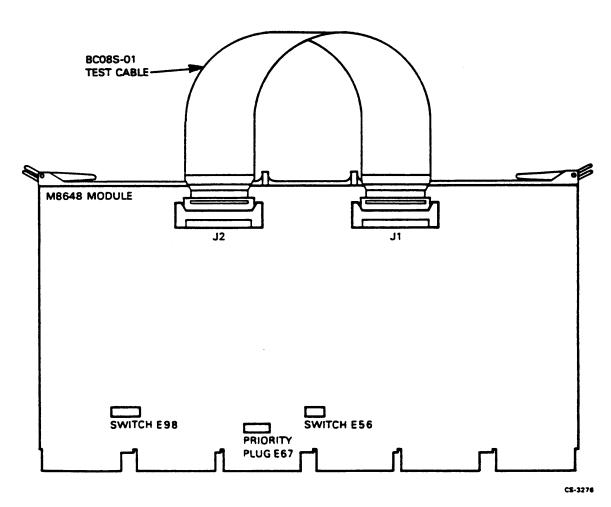

Two dip switchpacks and a replaceable bus grant jumper plug determine the M8648 module configurations. One dip switchpack (E98) is used for the device address, while the other dip switchpack (E56) is used for the interrupt vector address. A bus grant jumper plug is used to determine the BR level, normally BR6.

#### 2.4.1 M8648 Module Configuration Procedure

| 2.4.1 | M8648 Module Configuration Procedure                                                                                                                                                                                                                                                                                                                                       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step  | Procedure                                                                                                                                                                                                                                                                                                                                                                  |

| 1     | Verify that the correct device address (764100) is set in dip switchpack E98 (refer to Figure 2-1). If a second IEU11-A option is used in the same system, another device address must be assigned to the second IEU11-A option. The device address must always be in increments of 20 (octal) starting from 0. Refer to Figure 2-1 for the dip switchpack address scheme. |

| 2     | Verify that the correct interrupt vector address (270) is set in the dip switchpack E56 (refer to Figure 2-1). If a second IEU11-A option is used in the same system, another interrupt vector address must be assigned to the second IEU11-A option. Refer to Figure 2-1 for the dip switchpack address scheme.                                                           |

| 3     | Verify that the correct bus grant jumper plug (E67) is installed and seated properly (refer to Figure 2-1). If the plug (E67) does not meet the required BR level, remove the plug and install one of desired level.                                                                                                                                                       |

#### NOTE

Ensure that any changes from the standard configuration are noted and are considered during the software driver installation, because the default parameters expect a standard hardware configuration.

- 2.5 M8648 MODULE INSTALLATION

The IEU11-A option can be installed in any DD11 system unit or CPU backplane that accepts hex-height modules. The IEU11-A uses a SPC slot.

- 2.5.1 M8648 Module Installation Procedure

5.25 V.

| 2.5.1 | M8646 Module Installation Flocedure                                                                                                                                                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step  | Procedure                                                                                                                                                                                                                                                                     |

| 1     | Turn off system power.                                                                                                                                                                                                                                                        |

| 2     | Locate the SPC slot in the DD11 backplane that the M8648 module is to be installed in. DO NOT insert the M8648 module into the backplane at this time.                                                                                                                        |

| 3     | Remove the NPG jumper between pins CA1 and CB1 from the designated M8648 slot on backplane.                                                                                                                                                                                   |

| 4     | Remove the Grant Continuity Card from the designated M8648 slot.                                                                                                                                                                                                              |

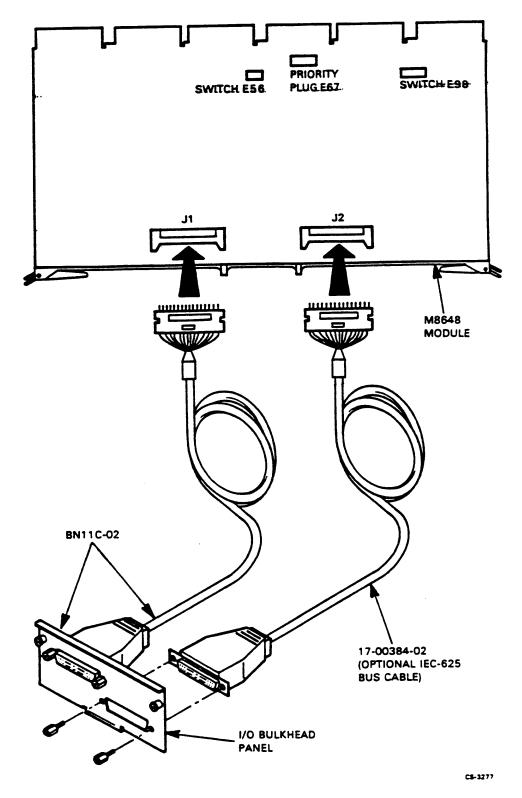

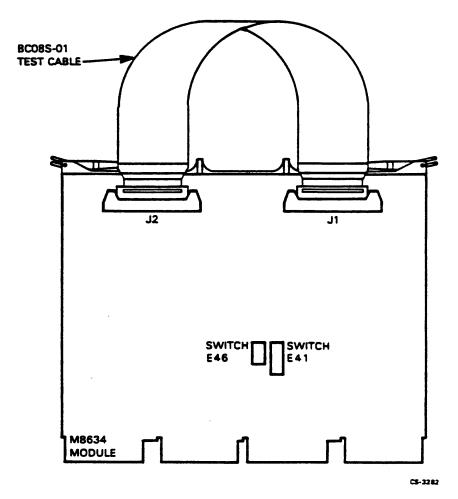

| 5     | Connect the M8648 Jl connector to the M8648 J2 connector with a BCØ8S-Øl cable (refer to Figure 2-2). Ensure that Pin A of connector Jl is connected to Pin A of connector J2. The BCØ8S-Øl cable needs to be installed to run the diagnostics and DEC-X/ll System Exerciser. |

| 6     | Insert the M8648 module into the designated SPC slot.                                                                                                                                                                                                                         |

| .7    | Turn on the system power.                                                                                                                                                                                                                                                     |

| 8     | Measure the +5 Vdc (Pin A2, any slot) on the DD11 system                                                                                                                                                                                                                      |

2.6 VERIFYING M8648 MODULE OPERATION

Choosing which diagnostic to use to verify the operation of the M8648 module depends on whether the M8648 is installed in a PDP-11 system or a VAX-11 system. Therefore, if the M8648 module is installed in a PDP-11 system, proceed to Section 2.6.1. If it is installed in a VAX-11 system, proceed to Section 2.6.2.

backplane. The voltage should be between 4.75 V and

#### NOTE

The diagnostics required to verify the operation of the M8648 module are not shipped with the IEU11-A option. The diagnostics are distributed to DIGITAL Field Service through the Software Distribution Center (SDC).

- 2.6.1 M8648 Module Operation Verified in a PDP-11 System The operation of the M8648 module (PDP-11) is verified by running the CZIEA?? IEU/IEQ Static Diagnostic. The loading and operating procedures for the diagnostic are contained in the program listing. The BC08S-01 cable must be installed (Figure 2-2). Perform the following:

- Run the default series of tests for the unit.

- Run three error free passes of Tests 1 through 26 with the 'Quick Verify' flag selected.

- Run one error free pass without the 'Quick Verify' flag selected.

- 2.6.2 M8648 Module Operation Verified in a VAX-11 System

The operation of the M8648 module (VAX-11) is verified by running

the IEU11-A M8648 Offline Test Diagnostic (EVCDC). The EVCDC

diagnostic is a repair level (Level 3) diagnostic that exercises

an M8648 module. This diagnostic requires a VAX-11 Diagnostic

Supervisor of V6.11 or later. Instructions for running the

Diagnostic Supervisor can be referenced in the Diagnostic System

User's Guide for the respective type of VAX-11 processor. The

BC08C-01 test cable must be installed to run the EVCDC diagnostic.

- 2.7 FIELD SERVICE AND CUSTOMER ACCEPTANCE

The procedure used for field service and customer acceptance depends on whether the M8648 module is installed in a PDP-11 system or a VAX-11 system. Therefore, proceed to Section 2.7.1 if the M8648 module is installed in a PDP-11 system, and if it is installed in a VAX-11 system, proceed to Section 2.7.2.

#### NOTE

The diagnostics required for field service and customer acceptance are not shipped with the IEU11-A option. The diagnostics are distributed to DIGITAL Field Service through the Software Distribution Center (SDC).

Figure 2-1 M8648 Module Configuration (UNIBUS)

### 2.7.1 Field Service and Customer Acceptance Procedure (PDP-11 System)

The following needs to be performed in order to demonstrate to the field engineer and to the customer that the IEU11-A option performs correctly. The BC08S-01 cable must be installed (Figure 2-2).

- Run the CZIEA?? IEU/IEQ static diagnostic as outlined in Section 2.6.1 (four error-free passes).

- Configure a DEC-X/ll System Exerciser to include all the devices in the PDP-ll system.

- Run the exerciser until a complete "relocation cycle" has been performed through the memory.

Figure 2-2 BC08S-01 Test Cable Installed (M8648 Module)

2.7.2 Field Service and Customer Acceptance Procedure (VAX-11 System)

After the EVCDC diagnostic (Section 2.6.2) is run, the EVCDB diagnostic needs to be run to demonstrate to both the field service engineer and the customer that the IEU11-A performs properly. The EVCDB diagnostic is a functional level (Level 2R) diagnostic that exercises an IEU11-A option. The program runs with the Diagnostic Supervisor under VMS Version 3.0 or later. The BC08S-01 test cable must be installed to run this diagnostic.

The VMS software driver (IXDRIVER) must be loaded and connected, using the SYSGEN utility. The VMS software driver (IXDRIVER) must be installed before the EVCDB diagnostic can be executed. Refer to the HELP file under the Diagnostic Supervisor (DS>HELP EVCDB).

- 2.8 IEC/IEEE BUS INTERCONNECTION

The IEU11-A can be a controller for either one or two IEC/IEEE bus systems. Therefore, there are four possible configurations:

- 1. IEU11-A acts as a controller for one IEC bus system.

- 2. IEU11-A acts as a controller for two IEC bus systems.

- 3. IEU11-A acts as a controller for one IEEE bus system.

- 4. IEU11-A acts as a controller for two IEEE bus systems.

#### 2.8.1 IEEE/IEC Bus Interconnect Procedure

#### Step Procedure

- Remove the BC08S-01 test cable from the M8648 module.

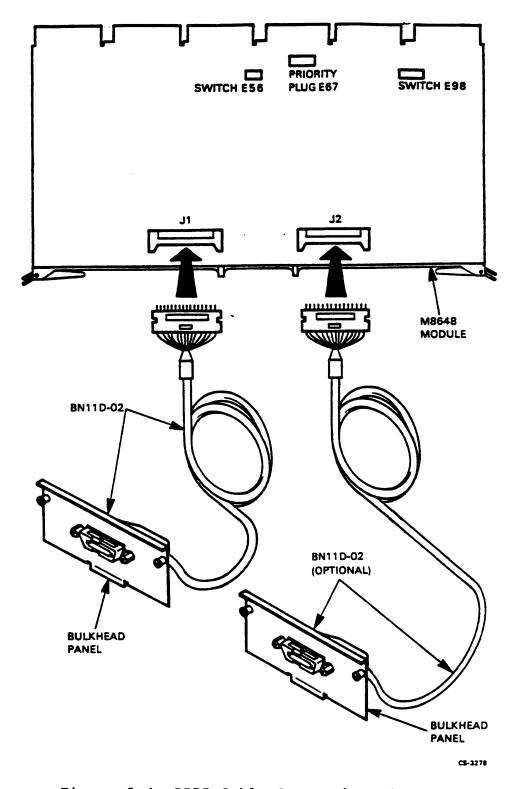

- Identify the 2-meter shielded cable with a Berg connector on one end and an Amphenol<sup>™</sup> or a Cannon connector on the other end. The Amphenol or Cannon connector is connected to the I/O bulkhead panel. An IEC cable has part number BN11C-Ø2, while an IEEE cable has part number BN11D-Ø2.

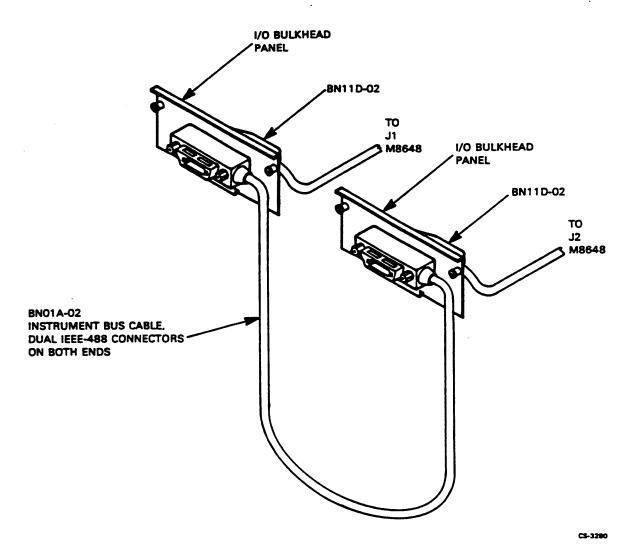

- Connect the Berg connector of the identified cable to the J1 connector on the M8648 module. Refer to Figure 2-3 for an IEC cable connection, or Figure 2-4 for an IEEE cable connection.

- Determine if one of the following optional components are present: a 2-meter IEC-625 Bus cable (17-00384-02), or an IEEE-488 Bus cable with an I/O bulkhead panel (BN11D-02). If this second cable is present, connect the Berg connector to J2 on the M8648 module. On an IECBus installation, connect the Amphenol or Cannon connector of the cable (17-00384-02) to the I/O bulkhead panel. Refer to Figure 2-3 for an IEC bus cable connection, or Figure 2-4 for an IEEE bus connection.

- Attach the I/O bulkhead panel(s) to an available bulkhead frame(s) with the four screws. If no bulkhead frame is available, the I/O panels can be attached to the cabinet frame wherever it is most convenient.

Berg<sup>™</sup> is a trademark of Berg Electronics.

Amphenol<sup>™</sup> is a trademark of Amphenol North America: Division of Bunker-Ramo.

$Cannon^{TM}$  is a trademark of ITT Cannon Electric.

Figure 2-3 IEC Cable Connections (UNIBUS)

Figure 2-4 IEEE Cable Connections (UNIBUS)

2.8.2 Testing the IEC/IEEE Bus Cables

To test the IEC/IEEE bus cables that interconnect the M8648 module

to the I/O bulkhead panel(s), the following procedure is performed.

## Step Procedure

- I Both channels on the IEUII-A option must be used; that is, the following must be installed:

- IEC installation -- an IEC bus cable with I/O bulk-head panel (BN11C-02) and an optional IEC bus cable (17-00384-02). Refer to Figure 2-3.

- IEEE installation -- two IEEE bus cables with two I/O bulkhead panels (BN11D-02). Refer to Figure 2-4.

- 2 Interconnect both channels by performing the following:

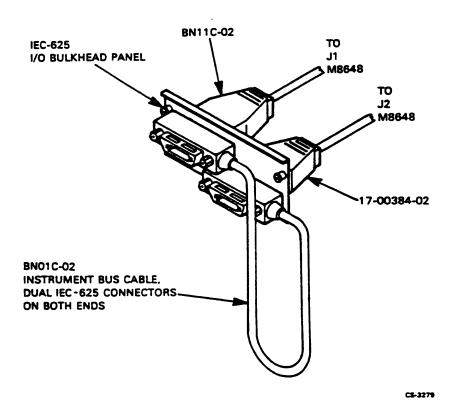

- IEC installation -- connect the two channels by installing an instrument bus cable, dual IEC-625 connector on both ends (BNØ1C-Ø2) to the I/O bulkhead panel (refer to Figure 2-5).

Figure 2-5 IEC Cable Test Configuration (UNIBUS)

## Step Procedure

- IEEE installation -- connect the two channels by installing an instrument bus cable, dual IEEE-488 connector on both ends (BNØ1A-Ø2) to the two I/O bulkhead panels (refer to Figure 2-6).

- Perform the module verification procedure in Section 2.6, ignoring the references in Section 2.6 to the BC08S-01 test cable.

Figure 2-6 IEEE Cable Test Configuration (UNIBUS)

2.9 IEQ11-A OPTION UNPACKING AND INSTALLATION