#

21-24674-01

Rev. 1.13

Contact: Paul Rubinfeld (SHORTY::RUBINFELD)

#### COMPANY CONFIDENTIAL

Copyright (C) 1984, 1985 by Digital Equipment Corporation

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may occur in this document.

This specification does not describe any program or product which is currently available from Digital Equipment Corporation. Nor does Digital Equipment Corporation commit to implement this specification in any product or program. Digital Equipment Corporation makes no commitment that this document accurately describes any product it might ever make.

| 1.0     | INTRODUCTION                                  | . 7 |

|---------|-----------------------------------------------|-----|

| 1.1     | Scope                                         | . 7 |

| 1.2     | Applicable Documents                          | . 7 |

| 1.3     | CVAX CPU Chip Features                        | . 7 |

| 1.4     | Summary Of Differences                        | . 8 |

| 2.0     | ARCHITECTURE SUMMARY                          | . 9 |

| 2.1     | Visible State                                 | . 9 |

| 2.1.1   | Virtual Address Space                         | . 9 |

| 2.1.2   | Physical Address Space                        | 10  |

| 2.1.3   | Registers                                     | 11  |

| 2.2     | Data Types                                    | 12  |

| 2.3     | Instruction Formats And Addressing Modes      | 14  |

| 2.3.1   | Opcode Formats                                | 14  |

| 2.3.2   | General Register Operand Specifiers           | 14  |

| 2.3.3   | Branch Operand Specifiers                     | 15  |

| 2.4     | Instruction Set                               | 16  |

| 2.4.1   | Integer Arithmetic And Logical Instructions . | 17  |

| 2.4.2   | Address Instructions                          | 19  |

| 2.4.3   | Variable Length Bit Field Instructions        | 19  |

| 2.4.4   | Control Instructions                          | 20  |

| 2.4.5   | Procedure Call Instructions                   | 21  |

| 2.4.6   | Miscellaneous Instructions                    | 21  |

| 2.4.7   | Queue Instructions                            | 22  |

| 2.4.8   | Character String Instructions                 | 22  |

| 2.4.9   | Operating System Support Instructions         | 22  |

| 2.4.10  | Floating Point Instructions                   | 23  |

| 2.4.11  | Microcode-Assisted Emulated Instructions      | 25  |

| 2.5     | Memory Management                             | 27  |

| 2.5.1   | Memory Management Control Registers           | 27  |

| 2.5.2   | System Space Address Translation              | 28  |

| 2.5.3   | Process Space Address Translation             | 30  |

| 2.5.3.1 | PO Region Address Translation                 | 30  |

| 2.5.3.2 | P1 Region Address Translation                 | 32  |

| 2.5.4   | Page Table Entry                              | 34  |

| 2.5.5   | Translation Buffer                            | 35  |

| 2.6     | Exceptions And Interrupts                     | 35  |

| 2.6.1   | Interrupts                                    | 35  |

| 2.6.2   | Exceptions                                    | 37  |

| 2.6.3   | System Control Block (SCB)                    | 38  |

| 2.6.4   | Machine Check Parameters                      | 41  |

| 2.6.5   | Restart Process                               | 42  |

| 2.7     | Process Structure                             | 43  |

| 2.7.1   | Process Control Block (PCB)                   | 43  |

| 2.8     | Processor Registers                           | 45  |

| 2.8.1   | Interval Clock Control And Status Register    |     |

|         | (ICCS)                                        | 46  |

| 2.8.2   | Cache Disable Register (CADR)                 | 47  |

| 2.8.3   | Memory System Error Register (MSER)           | 48  |

| 2.8.4   | Console Saved Registers (SAVPC, SAVPSL)       | 49  |

| 2.8.5   | System Identification Register (SID)          | 49  |

| 3.0     | INTERNAL CACHE                                | 50  |

| 3.1     | Cache Allocation                              | 51  |

| 3.2     | Read Cycle Classification                     | 52  |

| 3.3     | Cache Parity                                  | 53  |

| 3.4     | DAL H Parity                            | 5. |

|---------|-----------------------------------------|----|

| 4.0     | INTERFACE                               | 5! |

| 4.1     | Pinouts                                 | 5! |

| 4.1.1   | Summary                                 | 5  |

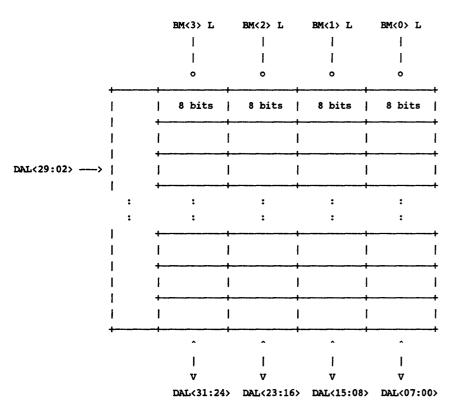

| 4.1.2   | Data And Address Bus                    | 56 |

| 4.1.2.1 | Data And Address Lines (DAL<31:00>)     | 56 |

| 4.1.2.2 | Cycle Status/Data Parity (CS/DP<3:0> L) | 56 |

| 4.1.2.3 | Data Parity Enable (DPE L)              | 58 |

| 4.1.3   | Bus Control                             | 58 |

| 4.1.3.1 | Address Strobe (AS L)                   |    |

| 4.1.3.2 | Data Strobe (DS L)                      |    |

| 4.1.3.3 | Byte Masks (BM<3:0> L)                  |    |

| 4.1.3.4 | Write (WR L)                            |    |

| 4.1.3.5 | Data Buffer Enable (DBE L)              |    |

| 4.1.3.6 | Ready (RDY L)                           |    |

| 4.1.3.7 | Error (ERR L)                           |    |

| 4.1.4   | System Control                          |    |

| 4.1.4.1 | Reset (RESET L)                         |    |

| 4.1.4.2 | Halt (HALT L)                           |    |

| 4.1.5   | Interrupt Control                       |    |

| 4.1.5.1 | Interrupt Request (IRQ<3:0> L)          |    |

| 4.1.5.2 | Power Fail (PWRFL L)                    |    |

| 4.1.5.3 | Corrected Read Data (CRD L)             |    |

| 4.1.5.4 | Interval Timer (INTTIM L)               |    |

| 4.1.5.5 | Memory Error (MEMERR L)                 |    |

| 4.1.6   |                                         |    |

| 4.1.6.1 | DMA Control                             |    |

| 4.1.6.2 | DMA Request (DMR L)                     |    |

| 4.1.7   | DMA Grant (DMG L)                       |    |

| 4.1.7.1 | Cache Control (CCTL L)                  |    |

|         | Conditional Cache Invalidate            |    |

| 4.1.7.2 | Prevent Data Caching                    |    |

| 4.1.8   | Coprocessor Control                     |    |

| 4.1.8.1 | Coprocessor Data Lines (CPDAT<5:0> H)   |    |

| 4.1.8.2 | Coprocessor Status Lines (CPSTA<1:0> H) |    |

| 4.1.9   | Miscellaneous                           |    |

| 4.1.9.1 | Power                                   |    |

| 4.1.9.2 | Ground                                  |    |

| 4.1.9.3 |                                         |    |

| 4.1.9.4 | Test (TESTO H, TEST1 H)                 | 6  |

| 4.1.9.5 | Bus Request (BR L)                      | 6  |

| 4.1.9.6 | Console Mode (CM L)                     | 6  |

| 4.2     | Bus Cycle Descriptions                  | 6  |

| 4.2.1   | Idle Cycle                              | 6  |

| 4.2.2   | Single Transfer CPU Read Cycle          | 6  |

| 4.2.3   | Multiple Transfer CPU Read Cycle        | 6  |

| 4.2.4   | CPU Write Cycle                         | 7: |

| 4.2.5   | External Processor Register Read Cycle  | 7  |

| 4.2.6   | External Processor Register Write Cycle | 7  |

| 4.2.7   | Interrupt Acknowledge Cycle             | 7  |

| 4.2.8   | DMA Grant Cycle                         | 7  |

| 4.2.9   | Cache Invalidate Cycles                 | 7  |

| 4.3     | Memory Access Protocol                  | 7  |

| 4.3.1   | I-stream Prefetching                    | 7  |

| Δ.Δ     | Converger Protocols                     | 7  |

# CVAX CPU CHIP ENGINEERING SPECIFICATION (Company Confidential) Page 4 TABLE OF CONTENTS

| 4.4.1   | Passing Opcode Information To The Coprocessor  | 77  |

|---------|------------------------------------------------|-----|

| 4.4.2   | Passing Operands To The Coprocessor            | 78  |

| 4.4.3   | Passing Results Back From The Coprocessor      | 78  |

| 4.4.4   | Coprocessor Reset                              | 80  |

| 4.5     | Test Logic                                     | 80  |

| 4.5.1   | Observablitiy Logic                            | 80  |

| 4.5.2   | Control Logic                                  | 81  |

| 4.5.3   | Normal State                                   | 81  |

| 4.5.4   | Test State                                     | 81  |

| 4.5.4.1 | Internal MAB                                   | 81  |

| 4.5.4.2 | External MAB                                   | 82  |

| 4.5.4.3 | Force Broadcast                                | 82  |

| 4.5.5   | Test Registers                                 | 82  |

| 4.5.6   | Main Reducer                                   | 82  |

| 4.5.7   | Test Control Pins Allocation                   | 83  |

| 5.0     | DC CHARACTERISTICS                             | 84  |

| 5.1     | Absolute Maximum Ratings                       | 84  |

| 5.2     | Electrical Characteristics                     | 84  |

| 5.3     | Signal Summary                                 | 85  |

| 6.0     | AC CHARACTERISTICS                             | 88  |

| 6.1     | Input Requirements                             | 88  |

| 6.2     | Output Responses                               | 89  |

| 7.0     | TIMING DIAGRAMS                                | 91  |

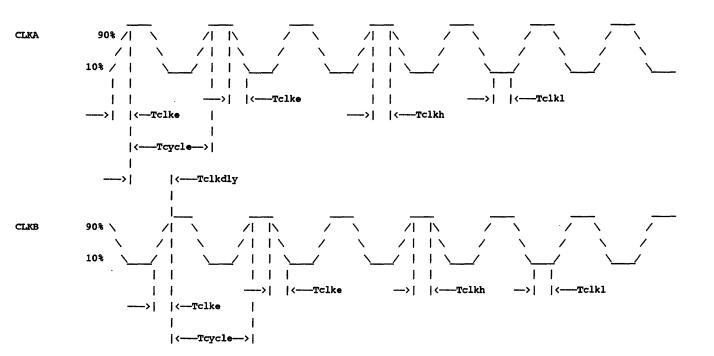

| 7.1     | Clock Timing Requirements                      | 91  |

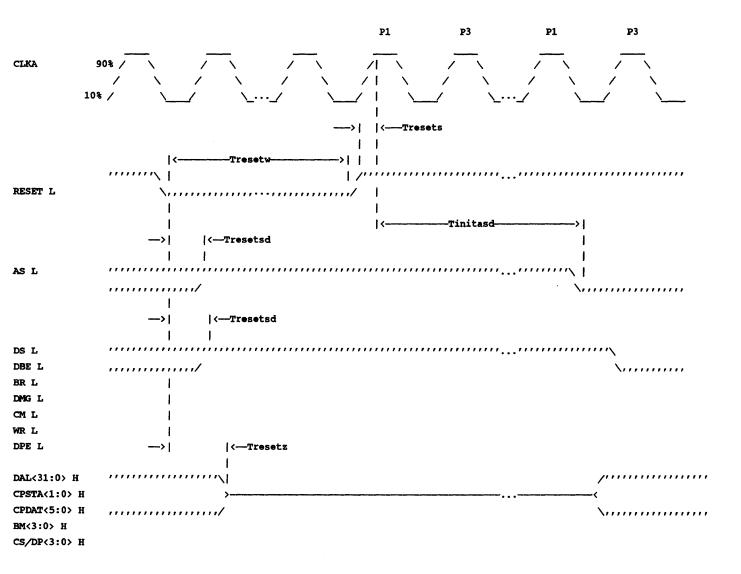

| 7.2     | Initialization                                 | 92  |

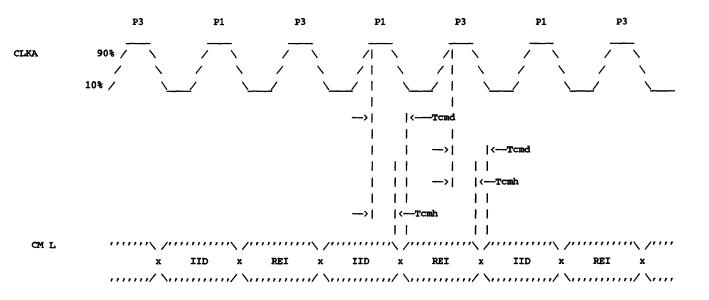

| 7.3     | CM L Timing                                    | 93  |

| 7.4     | External Interrupt Timing                      | 94  |

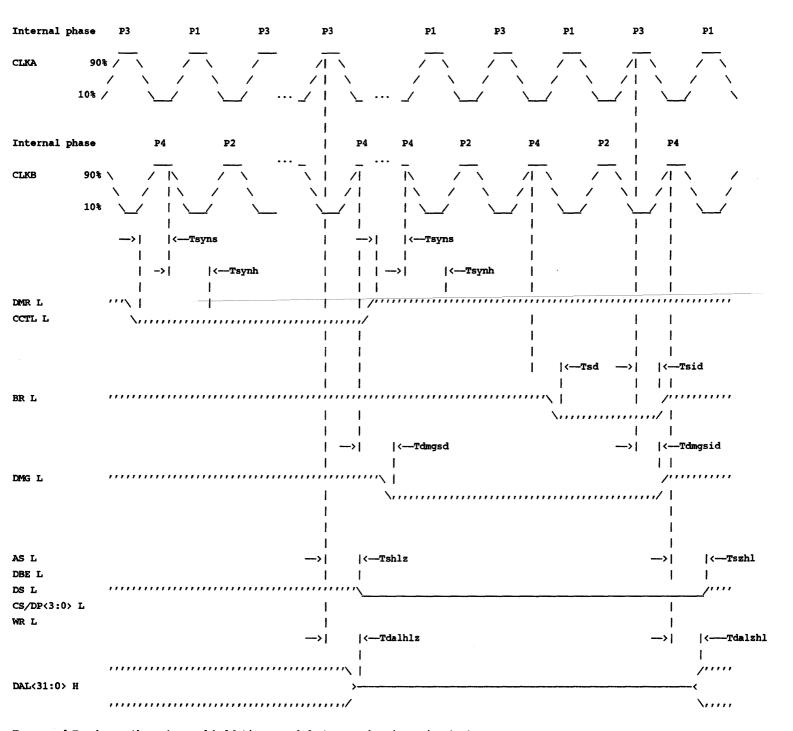

| 7.5     | External DMA Timing                            |     |

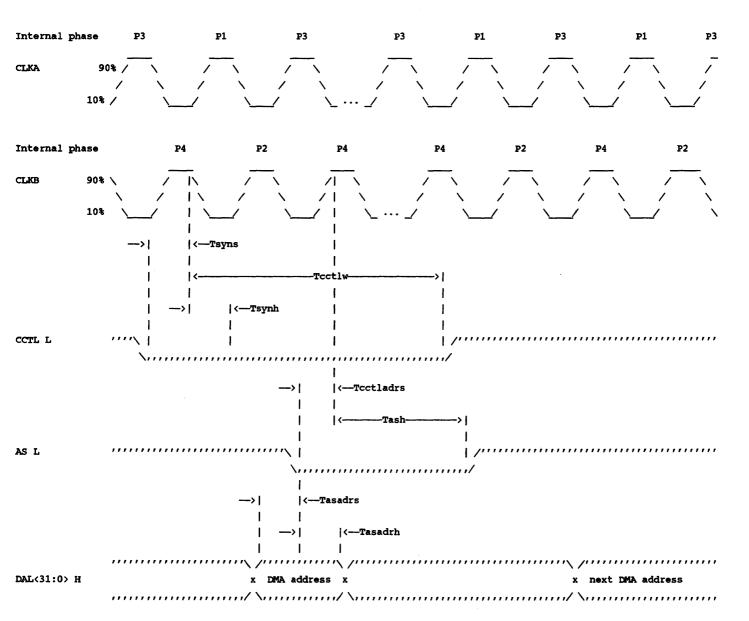

| 7.6     | Quadword Cache Invalidate Cycle                |     |

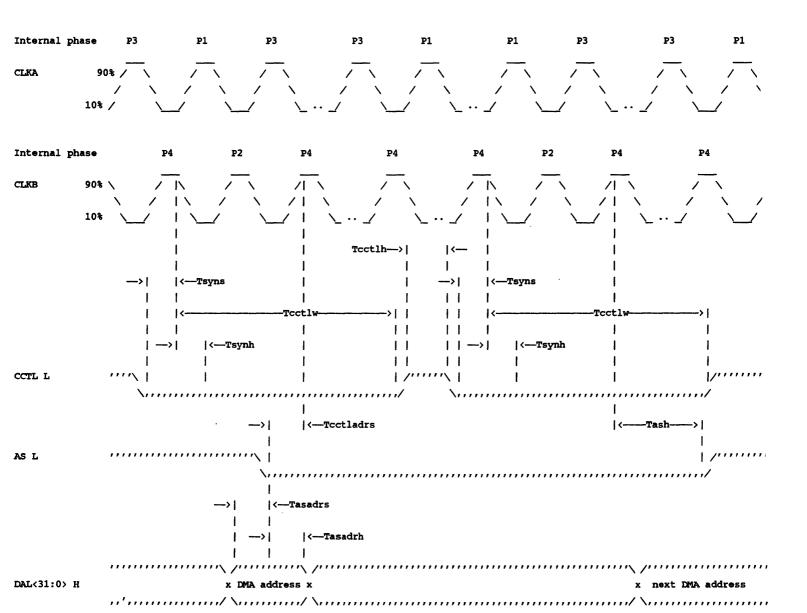

| 7.7     | Octaword Cache Invalidate Cycle                | 97  |

| 7.8     | Single Transfer CPU Read Cycle, Interrupt      |     |

|         | Acknowledge Cycle                              |     |

| 7.9     | Multiple Transfer CPU Read Cycle               |     |

| 7.10    | CPU Write Cycle                                | 102 |

| 7.11    | Coprocessor Timing                             | 104 |

| 7.11.1  | Single Precision CVAX To Coprocessor Transfer  | 104 |

| 7.11.2  | Double Precision CVAX To Coprocessor Transfer  | 105 |

| 7.11.3  | Single Precision Coprocessor To CVAX Transfers |     |

| 7.11.4  | Double Precision Coprocessor To CVAX Transfers |     |

| 8.0     | CHIP INTERCONNECT DIAGRAM                      |     |

| 9.0     | DIFFERENCES BETWEEN CVAX AND UVAX              |     |

| 9.1     | SOFTWARE DIFFERENCES                           |     |

|         |                                                |     |

# REVISION HISTORY

| REV  | DATE       | REASON                                                                                             |

|------|------------|----------------------------------------------------------------------------------------------------|

| 1.12 | 12-Apr-85  | Section 2.8.2 SEN and CEN definitions in CADR are swapped.                                         |

|      | 10 101 00  | Section 2.8.4 Added SID description.                                                               |

|      |            | Section 4.1.8.2 Coprocessor return ACB met by setting PSL V.                                       |

|      |            | Section 4.4.3 Coprocessor return ACB met by setting PSL V.                                         |

| 1.11 | 3-Apr-85   | Section 4.1.8.2 Added POLY even/odd coefficient flag.                                              |

|      | -          | Section 4.2.7 Parity can be checked on the interrupt vector.                                       |

|      |            | Section 4.4.2 Accelerated integer instruction defined.                                             |

|      |            | Section 4.5.* Added test logic description.                                                        |

|      |            | Section 4.9.4 Defined TESTOL and TESTI L functionality.                                            |

|      |            | Section 4.4.3 Added POLY even/odd coefficient flag.                                                |

|      |            | Section 5.2 Deleted Iils parameter.                                                                |

|      |            | Section 5.3 Added signal summary.                                                                  |

| 1.10 | 26-Mar-85  | Section 2.63, 4.1.3.7, 4.2.7, 9.1 Update to                                                        |

|      |            | incorporate VAXB ECO #85Q2-67, SCB vector 0 is                                                     |

|      |            | assigned to IRQ passive release.                                                                   |

| 1.09 | 22-Mar-85  | Section 6.2 added Tresetd, Treseth and Tbmh.                                                       |

|      |            | Section 7.2, 7.8, 7.9, 7.10 updated.                                                               |

| 1.08 | 22-Feb-85  | Section 4.1.8.2, 4.2.2, 4.2.3 updated.                                                             |

| 1.07 | 19-Feb-85  | Section 4.2.3 DAL parity error response corrected.                                                 |

|      |            | Section 6.1 Tds & Tdps min and max corrected.                                                      |

|      |            | Section 6.2 Tdsid, Tdmgsd & Tdmgsid added.                                                         |

|      |            | Section 7.5 Tdmgsd and Tdmgsid added.                                                              |

|      |            | Section 7.8, 7.9, 7.10 Tdsid added.                                                                |

| 1.06 | 7-Feb-85   | Section 2.5.5 TB description add.                                                                  |

|      |            | Section 2.6.4 machine check codes 2 through 5 clarified.                                           |

|      |            | Section 2.8.2 diagnostic mode should only be selected when one set                                 |

|      |            | is enabled.                                                                                        |

|      |            | Section 4.1.2.2 CS/DP<3> is undefined during non-cacheable references.                             |

|      |            | Section 4.1.7.1, 4.2.9 octaword invalidates added.                                                 |

|      |            | Section 4.1.9.6 CM L further defined.                                                              |

|      |            | Section 4.2.2 CCTL L operation added to single transfer description.                               |

|      |            | Section 4.2.3 CCTL L operation added to multiple transfer description.  Response table add.        |

|      |            | Section 4.4.4 Coprocessor reset operation defined.                                                 |

|      |            | Section 7.3 CM L AC waveforms added.                                                               |

|      |            | Section 7.4, 7.5 DMA and interrupt timing diagrams separated.                                      |

|      |            | Section 7.6, 7.7 quadword and octaword invalidate cycle timing shown.                              |

|      |            | Section 8.0 interconnect diagram fixed up.                                                         |

|      |            | Section 9.2 item 14 added to highlight IPR number DAL assignment difference between uVAX and CVAX. |

| 1.05 | 24-Jan-85  | Section 1.3 item 7 minimum IO cycle is 200ns.                                                      |

| 1.05 | 21 Out. 05 | Section 2.8.3 MSER change: <10> indicates hit/miss; <9> memory                                     |

|      |            | parity error caused machine check; <8> cache parity error caused machine check                     |

|      |            | Section 4.2.2.2 CS encoding has been changed. LLL and LHL have switch                              |

|      |            | meanings. Lith when WR L is asserted is reserved for DMA device use.                               |

|      |            | Section 4.1.2.3 External resistor now needed for DPE L.                                            |

|      |            | Section 4.1.3.4, 4.1.3.5 Control of DS L and DBE L is relinquished                                 |

|      |            | when DMG L is asserted.                                                                            |

|      |            | with a subseque                                                                                    |

| REV | TST | ON | HIST | <b>FORV</b> |

|-----|-----|----|------|-------------|

1.00

11-Nov-84

| Section | 4.1.3.7, | 4.1.6.2, 4.2.4, 8 | and 4.2.8 DMA is | arbitrated after |

|---------|----------|-------------------|------------------|------------------|

| every   | IO cycle | and retry respons | e, irrespective  | of read lock.    |

|         |          |                   |                  |                  |

Section 4.1.4.2, 4.1.5 Defined synchronizer operation for all internally synchronized signals.

Section 4.1.5.5 Memory Error interrupt added.

Section 4.1.7.2 Note typo corrected to describe CCTL L.

Section 4.1.8.2 Added stop coprocessor operation and last data transfer indication to CPDAT encoding.

Section 4.3.9 the nominal length of an DMA invalidate cycle is 300ns.

Section 4.4 Added I-stream Prefetching description.

Section 5.1 Absolute maximum ratings changed to tbs.

Section 5.2 Icc changed to tbs.

Section 6.1 Tclkr and Tclkf deleted. Tclke added. Tclkh and Tclkl changed to a min of 5ns, max of 25ns. Tdps added.

Section 6.2 Tparityh changed to Ons. Tdsd added.

Section 7.1 Tclkr and Tclkf have been replaced by Tclke.

Section 7.5, 7.6, 7.6 DS L now deasserts off of P1. Tsd on DS L has been changed to Tdsd. CS L, DP L, and DPE L signals separated.

Section 9.2 item 8 interrupt grant levels for CVAX and uVAX differ.

Items 13 and 14 added.

| 1.04 | 2-Jan-85  | Section 4.1.2.3, 4.1.2.3, and 4.2.7 modified to             |

|------|-----------|-------------------------------------------------------------|

|      |           | indicate that DAL parity checking is not done during an     |

|      |           | external processor register read, or interrupt              |

|      |           | acknowledge cycle. Section 4.2.7 modified to indicate       |

|      |           | that DAL<31:7,1:0> are driven with zeros when the interrupt |

|      |           | level is sent out.                                          |

| 1.03 | 17-Dec-84 | Section 9 filled in.                                        |

| 1.02 | 14-Dec-84 | General clean up. DMA invalidate cycles and timing          |

| 1.03 | 17-Dec-84 | Section 9 filled in.                               |

|------|-----------|----------------------------------------------------|

| 1.02 | 14-Dec-84 | General clean up. DMA invalidate cycles and timing |

|      |           | added. Many inconsistencies and typos corrected.   |

|      |           | Section 9 added.                                   |

| 1.01 | 11-Dec-84 | General clean up. Added that DMG L will never be   |

|      |           | asserted if read lock is pending.                  |

Preliminary version.

#### 1.0 INTRODUCTION

#### 1.1 Scope

This document describes the CVAX CPU chip, a CMOS/VISI chip that implements a MicroVAX central processor. This specification describes the external interface and behavior of the chip. It does not describe the internal organization or operation of the chip. For further information, the applicable documents should be consulted.

#### 1.2 Applicable Documents

VAX Architecture Standard (DEC Standard 032) CVAX CPU Chip Design Specification

#### 1.3 CVAX CPU Chip Features

The CVAX CPU chip is a 32-bit, virtual memory microprocessor. Implemented in CMOS I (double metal CMOS), the CVAX CPU chip is a high performance, low cost CPU for single board computers, single user workstations, low end systems, and other applications that do not need the flexibility of, or cannot afford the complexity of, the full VAX architecture. Its key features are:

- Subset VAX data types. The CVAX CPU chip supports the following subset of the VAX data types: byte, word, longword, quadword, character string, and variable length bit field. Support for f\_floating, d\_floating, and g\_floating data types is provided by an external Floating Point Coprocessor. Support for the remaining VAX data types can be provided by macrocode emulation.

- 2. Subset VAX instruction set. The CVAX CPU chip implements the following subset of the VAX instruction set: integer and logical, address, variable length bit field, control, procedure call, miscellaneous, queue, MOVC3/MOVC5, and operating system support. The f\_floating point, d\_floating point, and g\_floating point instructions are implemented in an external floating point unit. The remaining VAX instructions can be implemented via macrocode emulation (the CVAX CPU chip provides microcode assists for the emulation of the character string, decimal string, EDITPC, and CRC instructions).

- 3. Full VAX memory management. The CVAX CPU chip includes a demand paged memory management unit which is fully compatible with VAX memory management. System space addresses are virtually mapped through single level page tables, process space addresses through double level page tables.

- 4. On chip cache. The CVAX CPU chip includes 1k bytes of on chip cache to optimize the performance of the memory subsystem. The cache can be configured to store I-stream only references, or both I-stream and D-stream references.

- 5. External interface based on industry Standards. The CVAX CPU chip's external interface is a 32-bit extension of the defacto industry standard microprocessor interface. The CVAX chip functionally replaces the MicroVAX chip in existing designs although the exact timing, pin assignments, and external protocol have slightly changed. Chapter 9 highlights the interface differences between MicroVAX and CVAX.

- 6. Large virtual and physical address space. The CVAX CPU chip supports four gigabytes (2\*\*32) of virtual memory, and one gigabyte (2\*\*30) of physical memory.

- High performance. At its maximum frequency, the CVAX CPU chip achieves a 100 nsec microcycle and a 200 nsec I/O cycle.

- Single package. The CVAX CPU chip is packaged in a standard 84-pin surface mounted chip carrier.

#### 1.4 Summary Of Differences

The principal differences between the CVAX CPU chip and the full VAX architecture are these:

- The CVAX CPU chip omits these data types: decimal string, octaword, h\_floating. [These data types can be supported via macrocode emulation.]

- 2. The CVAX CPU chip omits these instruction classes: character string (except for MOVC3/MOVC5), decimal string, EDITPC, CRC, compatability mode, octaword, h\_floating. [The chip provides microcode assists for the macrocode emulation of the character string, decimal string, CRC, and EDITPC instructions.]

- 3. The CVAX CPU chip omits some of the required full VAX internal processor registers. Specifically, NICR, ICR, TODR, RXCS, RXDB, TXCS, TXDB and PMR are not built in CVAX. MFPR or MTPR references to these registers generates an external processor register read or write cycle, respectively. Therefore, these registers can externally supported.

- 4. The CVAX CPU chip does not have a built-in console function.

# 2.0 ARCHITECTURE SUMMARY

This section provides summary information about the architecture of the CVAX CPU chip. It is not intended as a complete reference but rather to give an overview of the user-visible features. For a complete description of the architecture, consult the "VAX Architecture Standard".

#### 2.1 Visible State

The visible state of the processor consists of memory, both virtual and physical, the general registers, and the processor status longword (PSL).

#### 2.1.1 Virtual Address Space -

The virtual address space is four gigabytes (2\*\*32), as follows:

| 00000000          | ! !      | length of PO Region in pages (POLR)       |

|-------------------|----------|-------------------------------------------|

|                   | P0       |                                           |

|                   | Region   |                                           |

| 3 <b>FFFFFF</b>   | V        | PO Region growth direction                |

| 40000000          | 1 1      | Pl Region growth direction                |

|                   | 1 1      |                                           |

|                   | P1       |                                           |

|                   | Region   |                                           |

| 7 <b>FFFFF</b> FF | 1        | length of P1 Region in pages (2**21-P1LR) |

| /FFFFFF           | 1        | rength of FI Region in pages (2""21-Film) |

|                   | +        |                                           |

| 80000000          | 1        | length of System Region in pages (SLR)    |

|                   | 1        |                                           |

|                   | System   |                                           |

|                   | Region   |                                           |

|                   |          |                                           |

| BFFFFFFF          | y 1      | System Region growth direction            |

|                   | +        |                                           |

| C0000000          | 1        |                                           |

|                   | i i      |                                           |

|                   | 1 7 1    |                                           |

|                   | Reserved |                                           |

|                   | Region   |                                           |

| PFFFFFFF          | 1        |                                           |

|                   | +        |                                           |

|                   | •        |                                           |

# 2.1.2 Physical Address Space -

The physical address space is one gigabyte (2\*\*30), as follows:

|                  | <del>+</del> | +   |

|------------------|--------------|-----|

| 00000000         | 1            | 1   |

|                  | 1            | 1   |

|                  | Memory       | i   |

|                  | Space        | 1   |

|                  | 1            | 1   |

| 1FFFFFFF         | 1            | ı   |

|                  | +            | +   |

| 20000000         | 1            | i   |

|                  | 1            | - 1 |

|                  | I/O          | 1   |

|                  | Space        | - 1 |

|                  | 1            | 1   |

| 3 <b>FFFFFFF</b> | 1            | ŀ   |

|                  | +            | +   |

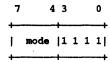

# 2.1.3 Registers -

16 general registers

[R0 - R11, general purpose

R12 = AP, argument pointer

R13 = FP, frame pointer

R14 = SP, stack pointer

R15 = PC, program counter]

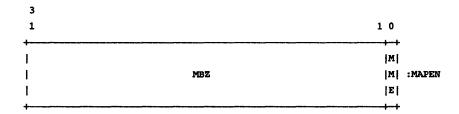

#### Processor Status Longword

[CM = compatability mode

TP = trace pending

FPD = first part done

IS = interrupt stack

CUR = current mode

PRV = previous mode

IPL = interrupt priority level

DV = decimal overflow trap enable

FU = floating underflow fault enable

IV = integer overflow trap enable

r = trace trap enable

N = negative condition code

Z = zero condition code

V = overflow condition code

C = carry condition code]

| 3 |   |     |

|---|---|-----|

| 1 | 0 |     |

| + | + |     |

| 1 | I | :Rn |

| • |   |     |

| 3 3 2 2 | 2 2 2 2 2 2 2 2 2 | 1 1       |                     |

|---------|-------------------|-----------|---------------------|

| 1 0 9 8 | 7 6 5 4 3 2 1 0   | 6 5       | 8 7 6 5 4 3 2 1 0   |

| +-+-+   | <del></del>       |           | <del></del>         |

| 111     | F     M           | j         |                     |

| C T     | P I CUR PRV B     | 1         | D F I          :PSL |

| M P MBZ | D S MOD MOD Z     | IPL   MBZ | V U V T N Z V C     |

| +-+     | <del></del>       |           | <del></del>         |

# 2.2 Data Types

The CVAX architecture supports nine data types: byte, word, longword, quadword, character string, variable length bit field, and, through an optional external processor, f\_floating, d\_floating, and g\_floating. These are summarized below:

| Type<br>  | Length      | Use<br>                       | Graphical Representation |                |

|-----------|-------------|-------------------------------|--------------------------|----------------|

| Byte      | 8 bits      | signed or                     | 7 0<br>+                 |                |

| Бусе      | o bits      | unsigned integer              | IA                       |                |

|           |             |                               | 1<br>5 0                 |                |

| Word      | 16 bits     | signed or<br>unsigned integer | A:                       |                |

|           |             |                               | 3 1                      | 0              |

| Longword  | 32 bits     | signed or<br>unsigned integer |                          | A:  <br>       |

|           |             |                               | 3<br>1                   | 0              |

| Quadword  | 64 bits     | signed integer                | <u> </u>                 | :A<br>+        |

|           |             |                               | 6                        | :A+4<br>+<br>3 |

|           |             |                               | 3                        | 2              |

| Character | 0-65k bytes | byte string                   | 7 0<br>+                 |                |

| String    |             |                               | :A+1                     |                |

| ·         |             |                               | •                        |                |

|           |             |                               | -<br>+                   |                |

|           |             |                               | 7 0                      |                |

|                                        |                | P+S P+S-1              | P P-1 0    |

|----------------------------------------|----------------|------------------------|------------|

| Variable Length 0-32 bits<br>Bit Field | bit string     | 1 1/1//////            | //////  :A |

| pre rieid                              |                | S-1                    | 0          |

|                                        |                | 1 1<br>5 4 7 6 0       |            |

| F_floating 32 bits                     | floating point | S  exponent   fraction | :А         |

|                                        |                |                        | :A+2       |

|                                        |                | 3 1<br>1 6             |            |

|                                        |                | 1 1<br>5 4 7 6 0       |            |

| D_floating 64 bits                     | floating point |                        | :A ·       |

|                                        |                |                        | :A+2       |

|                                        |                | fraction               | :A+4       |

|                                        |                |                        | :A+6       |

|                                        |                | 6 4 3 8                |            |

|                                        |                | 1 1<br>5 4 4 3 0       |            |

| G_floating 64 bits                     | floating point |                        | :А         |

|                                        |                | fraction               | :A+2       |

|                                        |                | fraction               | :A+4       |

|                                        |                | fraction               | :A+6       |

|                                        |                | 6 4 3 8                |            |

# 2.3 Instruction Formats And Addressing Modes

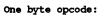

CVAX instructions consist of a one- or two-byte opcode, followed by zero to six operand specifiers.

# 2.3.1 Opcode Formats -

Two byte opcode:

# 2.3.2 General Register Operand Specifiers -

The general register address modes are:

|                       |                                                                                                                                                                                                                 | ACCESS                                                                                                                                                                                                                                                                                                                           |      |      |            |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------------|

| Name                  | Assembler                                                                                                                                                                                                       | rmwav                                                                                                                                                                                                                                                                                                                            | PC   | SP   | Indexable? |

|                       |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                  |      |      |            |

| literal               | S^#literal                                                                                                                                                                                                      | yffff                                                                                                                                                                                                                                                                                                                            | _    | _    | f          |

| index                 | i[Rx]                                                                                                                                                                                                           | ууууу                                                                                                                                                                                                                                                                                                                            | £    | Y    | f          |

| register              | Rn                                                                                                                                                                                                              | ууу f у                                                                                                                                                                                                                                                                                                                          | u    | uq   | f          |

| register deferred     | (Rn)                                                                                                                                                                                                            | ууууу                                                                                                                                                                                                                                                                                                                            | u    | У    | Y          |

| autodecrement         | -(Rn)                                                                                                                                                                                                           | ууууу                                                                                                                                                                                                                                                                                                                            | u    | y    | ux         |

| autoincrement         | (Rn)+                                                                                                                                                                                                           | ууууу                                                                                                                                                                                                                                                                                                                            | p    | y    | ux         |

| autoincrement         | @(Rn)+                                                                                                                                                                                                          | ууууу                                                                                                                                                                                                                                                                                                                            | p    | y    | ux         |

| deferred              |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                  |      |      |            |

| byte displacement     | B^d(Rn)                                                                                                                                                                                                         | ууууу                                                                                                                                                                                                                                                                                                                            | p    | y    | y          |

| byte displacement     | @B^d(Rn)                                                                                                                                                                                                        | ууууу                                                                                                                                                                                                                                                                                                                            | P    | y    | У          |

| deferred              |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                  |      |      |            |

| word displacement     | W^d(Rn)                                                                                                                                                                                                         | ууууу                                                                                                                                                                                                                                                                                                                            | P    | Y    | У          |

| word displacement     | @W^d(Rn)                                                                                                                                                                                                        | ууууу                                                                                                                                                                                                                                                                                                                            | p    | y    | У          |

| deferred              |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                  |      |      |            |

| longword displacement | L^d(Rn)                                                                                                                                                                                                         | ууууу                                                                                                                                                                                                                                                                                                                            | p    | y    | y          |

| longword displacement | @L^d(Rn)                                                                                                                                                                                                        | ууууу                                                                                                                                                                                                                                                                                                                            | p    | y    | Y          |

| deferred              |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                  |      |      |            |

|                       | literal index register register deferred autodecrement autoincrement autoincrement deferred byte displacement deferred word displacement word displacement deferred longword displacement longword displacement | literal s^#literal index i[Rx] register Rn register deferred (Rn) autodecrement -(Rn) autoincrement (Rn)+ autoincrement @(Rn)+ deferred byte displacement B^d(Rn) byte displacement @B^d(Rn) deferred word displacement W^d(Rn) word displacement @W^d(Rn) deferred longword displacement L^d(Rn) longword displacement @L^d(Rn) | Name | Name | Name       |

If the register is the PC, the address modes are:

|      |                   |                    | Access |            |

|------|-------------------|--------------------|--------|------------|

| Mode | Name              | Assembler          | rmwav  | Indexable? |

|      | ***********       |                    |        |            |

| 8    | Immediate         | I^#constant        | уицуу  | u          |

| 9    | absolute          | <b>@#address</b>   | ууууу  | У          |

| A    | byte relative     | B^address          | ууууу  | y          |

| В    | byte relative     | <b>@B^addre</b> ss | ууууу  | У          |

|      | deferred          |                    |        |            |

| С    | word relative     | W^address          | ууууу  | У          |

| D    | word relative     | W^address          | ууууу  | У          |

|      | deferred          |                    |        |            |

| E    | longword relative | L^address          | ууууу  | У          |

| F    | longword relative | L^address          | ууууу  | У          |

|      | deferred          |                    |        |            |

# Addressing Legend

| Access: |

|---------|

|---------|

| r | = | read    | i  | = | any indexable address mode      |

|---|---|---------|----|---|---------------------------------|

| m | = | modify  | đ  | = | displacement                    |

| w | = | write   | Rn | = | general register, $n = 0$ to 15 |

| а | = | address | Rx | = | general register, $x = 0$ to 14 |

| v | = | field   |    |   |                                 |

yes, always valid address mode reserved address mode fault logically impossible program counter addressing unpredictable

unpredictable for quad, d/g\_floating, uq = and field if pos + size > 32

unpredictable if index reg = base reg ux =

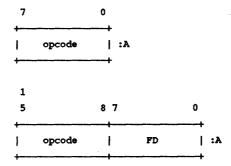

# 2.3.3 Branch Operand Specifiers -

Signed byte displacement:

0 displ 1 5 0 displ

Signed word displacement:

#### 2.4 Instruction Set

The standard notation for operand specifiers is:

<name>.<access type><data type>

#### where:

- Name is a suggestive name for the operand in the context of the instruction. It is the capitalized name of a register or block for implied operands.

- Access type is a letter denoting the operand specifier access type.

- a = address operand

- b = branch displacement

- m = modified operand (both read and written)

- r = read only operand

- v = if not "Rn", same as a, otherwise R[n+1]'R[n]

- w = write only operand

- 3. Data type is a letter denoting the data type of the operand.

- b = byte

- d = d floating

- f = f floating

- g = g floating

- l = longword

- q = quadword

- v = field (used only in implied operands)

- w = word

- \* = multiple longwords (used only in implied operands)

- 4. Implied operands, that is, locations that are accessed by the instruction, but not specified in an operand, are denoted by curly braces {}.

The abbreviations for condition codes are:

- \* = conditionally set/cleared

- = not affected

- 0 = cleared

- 1 = set

The abbreviations for exceptions are:

- rsv = reserved operand fault

- iov = integer overflow trap

- idvz = integer divide by zero trap

- fov = floating overflow fault

- fuv = floating underflow fault

- fdvz = floating divide by zero fault

- dov = decimal overflow trap

ddvz = decimal divide by zero trap

sub = subscript range trap

prv = privileged instruction fault

# 2.4.1 Integer Arithmetic And Logical Instructions -

| Opcode     | Instruction                    | N Z V C     | Exceptions |

|------------|--------------------------------|-------------|------------|

|            |                                | <del></del> |            |

| 58         | ADAWI add.rw, sum.mw           | * * * *     | iov        |

| 80         | ADDB2 add.rb, sum.mb           | * * * *     | iov        |

| C0         | ADDL2 add.rl, sum.ml           | * * * *     | iov        |

| A0         | ADDW2 add.rw, sum.mw           | * * * *     | iov        |

| 81         | ADDB3 add1.rb, add2.rb, sum.wb | * * * *     | iov        |

| C1         | ADDL3 add1.rl, add2.rl, sum.wl | * * * *     | iov        |

| A1         | ADDW3 add1.rw, add2.rw, sum.ww | * * * *     | iov        |

| D8         | ADWC add.rl, sum.ml            | * * * *     | iov        |

| 78         | ASHL cnt.rb, src.rl, dst.wl    | * * * 0     | iov        |

| 79         | ASHQ cnt.rb, src.rq, dst.wq    | * * * 0     | iov        |

| 8A         | BICB2 mask.rb, dst.mb          | * * 0 -     |            |

| CA         | BICL2 mask.rl, dst.ml          | * * 0 -     |            |

| AA         | BICW2 mask.rw, dst.mw          | * * 0 -     |            |

| 8B         | BICB3 mask.rb, src.rb, dst.wb  | * * 0 -     |            |

| CB         | BICL3 mask.rl, src.rl, dst.wl  | * * 0 -     |            |

| AB         | BICW3 mask.rw, src.rw, dst.ww  | * * 0 -     |            |

| 88         | BISB2 mask.rb, dst.mb          | * * 0 -     |            |

| C8         | BISL2 mask.rl, dst.ml          | * * 0 -     |            |

| A8         | BISW2 mask.rw, dst.mw          | * * 0 -     |            |

| 89         | BISB3 mask.rb, src.rb, dst.wb  | * * 0 -     |            |

| C9         | BISL3 mask.rl, src.rl, dst.wl  | * * 0       |            |

| A9         | BISW3 mask.rw. src.rw, dst.ww  | * * 0 -     |            |

| 93         | BITB mask.rb, src.rb           | * * 0 -     |            |

| D3         | BITL mask.rl, src.rl           | * * 0 -     |            |

| В3         | BITW mask.rw, src.rw           | * * 0 -     |            |

| 94         | CLRB dst.wb                    | 0 1 0 -     |            |

| D4         | CLRL{=F} dst.wl                | 0 1 0 -     |            |

| <b>7</b> C | CLRQ{=D=G} dst.wq              | 0 1 0 -     |            |

| B4         | CLRW dst.ww                    | 010-        |            |

| 91         | CMPB src1.rb, src2.rb          | * * 0 *     |            |

| D1         | CMPL src1.rl, src2.rl          | * * 0 *     |            |

|            |                                | -           |            |

| CVAX | CPU | CHIP | ENGINEERING | SPECIFICATION | (Company | Confidential) | Page 1 | .8 |

|------|-----|------|-------------|---------------|----------|---------------|--------|----|

|      |     |      | SUMMARY     |               | •        | ,             |        |    |

| P | a | a | • | 1 |

|---|---|---|---|---|

|   |   |   |   |   |

| B1         | CMPW src1.rw, src2.rw                                           | * * 0 * |           |

|------------|-----------------------------------------------------------------|---------|-----------|

| 98         | CVTBL src.rb, dst.wl                                            | * * 0 0 |           |

| 99         | CVTBW src.rb, dst.wl                                            | * * 0 0 |           |

| F6         | CVTLB src.rl, dst.wb                                            | * * * 0 | iov       |

| F7         | CVTLW src.rl, dst.ww                                            | * * * 0 | iov       |

| 33         | CVTWB src.rw, dst.wb                                            | * * * 0 | iov       |

| 32         | CVTWL src.rw, dst.wl                                            | * * 0 0 |           |

|            |                                                                 |         |           |

| 97         | DECB dif.mb                                                     | * * * * | iov       |

| 7מ         | DECL dif.ml                                                     | * * * * | iov       |

| в7         | DECW dif.mw                                                     | * * * * | iov       |

|            |                                                                 |         |           |

| 86         | DIVB2 divr.rb, quo.mb                                           | * * * 0 | iov, idvz |

| C6         | DIVL2 divr.rl, quo.ml                                           | * * * 0 | iov, idvz |

| <b>A</b> 6 | DIVW2 divr.rw, quo.mw                                           | * * * 0 | iov, idvz |

|            |                                                                 |         |           |

| 87         | DIVB3 divr.rb, divd.rb, quo.wb                                  | * * * 0 | iov, idvz |

| C7         | DIVL3 divr.rl, divd.rl, quo.wl                                  | * * * 0 | iov, idvz |

| A7         | DIVW3 divr.rw, divd.rw, quo.ww                                  | * * * 0 | iov, idvz |

| 7B         | EDIV divr.rl, divd.rq, quo.wl, rem.wl                           | * * * 0 | iov, idvz |

| ,,,        | and divinity divinity, quoting, romanic                         | · ·     | 101, 1411 |

| 7A         | EMUL mulr.rl, muld.rl, add.rl, prod.wq                          | * * 0 0 |           |

|            |                                                                 |         |           |

| 96         | INCB sum.mb                                                     | * * * * | iov       |

| D6         | INCL sum.ml                                                     | * * * * | iov       |

| В6         | INCW sum.mw                                                     | * * * * | iov       |

|            |                                                                 |         |           |

| 92         | MCOMB src.rb, dst.wb                                            | * * 0 - |           |

| D2         | MCOML src.rl, dst.wl                                            | * * 0 - |           |

| B2         | MCOMW src.rw, dst.ww                                            | * * 0 - |           |

| 8E         | MNEGB src.rb, dst.wb                                            | * * * * | iov       |

| CE         | MNEGL src.rl, dst.wl                                            | * * * * | iov       |

| AE         | MNEGW src.rw, dst.ww                                            | * * * * | iov       |

|            | and storen, ascent                                              |         | 101       |

| 90         | MOVB src.rb, dst.wb                                             | * * 0 - |           |

| D0         | MOVL src.rl, dst.wl                                             | * * 0 - |           |

| <b>7</b> D | MOVQ src.rq, dst.wq                                             | * * 0 - |           |

| в0         | MOVW src.rw, dst.ww                                             | * * 0 - |           |

|            |                                                                 |         |           |

| 9a         | MOVZBW src.rb, dst.wb                                           | 0 * 0 - |           |

| 9B         | MOVZBL src.rb, dst.wl                                           | 0 * 0 - |           |

| 3C         | MOVZWL src.rw, dst.ww                                           | 0 * 0 - |           |

|            |                                                                 |         |           |

| 84         | MULB2 mulr.rb, prod.mb                                          | * * * 0 | iov       |

| C4         | MULL2 mulr.rl, prod.ml                                          | * * * 0 | iov       |

| A4         | MULW2 mulr.rw, prod.mw                                          | * * * 0 | iov       |

| 85         | MITERS mult the muld the wood ob                                | * * * 0 | iov       |

| 65<br>C5   | MULB3 mulr.rb, muld.rb, prod.wb MULL3 mulr.rl, muld.rl, prod.wl | * * * 0 | iov       |

| A5         | MULW3 mulr.rw, muld.rw, prod.ww                                 | * * * 0 | iov       |

|            | TOWNS MASSIAN, MASSIAN, PAGESAN                                 | v       |           |

|            | CHIP ENGINEERING SPECIFICATION (Company Confidential TURE SUMMARY | l) Page 19         |            |

|------------|-------------------------------------------------------------------|--------------------|------------|

| DD         | PUSHL src.rl, {-(SP).wl}                                          | * * 0 -            |            |

| 9C         | ROTL cnt.rb, src.rl, dst.wl                                       | * * 0 -            |            |

| D9         | SBWC sub.rl, dif.ml                                               | * * * *            | iov        |

| 82         | SUBB2 sub.rb, dif.mb                                              | * * * *            | iov        |

| C2         | SUBL2 sub.rl, dif.ml                                              | * * * *            | iov        |

| A2         | SUBW2 sub.rw, dif.mw                                              | * * * *            | iov        |

| 83         | SUBB3 sub.rb, min.rb, dif.wb                                      | * * * *            | iov        |

| C3         | SUBL3 sub.rl, min.rl, dif.wl                                      | * * * *            | iov        |

| A3         | SUBW3 sub.rw, min.rw, dif.ww                                      | * * * *            | iov        |

| 95         | TSTB src.rb                                                       | * * 0 0            |            |

| D5         | TSTL src.rl                                                       | * * 0 0            |            |

| B5         | TSTW src.rw                                                       | * * 0 0            |            |

| 8C         | XORB2 mask.rb, dst.mb                                             | * * 0 -            |            |

| CC         | MORL2 mask.rl, dst.ml                                             | * * 0 -            | •          |

| AC         | XORW2 mask.rw, dst.mw                                             | * * 0 -            |            |

| 8D         | XORB3 mask.rb, src.rb, dst.wb                                     | * * 0 -            |            |

| CD         | XORL3 mask.rl, src.rl, dst.wl                                     | * * 0 -<br>* * 0 - |            |

| 2.4.2      | Address Instructions -                                            |                    |            |

| Opcode     | Instruction                                                       | NZVC               | Exceptions |

| 9E         | MOVAB src.ab, dst.wl                                              | * * 0 -            |            |

| DE         | MOVAL(=F) src.al, dst.wl                                          | * * 0 -            |            |

| 7E         | MOVAQ{=D=G} src.aq, dst.wl                                        | * * 0 -            |            |

| 3E         | MOVAW src.aw, dst.wl                                              | * * 0 -            |            |

| 9 <b>F</b> | PUSHAB src.ab, {-(SP).wl}                                         | * * 0 -            |            |

| DF         | PUSHAL{=F} src.al, {-(SP).wl}                                     | * * 0 -            |            |

| 7 <b>F</b> | <pre>PUSHAQ{=D=G} src.aq, {-(SP).wl}</pre>                        | * * 0              |            |

| 3 <b>F</b> | PUSHAW src.aw, {-(SP).wl}                                         | * * 0 -            |            |

| 2.4.3      | Variable Length Bit Field Instructions -                          |                    |            |

| Opcode<br> | Instruction                                                       | NZVC               | Exceptions |

|            |                                                                   |                    |            |

CMPV pos.rl, size.rb, base.vb, {field.rv}, src.rl

rsv

EC

|    | OU CHIP ENGINEERING SPECIFICATION (Company Confidential)     | Page 20 |     |

|----|--------------------------------------------------------------|---------|-----|

| ED | CMPZV pos.rl, size.rb, base.vb, {field.rv}, src.rl           | * * 0 * | rsv |

| EE | EXTV pos.rl, size.rb, base.vb, {field.rv}, dst.wl            | * * 0 - | rsv |

| EF | EXTZV pos.rl, size.rb, base.vb, {field.rv}, dst.wl           | * * 0 - | rsv |

| F0 | <pre>INSV src.rl, pos.rl, size.rb, base.vb, {field.wv}</pre> |         | rsv |

| EB | FFC startpos.rl, size.rb, base.vb, {field.rv}, findpos.wl    | 0 * 0 0 | rsv |

FFS startpos.rl, size.rb, base.vb, {field.rv}, findpos.wl

0 \* 0 0

rsv

# 2.4.4 Control Instructions -

EA

| Opcode     | Instruction                                 | NZVC    | Exceptions |

|------------|---------------------------------------------|---------|------------|

|            |                                             |         |            |

| 9D         | ACBB limit.rb, add.rb, index.mb, displ.bw   | * * * = | iov        |

| F1         | ACBL limit.rl, add.rl, index.ml, displ.bw   | * * * _ | iov        |

| 3D         | ACBW limit.rw, add.rw, index.mw, displ.bw   | * * * _ | iov        |

| <b>F</b> 3 | AOBLEQ limit.rl, index.ml, displ.bb         | * * * _ | iov        |

| F2         | AOBLSS limit.rl, index.ml, displ.bb         | * * * _ | iov        |

| 1E         | BCC{=BGEQU} displ.bb                        |         |            |

| 1F         | BCS{=BLSSU} displ.bb                        |         |            |

| 13         | BEQL{=BEQLU} displ.bb                       |         |            |

| 18         | BGEQ displ.bb                               |         |            |

| 14         | BGTR displ.bb                               |         |            |

| 1A         | BGTRU displ.bb                              |         |            |

| 15         | BLEQ displ.bb                               |         |            |

| 1B         | BLEQU displ.bb                              |         |            |

| 19         | BLSS displ.bb                               |         |            |

| 12         | <pre>BNEQ{=BNEQU} displ.bb</pre>            |         |            |

| 1C         | BVC displ.bb                                |         |            |

| 1D         | BVS displ.bb                                |         |            |

| E1         | BBC pos.rl, base.vb, displ.bb, {field.rv}   |         | rsv        |

| E0         | BBS pos.rl, base.vb, displ.bb, {field.rv}   |         | rsv        |

| <b>E</b> 5 | BBCC pos.rl, base.vb, displ.bb, {field.mv}  |         | rsv        |

| E3         | BBCS pos.rl, base.vb, displ.bb, {field.mv}  |         | rsv        |

| E4         | BBSC pos.rl, base.vb, displ.bb, {field.mv}  |         | rsv        |

| E2         | BBSS pos.rl, base.vb, displ.bb, {field.mv}  |         | rsv        |

| E7         | BBCCI pos.rl, base.vb, displ.bb, {field.mv} |         | rsv        |

| E6         | BBSSI pos.rl, base.vb, displ.bb, {field.mv} |         | rsv        |

| E9         | BLBC src.rl, displ.bb                       |         |            |

| E8         | BLBS src.rl, displ.bb                       |         |            |

|            |                                             |         |            |

|                 | U CHIP ENGINEERING SPECIFICATION (Company Confidential) CTURE SUMMARY | Page 21 |            |

|-----------------|-----------------------------------------------------------------------|---------|------------|

| 11<br>31        | BRB displ.bb BRW displ.bw                                             |         |            |

| 10              | BSBB displ.bb, {-(SP).wl}                                             |         |            |

| 30              | BSBW displ.bw, {-(SP).wl}                                             |         |            |

| 8 <b>F</b>      | CASEB selector.rb, base.rb, limit.rb, displ.bw-list                   | * * 0 * |            |

| CF              | CASEL selector.rl, base.rl, limit.rl, displ.bw-list                   | * * 0 * |            |

| AF              | CASEW selector.rw, base.rw, limit.rw, displ.bw-list                   | * * 0 * |            |

| 17              | JMP dst.ab                                                            |         |            |

| 16              | JSB dst.ab, {-(SP).wl}                                                |         |            |

| 05              | RSB {(SP)+.rl}                                                        |         |            |

| F4              | SOBGEQ index.ml, displ.bb                                             | * * * _ | iov        |

| F5              | SOBGTR index.ml, displ.bb                                             | * * * _ | iov        |

| 2.4.5<br>Opcode | Procedure Call Instructions -  Instruction                            | N Z V C | Exceptions |

| FA              | CALLG arglist.ab, dst.ab, {-(SP).w*}                                  | 0 0 0 0 | rsv        |

| FB              | CALLS numarg.rl, dst.ab, {-(SP).w*}                                   | 0 0 0 0 | rsv        |

| 04              | RET {(SP)+.r*}                                                        | * * * * | rsv        |

| 2.4.6           | Miscellaneous Instructions -                                          |         |            |

| Opcode | Instruction                                                                      | N Z V C | Exceptions |

|--------|----------------------------------------------------------------------------------|---------|------------|

| В9     | BICPSW mask.rw                                                                   | * * * * | rsv        |

| В8     | BISPSW mask.rw                                                                   | * * * * | rsv        |

| 03     | BPT {-(KSP).w*}                                                                  | 0 0 0 0 |            |

| 00     | HALT {-(KSP).w*}                                                                 |         | prv        |

| 0A     | <pre>INDEX subscript.rl, low.rl, high.rl, size.rl, indexin.rl, indexout.wl</pre> | * * 0 0 | sub        |

| DC     | MOVPSL dst.wl                                                                    |         |            |

|            | J CHIP ENGINEERING SPECIFICATION (Company Confidential) TURE SUMMARY   | Page 22 |            |

|------------|------------------------------------------------------------------------|---------|------------|

| 01         | NOP                                                                    |         |            |

| BA         | POPR mask.rw, {(SP)+.r*}                                               |         |            |

| ВВ         | PUSHR mask.rw, {-(SP).w*}                                              |         |            |

| FC         | XFC {unspecified operands}                                             | 0 0 0 0 |            |

| 2.4.7 (    | Queue Instructions —                                                   |         |            |

| Opcode     | Instruction                                                            | N Z V C | Exceptions |

| 5C         | INSQHI entry.ab, header.aq                                             | 0 * 0 * | rsv        |

| 5D         | INSQTI entry.ab, header.aq                                             | 0 * 0 * | rsv        |

| 0E         | INSQUE entry.ab, pred.ab                                               | * * 0 * |            |

| 5 <b>E</b> | REMQHI header.aq, addr.wl                                              | 0 * * * | rsv        |

| 5 <b>F</b> | REMQTI header.aq, addr.wl                                              | 0 * * * | rsv        |

| 0F         | REMQUE entry.ab, addr.wl                                               | * * * * |            |

| 2.4.8      | Character String Instructions —                                        |         |            |

| Opcode     | Instruction                                                            | N Z V C | Exceptions |

| 28         | MOVC3 len.rw, srcaddr.ab, dstaddr.ab, {R0-5.wl}                        | 0 1 0 0 |            |

| <b>2</b> C | MOVC5 srclen.rw, srcaddr.ab, fill.rb, dstlen.rw, dstaddr.ab, {R0-5.wl} | * * 0 * |            |

| 2.4.9      | Operating System Support Instructions —                                |         |            |

| Opcode     | Instruction                                                            | N Z V C | Exceptions |

| BD<br>BC   | CHME param.rw, {-(ySP).w*} CHMK param.rw, {-(ySP).w*}                  | 0 0 0 0 |            |

| BE         | CHMS param.rw, {-(ySP).w*}                                             | 0 0 0 0 |            |

| BF         | CHMU param.rw, {-(ySP).w*}                                             | 0 0 0 0 |            |

| Where ' | V=MINU(    | x. PSL | <pre><current< pre=""></current<></pre> | mode>) |

|---------|------------|--------|-----------------------------------------|--------|

| where.  | Λ≕LITIMO ( | X. PSL | Current                                 | mode>  |

| 06 | LDPCTX {PCB.r*, -(KSP).w*}      |         | rsv, prv |

|----|---------------------------------|---------|----------|

| DB | MFPR procreg.rl, dst.wl         | * * 0 - | rsv, prv |

| DA | MTPR src.rl, procreg.rl         | * * 0 - | rsv, prv |

| 0C | PROBER mode.rb, len.rw, base.ab | 0 * 0 - |          |

| 0D | PROBEW mode.rb, len.rw, base.ab | 0 * 0 - |          |

| 02 | REI {(SP)+.r*}                  | * * * * | rsv      |

| 07 | SVPCTX {(SP)+.r*, PCB.w*}       |         | prv      |

# 2.4.10 Floating Point Instructions -

These instructions are implemented in hardware only if an external floating point unit is present in the system.

| Opcode | Instruction                               | N Z V C | Exceptions    |

|--------|-------------------------------------------|---------|---------------|

|        |                                           |         |               |

| 6F     | ACBD limit.rd, add.rd, index.md, displ.bw | * * 0 - | rsv, fov, fuv |

| 4F     | ACBF limit.rf, add.rf, index.mf, displ.bw | * * 0 - | rsv, fov, fuv |

| 4FFD   | ACBG limit.rg, add.rg, index.mg,displ.bw  | * * 0 - | rsv, fov, fuv |

| 60     | ADDD2 add.rd, sum.md                      | * * 0 0 | rsv, fov, fuv |

| 40     | ADDF2 add.rf, sum.mf                      | * * 0 0 | rsv, fov, fuv |

| 40FD   | ADDG2 add.rg, sum.mg                      | * * 0 0 | rsv, fov, fuv |

| 61     | ADDD3 add1.rd, add2.rd, sum.wd            | * * 0 0 | rsv, fov, fuv |

| 41     | ADDF3 add1.rf, add2.rf, sum.wf            | * * 0 0 | rsv, fov, fuv |

| 41FD   | ADDG3 add1.rg, add2.rg, sum.wg            | * * 0 0 | rsv, fov, fuv |

| 71     | CMPD src1.rd, src2.rd                     | * * 0 0 | rsv           |

| 51     | CMPF src1.rf, src2.rf                     | * * 0 0 | rsv           |

| 51FD   | CMPG src1.rg, src2.rg                     | * * 0 0 | rsv           |

| 6C     | CVTBD src.rb, dst.wd                      | * * 0 0 |               |

| 4C     | CVTBF src.rb, dst.wf                      | * * 0 0 |               |

| 4CFD   | CVTBG src.rb, dst.wg                      | * * 0 0 |               |

| 68     | CVTDB src.rd, dst.wb                      | * * * 0 | rsv, iov      |

| 76     | CVTDF src.rd, dst.wf                      | * * 0 0 | rsv, fov      |

| 6A     | CVTDL src.rd, dst.wl                      | * * * 0 | rsv, iov      |

| 69     | CVTDW src.rd, dst.ww                      | * * * 0 | rsv, iov      |

| 48     | CVTFB src.rf, dst.wb                      | * * * 0 | rsv, iov      |

| 56     | CVTFD src.rf, dst.wd                      | * * 0 0 | rsv           |

| 99FD   | CVTFG src.rf, dst.wg                      | * * 0 0 | rsv           |

| 4A     | CVTFL src.rf, dst.wl                      | * * * 0 | rsv, iov      |

| 49     | CVTFW src.rf, dst.ww                      | * * * 0 | rsv, iov      |

| 48FD   | CVTGB src.rg, dst.wb                      | * * * 0 | rsv, iov      |

| 33FD  | CVTGF src.rg, dst.wf                               | * * 0 0 | rsv, fov, fuv       |

|-------|----------------------------------------------------|---------|---------------------|

| 4AFD  | CVTGL src.rg, dst.wl                               | * * * 0 | rsv, iov            |

| 49FD  | CVTGW src.rg, dst.ww                               | * * * 0 | rsv, iov            |

| 6E    | CVTLD src.rl, dst.wd                               | * * 0 0 |                     |

| 4E    | CVTLF src.rl, dst.wf                               | * * 0 0 |                     |

| 4EFD  | CVTLG src.rl, dst.wg                               | * * 0 0 |                     |

| 6D    | CVTWD src.rw, dst.wd                               | * * 0 0 |                     |

| 4D    | CVTWF src.rw, dst.wf                               | * * 0 0 |                     |

| 4DFD  | CVTWG src.rw, dst.wq                               | * * 0 0 |                     |

|       |                                                    |         |                     |

| 6B    | CVTRDL src.rd, dst.wl                              | * * * 0 | rsv, iov            |

| 4B    | CVTRFL src.rf, dst.wl                              | * * * 0 | rsv, iov            |

| 4BFD  | •                                                  | * * * 0 | · <u>-</u>          |

| ADLD  | CVTRGL src.rg, dst.wl                              | 0       | rsv, iov            |

| 66    | DITITO diam ad ana ad                              | * * 0 0 | 6 6 6               |

|       | DIVD2 divr.rd, quo.md                              |         | rsv, fov, fuv, fdvz |

| 46    | DIVF2 divr.rf, quo.mf                              | * * 0 0 | rsv, fov, fuv, fdvz |

| 46FD  | DIVG2 divr.rg, quo.mg                              | * * 0 0 | rsv, fov, fuv, fdvz |

| 67    | DIVD3 divr.rd, divd.rd, quo.wd                     | * * 0 0 | rsv, fov, fuv, fdvz |

| 47    | • • •                                              | * * 0 0 |                     |

|       | DIVF3 divr.rf, divd.rf, quo.wf                     | * * 0 0 | rsv, fov, fuv, fdvz |

| 47FD  | DIVG3 divr.rg, divd.rg, quo.wg                     | ^ ^ U U | rsv, fov, fuv, fdvz |

| 74    | EMODD mulr.rd, mulrx.rb, muld.rd, int.wl, fract.wd | * * * 0 | rsv, fov, fuv, iov  |

| 54    |                                                    | * * * 0 |                     |

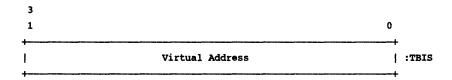

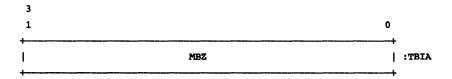

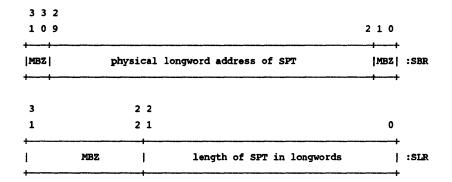

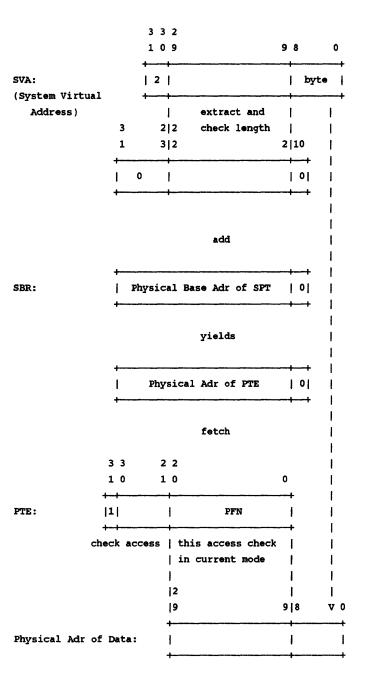

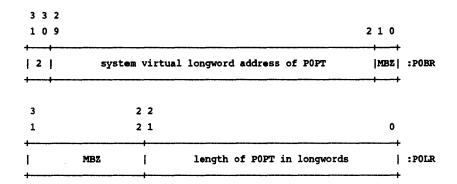

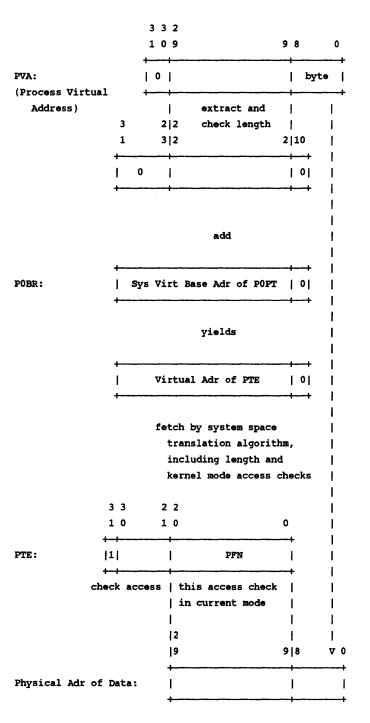

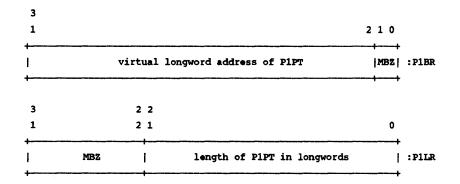

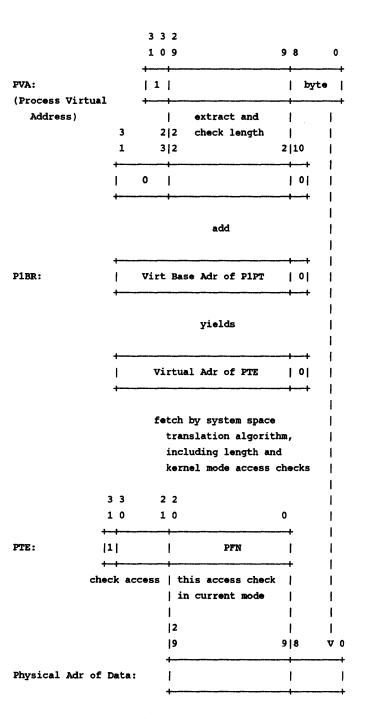

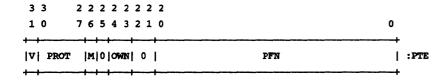

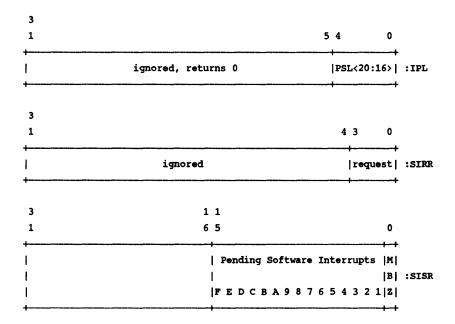

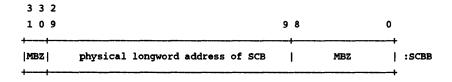

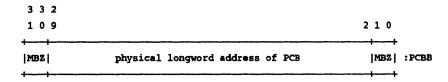

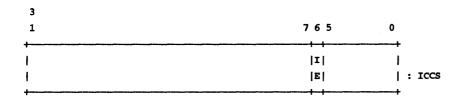

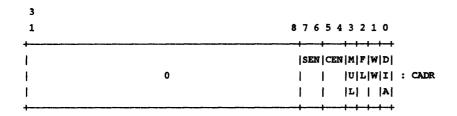

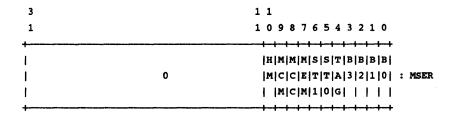

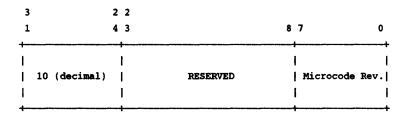

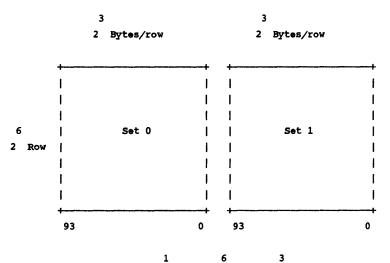

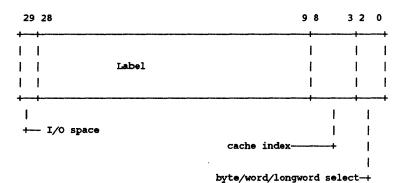

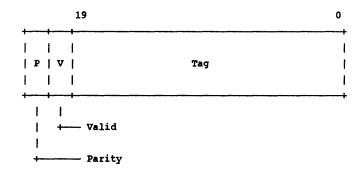

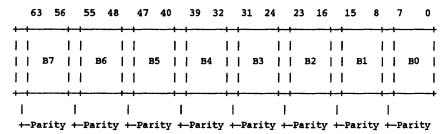

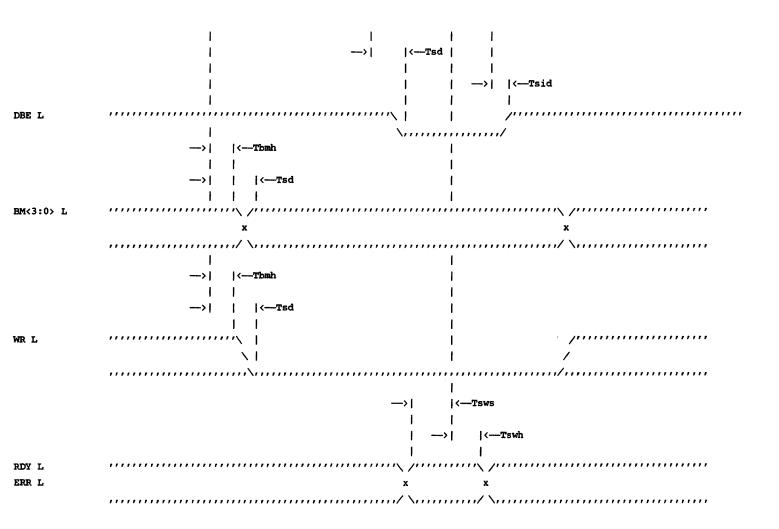

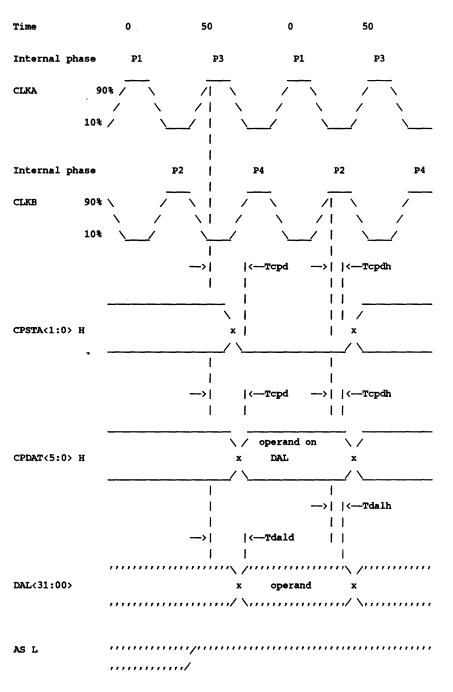

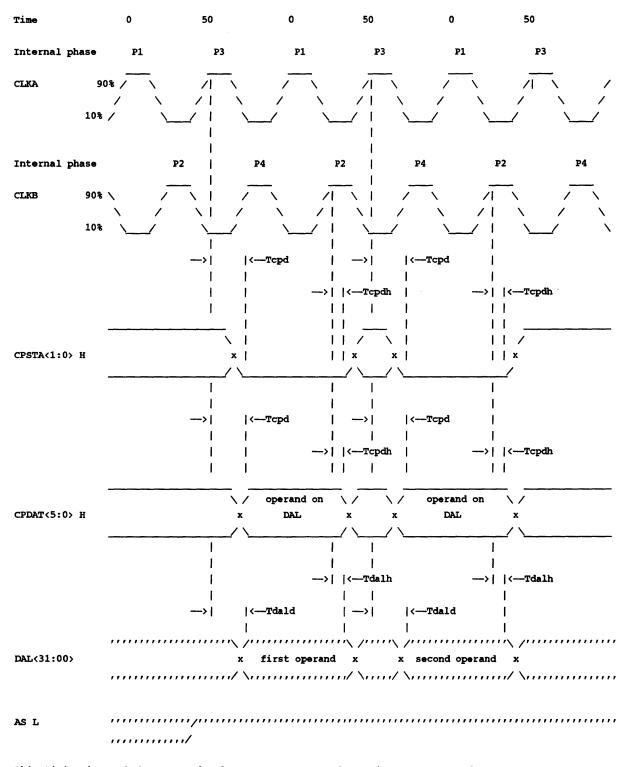

|       | EMODF mulr.rf, mulrx.rb, muld.rf, int.wl, fract.wf | _       | rsv, fov, fuv, iov  |