# PVAX2/PMariah Memory/Graphics/Video Controller

VAX Workstation Engineering

13-September-1990

This document is the hardware specification of the PVAX2/PMariah memory, graphics, and video controller.

#### Contacts:

```

Kim Meinerth, Jacob::Meinerth, ML05-2, 223-3328

Blaise Fanning, Jacob::Fanning, ML05-2, 223-2036

K. Srinivasan, Jacob::Srini, ML05-2, 223-2322

Ali Moezzi, Jacob::Moezzi, ML05-2, 223-2322

Colyn Case,

Colyn Case, Star::Case, ZK03-4, 381-1245

John Irwin, Star::Irwin, ZK03-4, 381-2813

Jonathan Kaplan, Star::Kaplan, ZK03-4, 381-1950

Chris Franklin, Star::Franklin, ZK03-4, 381-1952

Desty Masucci, Leddev::Masucci, ML021-4, 223-2824

```

# This document is COMPANY CONFIDENTIAL.

This information shall not be disclosed to non-Digital personnel or generally distributed within Digital. Distribution is restricted to persons authorized and designated by VAX Workstation Engineering.

This document shall not be left unattended, and, when not in use, shall be stored in a locked

These restrictions are enforced until this document is reclassified by VAX Workstation Engineering.

digital equipment corporation, maynard, massachusetts

# **Preface**

This document is the formal specification of the PVAX2/PMariah memory, graphics, and video controller hardware.

### **Document Structure**

This document is arranged in sections, each of which describes a major topic of the PVAX2/PMariah memory, graphics, and video controller hardware.

### **Associated Documents**

- PVAX2 System Specification—John Kirk

- PMariah System Specification—John Kirk

- PVAX2/PMariah S-Chip Specification—George Lord

- PVAX2/PMariah LCG Address Genarator Design Specification—Blaise Fanning

- PVAX2/PMariah LCG Virtual Memory Support—Colyn Case

- PVAX2/PMariah LCG Command Packets—Colyn Case

- PVAX2/PMariah LCG HW Overview (\included here)—Kim Meinerth

- PVAX2/PMariah LCG Pins, Interface & Internal Signals (included here)—Kim Meinerth

# **Revision Information**

| Date        | Editor                                  | Description/Summary of Changes                                                                   |  |  |  |  |

|-------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| 20-AUG-1990 | Kim Meinerth                            | updates                                                                                          |  |  |  |  |

| 12-JAN-1989 | John Irwin                              | Rework register section.                                                                         |  |  |  |  |

| 14-NOV-1989 | Kim A. Meinerth &<br>Jonathan C. Kaplan | Restructure GRAPHICS Registers, add MISC_ENABLE and MISC_STATUS, and merge in VMS register names |  |  |  |  |

| 21-SEP-1989 | John Irwin                              | Coverted to VAX-DOCUMENT format                                                                  |  |  |  |  |

| 08-SEP-1989 | Kim A. Meinerth                         | Start PMariah Updates                                                                            |  |  |  |  |

| 10-JAN-1989 | Kim A. Meinerth                         | Start SOC Updates                                                                                |  |  |  |  |

| 17-AUG-1988 | Kim A. Meinerth                         | Initial Working Draft                                                                            |  |  |  |  |

#### 1 Introduction

The Low Cost Graphics (LCG) system is jointly specified and architected with VMS DECwindows Engineering.

The PVAX2/PMariah Graphics (1, 8, 24 plane), Memory, and Video Controller is a portion of the PVAX2/PMariah System ASIC, S-Chip (DC7201). LCG is a smart memory controller which understands the most heavily used "X-Window" graphics primitives and executes them at memory bandwidth speeds with minimal memory latency. LCG provides competitive 2D Graphics performance and functionality for the lowest cost possible. The LCG architecture allows the graphics primitives supported to be greatly expanded in future implementations.

LCG operates on both frame buffer memory and virtual main memory. Graphics primitives are supported to multiple clipping rectangles (in frame buffer and virtual memory) for direct support of over-lapping windows and backing store with linear addressing. Main memory has byte parity for both lowest cost and graphics performance which tends to be byte (8 plane) oriented.

The memory system supports byte parity memory with up to 4 banks of 64 bit main memory, as well as, up to 4 frame buffers. This gives main memory configurations of 8M, 16M, 24M, and 32M bytes with 1Mx1 DRAMs which is the maximum memory range for PVAX2. The memory increments MUST be a multiple of 64 bits or 8M bytes.

The PMariah system can access up to 104M bytes with 4Mx1 DRAMs in 32M byte increments in the most significant 3 memory banks. The low order bank for both PVAX2 and PMariah is fixed at 8M bytes. Mixing 8M bytes memory banks with 32M bytes memory banks is allowed on the PMariah system, but the 32M byte banks must be in the high order memory banks.

With 254kx4 DRAMs, 2M bytes memory banks with a maximum memory range of 8M bytes are supported for an extremely low cost system. Byte Parity is supported with 8 1Mx1 DRAMs for the whole 8M byte address range.

The data access sizes are: byte, word, longword, quadword, and octaword. The DRAMs and VRAMs are 100 nsec access time fast page mode devices.

The video controller is programmable and supports multiple screen resolutions. It is capable of supporting formats up to a resolution of 2048x2048 (dependant on the final ASIC AC timing). The following frame buffers are planned:

| Module Type:                            | Resolution         | 8 Plane | 4 Plane | Refre | sh R | late | Overlays |

|-----------------------------------------|--------------------|---------|---------|-------|------|------|----------|

| ======================================= | ========           | ======  | ======  | ===== | ==== | ===  | =======  |

| High Resolution                         | $1280 \times 1024$ | yes     | yes     |       | 66   | 72   | No       |

| Low Resolution                          | 1024x 768          | yes     | no      | 60    |      |      | No       |

|                                         | 1024x 864          | yes     | no      | 60    |      |      | No       |

| Dual Head                               | $1280 \times 1024$ | yes     | no      |       | 66   | 72   | No       |

| Full Color                              | $1280 \times 1024$ | 24 E    | Planes  |       | 66   | 72   | Yes      |

A 64x64x2 cursor is supported and stored in 1k bytes of off-screen physical memory.

The System ASIC, S-Chip, is a 0.8 micron compacted array with 172k raw gates and ~40%-50% utilization which gives ~75k gates available. The Graphics, Memory, and Video subsystems implementations are ~48k gates.

Figure 1: PVAX2 Block Diagram

Figure 2: Low Cost Graphics/Memory/Video Controller Block Diagram

# 1.1 MV\_DAL Option

The S-Chip MV\_DAL option interface supports both Program I/O and LCG Virtual DMA. The protocal is specified in here in a later section. The Cursor<7:0> pins are used for communicating with the MV\_DAL Option. The MV\_DAL is a RAS/CAS memory bus.

#### 2 Overview

The following sections will give overviews for the major components of the Low Cost Graphics/Memory/Video subsystem in the PVAX2/PMariah System chip, S-Chip. The memory controller is integrated with the graphics and video control. The memory controller supports the memory access modes and special signals required for VRAM and 2D graphics primitives. The graphics address generator operates on both Frame Buffer VRAM and Virtual Main Memory at memory speeds. Data can be moved to and from VRAM and main memory for off-screen pixel maps and fonts, also at memory speeds. The design is highly pipelined with separate graphics and memory state machines for the highest memory bandwidth efficiency and minimal memory hogging by the graphics controller.

The LCG functionality off loads the CPU and conserves the VAX VUPS for the DECwindows server, operating system, and applications as much as possible. The goal is competitive system performance at minimal cost.

# 2.1 Memory Request Prioritiy

The low cost graphics controller is last on the priority list. It is effectively a background task. When graphics primitives are present, then it takes up all spare memory cycles. The priority of requests serviced are:

- 1. Video Controller:

- 1. Video Shift Register Load

- 2. Cursor Buffer Load Octaword read = 64 x 2 planes

- 3. Memory Refresh

- 2. NI Controller

- 3. CPU Interface / Bus Adapter

- 4. SCSI Controller

- 5. Graphics Address Generator

# 2.2 LCG Interrupt Vectors:

The LCG subsystem generates 2 different interrupt signals and status longwords with the following priority:

- 1. Graphics and Command FIFO and Vertical Retrace

- 2. MV\_DAL Option

# 2.3 PVAX2/PMariah Low Cost Graphics, LCG, Features List

- LCG is Highly Integrated with the PVAX2/PMariah Memory Controller.

Graphics is a Background Task Uses unused Memory Cycles.

- LCG is a Joint Design with VMS DECWindows Engineering.

Designed for Best Fit with X and Avoids Special Cases

Works with Virtual Memory:

- Unlimited Dawing Space

- Improves Performance

- Avoids Software Complexity

- Video Modules Designed for Minimal Cost Graphics Controller is free. Minimal VRAMs \_& Video Out Only

| Display            | No of VRAMs     | VRAM Cost   | Cost FY91 | Cost FY92 |

|--------------------|-----------------|-------------|-----------|-----------|

|                    |                 |             | =======   | =======   |

| 2M Pixel 1 Plane   | 4 128kx8s       | \$ 60/\$ 36 | ~\$180    | ~\$164    |

| All Resolutions    |                 |             |           |           |

| 1M Pixel 8 Plane   | 8 128kx8s       | \$120/\$ 72 | ~\$240    | ~\$200    |

| 1024x 864, 1024x   | 768, & 800x     | 600         |           |           |

| 2M Pixel 8 Plane   | 16 256kx4s      | \$208/\$144 | ~\$295    | ~\$240    |

| $1280 \times 1024$ |                 |             |           |           |

| 12010 17033        | vis & \$15 (FY9 | 1) 610 /57  | .021      |           |

|                    |                 |             |           |           |

128kx8 VRAMs @ \$15 (FY91) \$10 (FY92) 256kx4 VRAMs @ \$13 (FY91), \$ 9 (FY92)

- 64x64x2 Cursor Support for both Color and Monochrome

- PVAX2/PMariah LCG supports 2D Graphics Primitives:

LCG Offloads CPU Saves VUPs for Server and Applications

LCG Graphics Primitives Supported:

- Lines or Vectors

- 3 Operand RasterOps, Spans, and Points with Tiling, Stipples, Color Expansion, & Plane Extraction

- Text, Both Solid & Stenciled with Variable Sized Glyphs

- Multiple Clipping Rectangle Support for all Primitives

- All Operands can be Virtual

# 2.4 Graphics Performance Estimates (VMS & X-Server Overhead)

| 50k         ?         50k         ?           rel/PMAX         pixel/Dragon 35k         N.A.         N.A.         N.A.         N.A.           setangle Fill as Million Pixels Per Second         26-30ns         40         13         120         35         100           3G-35ns         32         10         105         28         80           AX1         40         N.A.         N.A.         N.A.         N.A.           sapon         8         N.A.         N.A.         N.A.         N.A.           sapon         8         N.A.         N.A.         N.A.         N.A.           sove Area/Scroll as Million Pixels Per Second         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         20         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      | Video Frame Buffer |                     |          | Virtual Pixel Map |         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|---------------------|----------|-------------------|---------|--|

| pixel/LCG-30r8260k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      | 8 Plane            | 24 Plane            | 1 Plane  | 8 Plane           | 1 Plane |  |

| pixel/LCG-35/g200k   200k   200k   125k   125k   125k   pixel/PVAX1   240k   N.A.      | Random Vectors       | Per Second         | d (Worst Case Orier | ntation) |                   |         |  |

| Size   PVAX1   240k   N.A.   Pixel   PVAX1   240k   N.A.   | 10 pixel/LCG-30      | n2s50k             | 85k                 | 250k     | 150k              | 150k    |  |

| 50k ? ? 50k ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10 pixel/LCG-35      | n2e00k             | 200k                | 200k     | 125k              | 125k    |  |

| tel/PMAX pixel/Dragon 35k N.A. N.A. N.A. N.A. N.A. N.A.    pixel/Dragon 35k N.A. N.A. N.A. N.A. N.A. N.A. N.A. N.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10 pixel/PVAX1<br>SP | 240k               | N.A.                | N.A.     | N.A.              | N.A.    |  |

| Actangle Fill as Million Pixels Per Second  ACG-30ns 40 13 120 35 100  ACG-35ns 32 10 105 28 80  ACX1 40 N.A. N.A. N.A. N.A. N.A.  AINARIPPOC  agon 8 N.A. N.A. N.A. N.A. N.A.  ACCOVE Area/Scroll as Million Pixels Per Second  ACG-30ns 18 6 60 15 50  ACG-35ns 15 5 5 52 12 40  ACX1 20 N.A. N.A. N.A. N.A. N.A.  ACXII 30 N.A. N.A. N.A. N.A. N.A.  ACXII 30 N.A. N.A. N.A. N.A. N.A.  ACXII 30 N.A. N.A. N.A. N.A. N.A. N.A.  ACXII 30 N.A. N.A. N.A. N.A. N.A. N.A.  ACXII 31 N.A. N.A. N.A. N.A. N.A. N.A. N.A.  ACXII 32 N.A. N.A. N.A. N.A. N.A. N.A. N.A. N.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10<br>pixel/PMAX     | 50k                | ?                   | ?        | 50k               | ?       |  |

| GG-30ns 40 13 120 35 100 GG-35ns 32 10 105 28 80 AXX1 40 N.A. N.A. N.A. N.A. N.A.  aapon 8 N.A. N.A. N.A. N.A. N.A.  Deve Area/Scroll as Million Pixels Per Second  GG-30ns 18 6 60 15 50 GG-35ns 15 5 52 12 40 AXX1 20 N.A. N.A. N.A. N.A. N.A. N.A.  DeanProc MAX 4.0/5.3 ? ? 4.0/5.3 ? DeanProc MAX 4.0/5.3 ? N.A. N.A. N.A. N.A. N.A.  Axis as Glyphs/Second  CXII/LCG-30ns 150k 50k 170k 95k 95k CXIII/LCG-35ns 130k 40k 150k 85k 85k CXIII/PVAX1 170k N.A. N.A. N.A. N.A. N.A.  CXIII/Dragon 25k N.A. N.A. N.A. N.A. N.A. N.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 pixel/Dragon      | 35k                | N.A.                | N.A.     | N.A.              | N.A.    |  |

| 2G-35ns 32 10 105 28 80  AX1 40 N.A. N.A. N.A. N.A. N.A.  AnnProc  agon 8 N.A. N.A. N.A. N.A. N.A.  Deve Area/Scroll as Million Pixels Per Second  CG-30ns 18 6 60 15 50  AX1 20 N.A. N.A. N.A. N.A. N.A.  CANTAR SECOND SE | Rectangle Fill as    | s Million Pixe     | els Per Second      |          |                   |         |  |

| AX1       40       N.A.       N.A. <t< td=""><td>LCG-30ns</td><td>40</td><td>13</td><td>120</td><td>35</td><td>100</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | LCG-30ns             | 40                 | 13                  | 120      | 35                | 100     |  |

| Agon 8 N.A. N.A. N.A. N.A. N.A. N.A. N.A. N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LCG-35ns             | 32                 | 10                  | 105      | 28                | 80      |  |

| Ove Area/Scroll as Million Pixels Per Second  CG-30ns 18 6 60 15 50  CG-35ns 15 5 52 12 40  //AX1 20 N.A. N.A. N.A. N.A. N.A.  SanProc  MAX 4.0/5.3 ? ? 4.0/5.3 ?  Fagon 8.0 N.A. N.A. N.A. N.A. N.A.  Oxt as Glyphs/Second  C11/LCG-30ns 150k 50k 170k 95k 95k  C11/LCG-35ns 130k 40k 150k 85k 85k  C11/PVAX1 170k N.A. N.A. N.A. N.A. N.A.  C11/Dragon 25k N.A. N.A. N.A. N.A. N.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PVAX1<br>ScanProc    | 40                 | N.A.                | N.A.     | N.A.              | N.A.    |  |

| CG-30ns 18 6 60 15 50 CG-35ns 15 5 52 12 40  //AX1 20 N.A. N.A. N.A. N.A. N.A.  ANALYMAX 4.0/5.3 ? ? 4.0/5.3 ?  Aragon 8.0 N.A. N.A. N.A. N.A. N.A.  Ext as Glyphs/Second  I1/LCG-30ns 150k 50k 170k 95k 95k  I1/LCG-35ns 130k 40k 150k 85k 85k  I1/PVAX1 170k N.A. N.A. N.A. N.A. N.A.  IXII/PVAX1 170k N.A. N.A. N.A. N.A. N.A. N.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Dragon               | 8                  | N.A.                | N.A.     | N.A.              | N.A.    |  |

| CG-35ns 15 5 52 12 40  /AX1 20 N.A. N.A. N.A. N.A. N.A.  canProc  MAX 4.0/5.3 ? ? 4.0/5.3 ?  ragon 8.0 N.A. N.A. N.A. N.A. N.A.  cxt as Glyphs/Second  c11/LCG-30ns 150k 50k 170k 95k 95k  c11/LCG-35ns 130k 40k 150k 85k 85k  c11/PVAX1 170k N.A. N.A. N.A. N.A. N.A.  c11/Dragon 25k N.A. N.A. N.A. N.A. N.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Move Area/Scro       | ll as Million      | Pixels Per Second   |          |                   |         |  |

| /AX1 20 N.A. N.A. N.A. N.A. N.A. SanProc MAX 4.0/5.3 ? ? 4.0/5.3 ? ragon 8.0 N.A. N.A. N.A. N.A. N.A. N.A.  ext as Glyphs/Second  ###################################                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | LCG-30ns             | 18                 | 6                   | 60       | 15                | 50      |  |

| ### San Proc ### A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LCG-35ns             | 15                 | 5                   | 52       | 12                | 40      |  |

| ragon 8.0 N.A. N.A. N.A. N.A. N.A. N.A.  ext as Glyphs/Second  ###################################                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PVAX1<br>ScanProc    | 20                 | N.A.                | N.A.     | N.A.              | N.A.    |  |

| ext as Glyphs/Second  11/LCG-30ns 150k 50k 170k 95k 95k  11/LCG-35ns 130k 40k 150k 85k 85k  11/PVAX1 170k N.A. N.A. N.A. N.A. N.A.  11/Dragon 25k N.A. N.A. N.A. N.A. N.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PMAX                 | 4.0/5.3            | ?                   | ?        | 4.0/5.3           | ?       |  |

| 11/LCG-30ns 150k 50k 170k 95k 95k 11/LCG-35ns 130k 40k 150k 85k 85k 85k 11/PVAX1 170k N.A. N.A. N.A. N.A. N.A. N.A. N.A. N.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Dragon               | 8.0                | N.A.                | N.A.     | N.A.              | N.A.    |  |

| 111/LCG-35ns 130k 40k 150k 85k 85k 85k 11/PVAX1 170k N.A. N.A. N.A. N.A. N.A. N.A. N.A. N.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Text as Glyphs/      | Second             |                     |          |                   |         |  |

| 11/PVAX1 170k N.A. N.A. N.A. N.A. N.A. N.A. N.A. N.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9x11/LCG-30ns        | 150k               | 50k                 | 170k     | 95k               | 95k     |  |

| r11/Dragon 25k N.A. N.A. N.A. N.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9x11/LCG-35ns        | 130k               | 40k                 | 150k     | 85k               | 85k     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9x11/PVAX1<br>SP     | 170k               | N.A.                | N.A.     | N.A.              | N.A.    |  |

| A. = Not Applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9x11/Dragon          | 25k                | N.A.                | N.A.     | N.A.              | N.A.    |  |

| · • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | N.A. = Not Applic    | able               |                     |          | -                 |         |  |

Need the graphics performance for managing large off-screen images for both Scan Proc and Dragon. The bottleneck here will be swapping the image in and out of the frame buffer, even when updating a relatively few pixels, such as a vertical line.

# 3 PVAX2/PMariah Memory System

The memory controller consists of a state machine, multiplexers, and parity generation and checking. The types of operations supported are reads, writes (VRAM bit masked and non-masked), and read-modify-writes with naturally aligned data sizes: longword, quadword, and octaword. All graphics primitives are broken up into one of these operations and presented to the memory controller.

# 3.1 Memory Controller State Machine

This state machine controls all of the Memory address, control, and data, as well as, the MV\_DAL timing. The Memory Controller State Machine receives all requests from the Memory Arbitration Priority Encoder within the Flow Control State Machine. The request will consist of:

- Requester ID (Video, NI, SCSI, CPU, or Graphics)

- Memory Access Type (Read, Write, Read-Modify-Write, Video Shift Register Load (Full and Split), and Memory Refresh)

- Access Size (Longword, Quadword, Octaword with 16 individual Byte Masks)

The Memory Controller State Machine latches the appropriate address. The address bits indicate whether the access is to VRAM, DRAM, ROM, or an internal Register. The Memory Address Output Controller will feed back the memory state to the Memory Controller State Machine which describes the configuration of the memory. The state machine will acknowledge to the appropriate source that the address has been latched so that the master can get ready for generating the next request address.

When idle, the Priority Encoder within the Memory Arbitration will direct the highest priority access information to the Memory Controller and through an open latch directly to the Memory Address Output Controller. The Memory Address Multiplexer will be left in the RAS address selection mode. The Address will be decoded for the appropriate RASEN assertions. With this approach, the Memory State Machine can assert RAS on the very first cycle, knowing that the address set up and address decoding has already taken place. The Memory State Machine sets all of the control/data paths in the idle state as soon as possible at the end of each memory access. The minimum read latency is achieved this way.

The Memory Controller State Machine is clocked every 60 to 80 nsecs, depending on the actual SOC or Mariah cycle time. The Memory Controller sends control to the Memory Address Output Controller which clocks some signals every 30 to 40 nsecs. These signals will contain 2 bits per signal. The least significant bit will be clocked first and the most significant bit second. This scheme allows signal transitions to occur on any 30 to 40 nsec edge.

The state machine also controls the Pixel SLU when data is coming from memory, as well as, when to output it to memory. The parity checker sends the state machine and the requesting memory master 1 error bit.

Figure 3: Memory Controller State Machine Block Diagram

Figure 4: PVAX2/PMariah Memory System Block Diagram

Figure 5: DWT Memory System Block Diagram

# 3.2 Memory System Implementation Strategy

The memory system is designed to work with 60 nsec cycles. When the system clock is slowed down, obviously the memory slows down. The first number for memory timing below reflects the 60 nsec cycle. The second is the 70 nsec cycle for the SOC.

The conservative implementation is the 2-way interleaved 240/280 nsec memory cycle times with the 120/140 nsec page mode. The implementation will support up to octaword accesses which gives a maximum bandwidth of 38.1/32.1 Mbytes/sec for reads and 44.4/35.7 Mbytes/sec for writes.

The memory system interfaces to the MV\_DAL through 5 74F543 latched transceivers. Data read and written to main memory is latched in both directions. Memory is configured as a 64 bit memory with separate parity bits per byte. For quadword and octaword accesses, 2 32 bit banks are accessed in parallel with 1 RASEN asserted.

Read data is latched into the 74F543s as 2 longwords plus parity, then transferred 1 longword plus parity at a time to the S-Chip, LCG. The M-DAL cycle time is 60/70 nsecs. When accessing an octaword, the first quadword transfers to the S-Chip in 120/140 nsec in parallel with the next quadword page mode access. The second quadword transfers across the MV\_DAL while the read access is being terminated and the next access is beginning.

Write data is transferred 1 longword plus parity at a time on the MV\_DAL, latched into the 74F543s, then output as 2 longwords plus parity to the DRAMs. When writing an octaword, the first quadword plus parity will be valid for 60/70 nsecs. The second quadword is transferred in parallel with the first quadword write and latched into the 74F543s starting 60/70 nsec after the last longword of the first quadword is assembled.

### 3.3 Memory Arbitration and Flow Control

The memory arbitration logic prioritizes requests and sets up the required information for the memory controller state machine and associated logic so that when one request is finished, the next memory access can occur immediately afterwards.

The memory arbitration and flow control communicates with all memory requesters for accepting and acknowledging requests. It also directs the octaword graphics data buffer, plane mask, and the Pixel SLU from information supplied by incoming requests, the memory controller state machine, and the graphics address generator. The arbitration and flow control also directs the reading and writing of all internal registers.

The memory state machine must also be involved with accessing the optional Scan Proc graphics which is only accessed in a program I/O environment.

# 3.3.1 Memory Request Prioritiy

The low cost graphics controller is last on the priority list. It is effectively a background task. When graphics primitives are present, then it takes up all spare memory cycles. The priority of requests serviced are:

- 1. Video Controller:

- Video Shift Register Load

- Cursor Buffer Load Octaword read = 64 x 2 planes

- Memory Refresh

- 2. NI Controller

- 3. CPU Port

- 4. SCSI Controller

- 5. Graphics Address Generator

# 3.4 Memory Address Output Controller

The Memory Address Output multiplexer selects between the Address In bus, Address Generator, and Video Address for shift register loads and memory refreshes. This section also outputs the address and control signals needed to control both main memory and the frame buffer.

The physical addresses will be multiplexed to output latches. The multiplexing will take care of the different configured memory components.

| RAM Configuration                       | Address Bits |

|-----------------------------------------|--------------|

| ======================================= | ==========   |

| 4Mx1 bit DRAMs                          | 11           |

| 1M bit DRAMs                            | 10           |

| 256kx4s VRAMs                           | 9            |

| 128kx8s VRAMs                           | 9            |

This section also contains a control register which signals the Memory Control State Machine of the configuration and memory type: DRAM or VRAM, as well as, whether the frame buffer is color or monochrome.

There is a 1 bit counter used for the least significant bit of the CAS address for incrementing the counter for page mode accesses: octaword.

All Memory Error and Configuration Registers reside in the section.

# 3.5 CPU Write Buffering Mechanism for LCG

The CPU write buffers up to a quadword for writes to main memory, the Command FIFO, and the frame buffer.

The Command FIFO is is mapped to a 256k byte I/O address space: 20180000 to 201FFFFF.

The Frame Buffer address space is mapped as 32M bytes: 21000000 to 22FFFFF. The bottom 16M bytes, 21000000 to 21FFFFFF, are CPU write buffered and the top 16M bytes, 22000000 to 22FFFFFF, are treated as I/O writes which flush the write buffer. LCG Register, 20100000 to 2013FFFF, writes are also considered I/O writes and also flush the write buffer.

### 3.5.1 LCG Command FIFO Mechanism

The Graphics interface is Command Packet oriented, versus a typical register address interface. The Command Packets contain an Opcode, Opcode specific flags, and parameters. The first longword of a command also contains 2 bits which indicate the number of additional longwords used for this command packet. The command opcode is be decoded for determining which registers are to be loaded.

The benefit of this FIFO mechanism is that since it takes between 1 and 4 longwords per command packet and up to 3 command packets per graphics operation, writing the LCG Command FIFO is a major memory bandwidth consideration.

When the Graphics System is busy, CPU writes to the Command FIFO are directed to the Command FIFO ring buffer in main memory. The CPU interface supplies the access size, byte mask, and within an octaword address<3:2>. The Command FIFO supplies the octaword address.

The LCG Command FIFO always reads an octaword of data from memory. If all longwords are required, then the appropriate LCG registers are loaded as the data is read from memory. The LCG Command FIFO read buffer is 3 longwords in size and it stores the unused longwords. These residue longwords are used on the next command and are not re-read from memory.

When the Command FIFO read buffer is empty and the Address Generator is busy (performing the graphics primitive), then the Command FIFO waits until the Busy signal is deasserted before posting the next memory read. The Busy signal deasserts before it finishes its last memory access, but after being granted a successful memory reference. This timing makes sure that the Command FIFO receives the next memory access cycle, depending on its priority level (last other than the LCG Address Generator).

When ever the Clip List is disabled, the LCG Command FIFO is empty, and LCG AG is Not Busy, then data destined for the Command FIFO is written to the LCG internal registers. Only the longwords required for a complete graphics primitive are written to the internal registers. The remaining longwords are stored within the Command FIFO Residue Buffer. If LCG AG is busy and there is room in the residue buffer, then data is stored in the Residue Buffer. Otherwise, the data is written to memory. This mechanism is called "short circuit".

The clipping rectangle hardware will allow the hardware to clip the drawing primitives to overlapping windows. A clip list can be specified in lieu of immediate clip data. When the clip list feature is active, each primitive will be clipped to each rectangle in the list. The clip list can be anywhere in contiguous main memory, but may not span a 64k byte boundary.

When the Clip List is enabled, then the data will always be written to the Command FIFO no matter if it is empty and/or the LCG is idle. It will also be stored within the LCG internal registers and/or Residue Buffer if the appropriate conditions dictate. The Command can be read multiple times and clipped to multiple rectangles.

There are programmable threshold interrupts available for both Command FIFO full and empty. This is for tuning the Server/LCG interface for stopping the FIFO writes before overflowing the FIFO and waking up the Server when the FIFO gets to an empty threshold. An interrupt will be sent whenever the threshold is reached and the interrupt enable is asserted.

The Command FIFO ring buffer wraps on it programmed size: 64k, 32k, or 16k bytes. The Clip List is also modulo 64k bytes and if it wraps, then it is considered an error. An interrupt will be sent to the CPU whenever the Clip List wraps.

# 3.6 Address Generator Interface, Virtual Translation, Graphics Interrupts, & Debug HW

All Address Generator requests and grants go through this section because of the Virtual Translations and debug hardware. Command FIFO, Clip List, Virtual Translation, and Address Generator operand requests are all funneled down to 1 request bit, access type, access size, and an ID tag which is forwarded to the memory arbitrator in the Flow Control state machine. The ID tag is transmitted on the Flow Control Bus during the memory or register access and signals the appropriate master that its request is being serviced.

# 3.6.1 Virtual Memory

The Virtual Translation supports supports 3 translation buffer entries with the base address of the page table pages. There is 1 set of translation buffer latches for each of the three operands for rasterops. The translation buffer entries are: destination, source, and stencil. With this hardware, LCG can now draw graphics primitives to any scattered portion of main memory. This allows the Pixel Maps to reside on the disk until accessed by the graphics system.

The Virtual Translation mechanism reads its page table entries from the Server's P0 page table. Checking is performed on the Valid Bit for both levels of translation, as well as, the access mode (User Write) and the modify bit (on writes) in the second level translation. A maximum virtual address check is also performed. If any faults are found, then the CPU is interrupted with the appropriate status available.

The performance will degrade, depending on the number of page crossings and the number of times that the physical address must be read from memory. Vertical vectors are the worst case; crossing a page boudary on every access. Horizontal vectors and Rasterops are much better since memory is accessed in contiguous byte accesses.

Neither the Command FIFO nor the Clip List are virtual. They must be contained in contiguous physical memory.

# 3.6.1.1 Virtual Memory Interface Overview

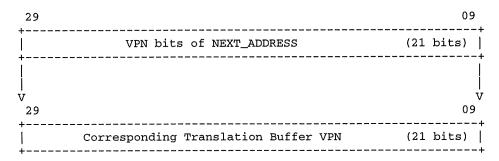

There are 3 Virtual Address latches for comparison with the address generator's 3 operand addresses. One latch is used for Vectors and Destination operands. A second latch is used for all 2 operand primitives. The third latch is used for the stencil operand. The address generator's addresses are 28 bits wide (bits<1:0> are ignored), but the least significant 7 bits (address<8:2>) are used for within a page. Address<29:09> are required for comparison.

Bits <29:09> of the operand's virtual address is compared with the corresponding Virtual Graphics Operand Address Latch for deciding whether the corresponding Physical Graphics Operand Address latch contains the correct physical address. The comparison is accomplished in 2 parts. Bits <29:15> indicate whether the current Process Page Table Page Address latch contains the correct page address. When this portion of the compare is true, but bits <14:09> fail, then the current Process Page Table Base Address latch contains the correct Page Table Base address. For this case, bits <14:09> are used to index into the Page Table Page for accessing the correct PFN.

When bits <29:15> of the virtual address and bits <20:06> of the Virtual Graphics Address latch comparison fails, then the P0 System Base Address latch is added to bits <29:15> of the virtual address for obtaining the correct Process Page Table Page Base Address. This

results in a double lookup and a length check for accessing the correct PFN. The P0 System Length Latch is also compared against the Operand's Virtual Address.

Whenever a miss occurs and the PFN is successfully loaded, then the Operand's virtual address will be loaded into the corresponding Virtual Graphics Operand Address Comparison Latch. When the Valid bit is deasserted on either access, an interrupt is generated and the virtual address may be accessed by the CPU. All drawing will suspend, until the CPU corrects the situation and restarts the Address Generator.

Cache Coherency is garenteed by the Invalidate TB mechanism. VMS writes an LCG I/O address which flushes all cached translation buffer entries whenever it has potentially modified one of the DECWindow Server's PFNs.

#### 4 Pseudo-code for LCG VM Translations

Assume the following constraints on the page table data structures and the manipulations on them:

- The system page table is physically resident and contiguous.

- 2) The process P0 page table resides in virtually contiguous system address space. Therefore, the system page table entries which map the P0 page table are physically contigous.

- 3) The PO page table is page-aligned.

- 4) No page of the process P0 page table can become non-resident without its constituent PTE's first becoming invalid.

- 5) The system virtual address of the process header (i.e. the PO page table) can be prevented from moving.

- 6) The process can be prevented from shrinking below LCG\_POLR

Assume the existence of the following registers ("XX" stands for one of {source,stencil,dest}):

### LCG\_PA\_S\_P0BR<26:2>

Physical address of the system page table entry which maps the first page of the process P0 page

The SPTE pointed at by LCG\_PA\_S\_POBR maps the address contained in the VAX POBR register.

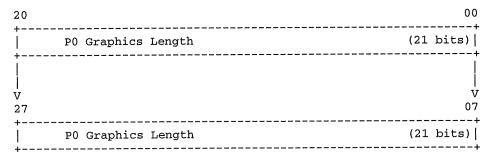

#### LCG\_P0LR<29:9>

P0 length register.

The P0 virtual address of the highest mapped page.

#### LCG\_NEXT\_VA<29:0>

The next address to be accessed by LCG. This will be the virtual address to be translated if the operand is virtual.

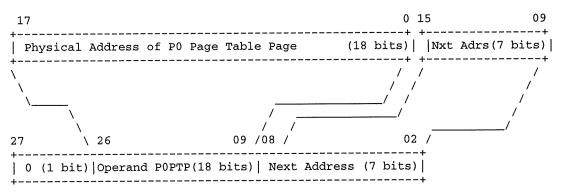

#### LCG\_XX\_PA\_P0PTP<26:9>

For each of the 3 LCG operands: the physical address of CURRENT PO page table page. That is, the address of the page table page containing the PTE for LCG\_XX\_VPN.

#### LCG\_XX\_VPN<29:9>

The virtual page number associated with LCG\_XX\_PFN. This is the same as <29:9> of the most recently translated address.

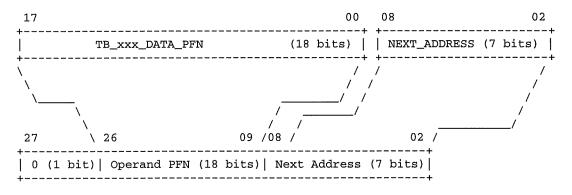

#### LCG\_XX\_PFN<26:9>

The page frame number associated with LCG\_XX\_VPN. In other words, physical address bits <26:9> of the most recently translated address.

Further assume the following symbols which are used below to identify intermediate values.

#### PA SPTE

The physical address of the system page table entry which maps the desired PO page table page.

### PA\_POPTE

The physical address of the process page table entry which maps the virtual address.

#### LCG\_NEXT\_PA

The translated address corresponding to LCG\_NEXT\_VA.

#### SETUP:

The following registers must be loaded by the server:

LCG\_PA\_S\_POBR must be loaded with the physical address of the SPTE which maps the first page of POPT.

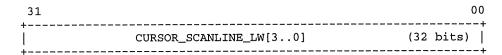

LCG\_POLR must be loaded with the highest virtual address which is to be accessed by LCG.