# **Technical Manual**

# FUNDAMENTALS OF MINI-COMPUTER HARDWARE

015-000022-02

# DATA GENERAL TECHNICAL MANUAL

# FUNDAMENTALS OF MINI-COMPUTER HARDWARE

Ordering No. 015-000022 ©Data General Corporation 1972, 1973, 1974 All Rights Reserved. Printed in the United States of America Rev. 02, January 1974

| A STATE OF THE PROPERTY OF THE | NUMBER SYSTEMS                        | I            |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|---|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ARITHMETIC OPERATIONS                 | П            |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LOGIC AND LOGIC CONVENTIONS           | ш            | • |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | COMPUTER ORGANIZATION                 | IV (         |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INSTRUCTION SET- MEMORY REFERENCE     | ⊻ (          |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ARITHMETIC LOGICAL INSTRUCTIONS (ALC) | <b>V</b>     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INPUT-OUTPUT (10) INSTRUCTION         | VII (        |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PROGRAM INTERRUPT AND DATA CHANNEL    | <b>∑</b> Ш € |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CONSOLE                               | IX •         |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |              |   |

BASIC PROGRAMMING AND PROGRAMS

#### NOTICE

The materials contained herein are proprietary to Data General Corporation (DGC) and have been prepared solely for use in DGC training Courses. No other use of the materials for any other purpose, including but not limited to the sale or manufacture of any of the items described, shall be made without DGC's written permission. Reproduction of this material in whole or in part is subject to DGC's prior written permission.

This publication was prepared by the Data General Corporation Education Department. It is intended to supplement the material presented in Data General's Fundamentals of Mini-Computer Hardware Course. PJS 2/74

Any comments concerning this publication should be forwarded to:

Education Department Data General Corporation Route 9 Southboro, MA. 01772

# TABLE OF CONTENTS

# SECTION I

# NUMBER SYSTEMS

|                                                                                                                                  | Pag                                    |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| SYSTEM BASES                                                                                                                     | 1 - 1<br>1 - 1                         |

| RADIX POINT                                                                                                                      | 1-1                                    |

| NUMBER SYSTEM CONVERSIONS  Binary to Decimal Octal to Decimal Decimal to Binary Decimal to Octal Binary to Octal Octal to Binary | 1-2<br>1-2<br>1-2<br>1-2<br>1-4<br>1-4 |

| SECTION II                                                                                                                       |                                        |

| ARITHMETIC OPERATIONS                                                                                                            |                                        |

| ADDITION                                                                                                                         | 2-1<br>2-1<br>2-2                      |

| SUBTRACTION                                                                                                                      | 2-2<br>2-2<br>2-5<br>2-5               |

| MULTIPLICATION-BINARY                                                                                                            | 2-5                                    |

| DIVISION-BINARY                                                                                                                  | 2-6                                    |

| LOGICAL AND                                                                                                                      | 2-6                                    |

| LOGICAL OR                                                                                                                       | 2-7                                    |

| LOGICAL EXCLUSIVE OR                                                                                                             | 2-7                                    |

| SIGNED NUMBER REPRESENTATION Sign Bit Definition Range of Signed Numbers                                                         | 2-8<br>2-8<br>2-9                      |

| SECTION III                                                                                                                      |                                        |

| LOGIC AND LOGIC CONVENTIONS                                                                                                      |                                        |

| GENERAL                                                                                                                          | 3-1                                    |

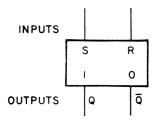

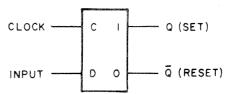

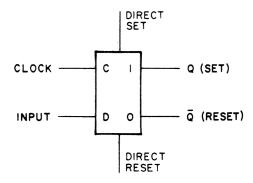

| LOGIC GATES AND Gate OR Gate XOR Gate Multiple Input Gates Flip-flops                                                            | 3-2<br>3-2<br>3-2<br>3-3<br>3-4<br>3-4 |

# TABLE OF CONTENTS (Continued)

# SECTION III (Continued)

# LOGIC AND LOGIC CONVENTIONS

|                                                                                                          | Page                                                 |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------|

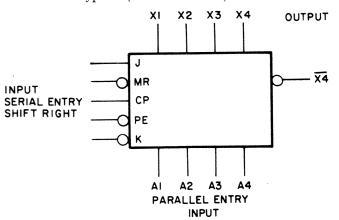

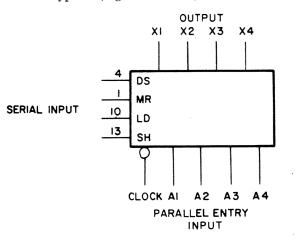

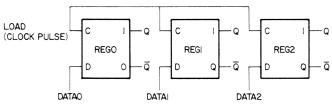

| Inverters Multiplexer Registers Four Bit Shift Register                                                  | 3-6<br>3-6<br>3-6<br>3-10                            |

| SECTION IV                                                                                               |                                                      |

| COMPUTER ORGANIZATION                                                                                    |                                                      |

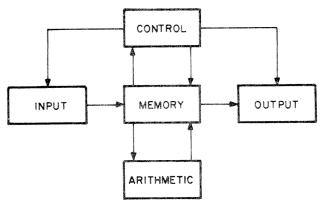

| DEFINITIONS                                                                                              | 4-1                                                  |

| COMPUTER ORGANIZATION                                                                                    | 4-2                                                  |

| I/O SECTION - INPUT/OUTPUT                                                                               | 4-4                                                  |

| MAJOR REGISTERS  CPU Hardware Registers                                                                  | 4-5<br>4-5<br>4-6                                    |

| MAJOR STATES                                                                                             | 4-6<br>4-6<br>4-6                                    |

| TIME STATES                                                                                              | 4-7                                                  |

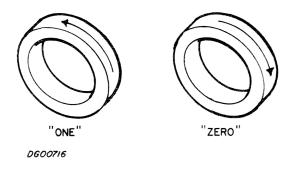

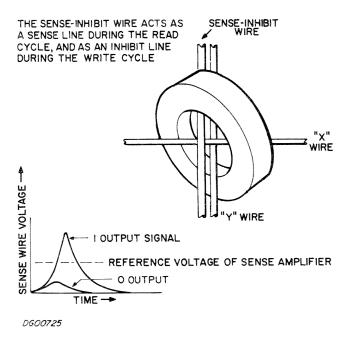

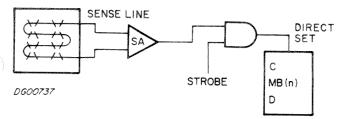

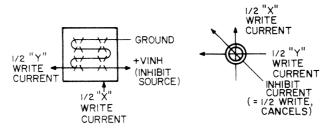

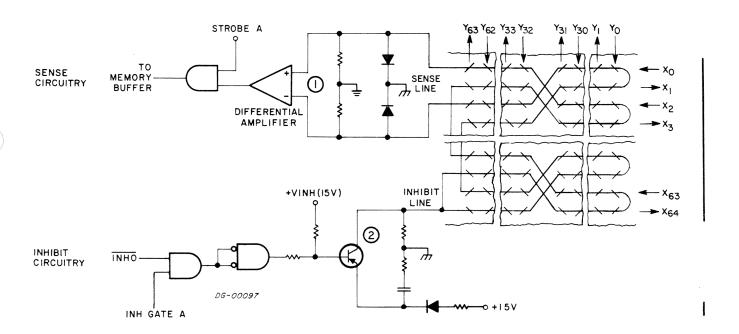

| MEMORY  Magnetic Core Theory  Definitions  Description  Read  Sense Line  Write                          | 4-7<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11             |

| SECTION V                                                                                                |                                                      |

| INSTRUCTION SET - MEMORY REFERENCE                                                                       |                                                      |

| GENERAL                                                                                                  | 5-1                                                  |

| INSTRUCTION WORD AND ADDRESSING  Decoding Cycles Addressing Modes Page Zero Mode Relative Mode Base Mode | 5-1<br>5-1<br>5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-2 |

| MEMORY REFERENCE INSTRUCTIONS                                                                            | 5-2                                                  |

| EXECUTION                                                                                                | 5-4                                                  |

# TABLE OF CONTENTS (Continued)

# SECTION V (Continued)

# INSTRUCTION SET - MEMORY REFERENCE

|                                                                                                                                                         | Pag                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| INDIRECT ADDRESSING  General  Defer Cycle  Multi-Level Defer                                                                                            | 5-4<br>5-4<br>5-4<br>5-4                      |

| AUTO INDEX, DECREMENT Auto Index (Increment) Auto Decrement                                                                                             | 5-5<br>5-5<br>5-5                             |

| SECTION VI                                                                                                                                              |                                               |

| ARITHMETIC LOGICAL INSTRUCTIONS (ALC)                                                                                                                   |                                               |

| GENERAL                                                                                                                                                 | 6-1                                           |

| INSTRUCTION WORD AND DECODING                                                                                                                           | 6-1                                           |

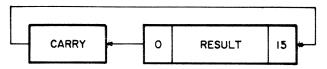

| SECONDARY OPERATIONS  Load Modes  Load Shifted Left  Load Shifted Right  Load Swap.  Carry and Carry Base  ALC Skips  ALC INSTRUCTION WORD  SECTION VII | 6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3<br>6-4 |

| INPUT-OUTPUT (IO) INSTRUCTION                                                                                                                           |                                               |

| GENERAL                                                                                                                                                 | 7-1                                           |

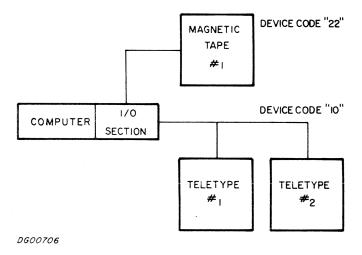

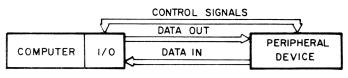

| INSTRUCTIONS IO Pulses Device Codes Typical Device Flags                                                                                                | 7-1<br>7-1<br>7-1<br>7-2                      |

| INSTRUCTION DESCRIPTION                                                                                                                                 | 7-2                                           |

| PROGRAMMING EXAMPLES                                                                                                                                    | 7-4<br>7-5                                    |

| CPU IO INSTRUCTIONS                                                                                                                                     | 7-5                                           |

# TABLE OF CONTENTS (Continued)

# SECTION VIII

# PROGRAM INTERRUPT AND DATA CHANNEL

|                                                 |                                | Page                                                 |

|-------------------------------------------------|--------------------------------|------------------------------------------------------|

| General                                         | e                              | 8-1<br>8-1<br>8-1<br>8-1<br>8-2<br>8-2<br>8-2<br>8-2 |

| Modes                                           |                                | 8-3                                                  |

|                                                 | SECTION IX                     |                                                      |

|                                                 | CONSOLE                        |                                                      |

| GENERAL                                         |                                | 9-1                                                  |

| REGISTERS                                       |                                | 9-1<br>9-1<br>9-1<br>9-1                             |

| Switches                                        |                                | 9-1<br>9-1<br>9-1                                    |

|                                                 | SECTION X                      |                                                      |

|                                                 | BASIC PROGRAMMING AND PROGRAMS |                                                      |

| GENERAL                                         |                                | 10-1                                                 |

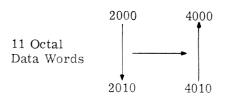

| Binary Loader                                   |                                | 10-1<br>10-2<br>10-3                                 |

| NOVA DIAGNOSTIC PROGR<br>Sample Diagnostic Loop | AAMS                           | 10-3<br>10-3                                         |

| APPENDICES                                      |                                |                                                      |

| A GLOSSAR                                       | Y OF TERMS AND DEFINITIONS     | A-1                                                  |

| B ABBREVI                                       | ATIONS                         | B-1                                                  |

| C REFERE                                        | NCES                           | C-1                                                  |

# LIST OF ILLUSTRATIONS

| Figure | Title                                             | Pag  |

|--------|---------------------------------------------------|------|

| 3-1    | Printed Circuit Board                             | 3-1  |

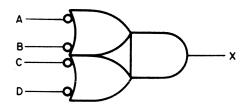

| 3-2    | Logic Diagram                                     | 3-2  |

| 3-3    | Logic Chart                                       | 3-3  |

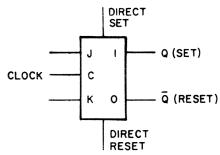

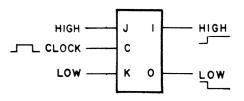

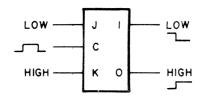

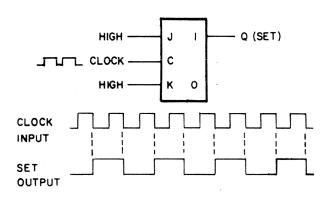

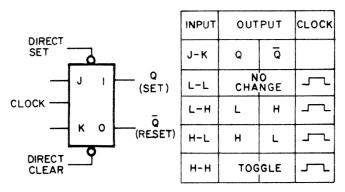

| 3-4    | Flip-flop                                         | 3-4  |

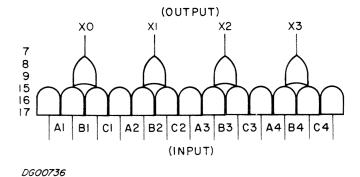

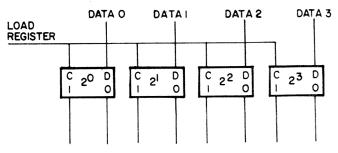

| 3-5    | Basic Register                                    | 3-6  |

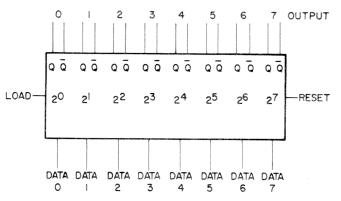

| 3-6    | Register Containing 8 Flip-flops                  | 3-7  |

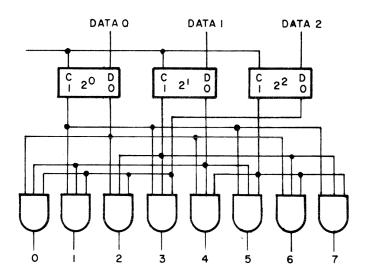

| 3-7    | Decoded Register                                  | 3-7  |

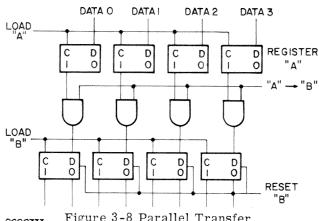

| 3-8    | Parallel Transfer                                 | 3-7  |

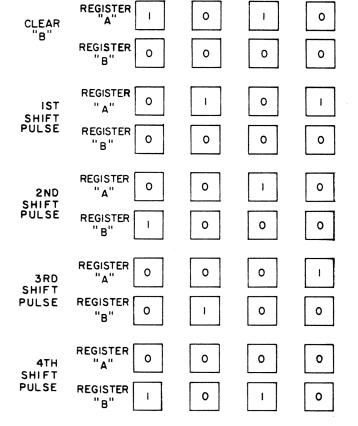

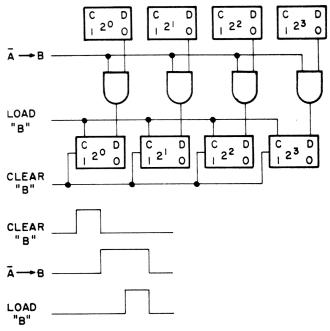

| 3-9    | Serial Transfer                                   | 3-7  |

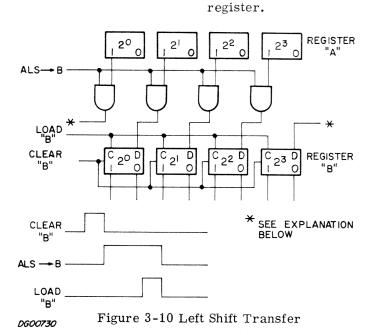

| 3-10   | Left Shift Transfer                               | 3-8  |

| 3-11   | Right Shift Transfer                              | 3-9  |

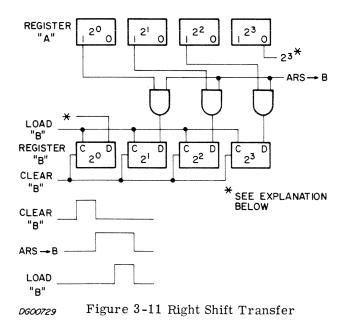

| 3-12   | Complement Transfer                               | 3-10 |

| 4-1    | A 16 bit Word                                     | 4-1  |

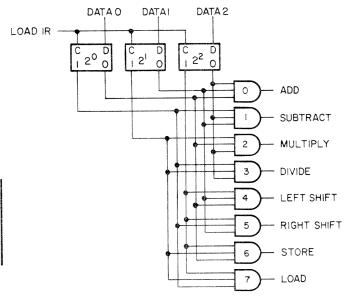

| 4-2    | Instruction Register Decoding                     | 4-2  |

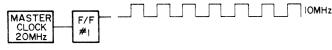

| 4-3    | Master Clock                                      | 4-2  |

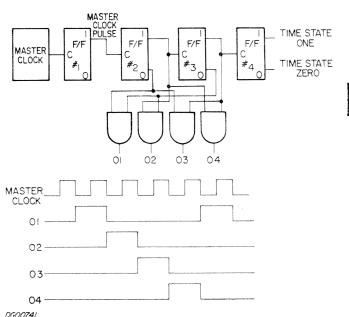

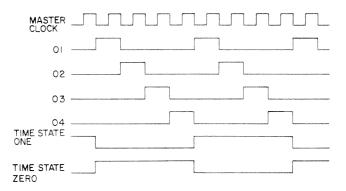

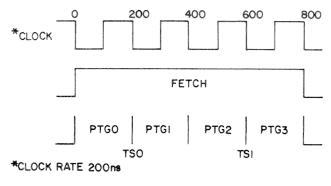

| 4-4    | Master Clock, Phase Timing, and Time State Timing | 4-2  |

| 4-5    | Bit Register                                      | 4-5  |

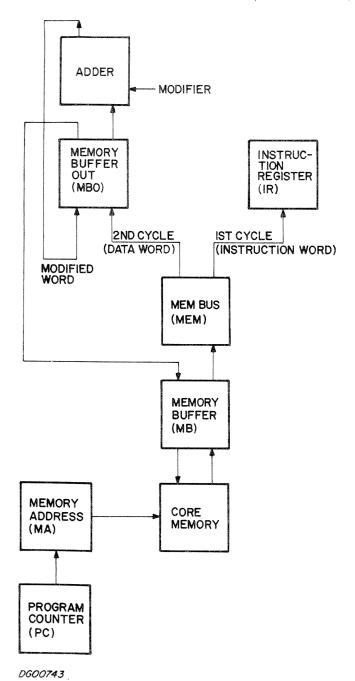

| 4-6    | Register Interrelation                            | 4-6  |

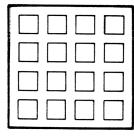

| 4-7    | Core Mat with 16 Planes                           | 4-9  |

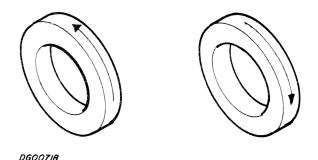

| 4-8    | Core Mountings                                    | 4-9  |

| 4-9    | Core Plane                                        | 4-9  |

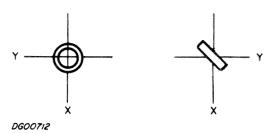

| 4-10   | Address Selection                                 | 4-9  |

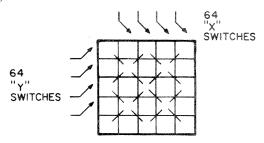

| 4-11   | X and Y Switches                                  | 4-10 |

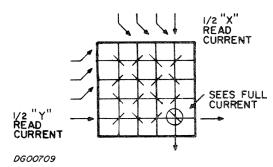

| 4-12   | Read Currents                                     | 4-10 |

| 4-13   | Sense Line and Amplifier                          | 4-11 |

| 4-14   | Write and Inhibit Currents                        | 4-11 |

| 5-1    | IR Bits 6-15 Breakdown                            | 5-1  |

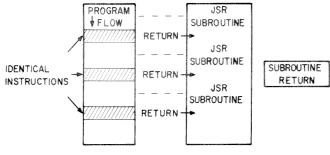

| 5-2    | Subroutine Principles                             | 5-3  |

| 6-1    | ALC Decoding                                      | 6-1  |

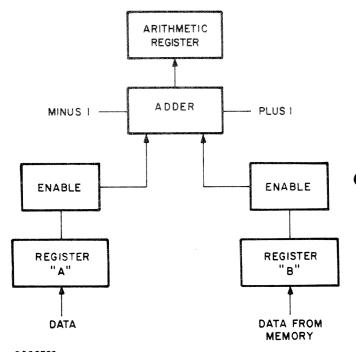

| 6-2    | Adder Concept (ADD 3,2)                           | 6-5  |

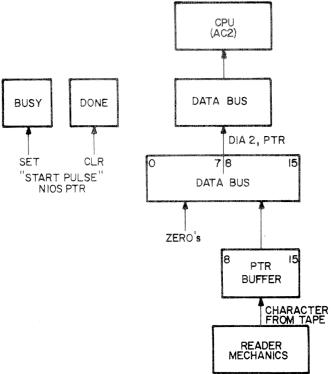

| 7-1    | Done and Busy Flip-flops                          | 7-2  |

| 7-2    | Paper Tape Reader I/O Controls                    | 7-5  |

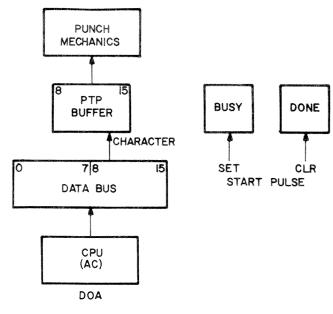

| 7-3    | Paper Tape Punch I/O Control                      | 7-5  |

| 7-4    | CPU I/O Instruction Decode                        | 7-6  |

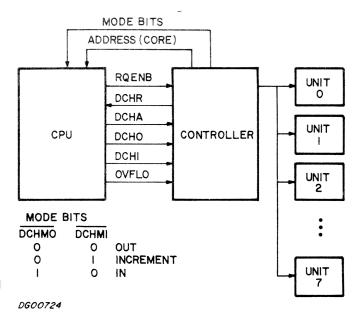

| 8-1    | Data Channel Signal Transfer                      | 8-3  |

This page intentionally left blank

#### SECTION I

#### NUMBER SYSTEMS

10

| SISIEM BASES                                           |    |        | _    |     | _  | 10  |

|--------------------------------------------------------|----|--------|------|-----|----|-----|

|                                                        | 30 | 11110  | 1010 | 132 | 36 | 1E  |

| Radix                                                  | 31 | 11111  | 1011 | 133 | 37 | 1 F |

|                                                        | 32 | 100000 | 1012 | 200 | 40 | 20  |

| To introduce the concept of number systems, look       | 33 | 100001 | 1020 | 201 | 41 | 21  |

| first at that number system most familiar to us,       | 34 | 100010 | 1021 | 202 | 42 | 22  |

| the decimal number system. The decimal number          | 35 | 100011 | 1022 | 203 | 43 | 23  |

| system contains ten (10) different symbols             | 36 | 100100 | 1100 | 210 | 44 | 24  |

| (0, 1, 2, 3, 4, 5, 6, 7, 8, 9), thus it is base 10, or | 37 | 100101 | 1101 | 211 | 45 | 25  |

| radix 10.                                              | 38 | 100110 | 1102 | 212 | 46 | 26  |

|                                                        | 39 | 100111 | 1110 | 213 | 47 | 27  |

| In this same manner, it is possible to define a        | 40 | 101000 | 1111 | 220 | 50 | 28  |

|                                                        |    |        |      |     |    |     |

In this same manner, it is possible to define a multitude of number systems by simply specifying a new base or radix. For examples, a number system with the base 5 would contain 5 symbols (0,1,2,3,4). A radix 16 number system would contain 16 symbols (0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F). It is insignificant that alphabetical characters are used as the additional symbols. The significance of the symbols is their relative position in the complete set. It is the position which determines the actual value of the symbol, not the symbol itself.

CVCTEM DACEC

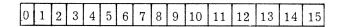

It should be evident, from the following table, how counting would proceed in various number systems.

| RADIX: | <u>10</u> | <u>2</u> | 3    | 4   | 8  | 16           |

|--------|-----------|----------|------|-----|----|--------------|

|        | 0         | 0        | 0    | 0   | 0  | 0            |

|        | 1         | 1        | 1    | 1   | 1  | 1            |

|        | 2         | 10       | 2    | 2   | 2  | 2            |

|        | 3         | 11       | 10   | 3   | 3  | 3            |

|        | 4         | 100      | 11   | 10  | 4  | 4            |

|        | 5         | 101      | 12   | 11  | 5  | 5            |

|        | 6         | 110      | 20   | 12  | 6  | 6            |

|        | 7         | 111      | 21   | 13  | 7  | 7            |

|        | 8         | 1000     | 22   | 20  | 10 | 8            |

|        | 9         | 1001     | 100  | 21  | 11 | 9            |

|        | 10        | 1010     | 101  | 22  | 12 | A            |

|        | 11        | 1011     | 102  | 23  | 13 | В            |

|        | 12        | 1100     | 110  | 30  | 14 | C            |

|        | 13        | 1101     | 111  | 31  | 15 | D            |

|        | 14        | 1110     | 112  | 32  | 16 | $\mathbf{E}$ |

|        | 15        | 1111     | 120  | 33  | 17 | $\mathbf{F}$ |

|        | 16        | 10000    | 121  | 100 | 20 | 10           |

|        | 17        | 10001    | 122  | 101 | 21 | 11           |

|        | 18        | 10010    | 200  | 102 | 22 | 12           |

|        | 19        | 10011    | 201  | 103 | 23 | 13           |

|        | 20        | 10100    | 202  | 110 | 24 | 14           |

|        | 21        | 10101    | 210  | 111 | 25 | 15           |

|        | 22        | 10110    | 211  | 112 | 26 | 16           |

|        | 23        | 10111    | 212  | 113 | 27 | 17           |

|        | 24        | 11000    | 220  | 120 | 30 | 18           |

|        | 25        | 11001    | 221  | 121 | 31 | 19           |

|        | 26        | 11010    | 222  | 122 | 32 | 1A           |

|        | 27        | 11011    | 1000 | 123 | 33 | 1B           |

|        | 28        | 11100    | 1001 | 130 | 34 | 1C           |

|        | 29        | 11101    | 1002 | 131 | 35 | 1D           |

The radix 10 number is more generally known as the decimal number system. Similar nomenclature is used for other number systems.

| <u>Radix</u> | Nomenclature |

|--------------|--------------|

|              |              |

| 10           | Decimal      |

| 2            | Binary       |

| 8            | Octal        |

| 16           | Hexadecimal  |

The binary number system (radix 2) contains 2 symbols (0,1). This has special significance since most physical devices have 2 states, and each state can be represented by one of the binary symbols. For example, a switch has 2 states: OFF (0) and ON (1); a door has 2 states: CLOSED (0) and OPEN (1); numbered areas on a computer card have 2 states: NO HOLE (0) and HOLE (1); small areas on magnetic tape have 2 states: NOT MAGNETIZED (0) and MAGNETIZED (1). It is for this reason that the binary number is so widely used in computers.

In order to indicate which number system is being used, the radix is subscripted at the end of the number. For example, the decimal number 179.65 would be written as 179.65<sub>10</sub>; the octal number 734.26, as 734.26<sub>8</sub>; and the binary number 1011.01101 would be written as 1011.01101<sub>2</sub>.

#### RADIX POINT

It has been shown how integer numbers (whole numbers, nonfractional numbers, etc.) are represented in various number systems. In the decimal number system, the fractional portion of a number is separated from the integer portion by a decimal point (ex: 123.24). This form of separation is used in all the number systems. In general, the point is called the radix point. In the decimal number system, it is referred to as the decimal point; in the binary number system as the binary point; and in the octal number system as the octal point.

An example of fractional numbers in different number systems is shown:

| Radix | <u>Example</u>    |

|-------|-------------------|

| 2     | 10001101.01001101 |

| 3     | 10200121.21102    |

| 8     | 7536.0214         |

| 10    | 8930.6345         |

#### NUMBER SYSTEM CONVERSIONS

Binary to Decimal

Consider the number 214<sub>10</sub>. This notation is shorthand for

$$4x1 = 4

1x10 = 10

2x100 = 200

214$$

In the decimal number system, this seems redundant, but it demonstrates the technique for converting a number of any radix to its decimal equivalent. In general, every number will have the following format:

$$\dots a_4 a_3 a_2 a_1 a_0 a_{-1} a_{-2} a_{-3} \dots R$$

where  $a_x$  is the value of the digit, the subscript of a is the digit's position relative to the radix point, and R is the radix of the number. The following formula is used to convert any number to its decimal equivalent:

$$\dots + (a_4 x R^4) + (a_3 x R^3) + a_2 x R^2) + (a_1 x R^1) + (a_0 x R^0) + \\ (a_{-1} x R^{-1}) + (a_{-2} x R^{-2}) + (a_{-3} x R^{-3}) + \dots = N_{10}$$

#### Example 1.1

Find N where

$$214.36_{10}=N_{10}$$

$$4x10^{0} = 4x1 = 4$$

$$1x10^{1} = 1x10 = 10$$

$$2x10^{2} = 2x100 = 200$$

$$3x10^{-1} = 3x.1 = .3$$

$$6x10^{-2} = 6x.01 = .06$$

#### Example 1.2

Find N where

$$1011. \ 01101_2 = N_{10}$$

$$1x2_1^0 = 1x1 = 1$$

$$1x2_2^1 = 1x2 = 2$$

$$0x2_3^2 = 0$$

$$1x2_{-1}^3 = 1x8 = 8$$

$$0x2_{-2}^{-1} = 0$$

$$1x2_{-3}^3 = 1x. \ 25 = .25$$

$$1x2_{-4}^3 = 1x. \ 125 = .125$$

$$0x2_{-5}^4 = 0$$

$$1x2_{-5}^5 = 1x. \ 03135 = .03125$$

$$11. \ 40625$$

$$1011.01101_2 = 11.40625_{10}$$

#### Octal to Decimal

A similar procedure is used to convert octal numbers to decimal numbers.

#### Example 1.3

$$1735.24_8 = 989.3125_{10}$$

#### Decimal to Binary

When converting a decimal number to a number in some other base, it is necessary to consider the integer portion (portion to the left of the decimal point) and the fractional portion (portion to the right of the decimal point) separately.

The procedure for converting the integer portion of a decimal number to some other radix R is as follows:

- Divide the integer by R, and separate the answer into a quotient and a remainder.

- 2. Record the remainder.

- 3. Divide the quotient by R, and separate the answer into another quotient and a remainder.

- 4. Repeat steps 2 and 3 until a quotient of 0 is obtained.

- Record the remainders in reverse order of their occurrence to form the converted number.

#### Example 1.4

Find N where

$17_{10} = N_2$

| Quotient                  | Remainder |     |

|---------------------------|-----------|-----|

| $\frac{2}{2}\frac{17}{8}$ | 1         | LSB |

| $2\sqrt{4}$               | 0         |     |

| $2\sqrt{2}$               | 0 🛉       |     |

| $2\sqrt{1}$               | 0         |     |

| 0                         | 1         | MSB |

$17_{10} = 10001_2$

#### Example 1.5

Find N where

$39_{10} = N_2$

| Quotient                       | Remainder |     |

|--------------------------------|-----------|-----|

| 2 /39                          |           |     |

| 2 / 19                         | 1         | LSB |

| $2\sqrt{9}$                    | 1         |     |

| $2\sqrt{4}$                    | 1         |     |

| 2 /2                           | 0 🛉       |     |

| $2 \left[ \frac{1}{2} \right]$ | 0         |     |

| 0                              | 1         | MSB |

The procedure for converting the fractional portion of a decimal number to some other radix R is as follows:

$39_{10} = 100111_2$

- 1. Multiply the fraction by R, and separate the answer into an integer and a fraction.

- 2. Record the integer.

- 3. Multiply the fraction by R, and separate the answer into another integer and a fraction.

- 4. Repeat steps 2 and 3 until a fractional answer of 0 is obtained.

- 5. Record the integer portion of the answers in the order of their occurrence to form the converted fraction.

# Example 1.6

Find N where  $.125_{10} = N_2$

| Integer                             |             | Fraction                |

|-------------------------------------|-------------|-------------------------|

| . 125x2=0<br>. 250x2=0<br>. 500x2=1 | +<br>+<br>+ | . 250<br>. 500<br>. 000 |

|                                     |             |                         |

$.125_{10} = .001_{2}$

#### Example 1.7

Find N where

$6_{10} = N_2$

| Integer                                             |                                  | Fraction                        |

|-----------------------------------------------------|----------------------------------|---------------------------------|

| . 6x2=1<br>. 2x2=0<br>. 4x2=0<br>. 8x2=1<br>. 6x2=1 | +<br>+<br>+<br>+                 | . 2<br>. 4<br>. 8<br>. 6<br>. 2 |

| . 6                                                 | <sub>10</sub> =. <del>1001</del> | 2                               |

The bar over a portion of a number indicates that that portion of the number is repetitive. In the above example, the group 1001 will repeat indefinitely as

. 10011001100110011001....

#### Example 1.8

$425_{10}=N_2$ Find N where

| Integer                                                                            |                            | Fraction                                       |

|------------------------------------------------------------------------------------|----------------------------|------------------------------------------------|

| . 425x2=0<br>. 85 x2=1<br>. 7 x2=1<br>. 4 x2=0<br>. 8 x2=1<br>. 6 x2=1<br>. 2 x2=1 | +<br>+<br>+<br>+<br>+<br>+ | . 85<br>. 7<br>. 4<br>. 8<br>. 6<br>. 2<br>. 4 |

|                                                                                    |                            |                                                |

$.425_{10} = .0\overline{1101}_{2}$

# Example 1.9

Find N where

9.

$$75_{10} = N_2$$

.75x2=1 + .5

.5 x2=1 + .0

9.  $75_{10}$ =1001.  $11_2$

#### Decimal to Octal

The conversion of decimal numbers to octal numbers uses the same procedure.

#### Example 1.10

Find N where

1

| Quotient   |                     | Remainder        |

|------------|---------------------|------------------|

| 8 / 176    |                     |                  |

| 8 \( 22 \) | +                   | 0                |

| 8 / 2      | +                   | 6 🛉              |

| 0          | +                   | 2                |

|            | 176 <sub>10</sub> = | 260 <sub>8</sub> |

# Example 1.11

Find N where

$$3_{10} = N_8$$

|                                         | Integer               |                         | Fraction                        |

|-----------------------------------------|-----------------------|-------------------------|---------------------------------|

| . 3x8 = . 4x8 = . 2x8 = . 6x8 = . 8x8 = | 2<br>3<br>1<br>4<br>6 | +<br>+<br>+<br>+        | . 4<br>. 2<br>. 6<br>. 8<br>. 4 |

|                                         | .3 <sub>10</sub> =    | $.2\overline{3146}_{8}$ |                                 |

#### Example 1.12

Find N where

253.

$$15_{10} = N_8$$

$253.15_{10} = 375.1\overline{1463}_{8}$

#### Binary to Octal

The octal number system has been employed, in most computer circles, as the standard number system. It is far less tedious to perform conversions between decimal and octal systems than between decimal and binary systems, and it is relatively simple to perform conversions between the octal and binary systems.

The relationship between the octal (radix 8) and binary (radix 2) number systems is the key to the conversion simplicity.

$$8 = 2^3$$

where the magic number is 3.

The procedure for converting binary numbers to octal numbers is as follows:

- 1. Starting at the binary point, proceed to the left and partition the number into groups of 3 bits (binary digits).

- Starting at the binary point, proceed to the right and partition the number into groups of 3 bits.

- Convert each group of 3 bits to its octal equivalent.

# Example 1.13

Find N where  $1011010.1011101_2=N_8$

$$\underbrace{0\ 0\ 1}_{1}\underbrace{0\ 1\ 1}_{3}\underbrace{0\ 1\ 0}_{2}\underbrace{1\ 0\ 1}_{5}\underbrace{1\ 1\ 0}_{6}\underbrace{1\ 0\ 0}_{4}$$

1011010. 10111101<sub>2</sub>=132. 564<sub>8</sub>

NOTE: Zeroes should be added at the beginning and at the end of a number to complete a group of 3 bits.

# Example 1.14

Find N where 1111000.0001111<sub>2</sub>=N<sub>8</sub>

$$\underbrace{0\ 0\ 1}_{1}\underbrace{1\ 1\ 1}_{7}\underbrace{0\ 0\ 0}_{0}\underbrace{1\ 0\ 0\ 0}_{7}\underbrace{1\ 1\ 1}_{4}\underbrace{1\ 0\ 0}_{4}$$

1111000.00011112=170.0748

Octal to Binary

The procedure for converting octal numbers to their binary equivalent is equally simple. Just reverse the binary to octal conversion procedure.

To convert octal numbers to binary, perform the following:

- 1. Starting at the octal point, proceed to the left and convert each number to its 3 bit binary equivalent.

- 2. Starting at the octal point, proceed to the right and convert each number to its 3 bit binary equivalent.

#### Example 1.15

173. 4058=1111011. 1000001012

NOTE: Leading and trailing zeroes may be dropped.

# Example 1.16

Find N where  $37526.1024_8 = N_2$

$37526.1024_8 = 111111101010110.0010000101_2$

This page intentionally left blank

#### SECTION II

#### ARITHMETIC OPERATIONS

#### ADDITION

#### Binary Addition

The addition of binary numbers follows the same procedure as the more familiar addition of decimal numbers.

To add two decimal numbers, proceed as follows:

- 1. Add the rightmost digit of each number to obtain a sum digit and a carry digit.

- 2. Record the sum digit.

- Add the next rightmost digit of each number, plus the carry digit left from the previous addition, and obtain another sum digit and carry digit.

- 4. Repeat steps 2 and 3, proceeding from right to left, until all the digits have been added.

- 5. The number constructed from the individual sum digits is the final sum.

Example 2.1

Add the two decimal numbers 566+624.

| 6+4=10   | 566<br>624                                                                                             | where Carry=1<br>Sum=0 |

|----------|--------------------------------------------------------------------------------------------------------|------------------------|

| 1+6+2=9  | $ \begin{array}{r} 1\\566\\\underline{624}\\0 \end{array} $                                            | where Carry=0<br>Sum=9 |

| 0+5+6=11 | $   \begin{array}{r}     01 \\     566 \\     \underline{624} \\     \hline     90   \end{array} $     | where Carry=1<br>Sum=1 |

| 1+0+0=1  | $   \begin{array}{r}     101 \\     0566 \\     \underline{0624} \\     \hline     190   \end{array} $ | where Carry=0 Sum=1    |

|          | $   \begin{array}{r}     101 \\     0566 \\     0624 \\     \hline     1190   \end{array} $            |                        |

Thus 566+625=1190 —

Binary addition follows exactly the same five steps used in decimal addition. But, it must be remembered that the binary number system has only two digits (0 and 1). The following table examines the addition of all possible operands resulting from the addition of two binary numbers:

| Carry<br>Prop. |   | Bit A |   | Bit B |        | Carry<br>Gen. | Sum |

|----------------|---|-------|---|-------|--------|---------------|-----|

| 0              | + | 0     | + | 0     | ****   | 0             | 0   |

| 0              | + | 0     | + | 1     | ****** | 0             | 1   |

| 0              | + | 1     | + | 0     |        | 0             | 1   |

| 0              | + | 1     | + | 1     | -      | 1             | 0   |

| 1              | + | 0     | + | 0     | ==     | 0             | 1   |

| 1              | + | 0     | + | 1     | =      | 1             | 0   |

| 1              | + | 1     | + | 0     | =      | 1             | 0   |

| 1              | + | 1     | + | 1     | =      | 1             | 1   |

#### Example 2.2

Add the two binary numbers 10111+10101.

| 1+1=10               | 10111<br>10101                                                                                | where                                   | Carry=1<br>Sum=0 |

|----------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------|------------------|

| 1+1+0=10             | $   \begin{array}{r}     1 \\     10111 \\     \underline{10101} \\     0   \end{array} $     | where                                   | Carry=1<br>Sum=0 |

| 1+1+1=11             | $   \begin{array}{r}     11 \\     10111 \\     \underline{10101} \\     00   \end{array} $   | where                                   | Carry=1<br>Sum=1 |

| 1+0+0=01             | $   \begin{array}{r}     111 \\     10111 \\     \underline{10101} \\     100   \end{array} $ | where                                   | Carry=0<br>Sum=1 |

| 0 + 1 + 1 = 10       | $0111 \\ 10111 \\ 10101 \\ \hline 1100$                                                       | where                                   | Carry=1<br>Sum=0 |

| 1+0+0=01             | 10111<br>010111<br>010101<br>101100                                                           | where                                   | Carry=0<br>Sum=1 |

| Thus 10111+10101=101 | 1100                                                                                          | *************************************** |                  |

The following example shows a shorthand method of keeping track of the sum and carry digits.

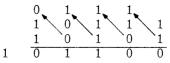

# Example 2.3

Repeat the Example 2.2 using the shorthand technique.

Thus 10111 + 10101 = 101100.

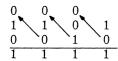

# Example 2.4

Add the two binary numbers 1101+10.

Thus 1101 + 10 = 1111.

If the number of digits in the answer exceeds the maximum allowable number of digits, the answer is said to overflow, and the leftmost digit of the answer is called the overflow digit.

If, in Example 2.3, the maximum allowable number of digits is five, then there is an overflow, and the overflow digit is 1. In Example 2.4, there is no overflow, so the overflow digit is 0.

#### Octal Addition

The procedure for performing octal addition is similar to that used for decimal and binary addition. The fact to keep in mind is that the octal number system has 8 digits (0 thru 7), and a carry occurs when the sum exceeds 7.

In the following examples, assume the maximum allowable number of digits is 5.

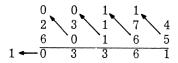

#### Example 2.5

Add the two octal numbers 23174 + 60165.

Thus 23174 + 60165 = 103361.

NOTE: In this example, an overflow occurred.

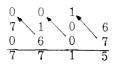

# Example 2. 6

Add the two octal numbers 7106 + 607.

Thus 7106 + 607 = 7715.

NOTE: In this example, no overflow occurred since the sum did not exceed the maximum allowable 5 digits.

#### SUBTRACTION

#### Complementary Arithmetic

In the previous section, the concept of "maximum allowable number of digits" was introduced. This concept is of great importance in the understanding of complementary arithmetic.

If the maximum allowable number of digits is 6, for example, then the decimal numbers

represent the same magnitude since the leftmost digit is an indication of overflow, and adds nothing to the value of the rightmost, maximum allowable 6 digits.

The normal counting sequence from zero is as follows:

| 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 2 |

| 0 | 0 | 0 | 0 | 0 | 3 |

|   |   | • |   |   |   |

|   |   | • |   |   |   |

|   |   | • |   |   |   |

| 9 | 9 | 9 | 9 | 9 | 7 |

| 9 | 9 | 9 | 9 | 9 | 8 |

| 9 | 9 | 9 | 9 | 9 | 9 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 1 |

|   |   |   |   |   |   |

It should be evident, from the previous table, that if 1 is added to the largest number, 999999, zero is obtained and the normal counting sequence is recycled.

1

What happens if the counting sequence is reversed?

|        |   | • |   |   |   |

|--------|---|---|---|---|---|

|        |   | • |   |   |   |

|        |   |   |   |   |   |

| 0      | 0 | 0 | 0 | 0 | 3 |

| 0      | 0 | 0 | 0 | 0 | 2 |

| 0      | 0 | 0 | 0 | 0 | 1 |

| 0      | 0 | 0 | 0 | 0 | 0 |

| 9<br>9 | 9 | 9 | 9 | 9 | 9 |

| 9      | 9 | 9 | 9 | 9 | 8 |

| 9      | 9 | 9 | 9 | 9 | 7 |

|        |   |   |   |   |   |

|        |   |   |   |   |   |

From this table, it can be seen that when 1 is subtracted from zero, the number simply cycles back through 999999, etc. But, 1 subtracted from zero is -1. To restate this, disregarding + and -, we say that, 999999 and 000001 are complements. Likewise, 000002 and 999998 are complements; 000003 and 999997 are complements; etc. Note that every number has a complement except 000000. The complement of 000000 is 000000.

To obtain the complement of a number, it is not necessary to count forwards and backwards from 000000. Simply subtract the number from (the largest possible number +1).

For the 6 digit maximum numbers used here, the largest possible number is 999999, and the largest possible number +1 is 1000000.

# Example 2.7

Find the complement of 000004.

#### Example 2.8

Find the complement of 923156.

#### Example 2.9

The complementary numbers obtained in Examples 2.7, 2.8 and 2.9 are more correctly referred to as the 10's (ten's) complement of the number (999996 is the 10's complement of 000004, etc.). This further restriction of the complement is used to indicate the operand from which the number was subtracted to obtain the complement. In Examples 2.7, 2.8 and 2.9, this operand is the next power of the base (in this case 10); thus the complement obtained is the 10's complement.

It is interesting to note that the original number was subtracted from the largest possible number +1 in order to obtain the 10's complement. The same result could be obtained if the number is subtracted from the <u>largest possible number</u>, and 1 added to the answer.

#### Example 2.10

Find the 10's complement of 923156.

NOTE: 076843 is known as the  $\underline{9's complement}$  of 923156.

Therefore, an easier method of finding the 10's complement of a number is as follows:

10's complement of X = 9's complement of X, plus 1

#### Example 2.11

Find the 10's complement of 000000.

Now let's apply the general rules of complementation to the binary number system. In the binary number system, the complement desired is the 2's complement of the number.

In the following examples, assume that the maximum allowable number of bits (binary digits) is 7.

#### Example 2.12

Find the 2's complement of 0000011.

- \*The largest possible number is 1111111.

- \*\*Direct binary subtraction follows the same rules as direct decimal subtraction:

But, as was shown before, it is possible to subtract the number from the largest possible number and add 1 to the result.

# Example 2.13

Find the 2's complement of 0000011.

NOTE: 1111100 is known as the  $\underline{1's}$  complement of 0000011.

Therefore, the 2's complement of a binary number may be obtained as follows:

2's complement of X = 1's complement of X, plus 1.

#### Example 2.14

Find the 2's complement of 1011101.

#### Example 2.15

Find the 2's complement of 000000.

Looking closely at the 1's complements of the numbers in Examples 2.13, 2.14 and 2.15, we see that the 1's complement of the number is the number, with all the 0's changed to 1's and the 1's changed to 0's.

#### Example 2.16

Find the 2's complement of 1110110.

#### Example 2.17

Find the 2's complement of 101101.

Applying the rules of complementation to octal numbers, we see that the 8's complement of a number is the 7's complement of the number, plus 1.

#### Example 2.18

Find the 8's complement of 77341.

#### Example 2.19

Find the 8's complement of 00000.

#### Binary Subtraction

By employing the techniques of complementary arithmetic, it is possible to effect a subtraction using the addition process.

To perform A-B, either of two methods may be used:

- 1) direct subtraction of B from A; or

- 2) the addition of A to the complement of B.

# Example 2.20

Perform 783<sub>10</sub>-25<sub>10</sub>

Method 1:

Method 2: 9 9 9-2 4=9 7 4 (9's complement of 25) 974+1 = 975 (10's complement of 25)

#### Octal Subtraction

Octal subtraction (A-B) may be performed by adding A to the 8's complement of B.

#### Example 2.23

Perform 6275g-31g

(Add leading 0's)

$$6275_8 - 0031_8$$

6275-31=6244

# Example 2.24

7000-76=6702

Perform 70008-768

#### Example 2.21

Perform 11011012-10112

NOTE: First add leading 0's to make numbers the same length.

Thus we are to perform 11011012-00010112

1101101-1011=1100010

#### Example 2.22

Perform 101011<sub>2</sub>-101011<sub>2</sub> (A-A)

Thus, a number plus its complement always equals zero.

#### MULTIPLICATION & BINARY

Binary multiplication is accomplished in a manner similar to decimal multiplication.

#### Example 2.25

Perform 1298<sub>10</sub>x10<sub>10</sub>

1298x10=12980

#### Example 2.26

Perform 8735<sub>10</sub>x63<sub>10</sub>

$$\begin{array}{c} 8 & 7 & 3 & 5 \\ x & 6 & 3 \\ 2 & 6 & 2 & 0 & 5 \\ \hline 5 & 2 & 4 & 1 & 0 \\ \hline 5 & 5 & 0 & 3 & 0 & 5 \end{array}$$

8735x63=550305

#### Example 2.27

Perform 101110012x102

|   | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 |

|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   | 1 | - |

|   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 |   |

| 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 |

1 10111001x10=101110010

# Example 2.28

Perform 1011102x11012

$$\begin{array}{c} 1 & 0 & 1 & 1 & 1 & 0 \\ & \times & 1 & 1 & 0 & 1 \\ \hline 1 & 0 & 1 & 1 & 1 & 0 \\ & 0 & 0 & 0 & 0 & 0 \\ & 1 & 0 & 1 & 1 & 1 & 0 \\ & 1 & 0 & 1 & 1 & 1 & 0 \\ 1 & 0 & 0 & 1 & 0 & 1 & 0 & 1 & 1 \end{array}$$

#### 101110x1101=1001010110

It is interesting to note from Example 2.25 that 10 times a decimal number simply appends a 0 to the right. From Example 2.27, we see that 2 times a binary number simply appends a 0 to the right.

#### **DIVISION-BINARY**

Binary division follows the same procedures as decimal division.

#### Example 2.29

Perform  $2288_{10} \div 13_{10}$

$2288 \div 13 = 176$

#### Example 2.30

Perform  $101100010_2 \div 110_2$

$101100010 \div 110=111011$

#### LOGICAL AND

In the binary number system, additional operations exist over and above addition, subtraction, multiplication, and division. These additional operations are known as logical or Boolean operations.

One such logical operation is the AND function.

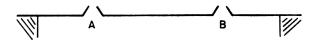

Consider the drawbridge in the following figure:

DG0069**5**

The bridge consists of 2 spans which can be opened: A and B. Obviously, the path across this bridge is continuous only if both A AND B are closed.

| SPAN A | SPAN B | BRIDGE |

|--------|--------|--------|

|        |        |        |

| OPEN   | OPEN   | OPEN   |

| OPEN   | CLOSED | OPEN   |

| CLOSED | OPEN   | OPEN   |

| CLOSED | CLOSED | CLOSED |

If the two states of each span are assigned the binary values OPEN=0 and CLOSED=1, the table can be rewritten.

|   |   | A AND B     |

|---|---|-------------|

|   |   | А. В        |

| A | В | $A \land B$ |

|   |   |             |

| 0 | 0 | 0           |

| 0 | 1 | 0           |

| 1 | 0 | 0           |

| 1 | 1 | 1           |

Two binary numbers can be ANDed by simply ANDing respective bits from each other.

#### Example 2.31

Perform 10111011 \(\triangle\) 00011011

NOTE: Both corresponding bits in A and B must be 1 for the resulting bit A·B to be a 1.

#### LOGICAL OR

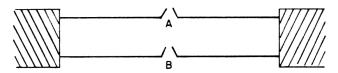

Consider 2 drawbridges spanning a river as shown in the following figure:

DG00696

A path from one side of the river to the other exists if A OR B or both is closed.

| SPAN A | SPAN B | PATH   |

|--------|--------|--------|

| OPEN   | OPEN   | OPEN   |

| OPEN   | CLOSED | CLOSED |

| CLOSED | OPEN   | CLOSED |

| CLOSED | CLOSED | CLOSED |

If we assign binary values to the states of each drawbridge, the table can be rewritten as follows:

| <u>A</u> | <u>B</u> | A OR B<br>A + B<br>A V B |

|----------|----------|--------------------------|

| 0        | 0        | 0                        |

| 0        | 1        | 1                        |

| 1        | 0        | 1                        |

| 1        | 1        | 1                        |

Notice that with the OR operation, if either of the corresponding bits in A or B is a 1, the resulting bit A + B is a 1.

Two binary numbers can be ORed by simply ORing respective bits from each number.

#### Example 2.32

Perform 10111011 V 00011011

# Example 2.33

Perform 10111011 V 01000100

This is equivalent to a V1's complement of A.

Thus, all 1's result when a number and its 1's complement are ORed.

#### LOGICAL EXCLUSIVE OR

The logical OR function described in the previous section is more precisely known as the logical inclusive OR function.

The exclusive OR function can be defined as follows: The resulting bit of  $A \oplus B$  is a 1 if either  $\mid$  of the corresponding bits in A or B is a 1, but not if both bits in A and B are a 1.

| <u>A</u> | <u>B</u> | $\underline{A \oplus B}$ |

|----------|----------|--------------------------|

| 0        | 0        | 0                        |

| 0        | 1        | 1                        |

| 1        | 0        | 1                        |

| 1        | 1        | 0                        |

#### Example 2.34

Perform 10111011 (+)00011011

# SIGNED NUMBER REPRESENTATION

#### Sign Bit Definition

In many applications where the use of both positive and negative numbers is required, some method to indicate the sign of the number must be employed. In written text, this is done with the + and - signs. The computer, however, works with binary numbers and would not easily recognize a + or - sign. Another method must be used to indicate the sign of the number. One possibility is to define the leftmost bit of the binary number to be the sign indicator or sign bit. A one (1) in this position would indicate that the number represented by the bits to the right is negative; a zero (0) would indicate that the number is positive. Utilizing this technique of signed number representation, the sign bit is followed by the absolute value of the number. Another method of representing signed numbers employs the concept of complementary numbers, as described in Section II. B. It is this last method which will be pursued further here.

If the maximum allowable number of bits is 4, then the following numbers are possible:

| 0           | 0 | 0 | 0 |

|-------------|---|---|---|

| 0           | 0 | 0 | 1 |

| 0           | 0 | 1 | 0 |

| 0<br>0<br>0 | 0 | 1 | 1 |

| 0           | 1 | 0 | 0 |

| 0           | 1 | 0 | 1 |

| 0           | 1 | 1 | 0 |

|             | 1 | 1 | 1 |

| 1           | 0 | 0 | 0 |

| 1           | 0 | 0 | 1 |

| 1           | 0 | 1 | 0 |

| 1           | 0 | 1 | 1 |

| 1           | 1 | 0 | 0 |

| 1           | 1 | 0 | 1 |

| 1           | 1 | 1 | 0 |

| 1           | 1 | 1 | 1 |

This set of 16 numbers is cyclic because adding 1 to 1111 brings us back to 0000.

Also, subtracting 1 from 0000, gives us 1111. If this set of numbers is said to contain only positive values, then the range of values is

Suppose we divide this set in half, and define one half as representing positive values, and the other half negative values (A). Also, let's restack the set so that 0000 is at the center (B).

| A                                       | B                                                                                                                                                                                  | _C_(decimal)                                      |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|                                         | itive hibers $ \begin{cases} 0 & 1 & 1 & 1 \\ 0 & 1 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 \\ 0 & 0 & 0 & 1 \end{cases} $                                      | 7<br>6<br>5<br>4<br>3<br>2                        |

| 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | ative bers $\begin{cases} 0 & 0 & 0 & 0 \\ \hline 1 & 1 & 1 & 1 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 0 & 1 \\ 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 1 \\ 1 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \end{cases}$ | 0<br>-1<br>-2<br>-3<br>-4<br>-5<br>-6<br>-7<br>-8 |

and a

Notice that all the negative numbers have a 1 in the leftmost bit position and all the positive numbers have a 0 in the leftmost bit position. Thus, if 0000 is defined as being a positive number, there is the same quantity of positive and negative values.

NOTE: If the programmer is using the leftmost bit for sign definition, care should be taken not to overflow the range of values.

# Example 2.35

Perform 5+(-4)

$$\begin{array}{ccc}

5 & 0101 \\

+ (-4) & + 1100 \\

\hline

1 & 1 & -0001

\end{array}$$

#### Example 2.36

Perform 6+(-6)

#### Example 2.37

Perform 7+2

$$\begin{array}{c} 7 & 0111 \\ \underline{2} & +0010 \\ \hline 9 & 1 \leftarrow 1001 \end{array}$$

Note that in this example the desired result was not obtained because the range has been exceeded. 1001 represents -7, not +9.

Range of Signed Numbers

In the 4-bit number set of the previous section, the range of unsigned numbers is as follows:

0000 thru 1111 or 010 thru 1510 or 08 thru 178

The range of signed numbers, however, from table B is as follows:

$\begin{array}{c} 1000 \; \rm{thru} \; \; 0111 \\ \rm{or} \; \; \text{-8}_{10} \; \rm{thru} \; \; \text{+7}_{10} \\ \rm{or} \; \; \text{-10}_{8} \; \rm{thru} \; \; \text{+7}_{8} \end{array}$

# Example 2.38

If a number set contains 16-bit numbers, the ranges are as follows:

#### Unsigned

# Signed

100000000000000000 thru 0111111111111111 or  $-32,768_{10}$  thru  $+32,767_{10}$  or  $-100000_8$  thru  $+077777_8$

This page intentionally left blank

#### SECTION III

#### LOGIC AND LOGIC CONVENTIONS

# GENERAL

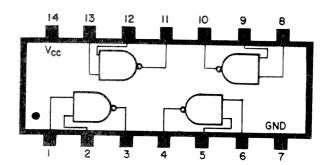

- 1. The various circuits, logic gates, logic conventions and integrated circuits common to mini-computers are discussed in this section.

- 2. Integrated circuits (IC's) are defined as a number of minute circuits bonded onto a small plug in pack roughly 1/4" by 3/4" in size. IC's are also referred to as "Chips", "Bugs", "Dips" or "Packs".

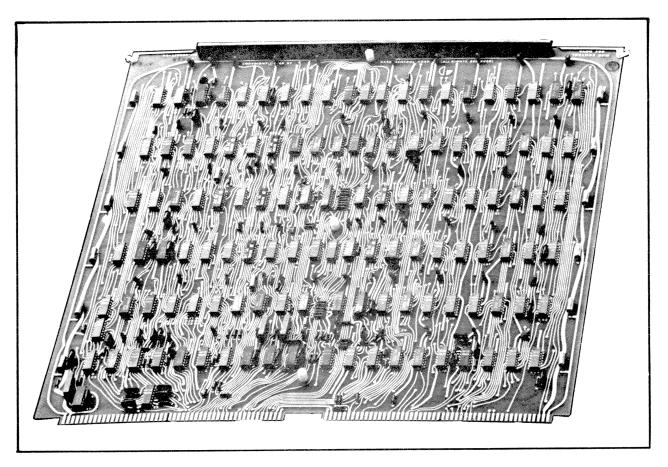

- 3. Printed Circuit Board (PCB) etched boards upon which are mounted numerous IC's making up an element of computer logic. A typical

- computer may have one to three PCB's which provide the necessary Central Processor Unit logic. (See Figure 3-1.)

- 4. Logic Levels a typical mini-computer has two logic levels ground and plus three volts (+3V). Where ground might represent a zero (0) and +3V and one (1).

- 5. Symbols

- a.  $\wedge$  or  $\cdot$  represent AND. For example  $A \wedge B$  or  $A \cdot B$ .

- b.  $\vee$  or + represent OR. For example  $A \vee B$  or A + B.

Figure 3-1 Printed Circuit Board

DG00697

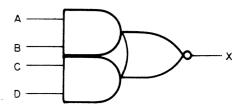

TRUTH TABLE

| $v_{IN}$ | $v_{\rm IN}$ | VOUT |

|----------|--------------|------|

| L        | L            | H    |

| L        | H            | H    |

| H        | L            | H    |

| H        | H            | L    |

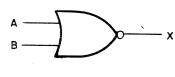

Figure 3-2 Logic Diagram

#### LOGIC GATES

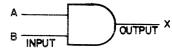

# AND Gate

a. Symbol

b. Two input - noninverting

Output is high if both inputs are high.

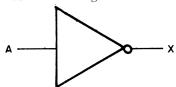

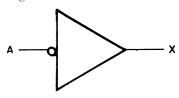

NOTE: A straight line into a gate represents a high condition. A straight line with a small circle will indicate a low condition.

Definition: Will give a desired output when  $\underline{ALL}$  input conditions are satisfied.

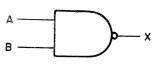

c. Two input - inverting (NAND Gate)

|   | АВ |

|---|----|

|   | LL |

| v | LΗ |

| X | ΗL |

|   | нн |

INPUT

Output is low if both inputs are high.

d. Three input - inverting (NEGATIVE NAND)

| INPUT | OUTPUT |

|-------|--------|

| ABC   | Х      |

| LLL   | н      |

| LLH   | L      |

| LHL   | L      |

| LHH   | L      |

| HLL   | L      |

| нцн   | L      |

| HHL   | L      |

| ннн   | L      |

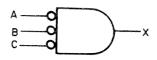

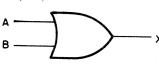

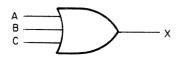

OR Gate

OUTPUT

X

L

L

L

Η

OUTPUT

X H H L

INPUT A B

LL

LH

ΗL

НН

a. Symbol

Definition: Will give a desired output when  $\overline{\text{ANY}}$  input condition is satisfied.

b. Two input - noninverting (OR)

| INPUT | OUTPUT |

|-------|--------|

| АВ    | Х      |

| LL.   | L      |

| LH    | Н      |

| HL    | Н      |

| нн    | Н      |

DIDION LONG

Output is high if either or both inputs are high.

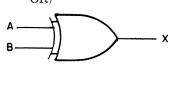

c. Two input - inverting (NOR Gate)

| INPUT | OUTPUT |

|-------|--------|

| АВ    | X      |

| LL    | Н      |

| LH    | L      |

| HL    | L      |

| нн    | L      |

Output is low if either or both inputs are high.

d. Three input - noninverting

| INPUT | OUTPUT |

|-------|--------|

| АВС   | X      |

| LLL   | L      |

| LLH   | Н      |

| LHL   | Н      |

| LHH   | Н      |

| HLL   | Н      |

| нгн   | Н      |

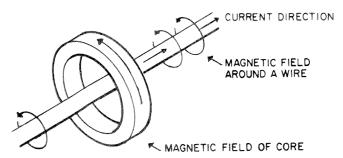

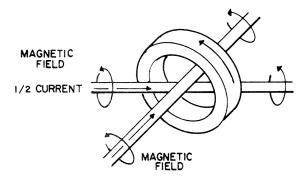

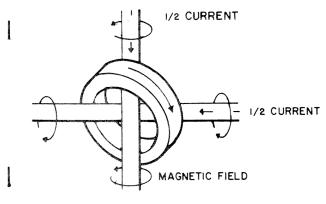

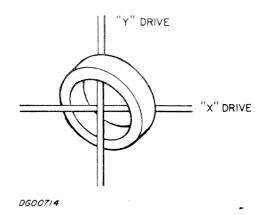

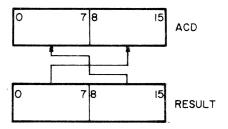

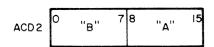

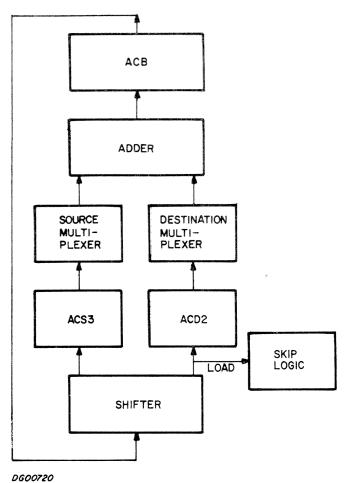

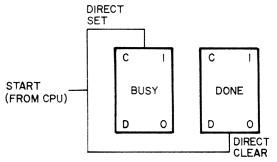

| HHL   | Н      |