# Microprogrammers' Reference, ECLIPSE MV/10000™ Computer

# Microprogrammers' Reference, ECLIPSE MV/10000™ Computer

014-701003

Ordering No. 014-701003

© Data General Corporation, 1983

All Rights Reserved

Printed in the United States of America

Revision 00, May 1983

#### NOTICE

Data General Corporation (DGC) has prepared this document for use by DGC personnel, customers, and prospective customers. The information contained herein shall not be reproduced in whole or in part without DGC's prior written approval.

DGC reserves the right to make changes in specifications and other information contained in this document without prior notice, and the reader should in all cases consult DGC to determine whether any such changes have been made.

THE TERMS AND CONDITIONS GOVERNING THE SALE OF DGC HARDWARE PRODUCTS AND THE LICENSING OF DGC SOFTWARE CONSIST SOLELY OF THOSE SET FORTH IN THE WRITTEN CONTRACTS BETWEEN DGC AND ITS CUSTOMERS. NO REPRESENTATION OR OTHER AFFIRMATION OF FACT CONTAINED IN THIS DOCUMENT INCLUDING BUT NOT LIMITED TO STATEMENTS REGARDING CAPACITY, RESPONSE-TIME PERFORMANCE, SUITABILITY FOR USE OR PERFORMANCE OF PRODUCTS DESCRIBED HEREIN SHALL BE DEEMED TO BE A WARRANTY BY DGC FOR ANY PURPOSE, OR GIVE RISE TO ANY LIABILITY OF DGC WHATSOEVER.

IN NO EVENT SHALL DGC BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS DOCUMENT OR THE INFORMATION CONTAINED IN IT, EVEN IF DGC HAS BEEN ADVISED, KNEW OR SHOULD HAVE KNOWN OF THE POSSIBILITY OF SUCH DAMAGES.

CEO, DASHER, DATAPREP, ECLIPSE, ENTERPRISE, INFOS, microNOVA, NOVA, PROXI, SUPERNOVA, ECLIPSE MV/4000, ECLIPSE MV/6000, ECLIPSE MV/8000, PRESENT, TRENDVIEW, and MANAP are U.S. registered trademarks of Data General Corporation.

AZ-TEXT, BusiPEN, BusiGEN, BusiTEXT, ECLIPSE MV/10000, DEFINE, DG/L, GENAP, GDC/1000, GW/4000, microECLIPSE, REV-UP, SLATE, SWAT, and XODIAC are U.S. trademarks of Data General Corporation.

Microprogrammers' Reference, ECLIPSE MV/10000 Computer 014-701003

Original Release - May 1983

### **Contents**

| Preface                                                                                                                                                                                                                                                                         | p-1                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Chapter 1 Introduction                                                                                                                                                                                                                                                          | 1-1                                                                                |

| Terminology                                                                                                                                                                                                                                                                     | 1-2<br>1-2                                                                         |

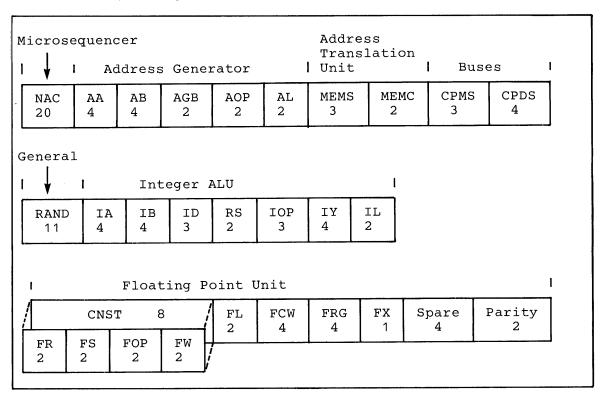

| Chapter 2 MV/10000 Architecture and Operation                                                                                                                                                                                                                                   | 2-1                                                                                |

| Clocks and Timing The Microsequencer Writable Control Store Microinstruction Register Microprogram Counters Microstack and Microstack Input Multiplexer Top of Stack Register RAM Address Multiplexer DSP Register, Crossbar Net, Dispatch Multiplexer AA Bus Flags SCP Control | 2-2<br>2-2<br>2-3<br>2-3<br>2-4<br>2-5<br>2-5<br>2-6                               |

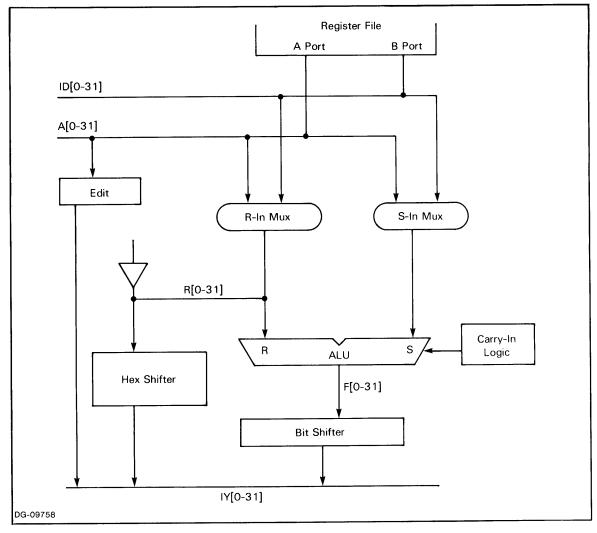

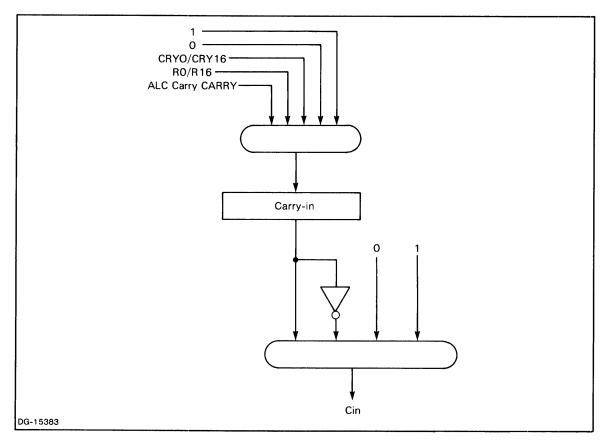

| Tests The Integer ALU Integer Register File Registers on the ID Bus Scratch Pad Transfer Register Hex Shifter ALU Carry-In Logic Commercial Test and Edit PROMs Bit Shifter Processor Status Register                                                                           | 2-7<br>2-8<br>2-10<br>2-11<br>2-12<br>2-13<br>2-14<br>2-15<br>2-16<br>2-17<br>2-18 |

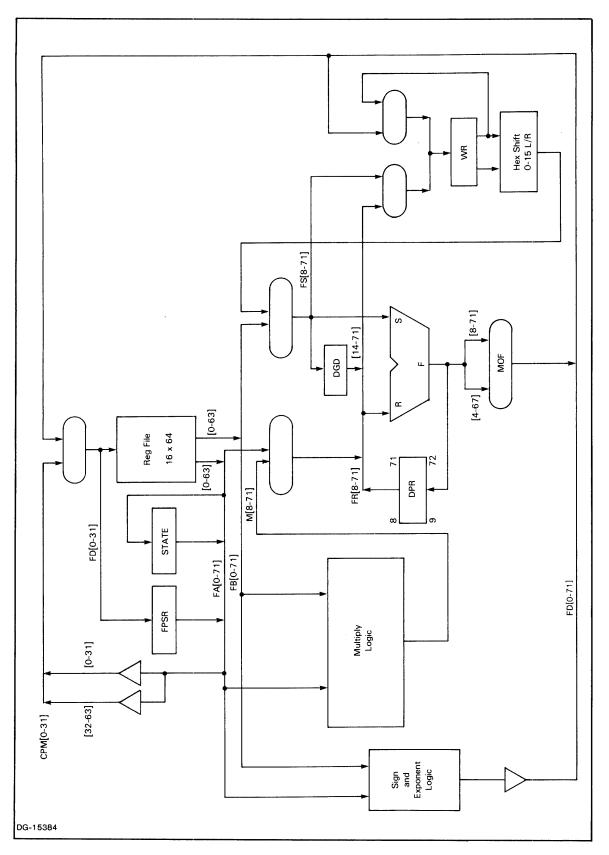

| The Floating-Point Unit  FPU Buses                                                                                                                                                                                                                                              | 2-19<br>2-19<br>2-21<br>2-21<br>2-22<br>2-22<br>2-22                               |

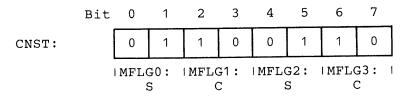

| Floating-Point STATE Register                    |           |

|--------------------------------------------------|-----------|

| Hex Shifter                                      | <br>2-24  |

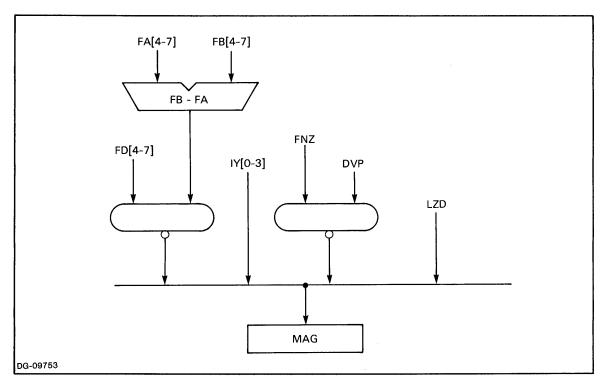

| MAG Register                                     | <br>2-24  |

| Mantissa ALU                                     | <br>2-26  |

| Working Register                                 |           |

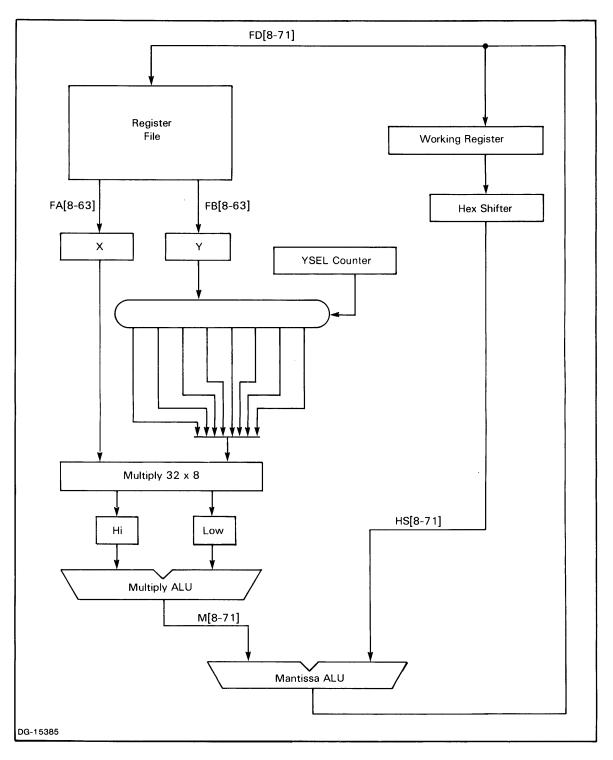

| Multiply Hardware                                |           |

| X and Y Registers                                |           |

| YSEL Counter                                     |           |

| Multiply ALU                                     |           |

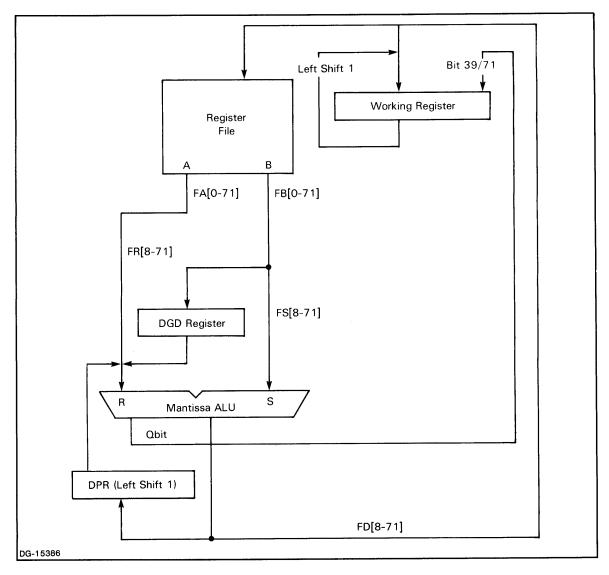

| Divide Hardware                                  |           |

| Divide Guard Digit Register                      |           |

| Divide Partial Remainder Register                |           |

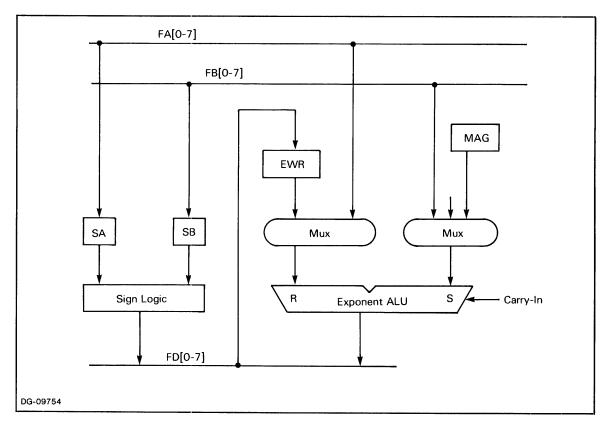

| Sign and Exponent Logic                          |           |

| Exponent Working Register                        |           |

| Exponent ALU                                     |           |

|                                                  |           |

| SA and SB Registers                              |           |

| Sign Logic                                       |           |

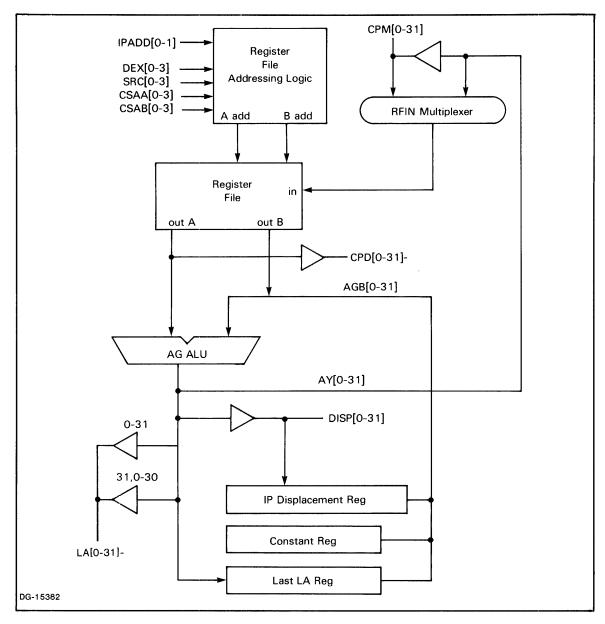

| The Address Generator                            |           |

| Buses                                            |           |

| Register File                                    |           |

| Register File Addressing                         |           |

| AGB Bus Sources                                  |           |

| RFIN Multiplexer                                 |           |

| Address Generator ALU                            | <br>2-36  |

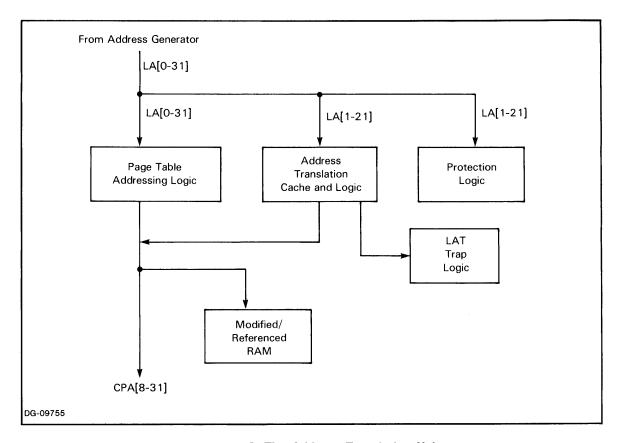

| The Address Translation Unit                     | <br>2-36  |

| Address Translation Cache                        | <br>2-37  |

| Referenced/Modified RAM                          |           |

| Validity RAM                                     |           |

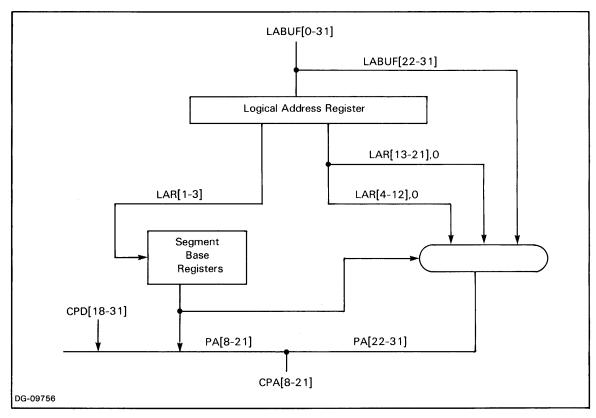

| Logical Address Translation                      |           |

| Page Table Addressing Logic                      |           |

| Ring Protection                                  |           |

| Indirection Protection                           |           |

| Read/Write/Execute Protection                    |           |

| ATU State                                        |           |

| ATU Diagnostic Register                          |           |

|                                                  |           |

| ATU Dispatch                                     |           |

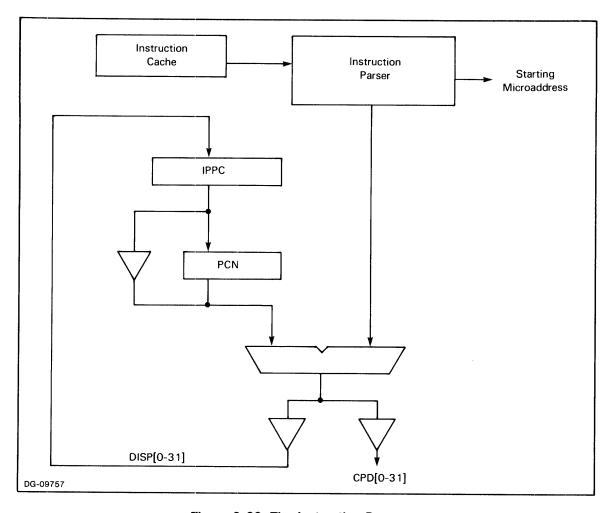

| The CPD Bus and Transfer Register                |           |

| Instruction Processor                            |           |

| Interrupts                                       |           |

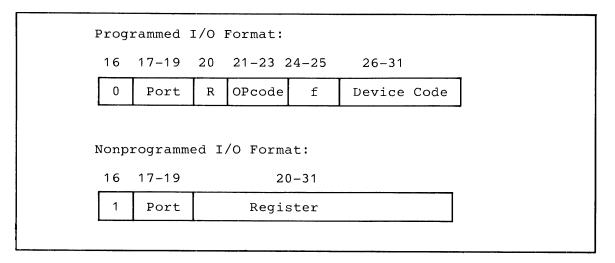

| I/O Protocols                                    | <br>2-46  |

| Chapter 3 Micro-order Format and Instruction Set | <br>. 3-  |

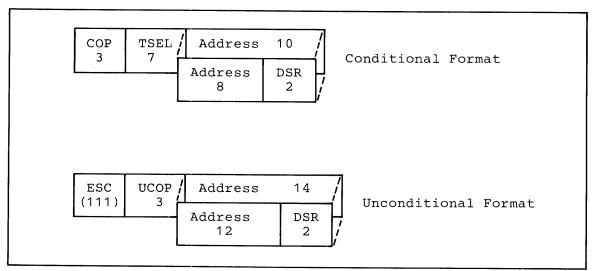

| NAC-Next Address Control                         |           |

| NAC:COP—Conditional OPcode                       |           |

| NAC:TSEL —Test Selection                         | <br>. 3-6 |

| Microsequencer Tests                             |           |

| Address Translation Unit Tests                   | <br>. 3-9 |

| Integer ALU Tests                                | <br>3-12  |

| Floating-Point Tests                             |           |

| NAC:UCOP—Unconditional OPcode                    |           |

| NAC:DSR – Dispatch Address Source                |           |

| Address Generator Micro-orders                   |           |

|                                                  | <br>1     |

| AA and AB—The Register File Address Fields    | 3-24  |

|-----------------------------------------------|-------|

| AGB—The Address Generator Bus Field           | 3-28  |

| AOP-Address Generator ALU Operation Field     | 3-29  |

| AL-Address Generator Register Loading         | 3-29  |

| Memory Control Micro-orders                   | 3-30  |

| MEMS – Memory Start                           | 3-31  |

| MEMC – Memory Complete                        | 3-32  |

| Bus Control Micro-orders                      | 3-34  |

| CPMS—CPM Bus Sources                          | 3-34  |

| CPDS—CPD Bus Sources                          | 3-35  |

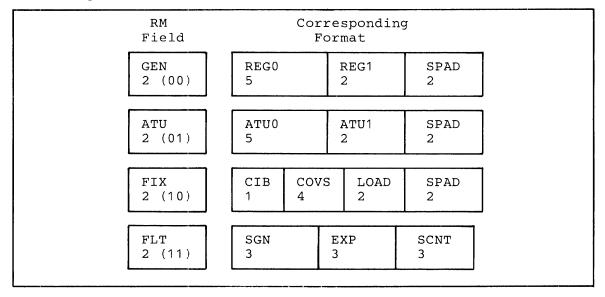

| RAND—Random Micro-orders                      | 3_39  |

| RAND:GEN—General Random Micro-orders          | 3-40  |

| RAND:GEN:REG0—General/ACSR/ACDR Micro-orders  |       |

| RAND:GEN:REG0—General/ACSK/ACDK Micro-orders  |       |

| RAND:GEN:REGI — Register Load Operations      |       |

| RAND:GEN:SPAD—Scratch Pad input Control       | 2.50  |

| RAND:ATU —ATU Random Micro-orders             |       |

| RAND:ATU:ATU0—ATU Operations                  |       |

| RAND:ATU:ATU1—Additional ATU Operations       |       |

| RAND:ATU:SPAD - Scratch Pad Input Control     | 3-59  |

| RAND:FIX - Fixed-point Random Micro-orders    | 3-60  |

| RAND:FIX:COVS—Carry, Overflow and Status      | 3-60  |

| RAND:FIX:LOAD - Load Registers                | 3-63  |

| RAND:FIX:SPAD Scratch Pad Input Control       | 3-63  |

| RAND:FLT - Floating-Point Random Micro-orders | 3-64  |

| RAND:FLT:SGN — Floating-Point Sign            | 3-65  |

| RAND:FLT:EXP—Floating-Point Exponent          | 3-66  |

| RAND:FLT:SCNT—Shift Count Control             | 3-69  |

| Integer ALU Micro-orders                      |       |

| IA and IB—Integer Register File Addressing    | 3-71  |

| ID – ID Bus Source Control                    | 3-75  |

| RS—ALU Input Multiplexer Control              | 3-77  |

| IOP—ALU Control and Shift Magnitude           | 3-77  |

| IY –IY Bus Source                             |       |

| IL—Integer Register File Input                |       |

| Floating-Point ALU Micro-orders               |       |

| FR —FR Bus Source                             | 3-86  |

| FS –FS Bus Source                             |       |

| FOP—Mantissa Operations                       |       |

| FWR—Working Register Input                    |       |

| FCW—Floating-Point Register Write Address     | 3-00  |

| FL—Register File Load Specifier               | 3-90  |

| FRG—Floating-Point Register Load Control      | 3 05  |

| FX—Froating-Point Register Load Control       |       |

| FX—Excess-64 Control                          | 3-77  |

| Chapter 4 Microprogramming Examples           | . 4-1 |

| •                                             |       |

| Memory Accesses                               | . 4-2 |

| IPOP—Crossing Macroinstruction Boundaries     | . 4-4 |

| Indirection Resolution                        | . 4-5 |

| Dispatching                                   | . 4-6 |

| Chapter 5 MV/10000 Microcode Macroassembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-1        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| The Macroassembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-1        |

| CPM Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| CPD Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| Memory Starts and Address Generator Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

| Memory Completion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| ALU Operation Constructs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-6        |

| IY Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| ALU Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| Loading SPAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

| Edit PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -10        |

| ID Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| IR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| FPU Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

| FD Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| FA and FB Buses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| $WR == \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| Sign and Exponent Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

| Shift Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| Multiply Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

| FPU State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

| Divide Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

| GEN Randoms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| ACSR (SRC Register Pointer) Randoms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| ACDR (DES Register Pointer) Randoms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| Flag Manipulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| Skips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -17        |

| Miscellaneous Randoms (NPDR and XTND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

| ATU Randoms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| FIX Randoms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |