#### 440/480

## FLEXIBLE DISK DATA STORAGE SYSTEMS

SERVICE MANUAL

QUALOGY

Formerly Data Systems Design

2241 Lundy Avenue

San Jose, CA 95131

## COPYRIGHT • 1983

All rights reserved. No part of this book may be reproduced in any form or by any means without prior written permission of Qualogy, Inc., formerly Data Systems Design, Inc.

Part Number: 040023-01 Printed in USA: 9/84

#### WARRANTY

The products of Qualogy, formerly Data Systems Design, are warranted against defects in materials and workmanship. For Qualogy products sold in the U.S.A., this warranty applies for ninety days from date of shipment. For products sold outside the U.S.A., contact your Qualogy distributor for warranty terms.

Qualogy will, at its option, repair or replace either equipment or components which prove to be defective during the warranty period. This warranty includes labor, parts, and surface travel costs of system modules or components.

Freight charges for other than surface travel or for complete systems returned for repair are not included in this warranty. Equipment returned to Qualogy for repair must be shipped freight prepaid and accompanied by a Material Return Authorization number issued by Qualogy Customer Service.

Repairs necessitated by shipping damage, misuse of the equipment, or by hardware, software, or interfacing not provided by Qualogy are not covered by this warranty.

No other warranty is expressed or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Qualogy shall not be liable for consequential damages or loss of data.

For superior reliability and long service life, Qualogy recommends that you use DYSAN or MAXELL floppy diskettes.

#### PREFACE

This manual provides theory of operation and service instructions for the DSD 440 and the DSD 480 Flexible Disk Data Storage Systems.

The material in this manual is subject to change without notice. The manufacturer assumes no responsibility for any errors which may appear in this manual.

Please note that DEC, PDP, OS/8, RT-11. UNIBUS, and OMNIBUS are registered trademarks of Digital Equipment Corporation.

### **SAFETY**

Operating and maintenance personnel must, at all times, observe sound safety practices. Do not replace components, or attempt repairs to this equipment with the power turned on. Under certain conditions, dangerous potentials may exist when the power switch is in the off position, due to charges retained by capacitors. To avoid injury, always remove power before attempting repair procedures.

Data Systems Design, Inc. will accept no responsibility or liability for injury or damage sustained as a result of operation or maintenance of this equipment with the covers removed and power applied.

#### WARNING

This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause interference to radio communications. As temporarily permitted by regulations, it has not been tested for compliance with the limits for Class A computing devices pursuant to sub-part J or Part 15 of the FCC rules which are designed to provide reasonable protection against such interference. The operation of this equipment in a residential area in likely to cause interference in which case the user at his own expense, will be required to take whatever measures may be required to correct the interference.

# TABLE OF CONTENTS

|     |             |                                            | Page |  |  |

|-----|-------------|--------------------------------------------|------|--|--|

|     | <b>~</b>    |                                            | •    |  |  |

| 1.0 | GEN         | ERAL INFORMATION                           | 1-1  |  |  |

|     | 1.1         | Purpose and Scope                          | 1-1  |  |  |

|     | 1.2         | Related Publications                       | 1-1  |  |  |

|     | 1.3         | Service Philosophy                         | 1-1  |  |  |

|     | 1.4         | Special Support Items                      | 1-1  |  |  |

|     | 1.5         | Service Limitations                        | 1-2  |  |  |

| 2.0 | INTE        | ERFACE MODULES                             | 2-1  |  |  |

|     | 2.1         | Introduction                               | 2-1  |  |  |

|     | 2.2         | Interface Bus Specifications               | 2-1  |  |  |

| 3.0 | CON         | TROLLER MODULE                             | 3-1  |  |  |

|     | 3.1         | Introduction                               | 3-1  |  |  |

|     | <b>3.2</b>  | Overview                                   | 3-1  |  |  |

|     | 3.3         | 8085 Microprocessor                        | 3-2  |  |  |

|     | 3.4         | Cable Connections                          | 3-14 |  |  |

|     | 3.5         | Read/Write Controller (R/WC)               | 3-29 |  |  |

|     | 3.6         | Serial Data Path                           | 3-40 |  |  |

|     | 3.7         | Phase-Lock-Loop Circuitry                  | 3-47 |  |  |

|     | 3.8         | DC Power Sensing Circuit                   | 3-51 |  |  |

| 4.0 | MAINTENANCE |                                            |      |  |  |

|     | 4.1         | Introduction                               | 4-1  |  |  |

|     | 4.2         | Preventive Maintenance                     | 4-1  |  |  |

|     | 4.3         | Servicing of Disk Drives and Power Supply  | 4-1  |  |  |

|     | 4.4         | Test Equipment                             | 4-1  |  |  |

|     | 4.5         | Test Points and Jumpers                    | 4-2  |  |  |

|     | 4.6         | Other Test Points                          | 4-2  |  |  |

|     | 4.7         | Adjustment Procedures                      | 4-3  |  |  |

|     | 4.8         | Removal and Replacement Procedures         | 4-5  |  |  |

|     | 4.9         | Troubleshooting Techniques                 | 4-5  |  |  |

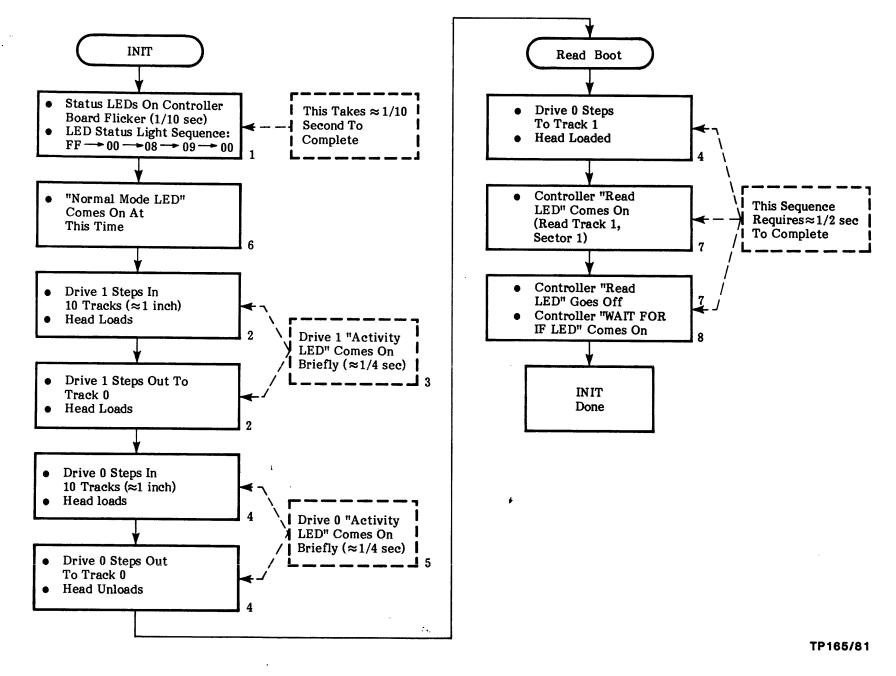

|     | 4.10        | Normal Initialization Sequence             | 4-7  |  |  |

|     | 4.11        | Troubleshooting a Failure During Bootstrap | 4-7  |  |  |

|     | 4.12        | How to Obtain Definitive Error Status      | 4-13 |  |  |

| 5.0 | MAIN        | TENANCE DOCUMENTS                          | 5-1  |  |  |

|     | 5.1         | Illustrations                              | 5-1  |  |  |

|     | 5.2         | Parts Lists                                | 5_1  |  |  |

# TABLE OF CONTENTS (Cont)

# **TABLES**

| Table No.                                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                                                        |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 2-1 3-1 3-2 3-3 3-4 3-5 3-6 3-7 3-8 3-9 4-1 4-2 4-3                                                          | I-Bus Signals and Pin Connections DSD 440/480 Busses Summary of Address Assignments Disk Drive Cable Bit Controller Instructions R/WC Vectoring Out Data Source Control Field Shift Register Control Output (EMIT) Bit Definitions Coder/Decoder PROM Logic Equations Other Test Points Bootstrap Halt Errors Bootstrap Loop Errors                                                                                                                                                                                                                                              | 2-2<br>3-3<br>3-15<br>3-28<br>3-32<br>3-35<br>3-37<br>3-37<br>3-38<br>3-48<br>4-3<br>4-10<br>4-12           |

|                                                                                                              | FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                             |

| Figure No.                                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                                                        |

| 2-1 2-2 3-1 3-2 3-3 3-4 3-5 3-6 3-7 3-8 3-9 3-10 3-11 3-12 3-13 3-14 3-15 3-16 3-17 3-18 3-19 3-20 3-21 3-22 | Timing, Interface to Controller Timing, Controller to Interface NO-OP Logic Circuit Bus Control Lines Clock Circuitry Status Lines Master Controller Nucleus Block Diagram Typical PROM Installation 2111 RAM Selection on Controller Module 2114 RAM Selection on Controller Module 8115 RAM/I/O/Timer Eight Position Dipswitch to 8155 Interface LED Indicator Bank Decoder PROMs Pulsed Outputs Latched Outputs Drive Status Port Interrupt Logic Watchdog Timer Watchdog Timer Timing READY Hardware Logic Cable Reversal Test Logic IF Cable Interface Shift Circuit Timing | 2-5 2-6 3-4 3-4 3-5 3-6 3-7 3-7 3-8 3-8 3-9 3-9 3-10 3-13 3-16 3-17 3-18 3-19 3-20 3-21 3-22 3-23 3-25 3-26 |

| 3-23<br>3-24<br>3-25<br>3-26<br>3-27                                                                         | Transfer Request Circuit Read/Write Controller Block Diagram Definition of Bit Controller Microword Functional Sequencing Example R/WC Branch Conditioning Circuitry                                                                                                                                                                                                                                                                                                                                                                                                             | 3-27<br>3-30<br>3-31<br>3-34<br>3-39<br>3-40                                                                |

# TABLE OF CONTENTS (Cont)

# **FIGURES**

| Figure No. | Description                                       | Page |

|------------|---------------------------------------------------|------|

| 3-29       | Write Serial Data Path                            | 3-42 |

| 3-30       | Read Serial Data Path                             | 3-43 |

| 3-31       | Generation of DEC-Modified Area of MFM Coding     | 3-44 |

| 3-32       | Write Precompensate Circuit                       | 3-46 |

| 3-33       | Precompensate Timing                              | 3-47 |

| 3-34       | Phase Comparator                                  | 3-49 |

| 3-35       | PLL Interface to Read/Write Controller            | 3-51 |

| 3-36       | PLL Charge Pump Circuit                           | 3-52 |

| 3-37       | DC Power Up/Down Timing                           | 3-53 |

| 3-38       | DC Power Up/Down Circuit                          | 3-54 |

| 3-39       | I-Bus Signal Line Driver Controller               | 3-55 |

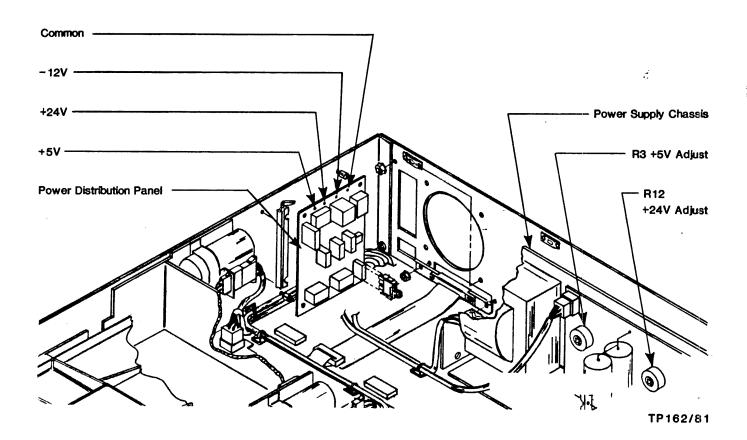

| 4-1        | Other Test Point Locations                        | 4-2  |

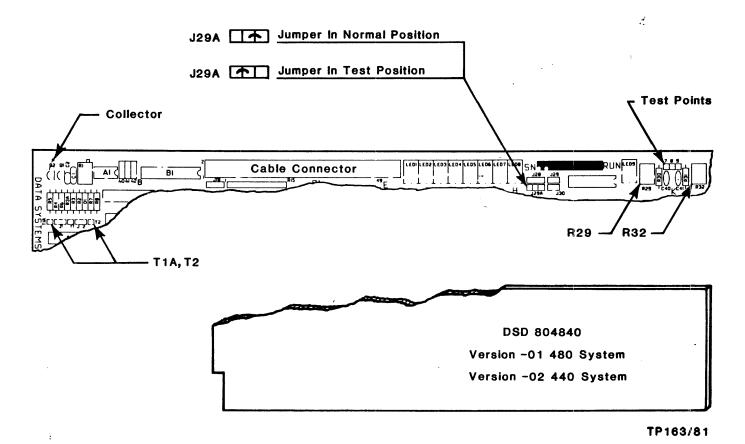

| 4-2        | Controller Board Test Points and Jumpers          | 4-4  |

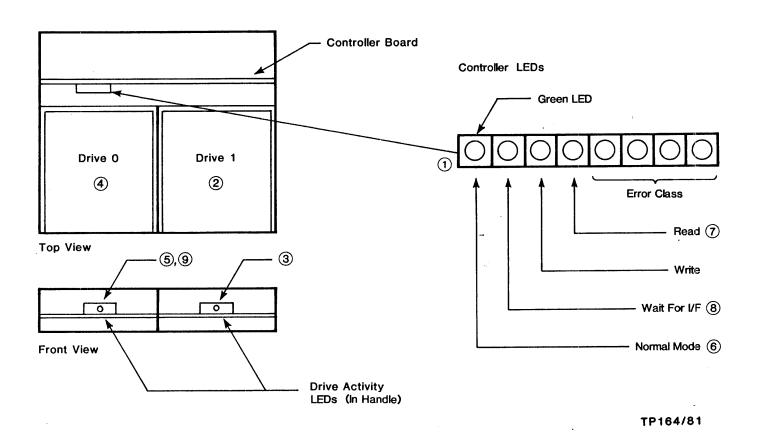

| 4-3        | Reference Notes                                   | 4-6  |

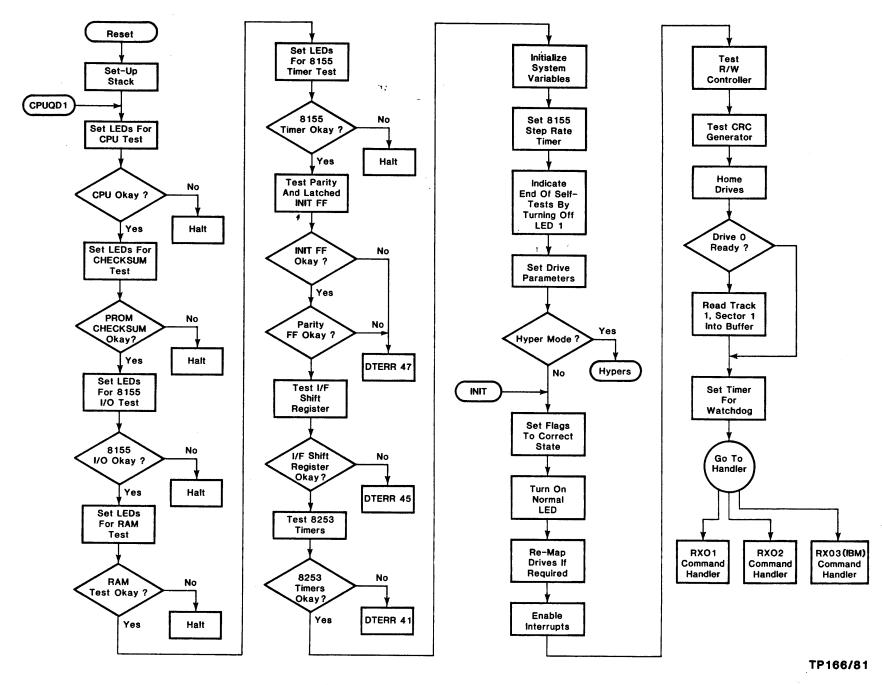

| 4-4        | INIT Sequence                                     | 4-8  |

| 4-5        | INIT Sequence in Microcode                        | 4-9  |

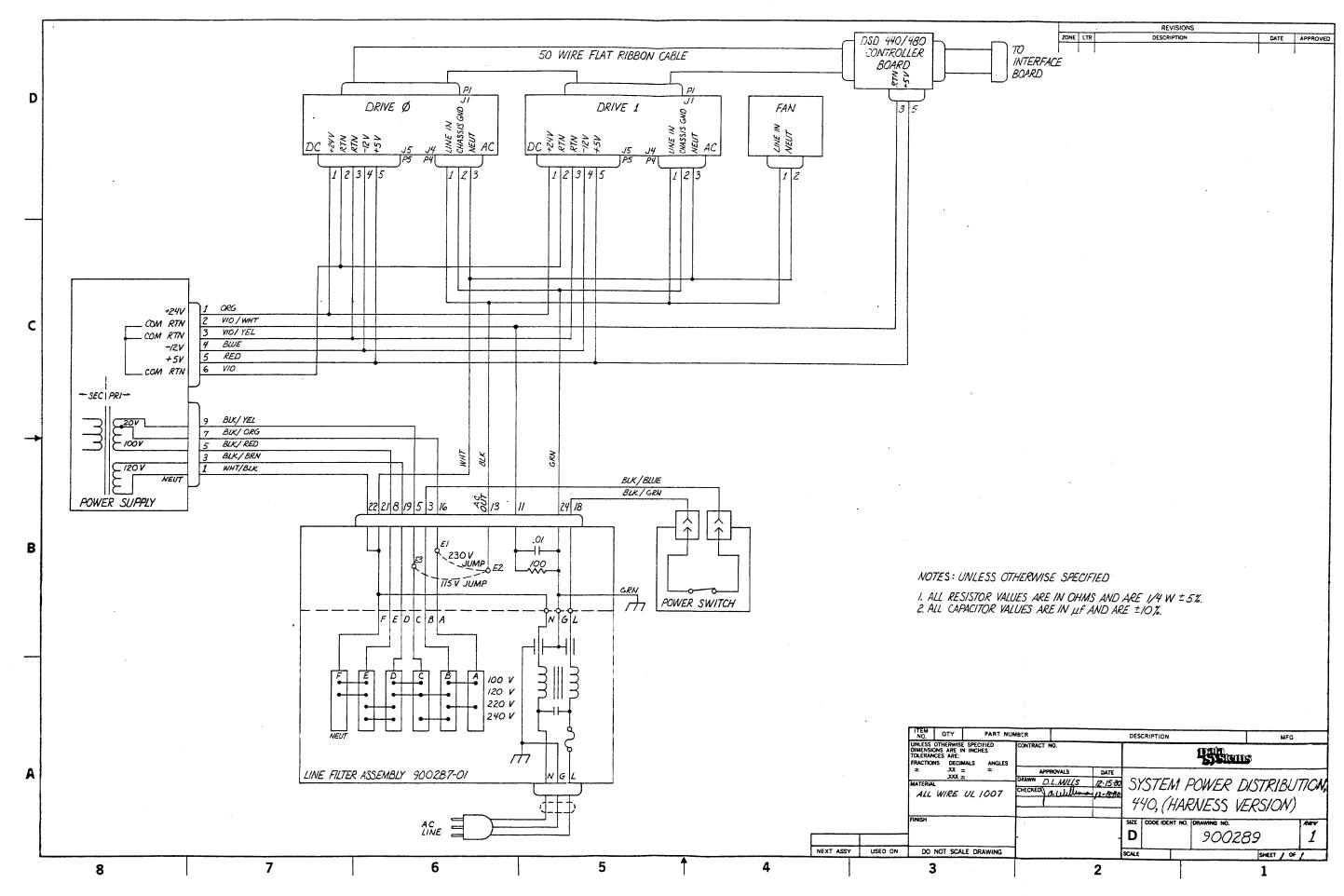

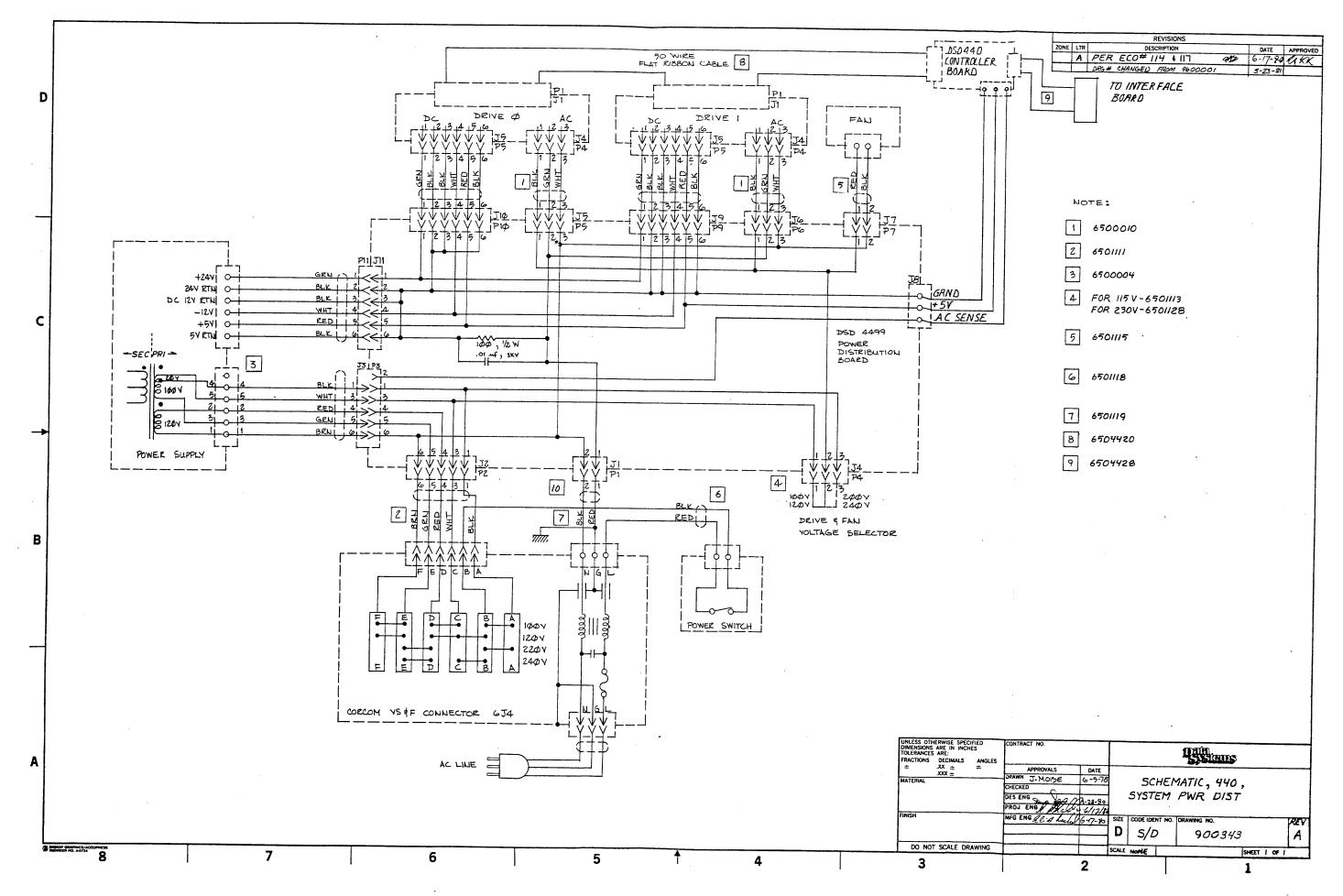

| 5-1        | System Power Distribution, Panel Version (0343)   | 5-2  |

| 5-2        | System Power Distribution, Harness Version (0289) | 5-3  |

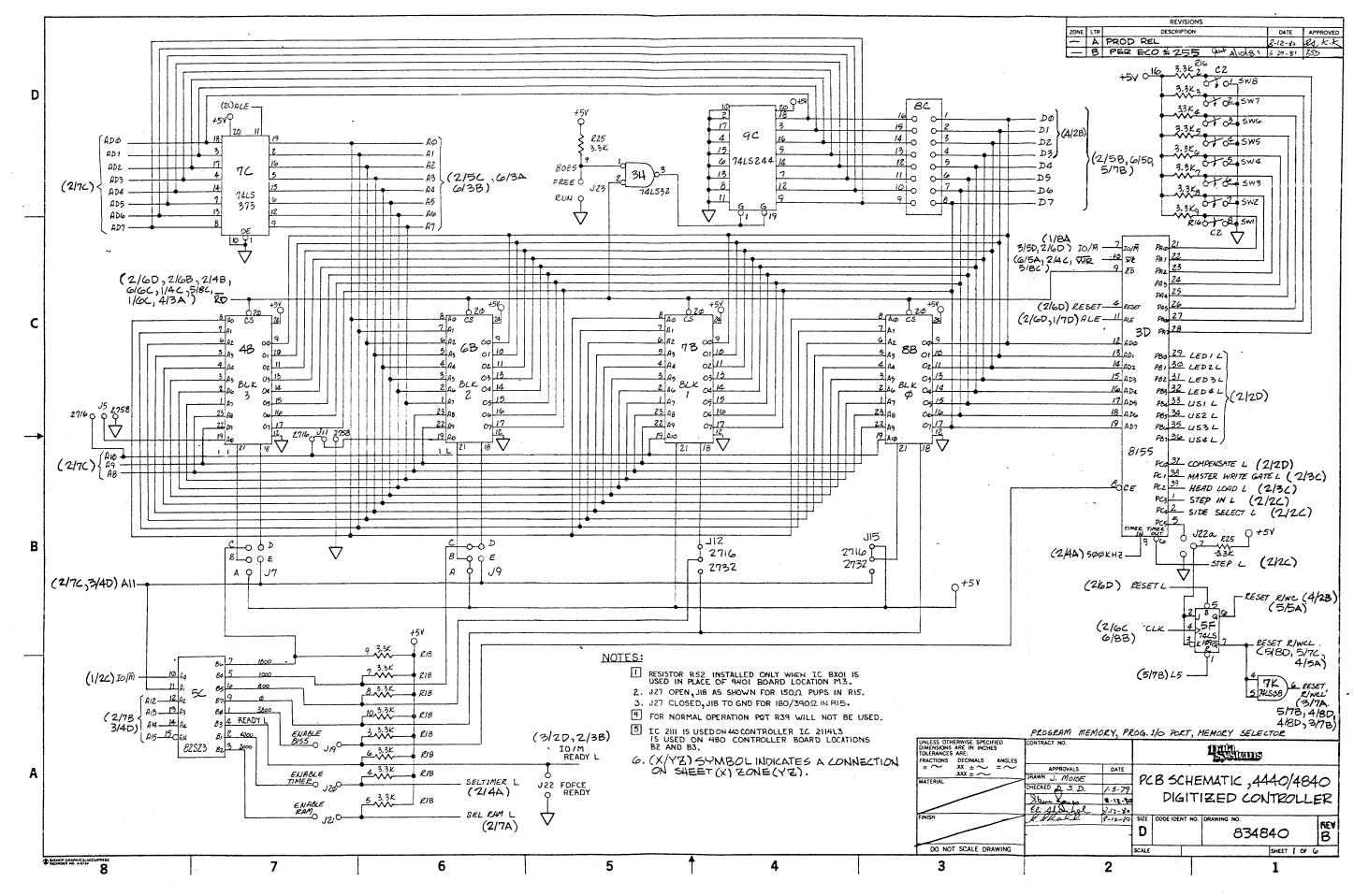

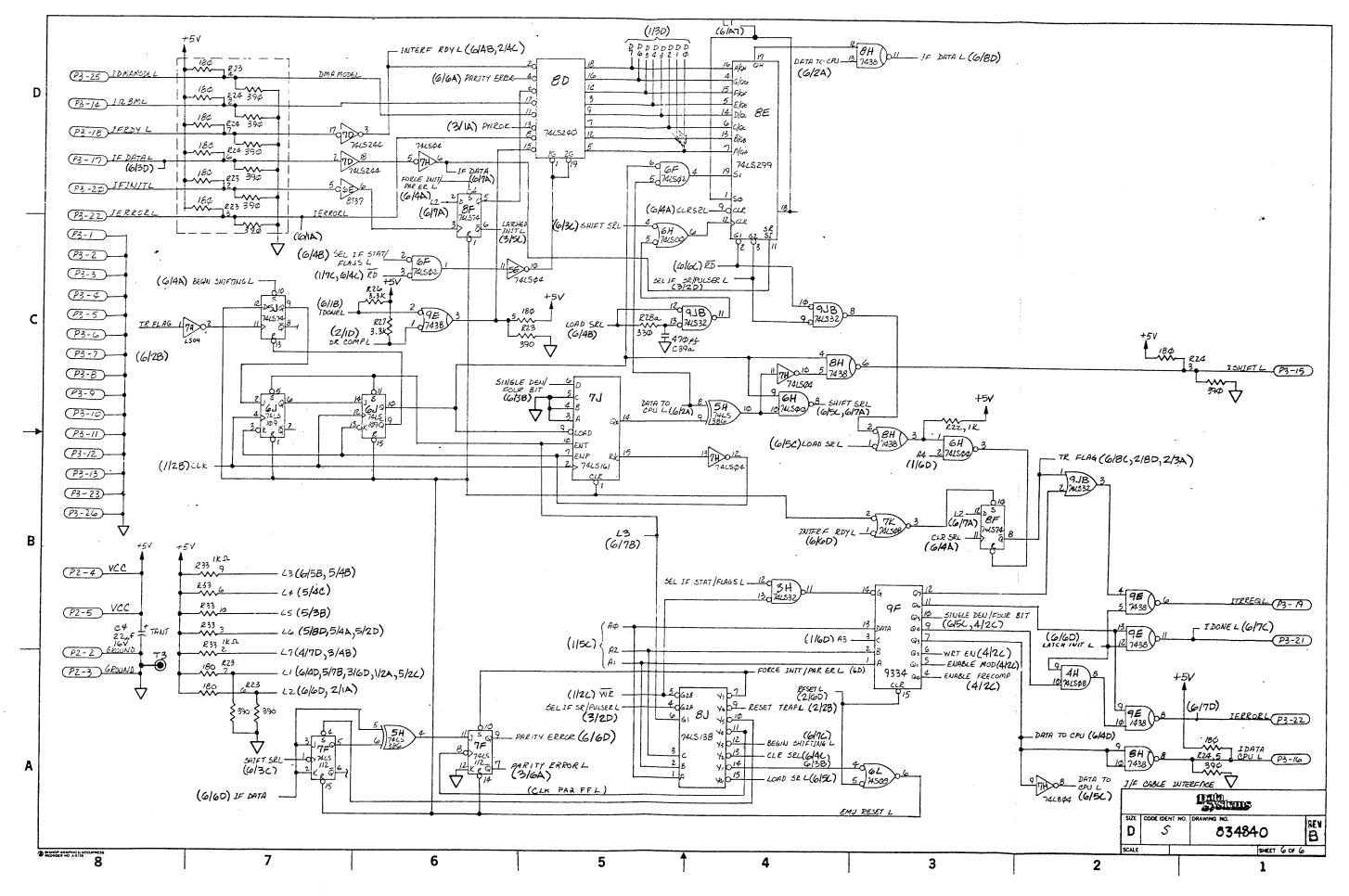

| 5-3        | 440/480 Controller Module (4840)                  | 5-4  |

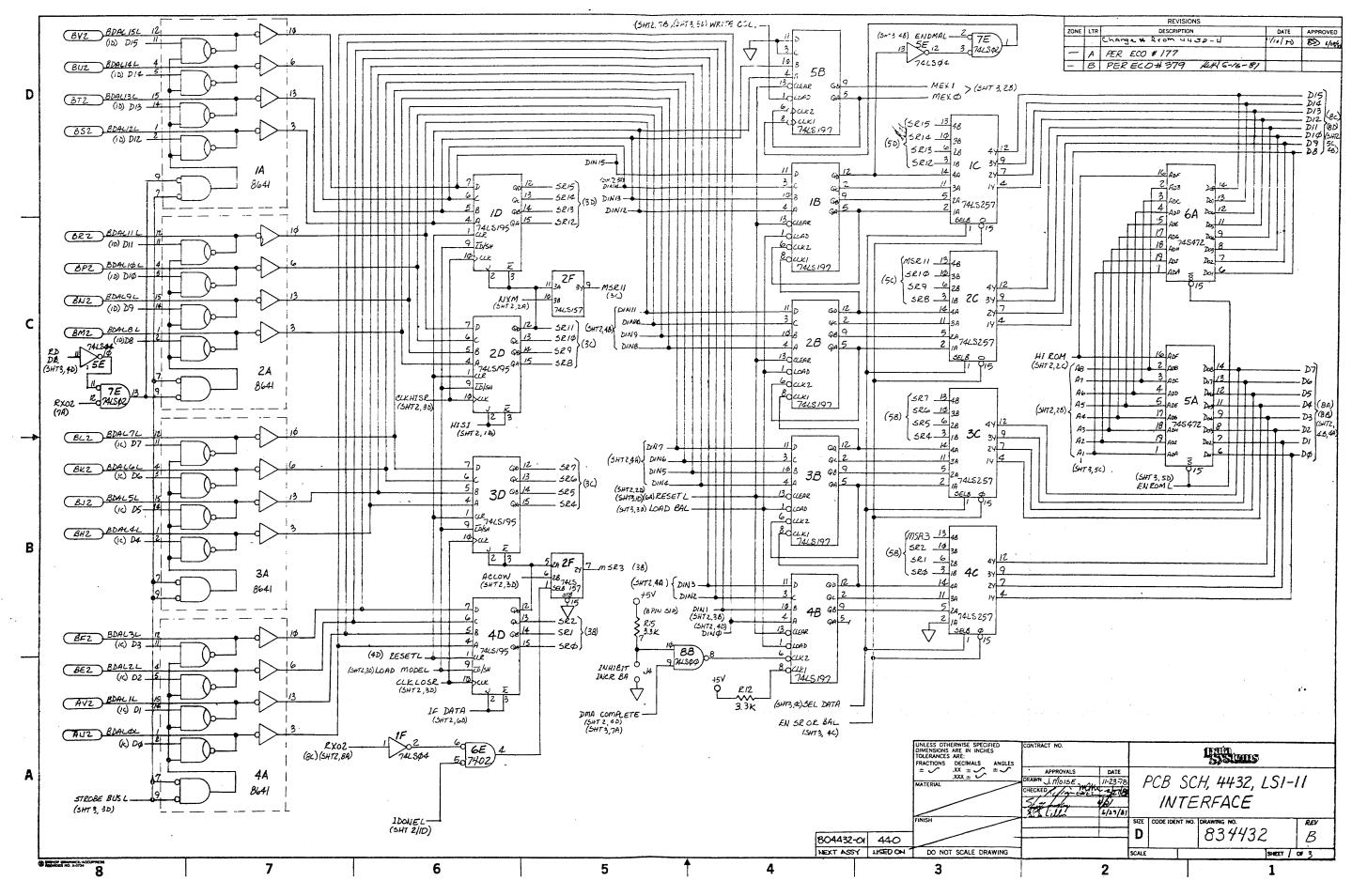

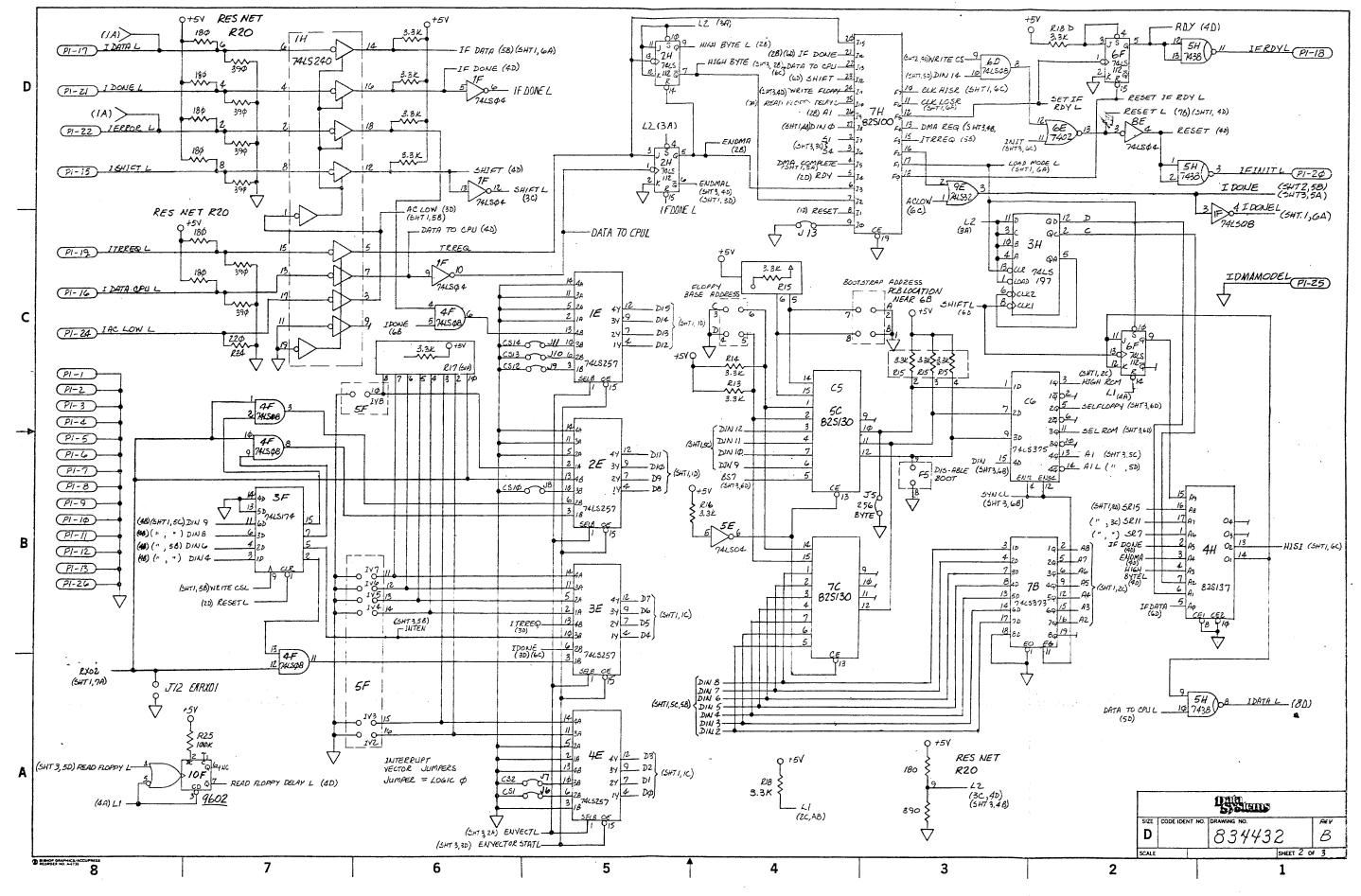

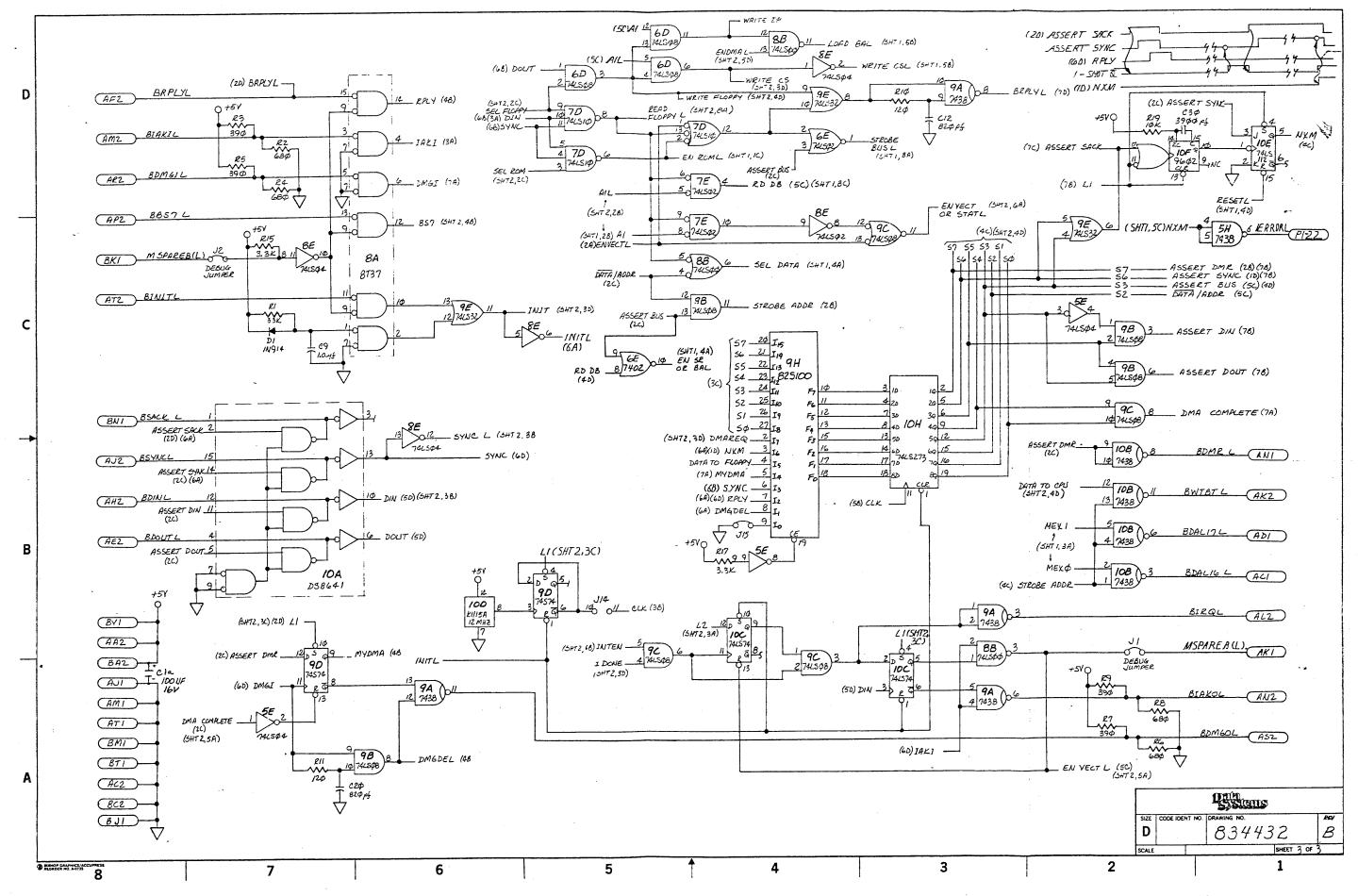

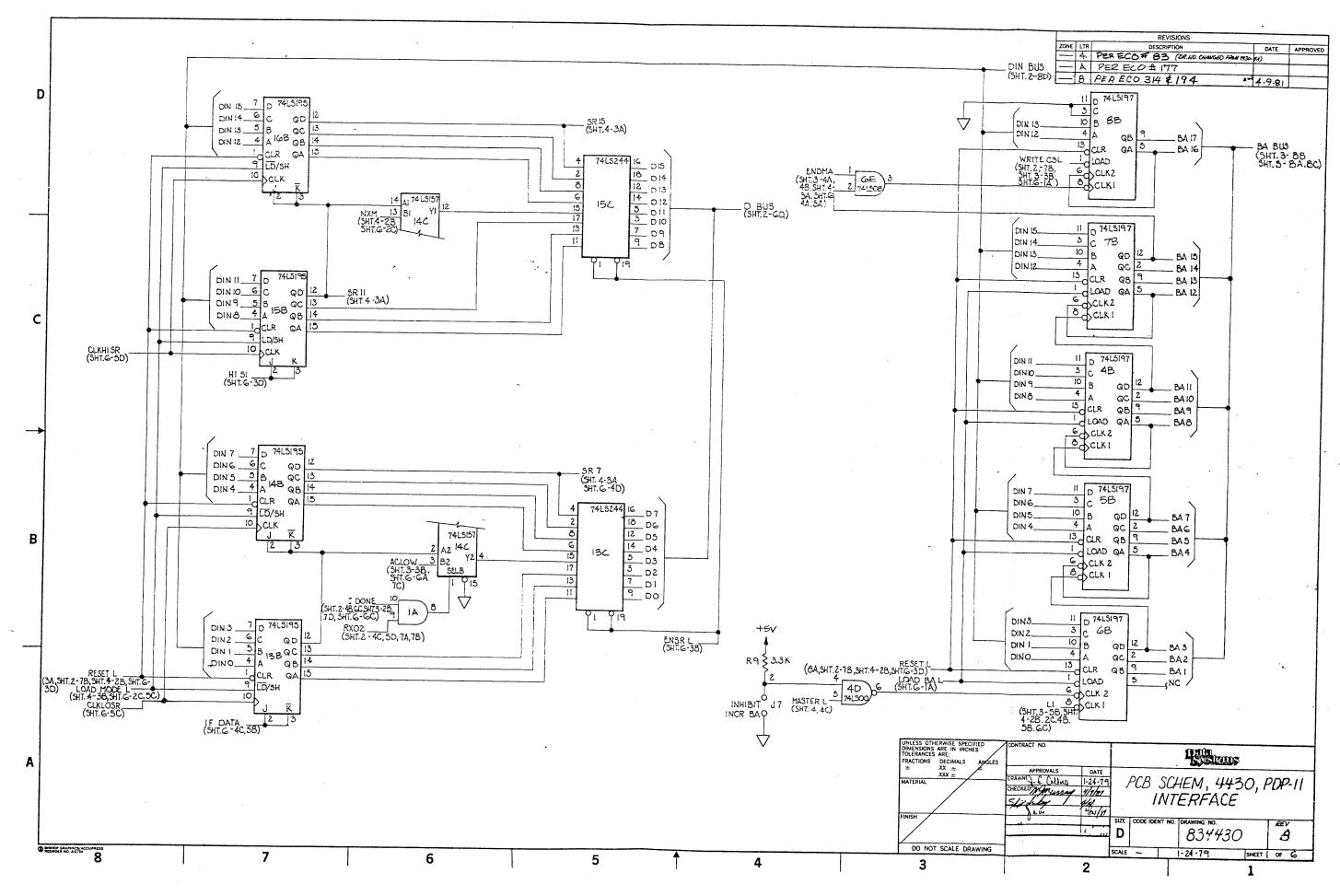

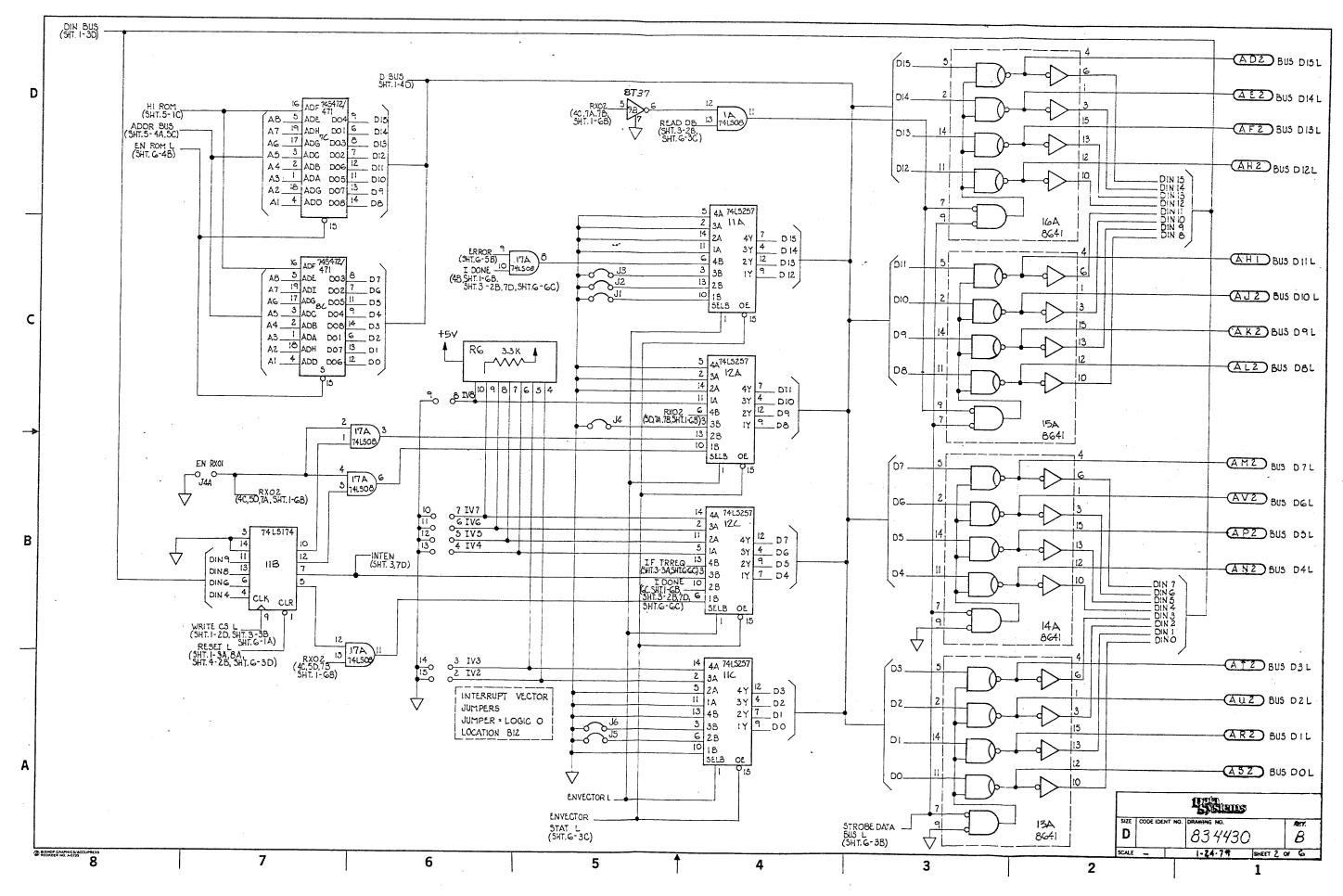

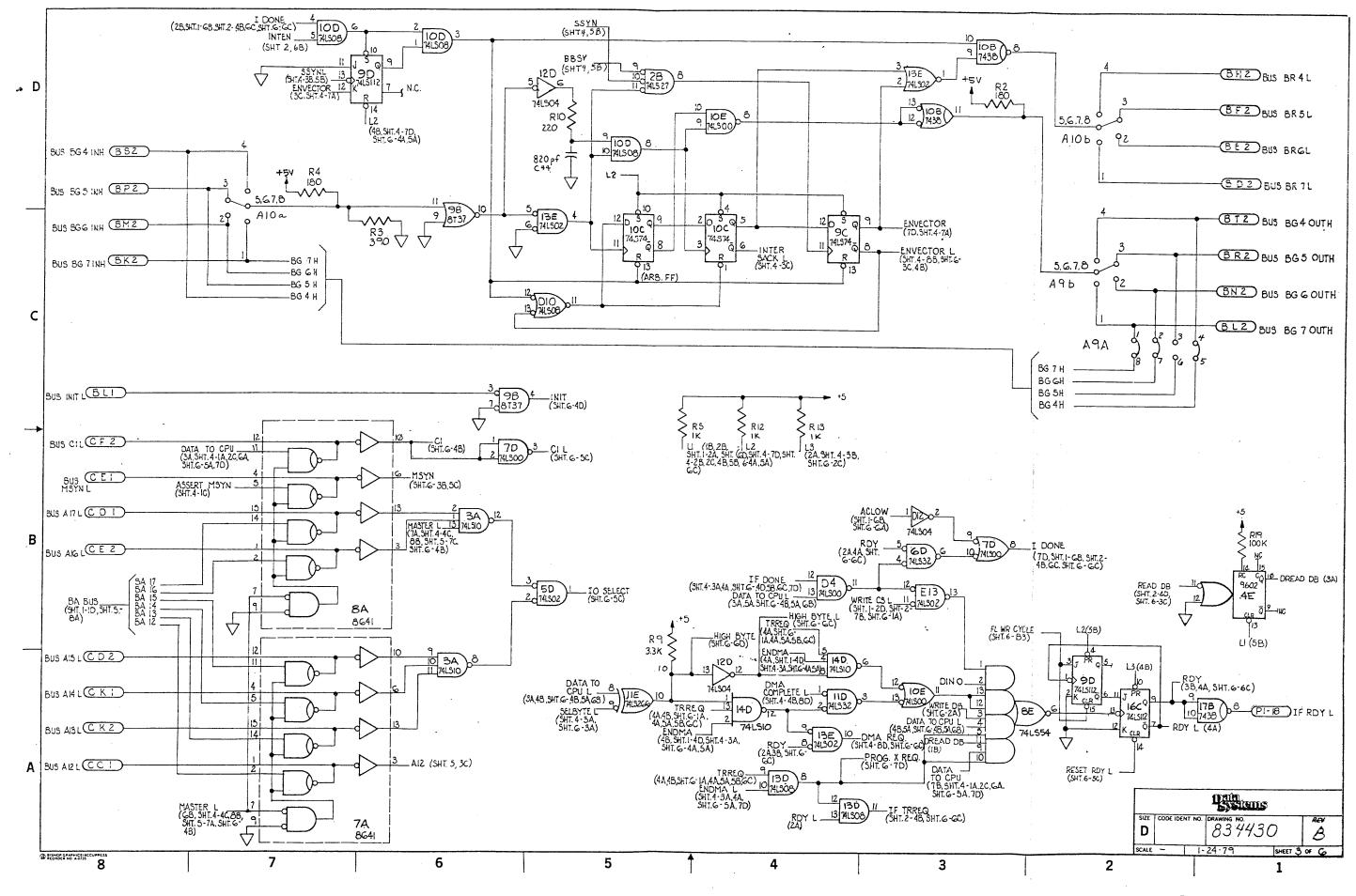

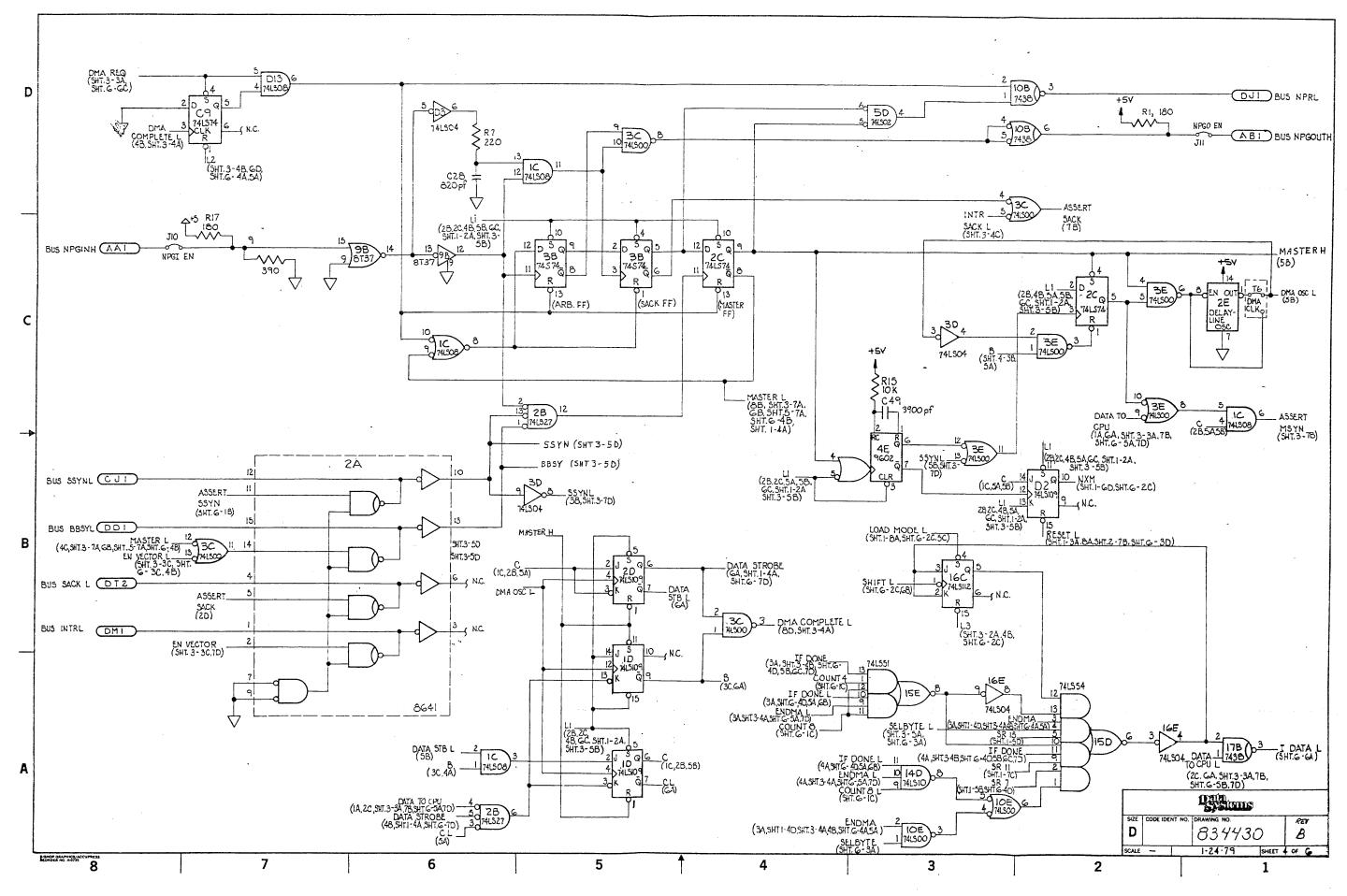

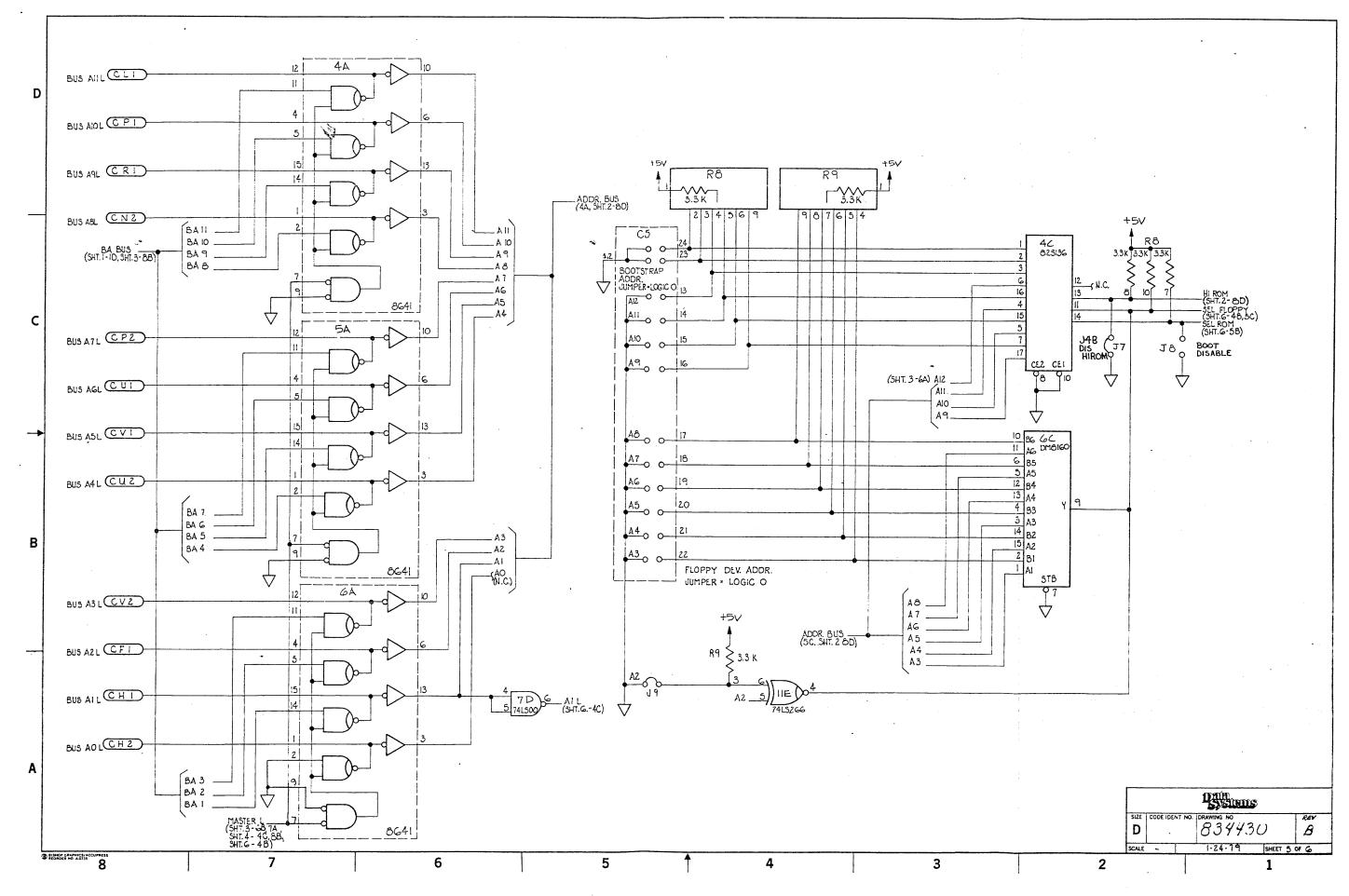

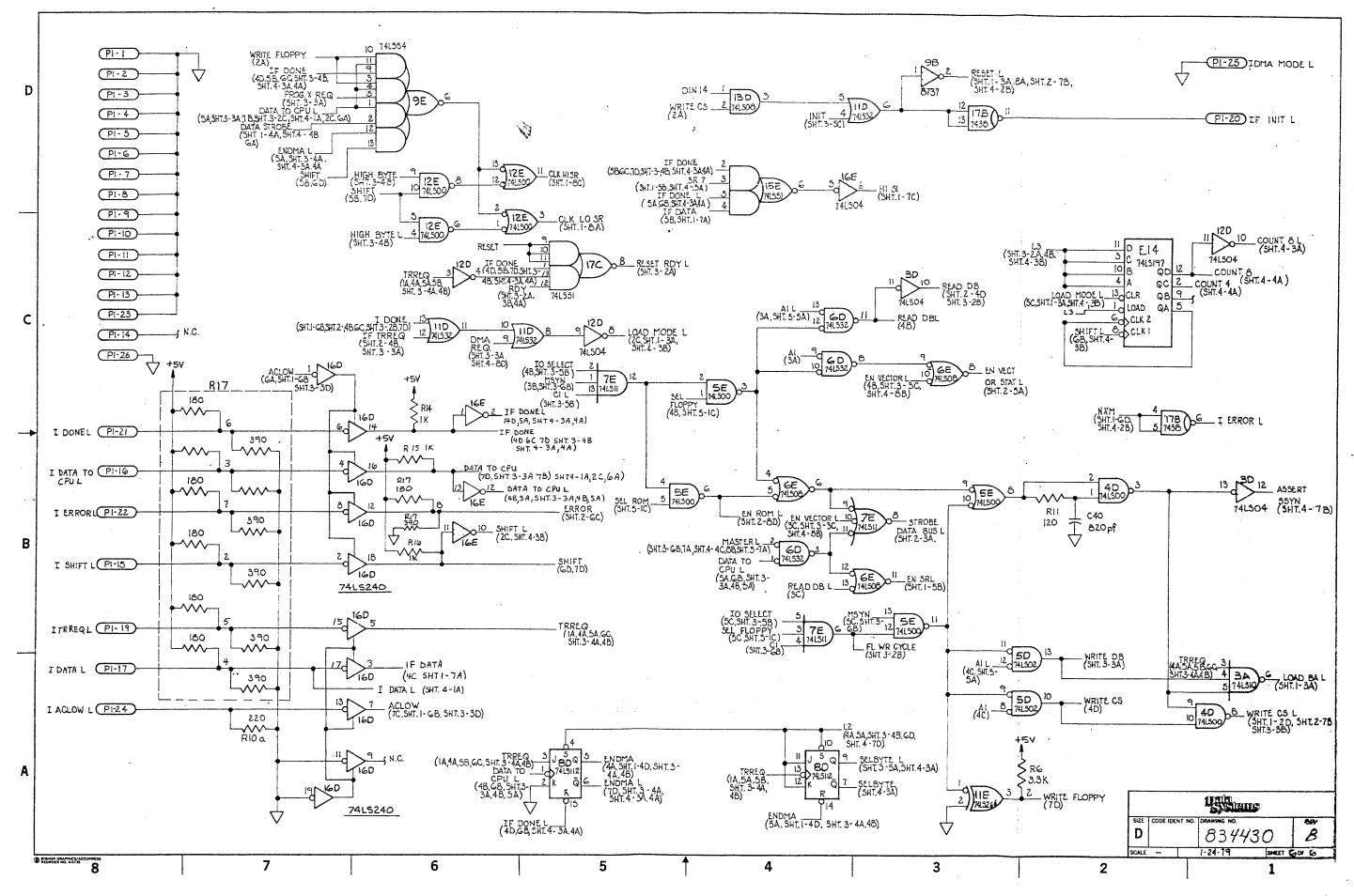

| 5-4        | 440/480 LSI-11 Interface Module (4432)            | 5-10 |

| 5-5        | 440/480 PDP-11 Interface Module (4430)            | 5-13 |

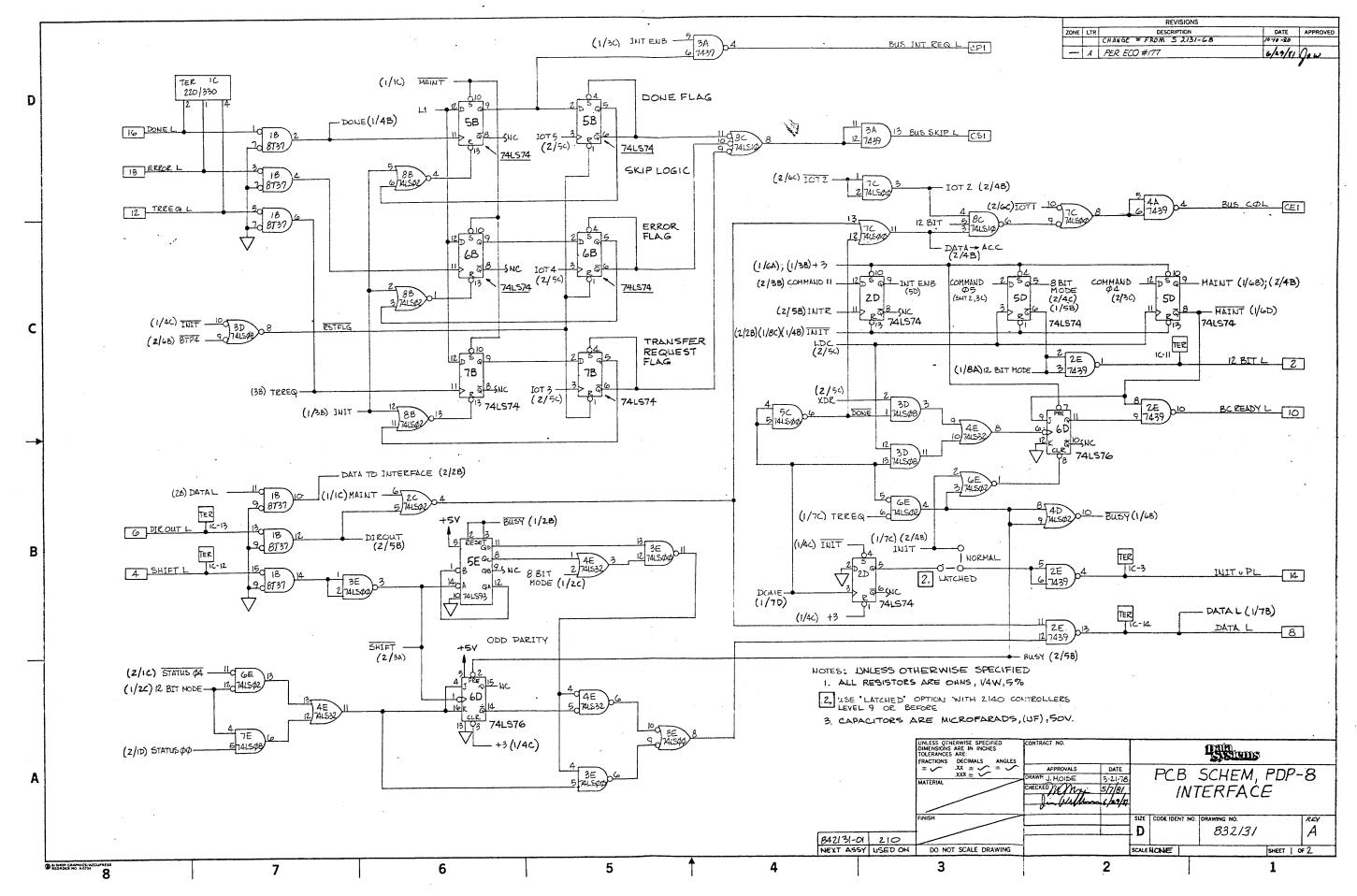

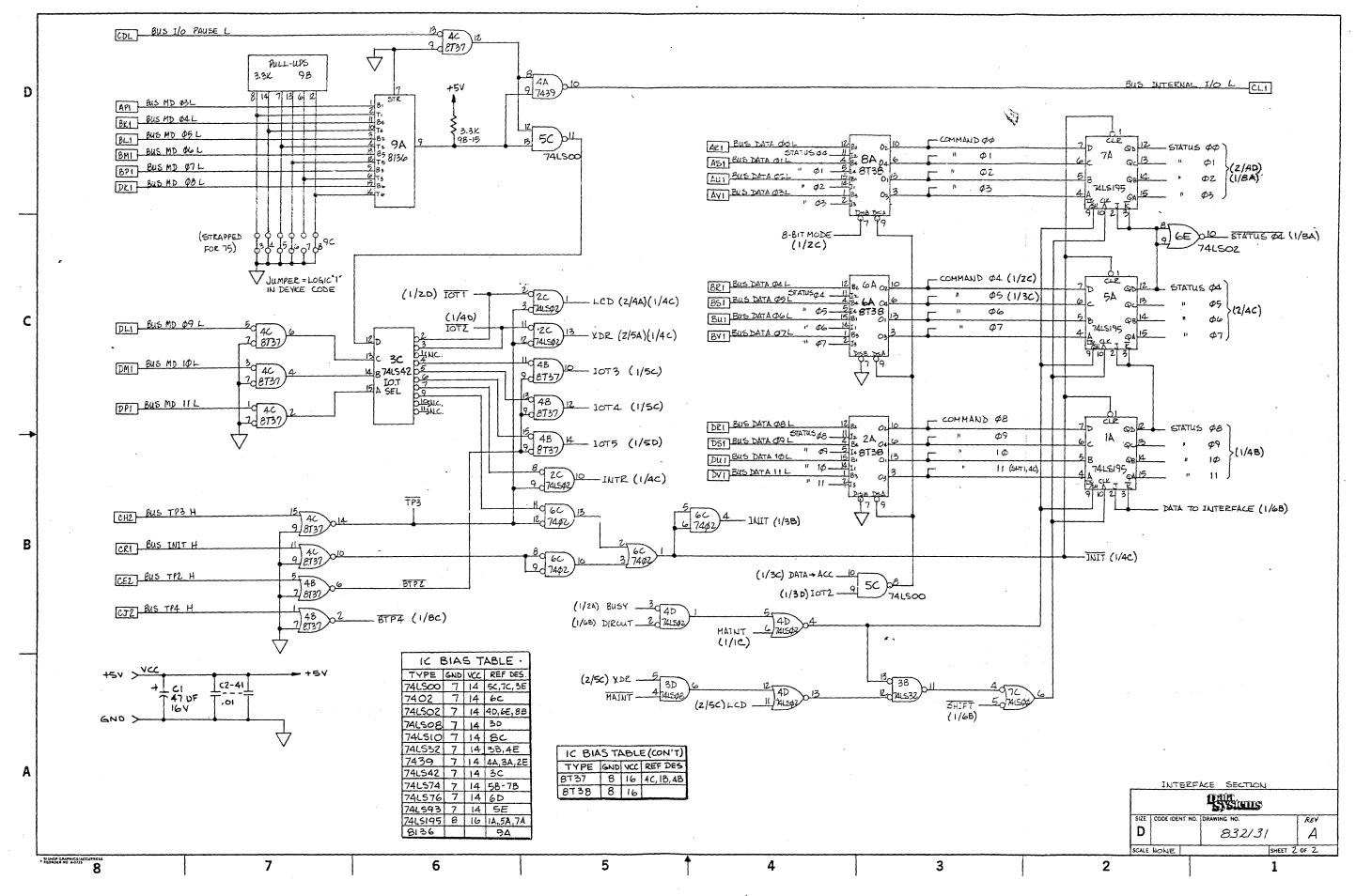

| 5-6        | 440 PDP-8 Interface Module (2131)                 | 5-19 |

# 1.0 GENERAL INFORMATION

# 1.1 Purpose and Scope

The intended purpose of this publication is to provide detailed theory of operation and necessary servicing information for the DSD 440 and DSD 480 Flexible Disk Data Storage Systems.

The manual contains five major sections. Section 1 contains general information, a list of related publications, a summary of follow-on services available to the customer, and a statement concerning our service philosophy. Section 2 provides information about the three computer interface modules available for use with the systems. Section 3 contains a detailed description of the operation of the controller module used with the systems. Section 4 contains instructions for servicing the equipment, lists recommended test equipment, and provides fault analysis procedures. Section 5 contains an illustrated parts breakdown, a power distribution panel assembly drawing, component layout drawings, and schematics for the equipment.

The Shugart Service Manuals listed in Paragraph 1.2 are shipped with The System User's Manuals, as obtained from Shugart. Data Systems Design accepts no responsibility for the content or accuracy of these publications.

### 1.2 Related Publications

The following is a list of related publications referenced in this manual. The service technician attempting repair of the DSD 440 and 480 Flexible Disk Data Storage Systems must be thoroughly familiar with the contents of the listed publications.

- DSD 440 Flexible Disk System Installation and Programming Manual

- DSD 480 Flexible Disk System Installation and Programming Manual

- Shugart SA800/801 Single-Sided Diskette Drive Service Manual (applicable to DSD 440)

- Shugart SA850/851 Double-Sided Diskette Drive Service Manual (applicable to DSD 480)

- Intel MCS-80/85<sup>(m)</sup> Family User's Manual

### 1.3 Service Philosophy

The service philosophy of Data Systems Design has been to limit any field maintenance to preventive maintenance and the replacement of subsystem modules (controller, interface modules, disk drives, power supply, and interface cable). The maintenance instructions contained in the User's Manuals are considered adequate for that level of maintenance.

The detailed theory of operation, error code analysis, and servicing procedures contained in the following sections of this manual are intended for use by senior level technicians who may be required to repair individual subsystem modules at facilities with required bench test setups.

#### 1.4 Special Support Items

For those activities doing field service on the DSD 440 and 480 equipment, the DSD Customer Service Department has the following items available:

- Subsystem Spares Kits

- Component Spares Kits

- DSD 440/480 Extended Self-Test Kit.

For information concerning these items, contact either of the listed offices:

#### DSD CUSTOMER SERVICE

Data Systems Design maintains a fully staffed Customer Service Department. If at any time during inspection, installation, or operation of the equipment you encounter a problem, contact one of these offices. Our trained staff can help you diagnose the cause of failure, and if necessary, speed replacement parts to you. Any time you need to return a product to the factory, please contact Customer Service for a Material Return Authorization Number.

Data Systems Design Customer Service

WESTERN REGION 718 Sycamore Milpitas, CA 95035 (408) 946-5815 CENTRAL REGION 5050 Quorum Drive Suite 339 Dallas, TX 75240 (214) 980-4884

EASTERN REGION

51 Morgan Drive

Norwood, MA 02062

(617) 769-7620

TWX: 710-336-0120

CORPORATE HEADQUARTERS

2241 Lundy Avenue

San Jose, CA 95131

i.

For products sold outside the United States, contact your local DSD distributor for parts and customer service assistance.

#### 1.5 Service Limitations

It should be noted that any repair actions or modifications that change the performance characteristics, affect the integrity of board traces, or otherwise render the equipment beyond economical repair will void the warranty and make the module ineligible for factory exchange.

#### 2.0 INTERFACE MODULES

### 2.1 Introduction

Data Systems Design manufactures interface modules for the DEC LSI-11, PDP-11, and PDP-8 computers. Two of these modules, DSD Part No. 4432 (LSI-11) and DSD Part No. 4430 (PDP-11), are used with both the DSD 440 and DSD 480 Systems. The PDP-8 Interface Module, DSD Part No. 2131, is used only with the DSD 440 System.

Both the systems User's Manuals (440 and 480) provide information concerning installation of the interface modules in the host computer, and detailed discussion of the programming protocols for each operational mode used to interface communications between the DSD Controller Module and the host computer.

# 2.2 Interface Bus Specifications

The DSD 440/480 Interface Bus (I-Bus) connects the system controller modules, or the diskette storage subsystem, to the computer interface modules, which in turn connects to the input/output bus of the host computer. The I-Bus is implemented on 26-conductor flat cable. It consists of 11 low-true signals, a serial data line, associated hand-shaking, and parallel status signals.

### Signals and Pin Connections

Table 2-1 lists all cable pin connections, identifies each by signal and source of the signal, and type termination used on each line.

### Signal Descriptions

IERROR L (Error line): The error line is asserted by the controller whenever a given function is terminated because of an error. When the controller is asserting the Error line, both the Done line and the Data-To-CPU line are also asserted. The Error line is negated either when the interface generates an initialize, or when a new command is sent to the controller. PDP-11 and LSI-11 interface modules may also assert the Error line when a non-existent memory error occurs during a DMA operation. This will cause the controller to execute an error termination.

<u>IFINIT L (Initialize line)</u>: The INIT line is asserted by the interface module in response to an I/O reset, or some other resetting function. The controller responds to an INIT by jumping to a special portion of microcode which initializes the controller/drive subsystem. The controller can mask out the INIT interrupt so that certain important operations, such as SECTOR WRITE routines, are not halted at critical times. Accordingly, the INIT line is latched in the controller until properly processed. The minimum pulse width for the INIT signal is one microsecond.

The initialization microcode in the controller includes the following: (The INIT sequence is further described in Section 4.)

- 1) Resets the Error and Done lines

- 2) Runs the controller self-tests

- 3) Checks the switch bank to see if the HyperDiagnostic<sup>®</sup> modes have been selected

- 4) Initializes all variables

- 5) Determines what drives are present and homes them

- 6) Reads Track 1, Sector 1 of Drive 0 into the DATA BUFFER

Table 2-1. I-Bus Signals and Pin Connections

|                                      |               |                 | Termination <sup>1</sup> |           |

|--------------------------------------|---------------|-----------------|--------------------------|-----------|

| Pin No.                              | Signal        | Source          | Controller               | Interface |

| 1                                    | Ground        | N/A             |                          |           |

| 2                                    | Ground        | N/A             |                          |           |

| 3                                    | Ground        | N/A             |                          |           |

| 4                                    | Ground        | N/A             |                          |           |

| 5                                    | Ground        | N/A             |                          |           |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | Ground        | N/A             |                          |           |

| 7                                    | Ground        | N/A             |                          |           |

| 8                                    | Ground        | N/A             |                          |           |

| 9                                    | Ground        | N/A             |                          |           |

| 10                                   | Ground        | N/A             |                          |           |

| 11                                   | Ground        | N/A             |                          |           |

| 12                                   | Ground        | N/A             |                          |           |

| 13                                   | Ground        | N/A             |                          |           |

| 14                                   | I 12BM L      | Interface       | A                        |           |

| 15                                   | I SHIFT L     | Controller      | i                        | A         |

| 16                                   | I DATATOCPU L | Controller      | l '                      | A         |

| 17                                   | IFDATA L      | Bidirectional   | A                        | Α         |

| 18                                   | IF RDY L      | Interface       | A-                       |           |

| 19                                   | ITRREQ L      | Controller      |                          | Α         |

| 20                                   | IFINIT L      | Interface       | A                        |           |

| 21                                   | IDONE L       | Controller      | C                        | A         |

| 22                                   | IERROR L      | Bidirectional 2 | A                        | A         |

| 23                                   | KEY 3         | N/A             |                          |           |

| 24                                   | IACLOW L      | Controller      |                          | B         |

| 25                                   | IDMA MODE L   | Interface       | A                        |           |

| 26                                   | Ground        | N/A             |                          | :         |

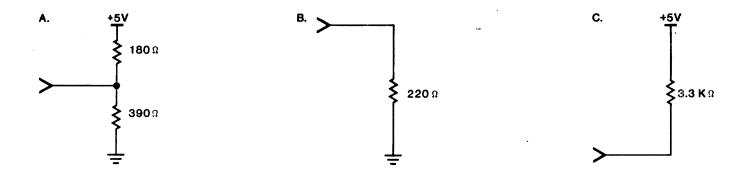

Notes: 1. Termination Types:

- 2. DSD 2131 interface cannot source this signal.

- 3. Pin 23 reserved for key.

If all the tasks are successfully completed, the Done line will be asserted. If an error occurs during any initialization function, both the Done and the Error lines will be asserted. If the controller enters the HyperDiagnostic mode, neither Done nor Error will be asserted.

IDMAMODE L (DMA Mode line): When the DMA Mode line is asserted by the interface card, this indicates to the controller that Direct Memory Access is to be employed when performing the FILL BUFFER, EMPTY BUFFER, AND READ ERROR CODE/READ EXTENDED STATUS functions. If the DMA Mode line is negated, this indicates that the interface card is capable only of programmed I/O. The controller microcode tests this line in many places to determine the protocol used on the I-Bus. The DMA Mode line should be asserted only when the controller is in the RX02 mode.

I12BM L (12-Bit Mode line): This line is asserted by the interface card to indicate that it is connected to a 12-bit computer, such as the PDP-8. The I-Bus protocols are again modified according to the state of this line.

<u>IDATATOCPU L (Data-To-CPU line)</u>: When this line is asserted by the controller, the direction of data transfer on the data line is from the controller to the interface (floppy disk to CPU). Conversely, when negated, the direction of data transfer is from the interface to the controller. An INIT function always negates this signal.

Normally, the Data-To-CPU line is placed in the appropriate state by the controller before TRANSFER REQUEST is asserted. In RX02 DMA Mode, however, the controller also uses the Data-To-CPU line in conjunction with the Transfer Request line to inform the interface when to switch from doing data transfers by programmed I/O, to doing them by DMA. The DMA mode is initiated when the controller asserts the Data-To-CPU line while the Transfer Request line is asserted. If the direction of data transfer, specified by the remainder of the current command, is from computer to controller, the controller will negate the Data-To-CPU line again. The interface should return to programmed I/O mode when the controller asserts the Done line.

IFDATA L (Interface Data line): The Interface Data line is bidirectional. It is used to transfer data, commands, and some status between the interface board and the controller in the form of 8- or 12-bit serial data streams. The most significant bit is always shifted first. DSD interface boards place an odd parity bit on the Interface Data line at the end of any 8- or 12-bit shift, when the direction of data transfer is from interface to controller. The controller performs a parity check only for commands and parameters, not for data. The controller does not generate parity.

ISHIFT L (Shift line): The Shift line is pulsed by logic in the controller and acts as a clock for the Interface Data line, moving data in and out of shift registers connected to each end of the Interface Data line.

IDONE L (Done line): The Done line, when negated, indicates that the controller is busy performing some function and cannot accept a new command (an INIT function may be performed at any time). When the Done line is asserted and the Data-To-CPU line is negated, the controller is ready to accept a new command.

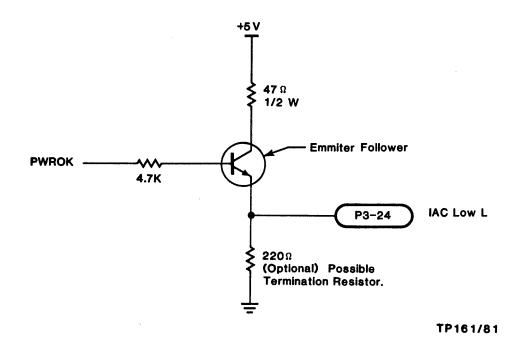

IACLOW L (AC Low line): This line is essentially a power fail detect signal. The controller asserts this line to indicate a drive box power failure. When a power fail is detected, all controller operations are terminated at their normal completion point, and no further operations are started. The driver on the controller is a 2N4124 emmitter-follower, sourcing +5 volts and current limited by a 47 ohm, \frac{1}{2}-watt resistor.

ITRREQ L (Transfer Request line): Transfer Request is the principal signal by which the controller initiates the propagation of serial data streams between the controller and the interface board. Transfer Request works in conjunction with the Data-To-CPU line and IFRDY to form a three wire bidirectional handshake.

When Data-To-CPU is asserted (data input to the CPU), the controller asserts Transfer Request as soon as it has sent enough shift pulses to load the data into the interface shift register. When the data has been input to the CPU, the interface asserts the IFRDY line. On detecting this, the controller negates the Transfer Request line. The interface, in turn, negates IFRDY. The result is that a byte has been transferred from the controller to the interface and on to the CPU.

The controller asserts Transfer Request with Data-To-CPU negated when it needs data from the interface. The interface, when it obtains data from the CPU, asserts the IFRDY line. This indicates that the data is in the interface shift register. The controller then negates Transfer Request, causing the interface to negate IFRDY. The controller then shifts the data from the interface shift register, using the Shift line as a clock (except that DMA memory addresses are not shifted).

IFRDY L (Interface Ready line): The Interface Ready line works in conjunction with the Transfer Request line during data transfers, as described above.

In addition, the interface board uses IFRDY to transfer a new command to the controller. When the controller is awaiting a new command, the Done line will be asserted and the Data-To-CPU line will be negated. The controller interprets IFRDY as an indication that a command is available to be shifted over on the Data line, using the Shift line as a clock. On receipt of the command, the controller will negate the Done line and the interface should negate IFRDY.

# **Detailed Timing**

The following paragraphs discuss details of timing of data transfers on the I-Bus. Protocols associated with specific commands are covered in your DSD 440/480 Systems User's Manuals.

Transfers of data and commands are generally under the control of the controller module. The direction of data transfer is determined by the state of the IDATATOCPU line. The following general rules apply:

- 1. The interface can drive the Interface Data line only when the Data-To-CPU line is negated. The controller will drive the Interface Data line only when the Data-To-CPU line is asserted.

- 2. The interface may assert the Interface Ready line only when the controller is asserting the Transfer Request line, or asserting the Done line (new command).

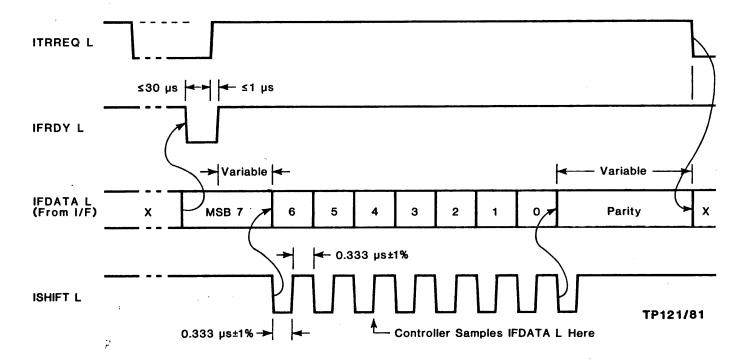

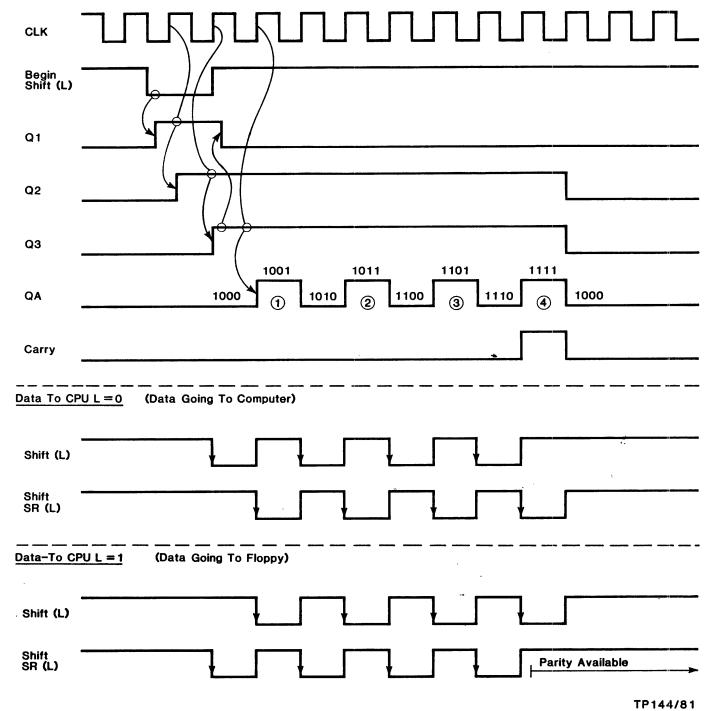

3. Data is always transferred most significant bit first. When the direction of transfer is to the controller (Data-To-CPU line negated), the interface should place the first bit on the line as soon as it is available from the CPU. A new bit should be shifted onto the Interface Data line on each high-to-low transition of the Shift line. The interface must maintain a parity count (odd parity) and the parity bit must be placed on the Data line on the last shift pulse. This parity bit must remain available on the Data line until the controller asserts Transfer Request, or Data-To-CPU. Figure 2-1 (timing diagram) shows details of the operation.

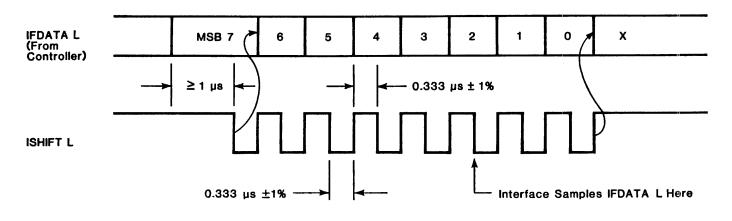

Figure 2-1. Timing, Interface to Controller

- 4. When the direction of data transfer is toward the CPU, the controller will assert Data-To-CPU and will control the Interface Data line. The interface must be able to accept new data at any time. The controller will place the most significant bit on the Data line. The interface should shift the bit into its shift register on the high-to-low transition of the Shift line. The controller will shift a new bit onto the Data line near the low-to-high transition of the Shift line. The controller does not generate parity. The Data line is meaningless after the last shift. Figure 2-2 (timing diagram) shows the details of this operation.

- 5. When the controller asserts Transfer Request, the interface is expected to eventually assert Interface Ready. On sensing Interface Ready, the controller will negate Transfer Request within 30 microseconds. On sensing the negation of Transfer Request, the interface should negate Interface Ready within 1 microsecond.

TP122/81

Figure 2-2. Timing, Controller to Interface

#### 3.0 CONTROLLER MODULE

### 3.1 Introduction

As currently shipped from the factory, the controller modules for the DSD 440 and 480 Systems are identified as follows:

DSD Part No. 804840-01 480 Systems DSD Part No. 804840-02 440 Systems

Functionally, the controller module used in both systems is the same. The differences between the two boards are because of the extended IBM format available only with the DSD 480 System. Basically, the differences reside in the microcode used, but also, a larger RAM chip is used on the DSD 480 controller module to accommodate the 1 K-byte sectors used in the extended IBM format.

The following theory of operation of the controller module is, therefore, applicable to both the DSD 440 and 480 system controller modules. In this manual, these modules are hereafter called the DSD 440/480 controller. The remainder of this section is arranged as follows:

- Overview

- 8085 Microprocessor

- Cable Connections

- Read/Write Controller

- Serial Data Path

- Phase-Locked-Loop Circuitry

- DC Power Sensing Circuit

#### 3.2 Overview

The DSD 440/480 controller is a general purpose floppy disk controller that can accommodate IBM single-density format and IBM, or DEC double-density format. It is implemented with state of the art LSI technology, and incorporates both an MOS microprocessor and a bipolar bit-slice microprocessor. It includes a high precision phase-lock-loop to guarantee accurate recovery of data from the floppy disk. It requires a single +5 volt supply, and is packaged on a single board measuring approximately 4.65 by 17.1 inches.

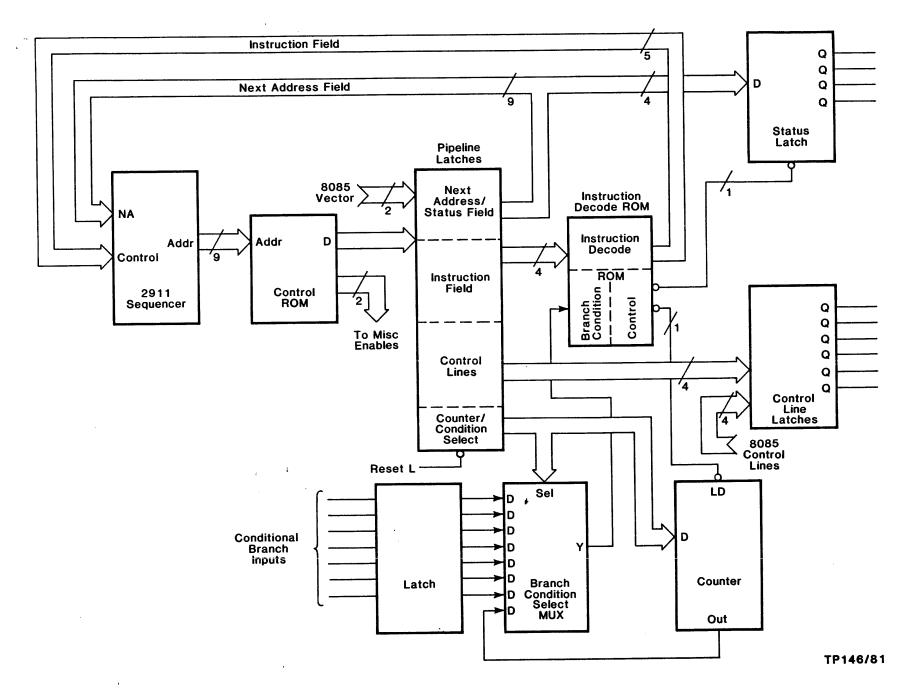

The DSD 440/480 controller was designed to accommodate a wide range of disk data formats. In order to accomplish this, a dual processor architecture was adopted. The first processor is the bi-polar bit-slice processor, based on the 2900 chip set. This high speed processor takes serial disk data and converts it to parallel, 8-bit wide data, that can be handled by the MOS microprocessor. The high speed bit-slice controller, called the Read/Write Controller (R/WC), has a basic cycle rate of 333 nanoseconds per instruction. There is enough microcode contained in the R/WC to recognize special data patterns, called address marks, that are present in the disk data formats used. The R/WC also contains all the logic to control the digital sections of the phase-lock-loop circuitry.

The controller module also contains an 8085 MOS microprocessor. The 8085 was chosen because it is a powerful, low cost, general purpose, 8-bit microprocessor that requires a single +5 volt supply. In addition, the 8155 MOS RAM with I/O ports and timer was incorporated because it includes a large number of essential functions in a relatively small space. The 8085 receives its instructions from up to four 2716 type PROMs.

The DSD 440/480 controller is a synchronous controller. A crystal controlled oscillator drives the 8085 microprocessor which, in turn, generates a signal called CLK that provides timing information for the rest of the circuitry.

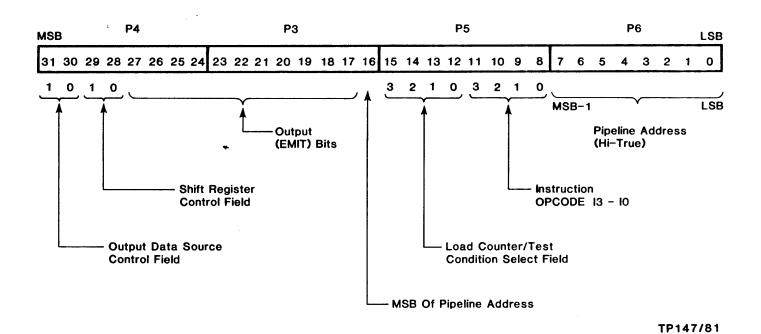

There are seven major busses in the DSD 440/480 controller. Three of these busses, the data bus, the address bus, and the control bus are related to the MOS microprocessor sections of the controller. Three additional busses, the microaddress bus, the P-Bus, and the next address bus are related to the R/WC. A final bus, the clock bus, consists of the various timing signals that drive major sections of the controller module. See Table 3-1 for a summation of the internal busses.

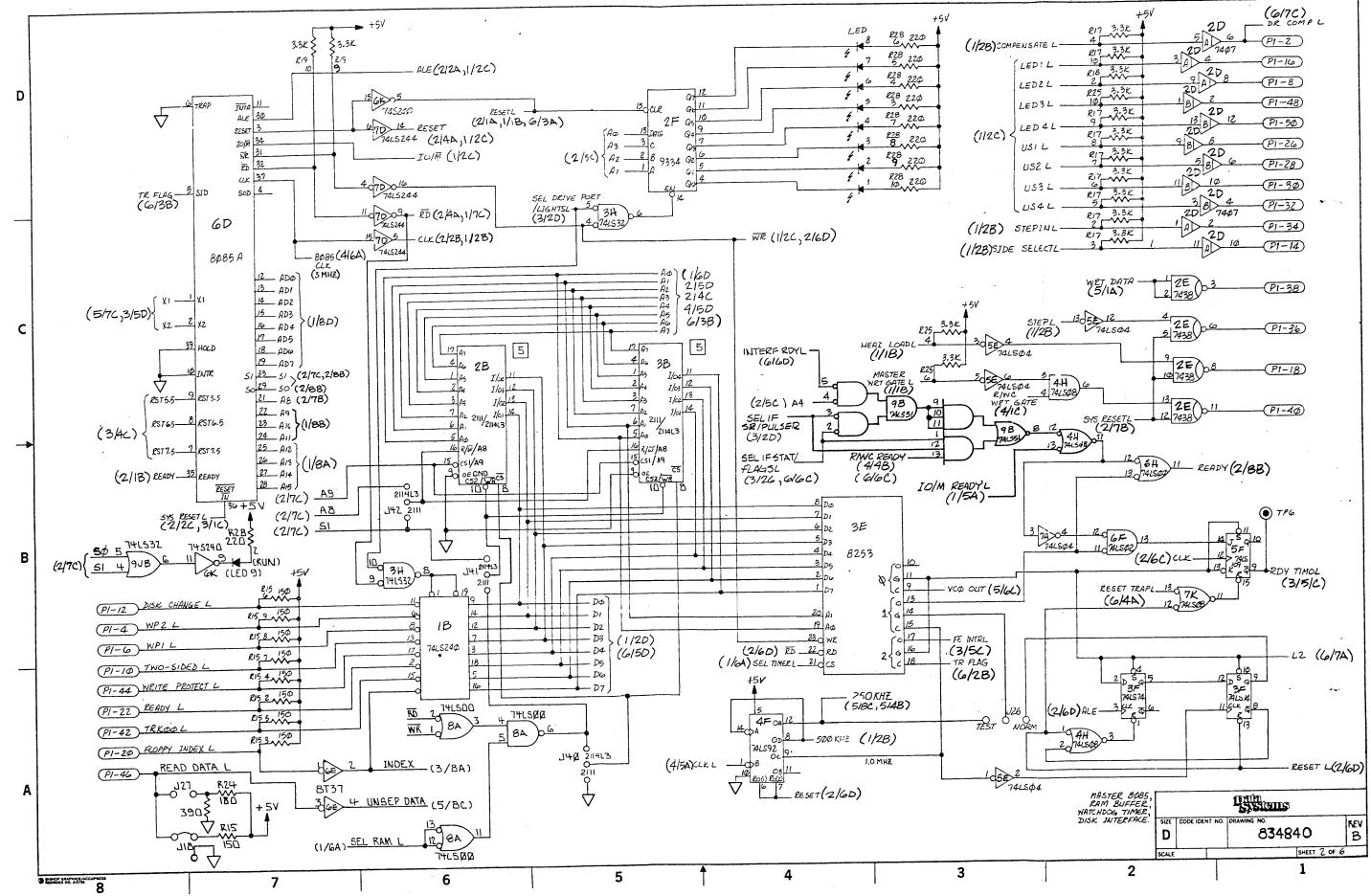

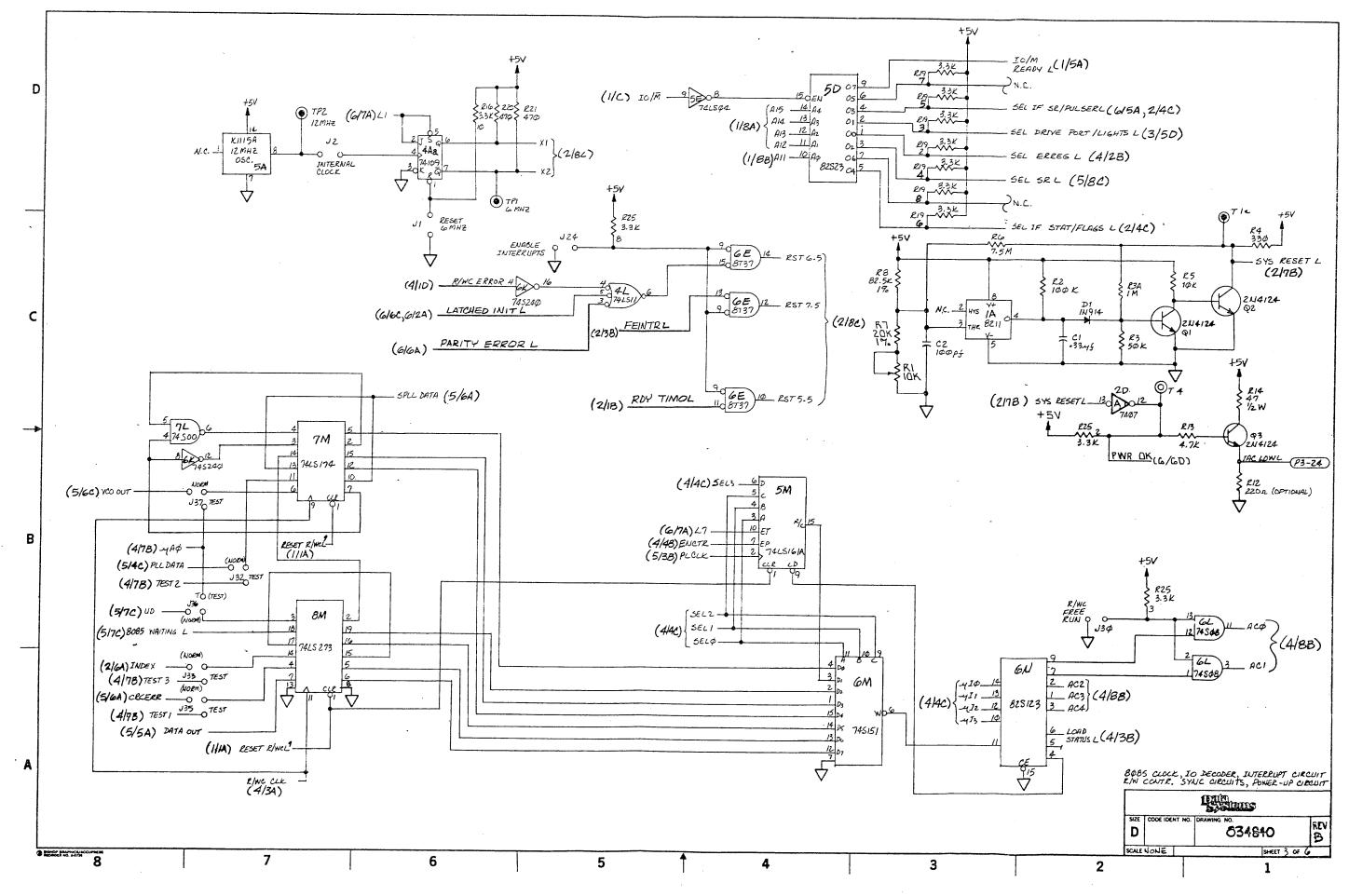

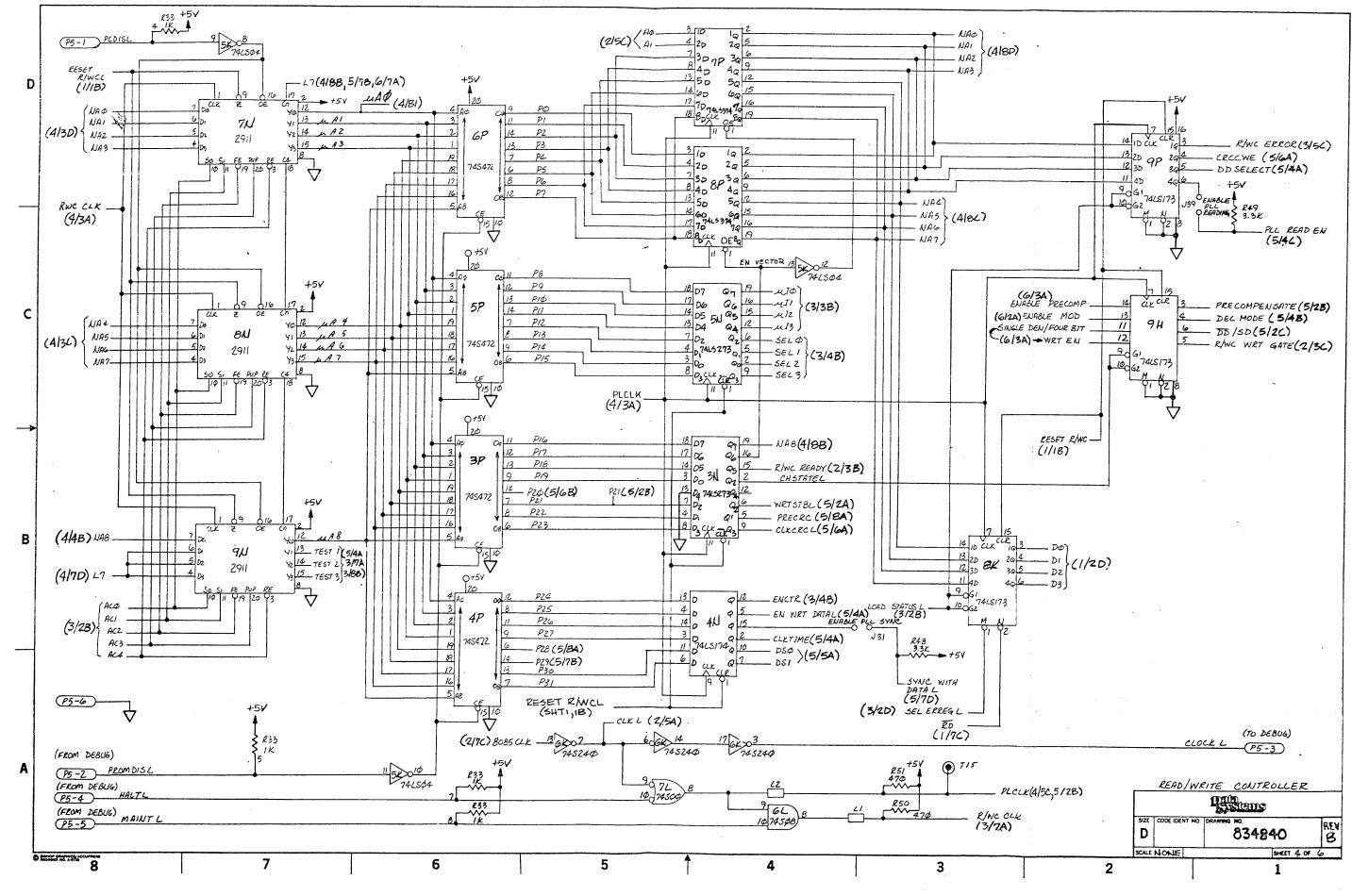

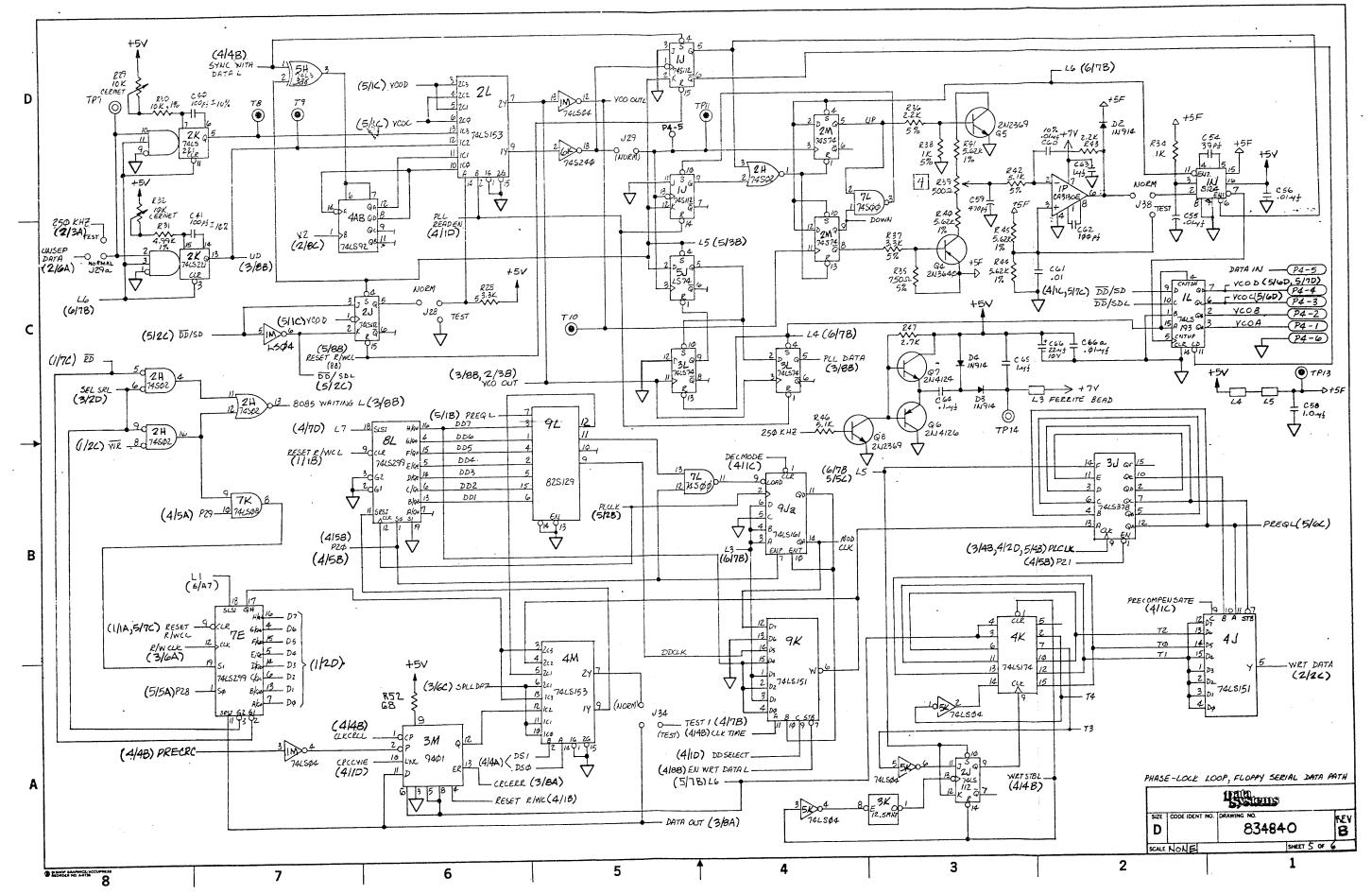

The DSD 440/480 schematic diagrams are located in Section 5 of this manual. Portions have been incorporated within the descriptive paragraphs that follow, where applicable. The user of this manual is expected to use the foldout feature of the schematics to follow the discussion.

# 3.3 8085 Microprocessor

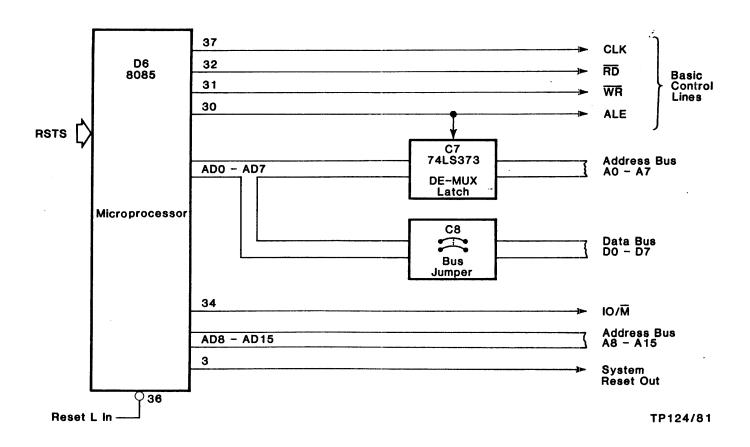

Internal Busses: (Reference sheet 2 of controller schematic)

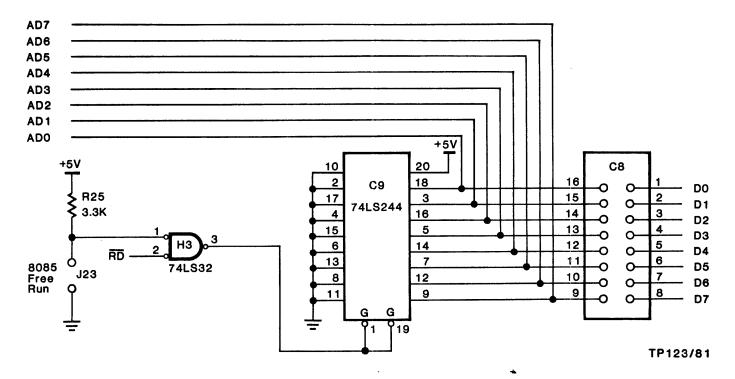

Data Bus: The data bus is used to transfer 8-bit data bytes between the 8085 microprocessor and the various memory locations and I/O ports accessible to the microprocessor. The lower eight address bits are time multiplexed with the eight data bits. Note that on the schematic diagram, the data bus is labelled AD0 through AD7 on the microprocessor side of the bus jumper (C8), and D0 through D7 on the opposite side of the jumper.

A special feature of the data bus is the NO-OP logic (Figure 3-1). This feature is used for maintenance purposes, and consists of a tri-state driver (C9), a bus jumper (C8), and the associated logic. The NO-Op logic forces all zeroes onto bus lines AD0 through AD7 whenever the 8085 does any bus cycle that asserts  $\overline{\text{RD}}$ . This will only happen if the free run jumper (J23) is installed. Octal jumper C8 must be removed to prevent bus contention problems. Since 00 (Hex) is a NO-Op to the 8085, this exercise should cause the processor to increment through its address space. Using a frequency counter, or oscilloscope, is a quick way to check-trace the address lines. Address lines should be observed with an oscilloscope in relation to the ADDRESS LATCH ENABLE (ALE) pulse. The ALE pulse is used to indicate the valid address timing.

Address Bus: The upper eight address bits (A8 through A15 come directly out of the 8085 microprocessor. During memory reference cycles, these lines will contain the upper byte of the memory address. During I/O reference cycles, A8 through A15 will contain the 8-bit address of the selected I/O port.

The lower eight address bits (A0 through A7) are stable at the output of the demultiplexing latch (C7) following the trailing edge of ALE. The  $IO/\overline{M}$  line has essentially the same timing as address bits A8 through A15. When  $IO/\overline{M}$  is low, a memory reference bus cycle is specified.

Bus Control Lines: The primary control lines which are sourced by the 8085 are WR, RD, ALE, and Reset (Figure 3-2). The Reset line serves as a master clear/power-on reset. Most counters and latches on the board have their clear inputs tied to the Reset line. The ALE signal is used to latch address bits A0 through A7 into octal latch C7. It also drives the watchdog timer circuitry. All devices which can be read by the microprocessor, typically, have an output enable line tied to the RD signal, in combination with some address decoding selection logic. Similarly, the WR signal is part of either a memory, or I/O cycle that strobes the data into the destination. Refer to the 8085 User's Manual by Intel for detailed information on timing diagrams and signal relationships.

| Name          | Number<br>of<br>Signals | Schematic<br>Designation                 | Source(s)                                                                          | Destination                                              | Function/Note                             |

|---------------|-------------------------|------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------|

| Data Bus      | 8                       | DO-D7                                    | 8085, PROM, 2111s,<br>8155, IF SR, DATA SR,<br>Input Ports, R/WC<br>Error Register | 8085, 2111s, 8155<br>IF SR, DATA SR                      | Carry 8-bit parallel<br>data from/to 8085 |

| Address Bus   | 17                      | A0-A15, IO/M                             | 8085                                                                               | PROM, 8155, 2111s,<br>Select Logic, R/WC<br>Vector Logic | Selects program mem-<br>ory, I/O ports    |

| Control Bus   | 4                       | RD, WR, ALE,<br>RESET                    | 8085                                                                               | · Miscellaneous Logic                                    | Controls read/write cycles of 8085        |

| Micro-Address | 12                      | μ ΑΟ- μ Α8,<br>Test 1, Test 2,<br>Test 3 | Read/Write Controller<br>2911s                                                     | Read/Write Controller PROMS (and misc. Test Logic).      |                                           |

| P-Bus         | 32                      | P0-P31                                   | Read/Write Controller<br>74S472 PROM                                               | Read/Write Controller<br>Instruction Register            | Read/Write<br>Controller busses           |

| Next Address  | 9                       | NA0-NA8                                  | Read/Write Controller<br>Instruction Register                                      | Read/Write Controller<br>2911s                           |                                           |

| Clock         | 5                       | X1, X2, CLK,<br>R/WC CLK,<br>PL CLK      | Crystal Oscillator<br>8085                                                         | Miscellaneous Logic                                      | Synchronize<br>functions                  |

Figure 3-1. NO-OP Logic Circuit

Figure 3-2. Bus Control Lines

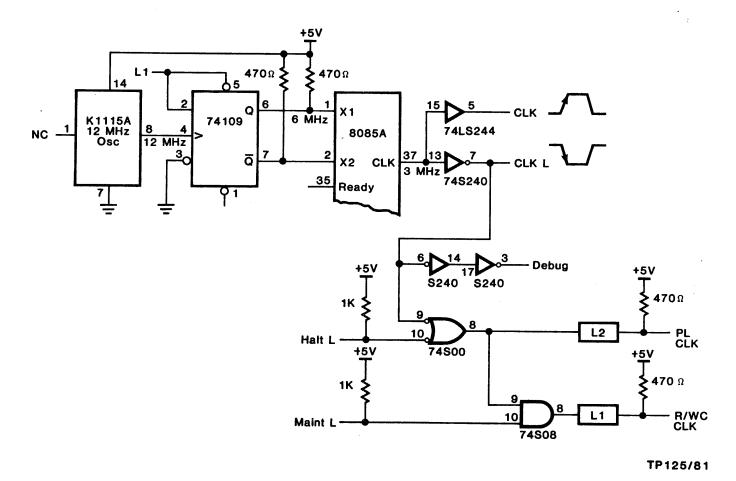

Master Oscillator and Clocks: The DSD 440/480 controller modules are synchronous controllers. A self-contained 12 MHz crystal oscillator provides the master clock. See Figure 3-3.

Figure 3-3. Clock Circuitry

A flip-flop converts the 12 MHz signal into two non-overlapped 6 MHz lines that are then applied directly to the clock generator inputs of the 8085. The 8085 clock period is then 333 nanoseconds (3 MHz). The minimum CLK cycle period specified for the 8085 is 320 nanoseconds (3.125 MHz).

The 3 MHz CLK (out) signal, on pin 37 of the 8085, is used to generate clock signals that are used throughout the controller module. The R/WC bipolar, bit-slice processor is driven by PL CLK and R/WC CLK. Both signals being generated by the 8085 CLK (out) signal.

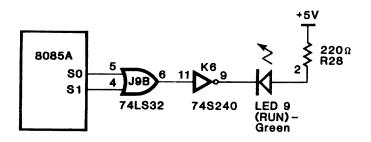

<u>Data Bus Status Lines</u>: The two Data Bus Status lines, S0 and S1, encode the activity, or lack of it, on the data bus according to the following:

|       | <u>S1</u> | <u>so</u> |

|-------|-----------|-----------|

| HALT  | 0         | 0         |

| WRITE | 0         | 1         |

| READ  | 1         | 0         |

| FETCH | 1         | 1         |

Using the circuit as shown in Figure 3-4, the RUN LED should be on as long as the 8085 is not halted. As the table indicates, the HALT condition is indicated when both S0 and S1 are zeroes.

TP126/81

Figure 3-4. Status Lines

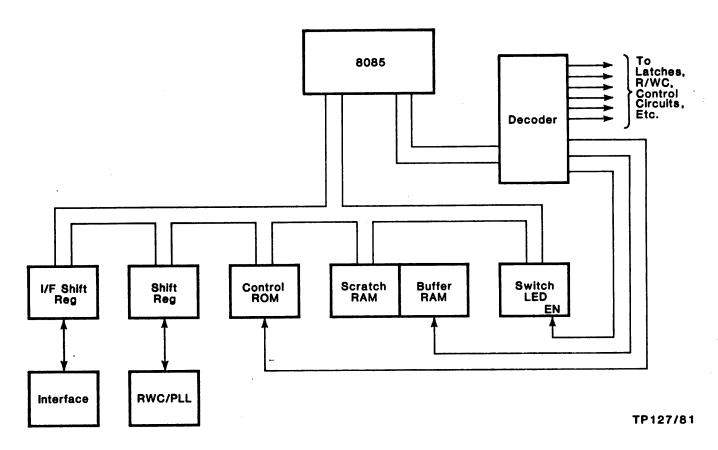

Master Controller: The nucleus of the master controller consists of several blocks that will be discussed independently of each other. These blocks supply the 8085 microprocessor with the basic information to process the commands sent from the interface and drives. The blocks included in this nucleus are; the 8085, RAM, ROM, mode/option selection, switches, decoders, watchdog timers, and I/F to external control blocks. A block diagram of the master controller nucleus is shown in Figure 3-5.

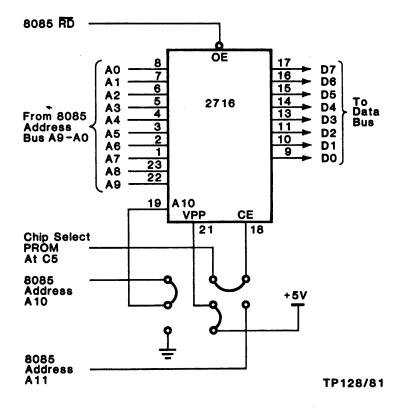

Control PROMs/ROMs: The 8085 control PROMs/ROMs consist of a combination of 2716, 2732, and/or 2758 EPROMs, or the equivalent ROMs. The type of PROM is selectable by using jumpers to select the various combinations of Address and Control lines to the PROMs. There are four locations for PROMs included on the controller module, referred to as Bank 0 to Bank 3. The individual bank is selected by the address decoder PROM, which is described later. A typical PROM location, and its associated jumper scheme, is shown in Figure 3-6.

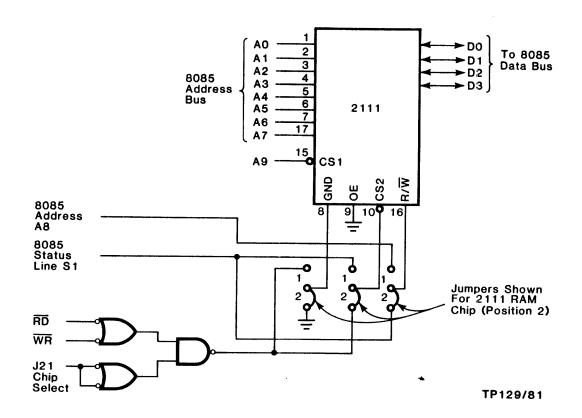

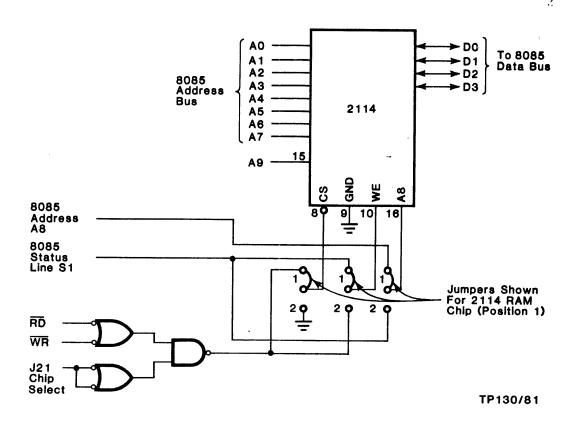

RAM Sector Buffer: The RAM sector buffer may consist of two type 2111, 256 x 4 RAM chips on the DSD 440 controller module, or two type 2114, 1K x 4 RAM chips on the DSD 480 module. These RAM chips are used to store the 128 to 1024 bytes of data stored in the diskette sectors. The number of bytes stored depends upon the diskette density, diskette format, and the system capabilities. The DSD 440 System cannot access the extended IBM format, which uses less than 26 sectors per track.

### CAUTION

To prevent damage to the RAM chips, the jumpers shown in Figures 3-7 and 3-8 <u>MUST</u> match the type of RAM chip installed.

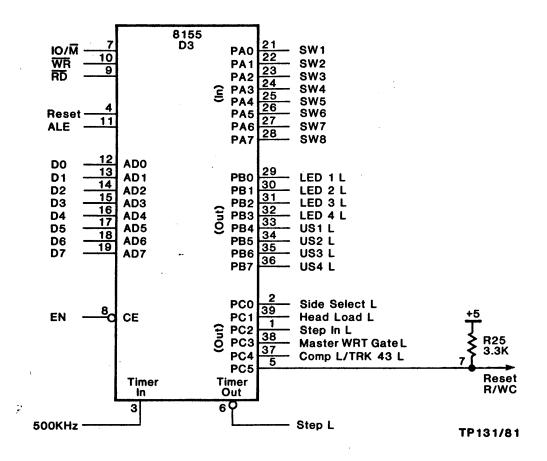

8155 RAM/I/O/Timer: The 8155 chip is an LSI device which contains RAM, I/O ports, and a timer. The 8155 RAM is addressed by asserting the IO/M line (active low), and selecting a memory address in the range of 3800 to 38FF (Hex).

The 8155 RAM memory is used for the 8085 stack operations, and for storage of variables associated with the current functions and drive status.

The 8155 timer is used to create the step pulse required for the drive logic. The pulse is set under software control for ten microseconds width. This pulse is then generated on command of the 8085. The pulse is a one-shot sequence and is not repeated until the next command is given.

Figure 3-5. Master Controller Nucleus Block Diagram

Figure 3-6. Typical PROM Installation

Figure 3-7. 2111 RAM Selection on Controller Module

Figure 3-8. 2114 RAM Selection on Controller Module

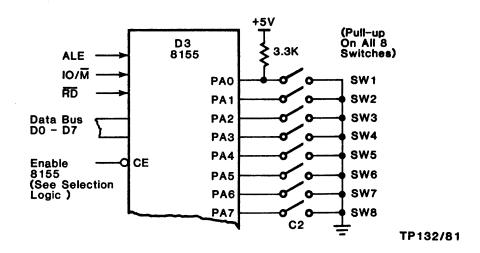

The 8155 I/O ports are addressed using the 8085 In/Out instructions. The I/O addresses associated with the 8155 I/O ports are 00 to 05 (Hex). Port 00 is used for input of the operator selectable switch bank shown in Figure 3-10. Ports 01 and 02 are used for the Drive Control lines, and are buffered before the signals are put onto the drive cable (see Figure 3-9).

Figure 3-9. 8155 RAM/I/O/Timer

Figure 3-10. Eight Position Dipswitch to 8155 Interface

## OUTPUT PORT ADDRESS FOR:

| LED #  | <u>on</u> | OFF        |

|--------|-----------|------------|

| 1      | 20        | 21         |

| 2      | 22        | 23         |

| 2<br>3 | 24        | 25         |

| 4      | 26        | 27         |

| 5      | 28        | 29         |

| 6      | 2A        | 2B         |

| 7      | 2C        | <b>2</b> D |

| 8      | 2E        | <b>2F</b>  |

## Microcode Interface:

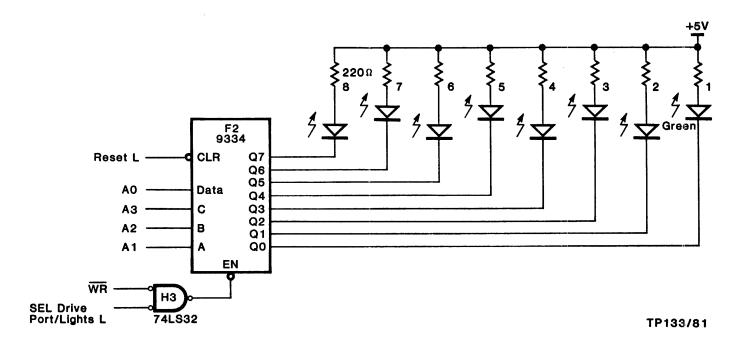

NOTE: Input or output instruction may be used to turn on/off LEDs. The accumulator data is ignored.

## Special Circuit Features:

- 1) If power is available, and there is a failure in the power-up/reset logic causing the signal RESET L to be held asserted, the 9334 latch will be held cleared. This type of failure situation is easy to diagnose because all 8 LEDs are held ON.

- 2) Note that the 9334 is a write only latch, and that <u>no</u> WAIT states are imposed using the 8085 Ready line.

- 3) See Controller LED Decoding Chart for interpretation specifics.

Figure 3-11. LED Indicator Bank

## READ/WRITE PORTS

## **8155 Ports**

# NOTE

For complete description of the 8155 refer to Intel MCS 80/85 Family User's Manual.

# These ports implement:

- 1. The switch (option) input register.

- 2. The unit select/drive activity LED control port.

- 3. The drive control port.

These ports are implemented by chip D3 (8155). (Sheet 1 of schematic)

Defines port A as Input (0), or Output (1)

# Port: CS8155 (00H)

Bit(s)

0

# Output Mode

| _             | - continue poi t in as input (5), or cateput (1)                   |

|---------------|--------------------------------------------------------------------|

| 1             | Defines port B as Input (0), or Output (1)                         |

| 3-2           | Defines port C:                                                    |

|               | 00 = ALT 1 (Input port)                                            |

|               | 11 = ALT 2 (Output port)                                           |

| į.            | 01 = ALT 3 (Control/Output port)                                   |

| <i>*</i>      | 10 = ALT 4 (Control port)                                          |

| A             |                                                                    |

| <b>4</b><br>5 | Enables (1) or disables (0) port A interrupts                      |

| 5             | Enables (1) or disables (0) port B interrupts                      |

| 7-6           | Controls the 8155 timer:                                           |

|               | <b>3.</b>                                                          |

|               | 00 = NOP: does not affect timer operation                          |

|               | 01 = STOP: NOP if timer has not started; stop counting if timer is |

|               | running                                                            |

|               | 10 = STOP AFTER TC: NOP if timer has not started; stop             |

|               | immediately after present TC is reached if timer is running        |

|               | 11 = START: load mode and count length and start immediately       |

|               | after loading if timer is not running. If timer is running, start  |

|               |                                                                    |

|               | the new mode and count length immediately after the present        |

**Purpose**

# Input Mode

| Bit(s) | Purpose                                           |

|--------|---------------------------------------------------|

| 0<br>1 | port A interrupt request port A buffer fill/empty |

| 2      | port A interrupt enable status                    |

TC is reached.

| 3 | port B interrupt request                                              |

|---|-----------------------------------------------------------------------|

| 4 | port B buffer fill empty                                              |

| 5 | port B interrupt enable status                                        |

| 6 | timer interrupt (This bit is latched high when terminal count (TC) is |

|   | reached, and is reset to low upon reading of the 8155 control/status  |

|   | register, or starting a new count.)                                   |

# Port: JUMPER (01H)

This port is used to input the option switch bank. It is configured by the controller microcode for input operations only.

| <u>Bit</u> | Switch               |

|------------|----------------------|

| 0          | 1 (Leftmost switch)  |

| 1          | 2                    |

| 2          | 3                    |

| 3          | 4                    |

| 4          | 5                    |

| 5          | 6                    |

| 6          | 7                    |

| 7          | 8 (Rightmost switch) |

# Port: USLED (02H)

This port implements the unit select and drive activity LED controls.

| <u>Bit</u> | Purpose                                |

|------------|----------------------------------------|

| 0          | LED-1 (drive 0 activity LED)           |

| 1          | LED-2 (drive 1 activity LED)           |

| 2          | LED-3 (drive 2 activity LED, Reserved) |

| 3          | LED-4 (drive 3 activity LED, Reserved) |

| 4          | US-1 (drive 0 unit select)             |

| 5          | US-2 (drive 1 unit select)             |

| 6          | US-3 (drive 2 unit select, Reserved)   |

| 7          | US-4 (drive 3 unit select, Reserved)   |

# Port: PORTC (O3H)

Used for drive control.

| <u>Bit</u>                 | Name                       | Purpose                                                                                                                                                                                                                                                                                                    |

|----------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5 | MASWTG HEADLD STEPIN RESRW | Write current control, 0 = tracks 43-76, 1 = 0-42 Master write gate control, 0 = enable, 1 = disable Head load control, 0 = load, 1 = unload Step direction control, 0 = in, 1 = out Side select (SA850 drives only) - Reserved Reset read/write controller, 0 = reset, 1 = run — does not exist, unused — |

| •                          |                            | <ul><li>does not exist, unused —</li></ul>                                                                                                                                                                                                                                                                 |

# Port: CT8155 (04H)

Used for timer control and as the MSB of the count length of the timer. May be read or written.

| <u>Bits</u> | Purpose                                     |

|-------------|---------------------------------------------|

| 5-0         | MSB of timer count length                   |

| 7-6         | Timer mode:                                 |

| •           | 00 = Output low during second half of count |

|             | 01 = Square wave output                     |

|             | 10 = Single pulse on TC                     |

|             | 11 = Pulse and restart on TC                |

## Port: CT8155+1 (05H)

Used for the LSB of the timer count length. May be read or written.

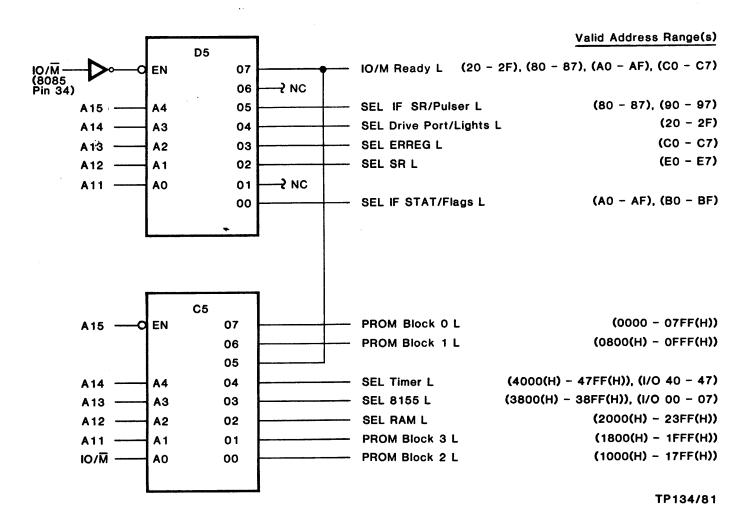

Decoder PROMs: The 8085 device selection is decoded by the two PROMs at locations C5 and D5 on the controller. These PROMs are shown in Figure 3-12. The PROM used in both cases is an 82S23 open collector PROM with enable pin.

Figure 3-12. Decoder PROMs

The decoder at C5 is used for decoding both I/O port addresses and memory blocks. The decoder at D5 is used solely for decoding I/O port addresses and is only enabled during In/Out cycles of 8085.

All selection lines have an associated 3.3K pull-up resistor. Jumpers are provided on the 8155 enable, 8253 (timer) enable, and RAM enable lines to disable these devices for testing individual devices in an isolated situation.

The Ready line to the 8085 also includes a jumper to force the 8085 ready input, ACTIVE HIGH, for testing 8085 circuitry without the interference of the R/WC or other timeout devices.

See the schematic for details on the jumpers and pull-up resistor networks.

Table 3-2 is a summary of the address assignments and their use.

Figure 3-12 is a diagram of the two decoder PROMs. It shows the function and address selected by each output.

### 3.4 Cable Connections

There are three cables that connect to the DSD 440/480 Controller Modules. They are; (1) the dc power cable, (2) the interface bus cable, and (3) the drive bus cable. Each of these cables will be discussed in detail.

# Power Supply Cable:

| Pin No. | Wire Color | Signal                       |

|---------|------------|------------------------------|

| 1       | Unused     |                              |

| 2       | Brown      | Common - return for 5V power |

| 3       | Green      | Common - return for 5V power |

| 4       | Red        | 5 V power source             |

| 5       | White      | 5V power source              |

A five-pin, Molex connector (denoted P2 on the schematic) is used to supply the controller module with 5 Vdc power. The male half of the connector is mounted on the rear, foil side of the board. Pin 1 is closest to the edge of the board.

Interface Bus Cable: The interface bus cable connects the controller module to an interface module installed in some nearby host computer. A 26-pin, male, 3M connector (denoted P3 on the schematics) accepts the I-Bus cable. Note that pin 23 has been removed so that the mating connector, which should have pin 23 plugged, can only be installed in the correct way. A complete description of the I-Bus cable signal timing and protocol can be found in Section 2 of this manual.

Table 3-2. Summary of Address Assignments

|                                                                                      |                              |                            | Select/                                |                            | Address Bits |                            |                            |                                 |                                 |               |                     |               |    |    |                      |                                              |                                           |    |     |     |                                                                            |

|--------------------------------------------------------------------------------------|------------------------------|----------------------------|----------------------------------------|----------------------------|--------------|----------------------------|----------------------------|---------------------------------|---------------------------------|---------------|---------------------|---------------|----|----|----------------------|----------------------------------------------|-------------------------------------------|----|-----|-----|----------------------------------------------------------------------------|

| Device                                                                               | Read<br>Write                | Mem-<br>ory<br>I/O         | RDY<br>PROM<br>Source                  | IO/M<br>RDY<br>L           | A7<br>A15    | A6<br>A14                  | A5<br>A13                  | A4<br>A12                       | A3<br>A11                       | A2<br>A10     | A1<br>A9            | A0<br>A8      | A7 | A6 | A5                   | — I/O<br>A4                                  |                                           | A2 | A1  | A0  | Comments                                                                   |

| PROM Block 0<br>PROM Block 1<br>PROM Block 2<br>PROM Block 3<br>8155 RAM<br>8155 I/O | R<br>R<br>R<br>R<br>R<br>R/R | M<br>M<br>M<br>M<br>M<br>M | C5<br>C5<br>C5<br>C5<br>C5<br>C5<br>C5 | 0<br>0<br>0<br>0<br>0<br>0 | 0 0 0 0      | 0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>1<br>1<br>1<br>1<br>1 | 0<br>1<br>0<br>0<br>1<br>1<br>1 | 1<br>1<br>X   | X<br>X<br>X<br>ev S | X<br>el-      | 1  |    | PR<br>PR<br>PR<br>PR | OM A<br>OM A<br>OM A<br>OM A<br>OM A<br>OM A | DDR -<br>DDR -<br>DDR -<br>DDR -<br>DDR - |    |     |     | 2716<br>3624<br>2716<br>3624                                               |

| 8253                                                                                 | R/W<br>R/W                   | M<br>I/O                   | C5                                     | 0                          | 0            | 1                          | 0                          | 0<br>0                          | 0<br>0                          | x<br>x        | X<br>Reg            | X<br>Sel      | х  | X  | x                    | X                                            | X                                         | X  | Reg | Sel |                                                                            |

| RAM Select  I/F Status                                                               | R/W<br>R                     | M<br>I/O                   | C5<br>D5                               | 0                          | 0            | 0                          | 1                          | 0<br>Wait                       | 0<br>X                          | X<br>X        |                     | x<br>x        | -  | -  | - R                  | AM A                                         | DDR -                                     |    |     |     | ,                                                                          |

| I/F Flags                                                                            | W                            | I/O                        | D5                                     | 1                          | 1            | 0                          | 1                          | Wait                            |                                 | Bit Se        |                     |               |    |    |                      |                                              |                                           |    |     |     | Waits for I/F                                                              |

| IF Shift Reg<br>IFTRCL Select<br>Pulser                                              | R/W<br>R/W                   | I/O<br>I/O<br>I/O          | D5<br>D5<br>D5                         | 1<br>1<br>·1               | 1 1 1        | 0<br>0<br>0                | 0                          | 0<br>1<br>Wait                  | 0<br>0<br>0                     | 0<br>0<br>— E | 0<br>0<br>3it Se    | 0<br>0<br>el— |    |    |                      |                                              |                                           |    |     |     | If Oper=R, A0-A3=X<br>Waits for I/F;<br>sets transfer flag<br>Wait for I/F |

| Drive Port                                                                           | R                            | I/O                        | D5                                     | 0                          | 0            | 0                          | 1                          | 0                               | x                               | x             | x                   | X             |    |    |                      |                                              |                                           |    |     |     | '                                                                          |

| LED                                                                                  | w                            | I/O                        | D5                                     | 0                          | 0            | 0                          | 1                          | 0                               | - L                             | ED Se         | el—                 | Sense         |    |    |                      |                                              |                                           |    |     |     | Sense: 0=ON,1=OFF                                                          |

| R/WC ERREG                                                                           | R                            | I/O                        | D5                                     | 0                          | 1            | 1                          | 0                          | 0                               | 0                               | X             | X                   | X             |    |    |                      |                                              |                                           |    |     |     | ·                                                                          |

| R/WC Shift Reg                                                                       | R/W                          | I/O                        | D5                                     | 1                          | 1            | 1                          | 1                          | 0                               | 0                               | X             | Vе                  | ctor          |    |    |                      |                                              |                                           |    |     |     | Waits for R/WC                                                             |

0=Auto Ready, 1=Wait -

Wait, when set together with the IO/M RDY Line, forces a wait for the interface.

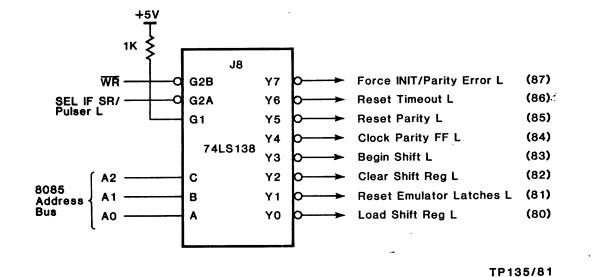

Pulser Output Circuits: The pulser circuit enables the microprocessor to address pulses to eight specific points of interest in the controller. The 74LS138, at J8, serves to route the pulse to the output addressed by A0, A1, and A2 during the WR pulse sent from the 8085. When A0, A1, and A2 are all 0, Y0 emits a pulse which passes through a pulse delay (R28a, C39a, J9b) before strobing the shift register (E8). The other seven pulse ports do the following: (See Figure 3-13.)

| Address | <u>Name</u> | <u>Purpose</u>                                            |

|---------|-------------|-----------------------------------------------------------|

| 80 (W)  | LDSH        | Load data from data bus to shift register                 |

| 80 (R)  | RDSHR       | Dump I/F shift register onto data bus                     |

| 81      | RSTEMU      | Reset all the emulator latches (Shifter, Parity, LINIT)   |

| 82      | CLRISR      | Clear the interface shift register                        |

| 83      | BEGSHF      | Start an interface bus shift operation (4-bit or 8-bit)   |

| 84      | CLKPAR      | Clock the parity status flip-flop (load final parity bit) |

| 85      | PREPAR      | Pre-set the parity status flip-flop                       |

| 86      | RSTTRP      | Reset the time-out trap flip-flop                         |

| 87      | FLINIT      | Force the parity and INIT flops set                       |

Figure 3-13. Pulsed Outputs

General Control Ports: These ports control the status of the serial data path, read/write controller, and interface emulator.

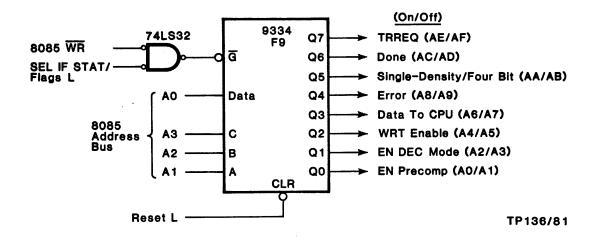

Implemented by chip F9 (9334). Appears on page 6 of the print set. (See Figure 3-14.)

| Address    | Name   | <u>Purpose</u>                                    |

|------------|--------|---------------------------------------------------|

| <b>A</b> 0 | NPRCMP | Turns off write precompensation                   |

| <b>A1</b>  | PRECMP | Turns on write precompensation                    |

| <b>A2</b>  | NDECMD | Turns off DEC MMFM coder/decoder                  |

| <b>A3</b>  | DECMOD | Turns on DEC MMFM coder/decoder                   |

| A4         | DISWTG | Disables the R/WC write gate                      |

| A5         | ENWRTG | Enables the R/WC write gate                       |

| A6         | DATFLP | Sets data direction to data-to-floppy             |

| A7         | DATCPU | Sets data direction to data-to-cpu                |

| A8         | CLRERR | Clears the interface error latch                  |

| A9         | ERROR  | Sets the interface error latch                    |

| AA         | DD8BIT | Sets double-density PLL clock and 8-bit shifts    |

| AB         | SD4BIT | Sets single-density PLL clock and 4-bit shifts    |

| AC         | CLRDON | Clears the interface DONE latch                   |

| AD         | DONE   | Sets the interface DONE latch                     |

| ΑE         | CLRTRR | Clears the interface TR latch                     |

| AF         | TRREQ  | Sets the interface TR latch                       |

| BD         | DONEW  | Sets the interface DONE latch and waits for ready |

| BF         | TRREQW | Sets the interface TR latch and waits for ready   |

Figure 3-14. Latched Outputs

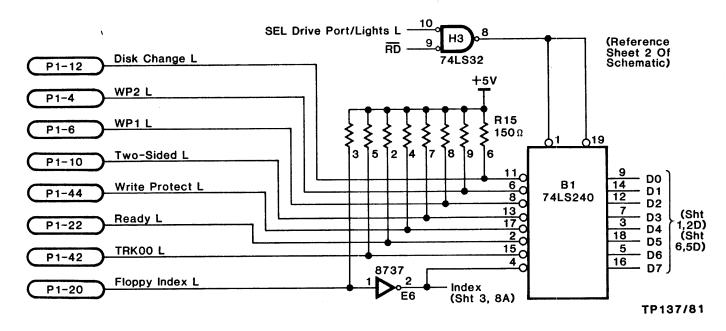

8085 I/O Status Ports: The 8085 microprocessor may also access status of the drive, the interface, and the R/WC error conditions. Drive status is accessed through port 20 H. The bits returned by the 8085 IN instruction are coded as follows:

| <u>Bit</u> | Name            | <u>Purpose</u>                                                                 |

|------------|-----------------|--------------------------------------------------------------------------------|

| 0          | DISKCH<br>WP2   | Indicates "disk changed" status<br>Reserved for "write protect switch 2"       |

| 2          | WP1<br>2Sided   | Reserved for "write protect switch 1" Reserved for "two-sided" disk indication |

| 3<br>4     | WRTPRT          | Indicates "write-protected" diskette status                                    |

| 5<br>6     | DSKRDY<br>TRK00 | Indicates "drive-ready" status Indicates "track 0" sensor status               |

| 7          | INDEX           | Indicates "index" sensor status                                                |

Figure 3-15. Drive Status Port

Interface status is accessed through reading port A0 H. The bits returned by the I/O read cycle to port A0 are coded as shown below. (See Figure 3-15.)

| <u>Bit</u> | <u>Name</u> | <u>Purpose</u>                            |

|------------|-------------|-------------------------------------------|

| 0          | BKWRDS      | Indicates "cable backwards" test status   |

| 1          | IFERR       | Indicates "interface-error" status        |

| 2          | ACOK        | Indicates "ac power ok" sensor status     |

| 3          | DMAIF       | Indicates "DMA mode interface"            |

| 4          | TWEL VE     | Indicates "12-bit interface mode"         |

| 5          | LINIT       | Indicates "latched initialize" status     |

| 6          | PERROR      | Indicates "interface parity error" status |

| 7          | IFRDY       | Indicates "interface ready" status        |

If an error occurs in the R/WC, the error is placed into the R/WC error register. This register may be read at port C0 by the 8085. The error is coded into the lower four bits. The upper four bits read are insignificant. Refer to the R/WC section for more information.

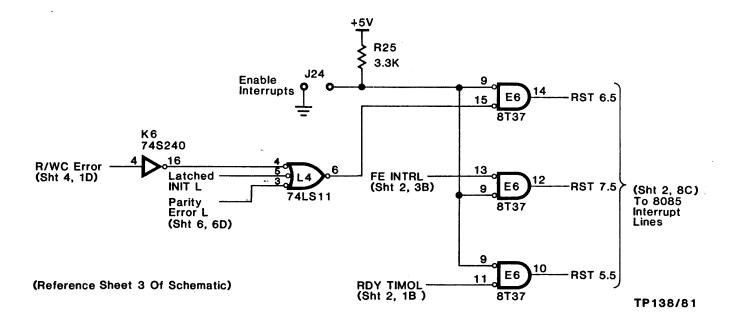

Interrupt Logic (Restarts): The controller microprocessor makes use of the RST5.5, RST6.5, and the RST7.5 interrupts. (See Figure 3-16.) The first interrupt we will discuss is RST7.5, which has the highest priority. As can be seen on schematic sheet 3, RST7.5 is derived from the signal FILL/EMPTY INTERRUPT that comes from the third counter in the 8253. Notice that this counter is configured to count transfer request flags. The counter gate is tied to logic 1, so the counter is always enabled. A hardware counter is utilized to count the bytes transferred while doing either a FILL BUFFER or EMPTY BUFFER cycle. When all 128 or 256 bytes have been transferred, the counter overflows and an interrupt is generated.

The purpose of using a dedicated hardware counter for the fill/empty routines is to speed up the tight loops associated with these routines. Normally, the 8085 microprocessor has to count the transfers by decrementing or incrementing a register. This process takes four

cycles, or 1.33 microseconds for each transfer. By using the hardware counter, approximately 340 microseconds can be saved for a typical 256-byte sector.

The RST6.5 interrupt can be generated by any one of three sources. These are; (1) R/WC error, (2) parity error, or (3) the Latched INIT. The 8085 will be interrupted if any of these events takes place. The microprocessor must be able to determine which event caused the interrupt so that this information can be reported back to the interface. The microprocessor reads the IF STAT/FLAGS Register (sheet 6 of the schematic, location D8) to get this information.

Figure 3-16. Interrupt Logic

The RST5.5 interrupt is generated when the READY TIME-OUT flip-flop becomes set. This will happen when the R/WC does not return with READY before the watchdog timer times out. This interrupt insures that the controller will not become hung if it has difficulty locating a particular address mark.

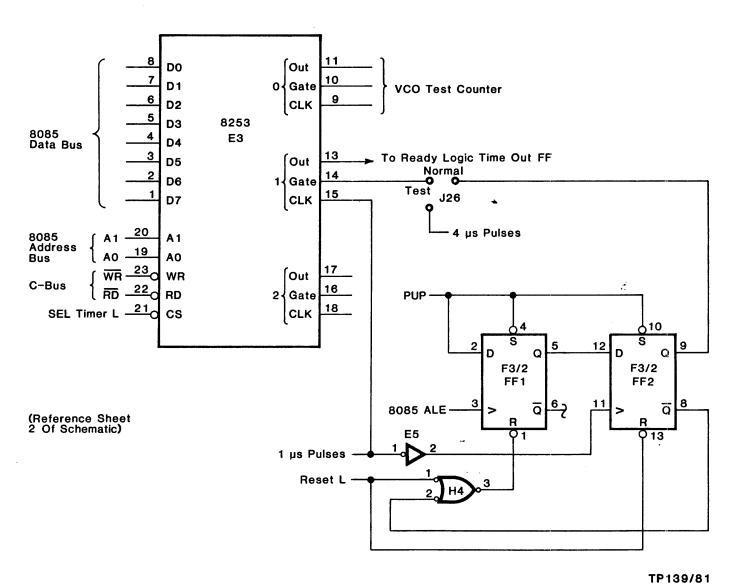

8253 Timers: The 8253 LSI chip contains three counter/timers that are used for the watchdog timer, the fill/empty counter, and the VC0 test circuitry.

Counter No. 1: The timeout watchdog timer circuit is shown in Figure 3-17. The function of this circuit is to detect the loss of the READY signal to the 8085. The READY signal may be delayed because of an R/WC problem or an inactive interface (no CPU action). The 8253 timer is preset with the expected timeout value, and is then gated on/off by the occurrence or non-occurrence of the 8085 ALE Control line. The timeout provides the 8085 with an escape route so that the system will not hang if an unexpected timeout occurs.

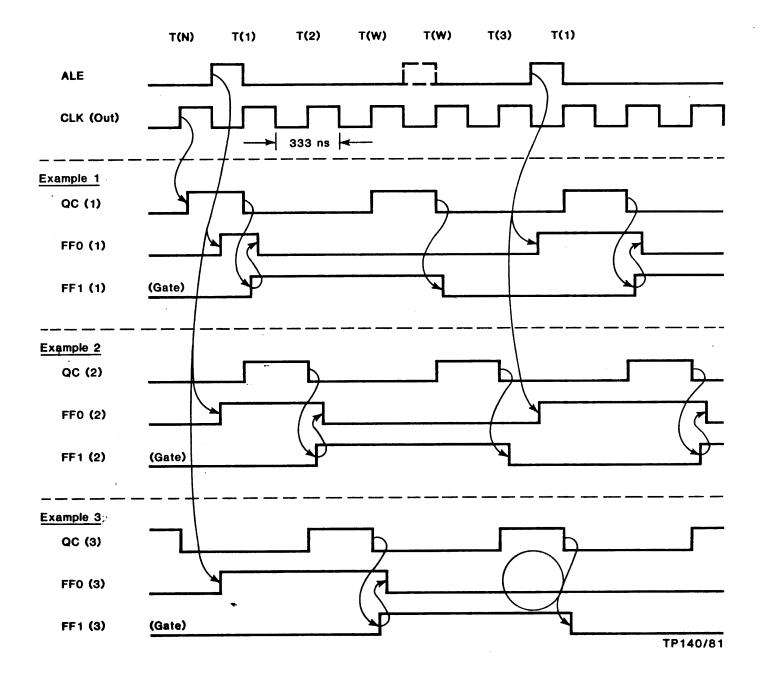

Figure 3-18 shows the watchdog timer timing during a normal I/O sequence. Three examples are shown which result from the timing relationship of the 0.1 microsecond pulse to the 0.333 microsecond CLK pulse from the 8085. During the T(W) state, the 8085 is in wait state, but the 8253 is still counting the 0.1 microsecond pulses. During normal operation, the 8253 counter does not complete its count while the 8253 gate has been enabled. There will not

be a terminal count pulse at the 8253 output unless terminal count has been reached, and the completion ALE pulse has not occurred. The accuracy of this circuit is approximately a 0.1 microsecond period during which the ALE pulse may have occurred, but has not inhibited the 8253 gate and output.

Counter No. 2: The fill/empty counter was described in the interrupt section of the 8085 circuitry. The counter records the number of transfer requests. When the correct number have occurred, an RST5.5 interrupt is generated to stop the fill/empty routine currently in progress.

Figure 3-17. Watchdog Timer

Figure 3-18. Watchdog Timer Timing

Counter No. 3: The third counter section of the 8253 timer is used to verify the accuracy of the VCO in the phase-locked-loop. This counter is used by the hardware self-test to count the number of VCO cycles during a given period, as measured by the 8085 12 MHz crystal oscillator. This timing measurement is done under software control, and the output is read through the 8253 software registers. The 8253 ports are assigned as shown below:

| Port Number | <u>Use/Comment</u>                                                                                                       |

|-------------|--------------------------------------------------------------------------------------------------------------------------|

| 40          | VCO counter test access port                                                                                             |

| 41          | Timeout counter access port                                                                                              |

| 42          | DMA fill/empty counter access port                                                                                       |

| 43          | 8253 control port - write only (Sets the mode of the ports 40 through 42 described in the Intel/NEC Product Data Books.) |

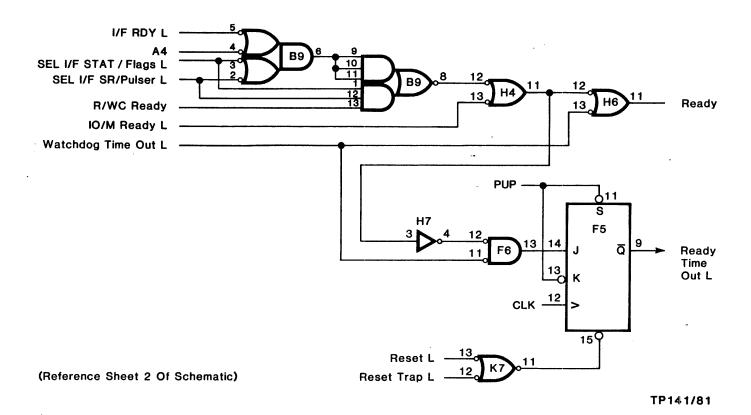

8085 Ready Logic: Figure 3-19 shows the READY hardware logic that drives the 8085 READY input. The Ready line is used to inhibit 8085 operation when the interface has been accessed and the interface is not ready, or when the R/WC is not ready and the 8085 is not trying to access the interface (during read/write operations for example). The READY logic derives its inputs from the decoder PROMs, the R/WC Status line, the watchdog timer, and Address line A4.

If the controller has failed due to a ready timeout, the watchdog timer will force the READY signal. After the ready has been asserted, the 8085 will be forced into a timeout routine by an interrupt, also caused by the watchdog timer.

It is possible to access the interface without inhibiting ready, by accessing the interface at addresses B0 to BF for interface STATUS, or 90 to 97 for interface DATA. This causes Address line A4 to be low (0) and will cause the Ready line to be asserted. Refer to the discussion on the watchdog timer.

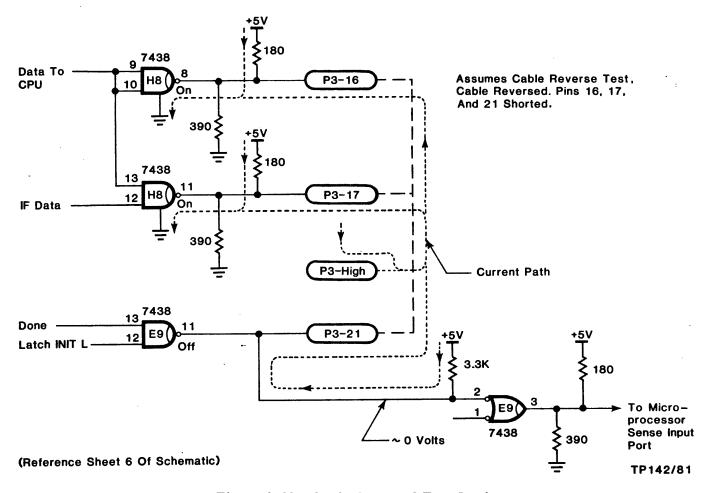

One unique feature of the I-Bus cable is the ability of the master controller to diagnose a cable that has been installed backwards. Pins 1 through 13 are all connected together to ground on both the controller module and the interface module. If the I-Bus cable is installed incorrectly, all the signals (pins 14 through 26) will be shorted together instead of all the grounds on pins 1 through 13. Refer to Figure 3-20. During the cable reversal test, the 8085 asserts Data-To-CPU and IFDATA lines to provide a sufficient current sink. The IDONE signal is asserted, at this time, by E9-11. The 8085 looks at IDONE through E9-2. If the cable is backwards, it will be low. If the cable is installed correctly or is missing, it will be high.

Figure 3-19. READY Hardware Logic

Figure 3-20. Cable Reversal Test Logic

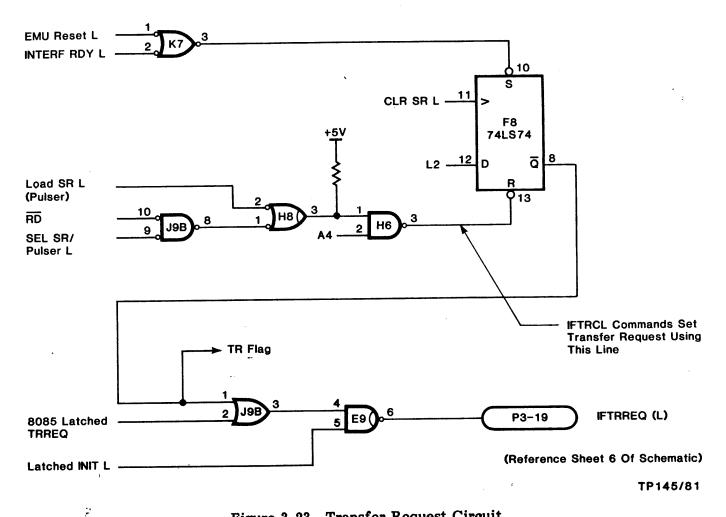

#### Controller Interface To The I-Bus

There are six input lines into the controller from the 26-pin I-Bus cable. Two of the lines, IFDATA L and IERROR L, are bidirectional. The IDMA mode, I12BM, IFRDY, and IERROR I-BUS lines are fed into the 8085 via the tri-state buffer at location D8. These lines may be read by doing an I/O read operation at the If STAT/FLAGS port (addresses A0 through AF or B0 through BF).

The IF INIT input is used to clock the latched INIT flip-flop at F8. This FF may be read at any time after it has been latched. This allows an INIT to occur while the 8085 is engaged elsewhere. The INIT can still be recognized later.

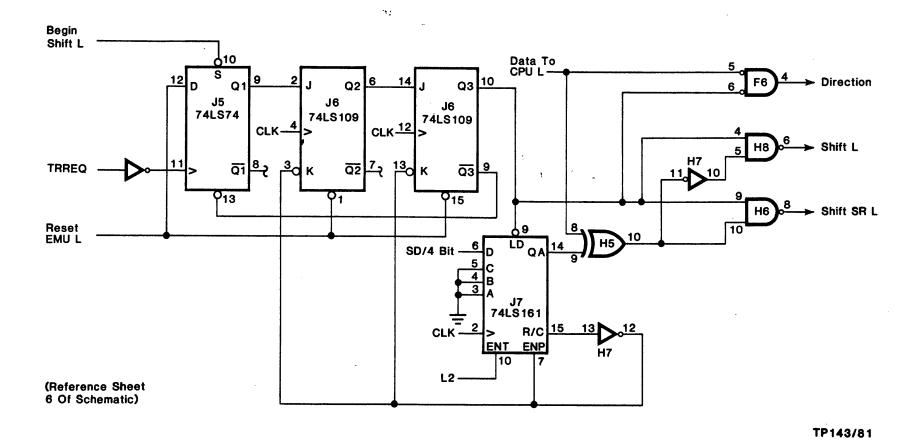

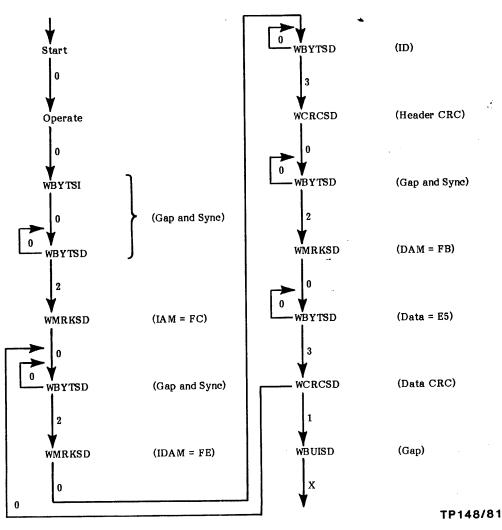

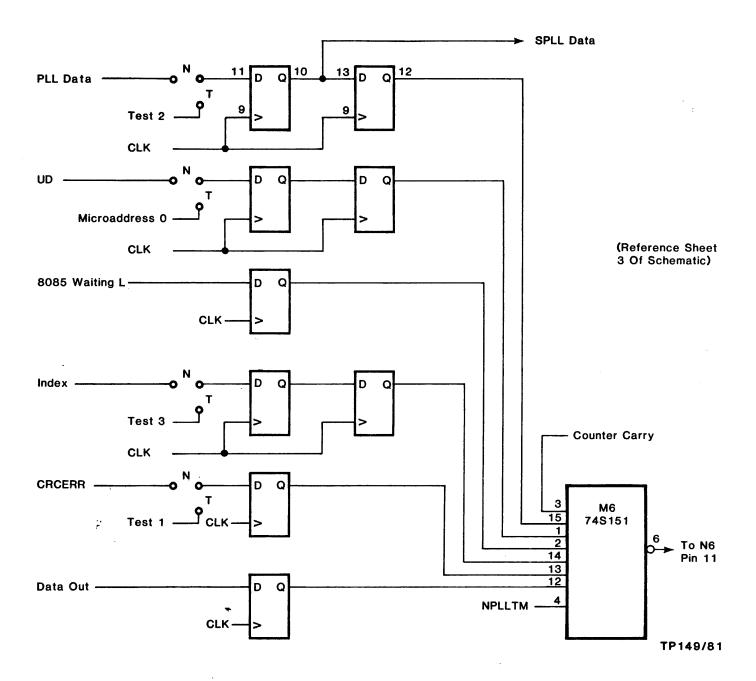

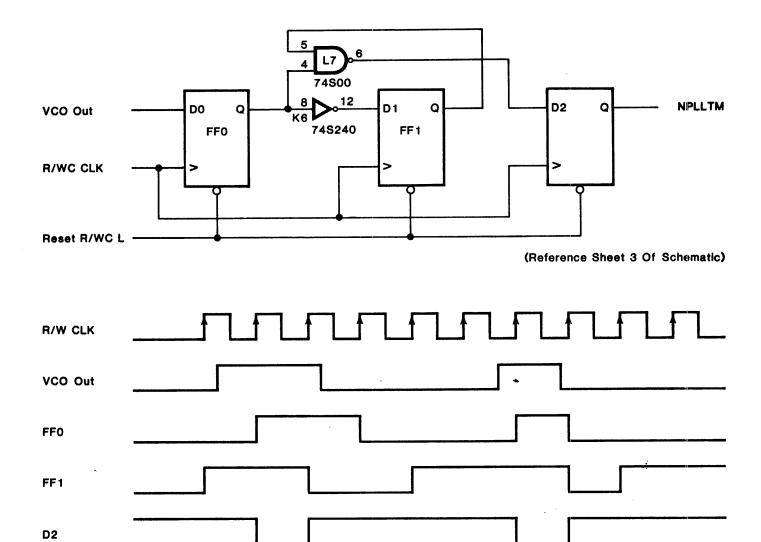

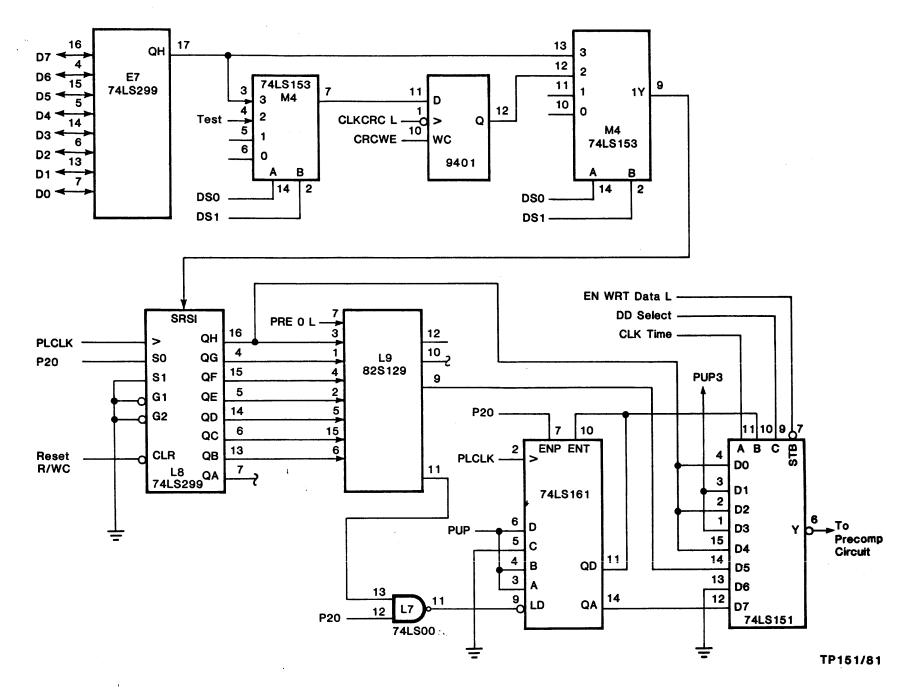

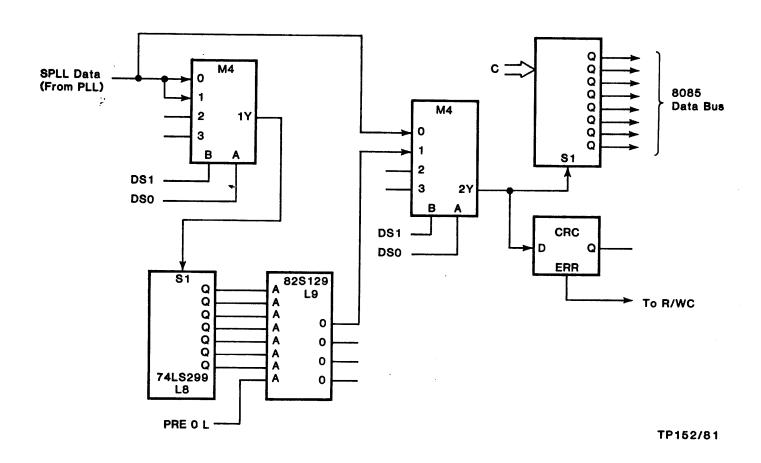

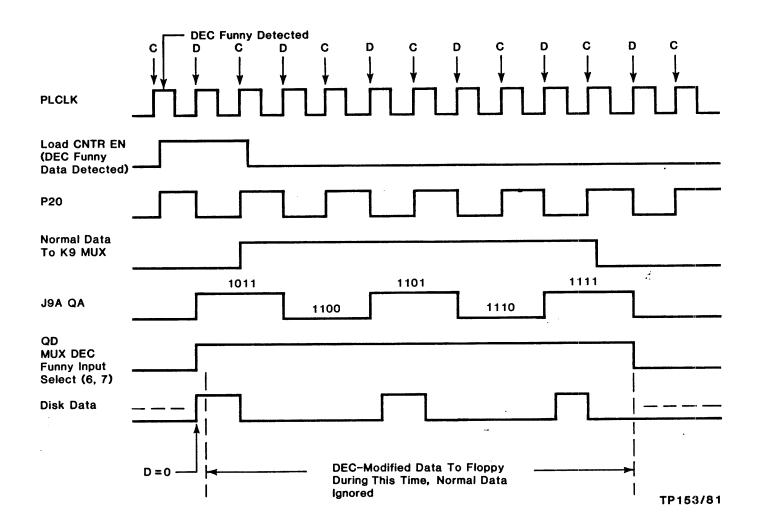

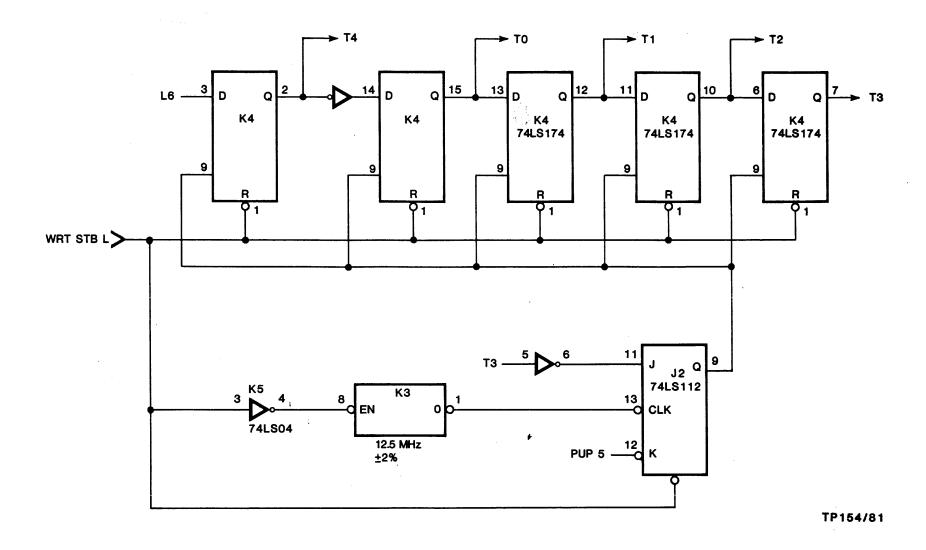

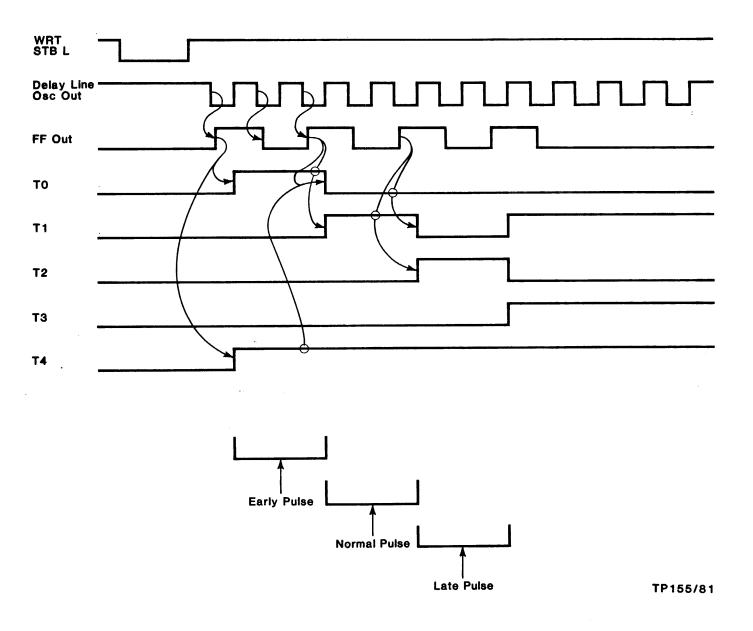

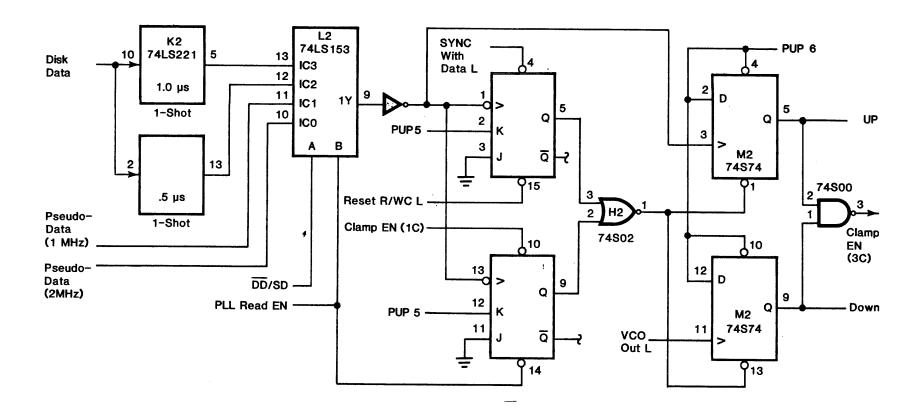

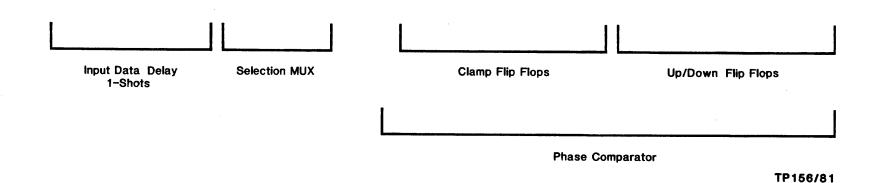

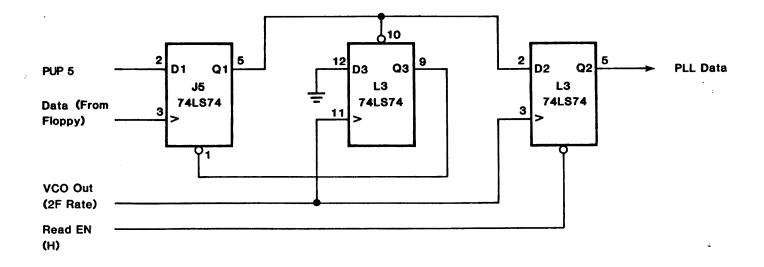

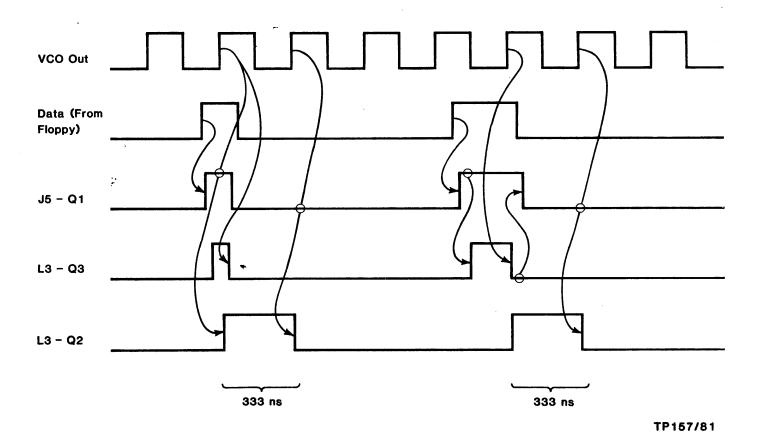

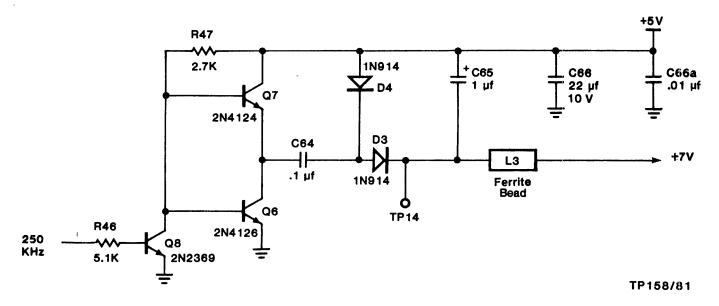

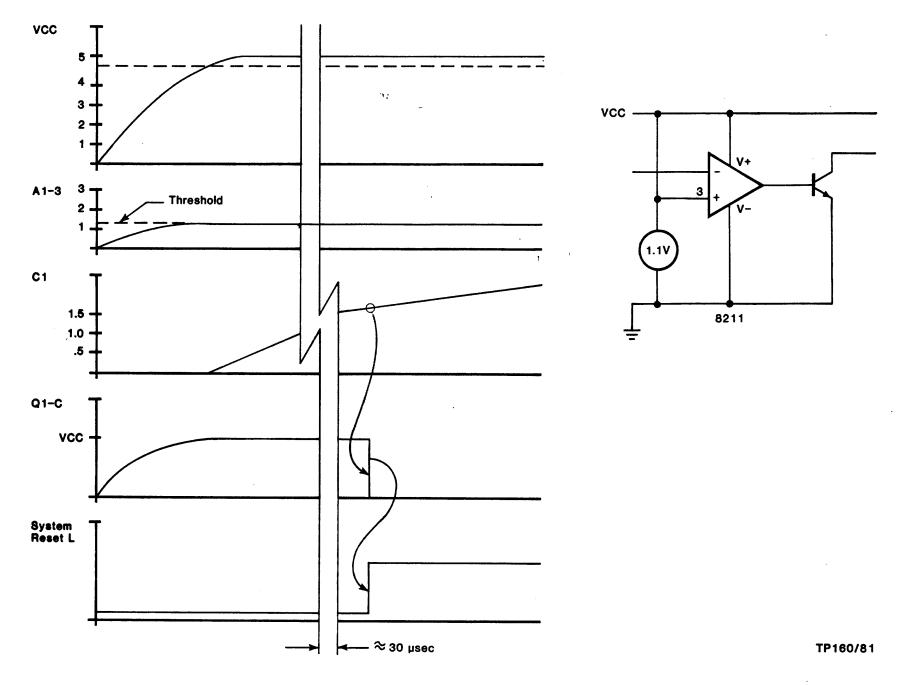

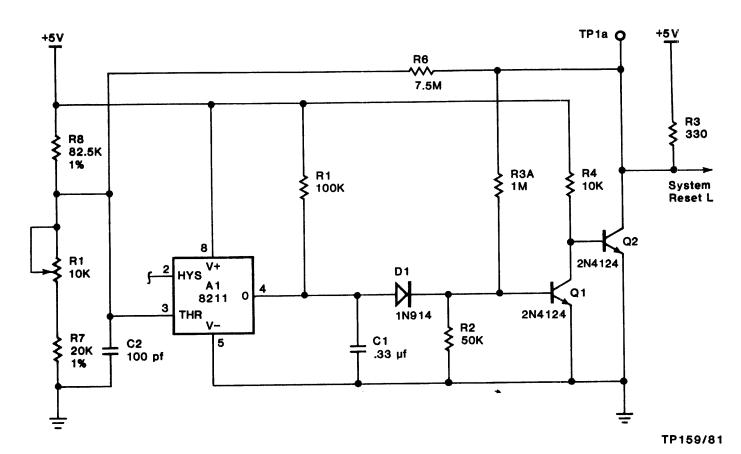

The IF DATA input is fed into the interface shift register and into the parity check circuit. The parity check circuit performs a parity test on all shifted data from the interface. The parity check circuit is also driven by the PULSER circuit of the 8085. This allows the parity check circuits to be tested by forcing and clearing the parity error, and checking that the circuit output is valid.