## TRAQ Reference Manual

### **Proprietary Statement**

Notice is hereby given that all data contained in, revealed by, or shown on this document, whether a drawing or other writing, is proprietary and belongs to DSP TECHNOLOGY INC., Fremont, California. It is furnished and received in confidence solely for information purposes or procurement of the product to which it relates. Neither the document nor any information/data contained in it shall be used for any other purpose or duplicated or disclosed in whole or in part to anyone else without the prior written authorization of DSP TECHNOLOGY INC. in each instance. If such written authorization be given by DSPT, any disclosure or revelation by the recipient to anyone else shall be accompanied by a written statement incorporating the language and contents of this legend.

### TABLE OF CONTENTS

| Section 1 T  | RAQ System                                     | 1    |

|--------------|------------------------------------------------|------|

|              | System Description.                            | 1    |

|              | TRAQ Controllers                               | 2    |

|              | TRAQ Memories                                  | 3    |

|              | Analog-To-Digital Converters                   | 4    |

|              | Digital-to-Digital Converters                  | 5    |

|              | Typical TRAQ Configurations.                   | 5    |

|              | TRAQ Current and Power Requirements.           | 5.   |

|              | TRAQ Installation.                             | 7    |

|              | System Interconnections                        | 7    |

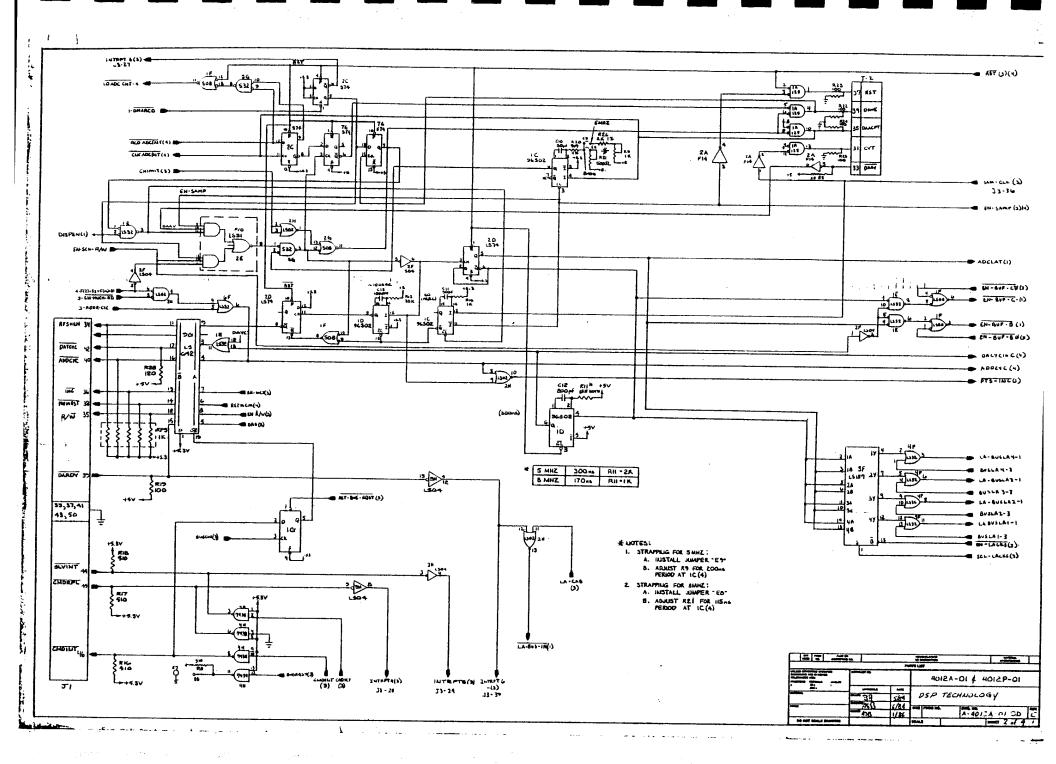

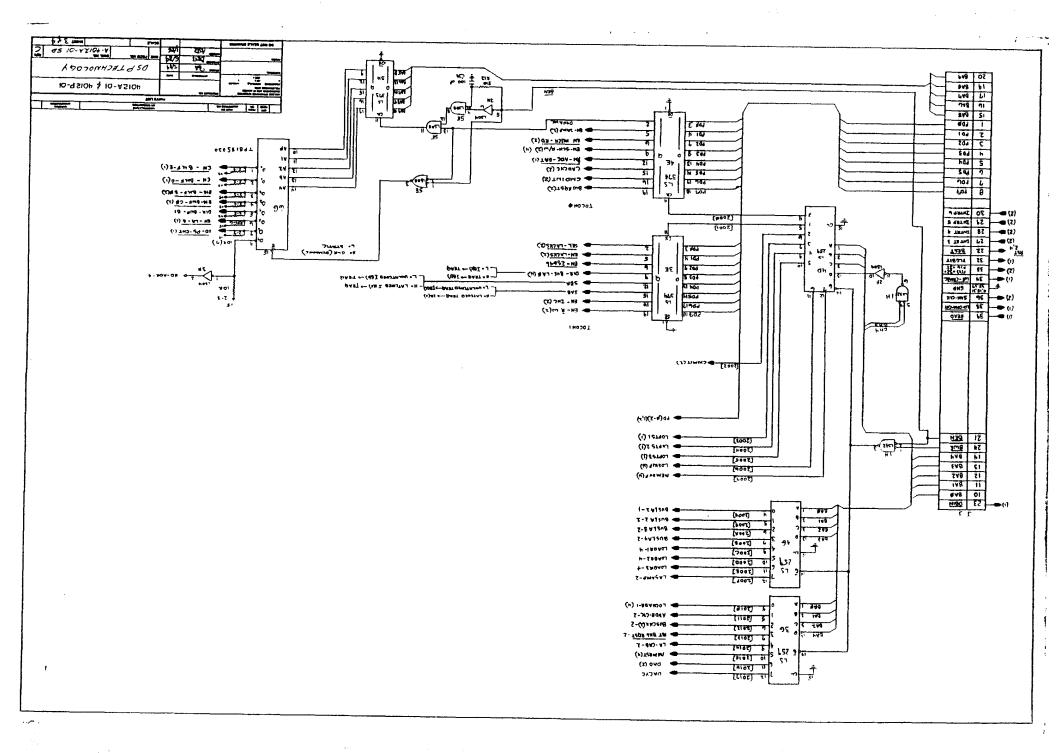

| Section 2 40 | 012 and 4032 TRAQ Controllers                  | 11   |

|              | General Description                            | 11   |

|              | Model 4012P and Model 4032P                    | 12.  |

|              | Models 4012 and 4032 Differences               | 13   |

|              | System Diagnostics                             | 13   |

| Section 3 F  | ront Panel Indicators                          | 15   |

|              | Alphanumeric LED Indicators.                   | 1.5. |

|              | Front Panel LED Indicators.                    | 21.  |

|              | Front Panel Switch Controls                    | 22.  |

|              | Front Panel Signals                            | 23   |

|              | Model 4012P and Model 4032P Rear Panel Signals | 24   |

|              | Front and Rear Panel Flat Cable Bus Connectors | 25   |

| Section 4 Programming the 4012/4032 Control Registers2 | 7  |

|--------------------------------------------------------|----|

| CAMAC Control                                          | 7  |

| Controlling Sampling and Data Readout From CAMAC30     | 0  |

| Section 5 Writing Common 4012/4032 Control Registers3  | 1  |

| Data Streamout                                         | 5  |

| Data Streamout with Auto-restart                       | б  |

| Section 6 Model 4012 Control Registers                 | 9  |

| Section 7 4032 Control Registers                       | 3  |

| Section 8 Reading the 4012/4032 Control Registers4     | 9  |

| Model 4012 Only                                        | 3  |

| Model 4032 Only                                        | 3  |

| Section 9 Diagnostics5                                 | 5  |

| Section 10 Switch Options6                             | 5  |

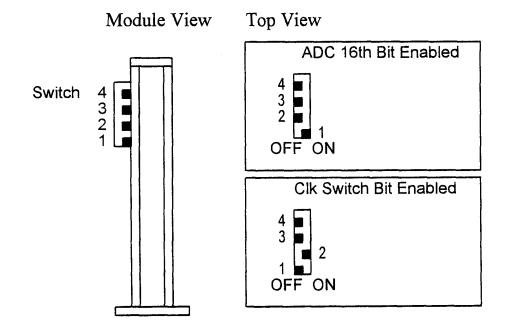

| CLK2 16th Bit Set 65                                   | 5  |

| Installation of TRAQ Firmware66                        | 5. |

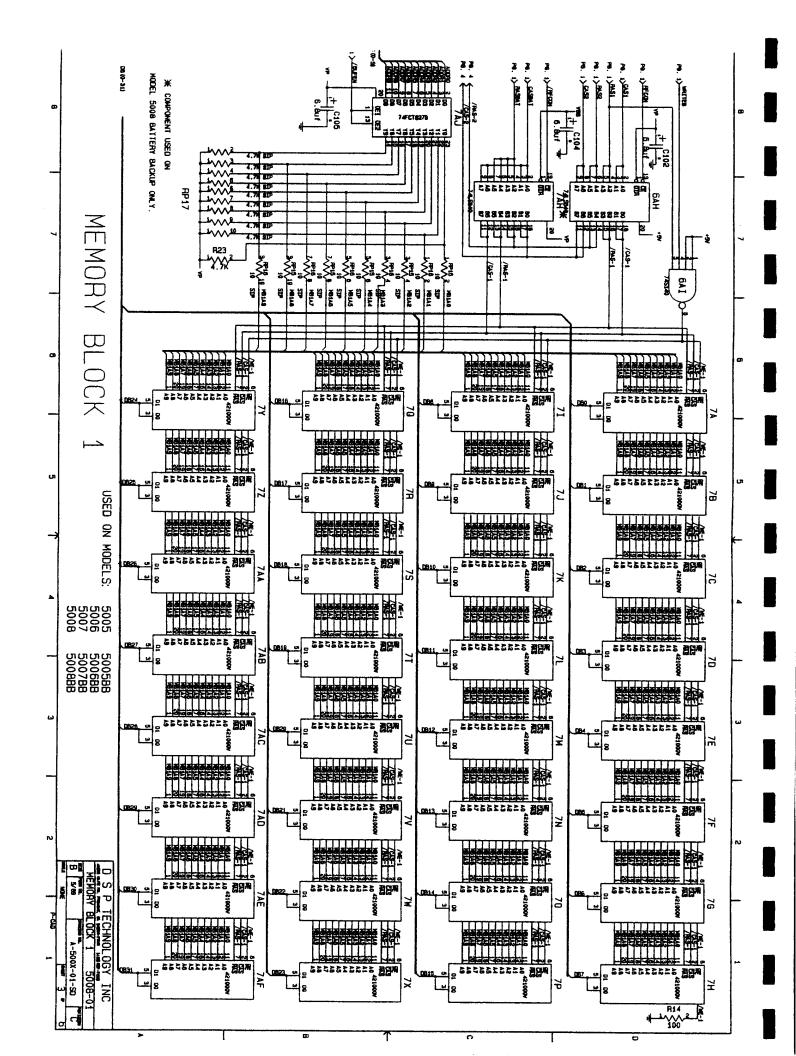

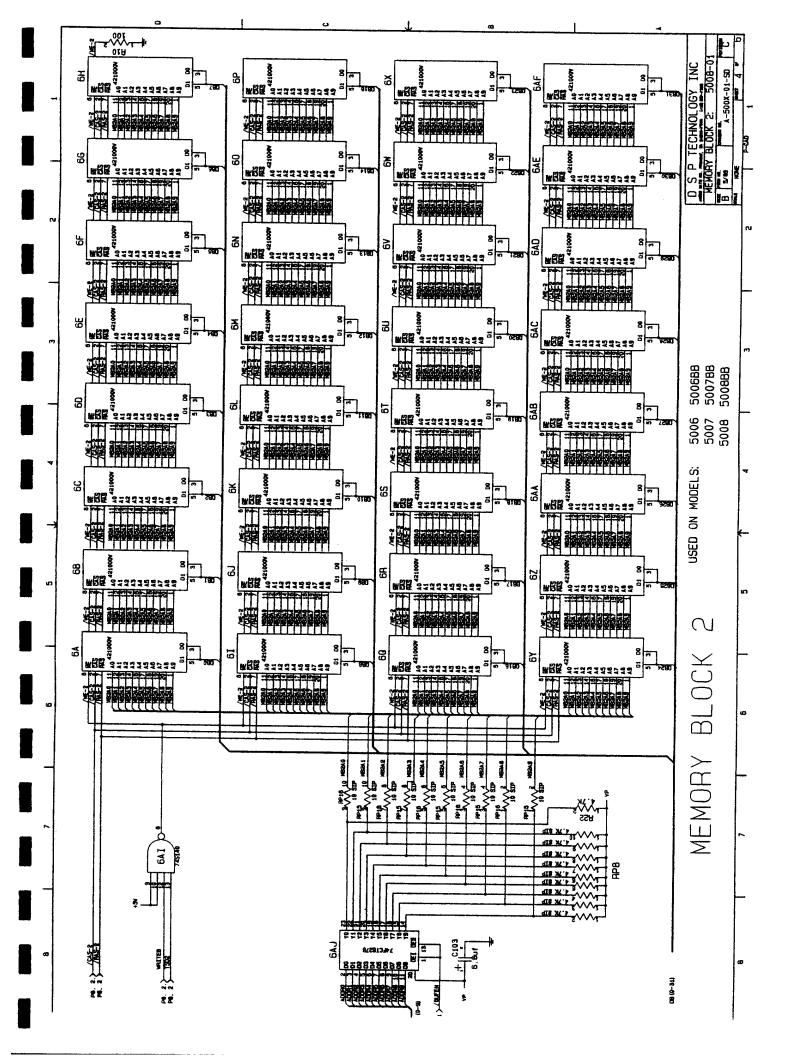

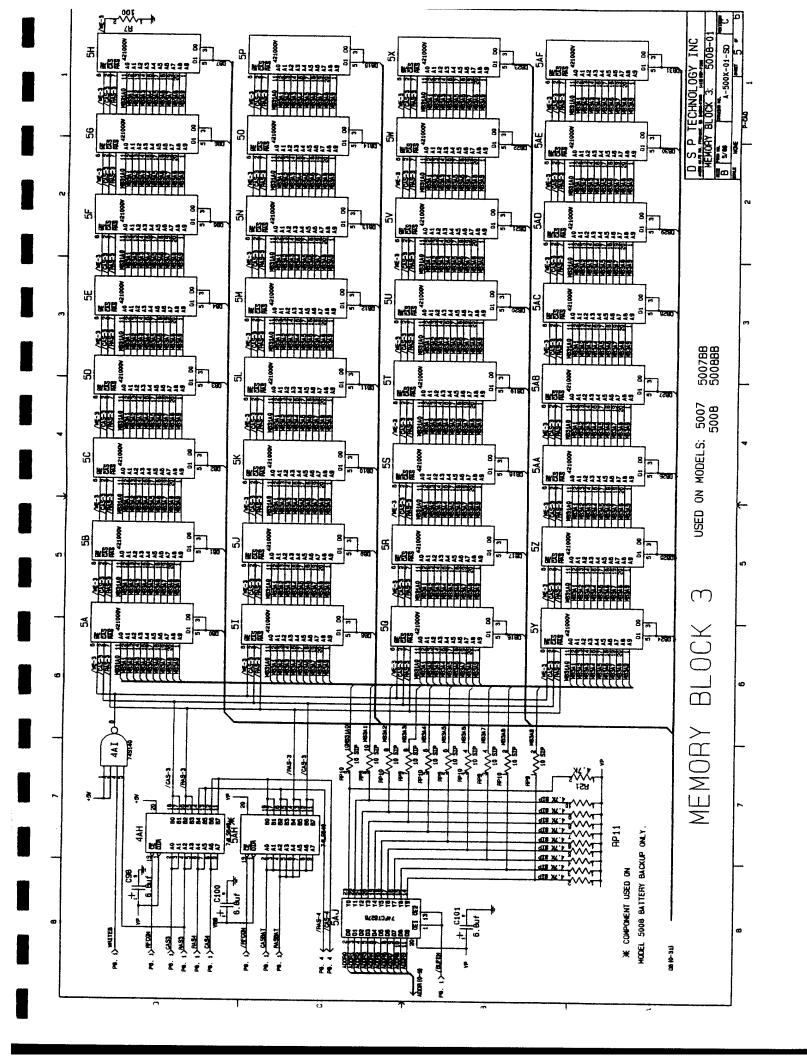

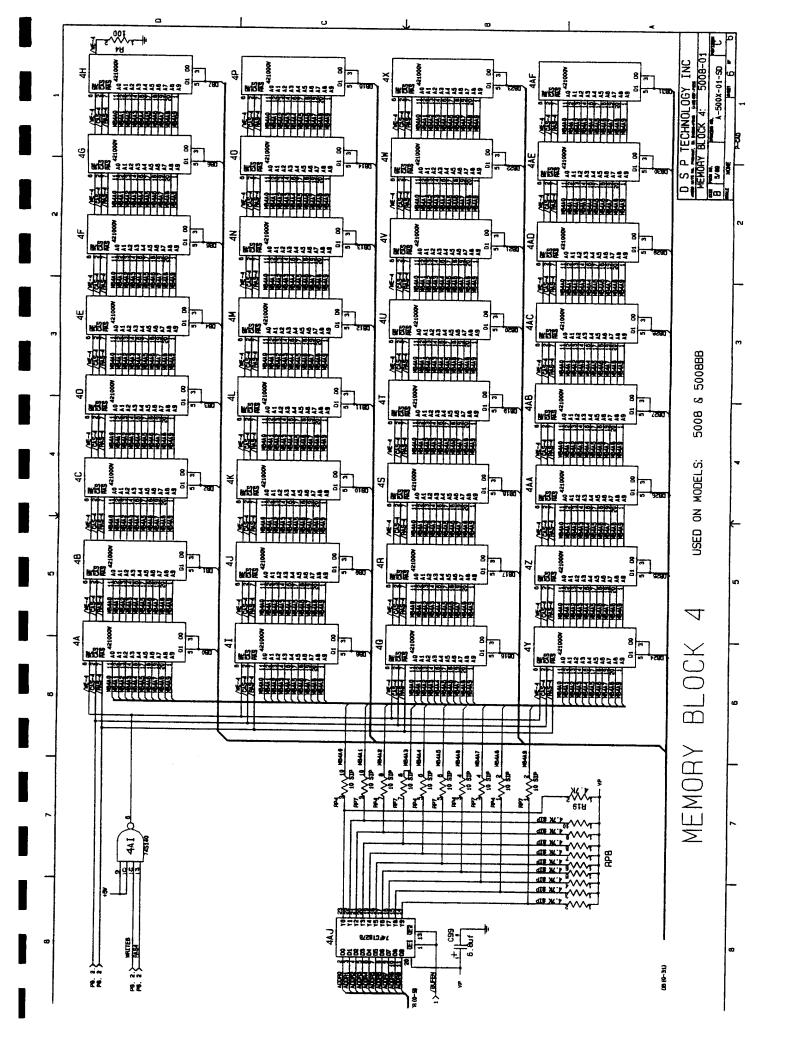

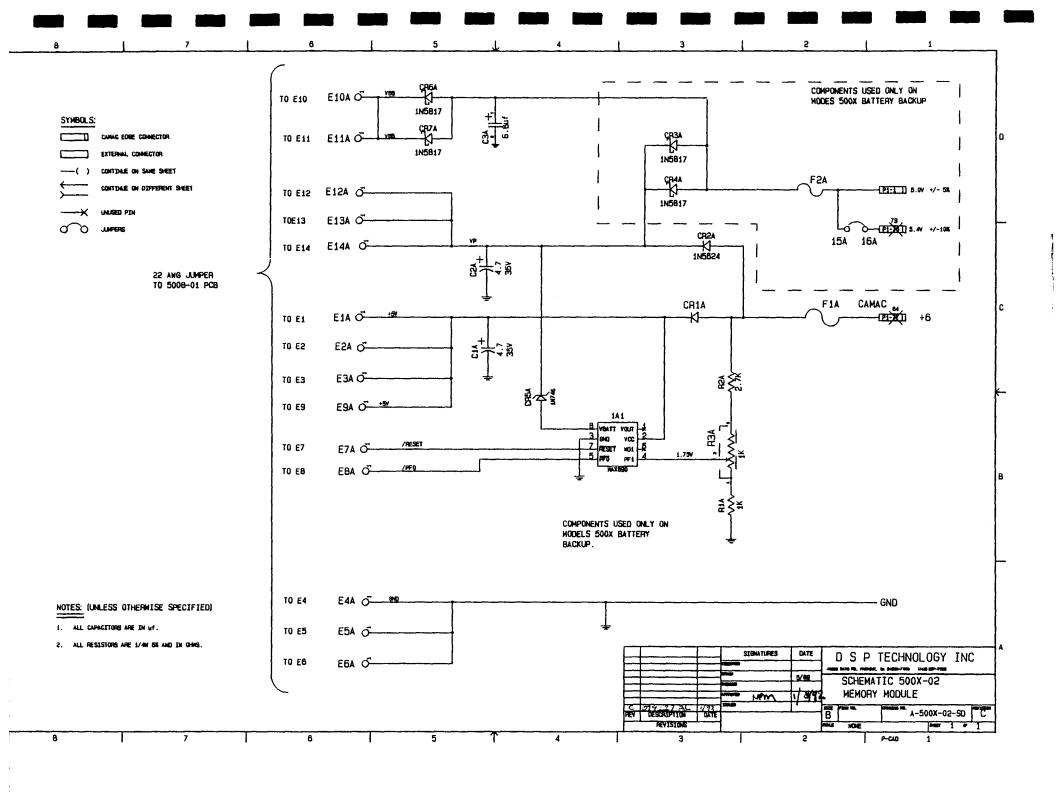

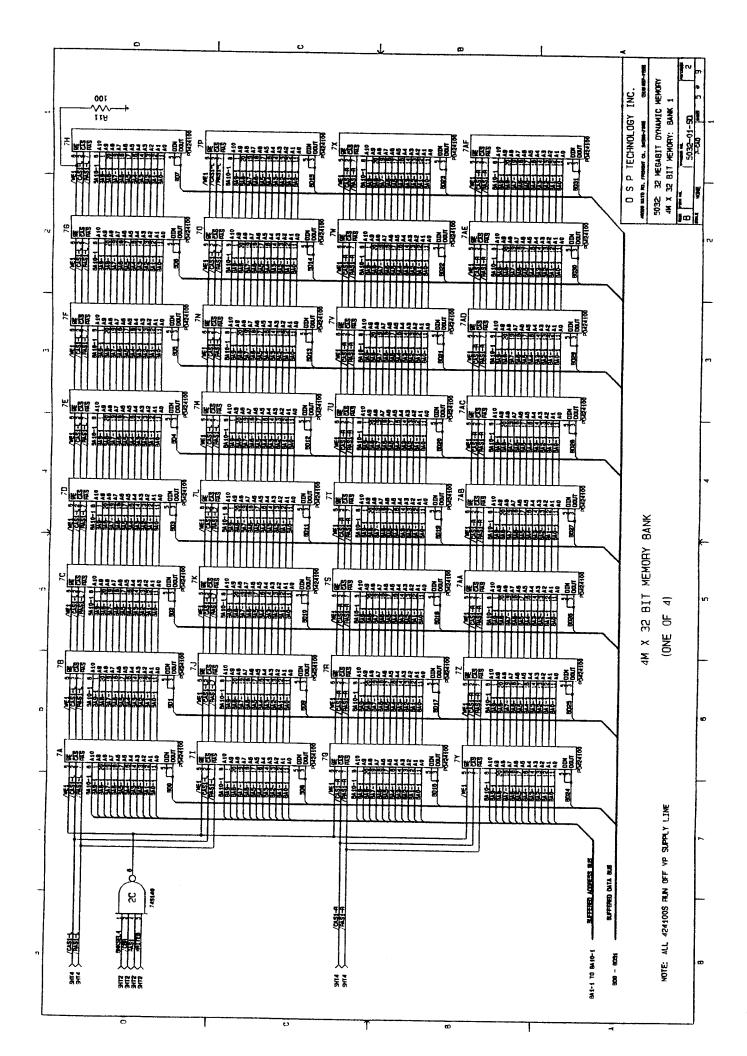

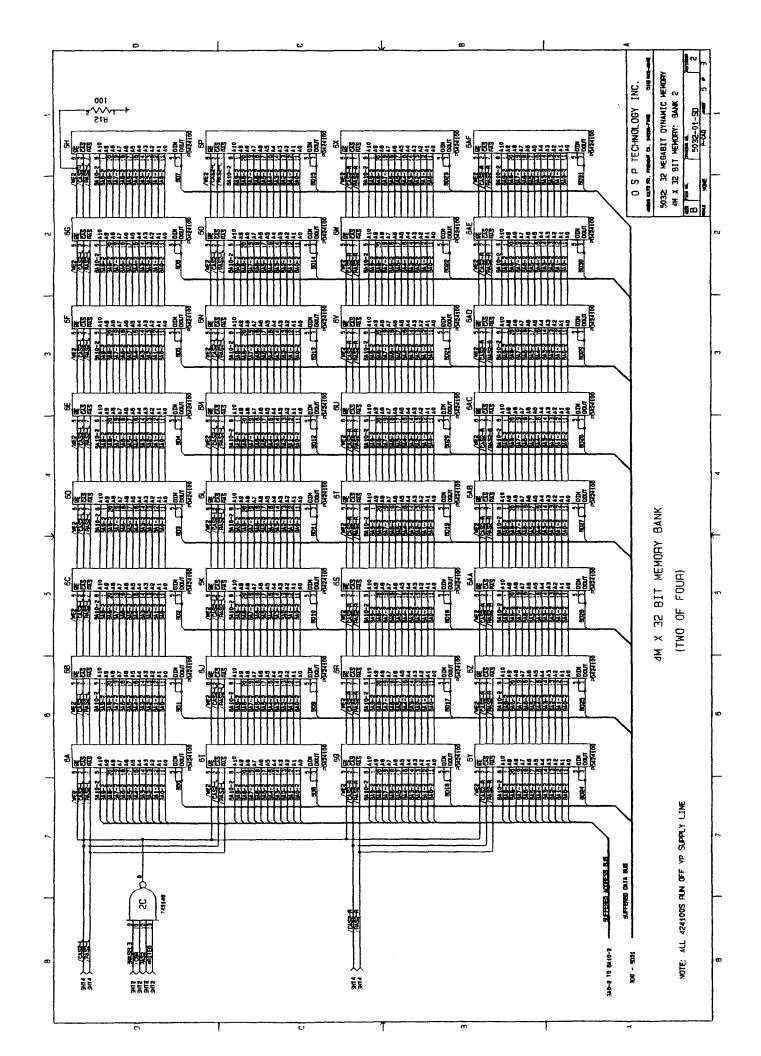

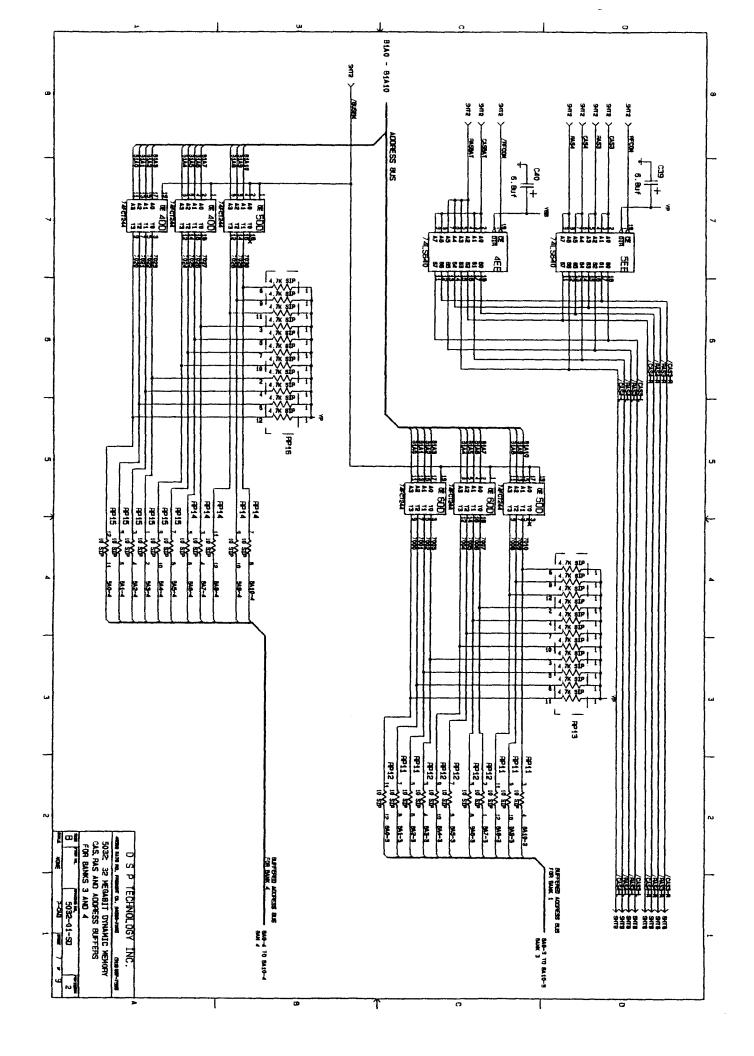

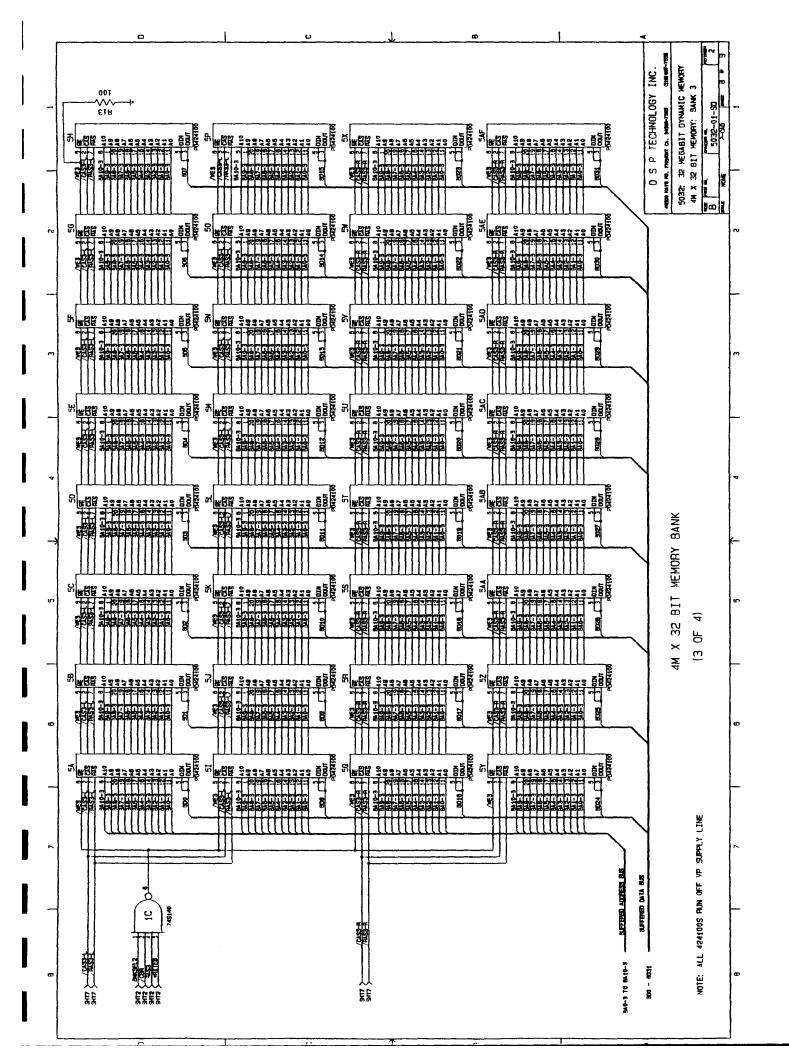

| Section 11 Series 5000 Memory Modules6                 | 7  |

| General Description 62                                 | 7  |

| Front Panel Indicators and Controls                    | 7. |

| LED Indicators 67                                      | 7  |

| Module ID Switches                                     | 3  |

| Module Switch Settings69                               | 9  |

| Input Signal (5200 Series Only)69                      | 9. |

| Write Lock                                             | Ω  |

| Section 12 TRAQ Digitizer Modules7                     | 1  |

|            | TRAQ Digitizer Module Specifications    | 7.2  |

|------------|-----------------------------------------|------|

|            | Temperature Range                       | 72.  |

|            | Front Panel Description                 | 73.  |

|            | LED Indicators                          | 73.  |

|            | Module ID Switches                      | 73.  |

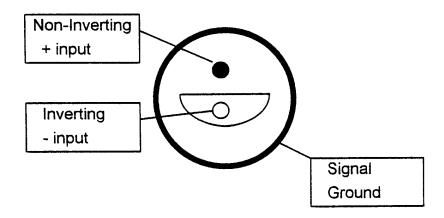

|            | Input Signal Connectors                 | 7.4  |

|            | Bipolar/Unipolar Input Option           | 7.4  |

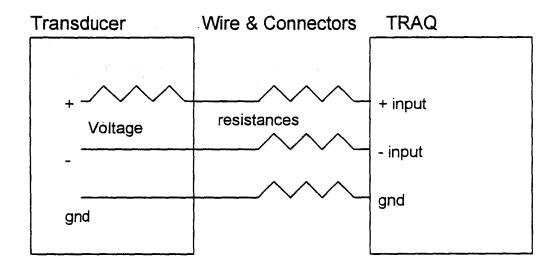

|            | Input Signal Connection                 | 7.5. |

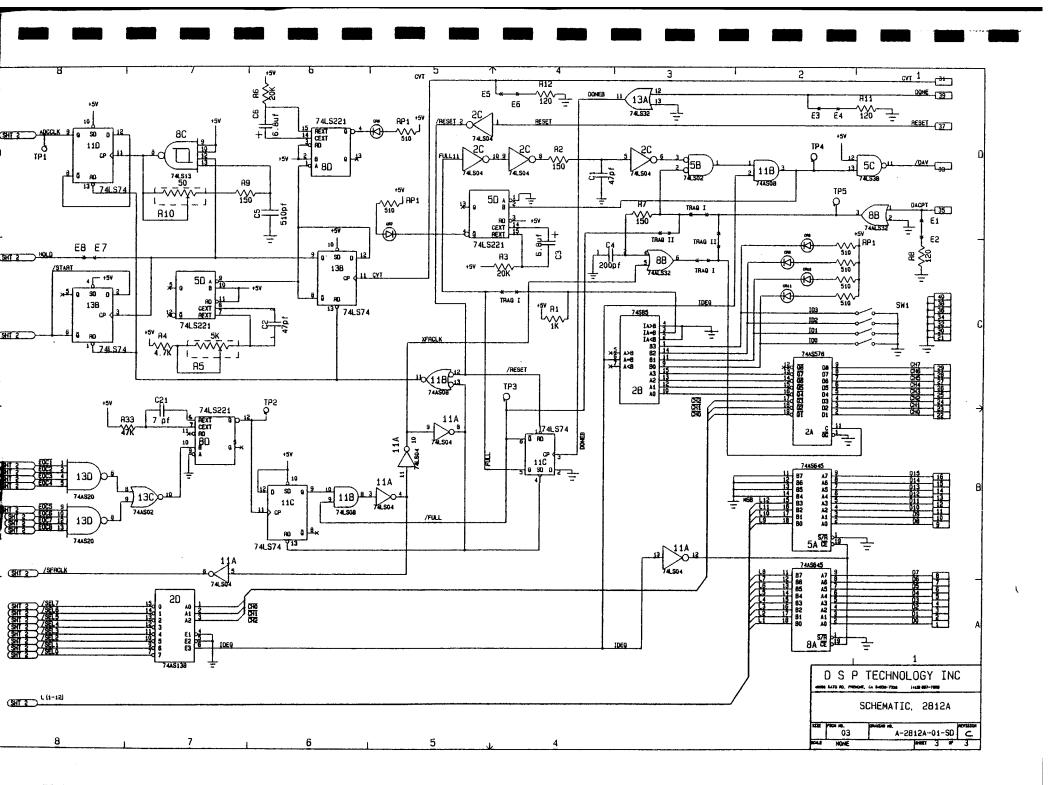

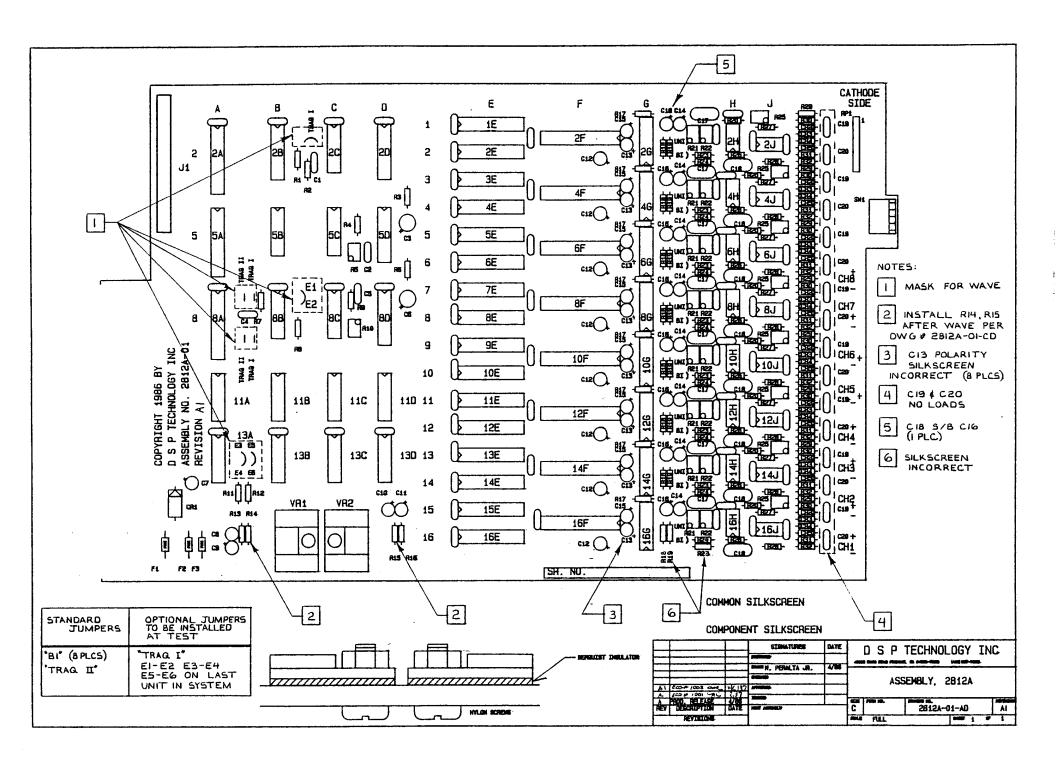

|            | 2812M                                   | 7.6. |

|            | Signal Conditioning.                    | 76.  |

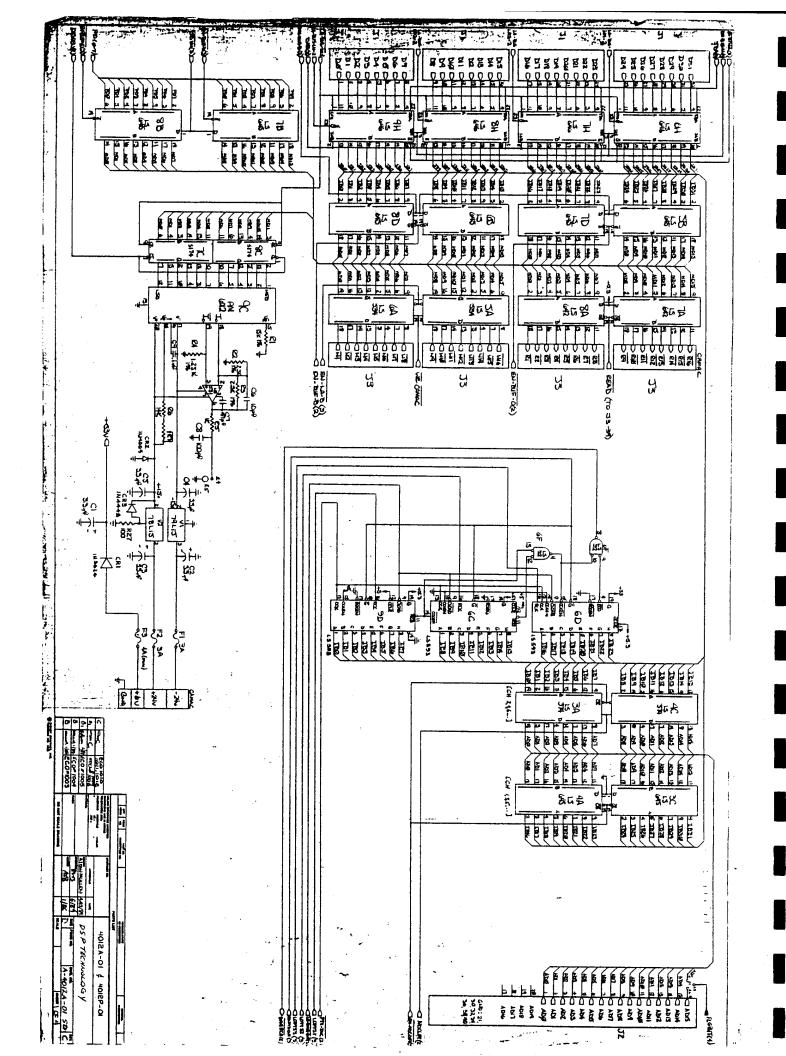

| Section 13 | Data Acquisition Module                 | 79   |

|            | Model 2812 12 bit/100 kHz/8 Channel ADC | 79   |

|            | Bipolar/Unipolar Signal Input Options   | 79   |

|            | Bipolar Calibration and Alignment       | 79   |

|            | Unipolar Calibration and Alignment      | 80   |

|            | Common Mode Rejection                   | 81   |

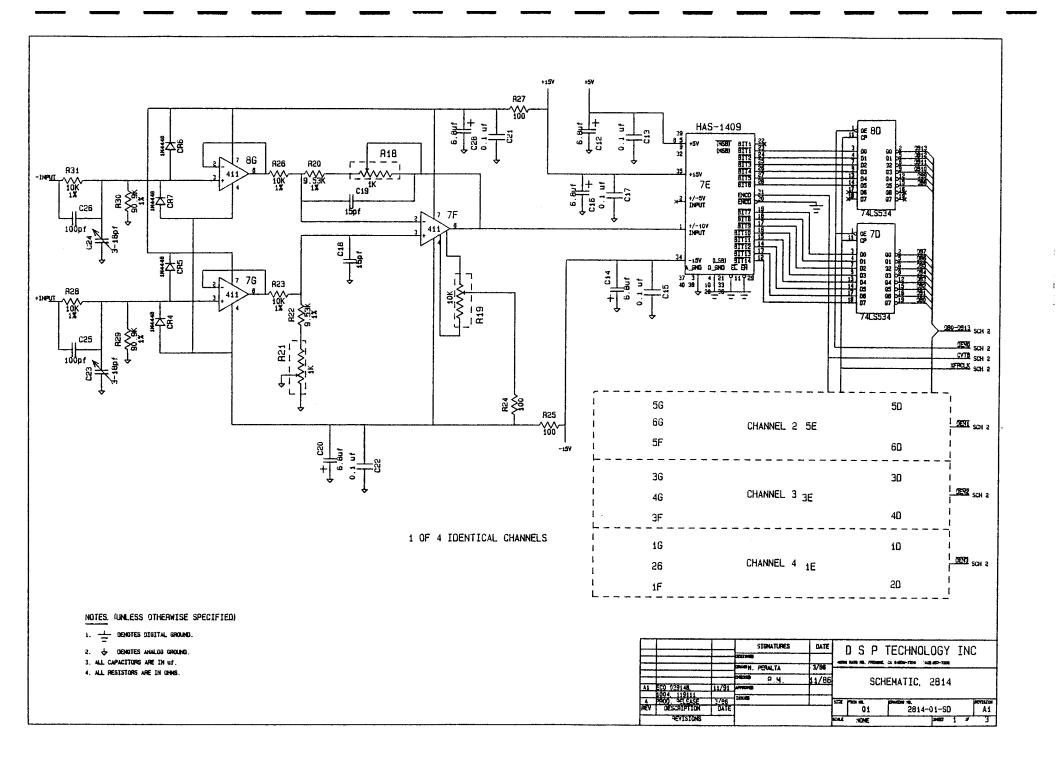

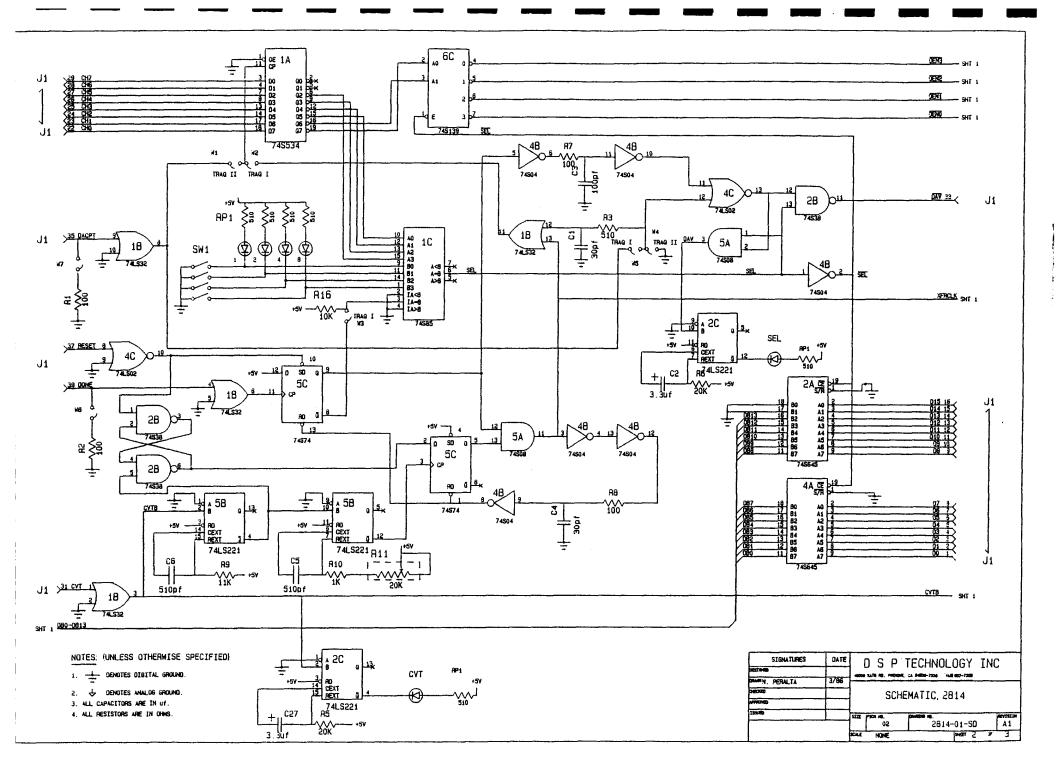

| Model 281  | 4 14 bit/100 kHz/4 Channel ADC          | 81   |

|            | Bipolar Calibration and Alignment       | 81   |

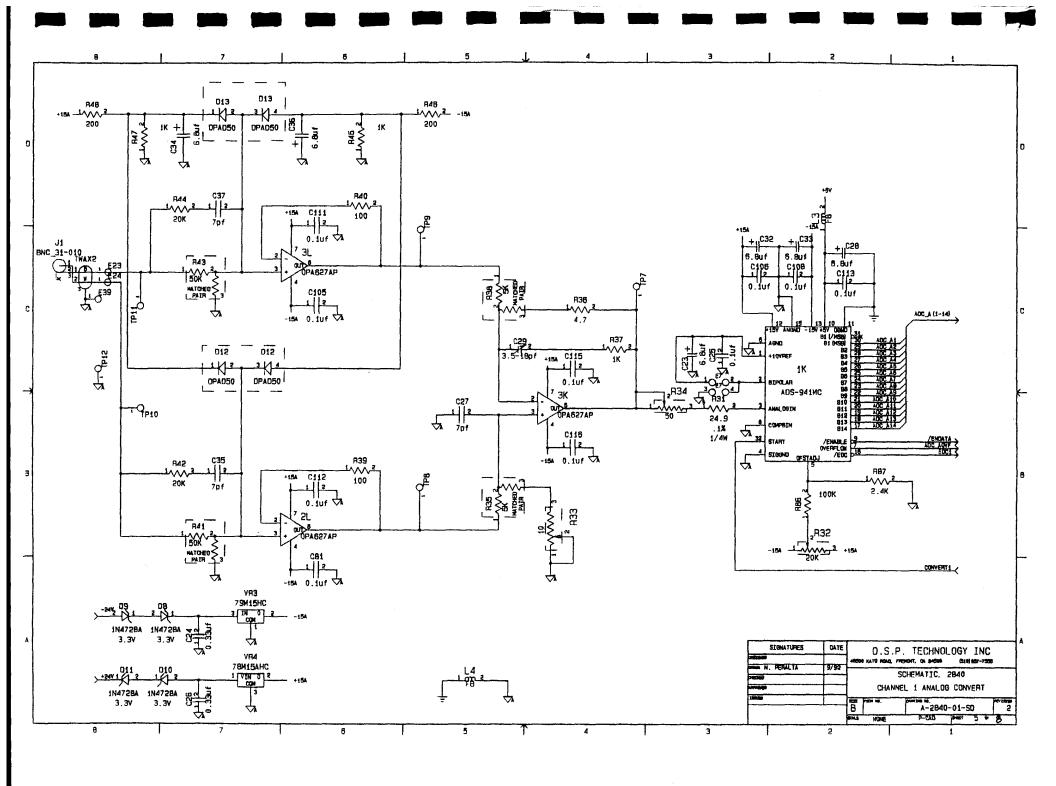

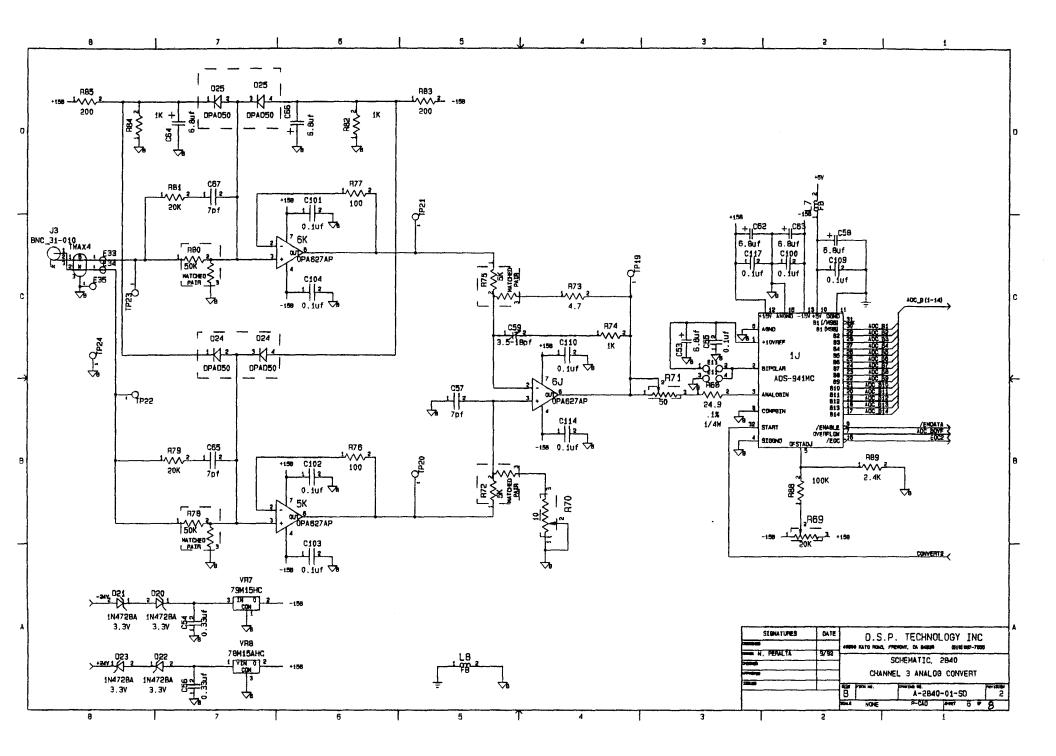

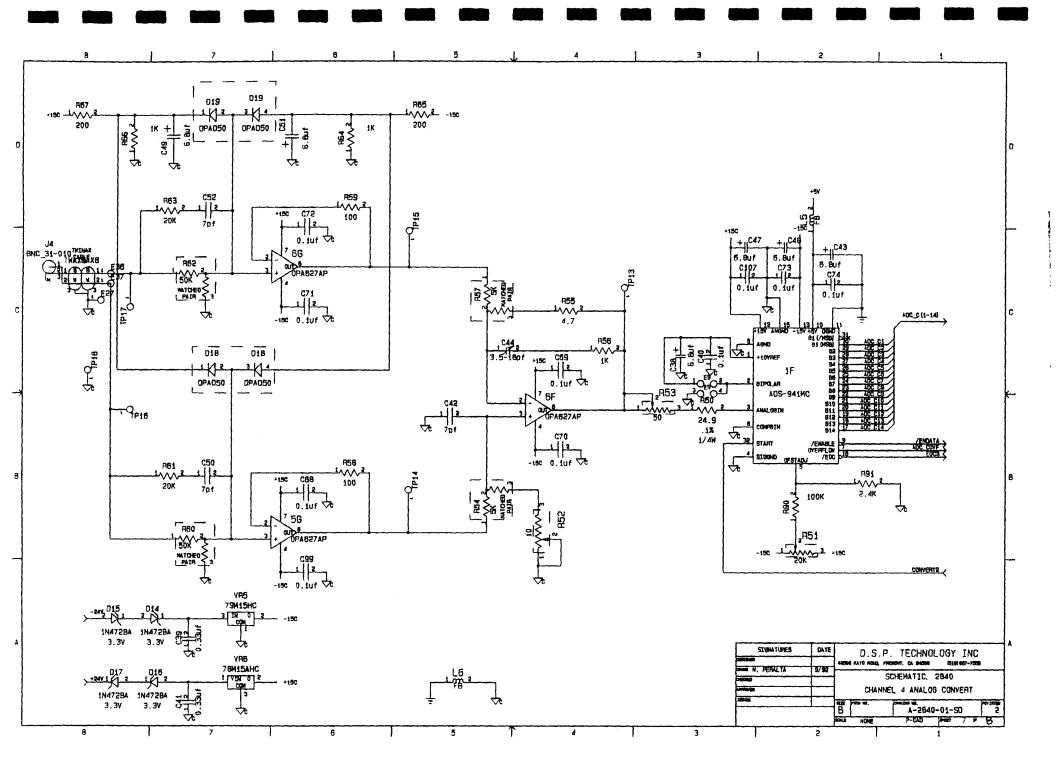

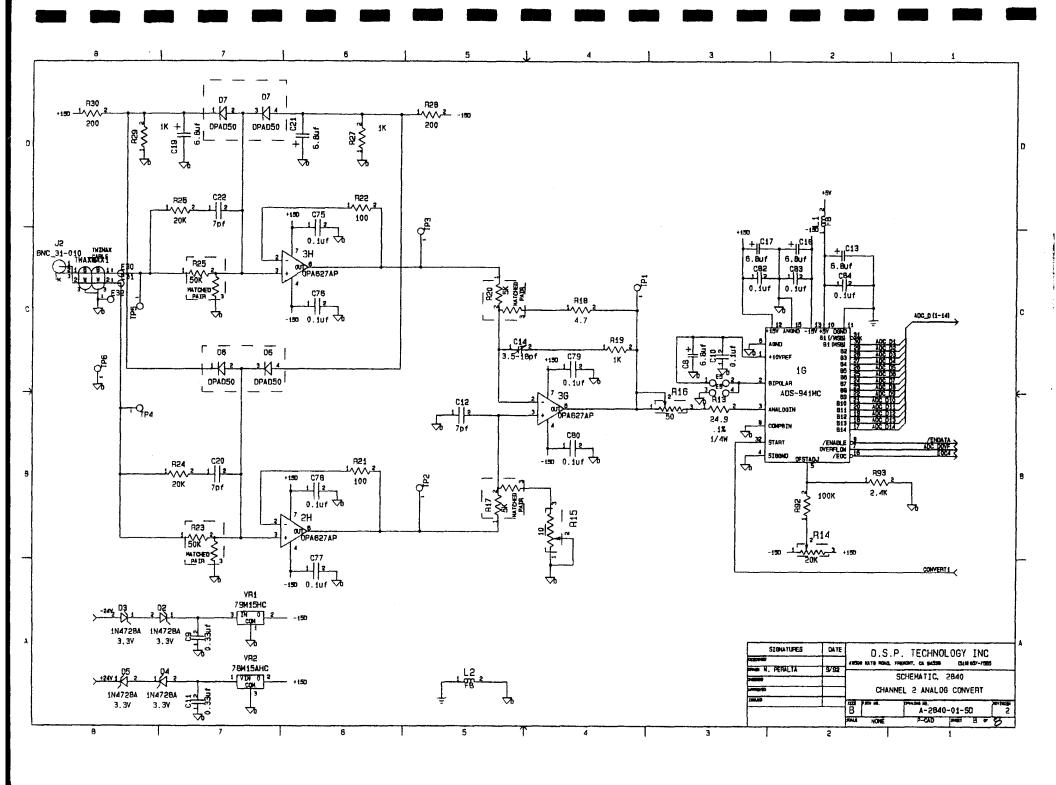

| Model 284  | 0 14 bit/1 mHz/4 Channel ADC            | 81   |

|            | Bipolar Calibration and Alignment       | 81   |

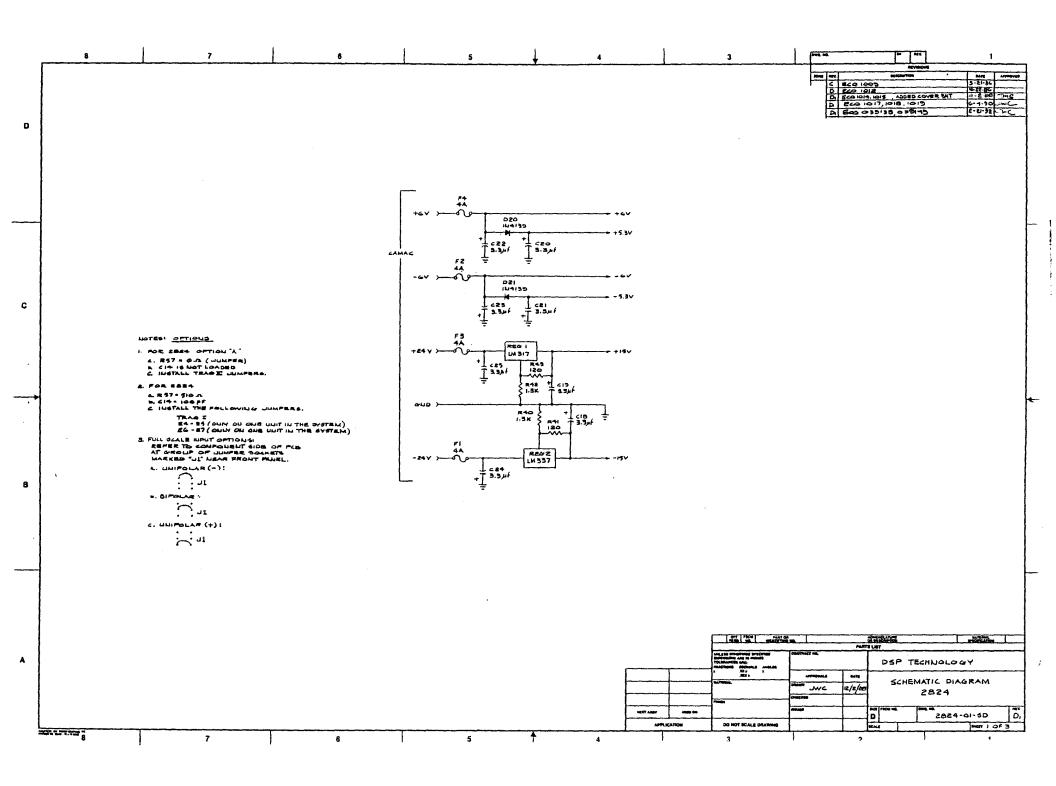

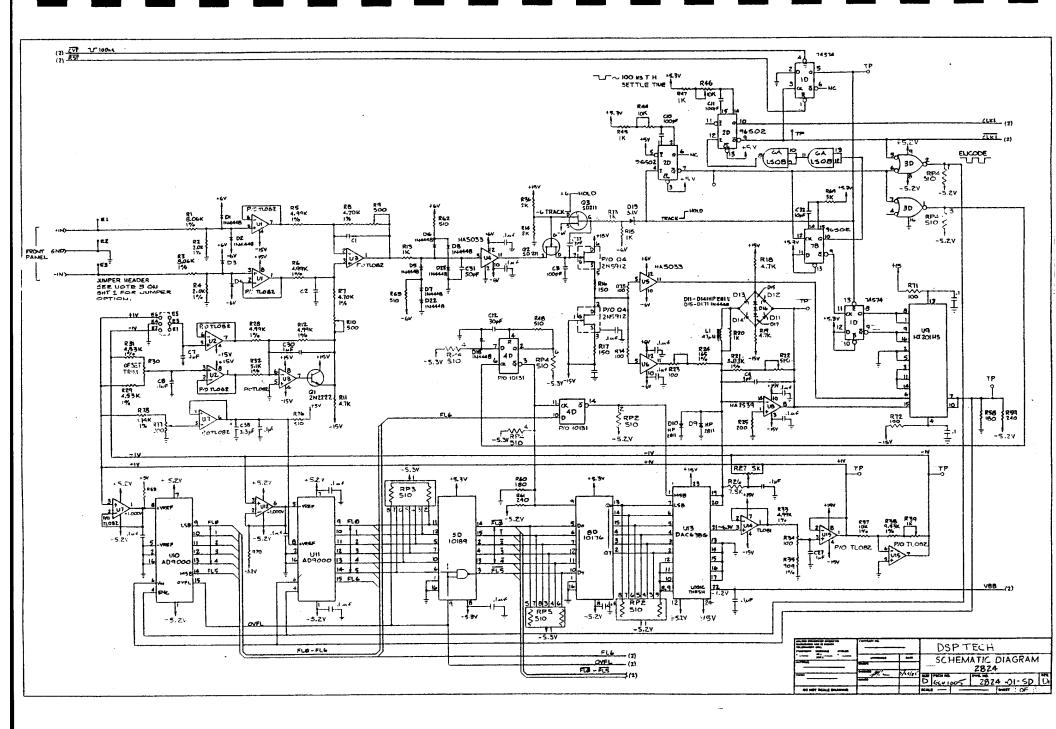

| Model 282  | 4 12 bit/2 mHz/1 Channel ADC            | 82   |

|            | Bipolar Calibration and Alignment       | 82   |

|            | -                                       |      |

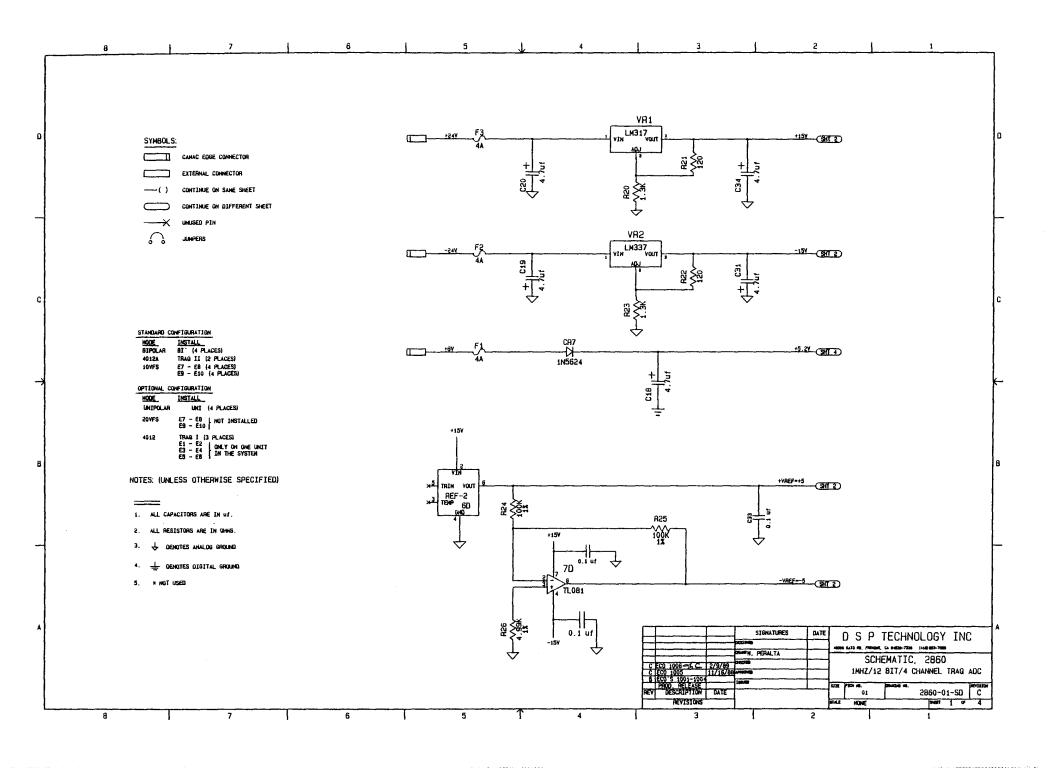

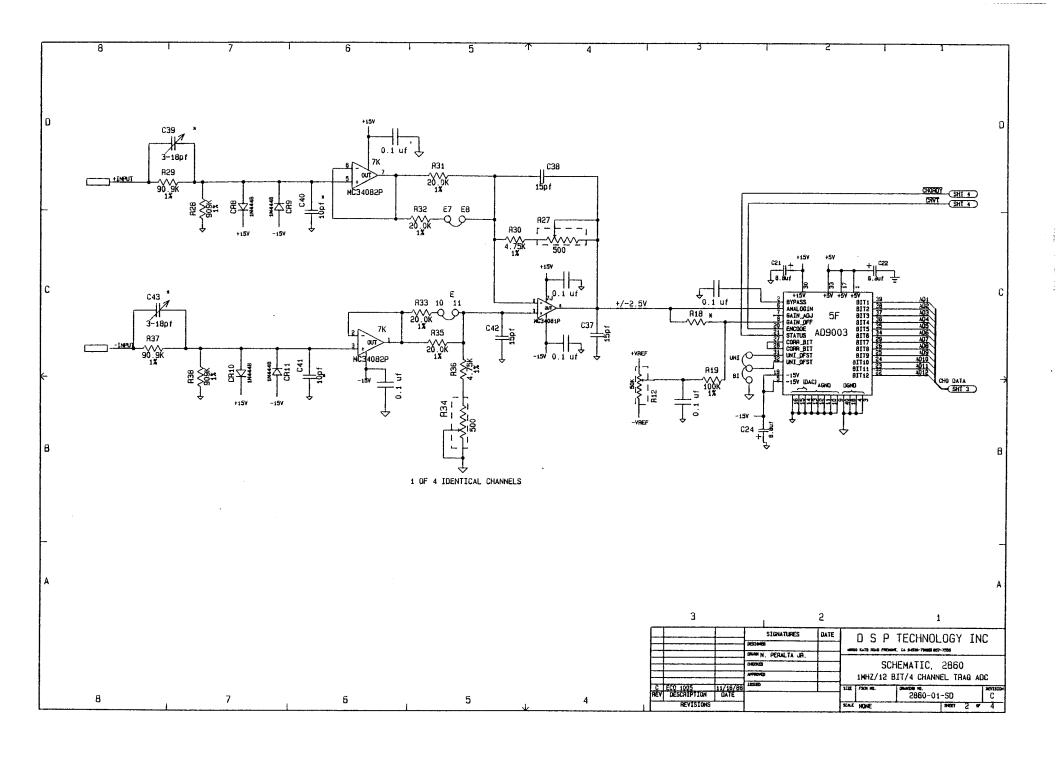

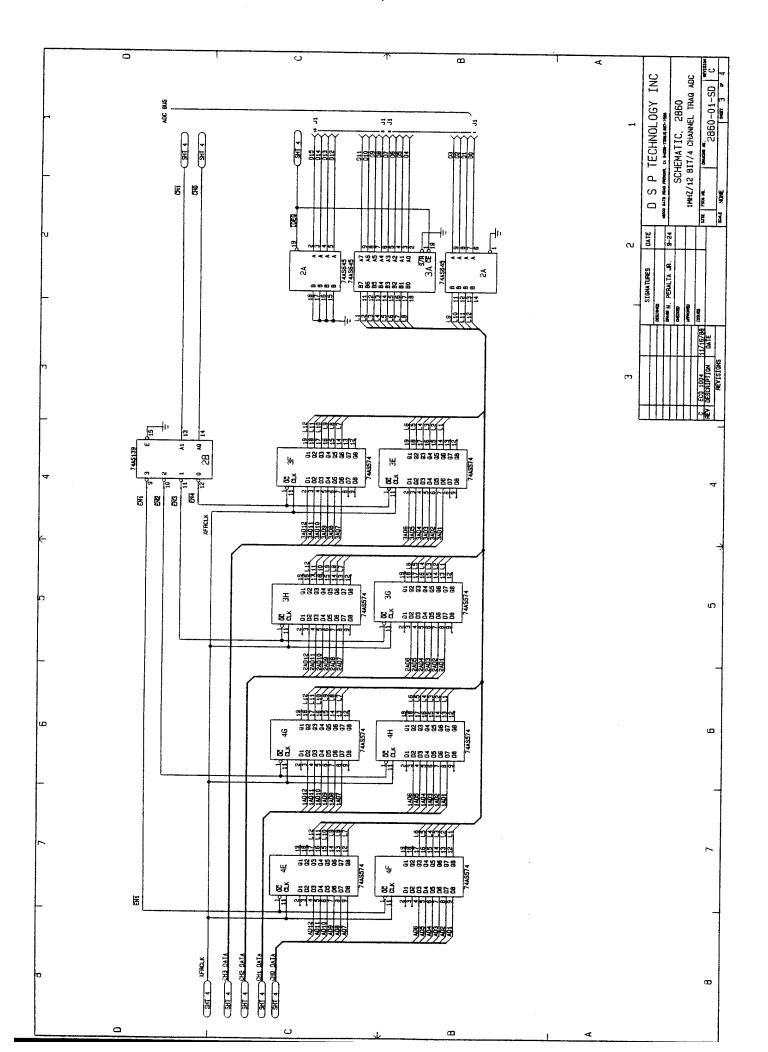

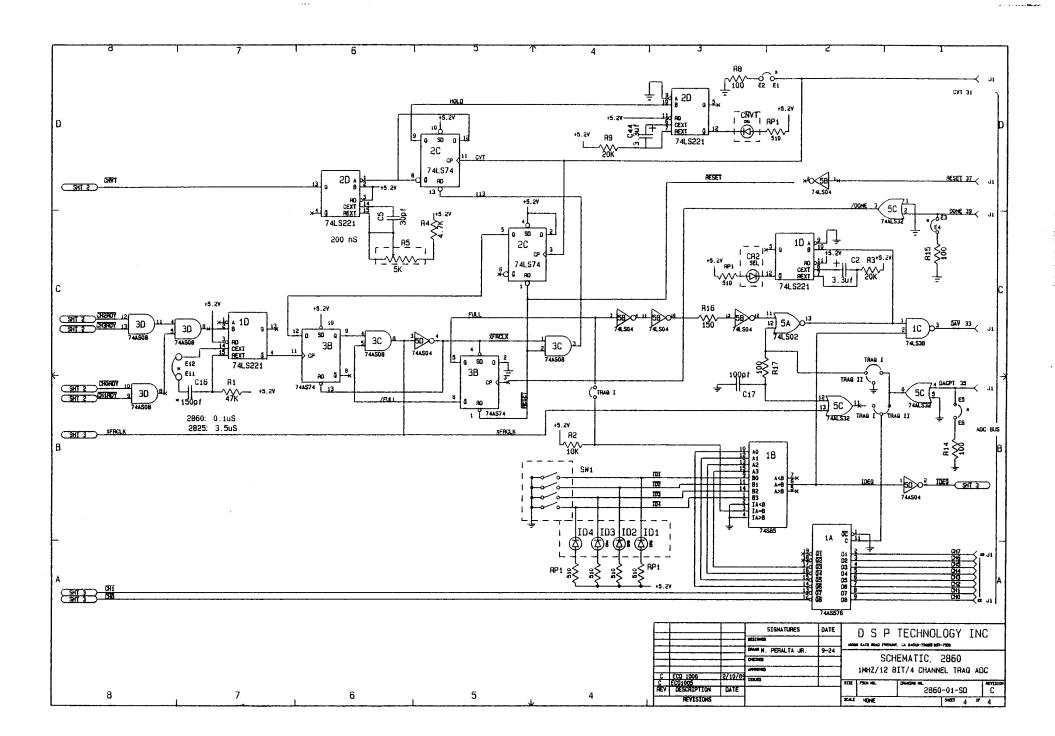

| <b>Model 2860</b> | 12 bit/1 mHz/4 Channel ADC            | .83 |

|-------------------|---------------------------------------|-----|

|                   | Bipolar/Unipolar Signal Input Options | .83 |

|                   | Bipolar                               | .83 |

|                   | Unipolar                              | .83 |

|                   | Calibration and Alignment             | 83. |

|                   | Bipolar Mode Calibration              | 83. |

| Appendices        |                                       |     |

| Schematics        |                                       |     |

| Index             |                                       |     |

### SECTION 1 TRAQ SYSTEM

### **System Description**

DSP Technology's TRAQ system is a modular product which acquires analog or digital data from multiple input channels and stores the information in local memory at rates up to 8 million data samples per second. Modular memory and analog digitizing (or digital interface) units allow easy system field expansion or reconfiguration.

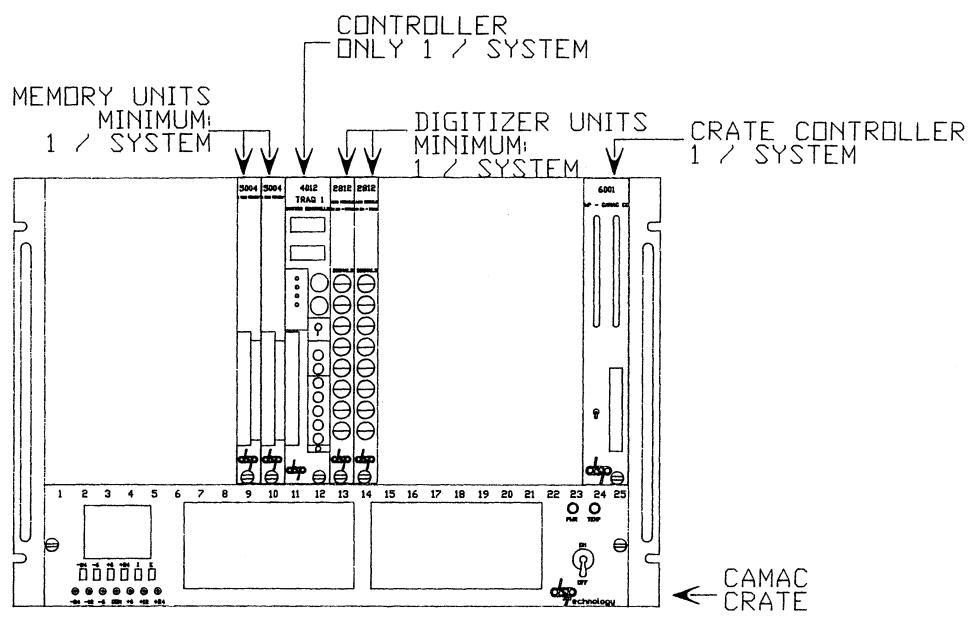

Each TRAQ system is defined by one controller (4012 A or P; 4032 A or P), at least one memory module (5003, 5004, 5200...5032) and at least one digitizer module or input channel (2812, 2824, 2814, 2860...).

Data transferred from the digitizer modules to memory is initiated by a clock pulse which the controller generates from an internal crystal or an external signal. There are actually two selectable internal clocks (CLK1, CLK2) which can be controlled by the user. This allows selected portions of the data to be sampled at different rates. There are many instances where some portions of the data which has higher frequency components needs to be sampled at faster rates. The 4012/4032 will accept an external control signal which causes the unit to switch between the two clock frequencies. There is also available a mode which enables the controller to switch to the second frequency after detecting a "stop trigger." When the controller is sampling with the second clock (CLK2) the 16th bit of the data (MSB) can be set to a binary one. This allows the user to differentiate data sampled at the two clock rates.

### **M** NOTE

This option can be defeated by a jumper strap if the 16th bit is used by the digitizer unit. (See Section 10.)

Once the digitizer units receive the clock pulse (conversion command) all analog data is sampled simultaneously and digital data is stored in local digitizer buffer memories. Analog data is captured by sample & hold circuits which hold the signals constant as the analog to digital converters (ADCs) operate. Each sample & hold feeds directly into its own ADC. At the end of the conversion cycle, a signal is sent back to the controller

signaling that data is ready for readout. The controller then sequentially reads data for all required channels. The user can select the Number Of Channels (NOC) that are actively converting. As NOC is decreased the controller will allocate more memory storage for the active channels. Data is transferred sequentially as 16-bit words to the controller at a 8 Megasample/second rate. The controller double buffers the digitizer data, forming a 32bit word which is stored in memory. When sampling is started the first data sample is stored at address zero of the memory and subsequent data at the next incremental memory location. After the memory is filled, new data is written over the previous data starting at address zero. This continues in a "round robin" fashion until a "stop trigger" is received. The "stop trigger" is either an external TTL signal, a front panel switch, or a computer command. This trigger initiates the "post trigger" sampling sequence which determines how much data is recorded before the trigger versus after the trigger. If "PTS" is set to "8/8" then all data is post trigger and sampling will stop once the entire memory is filled one more time.(i.e., if the memory size/channel is 32 K samples; another 32 K samples of data is recorded). If "PTS" = "0/8" then recording stops immediately and all the data was recorded before the time of the trigger. The controller allows the user not only to select the amount of memory per data channel, but also to divide this memory in 1/8th segments of post and pre-trigger data. The controller keeps track of where the earliest recorded sample resides in memory. All data read, or displayed starts from this sample.

After recording is complete the controller will display the data (through a digital-to-analog converter) or read it out to the computer. Data can be read starting at any 1024 block in the record. Also data readout can terminate at any point in the record and immediately go to another channel for readout.

### **TRAQ Controllers**

The system controller is in command of all data acquisition. It communicates with the computer or user (through front panel controls) to determine the required sampling rate, pre/post trigger information, number of active data channels, memory allocation, data display and data readout. All control settings can be saved in a non-volatile memory to be restored on power-up. Communication with the computer is via the CAMAC bus; however, all data acquisition is passed through two private busses. Data from the input units is sequentially passed to the controller and then out to memory. The data is sequentially retrieved by the controller for display and readout.

The controller also executes a set of diagnostic routines on command or power up. These routines will usually catch and isolate any fatal system problem.

There are presently four controllers available for the TRAQ system:

| Controller | TRAQ Memory<br>Limitations                        | Comments                                                                       |

|------------|---------------------------------------------------|--------------------------------------------------------------------------------|

| 4012A      | 16 MegaSamples total;<br>4 MegaSamples/Channel    | Standard Controller                                                            |

| 4012P      | 16 MegaSamples total;<br>4 MegaSamples/Channel    | Data retention on power down. (Requires battery backed-up TRAQ memory modules) |

| 4032A      | 256 MegaSamples total;<br>256 MegaSamples/Channel | Standard Controller                                                            |

| 4032P      | 256 MegaSamples total;<br>256 MegaSamples/Channel | Data retention on power down. (Requires battery backed-up TRAQ memory modules) |

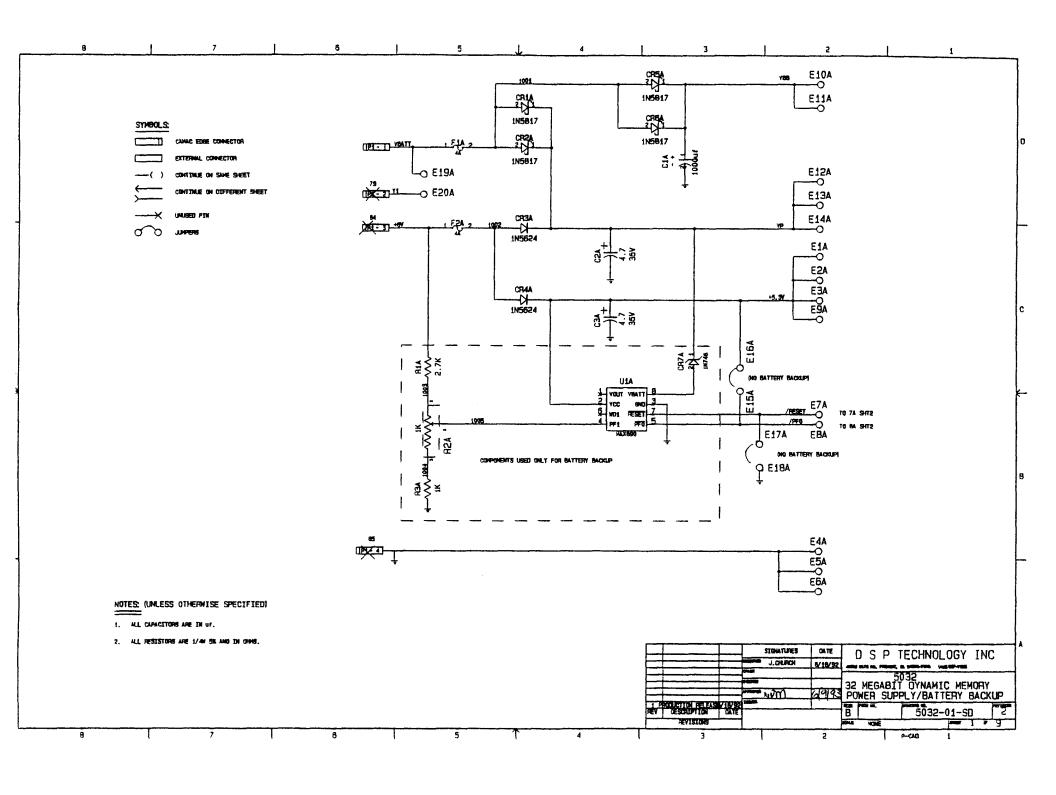

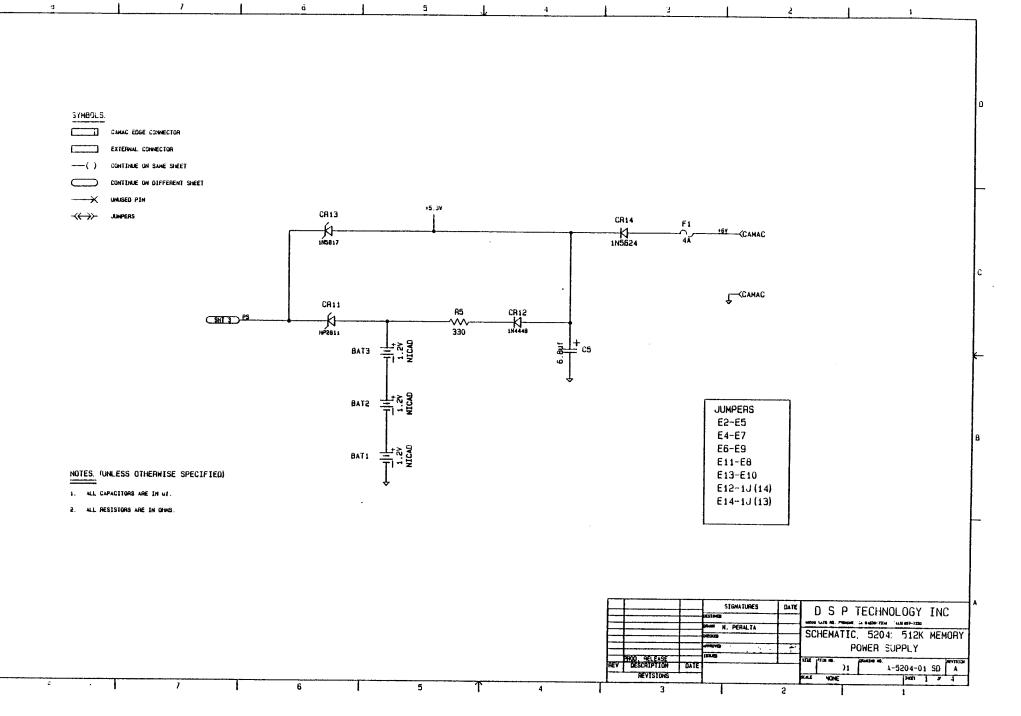

The 4012P/4032P units are used in environments where data retention upon loss of power is critical and they have extra control signals to protect acquired data. The 4012P has an optional reserved memory section for calibration data. These controllers are used with 5204 memory modules (internal batteries) or 5008 Bs, 5432 Bs (using external batteries).

### **TRAQ Memories**

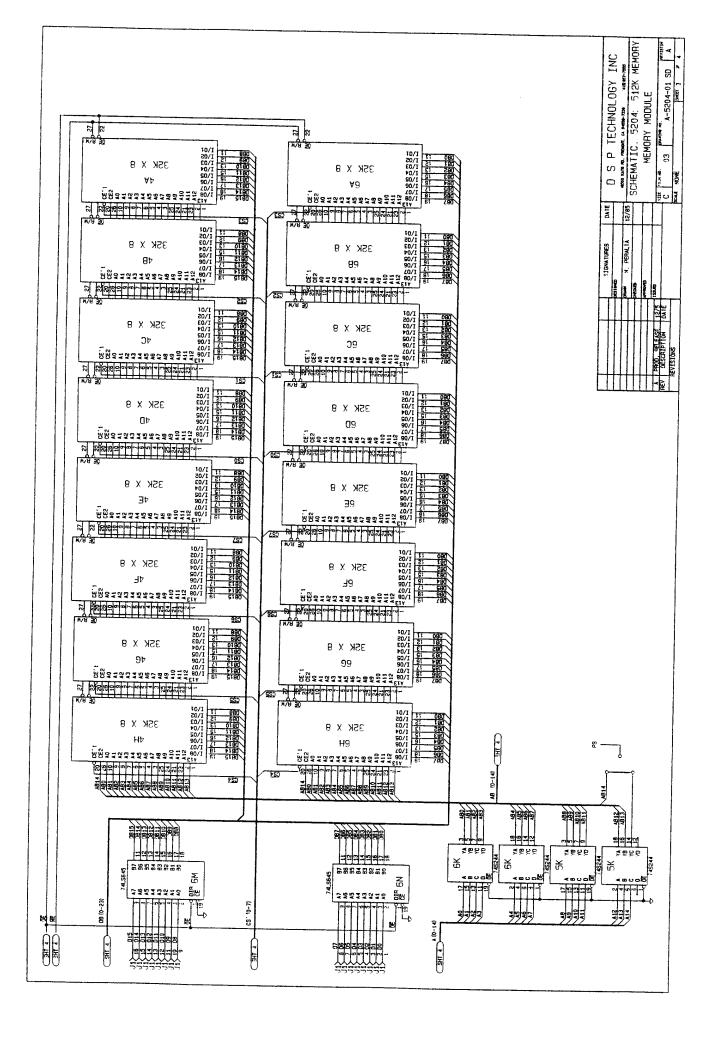

The amount of data storage in a TRAQ system depends on the selected controller and memory module.

| Model | Memory Size<br>(MegaSamples) | Max<br>Modules/System | Comments                |

|-------|------------------------------|-----------------------|-------------------------|

| 5004B | 1                            | 8                     | 4012 or 4032 Controller |

| 5005  | 2                            | 4                     | 4012 or 4032 Controller |

| 5006  | 4                            | 4                     | 4012 or 4032 Controller |

| 5007  | 6                            | 1                     | 4012 or 4032 Controller |

| 5008  | 8                            | 4                     | 4012 or 4032 Controller |

| 5408  | 8                            | 8                     | 4032 Controller         |

| 5416  | 16                           | 8                     | 4032 Controller         |

| 5424  | 24                           | 8                     | 4032 Controller         |

| 5432 | 32  | 8 | 4032 Controller                                        |

|------|-----|---|--------------------------------------------------------|

| 5204 | 0.5 | 8 | 4012 or 4032 Controller;<br>Internal Battery Retention |

### **M** NOTE

5005..5008 and 5408..5432 are also available in B version for external battery backup.

All memory modules on a system should be of the same type. If modules are mixed, consult the factory for configuration information.

### **Analog-To-Digital Converters**

A variety of analog to digital conversion units are currently available for the TRAQ system. A maximum of 256 digitizer channels can be run on one system but the total throughput rate cannot exceed 8 million samples per second. The total throughput is calculated as the product of the number of active digitizer channels times the sampling rate.

Presently the following units are available:

| Model | Number of<br>Channels/Module | Maximum Conversion<br>Rate/Channel | Resolution |

|-------|------------------------------|------------------------------------|------------|

| 2812  | 8                            | 100 KiloSamples/Sec                | 12         |

| 2814  | 4                            | 100 KiloSamples/Sec                | 14         |

| 2824  | 1                            | 2 MegaSamples/Sec                  | 12         |

| 2840  | 4                            | 1 MegaSamples/Sec                  | 14         |

| 2860  | 4                            | 1 MegaSamples/Sec                  | 12         |

### **Digital-to-Digital Converters**

Two modules, 2932 and 2904, are available for inputting digital information. The 2904 is used to record encoder signals from rotating devices and is not covered in this manual (see 2904 manual). The 2932 is a general purpose digital input module which will record two 16-bit TTL channels (32-bits) into TRAQ simultaneously with ADC data from the analog-to-digital channels. It also contains spare wire wrap socket space and a CAMAC interface for user customization.

### **Typical TRAQ Configurations**

| Controller | Метогу | Allowable<br>Memory Sizes | Max Nu<br>ADC ch | mber of |

|------------|--------|---------------------------|------------------|---------|

|            |        |                           | 2812             | 2860    |

| 4012 A/P   | 5004B  | 1 to 8 Meg                | 80               | 8       |

| 4032 A/P   | 5432   | 32 to 256 Meg             | 80               | 8       |

### **MNOTE**

This assumes that each channel of the

2812 is sampling at 100 kHz

2860 is sampling at 1 MHz

### **TRAQ** Current and Power Requirements

| Model       | Current (amps) |      |             |       | Power (avg.) |

|-------------|----------------|------|-------------|-------|--------------|

|             | +6             | -6   | +24         | -24   | (Watts)      |

| Controllers |                |      |             |       |              |

| 4012 (A/P)  | 4.0            | 0.05 | 0.05        | 0.05  | 27           |

| 4032 (A/P)  | 4.0            |      | 0.05        | 0.05  | 27           |

| Memories    |                |      | 1           | T     | T            |

| 5004B       | 2.5            |      |             |       | 15           |

| 5005        | 1.25           |      |             |       | 7.5          |

| 5006        | 1.5            |      |             |       | 9            |

| 5007        | 1.75           |      |             |       | 10.5         |

| 5008        | 2.0            |      |             |       | 12           |

| 5408        | 1.25           |      |             |       | 7.5          |

| 5416        | 1.5            |      |             |       | 9            |

| 5424        | 1.75           |      |             |       | 10.5         |

| 5432        | 2.25           |      |             |       | 13.5         |

| Digitizers  | <del></del>    |      | <del></del> | ī     | <del>1</del> |

| 2812        | 1.5            | 0.55 | 0.150       | 0.150 | 20           |

| 2814        | 1.3            |      | 0.150       | 0.250 | 18           |

| 2824        | 1.0            | 0.70 | 0.100       | 0.100 | 15           |

| 2840        | 1.0            |      | 0.600       | 0.600 | 35           |

| 2860        | 1.7            |      | 0.250       | 0.270 | 20           |

| 2932        | 1.0            |      |             |       | 6            |

| 2904        | 2.0            | -    |             |       | 12           |

### TRAQ Installation

The minimum system configuration consists of one signal conversion channel (ADC), one controller, and 1 Megasample of memory. A CAMAC crate is also required and usually a crate controller to allow the TRAQ system to communicate with a computer. (Only one crate controller is required for each CAMAC crate).

### System Interconnections

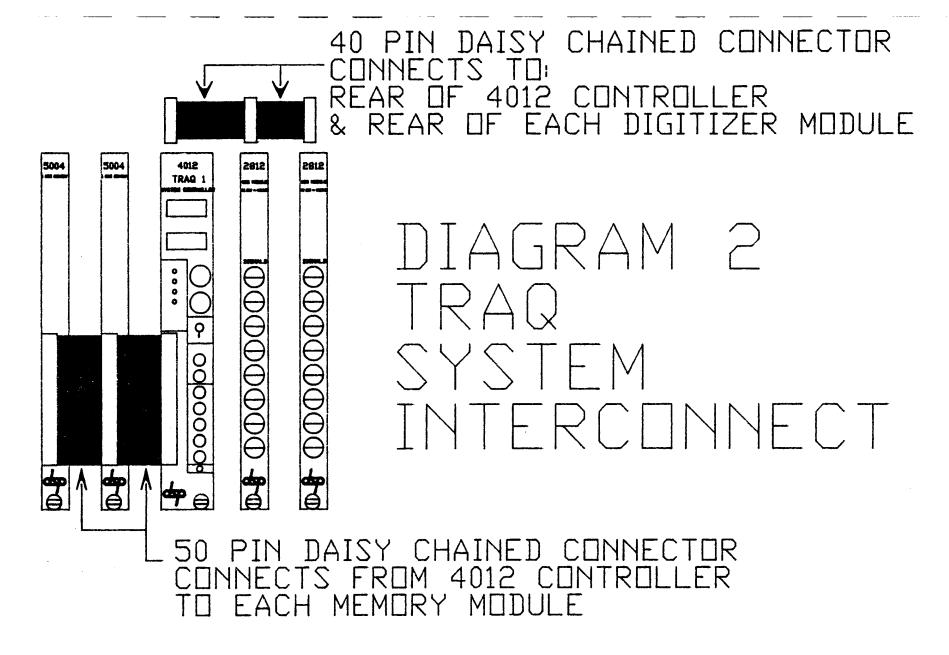

- 1) The memory modules are connected to the controller via a 50 pin flat cable. This cable plugs into the front panel TRAQBUS connectors. The memory modules usually reside to the left of the controller in the crate. This keeps the flat cable from interfering with the other controller signal cables. TRAQ systems are delivered with flat cables built for the system configuration ordered. If the system configuration is not specified, the cables will correspond to an equal distribution of ADC modules and memories.

- 2) During power-up diagnostics the controller will determine how much memory is on the bus. There must be at least 1024K words. The diagnostic routines will fail at the MEM1 test if no memory is found. Memory modules must have their I.D. switches set so that one module has ID=0, another ID=1, etc., (see Section 11, Memory Modules).

- 3) The modules can be located in any order in the crate relative to the controller. The 50-pin flat cable connector should be as short as possible to reduce bus noise and crosstalk. Refer to the memory module sections and the diagnostic section of this manual for further information regarding memory configurations.

- the rear of the modules. This cable is also built for the system configuration originally ordered. The digitizer modules are usually installed to the right of the controller in the crate. The first digitizer module must have its ID. switch set to zero, the second to one, etc. The modules can be located in any order relative to the 4012/4032. For DSP digitizers (ex: 2812,8 channel ADC), channel 1 will correspond to channel 1 of the module with ID. switch set to zero; channel 9 will correspond to channel 1 of the module with ID. switch set to 1, etc.

- 5) After installing the units in the crate and connecting the two flat cable connectors, turn on the crate power. The controller will now sequence through a set of

diagnostics. If any problem is found the controller will display a "FAIL" message at the current diagnostic. Refer to the diagnostic part of the controller section.

### **M** NOTE

The controller is not able to check the connection to the digitizer units. This can be checked by setting NOC to the maximum number of channels and CLK1 to the maximum conversion rate. Depress the "start" sampling switch and check that the "CVT" and "SEL" LEDs on the digitizer modules are on. Also the "DACY" LEDs on the memory modules should be on. If more than one memory module is present the "SEL" LEDs should be blinking on/off at a rate dependent on the sampling speed. If this fails check the cable interconnection between the controller and the digitizers.

A failed digitizer or memory can usually be determined without removing the interconnection cable. To locate a failed memory just change the ID to a number out of the contiguous memory address range (and the other memory IDs to fill in for the removed module), and repower the system.

### **☑ EXAMPLE**

Consider a four module memory system where the third module is suspected to have failed:

| Module Number | ID Before | ID After |

|---------------|-----------|----------|

| 1             | 0         | 0        |

| 2             | 1         | 1        |

| 3             | 2         | 15       |

| 4             | 3         | 2        |

When the system is re-powered the controller will find only 3 modules in the system (the controller assumes that an empty address space means the end of the memory chain). If the system is now functional, module 3 has failed.

The digitizers can be checked in the same fashion except that it is not necessary to re-power the system. A failed digitizer can also be isolated by changing NOC. This will reduce the number of active channels and not address the modules with higher IDs.

- 7) When using the TRAQ system for transient recording there are several parameters that must be set carefully:

- a) NOC (number of active ADC channels) must be equal to or less than the number of actual digitizer channels. The 4012/4032 expects a "handshake" signal from each channel when transferring data and if no channel is present the controller will wait indefinitely for the handshake.

- b) CLK1 or CLK2 must not be greater than the maximum conversion speed of the channels or else erroneous data will be recorded. Also, the user must be careful not to select a combination of NOC and CLK1, CLK2 which exceeds the maximum TRAQBUS speed of 8 megasamples/second. For instance,

CLK1 (FREQUENCY) <= 8 MHz/NOC

CLK2 (FREQUENCY) <= 8 MHz/NOC

### **☑ EXAMPLE**

Using 50 active channels of 2812 modules, each channel converting at 100 kHz gives:

(50 channels) x (100 KHz) = 5000 kilo samples/second (5 megasamples/second)

which therefore does not exceed the maximum bus rate.

c) Since the controller accommodates a large amount of memory/channel the user should be careful that "stop triggers" are not generated before sufficient

samples have been recorded or old and new data will be intermixed. This is especially true when PTS =0 (all pre trigger information).

### **☑ EXAMPLE**

Consider using one active channel at 1 MHz (NOC=1, CLK1 = 1 MHz) and one megaword of memory. With these parameters it requires one second to sample all of memory. If PTS=0 and the "stop trigger" is received 1/2 second after sampling begins the last 1/2 of memory is never written into and will contain old data. If PTS=8/8 there is no problem as all the data (and all of memory) will be recorded after the "stop trigger" arrives.

# Section 2 Model 4012 and Model 4032 TRAQ Controllers Operational Description

### **General Description**

The DSP models 4012(A and P) and 4032 (A and P) TRAQ system controllers direct the flow of data between signal conversion units such as analog to digital converters (ADCs), scalers, etc. and memory storage units (Models 5004B, 5008). Up to 256 signal conversion channels can be controlled by one controller with a maximum TRAQBUS transfer rate of 8 million samples per second. Up to 16 megasamples of 16 bit data can be stored using a 4012 Controller and 256 megasamples using a 4032.

As the number of active channels are decreased the controller will allocate more memory to each channel. Also the controller allows the user to increase the number of active channels (NOC) in increments of two (except for NOC=1), i.e. NOC can be 1, 2, 4, 6, 8, 10..256. The memory size (record size) allocated to each channel is set by the controller and depends on the number of active channels and the total memory size. The user may select record sizes from the maximum memory/channel allowed down to 1024 samples. Once data acquisition is initiated the memory is written into continuously until a "stop trigger" is received which causes the controller to stop sampling after the correct number of post trigger samples have been recorded. The number of post-trigger samples is set in increments of 1/8 of the record size (0, 1/8, 2/8....8/8). The "stop trigger" is either an external TTL signal, front panel switch, or computer command.

After completion of sampling, data is either displayed (through a digital-to-analog converter) or read to the computer. The controller has an internal 12 bit digital-to-analog converter which allows the user to view a reconstructed analog waveform on an oscilloscope. A trigger is also provided to synchronize the display. Data is displayed or read starting at the earliest sample recorded. The user can select which channel to display or read. The controller displays all of the recorded data; however, data can be read by the computer starting at any 1K (1024) block.

Signal conversion units are DSP units such as Models 2812 and 2824. Two clock frequencies are available to accommodate switchable sampling rates and are controlled by either:

- 1) An external control signal "CLK SWI" which activates the first clock (CLK1) when the signal is at TTL low and the second clock (CLK2) when "CLK SWI" is TTL high.

- 2) The "TRIG" signal which causes the controller to start counting down the preset number of post-trigger samples. In this mode all pre-trigger samples are recorded using CLK1 and all post-trigger samples using CLK2.

The controller can also be clocked using an external user supplied signal. The sampling clock is available to synchronize other controllers.

All controller parameters can be set from front panel switches and through CAMAC from a computer. These parameters can be stored in nonvolatile memory and automatically reloaded on power-up. Also on power-up, the controller sequences through a series of diagnostics and notifies the user if a problem is detected (see DIAGNOSTIC section).

#### Models 4012P/4032P

The 4012P and 4032 P are special versions of the 4012A and 4032A. The systems differ from the standard units in that:

- 1) There is a "LOCKOUT" signal which can force the controllers to always be in the LOCAL control mode and lockout the remote computer.

- 2) There are two signals which if received in the correct order will start the controller digitizing:

- a) "MASTER ARM"

- b) "MASTER ENABLED"

- 3) The controllers record the memory address of the first sample digitized in a non-volatile memory chip. After power-up this address is restored and data can be displayed/read from the battery backed-up memory modules.

- 4) The 5204 memory modules used in these systems have an input signal "WRITE LOCK" which prohibits the controllers from overwriting the memories.

An additional calibration data block is available only for the 4012:

A 128K sample section of memory can be reserved for calibration data. If enabled, the 4012 will display a total memory size which is 128K less than on the TRAQBUS as this memory is reserved for calibration data only. When the unit is in the acquisition calibration mode, "ACQ CAL", data is digitized as usual, however, after recording is complete the last 2048 samples of data for each channel are transferred to the reserved memory section (approximately 1/2 second is required to transfer data for each channel). The only time data is ever written into the reserved memory section is during this transfer time. The acquisition mode "ACQ DATA" is the standard mode. Data can be read from both the calibration and data sections of memory depending which acquisition mode is enabled. This feature requires a minimum memory size of 256K samples and can be enabled or disabled from the front panel (MCAL function) or by the computer.

The 4012P and 4032P users must be sure that "4012 P" (or "4032 P") has been saved in the non-volatile RAM. On power-up the unit checks this control setting and aborts the memory diagnostics if "4012 P" is set, otherwise the data will be rewritten. The firmware also checks for a valid control setting; detection of an invalid control word forces a default setting to the "4012 A" mode but no memory diagnostics.

### Model 4012 and Model 4032 Differences

The 4032 is an upgraded version of the 4012 and is able to read/write larger memory sizes. The 4012 is limited to 16 megasamples of storage while the 4032 is able to address 256 megasamples. The only functional differences are in the CAMAC control commands. (See Programming the Control Registers Section).

### System Diagnostics

Whenever the controller's microprocessor is reset, either by the front panel reset button or a CAMAC Z (or C) command a series of diagnostic tests are performed. Failure to pass any of these test indicates the system is not functional (refer to Diagnostic Test section).

### **SECTION 3**

### FRONT PANEL INDICATORS AND CONTROLS

### **Alphanumeric LED Indicators**

The controller has two alphanumeric LED displays which are controlled by two corresponding rotary switches. The **function** switch selects a control to be set and the **value** switch selects the control parameter to be used. As the **value** switch is incremented/decremented the new values are used by the internal processor to set control registers. Once sampling is initiated the values are locked-in and changing the switch values will only affect the next recording. If the controller is in remote mode only the local/remote control and the display channel can be changed. When the controller is initialized by a CAMAC clear (Z or C) or the front panel reset a series of diagnostic tests are performed (see diagnostic section). If any of these tests fail, a "**FAIL**" message will be displayed on the value LED with the corresponding test on the function LED. Failure to complete these tests indicates that the unit is not functional.

| Function | Value | Description                                                                                                                                                                                      |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACQ      | DATA  | The unit is enabled to take data in the standard recording mode.                                                                                                                                 |

|          | CAL   | The unit is enabled to take data for calibration recording. After calibration is complete the last 2048 samples for each channel are transferred to the reserved calibration memory. (4012 only) |

| CLKC     | NONE  | Both internal clocks(CLK1 & CLK2) and the external clock input are disabled.                                                                                                                     |

|          | EXT   | The external clock input is enabled and the internal clocks, CLK1 & CLK2, are disabled.                                                                                                          |

|          | INT   | The internal clocks (CLK1 & CLK2) are enabled and the external clock input is disabled.                                                                                                          |

| CKSW     | NONE  | Switching between CLK1 and CLK2 is disabled.                                                                                                                                                     |

|          | FTRG  | CLK1 is enabled when the SWI front panel input is TTL low. CLK2 is enabled when SWI is TTL high.                                                                                                 |

|          |       | □ NOTE                                                                                                                                                                                           |

|          |       | CLK1 is the normal sampling clock. When CLK2 is active the 16th bit of the data is set to 1.                                                                                                     |

|          | STRG  | CLK2 is enabled after receipt of a stop trigger. (All post-trigger samples are taken with CLK2)                                                                                                  |

| CLK1 | 5 MHz-10 Hz | Selects the sampling frequency for CLK1                                                          |

|------|-------------|--------------------------------------------------------------------------------------------------|

|      |             | <b>□</b> NOTE                                                                                    |

|      |             | Do not select a sampling speed greater than the maximum ADC conversion rate.                     |

| CLK2 | 5 MHz-10 Hz | Selects the sampling frequency for CLK2                                                          |

|      |             |                                                                                                  |

|      |             | □ NOTES                                                                                          |

|      |             | 1) Do not select a sampling speed greater than the maximum ADC conversion rate.                  |

|      |             | 2) Whenever CLK2 is active the 16th bit (MSB) of the data is set to 1. (see DATA FORMAT section) |

| Function | Value         | Description                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DISP     | 1NOC          | Displays recorded data from the selected channel through the "Display Out" front panel connector to an attached oscilloscope. NOC (number of active channels) is selected by the NOC control. The display is active only after sampling is complete and if there is no CAMAC readout. All data is displayed except when NOC = 1 which displays every other data sample. |

| INCR     | 1,10,100,1000 | Selects the increment/decrement value used by MSCH.                                                                                                                                                                                                                                                                                                                     |

| MSCH | 1              | Displays the memory/channel (record size) in 1k blocks. Changing the value switch will increment or decrement the memory/channel by the amount selected in INCR. The minimum memory/channel is 1024 samples and the maximum is determined by the following algorithm:  MSCH(MAX) = INTEGER(MSTO/NOC)  NOC = NUMBER OF ACTIVE CHANNELS  MSTO = TOTAL MEMORY SIZE |

|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                | ☑ EXAMPLE                                                                                                                                                                                                                                                                                                                                                       |

|      |                | MSTO = 256k : NOC = 6                                                                                                                                                                                                                                                                                                                                           |

|      |                | MSCH = INT(256k/6)                                                                                                                                                                                                                                                                                                                                              |

|      |                | = 42k                                                                                                                                                                                                                                                                                                                                                           |

|      |                | □ NOTE                                                                                                                                                                                                                                                                                                                                                          |

|      |                | The Total Memory Size (MSTO) Is                                                                                                                                                                                                                                                                                                                                 |

|      |                | Determined During The Power-Up Test Sequence.                                                                                                                                                                                                                                                                                                                   |

| MSTO | Not Adjustable | Displays the total memory size (1k blocks) which is determined during the power-up diagnostic test sequence.                                                                                                                                                                                                                                                    |

|      |                | □ NOTE                                                                                                                                                                                                                                                                                                                                                          |

|      |                | The 4012P will display 128K less memory for MSTO than actually present if enabled for calibration memory ("MCAL YES") since 128K is the required memory to store the calibration data.                                                                                                                                                                          |

| Function        | Value | Description                                                                                                                                                            |

|-----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE            | LOCL  | Front panel controls are enabled and computer control is locked-out.                                                                                                   |

|                 | RMOT  | Computer control is enabled and front panel controls are locked-out.                                                                                                   |

|                 |       |                                                                                                                                                                        |

|                 |       | ■ NOTE                                                                                                                                                                 |

|                 |       | The computer can override the LOCL control and change to RMOT. Also the front panel can override RMOT and change to LOCL. The display control can be set in RMOT mode. |

| 4012 or<br>4032 | A     | Sets control firmware to run 4012A or 4032A code.                                                                                                                      |

|                 | P     | Sets control firmware to run 4012P or 4032P code.                                                                                                                      |

| MCAL            | NO    | All TRAQ memory is used for data acquisition.  (required for 4032 & 4032P units)                                                                                       |

|                 | YES   | A 128K data block is reserved for calibration data.                                                                                                                    |

|                 |       | NOTE Only available for 4012 units.                                                                                                                                    |

| NOC  | 1,2,4,6<br>256 | Sets the number of active ADC channels.  NOC can be set from one to the total number of available ADC channels.  NOTE                                                                                                                                             |

|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                | Do not set NOC greater than the total number of available ADC channels.                                                                                                                                                                                           |

| PREV | xxxx           | Displays the current revision level of the microprocessor firmware. This message is only displayed after power-up diagnostics are completed.                                                                                                                      |

| PTS  | 0/8,1/8<br>8/8 | Sets the number of post-trigger samples in 1/8 intervals.  0/8: all data is recorded before the trigger.  1/8: 1/8 of the data is recorded after the trigger,  7/8 before.  4/8: 1/2 of the data will be recorded after the stop  trigger; 1/2 before the trigger |

|      |                | 8/8: all of the channel's data will be recorded after the stop trigger.                                                                                                                                                                                           |

| SAVE | [blank] or<br>DONE | Saves the control parameters in the non-volatile RAM memory. Turning the value switch one position forward or backwards causes the control parameters to be stored and the message "DONE" to be displayed. On power-up the unit will use these settings for the control registers. |

|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                    | If on power-up the non-volatile RAM containing the control settings has incorrect settings, the Controller will default to the following control values:                                                                                                                           |

|      |                    | ACQ : DAT                                                                                                                                                                                                                                                                          |

|      |                    | CLKC: INT                                                                                                                                                                                                                                                                          |

|      |                    | CKSW: NONE                                                                                                                                                                                                                                                                         |

|      |                    | CLK1: 100 KHz                                                                                                                                                                                                                                                                      |

|      |                    | CLK2: 100 KHz                                                                                                                                                                                                                                                                      |

|      |                    | MSCH : Full record size                                                                                                                                                                                                                                                            |

|      |                    | 4012 : A                                                                                                                                                                                                                                                                           |

|      |                    | MCAL : NO                                                                                                                                                                                                                                                                          |

|      |                    | MODE : LOCAL                                                                                                                                                                                                                                                                       |

|      |                    | NOC: 1                                                                                                                                                                                                                                                                             |

|      |                    | PTS: 8/8                                                                                                                                                                                                                                                                           |

### **Front Panel LED Indicators**

| Z   | Momentary LED. On for approximately 1/2 sec when the Controller is addressed by the CAMAC dataway. |

|-----|----------------------------------------------------------------------------------------------------|

| MST | Not Used                                                                                           |

| LOC | On when the controller is in local mode off when in remote mode. |

|-----|------------------------------------------------------------------|

| CVT | On when the controller is recording data.                        |

### **Front Panel Switch Controls**

| START/<br>STOP | Two position momentary switch. The "START" position starts sampling, and the "STOP" position generates a stop trigger (equivalent to the front panel trigger input). The controller will initiate or reinstate sampling any time "START" sampling is depressed. After "STOP" sampling is depressed, no further stop triggers will be acknowledged (until sampling is restarted.) |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | □ NOTE                                                                                                                                                                                                                                                                                                                                                                           |

|                | This switch is not active in the remote mode.                                                                                                                                                                                                                                                                                                                                    |

| RST            | Resets the microprocessor and initiates the power-up diagnostic sequences.                                                                                                                                                                                                                                                                                                       |

### **Front Panel Signals**

(The following signals use LEMO, single pin, coax connectors)

| DISPLAY<br>OUT | Analog output, approximately ±10 Volts max into 1 Kohm minimum. Displays a reconstructed 12 bit waveform of the recorded data. ADC data is shifted by 2 LSBS (divided by 4) before displaying. Data from 14-bit converters only displays the upper 12 bits; data from 12 bit converters displays only the upper 10 bits. The full scale display ranges for these ADCs are: |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                | 1) 14 bit converters:                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                | +10V = ADC + full scale.                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                | -10V = ADC -full scale.                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                | 2) 12 bit converters :                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                | +2.5V = ADC + full scale.                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                | -2.5V = ADC -full scale.                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                | The channel to be displayed is controlled by the front panel switches or CAMAC. At the beginning of each sweep there is approximately a 100 µsec. dead time during which no data is displayed. When there is only one active channel (NOC=1) every other data point is displayed. For all other cases all of the data is displayed.                                        |  |  |

| SYNCH          | TTL signal out, into 1 Kohm minimum. The positive edge is synchronized to the beginning of the display sweep.                                                                                                                                                                                                                                                              |  |  |

| TRIG           | Stop trigger which initiates post-trigger sampling, positive edge sensitive. After receipt of the first positive edge all further transitions are ignored until sampling is re-initiated. Optically isolated, protected to $\pm$ 300 Volts, requires approximately 1 ma. of current at 3 Volts to activate.                                                                |  |  |

| CLKIN   | External clock which initiates sampling of all active ADC channels, positive edge sensitive, TTL, 1 Kohm impedance. The clock frequency may change arbitrarily but the user must insure glitch free transitions. |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT  | TTL signal at the same frequency as the selected clock frequency (internal or external). Will drive one 50 ohm load.                                                                                             |

| CLKSWI  | TTL signal which causes the sampling rate to change from CLK1 to CLK2 if enabled. 1 Kohm impedance, TTL low enables CLK1, TTL high enables CLK2.                                                                 |

| BUS REG | Not Used                                                                                                                                                                                                         |

### Model 4012P and Model 4032P Rear Panel Signals

(The following signals use LEMO, single pin, coax connectors)

| ARM               | Optically isolated, TTL signal, protected to ± 300 Volts. A high TTL level must be detected by the controller followed by MASTER ENABLE before digitizing will be initiated. There should be at least a 100 µsec. time delay between assertion of MASTER ARM and MASTER ENABLE. Requires approximately 1 mA to activate at 3 Volts. |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MASTER<br>ENABLE  | Optically isolated, TTL signal, protected to ± 300 Volts. A high TTL level must be detected after assertion of MASTER ARM before digitizing will be initiated. Requires approximately 1 mA to activate at 3 Volts.                                                                                                                  |

| MASTER<br>LOCKOUT | Optically isolated, TTL signal, protected to ±300 Volts. A low TTL (or absence of) signal forces the controller into the local control mode. A high TTL level allows the remote control level to be activated. Requires approximately 1 mA to activate at 3 Volts.                                                                  |

### Front and Rear Panel Flat Cable Bus Connectors

| TRAQBUS | 50-pin connector, TTL signals. 32 bits of multiplexed data/address and 12 control signals. Transfers data from the TRAQ controller to |

|---------|---------------------------------------------------------------------------------------------------------------------------------------|

|         | memory modules or slave controllers.                                                                                                  |

| ADCBUS  | Rear panel, 40 pin, connector, TTL levels. Transfers data from signal conversion units to the TRAQ controller.                        |

## Section 4 PROGRAMMING THE 4012/4032 CONTROL REGISTERS

### **CAMAC Control**

The following list describes the response of the 4012/4032 to the CAMAC dataway commands. All commands require N(station number) and return X=1 and Q=1 unless stated.

| 000000000000000000000000000000000000000 |                                                                                                                                                                                                                                                                           |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F(0)*A(0)                               | Read data from the requested command register (see READING the 4012 CONTROL REGISTERS).                                                                                                                                                                                   |

| F(2)*A(0)                               | Read data for the selected channel number. Each F(2)*A(0) command reads one data sample and increments TRAQ memory to read the next sample. Data transfer rates up to the maximum CAMAC rates. Before data readout can proceed the correct CAMAC commands must be issued. |

| F(3)*A(0)                               | Read module ID. ("4012" or "4032")                                                                                                                                                                                                                                        |

| F(8)*A(0)                               | Returns Q=1 if the internal LAM is on, regardless if the LAM was enabled by F(26)*A(0) or not.                                                                                                                                                                            |

| F(9)*A(0)                               | Start sampling. (Only in remote control mode). There is, approximately, a 500 µsec delay from receipt of the F(9)*A(0) command to the actual start of sampling.                                                                                                           |

| F(10)*A(0)                              | Reset LAM Turns the internal and external(CAMAC dataway) LAM off.                                                                                                                                                                                                         |

| F(17)*A(0)                              | Selects a command register for reading/writing.(see WRITING the 4012 CONTROL REGISTERS, this section).                                                                                                                                                                    |

| F(24)*A(0)                              | Disables the LAM (look-at-me) signal from the CAMAC dataway. However the internal status can be monitored by the F(8)*A(0) command (Q=1 returned if the internal LAM is on).                                                                                              |

| F(25)*A(0) | Stop sampling (equivalent to then front panel" stop trigger").                                                 |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|            | □ NOTE                                                                                                         |  |  |  |  |  |

|            | The controller will respond to this command in both local and remote control modes.                            |  |  |  |  |  |

| F(26)*A(0) | Enables the internal LAM (look-at-me) signal onto the CAMAC dataway.                                           |  |  |  |  |  |

| Z/C        | Initializes the controller, resets the microprocessor, and starts power-up diagnostics.                        |  |  |  |  |  |

|            | □ NOTE                                                                                                         |  |  |  |  |  |

|            | The controller will respond to this command in both local and remote control modes.                            |  |  |  |  |  |

| LAM        | LAM, look-at-me is generated when sampling is complete and when data is ready for readout (if in remote mode.) |  |  |  |  |  |

Control registers are programmed using the F(17)\*A(0) command and W16-W1 CAMAC write lines. The W16-W13 lines address the control registers and W12-W1 contain the data to be loaded.

If the 4012/4032 controller is in the local control mode, only the local/remote (see 8 below) register can be changed. After commanding the unit to the remote mode all registers can be changed. As new values are programmed into the controller, the new values/functions are displayed on the front panel LEDs.

Since all command registers are read/written through the microprocessor there is a response time of approximately several hundred microseconds. The controller will respond with a Q=1 on F17\*A(0) [F(0)\*A(0)] if the unit is ready to accept (read) the command (data), otherwise a Q=0 is generated. When reading the control registers, which requires F(17)\*A(0) to be followed by F(0)\*A(0), both commands must be executed before the next F(17)\*A(0) can be generated. It is recommended that a minimum of 500

| usec delay be inserted between all commands which address the 4012 control reThis applies for F (17), F(0), and F(9) commands. | egisters. |

|--------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

|                                                                                                                                |           |

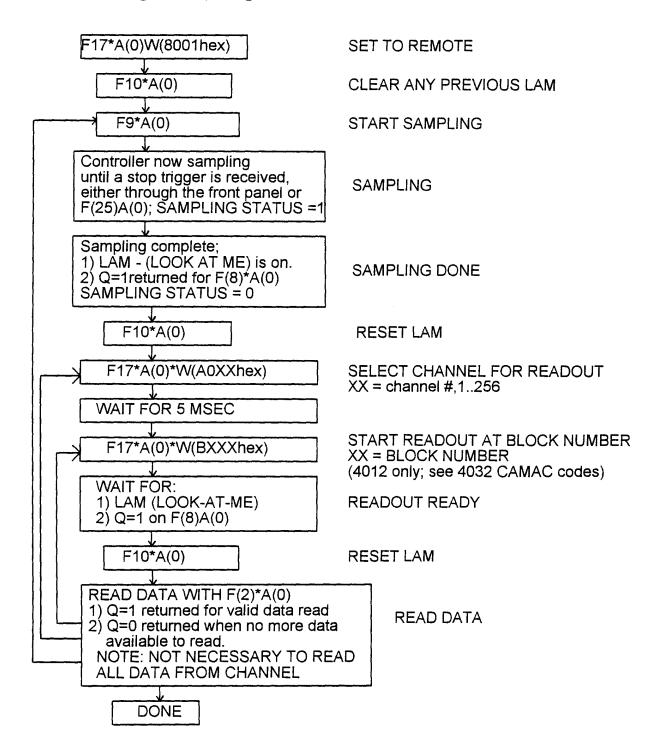

### Controlling Sampling and Data Readout From CAMAC

# Section 5 Writing Common 4012/4032 Control Registers

F(17)\*A(0)\*[(W16..W13 = Command) (W12..W1 = Data)]

**M** NOTE

COMMAND = upper 4 write bits (W16..W13) in hex

DATA = lower 12 write bits (W12..W1) in decimal

| Function                               | Command | Data             | Description                                                                                                                                                                               |

|----------------------------------------|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SET<br>NUMBER<br>OF ACTIVE<br>CHANNELS | 1       | 1 , 2,<br>4, 256 | 1=1 active ch. 2=2 active ch. : 256= 256 active ch.                                                                                                                                       |

|                                        |         |                  | Do not program more active channels than the total number of ADC channels, otherwise the controller will always be waiting for a "conversion complete" signal from the erroneous channels |

| SET NUMBER OF POST- TRIGGER FRACTION SAMPLES | 0,1,2,8 | <ul> <li>0 = No post-trigger samples -sampling, stops immediately after receipt of the "stop trigger".</li> <li>1 = 1/8 of the channels memory is sampled after receipt of "stop trigger"</li> <li>2 = 2/8 of the channels memory is</li> <li>3 = 3/8.</li> </ul> |

|----------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                              |         | 8 = all data is recorded after receipt of "stop<br>trigger"                                                                                                                                                                                                       |

| OTTO OT TES           |   |        |                                                                                                                                        |

|-----------------------|---|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| SET CLK1<br>FREQUENCY | 4 | 0,1,17 | 0 = 5  MHz  1 = 2  MHz  2 = 1  MHz                                                                                                     |

| T.                    |   |        | 3 = 500 Khz 4 = 200 Khz 5 = 100 Khz                                                                                                    |

|                       |   |        | 6 = 50 Khz 7 = 20 Khz 8 = 10 Khz                                                                                                       |

|                       |   |        | 9 = 5 Khz 10 = 2 Khz 11 = 1 KHz                                                                                                        |

|                       |   |        | 12 = 500 Hz 13 = 200 Hz 14 = 100 Hz:                                                                                                   |

|                       |   |        | 15 = 50 Hz 16 = 20 Hz 17 = 10 Hz                                                                                                       |

|                       |   |        |                                                                                                                                        |

|                       |   |        | □ NOTES                                                                                                                                |

|                       |   |        | <ol> <li>If using FTRG and FTRIG is TTL high or a<br/>"stop trg" has been detected using STRG<br/>then CLK2 will be active.</li> </ol> |

|                       |   |        |                                                                                                                                        |

|                       |   |        | <ol> <li>Do not set CLK1 frequencies higher than<br/>the maximum conversion rate of the ADC<br/>modules.</li> </ol>                    |

| SET CLK2<br>FREQUENCY             | 5 | 0,1,17 | Same as CLK1                                                                                                                                                                       |

|-----------------------------------|---|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •                                 |   |        | □ NOTES                                                                                                                                                                            |

|                                   |   |        | The W16 data bit is set to 1 (if enabled) for data sampled when CLK2 is active- see DATA FORMAT section                                                                            |

|                                   |   |        | 2. Do not set CLK2 frequencies higher than the maximum conversion rate of the ADC modules or the maximum transfer rate of the bus                                                  |

| SET CLOCK<br>SWITCHING<br>CONTROL | 6 | 0,1,2  | 0 = No switching from clock 1 to clock 2  1 = Switch from clock 1 to clock 2 when front panel input signal "CLK SWI" is high [FTRG]  2 = Switch from clock 1 to clock 2 when "STOP |

| SET CLOCK<br>CONTROL              | 7 | 0,1,2  | TRG" received [STRG]  0 = Both external and internal clocks are disabled.  1 = External clock (front panel input signal) is enabled; internal clocks are disabled.                 |

|                                   |   |        | 2 = Internal clocks are enabled and the external clock input is disabled.                                                                                                          |

| SET LOCAL REMOTE CONTROL           | 8 | 0,1                     | 0 = Set to local control mode  1 = Set to remote control mode  NOTE  If the controller is in the local control mode the computer may override and set to remote mode. This is required in order to set any other control registers or read data. Also, the LOCAL/REMOTE can be changed from the front panel                                                                                                                                   |

|------------------------------------|---|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SET THE D/A OUTPUT DISPLAY CHANNEL | 9 | 1, 2, 3,<br>4,5,<br>256 | [Data(decimal):]  1 = display channel 1  2 = display channel 2   256 = display channel 256  Displays data from the selected channel, (see "DISPLAY OUT," SIGNALS section).  Do not program a display channel greater then the number of active channels. If the controller is in the data readout mode then the display can be reactivated by reading out the last block of data in a channel until Q=0 is returned on the 1025th read cycle. |

| SELECT A<br>CHANNEL<br>FOR<br>READOUT<br>1,2,3,4,5256 | A | 1, 2, 3,<br>4,5,<br>256,<br>512 | [Data(decimal):]  1 : Select channel 1 for readout  2 : Select channel 2 for readout  .  256 : Select channel 256 for readout                                                                                                                    |

|-------------------------------------------------------|---|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                       |   |                                 | 512 : DATA STREAMOUT 513 : DATA STREAMOUT WITH AUTO RESTART 514 : MEMORY DUMP                                                                                                                                                                    |

|                                                       |   |                                 | This command must be executed at least once before data readout can begin. It is not necessary to re-issue the command if the channel readout number is not changed. Do not program a channel number greater than the active number of channels. |

#### Data Streamout

If the channel number = 512 then the controller will immediately enter the data streamout mode. Data is ready to read approximately 1.5 msec after issuing the command. This mode is useful for users who wish to read all TRAQ data without the overhead of setting up each channel and starting address (app. 3 msec). This mode reads data out in the following the following sequence:

Channel(NOC), Sample(1)

Channel(NOC-1), Sample(1)

Channel(1), Sample(1)

Channel(NOC), Sample(2)

Channel(NOC-1), Sample(2)

Channel(1), Sample(2),

etc.

#### Data Streamout with Auto-restart

This mode allows the controller to continuously sample/read/sample... data. After the controller is commanded into this mode it will automatically enter the data readout mode after sampling is complete. The data is read in the same format as above. After the last data sample + 1 is read the Controller will automatically restart sampling. This mode is enabled until the channel readout number is changed from 513.

**Data Dump:** The entire memory is readout starting at address 0.