# 640 DIGITAL COMPUTING SYSTEM INFORMATION MANUAL

# CONTENTS

| SECTION 1 | EAI <u>640</u> SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-1                                                                                                                                                                                    |

|           | 640 System Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-1                                                                                                                                                                                    |

|           | Characteristics of the Basic 640 Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-2                                                                                                                                                                                    |

|           | EAI 640 Central Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-7                                                                                                                                                                                    |

|           | Arithmetic Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-7                                                                                                                                                                                    |

|           | Control Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-9<br>1-10                                                                                                                                                                            |

|           | Memory Section<br>EAI 640 Address Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-10                                                                                                                                                                                   |

|           | Storage Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-11                                                                                                                                                                                   |

|           | Storage Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-11                                                                                                                                                                                   |

|           | Addressing Concept of the 640 Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-12                                                                                                                                                                                   |

|           | EAI 640 Interrupt System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-15                                                                                                                                                                                   |

|           | General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-15                                                                                                                                                                                   |

|           | Master Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-17                                                                                                                                                                                   |

|           | Program Status Word (K Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 - 17                                                                                                                                                                                 |

|           | Preservation of Registers During Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-17                                                                                                                                                                                   |

|           | Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-17                                                                                                                                                                                   |

|           | Internal Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-18                                                                                                                                                                                   |

|           | External Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-18                                                                                                                                                                                   |

|           | Absolute Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-19                                                                                                                                                                                   |

|           | Pointers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-19<br>1-19                                                                                                                                                                           |

|           | Description of Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-19                                                                                                                                                                                   |

|           | EAI 640 Memory Protect System<br>EAI 640 Input/Output System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-21<br>1-23                                                                                                                                                                           |

|           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-23<br>1-23                                                                                                                                                                           |

|           | Single Word Mode Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-23                                                                                                                                                                                   |

|           | Record Mode Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-24                                                                                                                                                                                   |

|           | Direct Memory Access Channel (DMAC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-25                                                                                                                                                                                   |

|           | EAI 640 Instruction Repertoire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-29                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-25                                                                                                                                                                                   |

| SECTION 2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-25                                                                                                                                                                                   |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-1                                                                                                                                                                                    |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                        |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-1                                                                                                                                                                                    |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-1<br>2-1<br>2-2<br>2-2                                                                                                                                                               |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing<br>Control Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-1<br>2-1<br>2-2<br>2-2<br>2-3                                                                                                                                                        |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing<br>Control Word Format<br>Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1<br>2-1<br>2-2<br>2-2<br>2-3<br>2-3                                                                                                                                                 |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing<br>Control Word Format<br>Software<br>Physical Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-1<br>2-1<br>2-2<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3                                                                                                                                   |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing<br>Control Word Format<br>Software<br>Physical Requirements<br>640/260 Data Disc Storage System.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-1<br>2-1<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3<br>2-5                                                                                                                                   |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing<br>Control Word Format<br>Software<br>Physical Requirements<br>640/260 Data Disc Storage System<br>Teletype Writer Station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-1<br>2-1<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3<br>2-5<br>2-7                                                                                                                            |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing<br>Control Word Format<br>Software<br>Physical Requirements<br>640/260 Data Disc Storage System<br>Teletype Writer Station<br>Paper Tape Station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-1<br>2-1<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3<br>2-5<br>2-7<br>2-9                                                                                                                     |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing<br>Control Word Format<br>Software<br>Physical Requirements<br>640/260 Data Disc Storage System<br>Teletype Writer Station<br>Paper Tape Station<br>640/520 Card Reader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-1 2-1 2-2 2-3 2-3 2-3 2-3 2-5 2-7 2-9 2-11                                                                                                                                           |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing<br>Control Word Format<br>Software<br>Physical Requirements<br>640/260 Data Disc Storage System<br>Teletype Writer Station<br>Paper Tape Station<br>640/520 Card Reader<br>640/610 Line Printer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-1<br>2-1<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3<br>2-5<br>2-7<br>2-9                                                                                                                     |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing<br>Control Word Format<br>Software<br>Physical Requirements<br>640/260 Data Disc Storage System<br>Teletype Writer Station<br>Paper Tape Station<br>640/520 Card Reader<br>640/610 Line Printer<br>640/720 Magnetic Tape Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-1 2-1 2-2 2-3 2-3 2-3 2-3 2-5 2-7 2-9 2-11                                                                                                                                           |

| SECTION 2 | EAI 640 PERIPHERALS DESCRIPTION<br>Introduction<br>640/960 Floating Point Processor<br>Data Format<br>Commands and Timing<br>Control Word Format<br>Software<br>Physical Requirements<br>640/260 Data Disc Storage System<br>Teletype Writer Station<br>Paper Tape Station<br>640/520 Card Reader<br>640/610 Line Printer<br>640/720 Magnetic Tape Controller<br>and Transport                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\begin{array}{c} 2-1\\ 2-1\\ 2-2\\ 2-2\\ 2-3\\ 2-3\\ 2-3\\ 2-3\\ 2-5\\ 2-7\\ 2-9\\ 2-11\\ 2-13\end{array}$                                                                            |

|           | EAI 640 PERIPHERALS DESCRIPTION         Introduction         640/960 Floating Point Processor         Data Format         Commands and Timing         Control Word Format         Software         Physical Requirements         640/260 Data Disc Storage System         Teletype Writer Station         Paper Tape Station         640/520 Card Reader         640/610 Line Printer         640/720 Magnetic Tape Controller         and Transport                                                                                                                                                                                                                                                                                                                                                                                            | 2-1 2-1 2-2 2-3 2-3 2-3 2-3 2-5 2-7 2-9 2-11 2-13 2-15                                                                                                                                 |

|           | EAI 640 PERIPHERALS DESCRIPTION         Introduction         640/960 Floating Point Processor         Data Format         Commands and Timing         Control Word Format         Software         Physical Requirements         640/260 Data Disc Storage System         Teletype Writer Station         Paper Tape Station         640/520 Card Reader         640/610 Line Printer         640/720 Magnetic Tape Controller         and Transport         EAI 640 System Configurator                                                                                                                                                                                                                                                                                                                                                        | $\begin{array}{c} 2-1\\ 2-1\\ 2-2\\ 2-2\\ 2-3\\ 2-3\\ 2-3\\ 2-3\\ 2-5\\ 2-7\\ 2-9\\ 2-11\\ 2-13\\ 2-13\\ 2-15\\ 2-17\end{array}$                                                       |

|           | EAI 640 PERIPHERALS DESCRIPTION         Introduction         640/960 Floating Point Processor         Data Format         Commands and Timing         Control Word Format         Software         Physical Requirements         640/260 Data Disc Storage System         Teletype Writer Station         Paper Tape Station         640/520 Card Reader         640/610 Line Printer         640/720 Magnetic Tape Controller         and Transport         EAI 640 System Configurator                                                                                                                                                                                                                                                                                                                                                        | 2-1 2-1 2-2 2-3 2-3 2-3 2-3 2-5 2-7 2-9 2-11 2-13 2-15 2-17 3-1                                                                                                                        |

|           | EAI 640 PERIPHERALS DESCRIPTION         Introduction         640/960 Floating Point Processor         Data Format         Commands and Timing         Control Word Format         Software         Physical Requirements         640/260 Data Disc Storage System         Teletype Writer Station         Paper Tape Station         640/520 Card Reader         640/610 Line Printer         640/720 Magnetic Tape Controller         and Transport         EAI 640 System Configurator         EAI 640 System SOFTWARE         Symbolic Assembler         ASA Standard FORTRAN                                                                                                                                                                                                                                                                | $\begin{array}{c} 2-1\\ 2-1\\ 2-2\\ 2-2\\ 2-3\\ 2-3\\ 2-3\\ 2-3\\ 2-5\\ 2-7\\ 2-9\\ 2-11\\ 2-13\\ 2-13\\ 2-15\\ 2-17\end{array}$                                                       |

|           | EAI 640 PERIPHERALS DESCRIPTION         Introduction         640/960 Floating Point Processor         Data Format         Commands and Timing         Control Word Format         Software         Physical Requirements         640/260 Data Disc Storage System         Teletype Writer Station         Paper Tape Station         640/520 Card Reader         640/610 Line Printer         640/720 Magnetic Tape Controller         and Transport         EAI 640 System Configurator         EAI 640 SYSTEM SOFTWARE         Symbolic Assembler         ASA Standard FORTRAN         Operations Interpreter                                                                                                                                                                                                                                 | 2-1 2-1 2-2 2-2 2-3 2-3 2-3 2-3 2-5 2-7 2-9 2-11 2-13 2-15 2-17 3-1 3-2                                                                                                                |

|           | EAI 640 PERIPHERALS DESCRIPTION         Introduction         640/960 Floating Point Processor         Data Format         Commands and Timing         Control Word Format         Software         Physical Requirements         640/260 Data Disc Storage System         Teletype Writer Station         Paper Tape Station         640/520 Card Reader         640/610 Line Printer         640/720 Magnetic Tape Controller         and Transport         EAI 640 System Configurator         EAI 640 System SOFTWARE         Symbolic Assembler         ASA Standard FORTRAN                                                                                                                                                                                                                                                                | 2-1 $2-1$ $2-2$ $2-2$ $2-3$ $2-3$ $2-3$ $2-5$ $2-7$ $2-9$ $2-11$ $2-13$ $2-15$ $2-17$ $3-1$ $3-2$ $3-4$                                                                                |

|           | EAI 640 PERIPHERALS DESCRIPTION         Introduction         640/960 Floating Point Processor         Data Format         Commands and Timing         Control Word Format         Software         Physical Requirements         640/260 Data Disc Storage System         Teletype Writer Station         Paper Tape Station         640/520 Card Reader         640/610 Line Printer         640/720 Magnetic Tape Controller         and Transport         EAI 640 System Configurator         EAI 640 System Configurator         Guide Assembler         ASA Standard FORTRAN         Operations Interpreter         640 Symbolic Text Editor         Basic Monitor (Librarian)         System Subroutine Library                                                                                                                           | 2-1 $2-1$ $2-2$ $2-2$ $2-3$ $2-3$ $2-3$ $2-5$ $2-7$ $2-9$ $2-11$ $2-13$ $2-15$ $2-17$ $3-1$ $3-2$ $3-4$ $3-5$                                                                          |

|           | EAI 640 PERIPHERALS DESCRIPTION         Introduction         640/960 Floating Point Processor         Data Format         Commands and Timing         Control Word Format         Software         Physical Requirements         640/260 Data Disc Storage System         Teletype Writer Station         Paper Tape Station         640/520 Card Reader         640/610 Line Printer         640/720 Magnetic Tape Controller         and Transport         EAI 640 System Configurator         EAI 640 System Configurator         G40 System Configurator         EAI 640 System Configurator         Symbolic Assembler         ASA Standard FORTRAN         Operations Interpreter         640 Symbolic Text Editor         Basic Monitor (Librarian)         System Subroutine Library         Digital Debug                              | $\begin{array}{c} 2-1\\ 2-1\\ 2-2\\ 2-2\\ 2-3\\ 2-3\\ 2-3\\ 2-3\\ 2-3\\ 2-5\\ 2-7\\ 2-9\\ 2-11\\ 2-13\\ 2-13\\ 2-15\\ 2-17\\ 3-1\\ 3-2\\ 3-4\\ 3-5\\ 3-5\\ 3-5\\ 3-6\\ 3-7\end{array}$ |

|           | EAI 640 PERIPHERALS DESCRIPTION         Introduction         640/960 Floating Point Processor         Data Format         Commands and Timing         Control Word Format         Software         Physical Requirements         640/260 Data Disc Storage System         Teletype Writer Station         Paper Tape Station         640/520 Card Reader         640/610 Line Printer         640/720 Magnetic Tape Controller         and Transport         EAI 640 System Configurator         EAI 640 System Configurator         EAI 640 System Configurator         G40 System Configurator         Symbolic Assembler         ASA Standard FORTRAN         Operations Interpreter         640 Symbolic Text Editor         Basic Monitor (Librarian)         System Subroutine Library         Digital Debug         Hardware Diagnostics | $\begin{array}{c} 2-1\\ 2-1\\ 2-2\\ 2-2\\ 2-3\\ 2-3\\ 2-3\\ 2-3\\ 2-5\\ 2-7\\ 2-9\\ 2-11\\ 2-13\\ 2-13\\ 2-15\\ 2-17\\ 3-1\\ 3-2\\ 3-4\\ 3-5\\ 3-5\\ 3-5\\ 3-6\\ 3-7\\ 3-8\end{array}$ |

|           | EAI 640 PERIPHERALS DESCRIPTION         Introduction         640/960 Floating Point Processor         Data Format         Commands and Timing         Control Word Format         Software         Physical Requirements         640/260 Data Disc Storage System         Teletype Writer Station         Paper Tape Station         640/520 Card Reader         640/610 Line Printer         640/720 Magnetic Tape Controller         and Transport         EAI 640 System Configurator         EAI 640 System Configurator         G40 System Configurator         EAI 640 System Configurator         Symbolic Assembler         ASA Standard FORTRAN         Operations Interpreter         640 Symbolic Text Editor         Basic Monitor (Librarian)         System Subroutine Library         Digital Debug                              | $\begin{array}{c} 2-1\\ 2-1\\ 2-2\\ 2-2\\ 2-3\\ 2-3\\ 2-3\\ 2-3\\ 2-3\\ 2-5\\ 2-7\\ 2-9\\ 2-11\\ 2-13\\ 2-13\\ 2-15\\ 2-17\\ 3-1\\ 3-2\\ 3-4\\ 3-5\\ 3-5\\ 3-5\\ 3-6\\ 3-7\end{array}$ |

Page

З

# EAI <u>640</u> SYSTEM

EAI <u>640</u> Digital Computing System

#### EAI 640 SYSTEM

#### INTRODUCTION

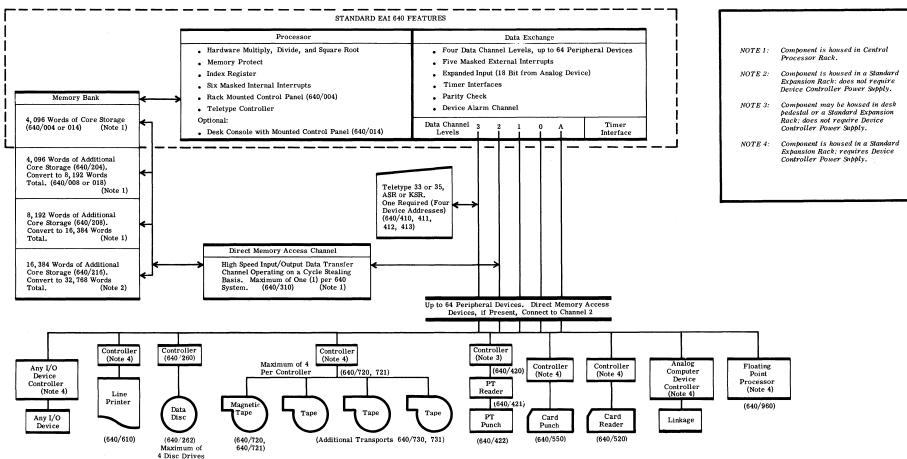

The EAI <u>640</u> Digital Computing System provides the user with an outstanding, general purpose, computing capability for handling a wide range of scientific applications. It includes flexible input/output and interrupt features that make it particularly useful in combined hybrid and special systems for simulation, hybrid computation, on-line monitoring/control and other uses.

The EAI <u>640</u> is a parallel, binary computer that operates with a fixed length 16 bit instruction and data word. It has a protected core memory with a maximum storage capacity of 32,768 words. Each word in memory has a protect bit and violations are immediately recognized through interrupt procedures in the computer.

The EAI  $\underline{640}$  offers an extensive list of instructions, multi-level interrupt capability and high speed input/output operations for communication with up to 64 peripheral devices.

The EAI <u>640</u> System is of modular design. Memory can be expanded from the basic 8K to 16 or 32 K. The basic EAI <u>640</u> contains interfaces for connection to interval timers. A Direct Memory Access Channel can be added to allow high speed input/output interleaved with computation on a cycle stealing basis. Advanced integrated circuitry makes the EAI <u>640</u> a member of the third generation computer family combining reliability with high speed logic.

#### 640 SYSTEM SUMMARY

- .... Stored program, general purpose digital computer

- .... Monolithic integrated circuitry

- .... 64 Instructions including:

- Add/Subtract

- Multiple precision hardware features for Add/Subtract

- Multiply/Divide Square Root

- Logical

- Inter-Register Exchanges

- **Condition Tests**

- .... Fixed word length of 16 data or instruction bits

- .... 16-bit Storage Word plus a memory Protect bit

- .... Magnetic Core Storage

- 1.65 Microseconds cycle time

- Basic Size 8,192 words

- Expandable to 16, 384 or 32, 768 words

- .... Multi-level Indirect Addressing

- .... Two's Complement Binary Arithmetic

- .... Index Registers

One Hardware register

An indefinite number of memory words can be used as index counters.

- .... 7 Internal Interrupts and 64 External Interrupts

- .... Input/Output

- Single Word Mode

- Record Mode

Direct Memory Access Channel (Optional)

.... Four Interval Timer Interfaces

#### CHARACTERISTICS OF THE BASIC 640 COMPUTER

#### **Arithmetic Operations**

The EAI  $\underline{640}$  performs all arithmetic operations using two's complement binary arithmetic.

ADD/SUBTRACT OPERATIONS

Addition and Subtraction can be performed in either single or multiple precision format. When the multiple precision bit is on, the carry/bor-row bit automatically provides a carry or a borrow when operating on the next higher precision word. When a multiple precision bit is off, single precision arithmetic is performed.

#### MULTIPLY/DIVIDE OPERATIONS

A Multiplicand contained in the Accumulator is multiplied by the multiplier as specified by the effective address. The resulting product is double length and is contained in the Accumulator and the Accumulator Extension (Q Register). The most significant portion (with sign) is in the Accumulator, the least significant portion is in the Q register. In the Divide operation, the dividend contained in the Accumulator and the Accumulator Extension is divided by the divisor contained in the memory location specified by the effective address. After division, the quotient with sign is contained in the Accumulator and the remainder is in the Accumulator Extension.

#### **Basic Computer**

The basic EAI  $\underline{640}$  Computer System is available with 8,192 words of core storage. The basic 640 Computer with 8K of memory and an upright console is the 640/008 and the same computer with a desk mounted operator console is the 640/018.

#### MEMORY EXPANSIONS

The 640/008 and 640/018 can be expanded to 16K in the field with the 640/208 Memory Conversion Unit. In addition, the 640/216 allows field modification of a 16K computer system to the full 32K version.

#### Memory Data and Address

A 16-bit Memory Data Register (M) holds data written into, or read out of core memory. The Memory Address Register (S) holds the address specifying where a word is to be read from or written into core storage.

#### **Indexing Operations**

#### HARDWARE INDEX REGISTER

The EAI  $\underline{640}$  has an Index Register (X) for high speed address modification without increasing instruction execution time. The X Register includes 15 address bits and a post-index indirect bit. This post-index indirect bit specifies whether the calculated address is to be the effective address or will result in a further indirect address. The Index Register can be transferred directly to or from memory without affecting the Accumulator. Increment or decrement of the Index Register followed by a Skip is performed in one instruction. 1

#### MEMORY COUNTERS

The EAI  $\underline{640}$  allows counting operations with the content of any memory location. With one instruction, a memory location can be incremented and tested. This capability allows the programmer an unlimited number of counters which can be serviced and tested with one instruction each.

#### **Memory Protection**

Each core memory location in the EAI  $\underline{640}$  Computer has a protect bit. This bit can be set or reset under program control only if the protect switch on the console is in the ON position. Violations of the protect system generate an interrupt and the contents of the memory location involved in the violation are not changed.

#### I/O System

The EAI <u>640</u> Computer can handle input and output in two modes. The single word mode transfers one word at a time into or out of the Accumulator. In the Record Mode, consecutive memory locations are automatically accessed for input or output. Block transfers can be made easily by specifying a starting and the final word address. After completion of the record transfer, a terminating address is available which can be examined against the last word address which has been specified. The extensive interrupt capabilities of the 640 allows I/O operations to proceed without constant need for status testing of the peripheral devices.

#### **Bootstrap Operation**

After clearing the computer (setting the hardware registers and memory to zero), the Execute Run switch will cause a bootstrap program to be read from the teletype paper tape reader which, after loading itself, will turn control over to the program which was loaded. This hardware feature allows the user to get off from a dead start with a minimum of inconvenience and loss of time.

#### Direct Memory Access Channel (640/310)

The basic EAI <u>640</u> Computer can expand its input/output capabilities through the addition of an optional Direct Memory Access Channel. Direct memory access operates on a cycle stealing basis which allows computation to proceed simultaneously with buffered input/output operations.

#### EAI <u>640</u> CENTRAL PROCESSOR

The EAI <u>640</u> Computer performs all calculations and processes data in a parallel, binary mode through the execution of individual instructions. Both instructions and data are stored in the magnetic core storage of the 640 Computer system. The 640 Computer is divided functionally into three sections, arithmetic, control, and memory.

#### **ARITHMETIC SECTION**

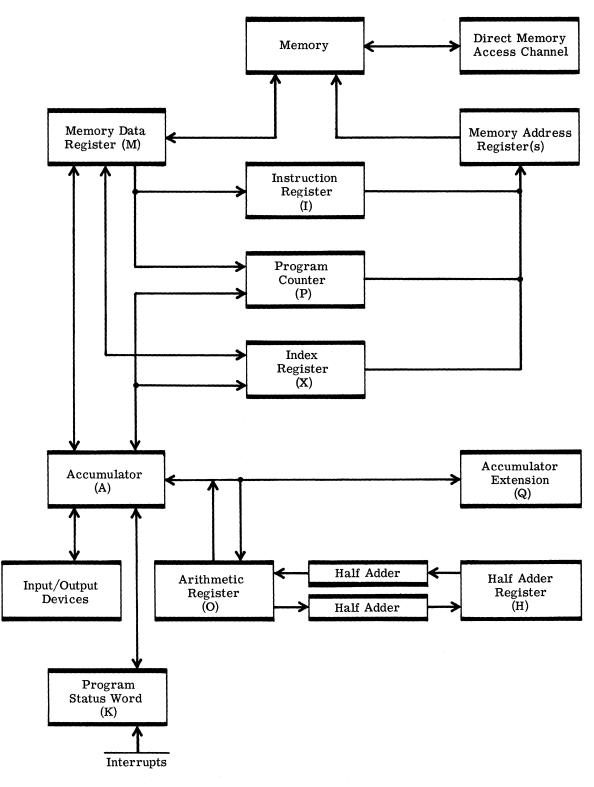

The Arithmetic Section of the EAI <u>640</u> Computer performs the arithmetic and logical operations necessary for execution of instructions. This section has several operational registers. Figure 1 shows a generalized logic block diagram of the 640 Computer. It should be emphasized that not all registers shown on this diagram are available to the programmer for direct operations. For example, the Half-Add Register (H) is necessary for proper operation of the Arithmetic Section, but cannot be directly manipulated by any instruction in the repertoire of the 640 Computer.

#### Accumulator (A Register):

The Accumulator is a 16-bit register used in arithmetic, logical and input/output operations.

#### Accumulator Extension (Q Register):

The Accumulator Extension is a 16-bit register used in double shifting operations,' multiply, divide, square root and record mode input/output operations.

#### Arithmetic Register (O Register):

The Arithmetic Register is a 16-bit register used in the execution of certain instructions. It is not available to the programmer, except for console display and manipulation.

#### Half-Adder (H Register):

This 16-bit register is used in the execution of certain instructions but is not available to the programmer for direct manipulation or display.

Figure 1. Block Diagram - EAI 640 Computer

#### **Program Counter (P Register):**

The Program Counter is a 15-bit register containing the memory address of the next instruction to be executed. After the instruction to be executed is placed in the Instruction Register the P register is incremented by one. The P register may be further changed by the instruction being executed. The P register has 15 bits and can generate addresses from 00000 to 32,767 which is the maximum memory capacity of the 640 Computer.

#### Index Register (X Register):

This 16-bit register is used in indexing operations. The index value can be positive or negative in two's complement form and contains an Indirect Addressing bit position.

#### Instruction Register (I Register):

The Instruction Register is a 17-bit register which contains the instruction currently being executed and its program protect bit. The register is not directly available to the programmer, except for console display and manipulation.

#### Program Status Word (K Register):

The Program Status Word is a 16-bit register which contains the enable/ disable bits for each interrupt level, the condition codes, the multiple precision and carry/borrow bits.

#### CONTROL SECTION

The control section of the EAI <u>640</u> Computer directs the operations required to execute instructions and establishes the timing relationships needed to perform these operations in their proper sequence. It also controls memory usage, interrupt processing, program protection, and input/output operations. The control section acquires an instruction from storage, interprets it, and sends the necessary commands to other sections. The Program Counter (P) provides program continuity by generating in sequence the storage addresses which contain the individual instructions.

#### **MEMORY SECTION**

The Memory Section of the EAI <u>640</u> Computer consists of two registers and the Storage Modules. The basic computer may have 8,192 words of high-speed, random access, 2-1/2 D, magnetic core storage which can be expanded to 16,384 or 32,768 words. Storage cycle time is 1.65 microseconds which is defined as the shortest possible time between successive read/write operations in core memory.

#### Memory Data Register (M Register):

The Memory Data Register is a 17-bit register from which information is written into memory and to which information is read from memory (16 information bits and a protect bit).

#### Memory Address Register (S Register):

The Memory Address Register is a 15-bit register which contains the address in memory from which information is to be read or into which information is to be written.

### EAI 640 ADDRESS STRUCTURE

#### STORAGE WORD

A Storage Word may be a 16-bit instruction, a 16-bit operand, one-half of a 31bit operand (divide or square root) or a 16-bit portion of a multiple precision operand. A Program Protect bit is appended to each 16-bit storage word, thus a storage word is 17 bits long. If the Protect Bit is a "1", it indicates that the word is part of a protected program.

#### STORAGE ADDRESSING

The location of each word in storage is identified by an assigned number (address). An address consists of 15 bits. Instructions, which reference core memory, have three fields: 4-bit Operation Code, 3-bit Address Mode (E field), and a 9-bit Displacement Field. As a matter of convenience, an instruction may be expressed as a six digit octal number, where the first digit may only be a 0 or 1. The first two octal digits will be the operation code, the third will be the E field and the last three digits the displacement address.

The terms used to describe memory addressing methods are:

EA - *effective address:* the destination location containing the data which is to be used for computation.

*IA - indirect address:* a location containing an address which indicates where the intended operand may be found. Multi-level indirect addressing is defined as a series of memory locations containing indirect addresses which are referenced in sequence by the computer.

D Field - displacement: bits 7 to 15 of a memory reference instruction. Treated as either:

(a) a 9-bit positive number in the range of 0 to 511;

(b) an 8-bit signed number in the range of -256 to +255.

The value in the D Field always participates in address computation.

*E Field*: bits 4, 5 and 6 of a memory reference instruction.

Bit 4 - indicates indirect addressing will take place (I).

- Bit 5 indicates index register addressing will take place (X).

- Bit 6 indicates relative-to-program-counter addressing will take place (P).

- I: Indirect addressing will take place followed (optionally) by Indexing and further Indirect Addressing.

- X: the contents of the index register. The most significant bit (zero) determines whether the resulting address is the effective address or is to be interpreted as a further indirect address. If bit 0 of the index register is "0" the resulting address is the effective address.

- P: the content of the program counter register which is the location of the current instruction.

#### ADDRESSING CONCEPT OF THE 640 COMPUTER

To understand the addressing concept of this computer, it is necessary to consider the memory of the computer in relation to the bits available in an instruction for addressing. The Displacement field, when treated as a 9-bit positive number, yields a range of 0 to 511 addresses. Therefore, the "Zone Zero" area from location 00000 to 00777 (octal) becomes available to the programmer directly.

The method of addressing these low core locations is commonly referred to as Absolute Addressing. It often is convenient to store counters or to provide temporary storage for intermediate results in this low core area because of the convenience of addressing through the displacement portion of the instruction.

The other method of addressing is commonly called "Relative" because it references locations which are relative to the current contents of the Program Counter (P Register) or the Index Register (X). It was stated earlier that the displacement portion of the instruction can also be an 8-bit signed number which gives a range of -256 to +255. This method allows a program to reference core forward or backward from its current Plocation and/or a value in the Index (X) Register. Both the Absolute and Relative form of addressing by themselves would not offer the flexibility of programming desired. For this reason, the 640 provides indirect addressing. Through the use of the program counter register, the index register, indirect addressing, and any combination thereof, the programmer has available any location in core storage for addressing.

#### Memory Address Mode Table

| Address Mode                   | E Field       | Initial Address                            | Indirect<br>Addressing<br>Follow? | Post Index<br>Indirect<br>Addressing? |

|--------------------------------|---------------|--------------------------------------------|-----------------------------------|---------------------------------------|

|                                |               |                                            |                                   |                                       |

| Absolute                       | E is 0        | D                                          | No                                | No                                    |

| Absolute Indirect              | E is 4        | (Zero Zone)                                | Yes                               | No                                    |

| Absolute Indirect Indexed      | E is $6 \int$ |                                            | Yes                               | Yes                                   |

| Relative                       | E is 1        | (P) ± D                                    | No                                | No                                    |

| <b>Relative Indexed Direct</b> | E is 3 \      | $(P + X) \pm D$                            | No                                | No                                    |

| Relative Indexed Indirect      | E is 3 ∫      | $(\mathbf{r} + \mathbf{A}) \pm \mathbf{D}$ | Yes                               | No                                    |

| <b>Relative Indirect</b>       | E is 5        | $(\mathbf{P}) \pm \mathbf{D}$              | Yes                               | No                                    |

| Relative Indirect Indexed      | E is 7∫       | (-) - 2                                    | Yes                               | Yes                                   |

| Indexed Relative Direct        | E is 2        | $(\mathbf{X}) \pm \mathbf{D}$              | No                                | No                                    |

| Indexed Relative Indirect      | E is $2 \int$ | $(\Delta) \pm D$                           | Yes                               | No                                    |

#### EAI 640 INTERRUPT SYSTEM

#### **GENERAL DESCRIPTION**

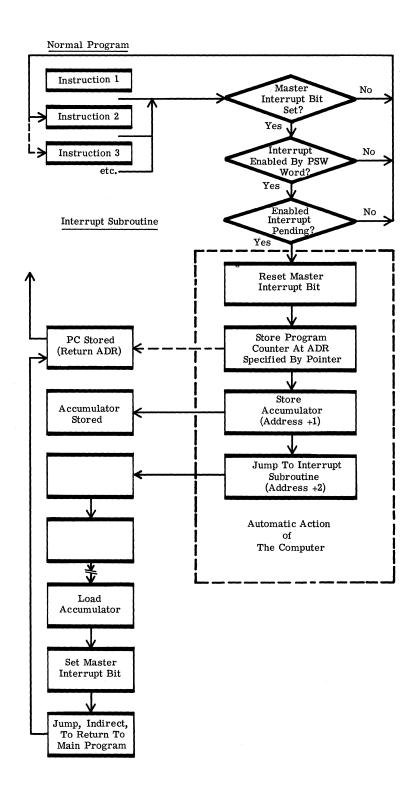

The Interrupt System of the EAI  $\underline{640}$  Computer allows the programmer a choice of interrupt priorities and actions. As the name implies, an Interrupt forces the computer to temporarily abandon its processing of the main program to service an anticipated condition.

Interrupts are signals which are generated internally or externally to the computer by certain conditions. An internal interrupt, for example, is caused by a memory protect violation. An example of an external interrupt would be the completion of an output through a peripheral piece of equipment causing an interrupt on that particular channel. The 640 Computer has a Master Interrupt Bit which enables or disables the interrupt system of the machine. The programmer can set or reset the Master Interrupt Bit. The exceptions to this interrupt procedure are the power failure interrupt and the interrupt test instructions which are programmed interrupts and will be processed regardless of the setting of the Master Interrupt Bit (Figure 2).

The Program Status Word (K Register) contains the enable/disable bits for each interrupt level. The programmer can "mask" the interrupts he desires by setting or resetting the bits in the K Register. Priority of interrupts is on the basis of bit position in the K Register. The PSW has the highest priority interrupts in the most significant bit positions.

The ability to mask interrupts through the Program Status Word allows the programmer to handle more than one interrupt. An interrupt automatically forces the computer to store the content of the Program Counter in the memory address specified by the Pointer. The content of the Accumulator is stored in the next memory location. The interrupt acknowledge procedure requires 5.8 microseconds. The first instruction executed to process the interrupt condition is located at the pointer address plus two. The Pointer itself is a fixed memory location assigned to each particular condition permitted to cause an interrupt and to each of the 64 possible external devices. 1

Figure 2. Diagram of 640 Interrupt System

#### MASTER INTERRUPT

The Master Interrupt Bit controls operation of the interrupt system. If the bit is set interrupts are recognized as specified by bits set in the PSW. Two instructions control setting and resetting of the Master Interrupt Bit.

The Master Interrupt is turned off (reset) upon recognition of an interrupt. The Master Interrupt can be set again as soon as the mask in the PSW has been modified to take into consideration the processing of the interrupt presently under consideration. The last instructions of the interrupt subroutine would normally be to set the Master Interrupt Bit followed by an indirect jump to the previously stored program counter.

#### **PROGRAM STATUS WORD (K Register)**

The K Register has 16 bits of which bit 0 through 10 are used to enable or disable corresponding levels of interrupts. If a bit in the PSW is a "1", the corresponding interrupt is enabled. If the bit is a "0", the interrupt is masked (disabled). Bit 12 is the Carry/Borrow bit, bit 13 is the Multiple Precision bit, bits 14 and 15 are condition codes which are set by arithmetic operations, and bit 11 is vacant.

The Exchange Accumulator and PSW instruction permits the programmer to store; modify it, or replace the present status word.

#### PRESERVATION OF REGISTERS DURING INTERRUPTS

On recognition of an interrupt, the Program Counter Register content is stored at the address designated by the Pointer and the content of the Accumulator is stored in the pointer address plus 1. The only exception to this is the TRAP instruction which modifies the Accumulator before it is stored. In the case of the TRAP, bits 8 through 15 of the Accumulator are set to equal the same bits of the instruction. The instruction will set bits 0 through 7 of the Accumulator to zero. Trap instructions can thus be numbered up to 256 (377<sub>o</sub>).

#### PRIORITY

Priority is established by bit position in the PSW, with the PSW bit zero having the highest priority. A further priority assignment is made in the case of peripheral equipment by the position of the device on the standard data channel or the buffered data channel.

#### **INTERNAL INTERRUPTS**

Internally generated interrupts have the highest priority. Internal interrupts are ignored and do not remain pending if the Master Interrupt Bit is reset or bits 0 through 4 of the PSW are reset. The single exception to this is the interval timer interrupt (bit 5 of PSW) which will remain pending until serviced.

The Internal Class of interrupts consists of:

Bit

- 0 Trap Instruction

- 1 Illegal Instruction

- 2 Illegal Procedure in Setting/Resetting Protect Bit

- 3 Memory Protect Violation

- 4 Machine Check and I/O Parity

- 5 Interval Timer (Up to Four, Optional)

#### **EXTERNAL INTERRUPTS**