## CS02/H1

## COMMUNICATIONS SUBSYSTEM

TECHNICAL MANUAL

(DH11/DM11 OR DHV11 COMPATIBLE)

3545 Harbor Boulevard Costa Mesa, California 92626 (714) 662-5600 TWX 910-595-2521

#### WARNING

This equipment generates, uses and can radiate radio frequency energy, and if not installed and used in accordance with the technical manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of Federal Communications Commission (FCC) Rules, which are designed to provide reasonable protection against such interference when operating in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Copyright (C) 1984 Emulex Corporation

The information in this manual is for information purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in the manual.

Printed in U.S.A.

## TABLE OF CONTENTS

| Section                                                                                                                              | Title                                                                                                                                                                                                                                                                                                                                                                                                                         | Page                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| ONE GEN                                                                                                                              | MERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                |

| 1.1<br>1.1.1<br>1.2<br>1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.4.1<br>1.4.2<br>1.5<br>1.5.1<br>1.5.2<br>1.5.3<br>1.5.4<br>1.5.5 | INTRODUCTION RELATED DOCUMENTATION SUBSYSTEM OVERVIEW PHYSICAL ORGANIZATION OVERVIEW CC02 CONTROLLER MODULE LSI-11 DISTRIBUTION PANELS CP24 DISTRIBUTION PANEL CP24/B DISTRIBUTION PANEL SUBSYSTEM MODELS AND OPTIONS DISTRIBUTION PANELS CBALES FOR THE CS02/H SUBSYSTEM FEATURES MICROPROCESSOR DESIGN FCC COMPLIANCE SELF-TEST PROGRAMMABLE CHANNEL PARAMETERS DMA ON TRANSMIT COMPATIBILITY DIAGNOSTICS OPERATING SYSTEMS | 1-1<br>1-2<br>1-3<br>1-3<br>1-3<br>1-5<br>1-5<br>1-5<br>1-7<br>1-8<br>1-8<br>1-8<br>1-9<br>1-9 |

| 1.6.3<br>1.6.4<br>1.6.5                                                                                                              | HARDWARE DISTRIBUTION PANEL CONNECTORS MODEM CONTROLS SUPPORTED                                                                                                                                                                                                                                                                                                                                                               | 1-9<br>1-9<br>1-10                                                                             |

|                                                                                                                                      | SSYSTEM SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |

| 2.3                                                                                                                                  | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-1<br>2-1<br>2-3<br>2-4                                                                       |

|                                                                                                                                      | APPLICATION AND CONFIGURATION  OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                       | 3-1                                                                                            |

| 3.1.1<br>3.1.2<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.1.3                                                                      | Q-BUS ADDRESS CONVENTION                                                                                                                                                                                                                                                                                                                                                                                                      | 3-1<br>3-1<br>3-2<br>3-2<br>3-3<br>3-3<br>3-3<br>3-4                                           |

| 3.2.1.4<br>3.3<br>3.4<br>3.4.1                                                                                                       | CP25 Distribution Panel                                                                                                                                                                                                                                                                                                                                                                                                       | 3-4<br>3-4<br>3-7<br>3-7                                                                       |

| 3.4.2                                                                                                                                | AUTOCONFIGURE DETERMINING THE VECTOR ADDRESS FOR USE WITH                                                                                                                                                                                                                                                                                                                                                                     | 3-9                                                                                            |

| 3.4.3<br>3.4.4                                                                                                                       | AUTOCONFIGURE  DH11 SYSTEM CONFIGURATION EXAMPLE  DHV11 SYSTEM CONFIGURATON EXAMPLE                                                                                                                                                                                                                                                                                                                                           | 3-12<br>3-13                                                                                   |

# TABLE OF CONTENTS (continued)

| Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| FOUR II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                |

| FOUR 4.1.1.2 4.1.3 4.2.1 4.1.3 4.2.2 4.3.3.3.3 4.3.3.3 4.3.3.4 4.3.3.4 4.3.4.3 4.3.5.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3.5 4.3 | OVERVIEW  SUBSYSTEM CONFIGURATIONS DIP SWITCH TYPES Q-BUS ADDRESS CONVENTION  INSPECTION  CC02 CONTROLLER MODULE INSPECTION CP22, CP24 AND CP24/B DISTRIBUTION PANELS INSPECTION  CC02 CONTROLLER MODULE SETUP DIP HEADER CONFIGURATION EMULATION SELECTION CC02 DEVICE ADDRESS SELECTION DH11/DM11 Device Register Addresses DHV11 Device Register Addresses CC02 INTERRUPT VECTOR ADDRESSES DH11 Vector Addresses DHV11 Vector Addresses DM11 Vector OPTIONS  CC02 Run/Halt/Reset Switch CC02 Tie CTS To DTR DH11 Baud Rate Option DH11 Expanded Silo CC02 Force Two Stop Bits DH11 22-Bit Addressing Mode Monitor Q-Bus DC Power OK Signal DH11 Clear To Send Flow Control DHV11 Level Flow Control Option DHV11 Level Flow Control DHV11 Level Flow Control DHV11 High Performance Throughput Option | 1-12-2-3-3-3-7-8-8-8-0-1-12-4-4-4-4-4-1-1-1-1-1-1-1-1-1-1-1-1- |

| 4.7.3 <b>FIVE O</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PERATOR SWITCHES AND INDICATORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-23                                                           |

| 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-1<br>5-1<br>5-1<br>5-1<br>5-2                                |

# TABLE OF CONTENTS (continued)

| Section | Title                                     | Page |

|---------|-------------------------------------------|------|

| SIX TRO | DUBLESHOOTING                             |      |

| 6.1     | OVERVIEW                                  | 6-1  |

| 6.1.1   | SERVICE                                   | 6-1  |

| 6.1.2   | TEST CONNECTOR                            | 6-2  |

| 6.2     | FAULT ISOLATION PROCEDURES                | 6-4  |

| 6.2.1   | SELF-TEST FAILURE FAULT ISOLATION         | 6-4  |

| 6.3     | POWER-UP SELF-TESTS                       | 6-4  |

| 6.3.1   | CC02 CONTROLLER MODULE SELF-TEST          | 6-4  |

| 6.4     | CC02 OPERATOR-INITIATED SELF-DIAGNOSTICS  | 6-6  |

| 6.4.1   | NORMAL RUN MODE                           | 6-6  |

| 6.4.2   | OVERRIDE MODE                             | 6-7  |

| 6.4.3   | CONTINUOUS EXTERNAL LOOPBACK MODE         | 6-7  |

| 6.4.4   | SEARCH MODE                               | 6-7  |

| 6.4.5   | ECHO MODE                                 | 6-7  |

| SEVEN I | DEVICE REGISTERS AND PROGRAMMING          |      |

| DUARM 1 |                                           |      |

| 7.1     | OVERVIEW                                  | 7-1  |

| 7.2     | DH11 REGISTERS                            | 7-1  |

| 7.2.1   | SYSTEM CONTROL REGISTER (SCR)             | 7-3  |

| 7.2.2   | RECEIVED CHARACTER REGISTER (RCR)         | 7-6  |

| 7.2.3   | LINE PARAMETER REGISTER (LPR)             | 7-7  |

| 7.2.4   | CURRENT ADDRESS REGISTER (CAR)            | 7-10 |

| 7.2.5   | BYTE COUNT REGISTER (BCR)                 | 7-10 |

| 7.2.6   | BUFFER ACTIVE REGISTER (BAR)              | 7-10 |

| 7.2.7   | BREAK CONTROL REGISTER (BRCR)             | 7-11 |

| 7.2.8   | SILO STATUS REGISTER (SSR)                | 7-12 |

| 7.3     | DM11 (MODEM CONTROL) REGISTERS            | 7-13 |

| 7.3.1   | CONTROL AND STATUS REGISTER (CSR)         | 7-13 |

| 7.3.2   | LINE STATUS REGISTER (LSR)                | 7-16 |

| 7.4     | DHV11 REGISTERS                           | 7-19 |

| 7.4.1   | CONTROL STATUS REGISTER (CSR)             | 7-19 |

| 7.4.2   | RECEIVER BUFFER (RBUF)                    | 7-22 |

| 7.4.3   | TRANSMIT CHARACTER BUFFER (TXCHAR)        | 7-23 |

| 7.4.4   | LINE PARAMETER REGISTER (LPR)             | 7-24 |

| 7.4.5   | LINE STATUS (STAT)                        | 7-27 |

| 7.4.6   | LINE CONTROL (LNCTRL)                     | 7-29 |

| 7.4.7   | TRANSMIT BUFFER ADDRESS 1 (TBUFFAD1)      | 7-32 |

| 7.4.8   | TRANSMIT BUFFER ADDRESS 2 (TBUFFAD2)      | 7-33 |

| 7.4.9   | TRANSMIT DMA BUFFER COUNTER (TBUFFCT)     | 7-34 |

| 7.5     | DH11/DM11 GENERAL PROGRAMMING INFORMATION | 7-35 |

| 7.5.1   | INITIALIZE                                | 7-35 |

| 7.5.2   | INTERRUPTS                                | 7-35 |

| 7.5.3   | 22-BIT ADDRESS PROGRAMMING PROCEDURE      | 7-36 |

| 7.5.4   | RECEIVER OPERATION                        | 7-37 |

| 7.5.4.1 | Receiver Scanner                          | 7-37 |

| 7.5.4.2 | Silo Operation                            | 7-37 |

| 7.5.4.3 | Half-Duplex Operation                     | 7-37 |

| 7.5.5   | TRANSMITTER OPERATION                     | 7-38 |

| 7.5.5.1 | DMA Transmission                          | 7-38 |

# TABLE OF CONTENTS (continued)

| Section | Title                                 | Page |

|---------|---------------------------------------|------|

| 7.6     | DHV11 GENERAL PROGRAMMING INFORMATION | 7-38 |

| 7.6.1   | INITIALIZE                            | 7-38 |

| 7.6.2   | PROGRAMMABLE PARAMETERS               | 7-39 |

| 7.6.3   | INTERRUPTS                            | 7-40 |

| 7.6.4   | DATA FLOW CONTROL                     | 7-40 |

| 7.6.5   | DIAGNOSTIC CODES                      | 7-42 |

| 7.6.5.1 | Self-Test Diagnostic Codes            | 7-42 |

| 7.6.5.2 | Interpretation of Self-Test Codes     | 7-42 |

| 7.6.5.3 | Skipping Self-Test                    | 7-44 |

| 7.6.6   | ERROR INDICATION                      | 7-44 |

| 7.6.7   | RECEIVER OPERATION                    | 7-45 |

| 7.6.7.1 | Receiver Scanner                      | 7-45 |

| 7.6.7.2 | FIFO Buffer Operation                 | 7-45 |

| 7.6.7.3 | Half-Duplex Operation                 | 7-45 |

| 7.6.8   | TRANSMITTER OPERATION                 | 7-45 |

| 7.6.8.1 | DMA Transmission                      | 7-46 |

| 7.6.8.2 | Single Character Transmission         | 7-46 |

| 7.6.8.3 | Modem Control                         | 7-47 |

| 7.7     | CC02 CONTROLLER ARCHITECTURE          | 7-48 |

| 7.7.1   | RECEIVER OPERATION                    | 7-49 |

| 7.7.2   | TRANSMITTER OPERATION                 | 7-49 |

| EIGHT : | INTERFACES                            |      |

| 8.1     | OVERVIEW                              | 8-1  |

| 8.2     | CC02 CONTROLLER MODULE                | 8-1  |

| 8.2.1   | Q-BUS                                 | 8-1  |

| 8.2.1.1 | Q-Bus Address                         | 8-2  |

| 8.2.1.2 | Interrupt Vector Address              | 8-2  |

| 8.2.2   | DISTRIBUTION PANEL INTERFACE          | 8-2  |

## LIST OF APPENDICES

| Appendi                                                                                           | ppendix Title                                                                                                                                                                                                                                                                                                                                 |                                                                    |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| A                                                                                                 | CABLE SCHEMATICS                                                                                                                                                                                                                                                                                                                              |                                                                    |

| В                                                                                                 | DH11 DIAGNOSTIC                                                                                                                                                                                                                                                                                                                               |                                                                    |

| B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.5.1<br>B.5.2<br>B.5.3<br>B.5.4<br>B.5.5<br>B.6<br>B.7<br>B.8 | GENERAL DESCRIPTION ZDHMD0 DIAGNOSTIC PATCHES REASONS FOR DIAGNOSTIC PATCHES LOADING PROCEDURES STARTING PROCEDURES PROGRAM OPTIONS SWITCHLESS CPU NORMAL PROGRAM START AT 200 DEFAULT PARAMETER START AT 204 LINE AND DEVICE PARAMETER CHANGE START AT 210 TEST SUMMARY ERROR HEADER MNEMONIC DEFINITIONS DECX11 SYSTEM EXERCISER DIAGNOSTIC | B-1<br>B-3<br>B-4<br>B-4<br>B-5<br>B-6<br>B-6<br>B-7<br>B-7<br>B-8 |

| c                                                                                                 | DHV11 DIAGNOSTICS                                                                                                                                                                                                                                                                                                                             |                                                                    |

| C.1<br>C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.6.1<br>C.6.2                                          | GENERAL DESCRIPTION DIAGNOSTIC TEST FUNCTIONS DIAGNOSTIC SUPERVISOR SUMMARY LOADING PROCEDURES STARTING THE DIAGNOSTIC PROGRAM DRS SUPERVISOR COMMANDS COMMAND SWITCHES CONTROL/ESCAPE CHARACTERS SUPPORTED DHV11 DIAGNOSTIC EXAMPLES                                                                                                         | C-1<br>C-2<br>C-3<br>C-4<br>C-5<br>C-6<br>C-7<br>C-8               |

| D                                                                                                 | ASCII CODE CONVERSION                                                                                                                                                                                                                                                                                                                         |                                                                    |

| E                                                                                                 | PROM REMOVAL AND REPLACEMENT                                                                                                                                                                                                                                                                                                                  |                                                                    |

| E.1.1                                                                                             | OVERVIEW EXCHANGING EMULATION PROMS                                                                                                                                                                                                                                                                                                           | D-1<br>D-1                                                         |

| F                                                                                                 | GLOSSARY                                                                                                                                                                                                                                                                                                                                      |                                                                    |

## LIST OF TABLES

| Table | Title                                                   | Page |

|-------|---------------------------------------------------------|------|

| 1-1   | CS02/H Contents and Part Numbers                        | 1-5  |

| 1-2   | Distribution Panels Available for the CS02/H            | 1-7  |

| 1-3   | Distribution Panel Cables                               | 1-7  |

| 2-1   | CS02/H General Specifications                           | 2-1  |

| 2-2   | CC02 Controller Module Physical Specifications          | 2-3  |

| 2-3   | CC02 Controller Module Environmental Specifications     | 2-4  |

| 3-1   | SYSGEN Device Table                                     | 3-8  |

| 3-2   | Priority Ranking for Floating Vector Addresses          | 3-10 |

| 3-3   | Bus and Vector Address Example                          | 3-12 |

| 3-4   | Floating Address Computation                            | 3-12 |

| 3-5   | Bus and Vector Address Example                          | 3-13 |

| 3-6   | Floating Address Computation                            | 3-14 |

| 4-1   | DH11/DM11 CC02 Switch Definitions/Factory Configuration | 4-5  |

| 4-2   | DHV11 CCO2 Switch Definitions/Factory                   | 4-6  |

| 4-3   | CC02 Jumper Definition/Factory Configuration            | 4-7  |

| 4-4   | CS02/H Q-Bus Address Selection                          | 4-9  |

| 4-5   | DH11/DHV11 Vector Address Selection                     | 4-11 |

| 4-6   | DMll Vector Address Selection                           | 4-13 |

| 4-7   | CC02 Internal Micro Test                                | 4-15 |

| 4-8   | Level Flow Control Switch Settings                      | 4-18 |

| 6-1   | Flow Chart Symbol Definitions                           | 6-2  |

| 6-2   | Self-Test Modes                                         | 6-6  |

| 7-1   | Tx and Rx Speed Table                                   | 7-8  |

| 7-2   | Transmit and Receive Baud Rates for the DHVll           | 7-25 |

| 7-3   | DHVll Self-Test Diagnostic Codes                        | 7-43 |

| 7-4   | DHVll Self-Test Error Codes                             | 7-43 |

| A-1   | Cable Applications                                      | A-1  |

| D-1   | ASCII Seven-Bit Code                                    | C-1  |

| E-1   | CC02 PROM Locations                                     | D-1  |

## LIST OF FIGURES

| Figure | Title                                                   | Page          |

|--------|---------------------------------------------------------|---------------|

| 1-1    | Subsystem Configuration in an LSI-11                    | 1-4           |

| 1-2    | Subsystem Configuration in a Micro/PDP/VAX              | 1-4           |

| ī-3    | CS02/H Basic Communications Subsystem                   | 1-6           |

| 2-1    | CC02 Controller Module Dimensions                       | 2-4           |

|        | An LSI-11 Application                                   | 3-5           |

| 3-2    | A Micro/PDP/VAX Application                             | 3-6           |

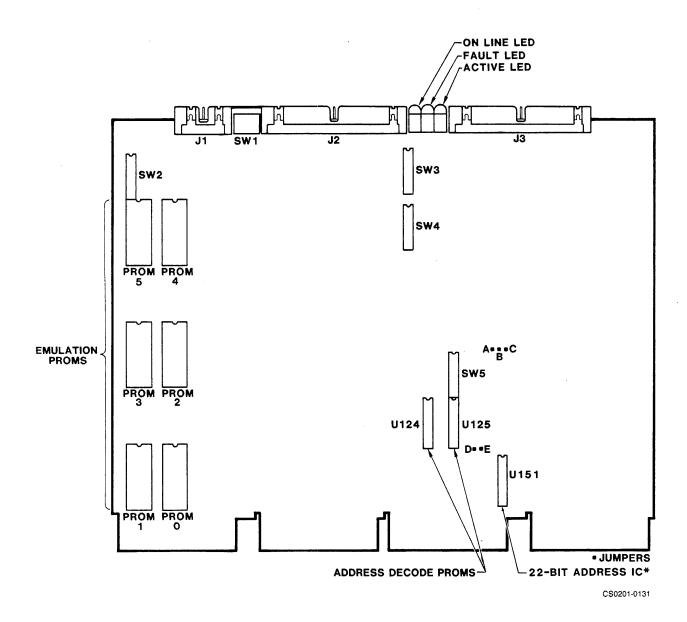

| 4-1    | CC02 Controller Module Component Locations              | 4-4           |

| 4-2    | CC02 DIP Header Orientation                             | 4-7           |

| 4-3    | Micro/PDP/VAX Patch and Filter Panel Assembly           | 4-22          |

| 5-1    | CC02 Controller Module Operator Controls and Indicators | 5-2           |

| 6-1    | CS02/H1 Configuration Reference Sheet                   | 6-2           |

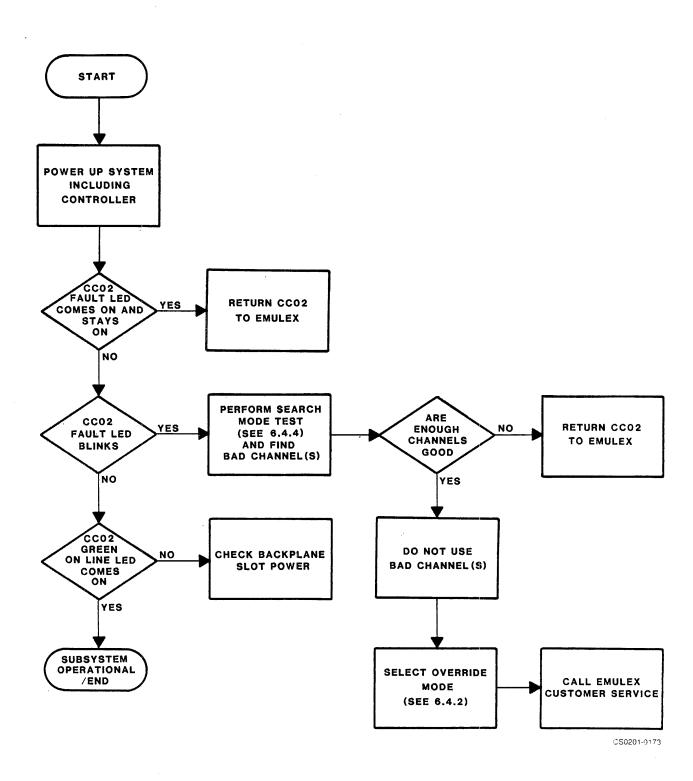

| 6-2    | Self-Test Fault Isolation Chart                         | 6-6           |

| 7-1    | DH11/DM11 Registers                                     | 7-2           |

| 7-2    | DHV11 Registers                                         | 7-18          |

| 7-3    | CC02 Controller Module Block Diagram                    | 7-48          |

| 8-1    | O-Bus Interface Connections                             | 8-3           |

| A-1    | CP22 or CP24/B to Terminal Cable                        | A-l           |

| A2     | CP24 to Terminal Cable                                  | A-2           |

| A3     | CP22 or CP24/B Null-Modem Cable                         | A-2           |

| A4     | CP24 Null-Modem Cable                                   | A-2           |

| A5     | CP22 or CP24/B Modem Cable                              | A-3           |

| A6     | CP24 Modem Cable                                        | A-3           |

| A7     | CP22, CP24 or CP24/B Cable with DTR                     | A-4           |

| A8     | DH11 CP22 and CP24/B Wrap-Around Connector              | A-4           |

| A9     | DHV11 CP22 and CP24/B Wrap-Around Connector             | A-4           |

| A-10   | DH11 CP24 Wrap-Around Connector                         | A-5           |

| A-11   | DHV11 CP24 Wrap-Around Connector                        | - <b>A−</b> 5 |

| A-12   | DHV11 CP22 and CP24/B Staggered Loopback Connector      | A-5           |

| A-13   | DHV11 Staggered Loopback Cable                          | A-5           |

| C-1    | Staggered Loopback Cable Configuration                  | C-2           |

#### EMULEX PRODUCT WARRANTY

CONTROLLER WARRANTY: Emulex warrants for a period of twelve (12) months from the date of shipment that each Emulex controller product supplied shall be free from defects in material and workmanship.

CABLE WARRANTY: All Emulex provided cables are warranted for ninety (90) days from the time of shipment.

The above warranties shall not apply to expendable components such as fuses, bulbs, and the like, nor to connectors, adaptors, and other items not a part of the basic product. Emulex shall have no obligation to make repairs or to cause replacement required through normal wear and tear or necessitated in whole or in part by catastrophe, fault or negligence of the user, improper or unauthorized use of the product, or use of the product is such a manner for which it was not designed, or by causes external to the product, such as but not limited to, power failure or air conditioning. Emulex's sole obligation hereunder shall be to repair or replace any defective product, and, unless otherwise stated, pay return transportation cost for such replacement. Purchaser shall provide labor for removal of the defective product, shipping charges for return to Emulex and installation of its replacement.

THE EXPRESSED WARRANTIES SET FORTH IN THIS AGREEMENT ARE IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING WITHOUT LIMITATION, ANY WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, AND ALL OTHER WARRANTIES ARE HEREBY DISCLAIMED AND EXCLUDED BY EMULEX. THE STATED EXPRESS WARRANTIES ARE IN LIEU OF ALL OBLIGATIONS OR LIABILITIES ON THE PART OF EMULEX FOR DAMAGES, INCLUDING BUT NOT LIMITED TO SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES ARISING OUT OF, OR IN CONNECTION WITH THE USE OR PERFORMANCE OF THE PRODUCT.

RETURNED MATERIAL: Warranty claims must be received by Emulex within the applicable warranty period. A replaced product, or part thereof, shall become the property of Emulex and shall be returned to Emulex at Purchaser's expense. All returned material must be accompanied by a RETURN MATERIALS AUTHORIZATION (RMA) number assigned by Emulex.

#### 1.1 INTRODUCTION

This manual is designed to help you install and use your CS02/H Communications Subsystem, manufactured by Emulex Corporation, in the most efficient and straightforward manner possible. The manual's eight sections and five appendices are described briefly below.

- Section 1 General Description: This section contains an overview of the CS02/H Communications Subsystem.

- Section 2 <u>Subsystem Specification</u>: This section contains a specification for each component of the subsystem.

- Section 3 <u>Application and Configuration</u>: This section contains the information necessary to plan your installation.

- Section 4 <u>Installation</u>: This section contains the information needed to set-up and physically install the subsystem.

- Section 5 Operator Switches and Indicators: This section describes the function of the subsystem switches and indicators.

- Section 6 <u>Troubleshooting</u>: This section describes fault isolation procedures that can be used to pinpoint trouble spots.

- Section 7 Controller Registers and Programming: This section contains a description of the subsystem's DH11-, DM11- and DHV11-type registers. This section also provides programming notes and describes the controller architecture.

- Section 8 <u>Interfaces</u>: This section describes the subsystem Q-Bus and serial interfaces.

- Appendix A <u>Cable Schematics</u>: This appendix contains schematics of the EIA cables required to attach terminals, printers, modems and wrap-around connectors to ports of the CS02/H.

- Appendix B <u>DHll Diagnostic</u>: This appendix contains operating instructions and patches for the DHll diagnostic, ZDHMD0.

- Appendix C <u>DHVll Diagnostics:</u> This appendix contains operating instructions for the DHVll diagnostics.

- Appendix D Code Conversion Table: This appendix provides an ASCII and decimal/hexadecimal/octal table.

## Subsystem Overview

Appendix E PROM Removal and Replacement: This appendix contains PROM removal/replacement instructions to allow the user to change the CC02 Controller Module's PROMs in the field. A list of firmware PROM numbers and their locations on the PCBA is also provided here.

#### 1.1.1 RELATED DOCUMENTATION

This manual is the main piece of documentation for the CS02/Hl subsystem. Two other manuals come with the subsystem: a distribution panel technical manual and a diagnostic manual (if diagnostics were ordered). These other manuals are used only during specific parts of the installation procedure and this manual will clearly reference the other manuals any time you need them.

#### 1.2 SUBSYSTEM OVERVIEW

This manual explains the use and installation of the CS02/H Communications Subsystem. The CS02/H Communications Subsystem emulates one Digital Equipment Corporation (DEC) 16-channel DH11 Asynchronous Communications Multiplexer, including partial DMll modem control for all channels, or it emulates two DEC eight-channel DHVll Asynchronous Multiplexers. The CS02/H Communications Subsystem is designed for use with DEC Q-Bus based processors.

The CS02/H Communications Subsystem consists of a controller module and istribution panel. The controller module takes multiplexed data from the host central processing unit (CPU), demultiplexes the data, and sends it to the ports on the distribution panel(s). Conversely, data from the distribution panel(s) is multiplexed by the controller module, and sent to the host CPU. The controller module also serializes and deserializes data.

The distribution panels hold the connectors that allow external devices such as terminals, printers and modems to be connected to the subsystem.

The CS02/H incorporates several advanced features for communications multiplexers. These features include direct memory access (DMA) on transmit, programed input/output (I/O) on reception, a 256-character receive silo with programmable fill alarm, individually programmable channel parameters, and data rates of up to 38,400 bits per second These features and the CS02/H's bus register structure are fully compatible with DEC's DHll communications multiplexer with DMll modem control, and with DEC's DHV11 asynchronous multiplexer.

#### 1.3 PHYSICAL ORGANIZATION OVERVIEW

The CS02/H Communications Subsystem is a modular, microprocessor-based controller that connects directly to the host computer's Q-Bus backplane. The microprocessor architecture ensures excellent reliability and compactness, while significantly reducing communications overhead for the host computer.

The CS02/H1 Communications Subsystem consists of two units: the CC02 Controller Module, and a distribution panel. Distribution panels are available that fit in either an LSI-11 CPU or a Micro/PDP-11 or MicroVAX chassis. Two asynchronous interfaces are available, RS-232 and RS-423.

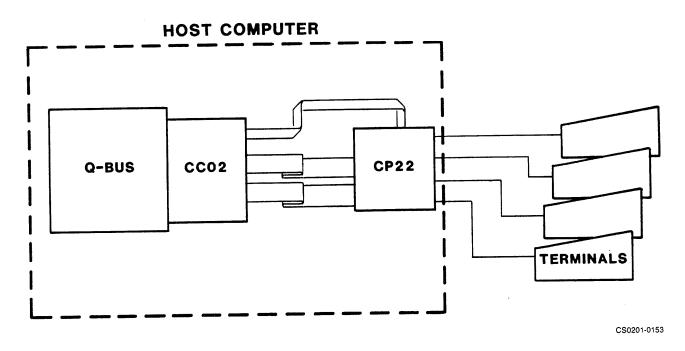

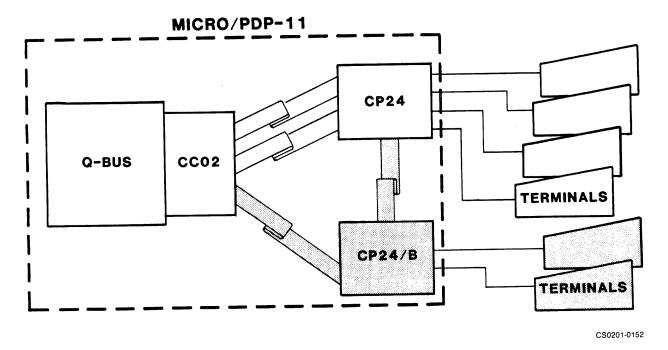

The relationship of the CS02/H components in an LSI-11 is shown in Figure 1-1. The relationship of CS02/H components in a Micro/PDP-11 or MicroVAX is shown in Figure 1-2. The component relationships for both applications are described in the following subsections.

#### 1.3.1 CC02 CONTROLLER MODULE

The microprocessor-based CC02 is contained on a single quad-wide printed circuit board assembly (PCBA) which plugs directly into any Q-Bus backplane slot. The CC02's firmware-driven microprocessor performs the DH11/DM11 or DHV11 emulation.

#### 1.3.2 LSI-11 DISTRIBUTION PANELS (CP22 and CP25)

When the CS02/H Communications Subsystem is mounted in an LSI-11, the CC02 Controller Module is used with either the CP22 or CP25 Distribution Panels. The CC02 Controller Module interfaces with the distribution panel via two 50-wire and one 16-wire flat cables. Signals are distributed by the distribution panel via 16 subminiature D-type connectors.

The LSI-11 distribution panels are designed to be rack-mounted on the rear RETMA rails of a CPU cabinet. An Emulex two-panel rack mount chassis accompanies these distribution panel.

### 1.3.3 CP24 DISTRIBUTION PANEL

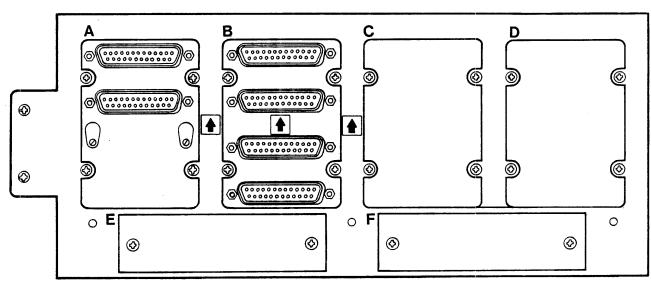

When the CS02/H Communications Subsystem is mounted in a Micro/PDP-11 or MicroVAX, the CC02 Controller Module is used with the CP24 Distribution Panel. The CP24 Distribution Panel is mounted in the rear bulkhead of the Micro/PDP-11 cabinet. The CC02 Controller Module interfaces with the CP24 Distribution Panel via two 50-wire flat cables. Signals are distributed by the CP24 Distribution Panel via 16 nine-pin subminiature D-type connectors.

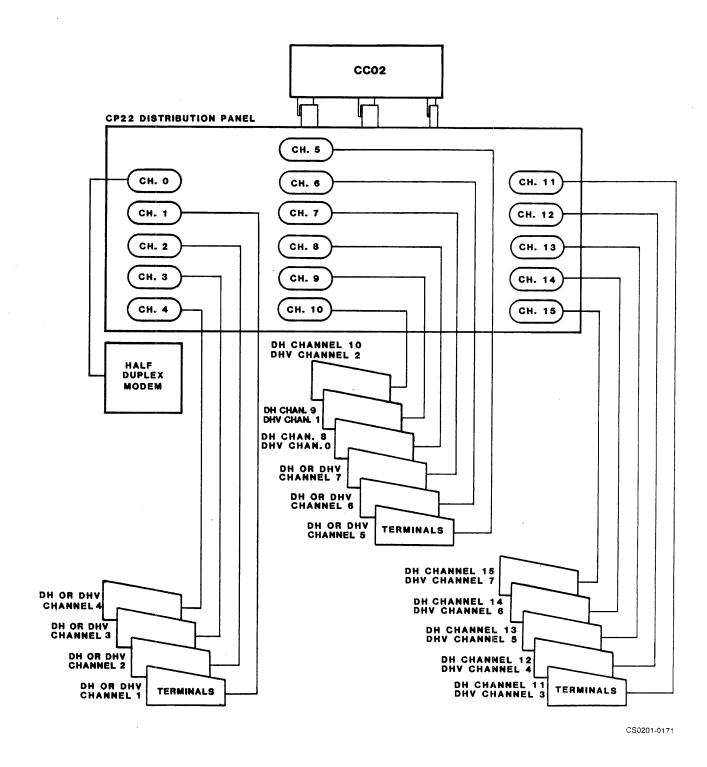

Figure 1-1. Subsystem Configuration in an LSI-11

Figure 1-2. Subsystem Configuration in a Micro PDP/VAX

1-4 General Description

## 1.3.4 CP24/B DISTRIBUTION PANEL

When the CS02/H Communications Subsystem is mounted in the Micro/PDP-11 or MicroVAX, an optional CP24/B Distribution Panel may be used in addition to the CP24 Distribution Panel. The CP24/B Distribution Panel provides extra modem control signals for the first four channels, and replaces CH.0 through CH.3 on the CP24 Distribution Panel. The CC02 Controller interfaces to the CP24/B Distribution Panel via one 16-wire flat cable. The CP24 Distribution Panel interfaces with the CP24/B Distribution Panel via one 34-wire flat cable. Signals are distributed by the CP24/B Distribution Panel via four RS-232-C compatible subminiature D-type connectors.

## 1.4 SUBSYSTEM MODELS AND OPTIONS

Table 1-1 shows the contents of the CS02/H subsystem. Subsection 1.4.1 describes the distribution panels available and lists their part numbers. Figure 1-2 shows the CS02/H with a CP22 Distribution Panel.

| Itm | Qty | Description                                     | Part Number                | Comment                                              |

|-----|-----|-------------------------------------------------|----------------------------|------------------------------------------------------|

| 1 2 | 1 1 | CC02 Controller Module<br>CS02 Extended Address | CS0210201-H1X<br>CS0113001 | For 22-bit                                           |

| "   | -   | Option Kit                                      |                            | addressing                                           |

| 3   | 1   | Distribution Panel                              | Varies                     | See subsection 1.4.1                                 |

| 4   | 1   | Wrap-Around Connector                           | Varies                     | For diagnostic<br>testing with<br>distribution panel |

| 5   |     | Ribbon Cable(s)                                 | Varies                     | CC02 to distribution panelsee subsection 1.4.2       |

| 6   | 1   | CS02/H Technical<br>Manual                      | CS0251001                  |                                                      |

| 7   | 1   | Distribution Panel<br>Technical Manual          | Varies                     |                                                      |

Table 1-1. CS02/H Contents and Part Numbers

## 1.4.1 DISTRIBUTION PANELS

Three distribution panels can be used with the CS02/H: the CP22 (RS-232-C), the CP24 (RS-232-C for the Micro/PDP-11 and MicroVAX), and the CP25 (RS-422-A). All of these panels are FCC compliant.

## Subsystem Models and Options

CS0201-0157

Figure 1-3. CS02/H Basic Communications Subsystem (shown with CP24 and CP24/B Distribution Panels)

The CP22 and CP25 distribution panels each contain 16 ports. They are the same size as DEC's DMF32 distribution panel and can be mounted directly in its place in CPU cabinets that are DMF32 compatible. They can also be mounted directly on RETMA rails if the rack mount chassis option is used. Mounting options are covered in more detail in the distribution panel technical manual.

The CP22 and CP25 support partial modem control on all 16 ports. The CP22 also supports full modem controls on the first four channels.

The CP22 can be ordered with EMI filters installed. This is a special order item, however, and is not generally required.

The CP24 Distribution Panel is designed to be mounted in a Micro/PDP-11 or MicroVAX chassis. The CP24 contains 16 ports with partial modem control. The CP24 uses 9-pin connectors on its 16 ports. If the optional CP24/B is ordered, the first four channels use standard 25-pin connectors and support full modem controls.

Table 1-2 lists the features and part numbers of each of the distribution panels.

Table 1-2. Distribution Panels Available for the CS02/H

| Dist.<br>Panel     | Part<br>Number               | Description                                                                                               |

|--------------------|------------------------------|-----------------------------------------------------------------------------------------------------------|

| CP22-01<br>CP22-02 | CP2210201-01<br>CP2210201-02 | RS-232-C<br>RS-232-C, with EMI filters                                                                    |

| CP24<br>CP24/B     | CP2410201-00<br>CP2410202    | RS-232-C, for Micro/PDP/VAX RS-232-C, provides full modem control on first four lines when used with CP24 |

| CP25               | CP2510401                    | RS422-A or RS-232-C                                                                                       |

## 1.4.2 CABLES FOR THE CS02/H SUBSYSTEM

The cables used to attach the distribution panel to the CC02 controller module vary depending on the distribution panel used. Table 1-3 shows the cables required for each type of distribution panel.

Table 1-3. Distribution Panel Cables

| Dist.<br>Panel | Cables Required                  | Comment                                                                                                                    |

|----------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| CP22           | CU2111201-02 (2)<br>CU0211201-03 | 50-wire ribbon cable, 8 foot<br>16-wire ribbon cable, 8 foot<br>(provides full modem control on<br>first four channels)    |

| CP24           | CU2411202 (2)                    | 50-wire ribbon cable, 1 foot                                                                                               |

| CP24/B         | CU2411201<br>CU0211201-01        | 34-wire ribbon cable, .25 feet<br>(connects CP24/B to CP24)<br>16-wire ribbon cable, 1.5 feet<br>(connects CP24/B to CC02) |

| CP25           | CU2111201-02 (2)                 | 50-wire ribbon cable                                                                                                       |

#### **Features**

#### 1.5 FRATURES

Several features enhance the usefulness of the CS02/H Communications Subsystem.

#### 1.5.1 MICROPROCESSOR DESIGN

The CS02/H design incorporates an eight-bit, high-performance bipolar microprocessor to perform all controller functions. The microprocessor approach provides a reduced component count, high reliability, easy maintainability, and most importantly the ability to perform an emulation of the equivalent DEC controller. Emulex controllers achieve functional capability beyond that of the DEC controllers which they emulate by providing enhancement features such as built-in self-test during power-up, and channel-loop test.

#### 1.5.2 FCC COMPLIANCE

The CS02/H Communications Subsystem complies with the appropriate Federal Communications Commission (FCC) standards that limit EMI radiation from computing devices. All models, if operated within Class A compliant cabinets, comply with the limits for FCC Class A.

### 1.5.3 SELF-TEST

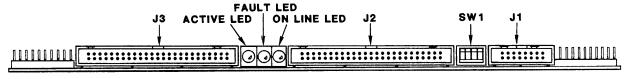

The CC02 Controller Module incorporates an internal self-test routine which is executed upon power-up. This test exercises all parts of the microprocessor, the on-board memory, and the dual universal asynchronous receiver transmitters (DUARTs). Although this test does not completely test all circuitry, successful execution indicates a very high probability that the CC02 Controller Module and the DUARTs are operational. The CC02 Controller Module uses on-board light emitting diodes (LEDs) to indicate self-test failure. In the event of self-test failure, the CC02 Controller Module cannot be addressed from the CPU.

#### 1.5.4 PROGRAMMABLE CHANNEL PARAMETERS

Parameters on all 16 channels provided by the CS02/H Communications Subsystem can be set individually under program control.

Parameters for channels include:

- All popular data rates from 50 to 38,400 bps

- The number of stop bits per character

- Parity (odd, even, or none)

- The number of data bits per character.

### 1-8 General Description

### 1.5.5 DMA ON TRANSMIT

The subsystem performs full-word direct memory access (DMA) on transmit. This feature considerably reduces the CPU overhead associated with data communications, especially when the host system is running terminal-I/O intensive software.

#### 1.6 COMPATIBILITY

#### 1.6.1 DIAGNOSTICS

The CS02/H Communications Subsystem executes the standard DEC DH11 and DM11 Diagnostics when Emulex-supplied patches are used (see Appendix B). The CS02/H also executes the standard DHV11 diagnostics.

#### 1.6.2 OPERATING SYSTEMS

The CS02/H Communications Subsystem is compatible (with minor modification if 22-bit addressing is used for the DH11 emulation), with all DEC LSI-11 and Micro/PDP-11 operating systems that support the DEC DH11 Communications Multiplexer and the DEC DHV11 Asynchronous Multiplexer. It is also compatible with all MicroVAX operating systems if the CC02 firmware set is Revision F or higher.

#### 1.6.3 HARDWARE

The CS02/H Communications Subsystem is electrically and mechanically compatible with all Q-Bus applications.

#### 1.6.4 DISTRIBUTION PANEL CONNECTORS

Emulex distribution panels are available that are compatible with the following interfaces:

- RS-232-C

- RS-422-A

- 20 mA current loop (requires nonstandard backplane wiring)

Details of distribution panel compatibility and functionality are in the distribution panel technical manual that came with your communications subsystem.

## Compatibility

## 1.6.5 MODEM CONTROLS SUPPORTED

Modem controls necessary for full-duplex operation are available on all channels. Pin/signal assignments vary with distribution panels, but the following modem controls are available on all distribution panels:

- Carrier Detect

- Data Terminal Ready

- Ring Indicator

On the CP22 and CP24/B, the following additional modem control signals are available on the first four channels:

- Request to Send

- Clear to Send

- Data Set Ready

Consult your distribution panel technical manual for more details on the port interface signal assignments.

### 2.1 OVERVIEW

This section contains general, physical, and environmental specifications for the CS02/H controller module. Specifications for the distribution panels are contained in their technical manuals. Controller specifications are contained in tables, each in its own subsection. The subsections include:

| Subsection | Title                                 |

|------------|---------------------------------------|

| 2.2        | General and Electrical Specifications |

| 2.3        | Physical Specifications               |

| 2.4        | Environmental Specifications          |

#### 2.2 GENERAL SPECIFICATIONS

General specifications for the CS02/H Communications Subsystem are contained in Table 2-1.

Table 2-1. CS02/H General Specifications

| Parameter                                    | Description                                                                                                                                                                                     |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Emulation</b>                             | Provides complete functional emulation of one DEC DH11 multiplexer and partial emulation of the associated DM11 modem control units, or complete functional emulation of two DHV11 multiplexers |

| Operating System Compatibility               | RSX-11M, RSX-11M+, RSTS/E. MicroVMS supported by firmware revision F and higher.                                                                                                                |

| Diagnostic<br>Compatibility<br>DH11<br>DHV11 | ZDHMD0<br>CVDHAA0, CVDHBA0, CVDHCA0                                                                                                                                                             |

| Number of Channels                           | 16                                                                                                                                                                                              |

| Throughput Rate                              | 50,000 characters per second                                                                                                                                                                    |

continued on next page

# General Specifications

Table 2-1. CS02/H General Specifications (continued)

| Parameter                               | Description                                                                                                                                  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Silo                            | 64-character FIFO buffer for each DH11, expandable to 256, interrupt programmable for any FIFO fill level; 256-character FIFO for each DHV11 |

| Transmission Modes                      | Full-duplex, Half-duplex                                                                                                                     |

| Transmission Speeds                     | 50, 75, 110, 134.5, 150, 200, 300, 600, 1200, 1800, 2400, 4800, 9600, 19200, 38400 bps                                                       |

| Character Formats                       | Character lengths: 5 to 8 bit Stop bits: 1, 1.5, or 2 Parity: odd, even, or none                                                             |

| Modem Status                            | CD, Ring, CTS, DSR                                                                                                                           |

| Modem Control                           | RTS, DTR                                                                                                                                     |

| Emulex Distribution<br>Panels Supported | CP22<br>CP24<br>CP24/B<br>CP25                                                                                                               |

| Indicators                              | On Line<br>Fault<br>Activity                                                                                                                 |

| Option Switches                         | DIP switches for selection of controller options                                                                                             |

| CPU Interface                           | Standard Q-Bus interface. One bus load for both DH11 and DM11, or one bus load for DHV11.                                                    |

| DMA Address Range                       | 0 - 4.19 megabytes                                                                                                                           |

| DMA Transfer                            | 16-bit word with parity check                                                                                                                |

| Device Address                          | Switch selectable to cover most DEC-defined addresses                                                                                        |

continued on next page

| Table 2-1. | CS02/H | General | Specifications | (continued) |

|------------|--------|---------|----------------|-------------|

|------------|--------|---------|----------------|-------------|

| Parameter      | Description                                                                                                 |

|----------------|-------------------------------------------------------------------------------------------------------------|

| Vector Address | Switch selectable to cover most DEC defined vector addresses.                                               |

| Priority Level | BR5 for DH11 BR4 for DM11 BR5 for DHV11 (firmware Rev E and below) BR4 for DHV11 (firmware Rev F and above) |

| Electrical     |                                                                                                             |

| Power          | +5 VDC + 5%, 6.2 amps (typical) +12 VDC + 5%, 0.5 amps (typical)                                            |

## 2.3 PHYSICAL SPECIFICATION

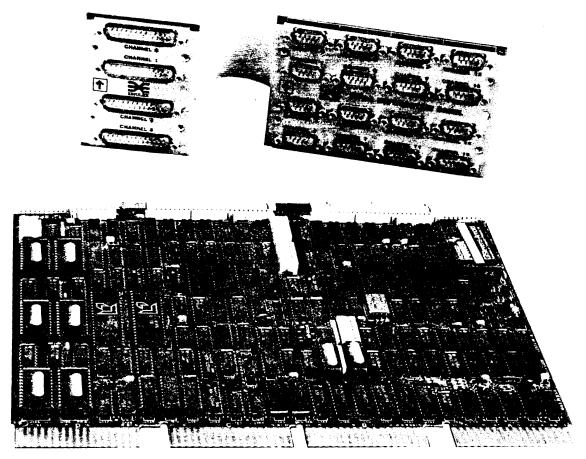

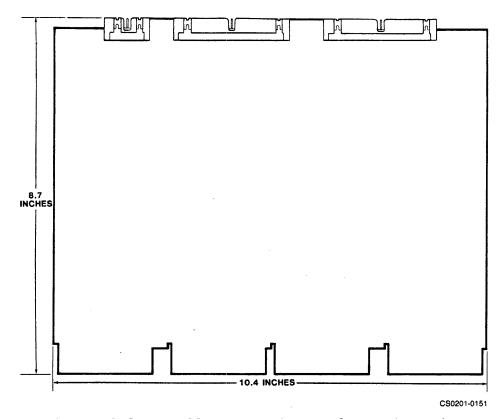

Table 2-2 contains the physical specifications for the CC02 controller module. Figure 2-1 depicts the CC02 Controller Module PCBA.

Table 2-2. CC02 Controller Module Physical Specifications

| Parameter          | Description                                      |

|--------------------|--------------------------------------------------|

| Packaging          | Single quad-sized, four-layer PCBA               |

| Dimensions         | 10.4 inches x 8.7 inches                         |

| Shipping Weight    | 4 pounds                                         |

| Connectors         |                                                  |

| Q-Bus              | Standard DEC PCBA edge connectors                |

| Distribution Panel | One 16-pin and two 50-pin male header connectors |

Figure 2-1. CC02 Controller Module Dimensions

## 2.4 ENVIRONMENTAL SPECIFICATIONS

Table 2-3 contains environmental specifications for the CC02 Controller Module.

Table 2-3. CC02 Controller Module Environmental Specifications

| Parameter             | Description                                                                             |

|-----------------------|-----------------------------------------------------------------------------------------|

| Operating Temperature | 10°C (50°F) to 40°C (104°F)                                                             |

|                       | Maximum temperature is reduced 1.8°C per 1000 meters (1°F per 1000 feet) altitude       |

| Relative Humidity     | 10% to 90% with a maximum wet bulb of 28°C (82°F) and a minimum dewpoint of 2°C (3.6°F) |

| Cooling               | ll cubic feet per minute                                                                |

| Heat Dissipation      | 70 BTU per hour                                                                         |

#### 3.1 OVERVIEW

This section is designed to help you plan the installation of your CS02/H Communications Subsystem. Taking a few minutes and planning the configuration of your subsystem before beginning its installation will result in a smoother installation with less system down time. As a planning tool, this section contains discussions of some of the practical matters that need to be considered before you begin your installation.

This section contains CS02/H application examples and configuration procedures. The subsections include:

| Subsection | Title                       |

|------------|-----------------------------|

| 3.2        | Configurations              |

| 3.3        | Application Examples        |

| 3.3        | Q-Bus Addresses and Vectors |

The procedures contained in these subsections will ensure that you get the most from your CS02/H Communications Subsystem.

### 3.1.1 Q-BUS ADDRESS CONVENTION

The Q-Bus addresses used in this manual are for a 22-bit Q-Bus. 18-bit addressing subtract 17000000g to obtain the desired address.

## 3.1.2 CONFIGURATION DEFINED

As used in the computer industry, the term configuration is generally used in reference to the physical and logical arrangement of a system, or put another way, the manner in which the parts of a system relate to one another.

When used this way, the word configuration has quite a number of implications: size (capacity, speed, bandwidth), cabling (what is hooked to what), logical arrangement (which functions are combined on which components), location (bus slot, bus address, vector, unit address), and so on.

### Configurations

Many of these factors can be affected by the user, either through the use of switches or by cabling the system one way instead of another. In other words, the configuration, and thus the function, of a system is defined and determined by the user.

#### 3.2 CONFIGURATIONS

The CS02/H is designed to provide 16 asynchronous communications channels. The CS02/H emulates either a DEC DH11 with associated DM11 modem control, or two DEC DHV11s. The CS02/H Subsystem allows a certain number of variables. The subsections below describe the functions and options on each distribution panel that should be considered before configuring the CS02/H Subsystem.

#### 3.2.1 DISTRIBUTION PANELS

Different distribution panels have different features, and which distribution panel you use depends on what applications you are planning to use the CS02/H for.

Three Emulex distribution panels can be used with the CS02/H: the CP22, CP24, and CP25. There are several main differences among them:

- The CP24 is the only panel that mounts in a Micro/PDP-11 or MicroVAX chassis.

- The CP22 and CP24/B offer full modem controls on the first four channels. The CP25 supports partial modem control on all channels.

- The CP25 offers an RS-422-A interface as an option on each port. The CP22 uses an RS-232-C interface. If you are planning to operate your terminals more than a few hundred feet from the distribution panel, the RS-422-A option is particularly useful. To use this option, your terminals must have RS-422-A interface circuits or you must use an RS-422-A converter, such as Emulex's CV422.

## 3.2.1.1 CP22 Distribution Panel

The CP22 is a passive, FCC-compliant distribution panel which can be mounted directly in DMF32-compatible CPU cabinets or rack-mounted on RETMA rails. It provides an RS-232-C interface on all ports.

Channels zero through three on the CP22 may be individually reconfigured to to provide an RS-423 interface. The CP22 Technical Manual describes the procedure for making this change.

Channels zero through three also provide the additional modem signals necessary for half-duplex operation.

## 3.2.1.2 CP24 and CP24/B Distribution Panels

The CP24 is a passive, FCC-compliant distribution panel which can be mounted in a Micro/PDP-11 or MicroVAX chassis. It uses 9-pin connectors and provides an RS-232-C interface at each of its 16 ports.

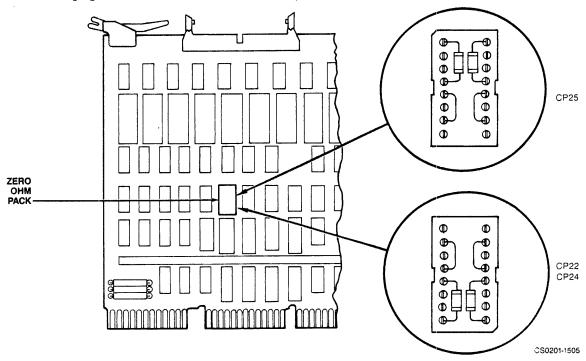

The CP24/B is an optional panel and is used in addition to the CP24. The CP24/B contains four 25-pin subminiature connectors that replace the first four channels of the CP24. If it is used, the first four channels provide full modem control support (the CP24 by itself provides partial modem support on all 16 ports).

Channels zero through three on the CP24 may be individually reconfigured to to provide an RS-423 interface. The CP24 Technical Manual describes the procedure for making this change.

### Application Examples

## 3.2.1.4 CP25 Distribution Panel

The CP25 is an active, FCC-compliant distribution panel which can be directly mounted in DMF32-compatible CPU cabinets or rack-mounted on RETMA rails. It provides either an RS-232-C or an RS-422-A interface at each port. Each port can be configured independently.

The RS-422-A interface allows higher transmission speeds and much longer cable lengths than the RS-232-C interface. For example, at 9600 baud the maximum practical cable length with the RS-232-C interface is 250 feet, and performance is guaranteed only up to 50 feet. The RS-422-A interface, however, allows cable lengths as long as 4000 feet with every transmission speed supported by the CS02/H.

#### 3.3 APPLICATION EXAMPLES

The CS02/H Communications Subsystem has several applications. Some examples are presented below.

- Example 3-1. Figure 3-1 illustrates a typical LSI-11 application with a half-duplex remote line. This subsystem consists of the CC02 Controller Module and the CP22 Distribution Panel. The two components are mounted in a DEC LSI-11 computer. A half-duplex modem is connected to CH.0 of the CP22 Distribution Panel. Terminals and printers are connected to the remaining 15 channels of the panel.

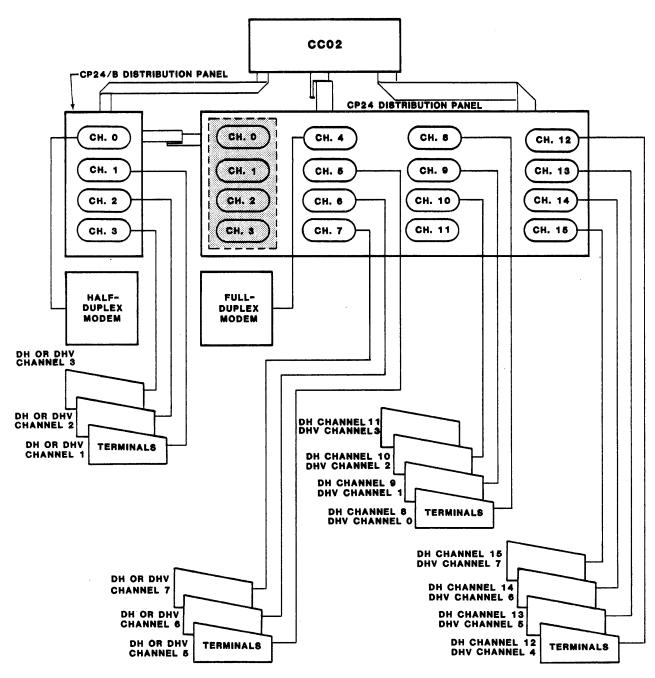

- Example 3-2. Figure 3-2 illustrates a typical Micro/PDP-11 or MicroVAX application with a full- and half-duplex remote line. This subsystem consists of the CC02 Controller Module, the CP24 Distribution Panel and the optional CP24/B Distribution Panel. The three components are mounted in a DEC Micro/PDP/VAX computer. A half-duplex modem is connected to Channel 0 of the CP24/B Distribution Panel. A full-duplex modem is connected to Channel 4 of the CP24 Distribution Panel. Terminals and printers are connected to Channels 1 through 3 of the CP24/B Distribution Panel and to Channels 5 through 15 of the CP24 Distribution Panel. Channels 0 through 3 on the CP24 Distribution Panel are shaded to indicate that they are not used when the CP24/B Distribution Panel is used.

Figure 3-1. An LSI-11 Application

NOTE: CH.O THROUGH CH.4 OF THE CP24 ARE SHADED TO INDICATE THEY ARE NOT USED WHEN THE CP24/B IS USED.

CS0201-0172

Figure 3-2. A Micro/PDP/VAX Application

### 3.4 Q-BUS ADDRESSES AND VECTORS

The CS02/H interfaces directly with the DEC host computer's Q-Bus backplane. The CS02/H performs one DH11/DM11 emulation, or two DHV11 emulations. The DHll emulation uses a block of eight addresses which are selected from a pool of floating addresses. Each DMll uses a block of two bus addresses. Addresses for DMll-type devices are assigned to a specific range. The DHVll emulation uses a block of eight addresses which are selected from a pool of floating addresses in the Q-Bus I/O page.

The DH11 emulations require two vector addresses; each DM11 emulation uses only one vector address. The DHVll emulation requires two vector addresses. The vector addresses for all types of devices are selected from a pool of floating vector addresses assigned by the user according to an algorithm that has been defined by DEC.

The following discussion presents the algorithm for assigning floating bus address space and vectors for RSTS/E, RSX-llM, and MicroVMS. DMll bus addresses are discussed in subsection 4.3.2.1.

#### 3.4.1 DETERMINING THE BUS ADDRESS FOR USE WITH AUTOCONFIGURE

The term Autoconfigure refers to a software utility that is run when the computer is bootstrapped. This utility finds and identifies I/O devices in the I/O page of system memory.

Addresses for those devices not assigned fixed numbers are selected from the floating address space (17760010g - 17763776g) of the Q-Bus input/output (I/O) page. This means that the presence or absence of floating devices will affect the assignment of addresses to other floating-address devices. Similarly, many devices have floating interrupt vector addresses. According to the DEC standard, vectors must be assigned in a specific sequence and the presence of one type of device will affect the correct assignment of vectors for other devices.