## CS11/F1

(DMF32 COMPATIBLE)

COMMUNICATIONS MULTIPLEXER

TECHNICAL MANUAL

Copyright (C) 1983 Emulex Corporation

The information in this manual is for informational purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in the manual.

Printed in U.S.A.

## TABLE OF CONTENTS

| Section | 1                                                                                                  | INTRODUCTION                                                                                                                                                                                                             |                                                                           |

|---------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|         | 1.1<br>1.2<br>1.2.1<br>1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.4.1                            | SCOPE OVERVIEW General Description FEATURES Microprocessor Design Packaging Configuration Flexibility Self-Test FUNCTIONAL COMPATIBILITY Differences Between the CS11/F1 and the DMF32 Diagnostics Operating Systems     | 1-1<br>1-1<br>1-1<br>1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2               |

| Section | 2                                                                                                  | GENERAL DESCRIPTION                                                                                                                                                                                                      |                                                                           |

|         | 2.2.1<br>2.2.1.1<br>2.2.1.2<br>2.2.1.3<br>2.2.1.4<br>2.2.1.5<br>2.2.2<br>2.2.2.1<br>2.2.2.2        | Switches PROMs RAM Buffer Distribution Panel Line Adapter Boards Interface Board                                                                                                                                         | 2-1<br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-4<br>2-4<br>2-4<br>2-4<br>2-4 |

|         | 2.3<br>2.3.1.1<br>2.3.1.2<br>2.3.1.3<br>2.3.1.4<br>2.3.1.5<br>2.3.2<br>2.3.2.1<br>2.3.3<br>2.3.3.1 | INTERFACES Unibus Unibus Starting Addresses Interrupt Vector Addresses BR (Interrupt) Priority Level DCLO and INIT Signals DMA Transfers CAll/H Line Adapter CAll/H Line Adapter CAll/C Line Adapter CAll/C Line Adapter | 2-6<br>2-6<br>2-6<br>2-6<br>2-6<br>2-8<br>2-8<br>2-9<br>2-9               |

|         | 2.3.3.1<br>2.4<br>2.4.1<br>2.4.1.2<br>2.4.1.3<br>2.4.1.4<br>2.4.1.5<br>2.4.2                       | FUNCTIONAL DESCRIPTION  Receiver Operation  UART  Receiver Scanner  Silo Operation  Half-Duplex Operation  Received Character Distortion  Transmitter Operation  UART                                                    | 2-10<br>2-10<br>2-10<br>2-10<br>2-10<br>2-11<br>2-11<br>2-11              |

|         | 2.4.3            | Modem Control                                               | 2-11         |

|---------|------------------|-------------------------------------------------------------|--------------|

| Section | 3                | CONTROLLER REGISTERS                                        |              |

|         | 3.1<br>3.1.1     | MULTIPLEXER OPERATION Initial Operation                     | 3-1<br>3-1   |

|         | 3.1.2            | Parameter Initialization                                    | 3-1          |

|         | 3.1.3            | Transmission                                                | 3-1<br>3-1   |

|         | 3.1.3.1          | SILO Mode<br>NPR (DMA) Mode                                 | 3-2          |

|         | 3.1.3.2<br>3.1.4 | Receiver Operation                                          | 3-2          |

|         | 3.2              | CONTROLLER REGISTERS                                        | 3-4          |

|         | 3.2.1            | Configuration CSR (CONFIG.REG)                              | 3-5          |

|         | 3.2.2            | Diagnostic CSR (MAINT.REG)                                  | 3-5          |

|         | 3.2.3            | Synchronous Receive CSR (SY.RX.CSR)                         | 3-5          |

|         | 3.2.4            | Synchronous Transmit CSR (SY.TX.CSR)                        | 3-5          |

|         | 3.2.5            | Synchronous Miscellaneous Register (SY.MISC.REG)            | 3-6          |

|         | 3.2.6            | Synchronous Indirect Register (SY.IND.REG)                  | 3-6          |

|         | 3.2.7            | Aysnchronous CSR (AS.CSR)                                   | 3-6          |

|         | 3.2.8            | Asynchronous Line Parameter Register (AS.LINE.PAR.REG)      |              |

|         | 3.2.9            | Asynchronous Receiver Buffer (AS.RX.BUF)                    | 3-10         |

|         | 3.2.9.1          | Receiver Buffer (Read)                                      | 3-11         |

|         | 3.2.9.2          | Receiver Buffer (Write)                                     | 3-12         |

|         | 3.2.10           | Indirect Registers                                          | 3-13<br>3-13 |

|         | 3.2.10.1         | Indirect Register 0 (IND.REG0) (Read)                       |              |

|         | 3.2.10.2         | (Write)                                                     | 3-14         |

|         | 3.2.10.3         | Indirect Register 8 (IND.REG8)                              | 3-15         |

|         | 3.2.10.4         | Indirect Register 10 (IND.REG10)                            | 3-18<br>3-18 |

|         | 3.2.10.5         | Indirect Register 18 (IND.REG18)                            | 3-19         |

|         | 3.2.11           | Line Printer CSR (LP.CSR)<br>Line Printer Indirect Register | 3-19         |

|         | 3.2.12           | (LP.IND.REG)                                                | 0            |

|         | 3.2.13           | DR11 CSR (DR.CSR)                                           | 3-19         |

|         | 3.2.14           | DR11 Output Buffer (DR.OUT.BUF)                             | 3-19         |

|         | 3.2.15           | DR11 Input Buffer (DR.IN.BUF)                               | 3-19         |

|         | 3.2.16           | DR11 Indirect Register (DR.IND.REG)                         | 3-19         |

|         | 3.3              | MULTIPLEXER MAINTENANCE                                     | 3-19         |

|         | 3.3.1            | Maintenance Features                                        | 3-19         |

|         | 3.3.1.1          | Relationship Between Maintenance                            | 3-20         |

|         |                  | Modes and Modem Signals                                     |              |

| Section | 4                | INSTALLATION                                                |              |

|         | 4.1              | INSPECTION                                                  | 4-1          |

|         | 4.2              | PREPARE THE CPU                                             | 4-1          |

|         | 4.3              | UPGRADING A CS11/XX TO A CS11/F1                            | 4-2          |

|         | 4.3.1            | Exchanging Emulation PROMS                                  | 4-2<br>4-2   |

|          | 4.3.3    | Address PROMS                                                | 4-4  |

|----------|----------|--------------------------------------------------------------|------|

|          | 4.3.4    | RAM Buffer                                                   | 4-2  |

|          | 4.4      | CONTROLLER BOARD SETUP                                       | 4-2  |

|          |          |                                                              | 4-4  |

|          | 4.4.1    | Number of DMF32 Emulations                                   | _    |

|          | 4.4.2    | Unibus Starting Address                                      | 4-4  |

|          | 4.4.2.1  | Determining the DMF32 CSR Address for Use with Autoconfigure | 4-4  |

|          | 4.4.2.2  | DMF32 CSR Address and the CONNECT                            | 4-6  |

|          |          | Command                                                      |      |

|          | 4.4.2.3  | Programming the CSR Address into the CS11/F1                 | 4-6  |

|          | 4.4.3    | Interrupt Vector Address                                     | 4-7  |

|          | 4.4.4    | Controller Options                                           | 4-7  |

|          |          |                                                              | 4-7  |

|          | 4.4.4.1  | CTS Flow Control Enable                                      |      |

| ,        | 4.4.4.2  | Force two Stop Bits                                          | 4-8  |

|          | 4.4.4.3  | Force Local Loopback                                         | 4-8  |

|          | 4.5      | CP11 DISTRIBUTION PANEL CONFIGURATION                        | 4-8  |

|          | 4.5.1    | Panel Numbering                                              | 4-8  |

|          | 4.5.2    | DSR Modem Control Option                                     | 4-8  |

|          |          |                                                              | 4-8  |

|          | 4.5.3    | CTS Flow Control                                             |      |

|          | 4.5.4    | International Power Supply                                   | 4-10 |

|          |          | Conversion Instructions                                      |      |

|          | 4.6      | LINE ADAPTER CONFIGURATION/INSTALLATION                      | 4-10 |

|          | 4.6.1    | Compatability Mode Selection                                 | 4-11 |

|          | 4.6.2    | CAll Option Selection                                        | 4-12 |

|          |          |                                                              | 4-12 |

| •        | 4.6.2.1  | Pinning Assignment Options                                   |      |

|          | 4.6.3    | CAll/C Option Selection                                      | 4-14 |

|          | 4.7      | CP11 DISTRIBUTION PANEL INSTALLATION                         | 4-16 |

|          | 4.8      | CC11 CONTROLLER INSTALLATION                                 | 4-16 |

|          | 4.8.1    | SPC Slot Selection                                           | 4-16 |

|          |          | NPG Signal Jumper                                            | 4-16 |

|          | 4.8.2    |                                                              | 4-16 |

|          | 4.8.3    | Controller Mounting                                          |      |

|          | 4.9      | CABLING                                                      | 4-16 |

|          | 4.9.1    | Controller to Distribution Panel                             | 4-16 |

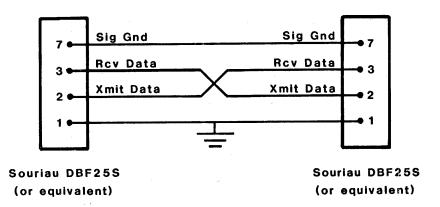

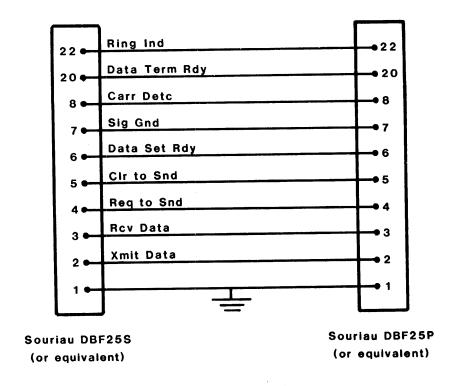

|          | 4.9.2    | CAll/H Line Adapter to External Device                       | 4-17 |

|          | 4.9.2.1  | Cable Types                                                  | 4-17 |

|          |          |                                                              | 4-20 |

|          | 4.9.2.2  | Cable Lengths                                                |      |

|          |          | CAll/C Line Adapter to External                              | 4-20 |

|          | 4.9.3.1  | Cable Type                                                   | 4-20 |

|          | 4.9.3.2  | Cable Length                                                 | 4-21 |

|          | 4.10     | VERIFICATION                                                 | 4-21 |

|          | 4.10.1   | Self-Test                                                    | 4-21 |

|          | 4.10.2   | Register Examination                                         | 4-22 |

|          |          |                                                              | 4-22 |

| 1        |          | Line Adapter Wrap-Around Test                                |      |

|          | 4.10.3.1 |                                                              | 4-22 |

|          | 4.10.3.2 | CAll/C Tests                                                 | 4-23 |

|          | 4.10.4   | Diagnostics                                                  | 4-25 |

| Appendix | A        | CONTROLLER OPTION SWITCHES                                   |      |

|          | A.1      | CC11 CONTROLLER PCBA                                         | A-1  |

|          | A. 2     | CP11 DISTRIBUTION PANEL                                      | A-2  |

|          |          |                                                              | A-3  |

|          | A.2      | CAll/H LINE ADAPTER                                          | n-J  |

|          |          |                                                              |      |

## LIST OF TABLES

| Table No.  | Title                                                    |      |

|------------|----------------------------------------------------------|------|

| Table 1-1  | Differences Between the CS11/F1 and the DMF32            | 1-3  |

| Table 1-2  | CS11/Fl Subsystem Specifications                         | 1-4  |

| Table 2-1  | DMF32 Unibus Starting Addresses                          | 2-6  |

| Table 2-2  | SPC Unibus Connections                                   | 2-7  |

| Table 2-3  | CAll/H Interface Connector                               | 2-8  |

| Table 3-1  | Split Speed Example                                      | 3-9  |

| Table 3-2  | CS11/F1 Baud Rates                                       | 3-9  |

| Table 4-1  | Number of DMF32 Emualtions (CP11<br>Distribution Panels) | 4-3  |

| Table 4-2  | SYSGEN Device Table                                      | 4-6  |

| Table 4-3  | Unibus Starting Address Selection                        | 4-7  |

| Table 4-4  | CTS Flow Control Enabling                                | 4-10 |

| Table 4-5  | Line Adaptor Type ID Codes                               | 4-12 |

| Table 4-6  | RS-232-C Cable Lengths                                   | 4-19 |

| Table 4-7  | 20 mA Current Loop Cable Lengths                         | 4-21 |

| Table A-1  | Option Switches                                          | A-1  |

| Table A-2  | Option Switches                                          | A-1  |

| Table A-3  | Distribution Panel Select                                | A-2  |

| Table A-4  | Controller Starting Address                              | A-2  |

| Table A-5  | Modem Control Option Selection                           | A-2  |

| Table A-6  | Line Test Switch                                         | A-3  |

| Table A-7  | Panel Type Code                                          | A-4  |

|            | LIST OF FIGURES                                          |      |

|            |                                                          |      |

| Figure No. | <u>Title</u>                                             |      |

| Figure 2-1 | CS11/F1 Block Diagram                                    | 2-3  |

| Figure 2-2 | CC11 Controller Board and                                | 2-5  |

| 119010     | CPll Distribution Panel                                  |      |

| Figure 3-1 | DMF32 Control and Status Registers                       | 3-3  |

| Figure 3-2 | DMF32 Indirect Registers                                 | 3-4  |

| Figure 4-1 | CC11 Controller                                          | 4-5  |

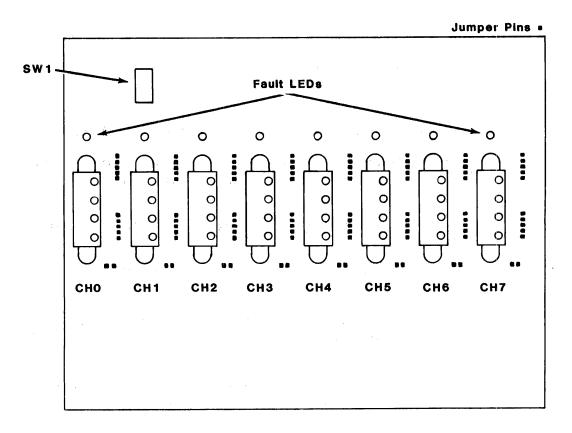

| Figure 4-2 | CPll Distribution Panel                                  | 4-9  |

| Figure 4-3 | CAll/H Line Adapter                                      | 4-13 |

| Figure 4-4 | CAll/C Line Adapter                                      | 4-13 |

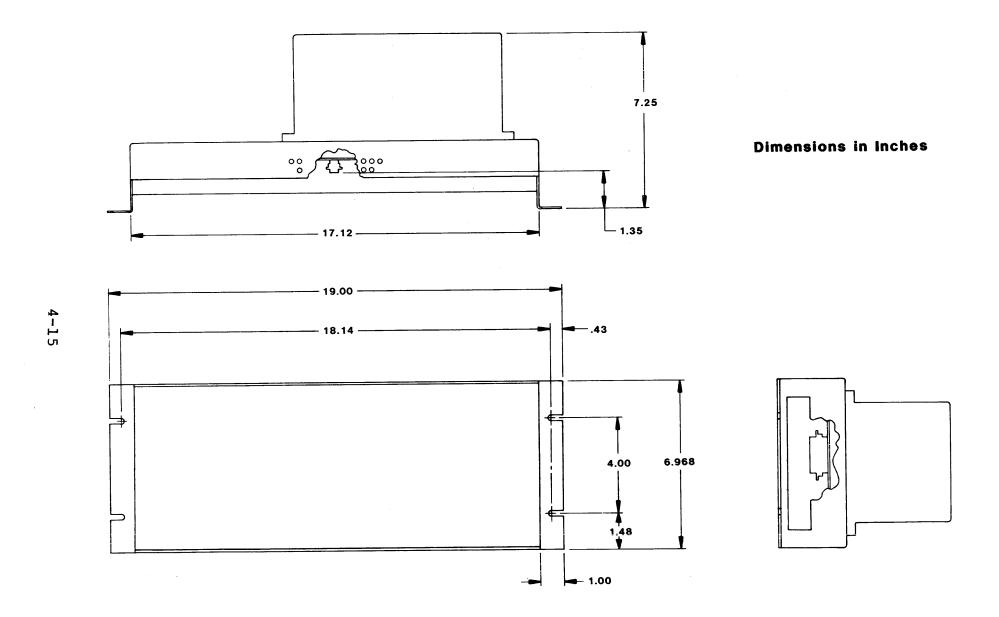

| Figure 4-5 | CPll Distribution Panel Physical                         | 4-15 |

| •          | Dimensions                                               |      |

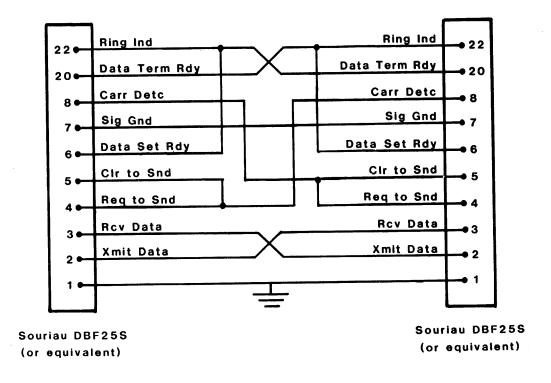

| Figure 4-6 | Terminal Cable Schematic                                 | 4-17 |

| Figure 4-7 | Modem Cable Schematic                                    | 4-18 |

| Figure 4-8 | Null-Modem Cable Schematic                               | 4-18 |

#### 1.1 SCOPE

This manual provides information related to the capabilities, design, installation, and use of the CSll/Fl communications multiplexer. In addition, this manual provides diagnostic and application information.

#### 1.2 OVERVIEW

## 1.2.1 General Description

The CS11/F1 Communications Multiplexer connects up to 48 asynchronous serial communication lines with individually programmable parameters to the VAX-11 computers manufactured by Digital Equipment Corporation.

The CS11/F1 emulates 2, 4 or 6 DEC DMF32 Asynchronous 8-Line Multiplexers with modem control on all lines. The subsystem consists of a CC11/F controller board and 1 to 3 CP11 Distribution Panels, each containing two CA11 line adapter boards. The CC11 is a single hex-size board which plugs directly into the VAX Unibus. The line adapter boards contain the line connection and the line circuitry which interface the serial communication line with the parallel data cable to the communications controller.

#### 1.3 FEATURES

#### 1.3.1 Microprocessor Design

The CS11/F1 design incorporates an 8-bit high performance bipolar microprocessor to perform all controller functions. The microprocessor approach provides for a reduced component count, high reliability, easy maintainability, and most importantly the ability to perform an emulation of the equivalant DEC controller. The Emulex controllers achieve functional capability beyond that of the DEC controllers which they emulate, by providing enhancement features such as built-in self-test during power-up and line-loop test.

#### 1.3.2 Packaging

The CCll/F controller is constructed on a single hex-size PC board which plugs directly into the VAX Unibus chassis or an expansion chassis. A single 34-pin flat cable daisy-chains to a maximum of three CPll distribution panels which contain the line adapter circuitry. The CAll line adapter boards are plugable modules in eight line groups.

## 1.3.3 Configuration Flexibility

Each communications controller emulates up to six eight-line DMF32s for a maximum of 48 lines. Various types of line adapters may be mixed in eight line groups.

### 1.3.4 Self-Test

The controller incorporates an internal self-test routine which is executed upon power-up. This test exercises all parts of the microprocessor, the on-board memory, and the individual line adapters. Although this test does not completely test all circuitry, successful execution indicates a very high probability that the controller and the line adapters are operational. If the controller fails the self-test, it leaves the Fault LED ON and the controller cannot be addressed from the CPU.

The power-up self-test also does a loop test on each of the line adapter UART circuits. In addition it is possible to perform either an internal or external loop-back test on groups of eight circuits while the CS11/F1 is online.

## 1.4 FUNCTIONAL COMPATIBILITY

## 1.4.1 Differences Between the CS11/F1 and the DMF32

Emulex's DMF32 emulation, the CS11/F1, provides only the asynchronous portion of the DMF32. There are some other minor differences between the CS11/F1 and the DMF32. Those differences are summarized in Table 1-1.

## 1.4.2 Diagnostics

The CS11/F1 executes the following standard DEC DMF32 diagnostics:

EVDLC Asynchronous Multiplexer Diagnostic

## 1.4.3 Operating Systems

The CS11/F1 communications multiplexer is compatible with DEC's VMS operating system, version 3.0 and above, without modification.

Table 1-1

Differences Between the CS11/F1 and the DMF32

| CS11/F1                                                                               | DMF32                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16, 32, or 48                                                                         | Eight                                                                                                                                                                                  |

| All lines have DHll<br>Compatible Modem<br>Control (see Table<br>2-3 for differences) | Only two lines have<br>Full Modem Control                                                                                                                                              |

| 3600 and 7200 baud not supported                                                      | 16 rates - 50 to<br>19.2k                                                                                                                                                              |

| Each 16 line group must have the same receive rate.                                   | Independent split rate on 2 lines                                                                                                                                                      |

| No                                                                                    | Yes                                                                                                                                                                                    |

| No                                                                                    | Yes                                                                                                                                                                                    |

| No                                                                                    | Yes                                                                                                                                                                                    |

|                                                                                       | 16, 32, or 48  All lines have DHll Compatible Modem Control (see Table 2-3 for differences)  3600 and 7200 baud not supported  Each 16 line group must have the same receive rate.  No |

## Table 1-2 CSll/Fl Subsystem Specifications

| Characteristic                  | Specification                                                                                               |

|---------------------------------|-------------------------------------------------------------------------------------------------------------|

| CC11/F CONTROLLER               |                                                                                                             |

| Design                          | High-speed bipolar microprocessor implementation of all CS11 functional operations.                         |

| Function                        | Provides complete functional emulation of up to six DMF32 asynchronous multiplexers.                        |

| Software Compatibility          | Diagnostics: EVDLC Operating Systems: VAX/VMS, V3.0 and above.                                              |

| No. of Distribution Panels      | 1 to 3                                                                                                      |

| No. of Lines                    | 8 to 48                                                                                                     |

| Throughput                      | 50,000 characters per second total                                                                          |

| Distribution Panel<br>Interface | Eight-bit bidirectional data bus with necessary addressing and control in a single 34-conductor flat cable. |

| Receive Silo                    | 48-character FIFO buffer for each functional 8-channel DMF32.                                               |

| CPU Interface                   | Standard Unibus SPC interface. One bus load for DMF32.                                                      |

| DMA Address Range               | 0 - 128K words                                                                                              |

| DMA Transfer                    | 16-bit word with parity check                                                                               |

| DMA Transfer                    | 16-bit word with parity check                                                                               |

# Table 1-2 (Cont.) CS11/Fl Subsystem Specifications

Device Address Selectable with switches and PROMs

to cover all DEC-defined DMF32

assignments.

Vector Address Operating system programable for

DMF32

Priority Level BR5

Indicator Controller self-test fault/activity

indicator

Option Switches DIP switches for selection of

controller options.

Packaging Single hex-size two layer printed

circuit board

Power 5v + - 5%, 4 amps.

CP11 DISTRIBUTION PANEL

Configuration Seven inch high panel for two

8-channel line adapters, including

power supply and cable interface.

Dimensions 7" high x 19" wide x 7" deep

Weight 16 lbs.

Power Self-contained supply, 50-60 Hz.

115/230 vac, 35 watts

# Table 1-2 (Cont.) CS11/Fl Subsystem Specifications

| CAI | 1/5  | LINE     | בחב י | PTER  |

|-----|------|----------|-------|-------|

| CAT | T/ E | I LITINE | , aur | TETRI |

Configuration Two-sided PCB measuring 6-1/2" x 8"

which plugs into CPll Distribution

Panel.

Interface RS-232-C, with DEC DMF32-compatible

modem control.

Connectors Standard EIA RS-232-C, 25-pin male

connector.

Indicators Fault LED per line.

Transmission Modes Half-duplex, full-duplex

Line Formats Character lengths: 5-8 bits

Stop bits: 1, 2

Parity: odd, even, none

Data Rates 50, 75, 110, 134.5, 150, 300, 600,

1200, 1800, 2000, 2400, 4800, 9600,

19200 baud.

Distortion Transmitter: less than 2%

intersymbol

Receiver: up to 43% intersymbol distortion and speed variation

Modem Control Signals To: RTS, DTR, Secondary Tx

From: CTS, CD, RI, Secondary Rx (or

DSR)

CAll/C LINE ADAPTER

Configuration Same as CAll/H.

Interface 20 mA current loop.

Connections Four screw posts

Transmission Modes Half-dulpex, full-duplex

Line Formats Same as CAll/H.

Data Rates Same as CAll/H.

Distortion Same as CAll/H.

#### 2.1 ORGANIZATION

The CS11/F1 communications multiplexer consists of two units: the CC11/F Communications Controller and one to three CP11 Distribution Panels which are connected to the controller by a single 34-conductor flat cable.

#### 2.1.1 Controller

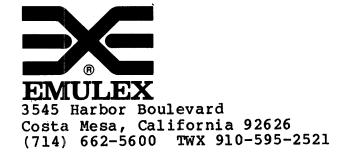

A block diagram showing the major functional elements of the CCll controller is shown in Figure 2-1. The controller is organized around an 8-bit high-speed bipolar microprocessor which performs all controller functions. The ALU and register file portion of the microprocessor are implemented with two 2901 bit slice components. The microinstruction is 48 bits in length and the control memory of 2K words is implemented with 12 2K X 4 PROMs.

A 3K x 8 high-speed RAM holds device registers, silo buffer and working storage for the microprocessor. The RAM is both a source and destination to the internal data bus and is addressed directly and indirectly by the microprocessor.

The Unibus interface consists of a 16-bit bidirectional set of data lines and an 18-bit set of address lines. The Unibus interface is used for programmed I/O, CPU interrupts and NPR data transfers. The microprocessor responds to all programmed I/O and carries out the I/O functions required for the addressed controller register. The microprocessor also controls all NPR read operations and transfers data between the Unibus data lines and the distribution panels.

The line adapter boards with their UART circuits are interfaced to the controller by a 34-conductor cable. This cable contains an 8-bit bidirectional data path, seven address signals and control signals. The Output Data Register holds data going to the line adapters. The Line Address Register holds the address of the line and the distribution panel.

## 2.1.2 Distribution Panel

Each distribution panel contains one or two eight-line CAll Line Adapters and an integral power supply. Two types of line adapters are available. The CAll/H provides a RS-232-C interface with modem control. The CAll/C has a 20 mA current loop interface and does not support modem control. The line adapters provide the data and modem interface circuitry plus the UART circuits which provide the serial to parallel and parallel to serial conversions normally

found in these type devices. The UART also contains the baud rate generator for each line. Data control and status transfers between the line adapters and communications controller are on a parallel byte basis.

#### 2.2 PHYSICAL DESCRIPTION

#### 2.2.1 Controller

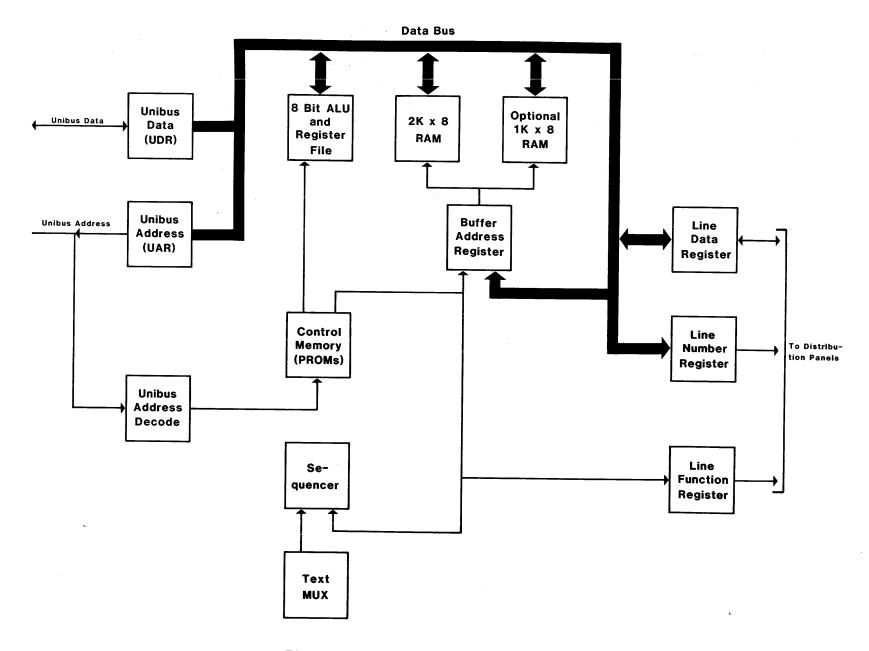

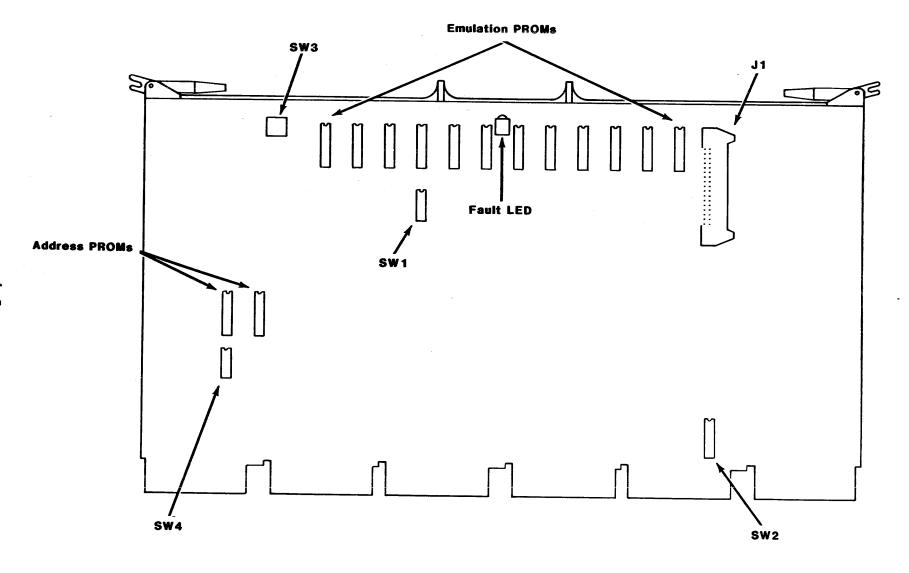

The CCll controller board is designated Part Number CUll10401. The board is shown in Figure 2-2. The board dimensions correspond to the DEC hex-size board. The board is two-sided and contains extractors which interface mechanically with the chassis box into which the controller is to be placed.

#### 2.2.1.1 Connectors

The distribution panels interface to the controller by means of the 34 pin connector Jl located in the upper right hand corner of the board. Connectors J2 and J3 are used for connecting special test equipment for factory test and repair operations and are not intended for use in normal controller operations.

### 2.2.1.2 Indicator

The LED located on the top of the board is a fault indicator which will remain ON after powering-up the controller if a fault is detected during the self-test.

## 2.2.1.3 Switches

There are three DIP switches on the board. In addition there is a four pole switch (SW3) located along the top edge of the board. The use of these four switches is as follows:

- SW1 Controller options

- SW2 Not used.

- SW3 Number of DMF32 emulations (No. of panels) Controller Reset Power-up line test fail override

- SW4 DMF32 Unibus starting address selection

Appendix A contains switch settings for these option switches.

Figure 2-1 CS11 Block Diagram

#### 2.2.1.4 PROMS

The 12 firmware emulation PROMs are located along the top edge of the board. The PROM locations are designated 0 through 11. The number written on top of the PROM IC is the Emulex part number which identifies the unique pattern and revision level of the PROM. These numbers are in the same numerical order as that of the PROM numbers.

The controller makes use of two special PROMs located at U59A and U59B to perform Unibus address decoding.

## 2.2.1.5 RAM Buffer

The six 2148 RAM ICs located at U21, U22, U38, U39, U40 and U41 provide sufficient RAM for configuations of up to 48 lines.

## 2.2.2 Distribution Panel

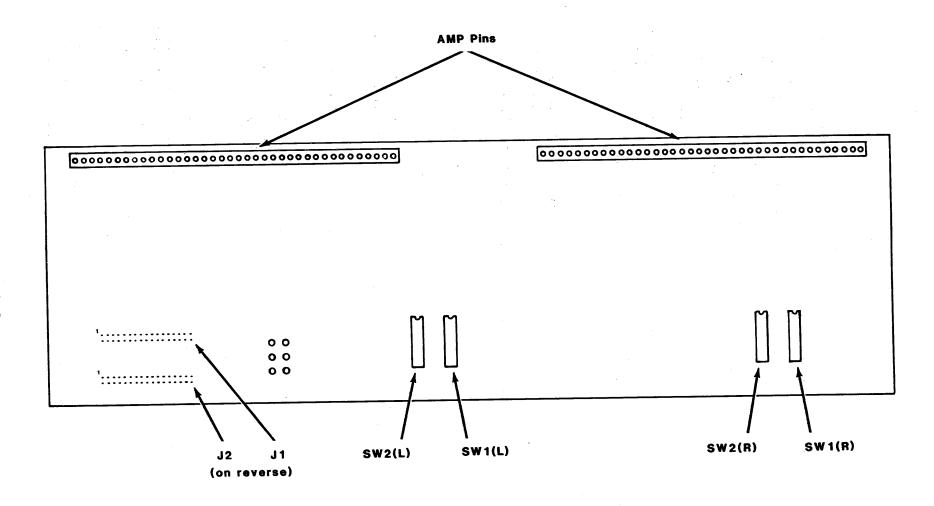

The distribution panels consist of a mechanical assembly, a power supply, an interface board, and one or two line adapter boards with their cover plates. The distribution panel with two CAll Adapter Panels installed is shown in Figure 2-2.

## 2.2.2.1 Line Adapter Boards

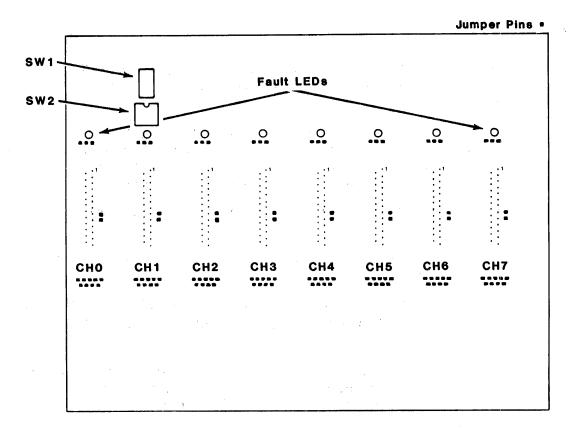

Both the CAll/H and CAll/C line adapter boards measure 6-1/2" x 8" and connect to the Interface Board, located in the back of the panel, through a set of 38 AMP MOD l pins. The CAll/H board contains eight 25-pin male connectors for interfacing to RS-232-C terminals, modems, or like devices. The CAll/C also provides eight lines, but it uses a four-screw terminal strip for interface to 20 mA current loop devices. Both contain UART and level conversion circuitry for each line.

Each line has a small LED indicator mounted directly above the connector which is used to indicate that the internal self-test of the controller has detected a fault for that line adapter. A three position slide switch in the upper left hand corner of the line adapter board is used to enable an internal or external wrap-around test for the eight line group.

## 2.2.2.2 Interface Board

The interface board interfaces the daisy-chain cable and the power supply to the two line adapter boards. it is mounted by a set of screws to the distribution panel. each of the line adapter boards plugs into the amp pins connected to the interface board and in turn is fastened to the panel by four screws. two daisy-chain cable connectors protrude through the back of the panel so that the cable may be continued or terminated if the panel is the last one on the cable. the power supply cable plugs into a connector on the back of the interface board which also protrudes through the panel.

CCll Controller Board and Distribution Panel

#### 2.3 INTERFACES

#### 2.3.1 Unibus

The controller interfaces to the VAX-11 Unibus via a Small Peripheral Controller (SPC) connector. The Unibus consists of 18 address lines and 16 bi-directional data lines, plus control signals for data and interrupt vector address transfer and for becoming bus master. The signal connections of the controller to the Unibus are shown in Table 2-2.

### 2.3.1.1 Unibus Starting Addresses

The Unibus starting address for the first DMF32 is selected by SW4. The available addresses are listed in Table 2-1, below. Instructions for setting SW4 are given in paragraph 4.4.2.3.

Table 2-1

DMF32 Unibus Starting Addresses

| 785*                                                                                             | Addres<br>786                                                                          | ss PROM Nu<br>787                                                                                | mber<br>788                                                                            | 789                                                                                              |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 760340<br>760400<br>760440<br>760500<br>760540<br>760600<br>760640<br>760700<br>760740<br>761000 | 761040<br>761100<br>761140<br>761200<br>761240<br>761340<br>761340<br>761440<br>761440 | 761540<br>761600<br>761640<br>761700<br>761740<br>762000<br>762040<br>762100<br>762140<br>762200 | 762240<br>762300<br>762340<br>762400<br>762440<br>762500<br>762540<br>762640<br>762700 | 762740<br>763000<br>763040<br>763100<br>763140<br>763200<br>763240<br>763340<br>763340<br>763400 |

|                                                                                                  |                                                                                        |                                                                                                  |                                                                                        |                                                                                                  |

<sup>\*</sup>Standard Address PROM

## 2.3.1.2 <u>Interrupt Vector Addresses</u>

The DMF32 interrupt vector addresses are programmed by the operating system during autoconfigure.

#### 2.3.1.3 BR (Interrupt) Priority Level

The two DMF32 interrupts are on BR5.

#### 2.3.1.4 DCLO and INIT Signals

The DCLO or INIT signals perform a controller clear. The self-test is performed only if DCLO has been asserted.

Table 2-2 SPC Unibus Connections

| Column   | С      |      | D    |         | Е    |      | F                         |      |

|----------|--------|------|------|---------|------|------|---------------------------|------|

| Pin      | 1      | 2    | 1    | 2       | 1    | 2    | 1                         | 2    |

| <b>A</b> | NPGIN  | +5V  |      | +5V     |      | +5V  |                           | +5V  |

| В        | NPGOUT |      |      |         |      | -15V |                           | -15V |

| С        | PA     | GND  |      | GND     | A12  | GND  |                           | GND  |

| D        |        | D15  |      | BR7     | A17  | A15  | BBSY                      |      |

| E        |        | D14  |      | BR6     | MSYN | Al6  |                           |      |

| F        |        | D13  |      | BR5     | A02  | Cl   |                           |      |

| H        | Dll    | D12  |      | BR4     | A01  | A00  |                           |      |

| J        |        | D.10 |      |         | SSYN | C0   | NPR                       |      |

| K        |        | D09  |      | BG7IN   | A14  | A13  |                           |      |

| L        |        | D08  | INIT | BG7OUT  | All  |      |                           |      |

| M        |        | D07  |      | BG6 IN  |      |      | INTR                      |      |

| N        | DCLO   | D04  |      | BG6 OUT |      | 8 0A |                           |      |

| P        |        | D05  |      | BG5 IN  | A10  | A07  |                           |      |

| R        |        | D01  |      | BG5OUT  | A09  |      | -                         |      |

| s        | PB     | D00  |      | BG4 IN  |      |      |                           |      |

| т        | GND    | D03  | GND  | BG4OUT  | GND  |      | GND                       | SACK |

| Ū        |        | D02  |      |         | A06  | A04  |                           |      |

| V        | ACLO   | D06  |      |         | A05  | A03  | , acc acc acc acc acc acc |      |

## 2.3.1.5 DMA Transfers

The CS11/F1's transmit buffer can be loaded on a character by character basis by the operating system (Silo mode) or the controller can fetch the data directly from memory (DMA mode) as instructed by the I/O driver. When in the DMA mode, the controller performs word DMA transfer read operations, so as to halve Unibus loading. The controller checks for memory parity errors (if the system has a memory parity controller) which is posted as an NXM error when a parity error is detected.

### 2.3.2 CAll/H Line Adapter

The CAll/H Line Adapter has eight channel interfaces. There are some minor differences between the CSll/Fl and DMF32 interface pinning assignments. See Table 2-3 for the standard Emulex pinning assignments compared to the DMF32. Note also that the CSll/Fl provides modem control on all lines rather than just the first two.

The standard Emulex pinning assignments are those specified for Bell 202C Data Sets (modems).

Electrical signal levels are per EIA RS-232-C specifications. The receiver circuits are implemented with 1489 devices; the transmitter circuits are implemented with 1488 devices.

Table 2-3 CAll/H Interface Connector

| Pin #  |                | Function                | CS11/F1 | DMF32        |

|--------|----------------|-------------------------|---------|--------------|

| Pin 1  |                | Chassis Ground          | Yes     | Yes          |

| Pin 2  | _              | Transmit Data           | Yes     | Yes          |

| Pin 3  | _              | Receive Data            | Yes     | Yesl         |

| Pin 4  |                | Request To Send         | Yes     | Yesl         |

| Pin 5  | -              | Clear To Send           | Yes     | Yes          |

| Pin 6  | _              | Data Set Ready          | No2     | Yes          |

| Pin 7  | -              | Logic Ground            | Yes     | Yes          |

| Pin 8  | _              | Carrier Detector        | Yes     | Yes          |

| Pin ll | · <del>-</del> | Secondary Transmit      | Yes     | No           |

| Pin 12 |                | Secondary Receive       | Yes     | Yes          |

| Pin 15 | _              | Transmit Clock          | Yes     | No           |

| Pin 16 | _              | Receive Data            | No      | Yesl         |

| Pin 17 | _              | Receive Clock           | Yes     | No _         |

| Pin 18 | -              | User Transmit           | $No^2$  | Yes <u>l</u> |

| Pin 19 | _              | Secondary RTS           | No      | Yesl         |

| Pin 20 | _              | Data Terminal Ready     | Yes     | Yes          |

| Pin 22 | -              | Ring Indicator          | Yes     | Yes          |

| Pin 23 | _              | Data Signal Rate Select | No      | Yes          |

| Pin 24 | -              | Transmit Clock Out      | Yes     | No ,         |

| Pin 25 | -              | User Receive            | No      | Yesl         |

|        |                |                         |         |              |

<sup>&</sup>lt;sup>1</sup>The DMF has switches to disconnect these signals.

<sup>2</sup>The CS11 can be configured to provide these signals.

See paragraph 2.3.2.1.

## 2.3.2.1 CAll/H Line Adapter Options

To provide the CS11 with DMF32 compatibility in applications where the host operating system requires direct access to DSR on pin 6, Secondary Receive can be removed from pin 12 and strapped to pin 6. A switch on the distibution panel is set to inform the firmware of the change. See paragraphs 4.5.2 and 4.6.2.1.

To provide the CS11 with DMF32 compatibility in applications where User Transmit (pin 18) is required, Secondary Transmit may be removed from pin 11 and straped to pin 18. See paragraph 4.6.2.1.

The CAll/H interface can be reconfigured to allow use of a number of modems besides the Bell 103. The following is a list of the modem options and their pinning assignments. The changes are effected using wire wrap jumpers. Instructions for implementing the options are in the chapter on installation, paragraph 4.6.2.1. Note that the additional modems may not be supported by DEC software and that custom drivers may have to be written for their implementation.

| Option             | Pinning Assignments                                                |

|--------------------|--------------------------------------------------------------------|

| Standard RS-232-C  | Secondary Receive, Pin 16.<br>Secondary Transmit, Pin 14.          |

| 103 E,G,H,J Modems | Make Busy, Pin 25 = Ready to Send, Pin 4.                          |

| 212 A Modem        | Make Busy, Pin 18 = Ready to Send, Pin 4.                          |

| 811 B              | Receive Signal Element Timing, Pin 17 = Secondary Receive, Pin 12. |

| DSR for Sec RX     | Data Set Ready, Pin 6 = Sec RX, Pin 12.                            |

## 2.3.3 CAll/C Line Adapter

The CAll/C Line Adapter provides a 20 mA current loop interface for each of its eight lines. Modem control is not supported. Both the transmit and receive circuits are optically coupled. This provides common noise rejection that is much greater than RS-232-C and 20 mA interfaces that are not optically coupled. LEDs above each channel's interface connector are used to indicate faulty channels.

## 2.3.3.1 CAll/C Line Adapter Options

There are several options that can be selected using jumpers on the CAll/C. The CAll/C comes from the factory configured with active transmitters and receivers. The transmitters and receivers can be independently reconfigured for passive operation if required. The CAll/C also comes configured from the factory with an open circuit

voltage of 12VDC. A Long Line (L.L.) option with an open circuit voltage of 24VDC can be selected if longer line lengths and/or increased immunity to noise are required. To further increase noise rejection, additional filtering may be strapped to the receiver loop. Implementation of these options is described in the Installation Section, paragraph 4.6.2.

## 2.4 FUNCTIONAL DESCRIPTION

### 2.4.1 Receiver Operation

#### 2.4.1.1 <u>UART</u>

Reception on each line is by means of universal asynchronous receiver/transmitters (UARTs). These MOS/LSI devices perform all the functions of double buffered asynchronous character assembly. The receiver section of the UART samples the line at 16 times the bit rate of the signals to be received on the line. Upon detection of a mark to space transition, the UART counts eight clock pulses and checks the state of the line again. This sampling occurs in the center of the normal start bit. If the sample is a mark, the receiver returns to its idling state, ready to detect another mark to space transition. If the sample is a space, the receiver enters the data entry condition and samples the state of the line at subsequent sample points spaced at multiples of 16 clocks from the center of the start bit. The number of samples taken is determined by the character length information and parity enable programmed in the Line Parameter Register. If parity checking is enabled for the line, the receiver computes the parity of the character received and compares it with the parity sense specified for the reception on the line. If the parity does not check, the parity error bit is

The character length, parity, and number of stop bits that are used by the UART to perform the above operations are stored in each UART from information received from the Line Parameter Register for the associated UART.

#### 2.4.1.2 Receiver Scanner

The receiver section of the UARTs are serviced by a receiver scanner which polls the UARTs for a line which has assembled a received character. The received character and its associated status bits are transferred to the silo, if it is not full. The receiver scanner has priority over the transmitter scanner since the transmitting output is by means of DMA and can be deferred if necessary during conditions of peak activity. In this manner, characters will not be lost, or overrun conditions generated because of the operation of the controller itself.

#### 2.4.1.3 Silo Operation

The silo for each DMF32 is contained in the RAM memory. A 16-bit wide by 49 word deep first-in-first-out (FIFO) storage is

maintained by the controller's microprogram. In effect, a 16-bit word entered at the top of the silo is automatically shifted down to the lowest location that does not already contain an entry. The bottom of the silo is the received character register.

The Asynchronous Receive Buffer is a read-once register that is the bottom location of the silo. Reading AS.RX.BUF extracts the character and its associated status from the silo, and causes all other entries to shift down one word position.

## 2.4.1.4 Half-Duplex Operation

When the line is programmed for half-duplex operation, the receiver is enabled at all times. The receiver is blinded from receiving the characters being transmitted, since the transmitting is done on the same circuit as the receiving. No transmit characters are sent to the silo.

#### 2.4.1.5 Received Character Distortion

Received characters may contain up to 43.75 percent distortion on any bit due to the sampling rate employed in the UART. However, the overall bit rate must be accurate. Specifically, errors in bit rate are cumulative such that when the receiver samples the first stop bit to see if it is a mark, the error accumulated by that time must not exceed 43.75 percent of the bit time. The accumulated error (called "gross start-stop distortion") is calculated as clock error times number of bits plus one, plus the bias distortion of the final character. Assuming the reception of eight data bits, or seven data bits plus parity, 4.8 percent speed distortion would be permissible. Speed distortion (clock error and bit rate error) of any amount causes severe problems to an echo situation. If a terminal sends at a slightly fast rate and the controller sends the exact same characters back to the terminal at the correct rate, the silo will eventually fill with unechoed characters.

#### 2.4.2 Transmitter Operation

#### 2.4.2.1 UART

Transmission on each line is also performed by UARTs. These MOS/LSI devices perform all the necessary functions for double buffered asynchronous character transmission. The transmitter section of the UART holds the serial output at a marking state when idle. When a character has been loaded into the transmitter holding buffer, the UART will generate a start bit within 1/16 of the bit time. The start space is followed by five, six, seven, or eight data bits and the parity bit if parity is selected. Control of the UART is performed by the Line Parameter Register. Data bits are presented to the line least significant bit first.

The minimal number of stop bits depends upon the setting in the Line Parameter Register. If transmission is in five-bit code, either one or two stop bits is transmitted.

If the transmitter's holding register is loaded while a character is being transmitted, the second character will have its start bit transmitted immediately at the end of the preceding character's stop bits.

## 2.4.3 Modem Control

The line interface board provides level conversion for all modem control lines. The output control functions are: Terminal Ready, Request To Send, and Secondary Transmit. The received control functions are: Clear To Send, Carrier, Secondary Receive and Ring.

## 3.1 MULTIPLEXER OPERATION

## 3.1.1 Initial Operation

Initially, on power up (DCLO negated) or after INIT or Master Reset, a self-diagnostic is run during which the internal buses and components of the option are verified before jumping into the main microcode. At this time the multiplexer is prepared for loading line parameters.

## 3.1.2 Parameter Initialization

After an INIT or a Master Reset, the transmit and receive buffers The program MUST load are empty and all the lines are disabled. the line parameter register (AS.LINE.PAR.REG<15:00>) with the desired parameters for specific lines before enabling these lines. Note that the line parameter registers must be loaded even if all the parameters are zero. LINE.SEL<2:0> should contain the line number whose parameters are to be loaded. The program should also set the appropriate interrupt enable bits in the control status The program is now ready to enable the register (AS.CSR<15:00>). desired transmit and received lines. The modem control signals originating at the asynchronous multiplexer can be set or cleared at any time. Note that a Master Reset or INIT clears the bits the register representing the transmit modem bits. However, the acutal transmit modem signals are cleared only after an INIT, and are unaffected by a Master Reset.

## 3.1.3 Transmission

The transmit line is enabled by setting the line enable bit in the specific AS.LINE.CTRL register. A line must be enabled in order to transmit data. A disabled line is held in the ON (or marking) state, except in special maintenance situations. Transmission of data is handled using one of two techniques: SILO mode or NPR mode.

## 3.1.3.1 SILO Mode

A transmit line is enabled by setting the appropriate bit in the AS.LINE.CTRL register. A line must be enabled in order to transmit data. A disabled line is held marking (provided the line is not programmed for auto-echo or remote loopback).

In SILO mode, whenever a transmit silo becomes empty due to a character leaving the silo to be transmitted, TX.RDY is asserted. If TX.IE is active when TX.RDY becomes set, then an interrupt to the transmit vector is posted. The program should read AS.CSR<15:00> in order to determine the cause of the interrupt.

If TX.RDY is set, then AS.CSR<02:00> contains the line number whose silo has become empty. AS.CSR<12> will be set if the transmission was stopped due to an aborted DMA transfer. The act of reading AS.CSR<15:00> clears TX.RDY. Note that TX.RDY must be cleared (i.e., the program must read AS.CSR<15:00>) before the asynchronous multiplexer can reset TX.RDY for another line.

The operating system loads line output data into the dedicated 32-character line SILO, one or two characters at a time. asserted to indicate when the SILO has been emptied and therefore requires more transmit data to prevent an underrun. To minimize interrupt overload, the program should attempt to keep silos If the program intends to fill the silo, then it may inspect the transmit silo count register for the particular line in order to determine how many characters have been transmitted from the silo while it was being filled. The silo count indicates how many full positions there are in the silo. Thus, a silo count of zero indicates an empty silo, and a silo count of 32 indicates a full silo. The transmit silo count registers may be examined at any time, and a particular line's transmit silo may be loaded or flushed, regardless of whether the respective transmit line is If a line is disabled while its silo is being emptied, transmission stops after the current character has been transmitted. However, the silo contents remain valid, and upon enabling the line, transmission from the silo resumes.

The transmit SILO count register may be exercised at any time. It may be flushed or loaded regardless of whether the transmit line has been enabled. However, no actual transmission takes place unless the line is enabled. At that time, data will begin shifting out of the SILO for transmission.

#### 3.1.3.2 NPR (DMA) Mode

In NPR mode, the transmit SILOs are still used. Upon loading of the byte count and address register, the multiplexer begins filling the specific transmit SILO directly from memory and continues to do so until either the SILO fills to capacity or the NPR transfer is terminated.

If the silo fills to capacity, the NPR transfer stops until the SILO count falls below 2 characters at which time the NPR transfer resumes. Note that TX.RDY does not set at any time. If the NPR transfer completes (byte count is exhausted), TX.RDY is asserted even though there may be additional characters in the transmit SILO. These characters will continue to shift out in the normal manner.

#### 3.1.4 Receiver Operation

A receive line is enabled by setting the appropriate bit in the AS.LINE.CTRL register. A line must be enabled in order to receive data. All lines share a 49-character receive silo. This silo is also used to store modem signal change status. There is no DMA mode for the receiver.

| Mnemonic        | Off<br>Set | Access | Mnemonic        | Off<br>Set | Access |

|-----------------|------------|--------|-----------------|------------|--------|

| CONFIG DEC      | 0          | R/W    | AS.RX.BUF       | 20         | R      |

| CONFIG.REG      | 0          | R/W    | RX.SILO.PAR.REG | 20         | W      |

| MAINT.REG       | 2          | R/W    | AS.IND.REG      | 22         | R/W    |

| SY.RX.CSR       | 4          | R/W    | LP.CSR          | 24         | R/W    |

| SY.TX.CSR       | 6          | R/W    | LP.IND.REG      | 26         | R/W    |

| SY.MISC.REG     | 10         | R/W    | DR.CSR          | 30         | R/W    |

| SY.IND.REG      | 12         | R/W    | DR.OUT.BUF      | 32         | R/W    |

| AS.CSR          | 14         | R/W    | DR.IN.BUF       | 34         | R/W    |

| AS.LINE.PAR.REG | 16         | R/W    | DR.IND.REG      | 36         | R/W    |

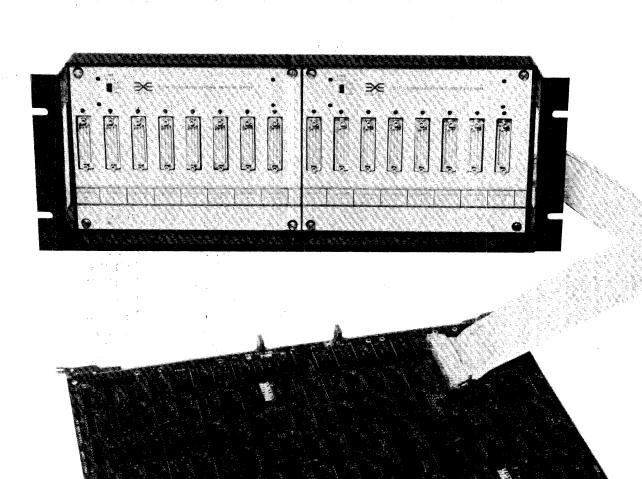

Figure 3-1 DMF32 Control and Status Registers

| 15 | 08          | 07             | 00  |    |   |

|----|-------------|----------------|-----|----|---|

|    | AS.MODEM.RX | AS.TX.SILO.CNT |     | R  | n |

|    | AS.T        | W              | U   |    |   |

|    | AS.MODEM.TX |                | R/W | 8  |   |

|    | AS.TX       | R/W            | 10  |    |   |

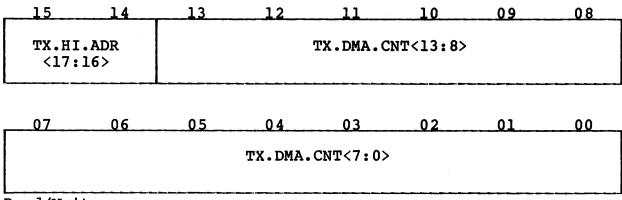

|    | TX.DMA.     |                | R/W | 18 |   |

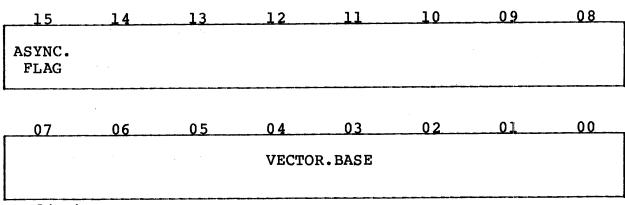

Figure 3-2 DMF32 Indirect Registers

## 3.2 CONTROLLER REGISTERS

The CS11/F1's 16 directly addressed registers and 40 indirectly addressed registers are used by the operating system to command and monitor the multiplexer. The registers are accessed by reading or writing 16 addresses in the I/O page of memory. The memory addresses vary according to the configuration of the system in which the CS11 is installed. In Figure 3-1 the offset from the base address (which is selected during system configuration) is given for each register. A few of the addresses are associated with different registers depending on whether the access is a read or a write. For example, see register 10.

Each functional register or segment of a register has a mnemonic assigned to it. The mnemonic for a particular address may vary if the register's function varies for write accesses verses read accesses. Also, in the case of the indirect registers, the mnemonic may describe only the upper or lower byte of the register.

The indirect registers are accessed through AS.IND.REG. The indirect registers are addressed by a five-bit address in AS.CSR<04:00>. The low three bits of the address indicate the line number being referenced. The upper two bits select which indirect register of that line is being accessed. Figure 3-2 gives the mnemonics for the generic indirect registers (0, 8, 10, 18) which exist for each line.

# 3.2.1 The Configuration Control Status Register (CONFIG.REG) base address + 0

Read/Write

The Configuration CSR is used by the operating system during auto-configure. The auto-configure routine scans the upper byte of this register to see what type of drivers should be loaded.

#### Asynchronous (ASYNC.FLAG) - CONFIG.REG<15>

This bit indicates that eight asynchronous lines are available on this communications multiplexer.

### Vector Address (VECTOR.BASE) - CONFIG.REG<07:00>

There are no switches on the board for interrupt vectors. The board is loaded (by the operating system at auto configure time) with the value of the first vector, VECTOR[O]<9:2>. The other vector is assumed by the multiplexer to be contiguous to (and of value greater than) the first vector.

# 3.2.2 The Diagnostic Control Status Register (MAINT.REG) base address + 2

The functions of the Diagnostic CSR are not implemented by the CSll/Fl. If read or written to at this address the controller responds with a Bus Acknowlege. A read will return all zeros; a write will have no affect.

## 3.2.3 Synchronous Receive CSR (SY.RX.CSR) base address + 4

The functions of the Synchronous Receive CSR are not implemented by the CSll/Fl. If read or written to at this address the controller responds with a Bus Acknowlege. A read will return all zeros; a write will have no affect.

## 3.2.4 Synchronous Transmit CSR (SY.TX.CSR) base address + 6

The functions of the Synchronous Transmit CSR are not implemented by the CSll/Fl. If read or written to at this address the controller responds with a Bus Acknowlege. A read will return all zeros; a write will have no affect.

## 3.2.5 Synchronous Miscellaneous Register (SY.MISC.REG) base address + 10

The functions of the Synchronous Miscellaneous Register are not implemented by the CSll/Fl. If read or written to at this address the controller responds with a Bus Acknowlege. A read will return all zeros; a write will have no affect.

# 3.2.6 <u>Synchronous Indirect Register (SY.IND.REG)</u> base address + 12

The functions of the Synchronous Indirect Register are not implemented by the CSll/Fl. If read or written to at this address the controller responds with a Bus Acknowlege. A read will return all zeros; a write will have no affect.

## 3.2.7 <u>Asynchronous Control Status Register (AS.CSR)</u> base address + 14

| 15       | 14    | 13 | 12               | 11 | 10           | 09 | 0.8 |

|----------|-------|----|------------------|----|--------------|----|-----|

| TX.RDY   | TX.IE | 0  | TX.DMA.<br>ERROR | 0  | TX.LINE<2:0> |    | 0>  |

| <u> </u> |       |    |                  |    |              |    |     |

| 07                    | 06    | 0.5   | 04 | 03   | 02       | 01   | 00 |

|-----------------------|-------|-------|----|------|----------|------|----|

| RX.<br>DATA.<br>AVAIL | RX.IE | RESET |    | IND. | ADR.REG< | 4:0> |    |

|                       |       |       |    |      |          |      |    |

Read/Write

#### Transmit Ready (TX.RDY) - AS.CSR<15>

This bit is set by the device when an enabled line (pointed to by TX.LINE<2:0>) has loaded the last character from the silo into the respective UART's holding register. An unsuccessful DMA transfer will set AS.CSR<12>.

This read/only bit is cleared when the program reads this register, by a Reset or an INIT.

## Transmit Interrupt Enable (TX.IE) - AS.CSR<14>

When set, this bit allows interrupt requests to be made to the transmit vector when TX.RDY becomes set.

This read/write bit is cleared by a Master Reset or INIT.

## Transmit DMA Error (TX.DMA.ERROR) - AS.CSR<12>

This bit is meaningful only when the respective line is in DMA mode. This bit is set if the multiplexer UNIBUS controller either

did not receive a BUS SSYN at least 32 microseconds after issuing a BUS MSYN, or the controller could not become bus master for at least 32 microseconds after having asserted BUS NPR. Bits TX.LINE<2:0> point to the line in error.

This read/only bit is cleared by a Master Reset, an INIT, or by reading this register.

### Transmit Line Number (TX.LINE<2:0>) - AS.CSR<10:08>

If TX.RDY is set, then these three bits contain the number of the line whose silo has become empty.

These bits are read only, and are cleared by a Master Reset or INIT.

#### Receiver Data Available (RX.DATA.AVAIL) - AS.CSR<07>

This bit is set by the device whenever data becomes available in the receive silo. It is automatically cleared when the receive silo becomes empty.

RX.LINE.AVAIL is read only, and is cleared by a Master Reset or INIT.

## Receive Interrupt Enable (RX.IE) - AS.CSR<06>

When set, this bit allows interrupt request to be made of the receive vector when:

- RDA has been set for longer than the timeout period.

- 2. More than 16 characters have entered the receive silo.

This read/write bit is cleared by a Master Reset or an INIT.

#### Controller Reset (RESET) - AS.CSR<05>

When the program sets this read/write bit, a Master Reset is initiated. This bit remains set while the reset is taking place, and clears automatically after the reset has finished. The program should not access async device registers (other than this one) while the reset is occurring. It is permissible for the program to write a one to MR while the reset is occurring (i.e. while RESET is high). Such action is ignored by the multiplexer for the reset is already in progress.

A Reset initializes various AS.CSR bits as specified in the bit descriptions.

## Indirect Address Register (IND.ADR.REG<4:0>) - AS.CSR<04:00>

These read/write bits point to one of thirty-two indirect registers. These registers are accessed through location BASE + 22. These bits are cleared by a Master Reset or INIT.

# 3.2.8 Asynchronous Line Parameter Register (AS.LINE.PAR.REG) BASE Address + 16

| _            | 15    | . 14           | 13             | 12                |    | 10  | 09       | 0.8 |

|--------------|-------|----------------|----------------|-------------------|----|-----|----------|-----|

| TX.BAUD<3:0> |       |                |                | RX.BAUD<3:0>      |    |     |          |     |

| _            | 07    | 06             | 05             | 04                | 03 | 02  | 01       | 00  |

|              | STOP. | EVEN<br>PARITY | PARITY.<br>ENA | CHAR.LEN<br><1:0> |    | LIN | E.SEL<2: | 0>  |

Read/Write

If this location is read, it will contain the line parameter for the line selected by bits <02:00> of AS.CSR.

#### NOTE

A Master Reset or INIT causes the bits in this read/write register to be set to zero. However, the parameters for the line are only updated after this register has been written to. Therefore, the line parameter register should ALWAYS be loaded with the parameters for the particular line before the line is enabled (even if the parameters are all zero).

## Transmit Baud Rate (TX.BAUD<2:0>) - AS.LINE.PAR.REG<15:12>

For the selected line, the RX Baud Rate specifies the receiver's baud rate, and the TX Baud Rate specifies the transmitter's baud rate.

Split baud rate capability is supported with qualifications. If the user elects to use split baud rates by specifing a RX speed that is different from the TX speed, all split RX rates must be the same for a 16 line group. That is, all split RX rates for the two consecutive DMF32 emualtions represented by a distribution panel would be the same. If more than one split RX rate is specified for a 16 line group, the last rate specified is the one that is used for all lines.

If split speeds for a line are not selected (i.e., TX and RX rates the same), then any speed from the range in the Table below may be used.

Table 3-1 Split Speed Example

|                  | Line                  | TX Rate                        | RX Rate                       | Туре                                |

|------------------|-----------------------|--------------------------------|-------------------------------|-------------------------------------|

| D<br>M           | 0<br>1<br>2           | 1200<br>1200<br>4800           | 1200<br>300<br>4800           | Standard<br>Split Speed<br>Standard |

| F<br>1           | :<br>:<br>7           | :<br>:<br>1200                 | 300                           | :<br>:<br>Split Speed               |

| D<br>M<br>F<br>2 | 0<br>1<br>:<br>:<br>7 | 9600<br>2400<br>:<br>:<br>1800 | 9600<br>300<br>:<br>:<br>1800 | Standard Split Speed : : : Standard |

Table 3-2 CS11/Fl Baud Rates

| Вi | ts (wr | ite-on: | ly) |       |

|----|--------|---------|-----|-------|

| 15 | 14     | 13      | 12  | Baud  |

| 11 | 10     | 09      | 8 0 | Rate  |

|    |        |         |     |       |

| 0  | 0      | 0       | 0   | 5.0   |

| 0  | 0      | 0       | 1   | 75    |

| 0  | 0      | 1       | 0   | 110   |

| 0  | 0      | 1       | 1   | 134.5 |

| 0  | 1      | 0       | 0   | 150   |

| 0  | 1      | 0       | 1   | 300   |

| 0  | 1      | 1       | 0   | 600   |

| 0  | 1      | 1       | 1   | 1200  |

| 1  | 0      | 0       | 0   | 1800  |

| 1  | 0      | 0       | 1   | 2000  |

| 1  | 0      | 1       | 0   | 2400  |

| 1  | 0      | 1       | 1   | 3600* |

| 1  | 1      | 0       | 0   | 4800  |

| 1  | 1      | . 0     | 1   | 7200* |

| 1  | 1      | 1       | 0   | 9600  |

| 1  | 1      | 1       | 1   | 19200 |

|    |        |         |     |       |

## Receive Baud Rate (RX.BAUD<2:0>) - AS.LINE.PAR.REG<11:08>

See TX.BAUD, above.

### Stop Code (STOP.CODE) - AS.LINE.PAR.REG<07>

This bit specifies the number of stop bits for the selected line.

- 0 = 1 stop bit

- 1 = 2 stop bits

## Even/Odd Parity (EVEN.PARITY) - AS.LINE.PAR.REG<06>

When PARITY.ENA is set, EVEN.PARITY specifies whether even or odd parity is generated and checked for the selected line.

- 0 = odd character parity

- 1 = even character parity

### Parity Enable (PARITY.ENA) - AS.LINE.PAR.REG<05>

When set, this bit causes a parity bit to be generated on transmission, and checked and stripped on reception for the selected line.

## Character Length (CHAR.LEN<1:0>) - AS.LINE.PAR.REG<04:03>

These two bits specify the character length (not counting start bits, stop bits and the parity bit, if enabled) for the selected line.

- 00 : NA 01 : NA

- 10: 7 bits per character

- 11 : 8 bits per character

#### Line Select (LINE.SEL<2:0>) - AS.LINE.PAR.REG<02:00>

The line select bits contain the binary number of the line whose parameters are to be loaded.

# 3.2.9 <u>Asynchronous Receiver Buffer (AS.RX.BUF)</u> BASE Address + 20

The Receiver Buffer is a dual register. When read, the upper byte of the register provides status information that pertains to the lower byte which contains the received character. When written, the lower byte of the register is used to specify the receiver silo alarm timeout period.

#### 3.2.9.1 Receiver Buffer (Read)

| _ | 15           | 14          | 13            | 12             | 11            | 10           | 09 | 0.8 |  |  |

|---|--------------|-------------|---------------|----------------|---------------|--------------|----|-----|--|--|

|   | DA.<br>VALID | OVR.<br>ERR | FRAME.<br>ERR | PARITY.<br>ERR | DS.<br>CHANGE | RX.LINE<2:0> |    |     |  |  |

|   | 07           | 06          | 0.5           | 04             | 03            | 02           | 01 | 00  |  |  |

|   | RX.DATA<7:0> |             |               |                |               |              |    |     |  |  |

| Į |              |             |               |                |               |              |    |     |  |  |

Read Only

It is through Receiver Buffer that the program acesses the receive silo. Every time this register is read, data words in the silo shift down by one position. Successive read cycles access successive silo entries. This receive silo not only contains receive characters and associated status information, but also contains data set change information.

This silo is flushed by a Master Reset or INIT.

#### Data Valid (DA.VALID) - AS.RX.BUF<15>

When this bit is set, the remaining bits in this register are valid. This bit is set when data is loaded into the register, and remains set as long as there is data in the buffer.

This bit is cleared by a Master Reset, INIT, or when the receive buffer becomes empty.

## Overrun Error (OVR.ERR) - AS.RX.BUF<14>

This bit is meaningful only if DS.CHANGE is clear. This bit is set if one or more previous characters were lost on the line on which the character was received due to the silo being full. The received character is valid.

## Framing Error (FRAME.ERR) - AS.RX.BUF<13>

This bit is meaningful only if DS.CHANGE is clear. This bit is set if the line on which the character was received was in the spacing (0) state at the time the first stop bit was sampled.

## Parity Error (PARITY.ERR) - AS.RX.BUF<12>

This bit is meaningful only if DS.CHANGE is clear. This bit is set if parity was enabled for the line on which the character was received, and the character was received with incorrect parity.

## Data Set Change (DS.CHANGE) - AS.RX.BUF<11>

When this bit is set, then Receiver Buffer is zero, and RX.LINE<2:0> contains the line number whose modem signals changed.

## Receive Line Number (RX.LINE<2:0>) - AS.RX.BUF<10:08>

These three bits contain the binary number of the line on which a character was received, or a data set change was experienced.

## Receive Character Buffer (RX.DATA<7:0>) - AS.RX.BUF<07:00>

If DS.CHANGE is clear, then the buffer contains the received character. Bits are received least significant bit (LSB) first. If parity is enabled, the parity bit is stripped off. Characters less then eight bits long are right justified with the high order bits set to zero.

If DS.CHANGE is set, then <07:00> will be zero and the program should read the RX.MODEM signals to see what has changed.

#### 3.2.9.2 Receiver Buffer (Write)

| 15 | 14 | 13                                                                                                            | 12 | 11 | 10 | 09 | 0.8 |

|----|----|---------------------------------------------------------------------------------------------------------------|----|----|----|----|-----|

|    | 0  |                                                                                                               |    |    |    |    |     |

|    |    | مناه المناف |    |    |    |    |     |

| 07 | 06                        | 0.5 | 04 | 0.3 | 0.2 | 01 | 0.0 |  |  |  |  |

|----|---------------------------|-----|----|-----|-----|----|-----|--|--|--|--|

|    |                           |     |    |     |     |    |     |  |  |  |  |

|    | RX.SILO.ALRM.TIMEOUT<7:0> |     |    |     |     |    |     |  |  |  |  |

| İ  |                           |     |    |     |     |    |     |  |  |  |  |

|    |                           |     |    |     |     |    |     |  |  |  |  |

Write Only

# Receive Silo Alarm Timeout (RX.SILO.ALRM.TIMEOUT<7:0>) - RX.SILO.PARAMETER.REG<07:00>

These eight bits specify the silo alarm timeout period. An interrupt will be generated if data has been sitting in the silo for a time equal to or larger than the timeout period. Every time the receive silo is read, or a Master Reset or an INIT occurs, the internal timer is initialized to zeros.

The timeout period can range from 0 to approximately 360 milliseconds. Loading a value of zero into this register causes an infinite timeout.

00000000 := Infinite Timeout 00000001 := No timeout

. Approximately 1.3 ms added timeout per bit increment

11111111 := Approximately 360 ms.

This interval timer is based on microcode loops and is not very accurate. This timeout value is set to a l (i.e. no timeout) after a Master Reset or an INIT.

# 3.2.10 Indirect Registers BASE Address + 22

The indirect registers are addressed by a five-bit address in AS.CSR<04:00>. The low three bits of the address indicate the line number being referenced. The upper two bits select which indirect register of that line is being accessed. This specification describes the generic indirect registers (0,8,10,18) which exist for each line.

## 3.2.10.1 Indirect Register 0 (IND.REG0) (Read)

| 15  | 14           | 13          | 12  | 11            | 10 | 0.9 | 0.8 |

|-----|--------------|-------------|-----|---------------|----|-----|-----|

| DSR | RING.<br>IND | CAR.<br>DET | CTS | S.CAR.<br>DET | 0  | 0   | 0   |

| 0.7 | 06       | 0.5 | 04       | 03      | 02 | 01 | 00 |

|-----|----------|-----|----------|---------|----|----|----|

|     | <b>A</b> |     |          |         |    |    |    |

|     | -        |     | rx.silo. | CNT<7:0 | >  |    |    |

|     | . 1      |     |          |         |    |    |    |

Read Only

When read, bits <15:08> of this read/only register contain the receive modem status for the selected line. All modem signals represented in this register emanate from the DCE.

This byte is cleared during a Master Reset or INIT but updated if the following conditions are met.

- Data set change flag clear, or

- Data set change flag set and there is room in the RX silo for a data set change entry.

After a Master Reset, condition one is true. Therefore, if the receive silo is full and data set change is enabled and there is a data set change, the change will be flagged after the silo has become non-full. This way data set changes are not lost when the RX silo is full.

## Data Set Ready (DSR) - AS.MODEM.RX<15>

This bit reflects the state of the Data Set Ready line (RS-232-C circuit CC) emanating from the modem (if enabled as described in paragraph 4.5.2).

#### Ring Indicator (RING.IND) - AS.MODEM.RX<14>

This bit reflects the state of the Ring Indicator line (RS-232-C circuit CE) emanating from the modem.

#### Carrier Detect (CAR.DET) - AS.MODEM.RX<13>

This bit reflects the state of the Received Line Signal Detector line (RS-232-C circuit CF) emanating from the modem.

#### Clear To Send (CTS) - AS.MODEM.RX<12>

This bit reflects the state of the Clear to Send line (RS-232-C circuit CB) emanating form the modem.

# Secondary Received Line Signal Detect (S.CAR.DET) - AS.MODEM.RX<11>

This bit reflects the state of the Secondary Received Line Signal Detector (RS-232-C circuit SCF) emanating from the modem.

## Transmit Silo Count (TX.SILO.CNT<7:0>) - AS.TX.SILO.CNT<07:00>

When read, bits <07:00> of this read/only register contain the number of entries in the 32-character transmit silo for selected line.

This register is cleared by a Master Reset or an INIT.

## 3.2.10.2 Indirect Register 0 (IND.REG0) (Write)