# CS23/E1 COMMUNICATIONS SUBSYSTEM (DHU11 COMPATIBLE) TECHNICAL MANUAL

3545 Harbor Boulevard Costa Mesa, California 92626 (714) 662-5600 TWX 910-595-2521

#### WARNING

This equipment generates, uses and can radiate radio frequency energy, and if not installed and used in accordance with the technical manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of Federal Communications Commission (FCC) Rules, which are designed to provide reasonable protection against such interference when operating in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Copyright (C) 1986 Emulex Corporation

The information in this manual is for information purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in the manual.

Printed in U.S.A.

| Section | Title                                          | Page |

|---------|------------------------------------------------|------|

| SECTION | 1 GENERAL DESCRIPTION                          |      |

| 1.1     | INTRODUCTION                                   | 1-1  |

| 1.1.1   | RELATED DOCUMENTATION                          | 1-2  |

| 1.2     | SUBSYSTEM OVERVIEW                             | 1-2  |

| 1.3     | PHYSICAL ORGANIZATION OVERVIEW                 | 1-4  |

| 1.3.1   | CC23 CONTROLLER                                | 1-4  |

| 1.3.2   | DISTRIBUTION PANEL                             | 1-5  |

| 1.4     | ORDERING INFORMATION                           | 1-5  |

| 1.5     | FEATURES                                       | 1-6  |

| 1.5.1   | MICROPROCESSOR DESIGN                          | 1-6  |

| 1.5.2   | FCC COMPLIANCE                                 | 1-7  |

| 1.5.3   | SELF-TEST                                      | 1-7  |

| 1.5.4   | PROGRAMMABLE CHANNEL PARAMETERS                | 1-7  |

| 1.5.5   | DMA ON TRANSMIT                                | 1-7  |

| 1.6     | COMPATIBILITY                                  | 1-8  |

| 1.6.1   | WITH DEC DIAGNOSTICS                           | 1-8  |

| 1.6.2   | EIA SIGNALS                                    | 1-8  |

| 1.6.3   | OPERATING SYSTEMS                              | 1-8  |

| 1.6.4   | EXTERNAL DEVICE INTERFACES                     | 1-9  |

| 1.0.4   | DATERIAL DEVICE INTERESTED                     |      |

| SECTION | 2 SUBSYSTEM SPECIFICATION                      |      |

|         |                                                | 2-1  |

| 2.1     | OVERVIEW                                       |      |

| 2.2     | GENERAL SPECIFICATION                          | 2-1  |

| 2.3     | ELECTRICAL SPECIFICATION                       | 2-4  |

| 2.4     | ENVIRONMENTAL SPECIFICATION                    | 2-4  |

| 2.5     | PHYSICAL SPECIFICATION                         | 2-5  |

| •       |                                                |      |

| SECTION | 3 PLANNING THE INSTALLATION                    |      |

| 3.1     | OVERVIEW                                       | 3-1  |

| 3.2     | CONFIGURATIONS                                 | 3-1  |

| 3.2.1   | CP22 DISTRIBUTION PANEL                        | 3-1  |

| 3.2.2   | CP23 DISTRIBUTION PANEL                        | 3-2  |

| 3.2.3   | CP25 DISTRIBUTION PANEL                        | 3-2  |

| 3.2.4   | CP26 DISTRIBUTION PANEL                        | 3-2  |

| 3.3     | MODEM SIGNALS                                  | 3-2  |

| 3.4     | DATA FLOW CONTROL                              | 3-2  |

| 3.5     | HARDWARE LEVEL FLOW CONTROL                    | 3-3  |

| 3.5.1   | BASIC LEVEL FLOW CONTROL                       | 3-4  |

| 3.5.1.1 | Programming Notes for Basic Level Flow Control | 3-4  |

| 3.5.2   | LEVEL FLOW CONTROL WITH XON/XOFF CONVERSION    | 3-4  |

| 3.5.2.1 | Programming Notes for Level Flow Control With  |      |

|         | XON/XOFF Conversion                            | 3-4  |

| 3.5.3   | SOFTWARE ASSISTED LEVEL FLOW CONTROL           | 3-5  |

| 3.5.3.1 | Programming Notes for Software Assisted Level  |      |

|         | Flow Control                                   | 3-5  |

| Section  | Title                                   | Page         |

|----------|-----------------------------------------|--------------|

| 3.6      | CHANNEL NUMBERING                       | 3-6          |

| 3.7      | INSTALLING THE CS23/E1 ON THE PDP-11    | 3-6          |

| 3.7.1    | ADDING A NEW DEVICE TO RSTS/E           | 3-6          |

| 3.7.1.1  | Generating a New Monitor With SYSGEN    | 3-7          |

| 3.7.1.2  | Modem Controls                          | 3-7<br>3-7   |

| 3.7.2    | ADDING A NEW DEVICE TO RSX-11M          | 3-8          |

| 3.7.2.1  | Modem Controls                          | 3-0          |

| 3.7.3    | ADDING A NEW DEVICE TO RSX-11M-PLUS     | 3-9<br>3-9   |

| 3.7.4    | ADDING A NEW DEVICE TO ULTRIX-11        | 3-3          |

| 3.7.4.1  | Autoconfigure                           | 3-11         |

| 3.7.4.2  | Enabling Terminals                      | 3-11         |

| 3.7.4.2  | 1 /dev/++vvv                            |              |

| 3.7.4.2  |                                         | 3-11         |

| 3.7.4.2  |                                         | 3-12<br>3-13 |

| 3.8      | INSTALLING THE CS23/E1 ON THE VAX-11    | 3-13         |

| 3.8.1    | ADDING A NEW DEVICE TO VMS              | 3-13         |

| 3.8.2    | ADDING A NEW DEVICE TO ULTRIX-32        |              |

| 3.8.2.1  |                                         | 3-16         |

| 3.8.2.2  | Autoconfigure                           | 3-17         |

| 3.8.2.2  | Enabling Terminals                      | 3-17         |

|          |                                         | 3-17         |

| 3.8.2.2. | , , , , , , , , , , , , , , , , , , , , | 3-17         |

| 3.8.2.2  | .3 /etc/ttytype                         | 3-18         |

|          |                                         |              |

| SECTION  | 4 INSTALLATION                          |              |

| 4.1      | OVERVIEW                                | 4-1          |

| 4.1.1    | MAINTAINING FCC CLASS A COMPLIANCE      | 4-1          |

| 4.1.2    | DIP SWITCH TYPES                        | 4-2          |

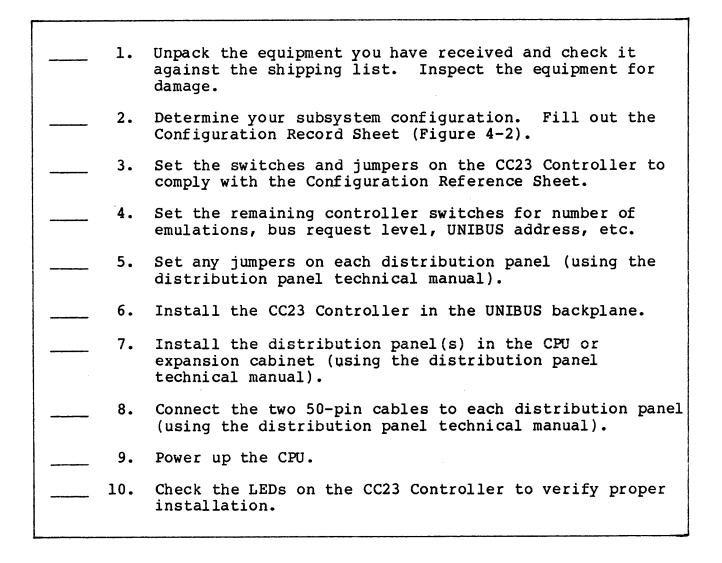

| 4.1.3    | INSTALLATION CHECKLIST                  | 4-3          |

| 4.2      | INSPECTION                              | 4-4          |

| 4.3      | SUBSYSTEM CONFIGURATIONS                | 4-4          |

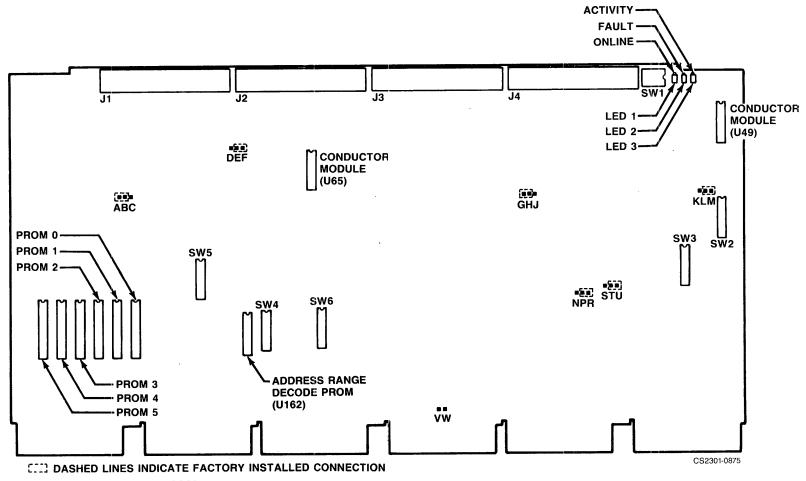

| 4.4      | CC23 CONTROLLER SETUP                   | 4-6          |

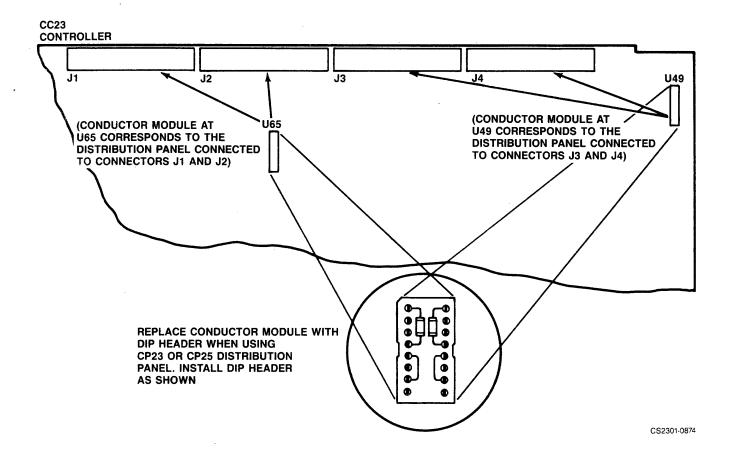

| 4.4.1    | DIP HEADER CONFIGURATION                | 4-11         |

| 4.4.2    | NUMBER OF DHULL EMULATIONS              | 4-11         |

| 4.4.3    |                                         |              |

| 4.4.4    | DHULL DEVICE REGISTER ADDRESSES         | 4-13         |

| 4.4.4.1  | Interrupt Vector Address Selection      | 4-15<br>4-15 |

| 4.4.4.2  |                                         |              |

| 4.4.5    | Bus Request/Grant Level Selection       | 4-16         |

| 4.4.5.1  | OPTION SWITCHES                         | 4-17         |

| 4.4.5.2  | CC23 Run vs Halt/Reset                  | 4-17         |

| 4.4.5.2  | Internal Test Select                    | 4-17         |

| 4.4.5.4  | 38,400 Baud vs. 2000 Baud               | 4-18         |

|          | CC23 Force Two Stop Bits                | 4-18         |

| 4.4.5.5  | Multi-Word DMA Transfer                 | 4-19         |

| 4.4.5.6  | Steal Grant                             | 4-19         |

| 4.4.5.7  | Hardware Level Flow Control             | 4-20         |

| 4.4.5.8  | Level Flow Control Mode                 | 4-21         |

| 4.4.6    | MODEM SIGNAL BIAS JUMPERS OPTION        | 4-22         |

| 4.5      | DISTRIBUTION PANEL SETUP                | 4-23         |

| 4.6      | CC23 CONTROLLER INSTALLATION            | 4-23         |

| 4.6.1    | SYSTEM PREPARATION                      | 4-23         |

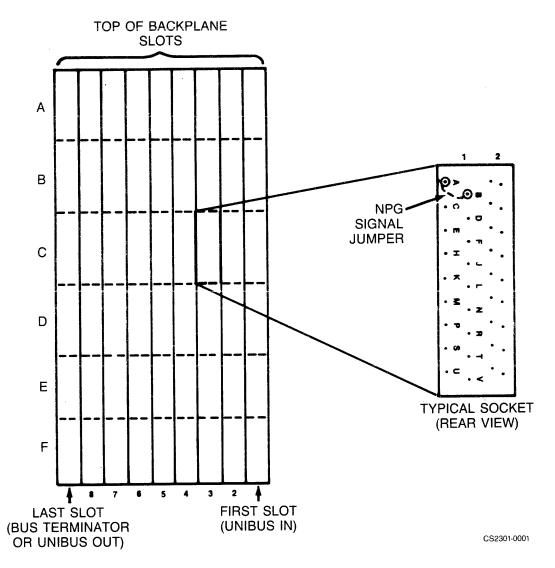

| 4.6.2    | SPC SLOT SELECTION                      | 4-23         |

| 4.6.3    | NPG SIGNAL JUMPER                       | 4-24         |

| Section | Title                                    | Page         |

|---------|------------------------------------------|--------------|

| 4.6.4   | CONTROLLER MOUNTING                      | 4-26         |

| 4.7     | DISTRIBUTION PANEL INSTALLATION          | 4-27         |

| 4.8     | SUBSYSTEM CABLING                        | 4-27         |

| 4.9     | SUBSYSTEM POWER-UP AND VERIFICATION      | 4-27         |

|         |                                          |              |

| SECTION | 5 TROUBLESHOOTING                        |              |

| 5.1     | OVERVIEW                                 | 5-1          |

| 5.2     | SERVICE                                  | 5-1          |

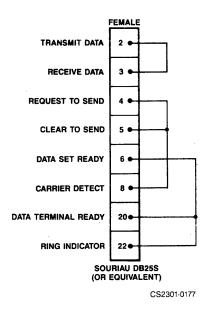

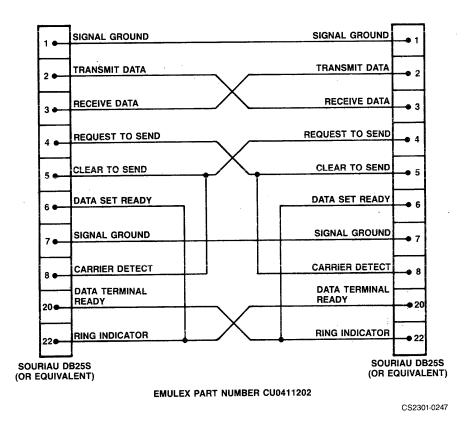

| 5.3     | TEST CONNECTOR                           | 5-2          |

| 5.4     | FAULT ISOLATION PROCEDURES               | 5-2          |

| 5.4.1   | SELF-TEST FAILURE FAULT ISOLATION        | 5-4          |

| 5.5     | POWER-UP SELF-TESTS                      | 5-4          |

| 5.5.1   | CC23 CONTROLLER SELF-TEST                | 5-4          |

| 5.6     | CC23 OPERATOR-INITIATED SELF-DIAGNOSTICS | 5-5          |

| 5.6.1   | NORMAL RUN MODE                          | 5-5          |

| 5.6.2   | OVERRIDE MODE                            | 5-6          |

| 5.6.3   | CONTINUOUS EXTERNAL LOOPBACK MODE        | 5-6          |

| 5.6.4   | SEARCH MODE                              | 5-6<br>5-6   |

| 5.6.5   | ECHO MODE                                | 5-6          |

| SECTION | 6 CONTROLLER REGISTERS AND PROGRAMMING   |              |

| 6.1     | OVERVIEW                                 | 6-1          |

| 6.2     | CONTROLLER REGISTERS                     | 6-1          |

| 6.2.1   | BASE CONTROL-AND-STATUS REGISTER (CSR)   | 6-4          |

| 6.2.2   | RECEIVE BUFFER (RBUF)                    | 6-7          |

| 6.2.3   | RECEIVE TIMER REGISTER (RXTIMER)         | 6-9          |

| 6.2.4   | LINE PARAMETER REGISTER (LPR)            | 6-10         |

| 6.2.5   | FIFO DATA REGISTER (FIFODATA)            | 6-13         |

| 6.2.6   | FIFO SIZE REGISTER (FIFOSIZE)            | 6-14         |

| 6.2.7   | LINE STATUS REGISTER (STAT)              | 6-15         |

| 6.2.8   | LINE CONTROL REGISTER (LNCTRL)           | 6-17         |

| 6.2.9   | TRANSMIT BUFFER ADDRESS REGISTER         |              |

|         | NUMBER 1 (TBUFFAD1)                      | 6-2]         |

| 6.2.10  | TRANSMIT BUFFER ADDRESS REGISTER         |              |

|         | NUMBER 2 (TBUFFAD2)                      | 6-21         |

| 6.2.11  | TRANSMIT DMA BUFFER COUNTER (TBUFFCT)    | 6-23         |

| 6.3     | PROGRAMMING FEATURES                     | 6-23         |

| 6.3.1   | INITIALIZATION                           | 6-23         |

| 6.3.2   | CONFIGURATION                            | 6-24         |

| 6.3.3   | TRANSMITTING                             | 6-24         |

| 6.3.3.1 | DMA Transfers                            | 6-25         |

| 6.3.3.2 | Programmed Transfers                     | 6-25         |

| 6.3.4   | RECEIVING                                | 6-26         |

| 6.3.5   | INTERRUPT CONTROL                        | 6-26<br>6-27 |

| 6.3.6   | AUTO XON AND XOFF                        |              |

| 6.3.7   | ERROR INDICATION                         | 6-28<br>6-29 |

| 6.3.8   | MODEM CONTROL                            | 6-30         |

| 6.3.9   | MAINTENANCE PROGRAMMING                  | 0-36         |

| Section  | Title                                 | Page |

|----------|---------------------------------------|------|

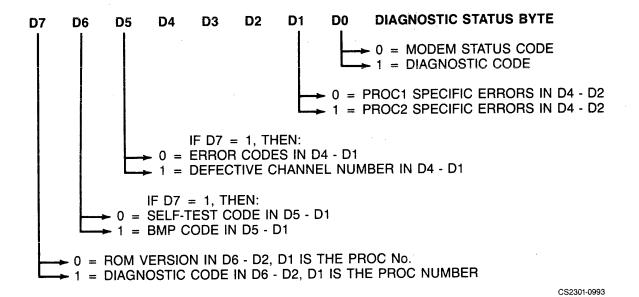

| 6.3.10   | DIAGNOSTIC CODES                      | 6-30 |

| 6.3.10.1 |                                       | 6-30 |

| 6.3.10.2 |                                       | 6-31 |

| 6.3.10.3 |                                       | 6-32 |

| 6.3.10.4 |                                       | 6-33 |

| 6.4      | CC23 CONTROLLER ARCHITECTURE          | 6-34 |

| 6.4.1    | RECEIVER OPERATION                    | 6-34 |

| 6.4.2    | TRANSMITTER OPERATION                 | 6-35 |

| SECTION  | 7 INTERPACES                          |      |

| 7.1      | OVERVIEW                              | 7-1  |

| 7.2      | UNIBUS                                | 7-1  |

| 7.3      | CC23 CONTROLLER TO DISTRIBUTION PANEL | 7-2  |

| 7.4      | EIA                                   | 7-2  |

# LIST OF APPENDICES

| Append                                                                                              | ix Title                                                                                                                                                                                                                                             | P <b>a</b> ge                                                                      |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| A                                                                                                   | AUTOCONFIGURE ALGORITHM                                                                                                                                                                                                                              |                                                                                    |

| A.1<br>A.2                                                                                          | OVERVIEW                                                                                                                                                                                                                                             | A-1                                                                                |

| A.3                                                                                                 | AUTOCONFIGURE DETERMINING THE VECTOR ADDRESS FOR USE WITH                                                                                                                                                                                            | A-1                                                                                |

| A.4                                                                                                 | AUTOCONFIGURE                                                                                                                                                                                                                                        | A-3<br>A-7                                                                         |

| В                                                                                                   | PROM REMOVAL AND REPLACEMENT                                                                                                                                                                                                                         |                                                                                    |

| B.1<br>B.1.1<br>B.1.2                                                                               | OVERVIEW EXCHANGING EMULATION PROMS ADDRESS RANGE DECODE PROM                                                                                                                                                                                        | B-1<br>B-1<br>B-1                                                                  |

| С                                                                                                   | PDP-11 DIAGNOSTICS                                                                                                                                                                                                                                   | •                                                                                  |

| C.1<br>C.2<br>C.3<br>C.3.1<br>C.3.2<br>C.3.3<br>C.3.4<br>C.4<br>C.5<br>C.6<br>C.7<br>C.7.1<br>C.7.2 | OVERVIEW TEST CONNECTORS DIAGNOSTIC TEST FUNCTIONS ZDHU ZDHV ZDHW ZDHX DECX/11 EXERECISER (XDHU) STARTING THE DIAGNOSTIC PROGRAM LOADING PROCEDURES DRS SUPERVISOR COMMANDS COMMAND SWITCHES CONTROL/ESCAPE CHARACTERS SUPPORTED  VAX-11 DIAGNOSTICS | C-1<br>C-2<br>C-4<br>C-4<br>C-5<br>C-6<br>C-6<br>C-7<br>C-9<br>C-10                |

| D.1 D.2 D.3 D.3.1 D.3.1 D.3.1 D.3.1 D.4 D.4.1 D.4.1 D.4.1 D.4.1 D.4.1                               | 2 Options 3 Event Flags 4 Sections EVDAH ONLINE DIAGNSOTIC RUNNING EVDAH ONLINE 1 Starting EVDAH 2 Options 3 Event Flags 4 Sections                                                                                                                  | D-1<br>D-3<br>D-4<br>D-4<br>D-5<br>D-6<br>D-6<br>D-7<br>D-7<br>D-9<br>D-11<br>D-11 |

| R                                                                                                   | ASCIT CODE CONVERSION                                                                                                                                                                                                                                |                                                                                    |

GLOSSARY

# LIST OF FIGURES

| Figure                          | Title                                   | Page                              |

|---------------------------------|-----------------------------------------|-----------------------------------|

| 1-1<br>1-2                      | CS23/El Communications Subsystem        | 1-3<br>1-4                        |

| 2-1                             | CC23 Controller Dimensions              | 2-5                               |

| 3-1<br>3-2                      | CONFIGURE Device Listing                | 3-15<br>3-16                      |

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5 | Switch Setting Example                  | 4-2<br>4-5<br>4-7<br>4-12<br>4-25 |

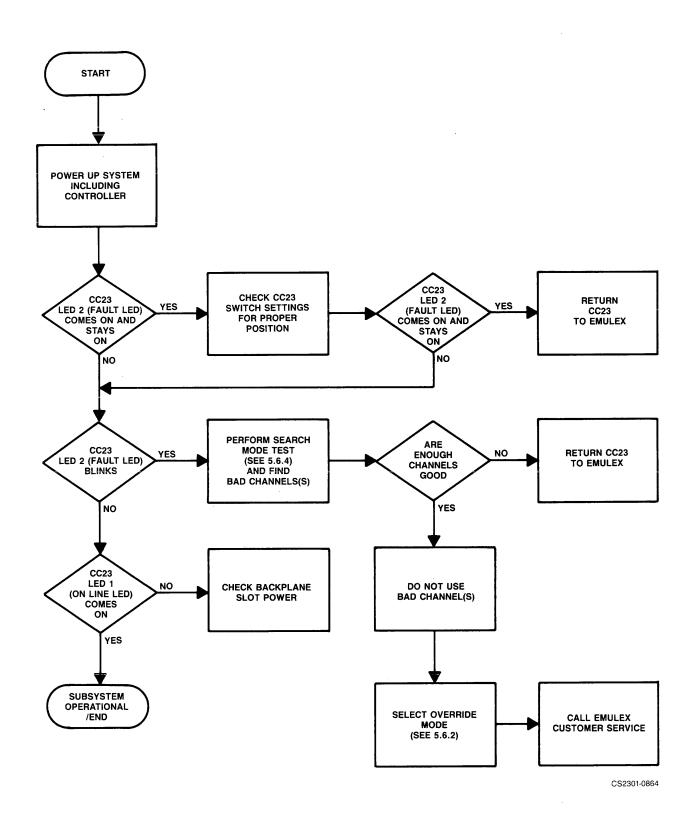

| 5-1                             | Self-Test Failure Fault Isolation Chart | 5-3                               |

| 6-1<br>6-2                      | Asynchronous Register Summary           | 6-3<br>6-31                       |

| C-1<br>C-2<br>C-3               | DHUll Wrap-Around Connector             | C-2<br>C-3<br>C-3                 |

| D-1<br>D-2<br>D-3               | DHUll Wrap-Around Connector             | D-1<br>D-2<br>D-3                 |

# LIST OF TABLES

| Table                                         | Title                                                                  | Page                                                 |

|-----------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------|

| 1-1<br>1-2                                    | CS23/El Basic Model                                                    | 1-6<br>1-6                                           |

| 2-1<br>2-2<br>2-3<br>2-4                      | General Specifications                                                 | 2-1<br>2-4<br>2-4<br>2-5                             |

| 4-1<br>4-2                                    | Installation Checklist                                                 | <b>4-</b> 3 <b>4-</b> 9                              |

| 4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9 | CC23 Controller Jumper Definition/Factory Configuration                | 4-10<br>4-14<br>4-15<br>4-18<br>4-21<br>4-22<br>4-28 |

| 5-1<br>5-2                                    | Flow Chart Symbol Definitions Self-Test Nodes                          | 5-2<br>5-5                                           |

| 6-1<br>6-2                                    | Data Rates CC23 Self Test Error Codes                                  | 6-11<br>6-32                                         |

| 7-1<br>7-2                                    | SPC UNIBUS Connections CC23 Controller to Distribution Panel Interface | 7-1<br>7-3                                           |

| A-1<br>A-2<br>A-3<br>A-4                      | SYSGEN Device Table                                                    | A-2<br>A-5<br>A-8<br>A-9                             |

| B-1                                           | Emulation PROM Locations                                               | B-1                                                  |

| r_1                                           | ASCII Seven-Bit Code                                                   | E-1                                                  |

#### **EMULEX PRODUCT WARRANTY**

WARRANTY: Emulex warrants for a period of twelve (12) months from the date of shipment that each Emulex CS23/El Communications Subsystem supplied shall be free from defects in material and workmanship.

During the warranty period, if the customer experiences difficulties with an Emulex controller and is unable to resolve the problem via the phone with Emulex Technical Support, a Return Authorization will be issued. Following receipt of a Return Authorization, the customer is responsible for returning the product to Emulex, freight prepaid. Emulex, upon verification of warranty will, at its option, repair or replace the component in question, and return to the customer freight prepaid.

CABLE WARRANTY: All Emulex provided cables, not included as part of a subsystem, are warranted for ninety (90) days from the time of shipment. Questionable cables should be returned to Emulex, freight prepaid, where they will be repaired or replaced by Emulex at its option and returned to the customer freight prepaid.

The above warranties shall not apply to expendable components such as fuses, bulbs, and the like, nor to connectors and other items not a part of the basic product. Emulex shall have no obligation to make repairs or to cause replacement required through normal wear and tear or necessitated in whole or in part by catastrophe, fault or negligence of the user, improper or unauthorized use of the Product, or use of the Product in such a manner for which it was not designed, or by causes external to the Product, such as but not limited to, power failure or air conditioning. Emulex's sole obligation hereunder shall be to repair or replace items covered in the above warranties. Purchaser shall provide for removal of the defective Product, shipping charges for return to Emulex and installation of its replacement.

RETURNED MATERIAL: Warranty claims must be received by Emulex within the applicable warranty period. A replaced product, or part thereof, shall become the property of Emulex and shall be returned to Emulex at Purchaser's expense. All returned material must be accompanied by a RETURN AUTHORIZATION number assigned by Emulex.

THE EXPRESSED WARRANTIES SET FORTH IN THIS AGREEMENT ARE IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING WITHOUT LIMITATION, ANY WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, AND ALL OTHER WARRANTIES ARE HEREBY DISCLAIMED AND EXCLUDED BY EMULEX. THE STATED EXPRESS WARRANTIES ARE IN LIEU OF ALL OBLIGATIONS OR LIABILITIES ON THE PART OF EMULEX FOR DAMAGES, INCLUDING BUT NOT LIMITED TO SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES ARISING OUT OF, OR IN CONNECTION WITH THE USE OR PERFORMANCE OF THE PRODUCT.

#### 1.1 INTRODUCTION

This manual is designed to help you install and use your CS23/El Communications Subsystem in the most efficient and straightforward manner possible. The contents of the seven sections and six appendices are described briefly below.

- Section 1 General Description This section contains an overview of the CS23/El Communications Subsystem.

- Section 2 Subsystem Specification This section contains general, electrical, environmental, and physical specifications for each component of the subsystem.

- Section 3 Planning the Installation This section contains the information necessary to plan your installation.

- Section 4 Installation This section contains the information needed to set up and physically install the subsystem.

- Section 5 Troubleshooting This section describes fault isolation procedures that can be used to pinpoint trouble spots.

- Section 6 Controller Registers and Programming This section contains a description of the subsystem's DHUll-type registers. This section also describes the controller architecture.

- Section 7 Interfaces This section describes the subsystem UNIBUS interface.

- Appendix A **DEC Autoconfigure Algorithm** This appendix contains an explanation of the autoconfigure algorithm for UNIBUS address assignment.

- Appendix B PROM Removal and Replacement This appendix contains instructions for PROM removal and replacement.

- Appendix C PDP-11 Diagnostics This appendix contains instruction for loading and starting the DEC PDP-11 diagnostics run by the CS23/E1.

- Appendix D **VAX-11 Diagnostics** This appendix contains instruction for loading and starting the DEC VAX-11 diagnostics run by the CS23/E1.

- Appendix E Code Conversion Tables This appendix provides ASCII and decimal/hexadecimal/octal code conversion tables.

#### Subsystem Overview

Glossary

This glossary contains definitions of words or phrases that do not have generally accepted meanings or that have a different connotation in this manual.

# 1.1.1 RELATED DOCUMENTATION

This manual is the main piece of documentation for the CS23/E1 Communication Subsystem. Two other manuals come with the subsystem: a distribution panel technical manual and a diagnostic manual (if the Emulex VAX diagnostic IVC23E was ordered). The Emulex part number for the VAX Installation Diagnostics User's Guide is VX9950902.

These other manuals are used only during specific parts of the installation procedure and this manual will clearly reference the other manuals any time you need them.

# 1.2 SUBSYSTEM OVERVIEW

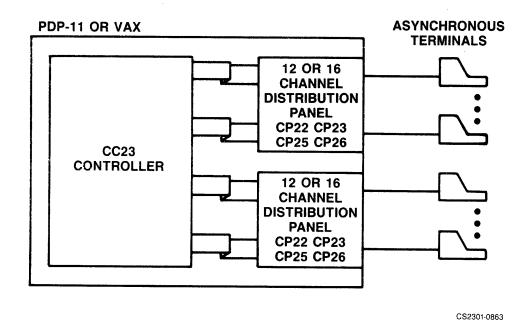

The CC23/El Communications Subsystem connects, via a single UNIBUS small peripheral controller (SPC) slot, up to 32 asynchronous data channels to PDP-11 or VAX-11 minicomputers manufactured by Digital Equipment Corporation (DEC).

To provide software transparency, the CS23/El emulates one or two DEC DHUll communications multiplexers.

The CS23/El subsystem components consist of the CC23 Controller, one or two distribution panels, and cables to connect the controller to the distribution panels.

The CS23/El incorporates several advanced features for communications multiplexers. These features include direct memory access (DMA) on transmit, 256-character receive silos with fill alarm for each sixteen-channel emulation, programmable channel parameters, and data rates up to 38400 bits per second (bps).

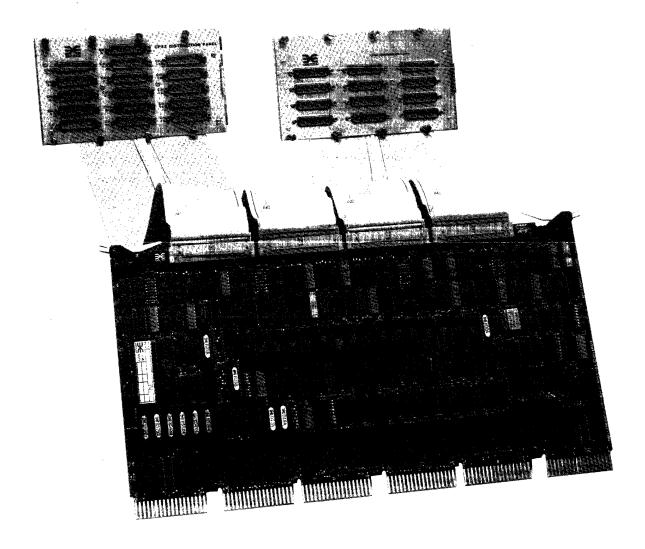

The CS23/El Communications Subsystem is shown in Figure 1-1.

Figure 1-1. CS23/El Communications Subsystem

#### 1.3 PHYSICAL ORGANIZATION OVERVIEW

The CS23/El Communications Subsystem consists of two components: the CC23 Controller and a distribution panel. Figure 1-2 shows the relationship of each component to the other. These relationships are explained in the following subsections.

Figure 1-2. CS23/El Subsystem Configuration

#### 1.3.1 CC23 CONTROLLER

The CC23 Controller is a single hex-wide printed circuit board assembly (PCBA) that plugs directly into a UNIBUS SPC backplane slot. The CC23's firmware-driven microprocessor performs the DHUll emulation and multiplexes/de-multiplexes data from the asynchronous channels.

The CC23 Controller is connected to the distribution panel(s) using two 50-pin flat cables for each panel.

#### 1.3.2 DISTRIBUTION PANEL

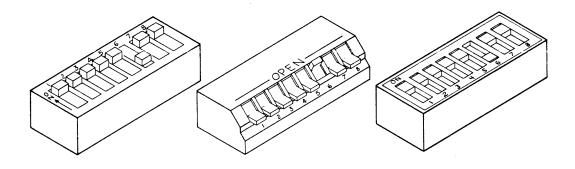

The CS23/El comes with one or two of the following distribution panels:

- CP22 (RS-232-C, 16 channels, partial modem control)

- CP23 (20 mA/RS-232-C, 16 channels, partial modem control)

- CP25 (RS-232-C/RS-422-A, 16 channels, partial modem control)

- CP26 (RS-232-C, 12 channels, full modem control on 8 channels, partial modem control on 4 channels))

All of the distribution panels are FCC compliant. All panels are the same size as DEC's DMF32 distribution panel. They can be mounted directly in place of a DMF32 panel in CPU cabinets that are DMF32 compatible, or in a DEC-FCC cabinet, or in a rack that mounts on RETMA rails.

The CP22 and CP23 can be ordered with EMI filters installed on each 25-pin connector. This is a special order item, however, and is not generally required.

# 1.4 ORDERING INFORMATION

The CS23/El Communications Subsystem is ordered using model numbers. The models available are:

- CS23/CP22

- CS23/CP23

- CS23/CP25

- CS23/CP26

- CS23/CP22/CP22

- CS23/CP22/CP23

- CS23/CP22/CP25

- CS23/CP22/CP26

- CS23/CP23/CP23

- CS23/CP23/CP25

- CS23/CP23/CP26

- CS23/CP25/CP25

- CS23/CP25/CP26

- CS23/CP26/CP26

The basic contents of the models is contained in Table 1-1. Table 1-2 contains a list of all CS23/El items that can be ordered separately.

Table 1-1. CS23/El Basic Model

| Emulex Part                                                                                                      | Coments                                                                                                               |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| CC23 Controller CPXX Distribution Panel  8 foot 50-wire ribbon cable CS23 Technical Manual CPXX Technical Manual | One or two, depending on model<br>ordered<br>Two per distribution panel<br>One for each distribution panel<br>ordered |

Table 1-2. CS23/El Accessories

| Model Number | Part Number   | Description                          |

|--------------|---------------|--------------------------------------|

| CC23/E1      | CS2310202-E1X | CC23 Controller                      |

| CP22-02      | CP2210202-02  | RS-232-C distribution panel          |

| CP23-02      | CP2310201-02  | 20 mA current loop/RS-232-C          |

|              |               | distribution panel                   |

| CP25         | CP2510202     | RS-422-A/RS-232-C distribution panel |

| CP26         | CP2610201-00  | RS-232-C distribution panel          |

| NA           | CU2111201-02  | 8 foot 50-wire ribbon cable, CC23    |

|              |               | Controller to distribution panel     |

| NAl          | NA            | Optional Address Range Decode PROM   |

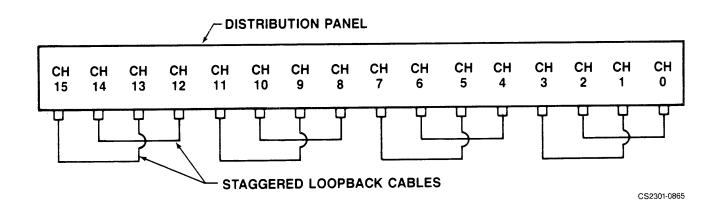

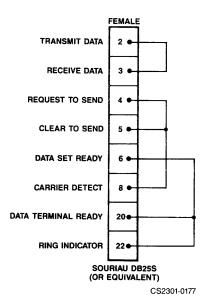

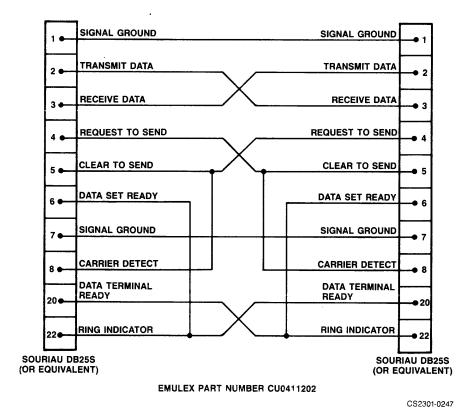

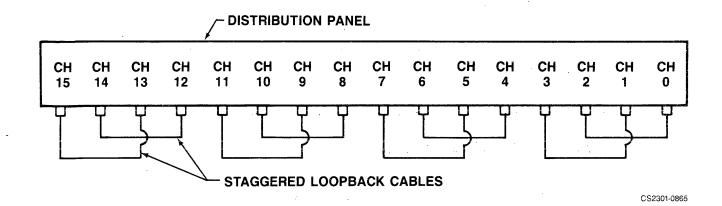

| NA           | CU0411202     | Staggered Loopback Connector         |

| NA           | CU0411203     | Wrap-Around Connector                |

| NA           | CS2351001     | CS23/El Technical Manual             |

| NA           | CP2251001     | CP22 Technical Manual                |

| NA           | CP2351001     | CP23 Technical Manual                |

| NA           | CP2551001     | CP25 Technical Manual                |

| NA           | CP2651001     | CP26 Technical Manual                |

<sup>&</sup>lt;sup>1</sup>Special order item.

Note: Distribution panel installation hardware and most cables are not listed. The need for these will vary by application. See your distribution panel manual to determine your requirements.

# 1.5 FEATURES

#### 1.5.1 MICROPROCESSOR DESIGN

The CC23 design incorporates an eight-bit, high-performance bipolar microprocessor to perform all controller functions. The microprocessor approach provides a reduced component count, high reliability, easy maintainability, and the ability to perform an emulation of the equivalent DEC controller.

#### 1.5.2 FCC COMPLIANCE

The CC23/El Communications Subsystem complies with the appropriate Federal Communications Commission (FCC) standards that limit EMI radiation from computing devices. All models, if operated within Class A compliant cabinets, comply with the limits for FCC Class A.

#### 1.5.3 SELF-TEST

The controller incorporates an internal self-test routine that is executed upon power-up. This test exercises all parts of the microprocessor and the on-board memory. Although this test does not completely test all circuitry, successful execution indicates a very high probability that the controller and the UNIBUS interface are operational. Failure of the self-test is indicated by Fault LEDs on the edge of the controller board. In addition, if the failure is in the controller electronics, the controller cannot be addressed from the central processing unit (CPU).

#### 1.5.4 PROGRAMMABLE CHANNEL PARAMETERS

Parameters on all 32 channels provided by the CS23/El Communications Subsystem can be set individually under program control.

Parameters for all channels include:

- Data rates from 50 to 38,400 bps

- The number of stop bits per character

- Parity (odd, even, or none)

- The number of data bits per character

- Independently programmable transmit and receive data rates per channel

#### 1.5.5 DMA ON TRANSMIT

The subsystem performs full-word direct memory access (DMA) on transmit. This feature considerably reduces the CPU overhead associated with data communications, especially when the host system is running terminal-I/O intensive software.

#### 1.6 COMPATIBILITY

# 1.6.1 WITH DEC DIAGNOSTICS

The CS23/El Communications Subsystem executes the following DEC DHUll PDP-11 diagnostics:

- ZDHU

- Z DHV

- Z DHW

- Z DH X

- XDHU

The CS23/El executes the following DEC DHUll VAX-11 diagnostics:

- EVDAI

- EVDAH

- UETP

The diagnostics EVDAH and UETP are run error-free by the CS23/El. Diagnostic EVDAI runs with some errors. See subsection D.3 for a list of the tests that run with errors. Instructions for loading and starting the diagnostics are contained in Appendix C, PDP-11 Diagnostics, and Appendix D, VAX-11 Diagnostics.

#### 1.6.2 EIA SIGNALS

The EIA signals supported vary for each distribution panel type. For a list of the signals supported, consult your distribution panel manual.

#### 1.6.3 OPERATING SYSTEMS

The CS23/El Communications Subsystem is compatible with the following operating systems without modification:

- RSX-llM, V4.1 update level D or above (PDP-11)

- RSX-11M-PLUS, V2.1 update level D or above (PDP-11)

- RSTS/E, V8.0-07 or above (PDP-11)

- VMS, V4.0 or above (VAX-11)

- Ultrix-11, V2.0 or above

- Ultrix-32, Vl.1 or above

# 1.6.4 EXTERNAL DEVICE INTERFACES

Distribution panels available for use with the CS23/El Communications Subsystem are compatible with the following interfaces:

- RS-232-C

- RS-422-A

- 20 mA current loop

Details of distribution panel compatibility and functionality are contained in the distribution panel technical manual that came with your communications subsystem.

#### 2.1 OVERVIEW

This section contains the general, electrical, environmental, and physical specifications for the CS23/El Communications Subsystem.

Specifications are contained in tables as listed below:

| Subsection                      | Title                                                                                                      |

|---------------------------------|------------------------------------------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Overview General Specification Electrical Specification Environmental Specification Physical Specification |

#### 2.2 GENERAL SPECIFICATION

A general specification for the CS23/El Communications Subsystem is contained in Table 2-1.

Table 2-1. General Specifications

| Parameter                                   | Description                                                         |

|---------------------------------------------|---------------------------------------------------------------------|

| FUNCTION                                    | Communications multiplexer providing up to 32 asynchronous channels |

| EMULATION                                   | Complete functional emulation of one or two DEC DHUll multiplexers  |

| Number of emulations                        | 1 or 2                                                              |

| Number of channels                          | Up to 32                                                            |

| Diagnostic Compatibility                    |                                                                     |

| PDP-11<br>VAX-11                            | ZDHU, ZDHV, ZDHW, ZDHX, XDHU<br>EVDAI <sup>1</sup> , EVDAH, UETP    |

| 1Runs with some errors. See subsection D.3. |                                                                     |

continued on next page

# General Specification

Table 2-1. General Specifications (continued)

| Parameter                            | Description                                                                                                                        |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Operating System Compatibility       |                                                                                                                                    |

| PDP-11                               | RSX-llM, V4.1 update level D or above RSX-llM-PLUS, V2.1 update level D or above RSTS/E, V8.0-07 or above Ultrix-ll, V2.0 or above |

| VAX-11                               | VMS, V4.0 or above<br>Ultrix-32, V1.1 or above                                                                                     |

| CPU I/O TECHNIQUE                    |                                                                                                                                    |

| Transmission                         | Interrupt driven DMA, or programmed I/O with transmit silo                                                                         |

| Reception                            | Interrupt driven, programmed I/O with receive silo                                                                                 |

| Transmission Modes                   | Full-duplex, half-duplex                                                                                                           |

| Programmable Data<br>Format          |                                                                                                                                    |

| Character Lengths                    | 5 to 8 bit data                                                                                                                    |

| Stop Bits                            | 1, 1.5, or 2                                                                                                                       |

| Parity                               | Odd, even, or none                                                                                                                 |

| Data Rates                           | 50, 75, 110, 134.5, 150, 300, 600, 1200, 1800, 2000, 2400, 4800, 7200, 9600, 19200, 38400; split speed capability1                 |

| Throughput Rate                      | 50,000 characters/second total                                                                                                     |

| EMULEX DISTRIBUTION PANELS SUPPORTED | CP22 (16 channels) CP23 (16 channels) CP25 (16 channels) CP26 (12 channels)                                                        |

| lSee Table 6-1                       |                                                                                                                                    |

continued on next page

Table 2-1. General Specifications (continued)

| Parameter                                                           | Description                                                                                    |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| INTERFACES                                                          |                                                                                                |

| CPU                                                                 | Standard UNIBUS SPC interface                                                                  |

| Device Address                                                      | All possible DHUll assignments (switch selectable) (change of PROMs needed for some addresses) |

| Vector Address                                                      | All possible DHUll assignments (switch selectable)                                             |

| Priority Level                                                      | Switch Selectable, BR5 or BR6                                                                  |

| EIA                                                                 |                                                                                                |

| Asynchronous ports                                                  | Serial, low order bit first, asynchronous                                                      |

| Connectors                                                          | 25-Pin Male                                                                                    |

| Configuration                                                       | Data Terminal Equipment (DTE)                                                                  |

| Modem Status Signals                                                |                                                                                                |

| 16 Channel Panel<br>All channels                                    | DCD, RI                                                                                        |

| 12 Channel Panel<br>Channels 0-3<br>Channels 4-7*<br>Channels 8-11* | DCD, RI, CTS, DSR<br>DCD, RI, CTS<br>DCD, RI                                                   |

| Modem Control Signals                                               |                                                                                                |

| 16 Channel Panel<br>All channels                                    | DTR                                                                                            |

| 12 Channel Panel<br>Channels 0-3<br>Channels 4-7<br>Channels 8-11   | DTR, RTS<br>DTR, RTS<br>DTR                                                                    |

| Modems Supported                                                    | Bell-Compatible: 103, 113, 212                                                                 |

|                                                                     | CCITT: V.22                                                                                    |

| *See subsection 6.2.7.                                              |                                                                                                |

# 2.3 ELECTRICAL SPECIFICATION

Table 2-2 lists and describes the electrical specification for the CC23 Controller.

Table 2-2. CC23 Electrical Specifications

| Parameter               | Description                                                                                                                                                                            |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| UNIBUS LOAD             | One                                                                                                                                                                                    |  |

| ELECTRICAL REQUIREMENTS | +5 volts DC <u>+</u> 5% at 8 amperes<br>+15 volts DC <u>+</u> 4% at 1 ampere<br>(with all channels connected)<br>-15 volts DC <u>+</u> 4% at 1 ampere<br>(with all channels connected) |  |

#### 2.4 ENVIRONMENTAL SPECIFICATION

Table 2-3 contains the environmental specifications for the CC23 Controller.

Table 2-3. CC23 Environmental Specifications

| Parameter             | Description                                                                             |

|-----------------------|-----------------------------------------------------------------------------------------|

| STORAGE TEMPERATURE   | -40°C ( °F) to 66°C ( °F)                                                               |

| OPERATING TEMPERATURE | 0°C (50°F) to 45°C (104°F)                                                              |

|                       | Where maximum temperature is reduced 1.8°C per 1000 meters (1°F per 1000 feet) altitude |

| RELATIVE HUMIDITY     | 10% to 90% with a maximum wet bulb of 28°C (82°F) and a minimum dewpoint of 2°C (3.6°F) |

| COOLING               | ll cubic feet per minute required                                                       |

# 2.5 PHYSICAL SPECIFICATION

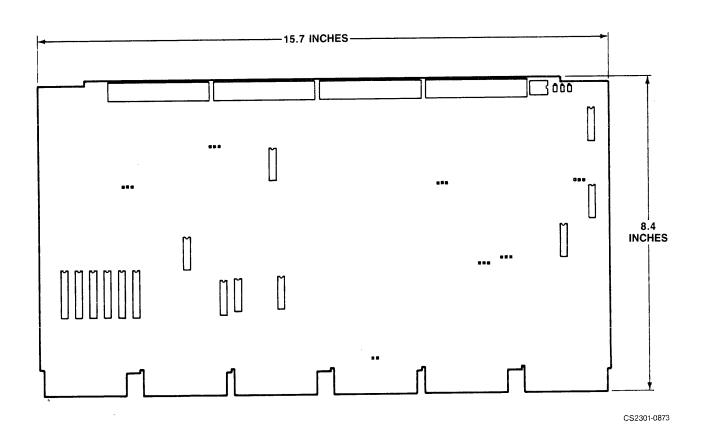

Table 2-4 contains the physical specifications for the CC23 Controller. The dimensions of the CC23 are shown in Figure 2-1.

| Table | 2-4. | CC23 | Physical | Specifications |

|-------|------|------|----------|----------------|

|-------|------|------|----------|----------------|

| Parameter       | Description                                             |

|-----------------|---------------------------------------------------------|

| PACKAGING       | Single, hex-size, six-layer PCBA                        |

| Dimensions      | 8.4 inches high by 15.7 inches wide by .625 inches deep |

| Shipping Weight | 5 pounds                                                |

Figure 2-1. CC23 Controller Dimensions

#### 3.1 OVERVIEW

This section is designed to help you plan the installation of your CS23/El Communications Subsystem. Taking time to plan the configuration of your subsystem before beginning its installation will result in a smoother installation with less system down time. As a planning tool, this section explains some of the practical matters that need to be considered before you begin your installation.

This section contains examples and explanations of configuration options. The subsections are listed in the following table:

| Subsection                                    | Title                                                                                                                                      |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Overview Configurations Modem Signals Data Flow Control Hardware Level Flow Control Channel Numbering Installing the CS23/El on the PDP-11 |

| 3.8                                           | Installing the CS23/El on the VAX/VMS                                                                                                      |

#### 3.2 CONFIGURATIONS

The CS23/El is designed to provide up to 32 channels on a PDP-ll or on a VAX-11. These channels are carried to external devices via distribution panels. The CS23/El can use any mix of two distribution panels from the following group:

- CP22

- CP23

- CP25

- CP26

This subsection discusses each panel in detail to help you determine which panels best suit your application.

#### 3.2.1 CP22 DISTRIBUTION PANEL

The CP22 is a 16-channel passive distribution panel. It can be mounted directly in DMF32-compatible CPU cabinets, a DEC FCC cabinet, or rack-mounted in a chassis on RETMA rails. The panel provides an RS-232-C compatible interface on all ports.

#### 3.2.2 CP23 DISTRIBUTION PANEL

The CP23 is a 16-channel active distribution panel. It can be mounted directly in DMF32-compatible CPU cabinets, a DEC FCC cabinet, or rack-mounted in a chassis on RETMA rails. Each port can be configured as either an RS-232-C or a 20 mA current loop interface.

#### 3.2.3 CP25 DISTRIBUTION PANEL

The CP25 is a 16-channel active distribution panel. It can be mounted directly in DMF32-compatible CPU cabinets, a DEC FCC cabinet, or rack-mounted in a chassis on RETMA rails. Each port can be configured as either an RS-232-C or an RS-422-A interface.

#### 3.2.4 CP26 DISTRIBUTION PANEL

The CP26 is a 12-channel passive distribution panel. It can be mounted directly in DMF32-compatible CPU cabinets, a DEC FCC cabinet, or rack-mounted in a chassis on RETMA rails. The panel provides an RS-232-C compatible interface on all ports.

The CP26 provides additional modem control signals for eight of the 12 ports.

#### 3.3 MODEM SIGNALS

The supported modem signals vary for each distribution panel. Because of this, careful consideration should be given to which devices will be connected to which ports.

# 3.4 DATA FLOW CONTROL

There are two common methods used to control the flow of data between the host CPU and external devices (such as terminals and printers):

- NON/XOFF Flow Control. With this method, XON/XOFF characters are used to start and stop the data flow. If the external device is receiving data too fast for it to keep up, it sends an XOFF character to the host and the host stops transmission. When it is able to accept more data, it transmits an XON character to the host.

- Hardware Level Flow Control. A device that uses this method drops a modem control signal (usually Data Terminal Ready) to signal the host that it cannot accept more data. The DTR pin on the device is cabled to one of the modem status pins on the distribution panel (usually Clear To Send or Carrier Detect), which is monitored by the host. When the device is able to accept more data, it raises its DTR signal.

There are advantages to both methods. XON/XOFF flow control allows devices to be attached to the distribution panel with only four wires and is the method used by DEC. For this reason, Emulex recommends using devices that are capable of XON/XOFF flow control.

However, many devices (especially printers) are receive-only devices and are incapable of transmitting XON/XOFF characters. For this reason, the CS23/El supports three switch-selectable versions of level flow control on a per-channel basis. The discussion in subsection 3.5 describes each version of hardware level flow control. The switch settings necessary to choose hardware level flow control are described in Section 4.

To preserve emulation transparency, in all three modes, all modem status signal changes are reported to the host operating system via the appropriate status register and receive FIFO.

In the Basic Level Flow Control and in the XON/XOFF Flow Control, the DTR bit in the Line Control Register always reflects what was last written to it, regardless of what the EIA DTR signal is. Also, channels enabled for both of these types of flow control have DTR deasserted at reset, then reasserted automatically.

The term congested is used in the following subsections to describe the state of certain silos. Congested means that the silo has been at least three-quarters full and has not yet dropped below one-half full.

#### 3.5 HARDWARE LEVEL FLOW CONTROL

When the hardware level flow control option is enabled, the CC23 controls transmitted data flow by monitoring the Carrier Detect (DCD) or Clear to Send (CTS) input at the distribution panel. The signal monitored (DCD or CTS) depends on which signal is selected using switches SW6-1 through SW6-5.

When DCD (or CTS if selected) is negated, the CC23 generates an XOFF character for transmission to the host. When DCD (or CTS if selected) is asserted, the CC23 generates an XON character for transmission to the host. An XOFF from the host negates Data Terminal Ready (DTR). An XON from the host asserts DTR.

This feature can be enabled only for the first of the two distribution panels connected to the CC23 (the panel connected to J1 and J2 on the CC23). If the panel is a 16 channel panel, channels one through fifteen in single channel increments can be enabled to use this feature. If the panel is a 12 channel panel, channels zero through eleven in single channel increments can be enabled to use this feature.

When enabled, the panel uses DCD (or CTS) for control of outbound data, and DTR for control of incoming data. DCD is converted to XON/XOFF characters for transmission to the host. XON/XOFF characters coming from the host are converted to DTR.

When switch SW6-5 is ON (closed), CTS is used instead of DCD on channels zero through eight of a twelve-channel panel in single channel increments.

# 3.5.1 BASIC LEVEL FLOW CONTROL

This is the simplest method. Transmission of outbound data stops within two character times if DCD (or CTS) drops, and restarts when DCD or CTS is raised.

# 3.5.1.1 Programming Notes for Basic Level Flow Control

After the CC23 receive silo is congested, inbound data reception of a character on any line results in the deassertion of DTR. DTR is reasserted when the receive silo drops to less than one-half full.

This version of flow control has limited application. VMS, for example, times output operations and will post a transmit timeout if the controller halts transmission for too long.

#### 3.5.2 LEVEL FLOW CONTROL WITH XON/XOFF CONVERSION

In this mode, the controller converts changes in modem signals into XON/XOFF characters for the benefit of the operating system.

Outbound transmission of data stops within two character times if DCD (CTS) changes to a deasserted condition. An XOFF character is passed to the host.

# 3.5.2.1 Programming Notes for Level Flow Control With XON/XOFF Conversion

If the OAUTO bit in the Line Control Register is set the TX.ENA bit in Transmit Buffer Address Register Number 2 is cleared when the silo becomes congested or DCD (CTS) is deasserted. See Section 6, Device Registers and Programming for bit descriptions.

Data transmission resumes when DCD (CTS) returns to an asserted condition. An XON character is passed to the host. If the OAUTO bit in the Line Control Register is set the TX.ENA bit in Transmit Buffer Address Register Number 2 is set.

If DCD is deasserted and the host operating system sets TX.ENA while in OAUTO mode, an XOFF is passed to the host and TX.ENA is cleared again within 30 ms.

# 3-4 Planning the Installation

After the receive silo has become congested, or after an XOFF is sent by the host operating system, or if the FORCE.XOFF in the Line Control Register is set, inbound data reception of characters on any channel results in the deassertion of DTR. An XOFF is not passed to the peripheral device.

DTR is reasserted when the receive silo becomes decongested and the FORCE. XOFF bit is cleared, or when the receive silo becomes decongested and the host operating system has sent an XON character. An XON character is not passed to the peripheral device.

This is the most useful mode of level flow control, because it allows standard DEC software to run transparently.

#### 3.5.3 SOFTWARE ASSISTED LEVEL FLOW CONTROL

This version of level flow control is used to improve response time with host operating software that already has the capability of using level flow control. Response time is improved for both transmitted data and received data.

This type of level flow control differs from Basic Level Flow Control in the ability of the host's control. With Software Assisted Level Flow Control the host has the ability to control DTR so that it can inhibit transmission from the external device. With Basic Level Flow Control the host cannot control DTR; the CC23 retains control of that function.

Transmission of outbound data stops within two character times if DCD (or CTS) drops, and restarts when DCD (CTS) is raised.

# 3.5.3.1 Programming Notes for Software Assisted Level Flow Control

Reception of inbound data is controlled if the receive silo is congested, or if the host operating system writes a zero to the DTR bit in the Line Control Register. Upon the happening of either event (congestion of the silo or writing to the DTR bit), the EIA DTR signal is deasserted. The EIA DTR signal is reasserted when the receive silo is decongested and when the host operating system writes a one to the DTR bit in the Line Control Register.

Channels enabled for Software Assisted Level Flow Control have DTR These channels will wait for the host to set deasserted at reset. the DTR bit in the Line Control Register before asserting DTR.

With this method, the host is still in control, but data flow is started and stopped more quickly because the controller "anticipates" the need for flow control.

#### 3.6 CHANNEL NUMBERING

The CS23/El emulates one or two 16-channel controllers. Thus, the CS23/El can accommodate up to 32 channels.

There are four distribution panels that can be used with the CS23/El. The CP22, CP23, and CP25 are 16-channel panels with ports 0-15. The CP26 is a 12-channel panel with ports 0-11. The DHUll channels correspond to the distribution panel ports in the way you would expect; that is, the DHUll with the lowest starting address controls ports 0 through 15, the next DHUll controls ports 16 through 31.

The distribution panel connected to CC23 connectors Jl and J2 is the first distribution panel, and the distribution panel connected to CC23 connectors J3 and J4 is the second distribution panel. Connectors Jl and J3 on the CC23 correspond to the first DHUll emulation, and connectors J2 and J4 correspond to the second DHUll emulation.

#### 3.7 INSTALLING THE CS23/E1 ON THE PDP-11

This subsection includes information you will need during the SYSGEN process when you add the CS23/El to your system. Information is included for RSTS/E, RSX-llM, RSX-llM-PLUS, and Ultrix-ll.

#### 3.7.1 ADDING A NEW DEVICE TO RSTS/E

All device drivers are an integral part of the RSTS/E monitor. Therefore, when you add a new device to your system, you must generate an entirely new RSTS/E monitor. You do not need to generate a new monitor if:

- You are merely replacing an existing device with an Emulex emulation of the same device. That is, if you already have two DEC DHUlls and you are replacing them with a single CS23/E1, there is no need to regenerate the RSTS/E monitor.

- Your present RSTS/E monitor already includes support for two DHUlls but they have been disabled. To enable them, simply type HARDWR at the INIT.SYS option prompt and answer ENABLE at the HARDWR suboption prompt. When it asks Controller to Enable, answer DHUO (the DEC mnemonic for DHUll). Repeat this for DHUl. To end, type Exit.

Other options (modem controls, etc.) are explained in subsection C.2.3.

# 3.7.1.1 Generating a New Monitor With SYSGEN

If your RSTS/E monitor does not include support for DHUlls, you must generate a new RSTS/E monitor which includes DHUll support. To do this, you must generate a new monitor as described in the DEC RSTS/E System Generation Manual. If the only change you are making to your system is to add the CS23/El, then most of your answers to the SYSGEN questions will not change. The only changes will be made during the Terminal Interface Configuration stage. The questions relating to the CS23/El are the following:

- DHUll's? Answer: This depends on the number of emulations you have programmed with switch SW4-8.

- DHUll unit 00 lines enabled? Answer: 16. This question will be repeated once more for the second emulation. Answer 16 again.

- Dataset support for DHUll's? Answer: yes

When you have finished the questions, you must generate your new monitor from the configuration files created with the system program. Complete the monitor building as described in the DEC RSTS/E manual.

#### 3.7.1.2 Modem Controls

After the RSTS/E monitor is complete, you must configure each CS23/El line as either local or remote. To enable modem controls for one or more lines:

- At the INIT.SYS Option prompt, type SET.

- At the SET suboption prompt, type LIST.

- At the Device prompt, type KB. The computer's response will be a list of all DHUll lines and the keyboard numbers associated with each line. Note down the keyboard numbers of all lines which will require modem support. For an explanation of how DHUll lines are numbered, see subsection 3.6.

- At the SET suboption prompt, type MODEM.

- At the KB prompt, type the keyboard numbers you noted down above. If you are constantly switching modems from line to line, you may enable modem controls for all lines by typing a range. If you do this, be sure to follow the external device cabling instructions in your distribution panel technical manual.

#### 3.7.2 ADDING A NEW DEVICE TO RSX-11M

In general, when a new device is added to the RSX-llM operating system, a completely new operating system must be generated. You do not need to do this if you already have two DEC DHUlls installed and are merely replacing them with a CS23/El.

If you are making no other changes to your system, then most of your answers to the SYSGEN questions will remain the same. The SYSGEN Phase I questions which relate to the CS23/El are the following:

- Autoconfigure the host system?

Answer: Yes, if you wish to use autoconfigure.

- Devices Answer: SYSGEN will print a list of the devices it found during the autoconfigure process. If it is correct, simply type a period. The RSX-llM mnemonic for a DHUll is YV, so autoconfigure should include YVA and YVB in its listing if you are emulating two DHUll's. Note down the bus and vector addresses; you will need them later.

- Loadable device drivers?

Answer: Yes. The DHUll requires a loadable driver.

- Terminal driver desired Answer: Full-duplex

- YV controller 0 Answer: This question asks for the vector and bus addresses for the DHUll, the number of lines on the DHUll, and the default baud rate for remote lines. Autoconfigure should provide the correct responses already, which will look something like this:

340,760260,16,300

If the listed values are not correct, enter the correct values. Note that the default baud rate can be changed after SYSGEN is completed if you wish. If you do not want modem support, enter a default baud rate of zero. The CS23/El emulates up to two DHUlls, and this question will repeat for each emulation. YVO corresponds to the first 16 channels of the CS23/El, and YVl to the second set of 16 channels.

After you have finished the Phase I questions, you must complete Phases II and III as described in the DEC RSX-llM manual.

#### 3.7.2.1 Modem Controls

The MCR command SET can be used to change a terminal's status from remote to local and vice versa. It can also be used to change the baud rate of an individual channel. The command

SET /REMOTE

lists all remote channels. The command

SET /REMOTE=TT5:1200

sets the terminal line corresponding to TT5 as a remote dial-up line with a baud rate of 1200. Similarly, the command

SET /NOREMOTE

lists all local channels, and the command

SET /NOREMOTE=TT5:

sets the terminal line corresponding to TT5 as a local line. To find out which DHUll line corresponds to TTn, you must check your hardware to see which terminals are connected to which ports on the distribution panel. See subsection 3.6 for an explanation of DHUll channel numbering. Any user may use the SET command to change his own characteristics, but only a privileged user may change a channel characteristic of another.

Some users enable modem controls for all channels because they are constantly switching modems from channel to channel. If you do this, be sure to follow the external device cabling instructions in your distribution panel technical manual.

#### 3.7.3 ADDING A NEW DEVICE TO RSX-11M-PLUS

To add a new device to the RSX-llM-Plus operating system, the appropriate device driver must be added to the RSX-llM-Plus kernel. Most devices can be added to RSX-llM-Plus without doing a new SYSGEN. However, this is not the case with communications equipment. When you add the CS23/El, you will need to generate a completely new operating system.

If you are making no other changes to your system, most of your answers to the SYSGEN questions will remain the same. The SYSGEN questions which relate to the CS23/El are the following:

- Enter number of DHUll multiplexers

Answer: This depends on the number of emulations you have selected with switch SW4-8.

- Enter number of DHUll dial-up lines

Answer: List the number of lines which will require modem

support. These lines will be the first lines on your system

(i.e., the lowest numbered channels).

- At which baud rate do you want to answer?

Answer: This question is asked only if you specified one or more dial-up lines. Answer with the baud rate of the modems you are using.

- Enter total number of DHUll local lines

Answer: All lines are either local or dial-up. So, if you specified any dial-up lines, specify the rest as local lines. For example, if you specified 12 dial-up lines, channels DHU0,0 through DHU0,11 would be, dial-up lines and channels DHU0,12, through DHU1,15 would be local lines. See subsection 3.6 for an explanation of DHUll channel numbering.

- Enter vector address of YVA

Answer: this is the interrupt vector address programmed into the CS23/El (see subsection 4.4.4). YV is the RSX-llM-Plus mnemonic for DHUll.

- What is its bus address? Answer: this is the bus address programmed into the CS23/El (see subsection 4.4.3).

The bus and vector addresses must be entered for each DHUll emulation. Enter the bus and vector for each emulation when the question appears.

Enter terminal type for YVA Answer: respond with the terminal types you are using. This can be changed later without doing a new SYSGEN, so choose the default answer if you are not sure what terminal types you will be using.

#### 3.7.4 ADDING A NEW DEVICE TO ULTRIX-11 (V2.0)

Support for new devices MUST be included in a monitor at SYSGEN time. A configuration file is generated (and a monitor is built) with the 'sysgen' program. The following is an example of the dialog form the 'sysgen' program that specifies a CS23/El controller:

Communications devices:

< dz dzv dzg dh dhu dhv dhdm du dn kl dl > ? dhu

Number of units <1> ? 1

CSR address for unit 1 <160020> ? 160440

Vector address for unit 1 <300> ? 300

Communications devices:

< dz dzv dzg dh dhu dhv dhdm du dn kl dl > ?

For more information on configuring a new monitor with the 'sysgen' program, see Appendix C of the Ultrix-ll System Installation Guide.

# 3.7.4.1 Autoconfigure

At boot time, Ultrix-ll attempts to auto-configure the devices included in the booted monitor's configuration file. If the device was not included in the configuration file, it will not be configured into the running system. If the device was included, but is not present, Ultrix-ll will skip it.

#### 3.7.4.2 Enabling Terminals

To enable terminals, there must be a special file created for each line of the CS23/E1. Also the files 'ttys' and 'ttytype' must be edited to reflect the number, availability, and terminal types for each line.

#### 3.7.4.2.1 /dev/ttyxx

The special files can be created with the supplied command file 'msf' in the /dev account. It will create the special files for the devices specified. For example:

#### # msf dhvll 0 tty00

will create the 16 special files for the CS23/El (beginning at tty00 through tty15).

# 3.7.4.2.2 /etc/ttys

The 'ttys' file is used by the 'init' program to determine which terminals to create the login process for (and allow logins). The format for each line is: nctty##

6 = 2400 bits/sec 7 = 4800 bits/sec f = 1200 bits/sec

The remainder of the line is the terminal's entry in the device directory, /dev. An example of this file is as follows:

22console 22tty00 22tty01 22tty02 22tty03 22tty04 22tty05 22tty06 22tty07 22tty08 22tty09 22tty10 22tty11 22tty12 22tty13 22tty14 22tty15

# 3.7.4.2.3 /etc/ttytype

The 'ttytype' file is used by the 'login' program to initialize TERM variables at login time. An example of this file is:

vtl00 console vt100 tty00 vt100 tty01 vtl00 tty02 vt100 tty03 vt100 tty04 vt100 tty05 vt100 tty06 vt100 tty07 vt100 tty08 vt100 tty09 vtl00 ttyl0 vt100 ttyll vtl00 ttyl2 vt100 tty13 vt100 tty14 vt100 tty15

For more information on configuring terminals, see Chapter 4.7 "Enabling User Terminals" in the Ultrix-ll System Management Guide.

# 3.8 INSTALLING THE CS23/El ON THE VAX-11

The CS23/El Communication Subsystem is fully compatible with the DHUll and consequently, it is supported on any VAX UNIBUS under VMS or Ultrix-32.

### 3.8.1 ADDING A NEW DEVICE TO VMS

You can use autoconfigure to automatically connect the CS23/El on power-up. Autoconfigure requires that specific device-types be installed at specific UNIBUS addresses so that it can identify the devices that it finds. VMS has a software utility called SYSGEN that can be used to determine the UNIBUS address and interrupt vector address for any I/O devices to be installed on the computer's UNIBUS. A running VAX/VMS computer system is required to use this utility. If you do not have access to a running system, you will have to determine the UNIBUS addresses and vector addresses manually (although autoconfigure can still be used to automatically connect the devices to the computer on power up). See Appendix A for a description of the algorithm used by SYSGEN to determine UNIBUS addresses.

The following procedure tells how to use SYSGEN to determine UNIBUS CSR addresses and interrupt vectors as well as how to use autoconfigure to connect the CS23/El.

- 1. Login to the system manager's account. Set your default to SYS\$SYSROOT: [SYSEXE].

- 2. Run the SYSGEN utility:

\$ RUN SYSGEN<cr>

SYSGEN>

The SYSGEN> prompt indicates that the utility is ready to accept commands.

3. Obtain a list of devices already installed on the VAX UNIBUS by typing:

SYSGEN> SHOW/CONFIGURATION<cr>

SYSGEN will list the devices already installed in the UNIBUS by logical name. Make a note of the devices with floating addresses (greater than 7600008) or floating vectors (greater than 3008) that you plan to re-install with your CS23/E1.

4. To determine the UNIBUS addresses and vectors that autoconfigure will expect for that device type, execute the CONFIGURE command:

SYSGEN> CONFIGURE < cr> DEVICE>

Specify the UNIBUS devices to be installed by typing their UNIBUS names at the DEVICE prompt:

DEVICE> DHUll,2<cr>

A comma separates the device name from the number of devices of that type to be installed. The number of devices is specified in decimal.

For the installation of the CS23/El, you need only specify devices that have floating addresses or vectors. Devices with fixed addresses or vectors will not affect the address or vector assignments of devices with floating addresses and vectors.

5. Indicate that all devices have been entered by pressing the CTRL and Z keys simultaneously:

DEVICE> ^Z

SYSGEN will list the addresses and vectors of the devices entered in the format shown in Figure 3-1.

DEVICE> DZ11 DEVICE> DMC11 DEVICE> DHUll,2 DEVICE> ^Z CSR: 760070\* Vector: 300\* Support: yes Device: DMCll Name: XMA Vector: 310\* CSR: 760110\* Support: yes Name: TTA Device: DZ11 Name: COMB CSR: 760500\* Vector: 320\* Support: yes Device: DHUll Name: COMB CSR: 760520\* Vector: 330\* Support: yes Device: DHUll

SYSGEN> CONFIGURE

# Figure 3-1. CONFIGURE Device Listing

- 6. Note the CSR addresses listed for the UNIBUS devices in floating address space. Program the listed addresses into non-Emulex devices as instructed by that manufacturer's documentation. For the CS23/El, program the address given for the first device (lowest numerical address) into the CC23 Controller as described in subsection 4.4.3.

- 7. A command to initiate autoconfigure during power-up must be included in one of several start up command files on the system. As shipped from DEC, this command is included in SYS\$SYSTEM:STARTUP.COM file. See Figure 3-2 for an example of the command.

<sup>\*</sup>Floating address or vector.

8. Emulex recommends setting the default line parameters as shown in Figure 3-2.

```

$!

$!

TXAO: IS NOW CONNECTED TO A DIAL UP LINE AND A MODEM

SI

$SET TERMINAL TXA0:/SPEED=1200/MODEM/HANGUP/VT100/PERM

$!

$SET TERMINAL TXA1:/SPEED=9600/PERM/VT100

$SET TERMINAL TXA2:/SPEED=9600/PERM/VT100

$SET TERMINAL TXA2:/SPEED=9600/PERM/VT100

$SET TERMINAL TXA3:/SPEED=9600/PERM/VT100

$SET TERMINAL TXA4:/SPEED=9600/PERM/VT100

$SET TERMINAL TXA5:/SPEED=9600/PERM/VT100

$SET TERMINAL TXA6:/SPEED=9600/PERM/VT100

$SET TERMINAL TXA7:/SPEED=9600/PERM/VT100

$SET TERMINAL TXB0:/SPEED=9600/PERM/VT100

$SET TERMINAL TXB1:/SPEED=9600/PERM/VT100

$SET TERMINAL TXB2:/SPEED=9600/PERM/VT100

$SET TERMINAL TXB3:/SPEED=9600/PERM/VT100

$SET TERMINAL TXB4:/SPEED=9600/PERM/VT100

$SET TERMINAL TXB5:/SPEED=9600/PERM/VT100

$SET TERMINAL TXB6:/SPEED=9600/PERM/VT100

$SET TERMINAL TXB7:/SPEED=9600/PERM/VT100

```

Figure 3-2. DHUll Autoconfigure Command File

### 3.8.2 ADDING A NEW DEVICE TO ULTRIX-32 (V1.1)

Support for new devices MUST be included in a monitor at SYSGEN time. The configuration file is edited to reflect the number of controllers and devices connected to each controller.

The following example is from a configuration file that specifies a single CS23/El controller:

device dhu0 at uba0 csr 0160440 flags 0xff vector dhurint dhuxint

The flag value is a binary value that specifies which terminals are 'hard wired', where bit zero corresponds to therminal line 0, etc.

### 3.8.2.1 Autoconfigure

At boot time, Ultrix-32 attempts to auto-configure the devices included in the booted monitor's configuration file. If the device was not included in the configuration file, it will not be configured into the running system. If the device was included, but is not present, Ultrix-32 will skip it.

When Ultrix-32 finds a device at autoconfigure time it prints a message as follows:

dhu0 at uba0 at csr 160440 vec 300, ipl 15

The CSR addresses were set in the configuration file. The vectors are set with the switches on the controller board. The operating system 'pokes' the device and records it's interrupt vector address. If the CSR doesn't match the configuration file, the device will be skipped (and no message will be printed).

# 3.8.2.2 Enabling Terminals

To enable terminals, there must be a special file created for each line of each emulation of the CS23/El. Also the files 'ttys' and 'ttytype' must be edited to reflect the number, availability, and terminal types for each line.

### 3.8.2.2.1 /dev/ttyxx

The special files can be created with the supplied command file 'MAKEDEV' in the /dev account. It will create the special files for the devices specified. For example:

### # MAKEDEV dhu0

will create the 16 special files for the CS23/E1.

# 3.8.2.2.2 /etc/ttys

The 'ttys' file is used by the 'init' program to determine which terminals to create the login process for (and allow logins). The first digit is either '0' or 'l'. If the first character is a a zero (0), the 'init' program ignores that line. If the first character is a one (1), the 'init' program creates a login process for that line. The second character is an argument to the 'getty' program. It determines the autobaud speed detection pattern. The remainder of the line is the terminal's entry in the device directory, /dev. An example of this file follows:

# Installing the CS23/El on the VAX-11

```

12console

12ttyA0

12ttyAl

12ttyA2

12ttyA3

12ttyA4

12ttyA5

12ttyA6

12ttyA7

12ttyA8

12ttyA9

12ttyAa

12ttyAb

12ttyAc

12ttyAd

12ttyAe

12ttyAf

```

# 3.8.2.2.3 /etc/ttytype

The 'ttytype' file is used by the 'login' program to initialize TERM variables at login time. An example of this file is:

```

vtl00 console

vtl00 ttyA0

vtl00 ttyAl