# MB01 MULTIBUS HOST ADAPTER TECHNICAL MANUAL

3545 Harbor Boulevard Costa Mesa, California 92626 (714) 662-5600 TWX 910-595-2521

HA5151001 Rev 06 April, 1985

### WARNING

This equipment generates, uses and can radiate radio frequency energy, and if not installed and used in accordance with the instructions in this technical manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of Federal Communications Commission (FCC) Rules, which are designed to provide reasonable protection against such interference in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Emulex is a registered trademark of Emulex Corporation.

Medalist, Champion, and Titleist are trademarks of Emulex Corporation.

Multibus is a registered trademark of Intel Corporation.

Copyright (C) 1984 Emulex Corporation

The information in this manual is for information purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in the manual.

Printed in U.S.A.

# TABLE OF CONTENTS

| ONE                                                                     | G ENERAL                                                             | DESC                                                                             | RIPI                                                   | MOI                                               |                                                                                 |                                                            |                                   |                          |                                       |                  |       |       |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |                                         |                                         |                                         |                                         |   |                                                                    |

|-------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------|--------------------------|---------------------------------------|------------------|-------|-------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|---|--------------------------------------------------------------------|

| 1.1                                                                     | OV ER                                                                | VIEW                                                                             |                                                        |                                                   |                                                                                 |                                                            |                                   |                          |                                       |                  |       |       |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |                                         |                                         |                                         |                                         |   | 1-1                                                                |

| 1.1.1                                                                   |                                                                      | LATEI                                                                            |                                                        |                                                   |                                                                                 |                                                            |                                   |                          |                                       |                  |       |       |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |                                         |                                         |                                         |                                         |   | 1-2                                                                |

| 1.1.2                                                                   |                                                                      | CHNIC                                                                            | AL M                                                   | IANUA                                             | L                                                                               | VNC                                                        | ENT                               | יסדי                     | NS                                    | • • •            |       | • •   |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • •                                     |                                         | • •                                     |                                         | • •<br>                                 | • | 1-2                                                                |

| 1.2                                                                     |                                                                      | ICAL                                                                             | DESC                                                   | RIPT                                              | ION                                                                             | 1                                                          |                                   |                          |                                       | • • •            |       | ••    | • • • |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ••                                      | ••                                      | • •                                     | •                                       | • •                                     | • | 1-3                                                                |

| 1.3                                                                     | FUNC                                                                 | TIONA                                                                            | L DE                                                   | SCRI                                              | PT]                                                                             | ON                                                         |                                   | • •                      |                                       | •                |       | ••    | • • • |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ••                                      | ••                                      | • •                                     |                                         | • •                                     | • | 1-4                                                                |

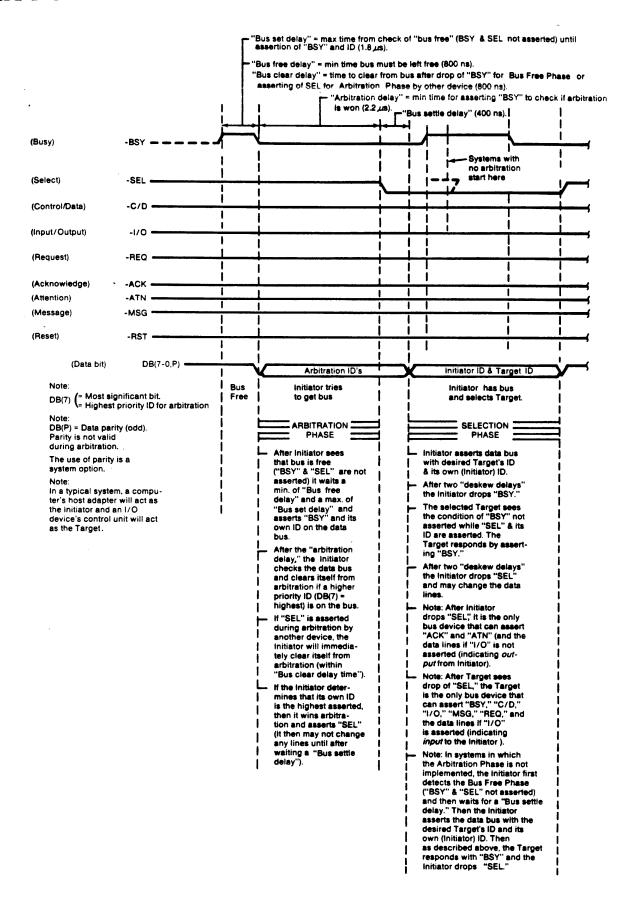

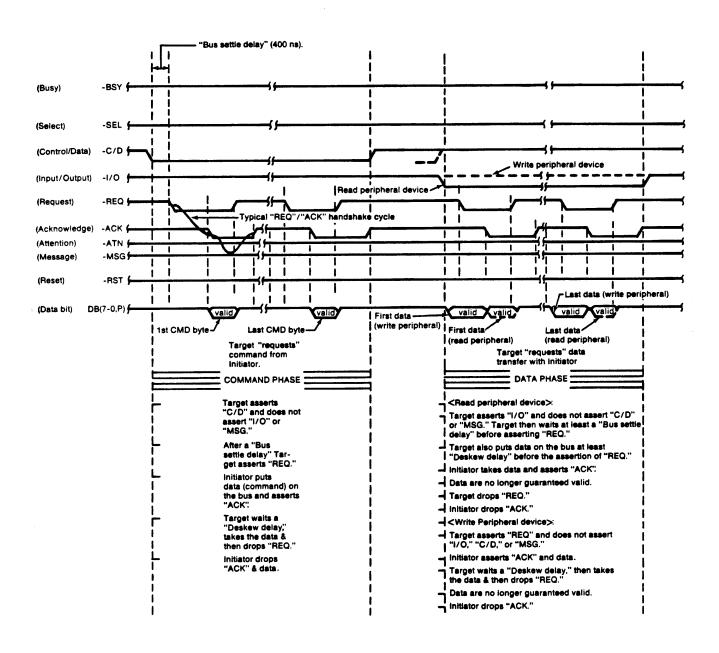

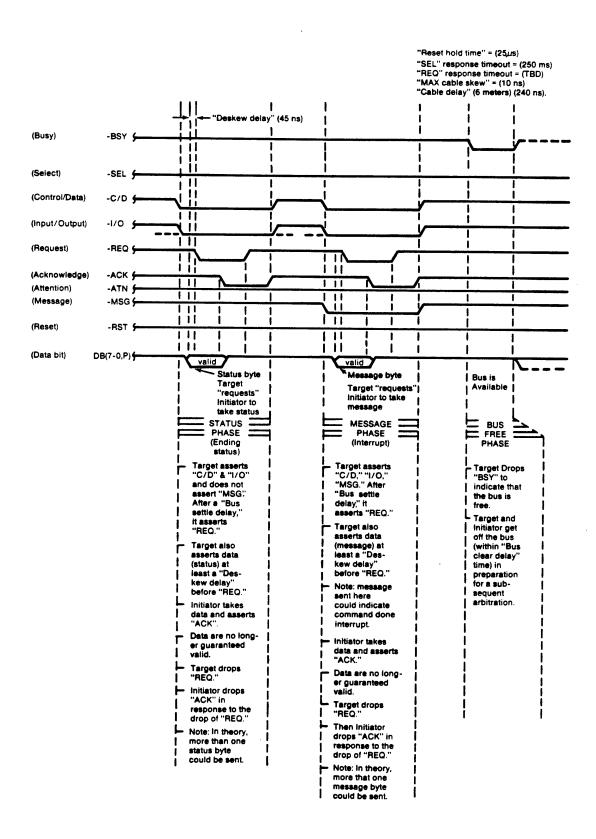

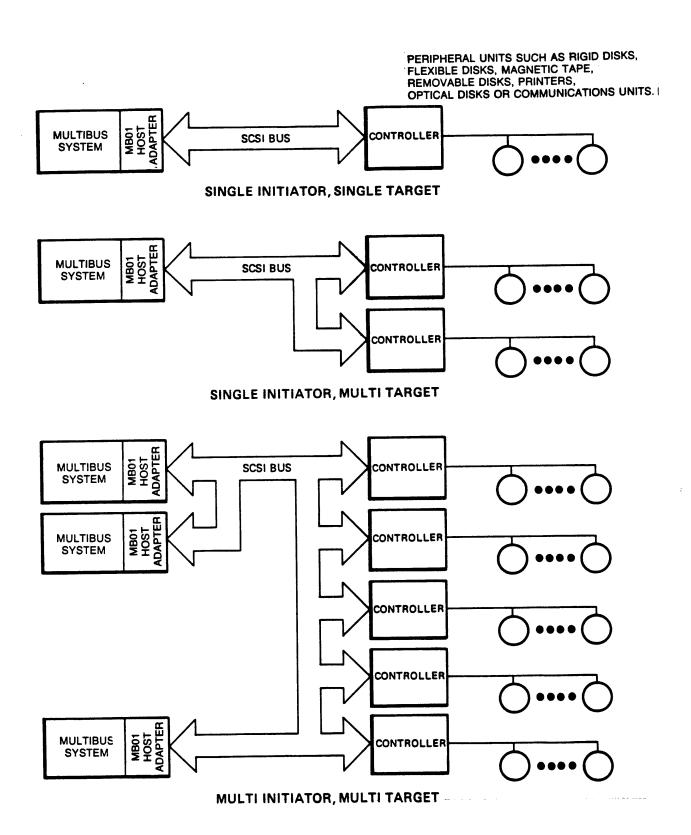

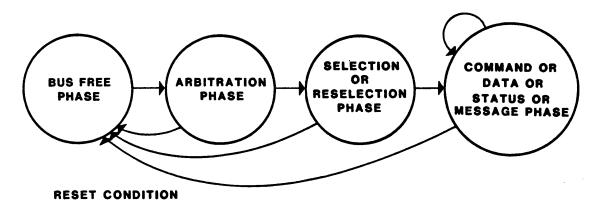

| 1.4                                                                     | SCSI                                                                 | BUS                                                                              | DESC                                                   | RIPT                                              | ION                                                                             | 1                                                          | • • •                             |                          |                                       |                  |       |       |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | ••                                      |                                         |                                         |                                         |   | 1-4                                                                |

| 1.5                                                                     | MULT                                                                 | BUS                                                                              | DESC                                                   | RIPT                                              | ION                                                                             |                                                            | • • •                             |                          |                                       |                  |       |       | • • • |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | ••                                      | • •                                     |                                         | • •                                     | • | 1-5                                                                |

| 1.6                                                                     | FEAT                                                                 | URES                                                                             |                                                        | • • • •                                           |                                                                                 |                                                            | • • •                             | •                        | • • •                                 |                  |       | • •   | • • • |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                       |                                         |                                         |                                         |                                         | • | 1-5                                                                |

| 1.6.1                                                                   | MB                                                                   | 01 HC                                                                            | ST A                                                   | DAPT                                              | ER                                                                              | SCS                                                        | ΙB                                | US                       | FE                                    | ATU              | JRE   | S     | • • • |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • •                                     | • •                                     |                                         |                                         |                                         |   | 1-5                                                                |

| 1.6.2                                                                   | MB                                                                   | D1 HC                                                                            | ST A                                                   | DAPT                                              | ER                                                                              | MUL                                                        | TIB                               | US                       | FE                                    | ATI              | JRE   | S     | • • • | •       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                       | •                                       |                                         |                                         |                                         |   | 1-6                                                                |

| 1.6.3                                                                   | DM                                                                   | A OPE                                                                            | RATI                                                   | ON .                                              |                                                                                 |                                                            | • • •                             | • •                      |                                       | • • •            |       |       | • • • |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • •                                     |                                         |                                         |                                         |                                         |   | 1-7                                                                |

| 1.6.4                                                                   | MB                                                                   | 01 HC                                                                            | ST A                                                   | DAPT                                              | ER                                                                              | I/O                                                        | OF                                | ER                       | ATI                                   | ONS              | 3.    |       | • • • |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • •                                     |                                         |                                         |                                         |                                         | • | 1-7                                                                |

| 1.6.5                                                                   | <b>co</b> :                                                          | NFIGU                                                                            | RATI                                                   | ON S                                              | riw                                                                             | CH E                                                       | s.                                |                          |                                       | • • •            |       | • •   | • • • |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • •                                     | •                                       |                                         | •                                       |                                         | • | 1-7                                                                |

| 1.7                                                                     | COMP                                                                 | AT IB I                                                                          | LITY                                                   |                                                   |                                                                                 |                                                            |                                   |                          |                                       | • • •            |       |       | • • • |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • •                                     | ••                                      |                                         | •                                       |                                         | • | 1-8                                                                |

| 1.7.1                                                                   | sc                                                                   | SI BU                                                                            | s co                                                   | MPAT                                              | IB I                                                                            | LIT                                                        | Y.                                |                          |                                       |                  |       |       |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |                                         |                                         |                                         |                                         | • | 1-8                                                                |

| 1.7.1                                                                   | .1                                                                   | Hardw                                                                            | are                                                    | Comp                                              | ati                                                                             | bil                                                        | itv                               |                          |                                       | • • •            |       |       |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ••                                      | ••                                      |                                         | •                                       | · •                                     | • | 1-8                                                                |

| 1.7.1                                                                   | . 2                                                                  | Softw                                                                            | are                                                    | Comp                                              | ati                                                                             | bil                                                        | itv                               |                          |                                       |                  |       |       |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ••                                      |                                         |                                         |                                         | • •                                     | • | 1-8                                                                |

| 1.7.2                                                                   |                                                                      | LTIBU                                                                            | is co                                                  | MPAT                                              | IB I                                                                            | LIT                                                        | Y.                                |                          |                                       |                  |       | ••    |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • •                                     |                                         |                                         | •                                       |                                         | • | 1-8                                                                |

| 1.7.2                                                                   | .1                                                                   | Hardw                                                                            | are                                                    | Comp                                              | ati                                                                             | bil                                                        | itv                               | •                        |                                       |                  |       |       |       | • • •   | • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • •                                     | ••                                      | • •                                     | • •                                     | • •                                     | • | 1-8                                                                |

| 1.7.2                                                                   |                                                                      | Softw                                                                            | are                                                    | Comp                                              | ati                                                                             | bil                                                        | itv                               | •                        |                                       |                  |       |       | • • • | • • •   | • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • •                                     | ••                                      | • •                                     | • •                                     | • •                                     | • | 1-9                                                                |

| 1.7.3                                                                   |                                                                      | MPATI                                                                            | BILT                                                   | יש צידי                                           | TTH                                                                             | חיי                                                        | HER                               | E                        | MTTT.                                 | EX               | DR    | ומט   | יי    | פי      | • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • •                                     | • •                                     | • •                                     | •                                       | • •                                     | • | 1-9                                                                |

|                                                                         |                                                                      |                                                                                  |                                                        |                                                   |                                                                                 |                                                            |                                   |                          |                                       | ~                |       | .00   |       |         | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ••                                      | ••                                      | • •                                     | • •                                     | •                                       | • | 1-9                                                                |

| TWO                                                                     | MB01 HO                                                              | מג מפ                                                                            | א ואמו ב                                               | יתם מי                                            | P/T                                                                             | . D.T.C                                                    | 3 M T                             | <b>ORT</b>               | ~                                     |                  |       |       |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |                                         |                                         |                                         |                                         |   |                                                                    |

| 140                                                                     | ADUI HO                                                              | or wh                                                                            | AFIE                                                   | ik op.                                            | PC1                                                                             | FIC                                                        | WII                               | UR                       | •                                     |                  |       |       |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |                                         |                                         |                                         |                                         |   |                                                                    |