## SC31/BX

(RM02/RM03/RM05/RM80, RP06 COMPATIBLE)

DISK CONTROLLER

TECHNICAL MANUAL

3545 Harbor Boulevard Costa Mesa, California 92626 (714) 662-5600 TWX 910-595-2521

Copyright (C) 1983 by Emulex Corporation

The information in this manual is for informational purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

# TABLE OF CONTENTS

| Section | 1                                                                                                                                                 | INTRODUCTION                                                                                                                                                                                                                                                                 |                                                                                         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|         | 1.1<br>1.2<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.3.5<br>1.3.6<br>1.3.7<br>1.3.8<br>1.4.1<br>1.4.1<br>1.4.2<br>1.4.3<br>1.4.4                   | SCOPE OVERVIEW FEATURES Microprocessor Design Packaging Self-Test Buffering Error Correction Option and Configuration Switches Dual Port Capability Dual Access Capability FUNCTIONAL COMPATIBILITY Media Compatibility Disk Mapping Diagnostics Operating Systems           | 1-1<br>1-1<br>1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-3<br>1-3        |

| Section | 2                                                                                                                                                 | GENERAL DESCRIPTION                                                                                                                                                                                                                                                          |                                                                                         |

|         | 2.1<br>2.2<br>2.2.1.1<br>2.2.1.2<br>2.2.1.3<br>2.2.2<br>2.2.3<br>2.3.1<br>2.3.1.1<br>2.3.1.2<br>2.3.1.3<br>2.3.2<br>2.3.2.1<br>2.3.2.2<br>2.3.2.1 | Connectors A Cable Connector B Cable Connector Test Connectors Switches Indicators PROMS INTERFACES Disk Interface Drivers and Receivers A Cable B Cable Unibus Interface BR (Interrupt) Priority Level Register Address DCLO and INIT Signals DISK FORMAT Disk Organization | 2-1<br>2-4<br>2-4<br>2-4<br>2-4<br>2-4<br>2-5<br>2-5<br>2-5<br>2-5<br>2-8<br>2-8<br>2-8 |

| t       | 2.4.2<br>2.4.3<br>2.4.4.1<br>2.4.4.2<br>2.5<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4                                                                   | Mapping Sector Organization Header Header Description Header Field Handling GENERAL PROGRAMMING INFORMATION Clearing the Controller Interrupt Conditions Termination of Data Transfers Ready Bits                                                                            | 2-8<br>2-8<br>2-10<br>2-10<br>2-11<br>2-11<br>2-12<br>2-12                              |

| 2.6.3<br>2.6.4<br>2.6.5<br>2.6.6                                                                                                                                               | Dual Port Drives<br>Unseized State<br>Seized State<br>Returning to the Unseized State                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-14                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Section 3                                                                                                                                                                      | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |

| 3.2.3<br>3.2.4<br>3.2.5<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.5.1<br>3.4.5.1<br>3.4.5.2<br>3.4.5.3<br>3.4.5.4<br>3.4.5.5<br>3.4.5.6<br>3.4.5.6<br>3.4.5.7<br>3.4.5.8 | DISK DRIVE PREPARATION Drive Placement Local/Remote Sectoring Drive Numbering Sector and Index Modifications SYSTEM PREPARATION CONTROLLER SETUP Controller Address Selection Interrupt Vector Address Drive Configuration Selection Index and Sector Pulse Selection SC31/BX Options Logical Unit Swap Replacement Track Mode Dual Port Mode DMA Bandwidth Control Sector and Index Signals Dual Access Mode Sector Interleave Defeat Suspended DMA Option Mapping Two RP06s on 19 Head Drives PHYSICAL INSTALLATION SPC Slot Selection | 3-6<br>3-6<br>3-6<br>3-6<br>3-6<br>3-8<br>3-8 |

| Section 4                                                                                                                                                                      | CONTROLLER REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| 4.1<br>4.1.1                                                                                                                                                                   | OVERVIEW Common Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-1<br>4-1                                    |

| 4.2            | CONTROL/STATUS REGISTER ONE                                         | 4-1  |

|----------------|---------------------------------------------------------------------|------|

|                | (RPCS1/RMCS1)                                                       |      |

| 4.3            | WORD COUNT REGISTER (RPWC/RMWC) UNIBUS ADDRESS REGISTER (RPBA/RMBA) | 4-3  |

| 4.4            | UNIBUS ADDRESS REGISTER (RPBA/RMBA)                                 | 4-3  |

| 4.5            | DISK ADDRESS REGISTER (RPDA/RMDA)                                   | 4-4  |

| 4.6            | CONTROL/STATUS REGISTER TWO                                         | 4-4  |

|                | (RPCS2/RMCS2)                                                       |      |

| 4.7            | DRIVE STATUS REGISTER (RPDS/RMDS)                                   | 4-6  |

|                | ERROR REGISTER ONE (RPER1/RMER1)                                    | 4-8  |

| 4.9            | ATTENTION SHMMARY REGISTER (RPAS/RMAS)                              | 4-10 |

| 4.10           | LOOK-AHEAD REGISTER (RPLA/RMLA) DATA BUFFER (RPDB/RMDB)             | 4-11 |

| 4.11           | DATA BUFFER (RPDB/RMDB)                                             | 4-11 |

| 4.12           | MAINTENANCE REGISTERS                                               | 4-11 |

| 4.12.1         |                                                                     | 4-11 |

|                | Maintenance Register (RPMR)                                         |      |

| 4 13           | DRIVE TYPE REGISTER (RPDT/RMDT)                                     | 4-12 |

| 4 1 A          | CEDIAL MUMDED DECICHED (DDCM/DMCM)                                  | 4-12 |

| 7 1E           | SERIAL NUMBER REGISTER (RPSN/RMSN) OFFSET REGISTER (RPOF/RMOF)      | 4-13 |

| 4.16           | DECIDED CVITNDED DECIGNED (DDDG (DNDG)                              | 4-13 |

|                |                                                                     | 4-14 |

|                | CURRENT CYLINDER AND HOLDING REGISTERS                              |      |

| 4.17.1         |                                                                     | 4-15 |

| 4.17.2         | - J \                                                               | 4-15 |

| 4.18           |                                                                     |      |

| 4.18.1         | Maintenance Register Two (RMMR2)                                    | 4-16 |

| 4.18.2         |                                                                     | 4-16 |

| 4.19           |                                                                     |      |

| 4.19.1         | Error Register Two (RMER2)                                          | 4-16 |

| 4.19.2         | Error Register Three (RPER3)                                        | 4-18 |

| 4.20           | ECC POSITION REGISTER (RPEC1/RMEC1)                                 | 4-19 |

| 4.21           | ECC PATTERN REGISTER (RPEC2/RMEC2)                                  | 4-19 |

| Coation E      | COMMANDO                                                            |      |

| Section 5      | COMMANDS                                                            |      |

| E 1            | OVERVITED OF COMMANDS                                               | 5-1  |

| 5.1            | OVERVIEW OF COMMANDS                                                |      |

| 5.4            | DATA TRANSFER COMMANDS                                              | 5-1  |

| 5.2.1          | Write Check Data (51)<br>Write Check Header and Data (53)           | 5-2  |

| 5.2.2          | Write Check Header and Data (53)                                    | 5-2  |

| 5.2.3<br>5.2.4 | Write Data (61)                                                     | 5-2  |

| 3.2.4          | Write Header and Data                                               | 5-2  |

| 5.2.5          | (format operation) (63)                                             | F 0  |

| 5.2.6          | Read Data (71)                                                      | 5-2  |

| 5.3            | Read Header and Data (73)                                           | 5-3  |

|                | POSITIONING COMMANDS                                                | 5-3  |

| 5.3.1          | Unload (03)                                                         | 5-3  |

| 5.3.2          | Seek Command (05)                                                   | 5-3  |

| 5.3.3          | Recalibrate (07)                                                    | 5-4  |

| 5.3.4          | Offset Command (15)                                                 | 5-4  |

| 5.3.4.1        | Offset Command for RP Drives                                        | 5-4  |

| 5.3.4.2        | Offset Command for RM Drives                                        | 5-4  |

| 5.3.5          | Return-to-Centerline Command (17)                                   | 5-5  |

| 5.3.5.1        | Return-to-Centerline for RP Drives                                  |      |

| 5.3.5.2        | Return-to-Centerline for RM Drives                                  | 5-5  |

|          | 5.3.6                                         |                                                           | 5-5          |

|----------|-----------------------------------------------|-----------------------------------------------------------|--------------|

|          | 5.4                                           | HOUSEKEEPING COMMANDS                                     |              |

|          | 5.4.1<br>5.4.2<br>5.4.2.1<br>5.4.2.2<br>5.4.3 | No Op (01)                                                | 5-5          |

|          | 5.4.2                                         | Drive Clear (11)                                          | 5-5          |

|          | 5.4.2.1                                       | Drive Clear for RP Drives                                 | 5-5          |

|          | 5.4.2.2                                       | Drive Clear for Dw Drives                                 | 5-5          |

|          | 5.4.3                                         | Drive Clear for RM Drives                                 | 5-5          |

|          | 5.4.4                                         | Release Command (13)<br>Read-In Preset (21)               | 5-6          |

|          | 5.4.4.1                                       | Read-In Preset (21)                                       | 5-6          |

|          | 5 4 4 0                                       |                                                           | 5-6          |

|          | 5.4.4.2                                       | Read-In Preset for RM Drives                              | 5-6          |

|          | 5.4.5                                         | Pack Acknowledge (23)                                     | 5-6          |

|          | 5.5                                           | OPTIONAL COMMANDS                                         | 5-6          |

|          | 5.5.1                                         | DMA Bandwidth Set (25)                                    | 5 <b>-</b> 6 |

|          | 5.5.2                                         | DMA Burst Length (27)                                     | 5-7          |

|          | 5.5.3                                         | Suspended DMA Stall Count (35)                            | 5-7          |

|          | 5.5.4                                         | Transparent ECC Correction (33)                           | 5-7          |

|          | 5.5.5                                         | Transparent ECC Correction (37)                           | 5-7          |

|          | 5.5.6                                         | Word Count Equals Sector Count (41)                       |              |

|          | 5.5.0                                         | Physical Read/Write/Write Check                           | 5-8          |

|          | c c -                                         | Header and Data                                           |              |

|          | 5.5./                                         | Format (77)                                               | 5-9          |

|          | 5.5.7.1                                       | Format (77) Format for RP Drives                          | 5-9          |

|          | 3.3./.2                                       | Format for RM Drives                                      | 5-9          |

|          | 5.5.8                                         | Automatic Skip-Sector Feature                             | 5-9          |

|          |                                               |                                                           | _            |

| Appendix | A                                             | SC31/BX CONFIGURATION AND OPTION SELECT                   | TON          |

|          |                                               |                                                           |              |

|          | A.1                                           | INTRODUCTION                                              | A-1          |

|          | A.2                                           | CONTROLLER CONFIGURATION                                  |              |

|          | A.2.1                                         |                                                           | A-1          |

|          | 3 7 7 7                                       | Unit Number Assignment                                    | A-T          |

|          | A.2.2                                         | Unit Number Assignment Sectoring CDC Drives and the 2351A | A-1          |

|          | *** 2 • 2                                     | Beccoring CDC Drives and the 2351A                        | A-2          |

|          | X 2 2                                         | Fujitsu                                                   |              |

|          | A.2.3                                         | Drive Configuration Selection                             | A-2          |

|          | A.3                                           | USER SELECTABLE OPTIONS                                   | A-9          |

| Amma 34  | _                                             |                                                           |              |

| Appendix | В                                             | DRIVE MODIFICATIONS                                       |              |

|          |                                               |                                                           |              |

|          | B.1                                           | CDC 9766                                                  | B-1          |

|          | B.2                                           | TRIDENT DRIVES                                            | B-1          |

|          | B.3                                           | FUJITSU DRIVES                                            | B-1          |

|          | B.4                                           | CDC 9775                                                  |              |

|          | B.5                                           | CDC 9762                                                  | B-2          |

|          | B.6                                           | CDC 9730                                                  | B-2          |

|          | _,,                                           | GDC 3730                                                  | B-3          |

| Appendix | C                                             | EMILEY MODIFICATIONS TO DES PROS PERSON                   |              |

| PP-11-CL | · ·                                           | EMULEX MODIFICATIONS TO DEC RM02 DIAGNO                   | STICS        |

|          | C.1                                           | C7DMIDO DMO2/DMO0 DIGHT DGG                               |              |

|          | C.1                                           | CZRMJBO - RM03/RM02 DISKLESS                              | C-1          |

|          | C 2                                           | DIAGNOSTICS                                               |              |

|          | C.2                                           | CZRMCBO - RM03/RM02 FUNCTIONAL TEST -                     | C-1          |

|          | 0 0                                           | PART 1                                                    |              |

|          | C.3                                           | CZRMDBO - RM03/RM02 FUNCTIONAL TEST -                     | C-3          |

|          |                                               | PART 2                                                    |              |

|          | C.4                                           | CZRMEBO - RM03/RM02 FUNCTIONAL TEST -                     | C-4          |

|          |                                               | PART 3                                                    | - •          |

|          | C.5  | CZRMFBO - RM03/RM02 EXTENDED TEST DRIVE                   | C-6  |

|----------|------|-----------------------------------------------------------|------|

|          | C.6  | CZRMIBO - RM03/RM02 COMPATIBILITY TEST                    | C-7  |

|          | C.7  | CZRMACO - RM03/RM02 FORMATTER                             | C-7  |

|          | C.8  | CZRMBBO - RM03/RM02 PERFORMANCE<br>EXERCISER              | C-9  |

|          | C.9  | CZRMGBO - RM03/RM02 DUAL PORT LOGIC<br>TEST - PART 1      | C-10 |

|          | C.10 | CZRMHBO - RM03/RM02 DUAL PORT LOGIC<br>TEST - PART 2      | C-10 |

| Appendix | D    | MODIFICATIONS TO DEC RP06 DIAGNOSTICS                     |      |

|          | D.1  | CZRJGBO - RP04/5/6 DISKLESS CONTROLLER<br>TEST - PART 1   | D-1  |

|          | D.2  | CZRJHBO - RPO4/5/6 DISKLESS CONTROLLER<br>TEST - PART 2   | D-2  |

|          | D.3  | CZRJIBO - RPO4/5/6 FUNCTIONAL<br>CONTROLLER TEST - PART 1 | D-3  |

|          | D.4  | CZRJJBO - RP04/5/6 FUNCTIONAL<br>CONTROLLER TEST - PART 2 | D-4  |

|          | D.5  | DZRJA-B-D - RP04/5/6 MECHANICAL AND<br>READ-WRITE TEST    | D-5  |

|          | D.6  | CZRJBBO - RP04/5/6 FORMATTER PROGRAM                      | D-5  |

|          | D.7  | CZRJDC0 - RP04/5/6 MULTIDRIVE EXERCISER                   | D-5  |

| -        | D.8  | CZRJCBO - RP04/5/6 HEAD ALIGNMENT<br>PROGRAM              | D-6  |

|          | D.9  | CZRJEBO - RPO4/5/6 DUAL CONTROLLER<br>LOGIC TEST - PART 1 | D-6  |

|          | D.10 | DZRJF-A-D - RP04/5/6 DUAL CONTROLLER<br>LOGIC TEST        | D-6  |

## LIST OF TABLES

| Table No.                                                                    | <u>Title</u>                                                                                                                                        | <u>Page</u>                                    |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Table 1-1                                                                    | General Specification                                                                                                                               | 1-5                                            |

| Table 2-1                                                                    | Disk Drive Connections                                                                                                                              | 2-6                                            |

| Table 2-2                                                                    | SPC Unibus Connections                                                                                                                              | 2-7                                            |

| Table 2-3                                                                    | Register Access on Dual Controller Operation                                                                                                        | 2-17                                           |

| Table 3-1                                                                    | Controller Address Switch Settings                                                                                                                  | 3-4                                            |

| Table 3-2                                                                    | Interrupt Vector Address Switch<br>Settings                                                                                                         | 3-4                                            |

| Table A-l                                                                    | Drives Supported                                                                                                                                    | A-3                                            |

| Table A-2                                                                    | Drive Configurations                                                                                                                                | A-3                                            |

| Table A-3                                                                    | Non-Standard Drive Sizes                                                                                                                            | A-9                                            |

| Table A-4                                                                    | Factory Switch Settings                                                                                                                             | A-10                                           |

| Table A-5                                                                    | Option Switch SWl Settings                                                                                                                          | A-10                                           |

| Table A-6                                                                    | Option Switch SW2 Settings                                                                                                                          | A-11                                           |

| Table A-7                                                                    | Option Switch SW3 Settings                                                                                                                          | A-11                                           |

|                                                                              | LIST OF FIGURES                                                                                                                                     |                                                |

| Figure No.                                                                   | Title                                                                                                                                               | Page                                           |

| Figure 2-1 Figure 2-2 Figure 2-3 Figure 2-4 Figure 3-1 Figure 3-2 Figure 3-3 | SC31 Block Diagram SC31 Controller Board RM Sector Format RM Header Format SC31 Controller Assembly NPG Signal Jumper Location SC31 Cabling Diagram | 2-2<br>2-3<br>2-9<br>2-9<br>3-3<br>3-7<br>3-10 |

|                                                                              | <u> </u>                                                                                                                                            |                                                |

#### 1.1 SCOPE

This manual provides information related to the capabilities, design, installation, and use of the SC31/BX Disk Controllers. In addition, this manual provides diagnostic and application information.

#### 1.2 OVERVIEW

The SC31/BX Disk Controller is a one-board embedded controller for PDP-11 and VAX-11 computers manufactured by Digital Equipment Corporation (DEC). This controller can be used to interface any large disk having a Storage Module Drive (SMD) interface. The SC31/BX series of controllers is capable of emulating the DEC RJM02/05, RM80 and RJP06 Massbus disk subsystems. This controller is capable of operating with disk drives having different characteristics from those used in the DEC disk subsystems. The SC31/BX controller provides the capability of operating with a mixture of disks having storage capacities ranging from five to 600 megabytes.

#### 1.3 FEATURES

Features that enhance performance and increase versatility are described in the following paragraphs. Table 1-1 lists and describes specifications for the SC31/BX Disk Controller.

#### 1.3.1 <u>Microprocessor Design</u>

The SC31/BX design incorporates a unique (patent pending) 16-bit bipolar microprocessor to perform all controller functions. The microprocessor approach provides for a reduced component count, high reliability, easy maintainability, and most importantly, the ability to adapt a single set of hardware to a wide range of emulation capabilities through the use of microprogramming. The Emulex controllers achieve functional capability beyond that of the DEC controllers they emulate, by providing enhancement features such as built-in self-test during power-up, built-in disk formatting and the ability to work with disk drives of various capacities.

#### 1.3.2 Packaging

The SC31/BX is constructed on a single hex-size multi-layer printed circuit board assembly (PCBA) which plugs directly into the PDP-11 or VAX-11 chassis, or an expansion chassis. No cabling is required between the computer and the disk controller. The controller obtains its power from the chassis in which it is mounted.

#### 1.3.3 Self-Test

The controller incorporates an internal self-test routine which is executed upon power-up. This test exercises all parts of the microprocessor, buffer and disk data logic. Although this test does not completely test all controller circuitry, successful execution indicates a very high probability that the controller is operational. If the controller fails the self-test, it leaves the Fault LED ON and the controller cannot be addressed from the central processing unit (CPU).

## 1.3.4 Buffering

The controller contains a 4K x 16 bit high-speed random access memory (RAM) buffer used to store the device registers of the controller and drive being emulated plus fourteen sectors of data buffering. Because of the buffering and the strategies used to employ it, data late situations on the Unibus are not possible.

#### 1.3.5 Error Correction

The controller incorporates a 32-bit error correcting code (ECC) capable of correcting single error bursts of up to 11 bits in length and detecting bursts of longer length. The controller determines the location of the error and the error pattern and passes this information to the PDP-11 which performs the actual correction. A 16-bit CRC is employed with the header of every sector.

## 1.3.6 Option and Configuration Switches

Two ten-pole and one four-pole DIP switches are used to configure the controller for various disk capacities, Unibus addresses and certain firmware options. It is possible to select one of several possible combinations of disk characteristics for the four drives which can be handled by the controller, including a mixture of disk sizes and drive type codes.

#### 1.3.7 Dual Port Capability

The controller can operate with disk drives having dual port capability; therefore a second controller can have access to the drive on a priority basis.

#### 1.3.8 Dual Access Capability

To provide compatibility with dual access drivers when configured for dual access, the Dual Access mode is provided. When in this mode, the controller sets DPM in the Drive Type Register and PGM in the Drive Status Register to imitate the DEC neutral state.

## 1.4 FUNCTIONAL COMPATIBILITY

## 1.4.1 Media Compatibility

The SC31/BX is media compatible with DEC RM02/RM03 packs when using a CDC 9762 drive or equivalent, and with DEC RM05 packs when using a CDC 9766 drive or equivalent.

## 1.4.2 Disk Mapping

Depending upon the type and capacity of the disk drive, one or two logical units may be mapped on it. Various mapping organizations are used; some do not leave direct 1:1 correlation between the logical and physical addresses.

## 1.4.3 Diagnostics

The controller executes the following standard DEC RM02/RM03 and DEC RP06 diagnostics:

ZRMA - Formatter

ZRMB - Performance Exerciser

ZRMC - Functional Controller, Part I\*

ZRMD - Functional Controller, Part II\*

ZRME - Functional Controller, Part III\*

ZRMF - Extended Drive Test

ZRMI - Drive Compatibility Test

ZRJA - Mechanical and Read Write Test

ZRJB - Formatter

ZRJD - Multi-Drive Exerciser

ZRJG - Diskless Controller Test - Part 1 \*

ZRJH - Diskless Controller Test - Part 2 \*

ZRJI - Functional Controller Test - Part 1 \*

ZRJJ - Functional Controller Test - Part 2 \*

The diagnostics marked with an asterisk require certain patches to correct coding problems or to bypass unsupported maintenance functions. All diagnostics require patches to run with drive capacities other than that of a standard RM02/RM03 or RP06. In addition, the ZRMB Performance Exerciser will not run on any drive with more than 16 bad sectors.

Emulex has available self-sizing RM diagnostics which have all the required patches, will work on any size drive and can handle 126 bad sectors.

#### 1.4.4 Operating Systems

The SC31/BX controller is compatible with DEC operating systems without modification when emulating any standard DEC disk subsystem. Patches to the operating system are required when operating with other than standard size disks. These patches

numerically redefine the logical drive capacity to the operating system and generally do not involve modification to program instructions.

The RM02/03/05/80 and RP06 disk drives are not supported by all DEC operating systems, in particular, RT11.

# Table 1-1

## GENERAL SPECIFICATIONS

Functional

Emulation DEC RM02/03/05/80, RP04/05/06

Media Compatibility DEC RM02/03/05 with appropriate disk

drives

Drive Interface SMD

Drive Ports

Error Control 32-bit ECC for data and 16-bit CRC for

headers. Correction of single error

burst of up to 11 bits.

Sector Size 256 words (512 bytes)

Sectors/Track Selectable for each drive

Tracks/Cylinder Selectable for each drive

Cylinders/Drive Selectable for each drive

Drive Type Code Selectable for each drive

Computer Interface SPC Unibus

Unibus Address

Standard 776700 (20 Registers) 776300 (20 Registers) 776400 (20 Registers) Alternates 776600 (20 Registers)

Vector Address

Standard 254

Alternates 150, 370, 374, 354, 224, 270, 274

Priority Level BR5

Data Bufferring 14 full sectors

Data Transfer High speed NPR operation

Maximum Disk Data Rate 16 MHz (2 MBytes/second)

## Table 1-1 (cont'd)

Self-Test Extensive internal self-test on powering up Indicators Activity and Fault LEDs Design High-speed bipolar microprocessor using 2901 bit-slice components. Physical Packaging One DEC hex-size PCBA Mounting Any SPC slot in CPU or expansion box Connectors One 60-pin A Cable connector and four 26-pin B Cable connectors (Flat cable types) Electrical Unibus Interface DEC approved line drivers and receivers. Drive Interfaces Differential line drivers and receivers. A Cable cumulative length to 100 feet, B Cable length to 50 feet. Power +5 V, 8 A maximum -15 V, 1 A maximum

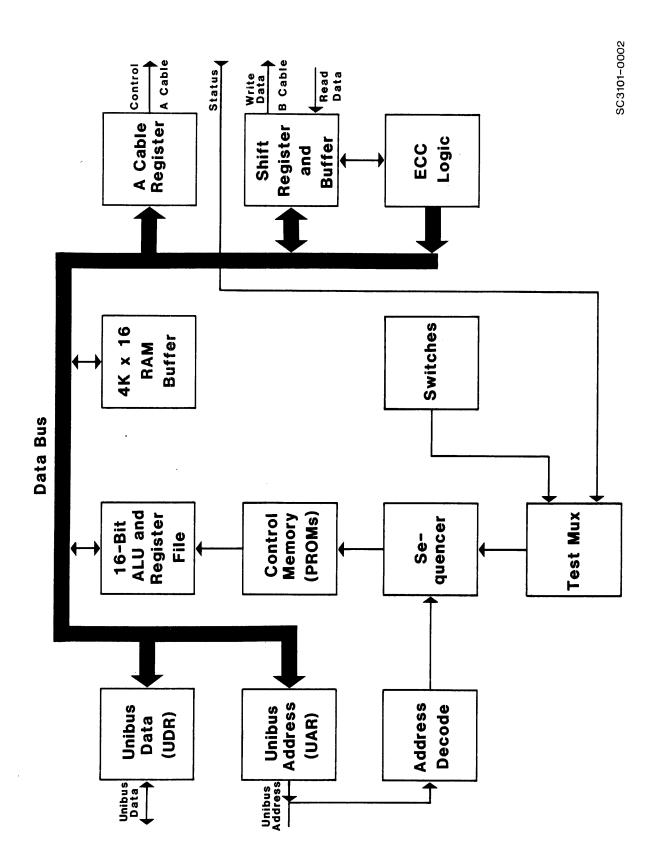

## 2.1 CONTROLLER ORGANIZATION

A block diagram showing the major functional elements of the SC31/BX controller is shown in Figure 2-1. The controller is organized around a 16-bit, high-speed bipolar microprocessor. The arithmetic and logic unit (ALU) and register file portion of the microprocessor are implemented with four, 2901 bit-slice components. The microinstruction is 48 bits in length and the control memory of 4K words is implemented with six 4K x 8 bit PROMs.

The controller incorporates a  $4K \times 16$  bit high-speed RAM buffer which is used to store the controller's device registers plus fourteen sectors (3584 words) of data buffering.

The A Cable Register (ACR) provides the storage of all A Cable signals going to the disk drives. The inputs from the selected drive are testable by the microprocessor.

Serial data from the drive is converted into 16-bit parallel data and transferred to the buffer via the microprocessor. Likewise, the data accessed from the buffer by the microprocessor is serialized and sent to the drive under the control of the servo clock received from the drive. A 32-bit ECC shift register is used to generate and check the ECC for the data field. The same register is also used in a 16-bit CRC mode for the headers. The actual ECC polynomial operation is done independently of the microprocessor, but determination of the error position and error pattern is done under the control of the microprocessor.

The Unibus interface consists of a 16-bit bi-directional set of data lines and an 18-bit set of address lines. The Unibus interface is used for programmed input/output (I/O), CPU interrupts, and data transfers. The microprocessor responds to all programmed I/O and carries out the I/O functions required for the addressed controller register. The microprocessor also controls all NPR operations and transfers data between the Unibus data lines and the buffer.

## 2.2 PHYSICAL DESCRIPTION

The SC31/BX controller consists of a single hex-size PCBA which plugs directly into a PDP-11 chassis, or an expansion chassis. Figure 2-2 shows the PCBA.

Figure 2-1 SC31 Block Diagram

#### 2.2.1 Connectors

## 2.2.1.1 A Cable Connector

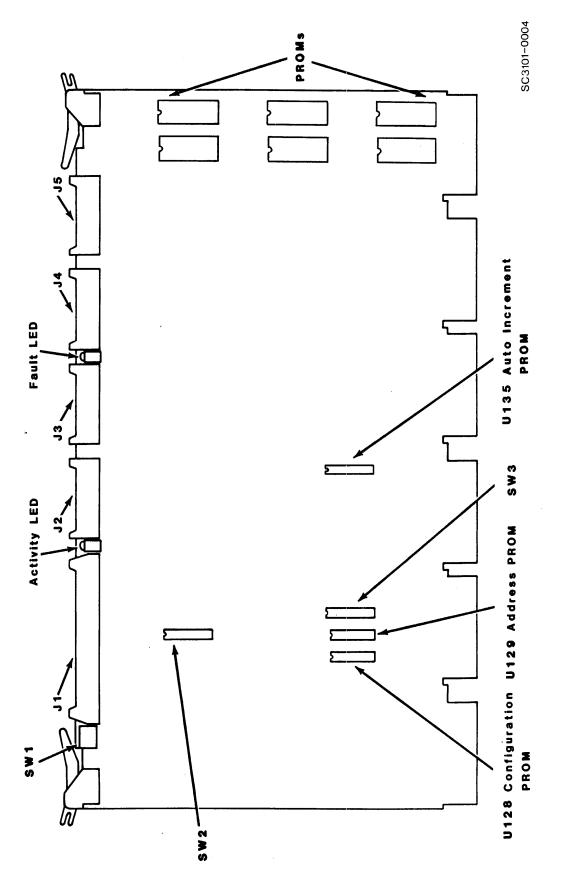

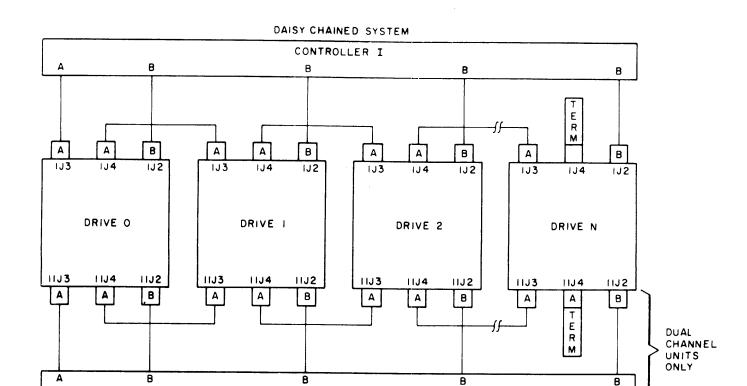

The 60-pin flat cable connector labeled J1 at the top edge of the board is for the A Cable which daisy-chains to all the drives for control and status. Pin 1 is located on the left side of the connector.

## 2.2.1.2 B Cable Connector

The four 26-pin flat cable connectors labeled J2, J3, J4, and J5 are for the radial B Cables to each of four physical drives which may be attached to the controller. Pin 1 is located on the left side of the connector. The four B Cable ports are all identical and any drive may be plugged into any connector.

## 2.2.1.3 Test Connectors

Connectors J6 and J7 are used with the Emulex test panel during manufacturing test and factory repair. They have no use in normal operation.

## 2.2.2 Switches

The two ten-pole and one four-pole DIP switches labeled SW1, SW2 and SW3 are used to configure the controller. SW1 and SW2 provide firmware options, while SW3 provides selection of controller address and drive configurations.

#### 2.2.3 Indicators

There are two LED indicators mounted between the connectors at the top of the board. They have the following use:

Fault - Indicates unsuccessful self-test execution. A flashing LED indicates successful self-test, but unable to find any drive connected and/or powered-up.

Activity - Indicates activity of disk Read or Write operation.

#### 2.2.4 PROMS

There are six PROM sockets, used for the control memory, located along the right edge of the board. The sockets are labeled PROM 0 through PROM 5 in a discontinuous physical order. The numbers on the top of the PROM ICs are Emulex part numbers which identify the unique pattern of the PROM. When inserting PROMs in the board, the ID numbers are placed in the same sequence as the PROM numbers on the board beside each socket. In addition, there are three PROM sockets in the lower left portion of the board. The PROM at U128

is the Drive Configuration PROM. The PROM at Ul29 is the Address Decode PROM. The PROM at Ul35 is the Buffer Address Auto Increment PROM.

## 2.3 INTERFACES

## 2.3.1 <u>Disk Interface</u>

The controller's disk interface conforms to the Flat Cable Interface Specification for the SMD, MMD, and CMD (CDC Document No. 64712400). The controller has been tested with most drives using the SMD interface and is compatible with the electrical and timing characteristics of such disk drives.

The following paragraphs define the electrical interface and the recommended cables.

# 2.3.1.1 <u>Drivers and Receivers</u>

The drivers for the A and B Cables are MC3453, which are equivalent to 75110A drivers. The receivers are MC3450 quad differential receivers, which are equivalent to 75108 receivers. The lines of the A Cable are terminated with 82 ohms to ground. The lines of the B Cable are terminated with 56 ohms to ground.

## 2.3.1.2 <u>A Cable</u>

The 60-conductor A Cable is daisy-chained to all disk drives and terminated at the last drive. The signals in this cable, along with their function when the control tag (Tag 3) is asserted, are listed in Table 2-1. The A Cable should be a 30 twisted pair flat cable with an impedance of 100 ohms and a cumulative length not greater than 100 feet.

## 2.3.1.3 <u>B Cable</u>

The 26-conductor B Cable is radial to all drives and contains the data and clock signals. The signals and grounds in this cable are listed in Table 2-1. The B Cable should be a 26-conductor flat cable with ground plane and drain wire. The impedance should be 130 ohms and the length not greater than 50 feet.

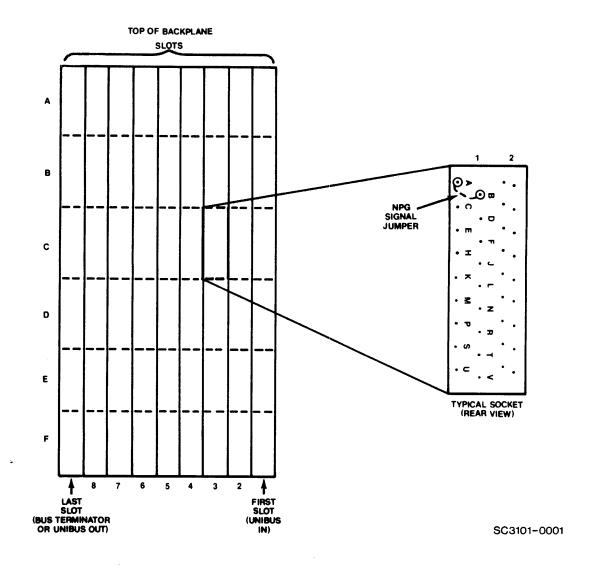

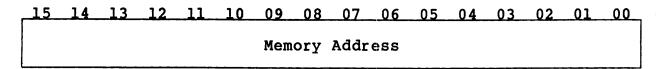

## 2.3.2 Unibus Interface

The controller interfaces to the Unibus via a Small Peripheral Controller (SPC) connector. The Unibus consists of 18 address lines and 16 bi-directional data lines, plus control signals for data and interrupt vector address transfer and for becoming bus master. The signal connections of the controller to the Unibus are shown in Table 2-2.

Table 2-1

Disk Drive Connections

| Pins Lo/Hi    | Signal                                                                  | (Tag 3 Function)                | From/To  |

|---------------|-------------------------------------------------------------------------|---------------------------------|----------|

| A Cable:      |                                                                         |                                 |          |

| 22,52         | Unit Select Unit Select Unit Select Unit Select                         | Tag -                           | То       |

| 23,53         | Unit Select                                                             | bit 0                           | То       |

| 24,54         | Unit Select                                                             | bit 1                           | То       |

| 26,56         | Unit Select                                                             | bit 2                           | То       |

| 4/,3/         | ourr serect                                                             | bit 3                           | То       |

| 1,31          | Tag l                                                                   |                                 | То       |

| 2,32          | Tag 2                                                                   |                                 | To       |

| 3,33          | Tag 2 Tag 3 Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 Bit 8 Bit 9 | <b>/</b> 1.                     | To       |

| 4,34          | Bit U                                                                   | (Write Gate)                    | To       |

| 5,35          | BIC I                                                                   | (Read Gate)                     | To       |

| 0,30          | BIT Z                                                                   | (Servo Offset Plus)             | То       |

| 7,37          | BIT 3                                                                   | (Servo Offset Minus)            | То       |

| 0,30          | BIC 4                                                                   | (Fault Clear)                   | То       |

| 3,39          | BIT 5                                                                   | (AM Enable)                     | To       |

| 10,40         | DIL O                                                                   | (Return to Zero)                | То       |

| 17 47         | DIL /                                                                   | (Data Strobe Early)             | To       |

| 12,42         | Bit 9                                                                   | (Data Strobe Late)<br>(Release) | То       |

| 30 60         | Bit 10                                                                  | (Release)                       | To<br>To |

| 14.44         | Open Caple D                                                            | etest                           | To       |

| 15,45         | Open Cable D<br>Fault                                                   | etect                           | From     |

| 16.46         | Seek Error<br>On Cylinder<br>Index                                      |                                 | From     |

| 17.47         | On Cylinder                                                             |                                 | From     |

| 18.48         | Index                                                                   |                                 | From     |

| 19.49         | Unit Ready                                                              |                                 | From     |

| 20.50         | Address Mark                                                            | Found                           | From     |

| 21,51         | Busy (dual p                                                            | ort only)                       | From     |

| 25,55         | Sector                                                                  |                                 | From     |

| 28,58         | Write Protec                                                            | ted                             | From     |

| 29            | Power Sequen                                                            | ce Hold                         | To       |

| 59            | Power Sequen                                                            | ce Pick                         | To       |

|               |                                                                         |                                 |          |

| B Cable:      | 77                                                                      |                                 | _        |

| 8,20          | Write Data                                                              |                                 | To       |

| 6,19          | Write Clock                                                             |                                 | To       |

| 2,14          | Servo Clock                                                             |                                 | From     |

| 3,16<br>5,17  | Read Data<br>Read Clock                                                 |                                 | From     |

| 5,17          | Seek End                                                                |                                 | From     |

| 10,23<br>22,9 | Unit Selected                                                           | a                               | From     |

| 12,24         | Index                                                                   | u                               | From     |

| 13,26         | Sector                                                                  |                                 | From     |

| TJ / 20       | MECCOT                                                                  |                                 | From     |

Table 2-2 SPC Unibus Connections

| Column         |        | С   |      | D           |      | E    | F    |      |  |

|----------------|--------|-----|------|-------------|------|------|------|------|--|

| Pin            | 1      | 2   | 1    | 2           | 1    | 2    | 1    | 2    |  |

| A              | NPGIN  | +5V |      | +5 <b>V</b> |      | +5V  |      | +5V  |  |

| В              | NPGOU' | r   |      |             |      | -15V |      | -15V |  |

| C              | PA     | GND |      | GND         | A12  | GND  |      | GND  |  |

| D              |        | D15 |      | BR7         | A17  | A15  | BBSY |      |  |

| E              |        | D14 |      | BR6         | MSYN | A16  |      |      |  |

| F              |        | D13 |      | BR5         | A02  | Cl   |      |      |  |

| Н              | D11    | D12 |      | BR4         | A01  | A00  |      |      |  |

| J <sub>.</sub> |        | D10 |      |             | SSYN | CO   | NPR  |      |  |

| K              |        | D09 |      | BG7IN       | A14  | A13  |      |      |  |

| L              |        | D08 | INIT | BG70UT      | All  |      |      |      |  |

| M              |        | D07 |      | BG6IN       |      |      | INTR |      |  |

| N              | DCLO   | D04 |      | BG6OUT      |      | A08  |      |      |  |

| P              |        | D05 |      | BG5IN       | A10  | A07  |      |      |  |

| R              |        | D01 |      | BG5OUT      | A09  |      |      |      |  |

| S              | PB     | D00 |      | BG4IN       |      |      |      |      |  |

| T              | GND    | D03 | GND  | BG4OUT      | GND  |      | GND  | SACK |  |

| U              |        | D02 |      |             | A06  | A04  |      |      |  |

| V              | ACLO   | D06 |      |             | A05  | A03  |      |      |  |

## 2.3.2.1 BR (Interrupt) Priority Level

The controller is hardwired for BR5. The other three Bus Grant signals are jumpered through.

#### 2.3.2.2 Register Address

The controller's block of register addresses is decoded by a 2K X 4 bit PROM, located at Ul29. The specific address range is determined by configuration switch SW2 as discussed in paragraph 3.4.1.

## 2.3.2.3 DCLO and INIT Signals

The DCLO and INIT signals both perform a Controller Clear. The self-test is performed only if DCLO has been asserted.

#### 2.4 DISK FORMAT

#### 2.4.1 Disk Organization

The formatting of a disk pack and the mapping of one or two logical drives onto a physical drive varies with the drive capacity. Some of this information is supplied by the configuration PROM. The rest is computed based upon configuration PROM information.

## 2.4.2 Mapping

In most cases there is a 1:1 correspondence between logical and physical disk addresses. The controller has the capability to alter a logical address to a different physical address so that drives which do not match the number of tracks and cylinders of the unit being emulated may be accommodated.

Depending upon the type and capacity of the disk drive, one or two logical units may be mapped on it. The controller can handle a maximum of eight logical units distributed across a maximum of four physical drives. A logical drive may not be mapped across a physical unit boundary.

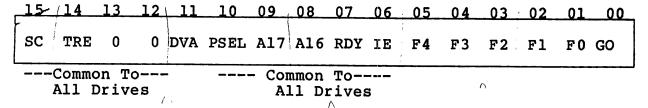

#### 2.4.3 Sector Organization

Figure 2-3 shows the RM sector format used by the controller. With the exception of an additional two words, the RP sector format is the same. Each track of 20,160 bytes is divided into 32 sectors of 630 bytes. The four byte header is preceded by a preamble of 30 bytes ending in the sync byte and is followed by a two byte CRC. The 512 byte data field is preceded by a preamble of 20 bytes ending in the sync byte, and is followed by four bytes of ECC.

If the actual size of the useful data is less than 512 bytes, the remainder of the data field will be filled with zeros until 512 bytes have been written. During disk formatting procedures, each data track is located and recorded with header information by means

|               |            | Length (RM) 6 |            |     |          |

|---------------|------------|---------------|------------|-----|----------|

| Preamble Sync | Header CRC | Preamble Sync | Data Field | ECC | Recovery |

|               |            | 20            |            |     |          |

Figure 2-3 RM Sector Format

# Header Word 1:

| _15      | 14 | 13  | 12 | 11 | 10 | 09 | 08 | 07  | 06   | 05   | 04   | 03 | 02 | 01 | 00 |

|----------|----|-----|----|----|----|----|----|-----|------|------|------|----|----|----|----|

| 1        | 1  | SSF | 1  | 0  |    |    |    | Cyl | inde | r Ad | dres | s  |    |    |    |

| <u> </u> |    |     |    |    |    |    |    |     |      |      |      |    |    |    |    |

## Header Word 2:

| 15 14 | 13 12 11 1 | 0 09 0 | 8 07 | 06 | 05 | 04 | 03   | 02   | 01   | 00 |

|-------|------------|--------|------|----|----|----|------|------|------|----|

| 0 0   | Track Ad   | dress  | 0    | 0  | 0  | S  | ecto | r Ad | dres | s  |

## Header Word 3:

Figure 2-4 RM Header Format

of the Write Header and Data command. A disk pack should be formatted and the format verified before any real data is written on it. Once formatted, individual sectors, or groups of sectors, should not be reformatted unless absolutely necessary.

#### 2.4.4 Header

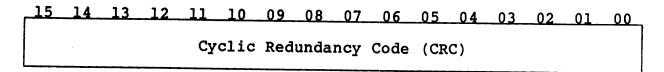

## 2.4.4.1 Header Description

Figure 2-4 shows the RM header format, which consists of the following three words:

Word One -

This word contains the cylinder address. It contains a one-bit in bit 12 to identify 16-bit format to the software and one-bits in bit positions 14 and 15 to identify a good sector. For RM80 emulations, a one-bit in bit 13 indicates that the data for this sector has been relocated to the next sector.

Word Two -

The low-order byte of this word contains the sector address. Each track on the drive typically contains 32 sectors. The least significant six bits of the upper byte of this word contain the track address.

Word Three -

This is the CRC word which is generated and checked by the controller logic. This word is not available to the software.

#### 2.4.4.2 Header Field Handling

After the drive reports that it is on cylinder, the controller locates the desired sector by means of the sector counters. A sector counter for each drive is maintained in the controller. The controller compares the first two words of the header with the desired track, sector and cylinder and then checks the CRC word for errors. An error in the header field is indicated by turning on the appropriate error bit in the error register (format error, header compare error, bad sector error, skip-sector error or CRC error). A header error is only valid when the sector count field of the RPLA/RMLA register and the sector field of the RPDA/RMDA register have already matched. It is immaterial where a CRC error occurs in the header field since the controller cannot determine its location in the field. Software may read the header to memory, however, by means of a Read Header and Data command. The header compare may be inhibited by setting the HCI bit in the RPOF/RMOF register.

## 2.5 GENERAL PROGRAMMING INFORMATION

## 2.5.1 <u>Clearing the Controller</u>

The controller is cleared by the following methods:

a. Controller Clear: Controller Clear is performed by writing a 1-bit into the CLR bit (bit 05 of RPCS2/RMCS2) or Unibus INIT. This causes the following registers to be cleared:

#### RP Drives:

RPCS1 bits <15:12>, <10:08>, <06:00>; RPCS2 bits <15:07>, <05:00>; RPBA bits <15:00>. Sets bit 06 of RPCS2 and bit 07 of RPCS1.

In all RP drives: RPER1; RPER2; RPER3; RPDA; RPEC1; RPEC2; RPAS ATA bit; RPOF bits <07:00>, RPDS ATA, ERR and LST bits; RPMR bits <15:09>, <07:00>. Sets bit 08 of RPMR.

#### RM Drives:

RMCS1 bits <15:12>, <10:08>, <06:00>; RMCS2 bits <15:07>, <05:00>; RMBA bits <15:00>. Sets bit 06 of RMCS2 and bit 07 of RMCS1.

In all RM drives: RMER1; RMER2; RMDA; RMAS ATA bit; RMEC2; RMDS ATA, ERR and LST bits; RMMR1 bits <15:04>, <02:00>. Sets bit 03 of RMMR1.

- b. Error Clear: The Error Clear is performed by writing a one-bit into the TRE bit (bit 14 of RPCS1/RMCS1). This writing causes a clearing of RPCS1/RMCS1 bits 13 and 14, and bits <15:08> of RPCS2/RMCS2. RPCS1/RMCS1 SC bit (bit 15) is reset if RPAS/RMAS equals zero.

- c. Drive Clear: The Drive Clear is a command. (Code 11) This command causes the following registers in the drive selected by U2-U0 to be cleared:

## RP Drives:

ATA and ERR bits in RPDS; RPAS ATA bit; bits <15:09> and <07:00> in RPMR, bits <15:00> in RPER1, RPER2, RPER3, RPEC1, and RPEC2; and bits <07:00> in RPOF. Sets bit 08 of RPMR.

#### RM Drives:

ATA and ERR bits in RPDS; RMAS ATA bit; bits <15:04> and <02:00> in RMMRl; and bits <15:00> in RMERl, RMER2, and RMEC2. Sets bit 03 of RMMRl.

## 2.5.2 Interrupt Conditions

The controller generates an interrupt on the following conditions:

- a. Upon termination of data transfer if interrupt enable is set when the controller becomes ready.

- b. Upon assertion of attention or occurrence of a controller error (SC being set) if the controller is not busy and the interrupt enable is set.

- c. When the program writes a one into IE and RDY at the same time. Note that this can be done by Read-Modify-Write instructions (BIS, BIC, etc.) which set the IE bit.

# 2.5.3 Termination of Data Transfers

A data transfer which has been successfully started may terminate in any of the following ways:

- a. Normal Termination: Word count overflows to zero and the controller becomes ready at the end of the current sector.

- b. Controller Error: An error occurs in the RPCS2/RMCS2 register bits <15:08>. Any of these errors sets TRE which terminates the data transfer immediately and makes the controller ready.

- c. Drive Error: The ERR bit in the RPDS/RMDS register and at least one bit in an error register are set. TRE is also set, and the controller becomes ready. The ATA for the drive doing the data transfer becomes asserted.

- d. Program-Caused Abort: By performing a Controller Clear or a RESET instruction, the program can cause an abort of any operation. Status and error information is lost when this abort is done, and both the controller and drive become ready immediately.

## 2.5.4 Ready Bits

RDY is the ready indicator for the controller. When RDY equals one, the controller is ready to accept a data transfer command. RDY is reset when the controller is doing a data transfer command. DRY is the ready indicator for the selected drive and is the complement of the drive's GO bit. To successfully initiate a data transfer command, both of these bits must be asserted; however, a non-data transfer command (Search, Drive Clear) may be issued to a drive at any time DRY is asserted, regardless of the state of the RDY bit.

When a Data Transfer command is successfully initiated, both RDY and DRY become negated. When a non-data transfer command is successfully initiated, only DRY becomes negated.

The assertion of RDY after the execution of a Data Transfer command does not occur until the DRY bit is set and the controller is done. RDY is asserted on the completion of the last memory cycle (or at the time of an abort condition) and the last disk transfer.

If any command other than Drive Clear is issued to a disk drive which has ERR asserted, the command is ignored by the drive. If a Data Transfer command is issued to a drive which has ERR asserted, the drive does not execute the command and the missed transfer error bit (MXF, bit 09 in RPCS2/RMCS2 register) is set.

## 2.6 DUAL CONTROLLER OPERATION

SMD drives may be equipped with a Dual Port option which allows two controllers (generally on separate computers) to access the drive. The SC31 controller supports this type of operation as a standard feature. Most of the dual port functions of the DEC controller being emulated are supported, and those which are not should be transparent to a properly written dual port driver.

## 2.6.1 <u>Dual Port Drives</u>

The two drive ports are known as Channel I and Channel II. Each channel has a disable switch which disables the port and prevents the computer from having access to it. Access to the drive in Dual Port operation is switched back and forth between the two controllers under program control of the two computers involved, as described in the following sections. Table 2-3 summarizes the controller's register responses in Dual Port operation.

## 2.6.2 <u>Unseized State</u>

The drive is in the unseized state when it is not connected to either controller. The CPU must issue a request for the controller to seize the drive. This request is made in one of the following ways:

- a. Writing into any drive register, including read-only registers.

- b. Writing a one into the drive's ATA bit in RPAS/RMAS.

## 2.6.3 Seized State

The drive is seized when it is logically connected to one of the controllers. At that time, the DVA (RPCS1/RMCS1, bit 11) is set, indicating that the drive is ready to communicate with the controller which has seized it. If the drive is seized by the other controller, then the DVA bit is reset, all the drive registers read as zeros and any write to a register is ignored. However, any attempt to seize a drive which is busy with the other port will cause the request to be remembered and acted upon when the drive is released by the other controller.

## 2.6.4 Returning to the Unseized State

The drive is released and returned to the unseized state by issuing a release command. In addition, a one second timer in the controller will timeout and release the drive if one of the events listed in section 2.6.2 for seizing the drive is not performed periodically to keep resetting the timeout timer. Furthermore, reading RPCS1/RMCS1 while the drive is already seized will set the timeout timer back to one full second. Reading RPCS1/RMCS1 while the drive is unseized will have no effect on the timer. This allows the programmer to check the DVA bit in RPCS1/RMCS1 which, if set, assures the programmer that his operation will complete without timing out.

When the controller sees a previously busy drive becoming unseized, it checks its Request flag. If the drive had been previously requested while busy on the other port, the controller will seize the drive, set the DVA bit and set the ATA bit which causes an interrupt to the CPU if the IE bit is set. If the CPU does not respond to the Attention within one second the drive will be released, but the ATA bit remains set.

## 2.6.5 DEC Compatibility

The SC31/BX controller differs from the equivalent DEC controller in three important areas. First, there is no neutral state. Since the controller does not have instantaneous access to all drives at the same time (a limitation of the daisy-chained A Cable and the microprocessor organization of the controller), the controller assumes a drive is busy on the other port if the controller has not already seized that port. The DEC controllers can switch from neutral to seized state within the time required to do a single Read or Write of a drive register. In that case no ATA is set and the drive would appear to have been already seized.

Second, the Release command is not instantaneous since the controller takes a few microseconds to execute the command. During this time the drive will appear to the CPU to be unseized.

Third, during a Data Transfer, the timeout timers will not operate and the drives can not be polled to determine if they are not busy. Therefore, no drives are seized or released during the execution of a Data Transfer operation.

The software driver should not issue a Release command and then attempt to save the current status of a drive, since the Release command has a drive clear implied within it, and the reading of the drive's registers will return all zero data. In order to allow the other controller time to poll the drive, the CPU should not communicate with any of the released drive's registers until required to seize the drive again.

## 2.6.6 Dual Port Drives in Single Port Mode

When using an operating system which does not have dual port drive software support, it may still be advantageous to use dual port drives while operating the controller in Single Port mode. This will allow for a non-dynamic type of operation between two CPUs. In this type of operation the controller does not release the drive and, in effect, it is seized by both controllers all the time.

The one-second-timeout timer (and the Release command) operate exactly as stated in paragraph 2.6.4. Even when released, a drive will still appear to be seized to the releasing controller. The ATA bit is not set is when the other controller finds the drive not busy. Should a command be issued to a controller while a drive is busy on the other port, the controller will wait until the drive becomes unbusy before executing the command. No timer exists in this case.

This mode of operation eliminates the need for manually switching the drive from one controller to another.

## 2.6.7 Dual Access Mode

To provide compatibility with software configured for dual access, the Dual Access mode is supported on the SC31/BX. Register access and drive states during Dual Access mode are described in Table 2-3.

This mode is enabled by setting SW2-9 to ON (closed). When in this mode, the controller sets Dual Port Mode (Drive Type Register) and Programmable (Drive Status Register) bits to imitate the DEC neutral state.

When DPM and PGM are set, the operating system will attempt to seize a drive by simply writing a command to it. If the drive is unbusy the command is executed. The operating system will not issue a command to a drive when that drive is busy.

The operating system's choice of controller depends on whether or not a controller is currently executing a command, and what type of command it is. A controller executing a Data Transfer command can not accept another data transfer. A controller executing positioning or a housekeeping commands may be given any command for a non-busy drive.

The first time the SC31 sees a drive, it is ignored for one second. This one-second stall occurs once for each drive on the controller. It prevents the controller from seeing erroneous status information when power is applied to the drive after the controller has been powered-up. For a drive in Dual Port mode the stall will prevent the other CPU from accessing the drive until the stall completes. The Dual Access option switch bypasses the stall in all cases. For proper system operation with the Dual Access switch option ON, all

drives must have power applied before either controller is powered-up.

Setting the Dual Port Option switch overrides the Dual Access Option, except for the one-second stall override.

# Table 2-3 Register Access on Dual Controller Operation

Controller Action

Drive State:

Response With Respect To Action On Ch. I

## Read RPCS1/RMCS1

Drive Not Seized: Reads the controller portion of the

RPCS1/RMCS1 only. The drive's portion is read as all zeros. No request flag

is set.

Drive Seized by Ch. I: DVA = 1; reads the register.

Drive Seized by Ch. II: DVA = 0; reads all zeros for the drive's

portion of the register. No flags set.

## Read any other drive register

Drive Not Seized: Reads all zeros.

Drive Seized by Ch. I: Reads the register.

Drive Seized by Ch. II: Reads all zeros.

## Write RPCS1/RMCS1

Drive Not Seized: The function code is attempted, and a

Port Request flag is set. An OPI error

usually results.

Drive Seized by Ch. I: Loads the Function code. (Switches to

unseized if the function is a Release).

Drive Seized by Ch. II: The Function code is attempted, and a

Port Request flag is set. An OPI error

usually results.

#### Write any other drive register

Drive Not Seized: The Write is ignored, and a Port Request

flag is set.

Drive Seized by Ch. I: Loads the register.

Drive Seized by Ch. II: The Write is ignored, and a Port Request

flag is set.

BLANK

This section describes the step-by-step procedure for installation of the SC31/BX Disk Controller in a PDP-11 system. The following list is an outline of the procedure. Each step corresponds to a second level heading in this section (i.e., item one, Inspect the SC31/BX, is covered in paragraph 3.1).

Emulex recommends that Section 3 be read in its entirety before installation is begun.

- 1. Inspect the SC31/BX.

- 2. Prepare the disk drives.

- Prepare the PDP-11.

- 4. Configure the SC31/BX.

- 5. Install the SC31/BX.

- 6. Route the drive I/O cables.

- 7. Test the controller.

- 8. Patch the operating system if required.

## 3.1 INSPECTION

Before unpacking the SC31/BX, examine the packaging for any signs of damage. Notify the carrier if any damage is noted.

Make a visual inspection of the board after unpacking. Check specifically for bent or broken connector pins, damaged components or any other evidence of physical damage. Examine the PROMs to ensure that they are firmly and completely seated in their sockets.

## 3.2 DISK DRIVE PREPARATION

The disk drive must be configured for the proper number of sectors and have an ID plug or address selection switches properly configured.

## 3.2.1 Drive Placement

Uncrate and install the disk drives according to the manufacturer's instructions. Position and level the disk drives in their final places before beginning the installation of the SC31/BX. This positioning allows the I/O cable routing and length to be accurately judged. Place the drives side-by-side to make installation of the daisy-chained A Cable simpler.

## 3.2.2 Local/Remote

The local/remote switch controls whether the disk drive can be powered up from the drive (local) or the controller (remote). Place the switch in the REMOTE position. With the CPU powered down, press the Start switch on the front panel of each of the drives (the Start LED will light, but the drive will not spin up and become ready). When the CPU is powered up, the drives will spin up sequentially. This sequential power-up prevents the heavy current draw that would be caused if all the drives were powered up at once. When in the remote mode the drives will power down when the CPU is powered down. While the CPU is powered on, the drives may be powered up and down individually (to change disk media, for example) by using the drive Start switch.

## 3.2.3 Sectoring

See Appendix A, Configuration Selection, for the correct sector count settings for the disk drives in use. The exact method of entering the sector count differs from one drive manufacturer to another and the particular drive manual should be consulted for the exact procedure.

## 3.2.4 Drive Numbering

An address from 0 to 3 must be selected for each drive. Be careful that no two drives are assigned the same number. To determine the number that each drive should be assigned, the user must first decide on the particular configuration that will be used. The drive numbers should then be assigned according to that configuration by matching the number of cylinders and tracks in Table A-2 to the drives. See paragraph A.2.1.2 for an example.

CDC drive addresses are selected by means of an ID plug. Drives by other manufacturers have their addresses selected by switches on one of the logic cards. Consult the particular drive manual for the exact procedure.

## 3.2.5 <u>Sector and Index Modifications</u>

It may be necessary to move the Sector and Index signals from the A Cable to the B Cable. See Section 3.4.3. Instructions for doing this for commonly used drives is included in Appendix B.

## 3.3 SYSTEM PREPARATION

Power down the system and switch OFF the main AC breaker at the rear of the cabinet (the AC power indicator will remain lit). Slide the CPU out of the cabinet and remove the cover.

Figure 3-1 SC31 Controller Assembly

Refer to Figure 3-1 for the locations of the configuration switch, PROMs and connectors on the SC31 Controller Board.

## 3.4.1 Controller Address Selection

All Unibus controllers have a block of several command and status registers through which the system can command and monitor the controller. The blocks are 2-20 registers long, and are addressed sequentially from a starting address assigned to that device type, in this case a disk controller. On the SC31 register addresses are decoded by decode PROM 798, located at Ul29. One of four starting addresses for the controller's Unibus registers is selected by DIP switch SW3. See Table 3-1 for register address switch settings. Make sure only one of the four switches is closed.

Table 3-1 Controller Address Switch Settings

| C       O       O       O       776700 (Standard)         O       C       O       O       776300 (Alternate)         O       O       C       776400 (Alternate)         O       O       C       0       776600 (Alternate) | e) |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

## 3.4.2 <u>Interrupt Vector Address</u>

The interrupt vector address is selected by means of SW2-1, SW2-2 and SW2-3. The standard vector address is 254. Table 3-2 lists the switch settings for the standard and alternate interrupt vector addresses.

Table 3-2

Interrupt Vector Address Switch Settings

| SW2-3 | SW2-2 | SW2-1 | Vector          |

|-------|-------|-------|-----------------|

| 0     | 0     | 0     | 254 (Standard)  |

| 0     | 0     | С     | 150 (Alternate) |

| 0     | С     | 0     | 370 (Alternate) |

| 0     | С     | С     | 374 (Alternate) |

| С     | 0     | 0     | 354 (Alternate) |

| С     | 0     | С     | 224 (Alternate) |

| С     | С     | 0     | 270 (Alternate) |

| С     | С     | С     | 274 (Alternate) |

|       |       |       |                 |

#### 3.4.3 Drive Configuration Selection

The phrase "drive configuration selection" describes the process that is used to select the logical disk drives that will be emulated by the SC31/BX controller when using a given set of

physical disk drives. Using those disk drives and the SC31/BX, the user emulates a specific type and arrangement of DEC subsystems. (The emulated system is referred to as a logical disk drive.) Setting SW3-1 through SW3-5 and SW3-10 on the controller allows selection of the logical disk drive configuration (limited, of course, by the physical disk drives available).

The SC31/BX has the capability to emulate both RM and RP type drives when certain configurations are selected. The drive types are roughly divided into three groups: RM02/03/05, RM80 and RP04/05/06. Each physical drive can support any drive type. When a physical drive has two logical units assigned to it, each logical unit has the same type and capacity, except the CDC 9448-96 drive. It has an RM02 as one logical unit and a different capacity RM03 as the other unit (see configuration numbers 20 and 22). Examples of configurations with mixed (both RP and RM) drive types may be seen in configuration numbers 42 and 43 in Table A-2.

For ease of manual maintenance, the configuration table for the SC31/BX is contained in Appendix A.

#### 3.4.4 Index and Sector Pulse Selection

The SC31/BX controller is designed to have the Index and Sector signals on the B Cable from each physical drive. The signals are necessary for proper operation of the sector counters associated with each drive. Both the RP and RM emulations require an updated sector counter which can be read by the CPU. Failure to have a valid sector counter may cause incorrect operation of the rotational position sensing software.

Depending on the disk drive, the Index and Sector pulse signals may be carried on the A instead of the B Cable. For example, standard CDC drives provide the Index and Sector signals on the A Cable; however they may be moved to the B Cable by minor rewiring of the drive backplane or by ordering this configuration from the factory. The procedure for making this modification to several of the more common drives is described in Appendix B. If the procedure for the drive in question is not covered there, it is generally described in the drive manual.

It is possible to operate with the Index and Sector signals on the A Cable by placing switch SW2-8 in the ON position. When operating in this manner there is considerable loss of capabilities and performance including: the Search command operates as a Seek; the sector counter in RPLA/RMLA will be incorrect; each transfer must wait for an Index pulse to sync-up the sector counter. Also, some of the lower level diagnostics will produce some errors.

# 3.4.5 SC31/BX Options

# 3.4.5.1 Logical Unit Swap