RH70

SC71/B1 SC70/B3

(RMO2/RMO3/RMO5 COMPATIBLE)

DISK CONTROLLER

TECHNICAL MANUAL

SC71/B1 SC70/B3

(RMO2/RMO3/RMO5 COMPATIBLE)

DISK CONTROLLER

TECHNICAL MANUAL

Copyright (C) 1980 by Emulex Corporation

The information in this manual is for informational purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

## TABLE OF CONTENTS

| Section | 1                                                                                                                               | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                   |                                                                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|         | 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.3.5<br>1.3.5<br>1.3.7<br>1.3.8<br>1.4.1<br>1.4.2<br>1.4.3 | SCOPE OVERVIEW General Description Controller Models FEATURES Microprocessor Design Packaging Self-Test Buffering Error Correction Option and Configuration Switches Dual-Port Capability Fixed Head Capability Fixed Head Capability FUNCTIONAL COMPATIBILITY Media Compatibility Disk Mapping Diagnostic Operating Systems                                   | 1-1<br>1-1<br>1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-3 |

| Section | 2                                                                                                                               | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                            |                                                                           |

|         | 2.2.1.0                                                                                                                         | A Board A Cable Connector B Cable Connectors Switches Indicators Toggle Switch PROM's B Board B Cable Connectors LED Indicators C Board PROM's INTERFACES Disk Interface Drivers and Receivers A Cable B Cable Unibus Interface BR(Interrupt)Priority Level Register Address Interrupt Vector Address DISK FORMAT Disk Organization Sector Organization Header | 2-3-3-3-3-3-3-3-3-3-3-3-3-3-3-3-3-3-3-3                                   |

|         | 2.6.4<br>2.6.5<br>2.6.6 | Header Field Handling GENERAL PROGRAMMING INFORMATION Clearing the Controller Interrupt Conditions Termination of Data Transfers Ready Bits DUAL CONTROLLER OPERATION Dual-Port Drives Unseized State Seized State Returning to the Unseized State DEC Compatibility Dual-Port Drives in Single-Port Mode FIXED HEAD OPERATION Drive Numbering Drive Characteristics                     | 2-17<br>2-17<br>2-17<br>2-17<br>2-18<br>2-18<br>2-19<br>2-19<br>2-19<br>2-19<br>2-20<br>2-20<br>2-20<br>2-21<br>2-21<br>2-21 |

|---------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Section | 3                       | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                              |

|         | 3.6.3                   | INSPECTION DISK DRIVE PREPARATION Sectoring ID Plug Sector and Index Modifications CONTROLLER SETUP Controller Address Selection Interrupt Vector Address Index and Sector Pulse Selection PHYSICAL INSTALLATION RH70 Slot Selection Mounting CABLING A Cable B Cable Grounding TESTING Self-Test Register Examination Hardware Formatting the Disk Diagnostics OPERATING SYSTEM PATCHES | 3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-2<br>3-3<br>3-4<br>3-4<br>3-4<br>3-4<br>3-5<br>5-6<br>6     |

| Section | 4                       | CONTROLLER REGISTERS                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                              |

|         | 4.7<br>4.8              | WORD COUNT REGISTER (RMWC) BUS ADDRESS REGISTER (RMBA) DISK ADDRESS REGISTER (RMDA) CONTROL/STATUS REGISTER 2 (RMCS2) DRIVE STATUS REGISTER (RMDS) ERROR REGISTER 1 ATTENTION SUMMARY REGISTER (RMAS) LOOK-AHEAD REGISTER (RMLA)                                                                                                                                                         | 4-1<br>4-3<br>4-3<br>4-3<br>4-4<br>4-6<br>4-8<br>4-10<br>4-11                                                                |

|         | 4.11<br>4.12<br>4.13<br>4.14<br>4.15<br>4.16<br>4.17<br>4.18<br>4.19<br>4.20<br>4.21<br>4.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MAINTENANCE REGISTER 1 (RMMR1) DRIVE TYPE REGISTER (RMDT) SERIAL NUMBER REGISTER (RMSN) OFFSET REGISTER (RMOF) DESIRED CYLINDER REGISTER (RMDC) HOLDING REGISTER (RMHR) MAINTENANCE REGISTER 2 (RMMR2) ERROR REGISTER 2 (RMER2) ECC POSITION REGISTER (RMEC1) ECC PATTERN REGISTER (RMEC2) BUS ADDRESS EXTENTION (RMBAE) CONTROL/STATUS REGISTER 3 (RMCS3)                                                                                                                  | 4-11<br>4-12<br>4-12<br>4-13<br>4-13<br>4-14<br>4-14<br>4-16<br>4-16<br>4-17 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Section | E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | COMMANDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                              |

|         | 5.1.23456<br>1.23456<br>1.2345<br>5.1.1.22.2.23<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.2345<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235<br>1.235 | DATA TRANSFER COMMANDS Write Check Data (51) Write Check Header and Data (53) Write Data (61) Write Header and Data (63) Read Data (71) Read Header and Data (73) POSITIONING COMMANDS Seek Command (5) Recalibrate (7) Offset Command (15) Return-to-Centerline Command Search Command (31) HOUSEKEEPING COMMANDS No OP (1) Drive Clear (11) Release Command (13) Read-In Preset (21) Pack Acknowledge (23) OPTIONAL COMMANDS Boot (75) Format (77) DMA Bandwidth Set (25) | 55555555555555555555555555555555555555                                       |

| Section | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DIAGNOSTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                              |

|         | 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3<br>6.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ZRMA-CO FORMATTER  Modifications to Correct Prgm Errors Modifications for Number of Cylinders Modifications for Number of Tracks Formatter Operation  ZRMB-BO PERFORMANCE EXERCISER Modifications to Correct Prgm Errors Modifications for Number of Cylinders Modifications for Number of Tracks Performance Exerciser Operation  ZRMC-BO FUNCTIONAL TEST - PART 1 Modifications for Correct Operation Modifications for Number of Cylinders                               | 6-1<br>6-3<br>6-3<br>6-3<br>6-3<br>6-3<br>6-4<br>6-4                         |

|          | 6.3.3 | Modifications for Number of Tracks ZRMD-BO FUNCTIONAL TEST - PART 2 | 6-5<br>6-5   |

|----------|-------|---------------------------------------------------------------------|--------------|

|          | 6.4.1 |                                                                     |              |

|          | 6.4.2 | Modifications for Number of Cylinders                               | 6-5          |

|          | 6.4.3 |                                                                     | 6-5          |

|          | 6.5   | ZRME-BO FUNCTIONAL TEST - PART 3                                    |              |

|          | 6.5.1 | Modifications for Correct Operation                                 | 6-5          |

|          | 6.5.2 | Modifications for Number of Cylinders                               | 6-6          |

|          |       | Modifications for Number of Tracks                                  | 6-6          |

|          | 6.6   | ZRMF-BO EXTENDED DRIVE TEST                                         | 6-6          |

|          | 6.6.1 | ZRMF-BO EXTENDED DRIVE TEST Modifications for Correct Operation     | 6-6          |

|          | 6.6.2 | Modifications for Number of Cylinders                               | 0-0          |

|          | 6.6.3 | Modifications for Number of Tracks                                  | 6-7          |

|          | 6.7   | ZRMI-BO DRIVE COMPATIBILITY                                         | 6-7          |

|          | 6.7.1 | Modifications for Correct Operation                                 | 6-7          |

| Appendix | A     | CONFIGURATION SWITCHES                                              | A-1          |

| Appendix | В     | DRIVE CONFIGURATION SETTINGS                                        | B-1          |

| Appendix | С     | DRIVE MODIFICATIONS                                                 | C-1          |

| Appendix | D     | RSTS/E V7.0                                                         |              |

| • •      |       | MIXED DISK CONFIGURATIONS                                           | D-1          |

|          |       | PATCHES FOR NON-STANDARD SIZE RM                                    | D-3          |

|          |       | PATCH PROCEDURE                                                     | D <b>-</b> 5 |

| Annendix | -     | RSX-11M V3.2                                                        | E-1          |

## LIST OF TABLES

| Table No.                                                                                 | <u>Title</u>                                                                                                                                                                                                                                    | Page                                                              |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Table 1-1 Table 2-1 Table 2-2 Table 2-3 Table 2-4 Table 2-5 Table 2-6 Table 2-7 Table 2-8 | General Specifications DIP Switches Control Memory Configuration Disk Drive Connections Register Block Starting Address Register Block Size Register Block Limit Interrupt Vector Address Switches Register Access on Dual Controller Operation | 1-4<br>2-3<br>2-4<br>2-11<br>2-13<br>2-13<br>2-14<br>2-14<br>2-22 |

## LIST OF FIGURES

| Figure No.                                                                   | <u>Title</u>                                                                                         | Page                                            |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Figure 2-1 Figure 2-2 Figure 2-3 Figure 2-4 Figure 2-5 Figure 2-6 Figure 2-7 | SC71 Block Diagram SC71 A Board SC71 B Board SC71 C Board SC71 CST Board Sector Format Header Format | 2-2<br>2-6<br>2-7<br>2-8<br>2-9<br>2-16<br>2-16 |

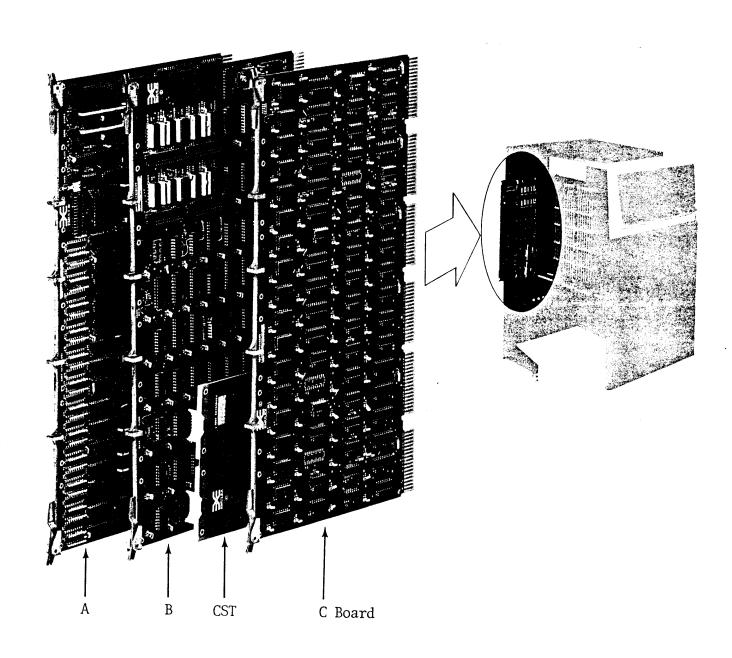

| Figure 3-1<br>Figure 3-2                                                     | SC71 Board Set<br>Unit Cabling                                                                       | 3-7<br>3-8                                      |

### 1.1 SCOPE

This manual provides information related to the capabilities, design, installation, and use of the SC71/B1 and SC70/B3 Disk Controllers. In addition, this manual provides diagnostics and application information.

### 1.2 OVERVIEW

## 1.2.1 General Description

The SC71/B1 Disk Controller is a three-board imbedded controller for PDP-11/70 computer manufactured by Digital Equipment Corporation. This controller can be used to interface any large disk having a Storage Module Drive (SMD) interface. The SC71/B series of controllers is capable of emulating the DEC Massbus disk subsystems. The SC71/B1 emulates the DEC RWM03 disk subsystem while the SC71/B2 emulates the DEC RWP06 disk subsystem. These controllers are capable of operating with disk drives having different characteristics from those used in the DEC disk subsystems. The SC71/B controllers provide the capability of operating with a mixture of disks having storage capacity of 5-600 megabytes.

## 1.2.2 Controller Models

The various SC71/B and SC70/B models performing RM02/RM03/RM05 emulations are described below:

- SC71/B1 Basic RM emulation with configuration PROM for drive size. Drives may be of different size.

- SC70/B3 Same as SC71/B1, except that there are eight built-in drive sizes and all drives must be of the same size.

## 1.3 FEATURES

## 1.3.1 Microprocessor Design

The SC71/B1 design incorporates a unique (patent pending) 16-bit bipolar microprocessor to perform all controller functions. The microprocessor approach provides for a reduced component count, high reliability, easy maintainability, and most importantly, the ability to adapt a single set of hardware to a wide range of emulation capabilities through the use of microprogramming. The Emulex controllers achieve functional capability beyond that of the DEC controllers which they emulate, by providing enhancement

features such as built-in self-test during power-up, built-in disk formatting and the ability to work with disk drives of various sizes.

### 1.3.2 Packaging

The SC71/B1 is constructed on three hex-size multi-layer PC board which plug directly into the PDP-11/70 chassis. No cabling is required between the computer and the disk controller. The controller obtains its power from the PDP-11/70.

### 1.3.3 Self-Test

The controller incorporates an internal self-test routine which is executed upon power-up. This test exercises all parts of the microprocessor, buffer and disk data logic. Although this test does not completely test all controller circuitry, successful execution indicates a very high probability that the controller is operational. If the controller fails the self-test, it leaves the FAULT LED on and the controller cannot be addressed from the CPU.

### 1.3.4 Buffering

The controller contains a 1K x 16 high-speed RAM buffer used to store the device registers of the controller and drive being emulated and for two sectors of data buffering. Because of the buffering and the strategies used to employ it, data late situations are not possible.

### 1.3.5 Error Correction

The controller incorporates a 32-bit error correcting code (ECC) capable of correcting single error bursts of up to 11 bits in length and detecting bursts of longer length. The controller determines the location of the error and the error pattern and passes this information to the PDP-11 which performs the actual correction. A 16-bit CRC is employed with the header of every sector.

### 1.3.6 Option and Configuration Switches

The controller has switches for configuring the disk size, the Unibus address and vector address and various controller options.

### 1.3.7 Dual-Port Capability

The controller can operate with disk drives having dual-port capability which allows a second controller to have access to the drive on a priority basis.

### 1.3.8 Fixed Head Capability

The SC71/B1 controller supports the fixed head storage found on some Winchester type disk drives.

## 1.4 FUNCTIONAL COMPATABILITY

# 1.4.1 Media Compatability

The SC71/B1 is media compatible with the DEC RM02/RM03 packs when using a CDC 9762 drive or equivalentand with the DEC RM05 when using CDC 9766 drive or equivalent.

## 1.4.2 Disk Mapping

For an 80 MB disk drive, the mapping is the same as the DEC RM02. When drives of different sizes are used, the mapping is done in a straight forward manner with only the number of heads and/or number of cylinders being varied. In all cases, the disk drive is configured for 32 sectors.

## 1.4.3 Diagnostics

The controller executes the following standard DEC RM02/RM03 diagnostics:

ZRMA - Formatter

ZRMB - Performance Exerciser

ZRMC - Functional Controller, Part I \*

ZRMD - Functional Controller, Part II

ZRME - Functional Controller, Part III \*

ZRMF - Extended Drive Test

ZRMI - Drive Compatibility Test

The diagnostics marked with an asterisk require certain patches to correct coding problems or bypass unsupported maintenance mode functions. All diagnostics require patches to run with drive sizes other than that of a standard RMO2/RMO3.

# 1.4.4 Operating Systems

The SC71/B1 controllers are compatible with DEC operating systems without modification when operating with an 80 MB disk drive having 823 cylinders and 5 tracks. Patches are required to the operating system when operating with other than standard size disks. These patches numerically redefine the logical drive capacity to the operating system and generally do not involve modification to program instructions.

#### Table 1-1

#### GENERAL SPECIFICATIONS

### Functional

Emulation DEC RM02, RM03, and RM05

Media Compatability DEC RM02, RM03, and RM05 when using

appropriate disk drives.

Drive Interface SMD

Drive Ports

Error Control 32-bit ECC for data and 16-bit CRC for

headers. Correction of single data error

burst of up to 11 bits.

Sector Size 256 words (512 bytes)

Sectors/Track 32

Tracks/Cylinder SC71/B: Selectable for each drive.

SC70/B: Selectable for all drives.

Cylinders/Drive SC71/B: Selectable for each drive.

SC70/B: Selectable for all drives.

Drive Type Code SC71/B: Selectable for each drive.

SC70/B: 24

Computer Interfaces Unibus and Cache Bus

Unibus Address Switch selectable

Vector Address Switch selectable

Priority Level BR5

Data Bufferring SC71/B: 2 Sectors (512 words)

SC70/B: 3 Sectors (768 words)

Data Transfer 32-bit transfer via Cache Bus

Self-Test Extensive internal self-test on powering

up.

Indicators READ, WRITE, FAULT, BUFFER PARITY ERROR

### Table 1-1 (cont'd)

Design

High-speed bipolar microprocessor using

2901 bit-slice components.

Physical

Packaging

Three DEC hex-size board.

Mounting

Any set of RH70 slots in PDP-11/70.

Connectors

One 60-pin A cable flat connector and four 26-pin B cable connectors. (Flat

cable type.)

Electrical

Unibus Interface

DEC approved line drivers and receivers.

Drive Interfaces

Differential line drivers and receivers. A cable accumulative length to 100 feet.

B cable length to 50 feet.

Power

+5 v, 11 Amp. max. -15 v, 1 Amp. max.

## 2.1 CONTROLLER ORGANIZATION

A block diagram showing the major functional elements of the SC71/B1 controller is shown in Figure 2-1. The controller is organized around a 16-bit high-speed bipolar microprocessor. The ALU and register file portion of the microprocessor are implemented with four 2901 bit slice components. The microinstruction is 48 bits in length and the control memory of 2K words is implemented with 12 2K x 4 PROM's.

The controller incorporates a 1K  $\times$  16 high-speed RAM buffer which is used to store the controller's device registers and three sectors (768 words) of data buffering.

The A Cable Register (ACR) provides the storage of all A cable signals going to the disk drives. The inputs from the selected drive are testable by the microprocessor.

Serial data from the drive is converted into 16-bit parallel data and transferred to the buffer via the microprocessor. Likewise, the data access from the buffer by the microprocessor is serialized and sent to the drive under the control of the servo clock received from the drive. A 32-bit ECC Shift Register is used to generate and check the ECC for the data field. The same register is also used in a 16-bit CRC mode for the headers. The actual ECC polynomial operation is done independent of the microprocessor, but the determination of the error position and error pattern is done under the control of the microprocessor.

The Unibus interface consists of a 16-bit bi-directional set of data lines and an 18-bit set of address lines. The Unibus interface is used for programmed I/O and CPU interrupts. The microprocessor responds to all programmed I/O and carries out the I/O functions required for the addressed controller register. The microprocessor also controls all data transfers between the buffer and the PDP-11/70 memory via the Cache Bus.

Figure 2-1 SC71 Block Diagram

# 2.2 PHYSICAL DESCRIPTION

The SC71 controller consists of three hex size boards and a small interconnect board, all of which plug directly into the RH70 slots of the PDP-11/70.

### 2.2.1 A Board

The A board of the controller is Part Number SU7010401 or SU7010405. This board contains the high-speed bipolar microprocessor, the A cable interface and the Unibus interface. The A board is shown in Figure 2-2. It is the rear board of the four board controller and fits into the PDP-11/70 slot 27, 31, 35, or 39 which are used by the BCT board of the RH70.

The board is a 4-layer pcb with power and ground planes in the inner layers and interconnection on the outer layers. The board dimensions are 15.7 inches high x 8.7 inches wide. The 18 pins of each connector row are designated A through V - excluding the letters G, I, O, and Q from the right to the left. The component side pins are designated 1 and the bottom side pins are designated 2.

# 2.2.1.1 A Cable Connector

The A board has a 60-pin flat cable connector labeled J1 at the top edge of the board. This connector is for the A cable which daisy-chains control and status information to all the drives. Pin 1 of the connector is located on the outside board edge.

## 2.2.1.2 <u>Test Connectors</u>

Connectors J2 and J3 are used with the Emulex test panel during manufacturing test and factory repair. They have no use in normal operation.

## 2.2.1.3 Switches

The four DIP switches are used for controller options and configuration, Unibus device register starting address and range, and interrupt vector address. The Unibus address switches are described in Section 4.2 and the option switches in Appendix A. These switches are identified in Table 2-1.

Table 2-1 DIP Switches

| Switches | Location | <u>Use</u>               |

|----------|----------|--------------------------|

| SW1      | U62      | Option and configuration |

| SW2      | U72      | Unibus address range     |

| SW3      | U94      | Unibus starting address  |

| SW4      | U77      | Vector address           |

## 2.2.1.4 Indicators

The four indicators at the top front edge of the board show the state of the BBSY, SACK, SSYN, and BGIN Unibus signals. These same indicators are available on the BCT board of the RH70 and show Unibus hang-up problems.

### 2.2.1.5 Toggle Switch

The small toggle switch located along the front edge of the board is a three position switch with the center position being the normally OFF position. In the lower position the extended functions (including format) are enabled. The upper position is not used in most SC71 models and should not be used. For normal operation, the switch should be in the center position.

## 2.2.1.6 PROM's

The A board has 24 PROM locations along the front edge of the board used by the Control Memory. These are labeled locations U1 to U24. Normally only 12 2K x 4 PROM's are used in the odd locations; the other locations being unused and without sockets. The sequence numbers on the PROM's should be in the same order as the U numbers on the board.

The SC71 can have control memory size other than 2K. By use of 4K-bit and 8K-bit PROM sizes, control stores of 1024 to 4096 words may be achieved as shown in Table 3-1. Pins A, B, and C located by U34 and pins D, E, and F located by U25 must be jumpered accordingly.

Table 2-2

Control Memory Configurations

| Words            | Jumper           | <u>Size</u> <u>Loc</u> | cations     | Address             |

|------------------|------------------|------------------------|-------------|---------------------|

| 1024             | A - D & E - F    | 1024 x 4               | Odd         | 0-1023              |

| 2048             | A - D &<br>E - F | 1024 x 4<br>1024 x 4   | Odd<br>Even | 0-1023<br>1024-2047 |

| 2048<br>(normal) | A - C &<br>D - E | 2048 x 4               | Odd         | 0-2047              |

| 3072             | A - C &<br>D - E | 2048 x 4<br>1024 x 4   | Odd<br>Even | 0-2047<br>2048-3071 |

| 4096             | A - C & D - C    | 2048 x 4<br>2048 x 4   | Odd<br>Even | 0-2047<br>2048-4095 |

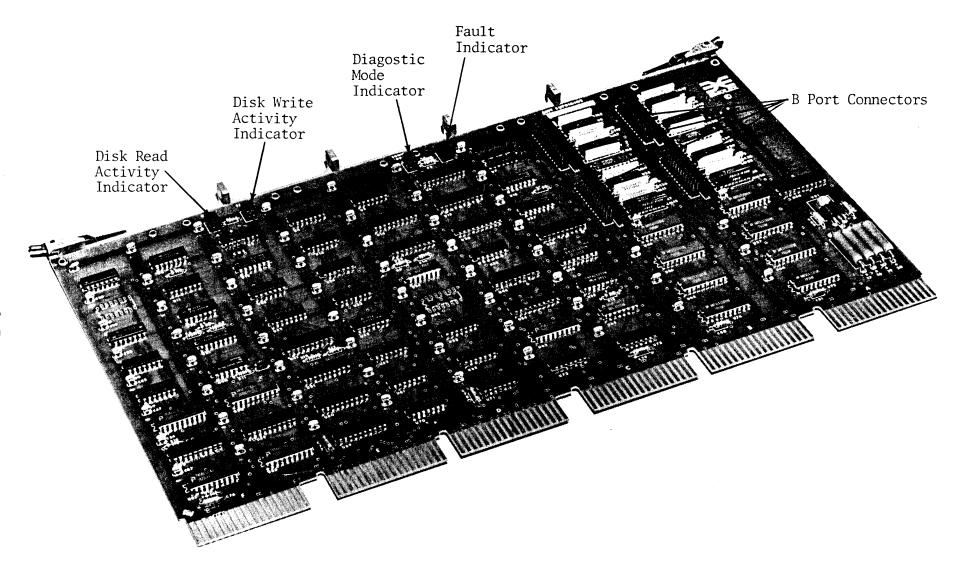

## 2.2.2 <u>B Board</u>

The B board of the controller is Part Number SU7010402 and incorporates all of the disk data circuitry, four B cable drive interfaces and the Cache bus address interface. Also included is a -5 volt power supply for the A cable and B cable transmitter and receiver circuits.

The B board is shown in Figure 2-3. The board is a two sided pcb with the same dimensions and backplane connector arrangement as the A board. The board plugs into slot 26, 30, 34, or 38 of the PDP-11/70 backplane which are used by the AWR board of the RH70.

# 2.2.2.1 B Cable Connectors

The B board contains four 26-pin flat cable connectors labeled J1, J2, J3, and J4. These connectors are for the radial B cables to each of four physical drives which may be attached to the controller. Pin 1 of these connectors is located at the left end of the connector adjacent to the J numbers. They are all interchangeable.

## 2.2.2.2 LED Indicators

The B board contains four LED indicators which provide the following information:

FAULT - Indicates controller fault or no drive

DIAGNOSTIC MODE - Indicates controller in self-test mode

WRITE - Indicates disk write activity

READ - Indicates disk read activity

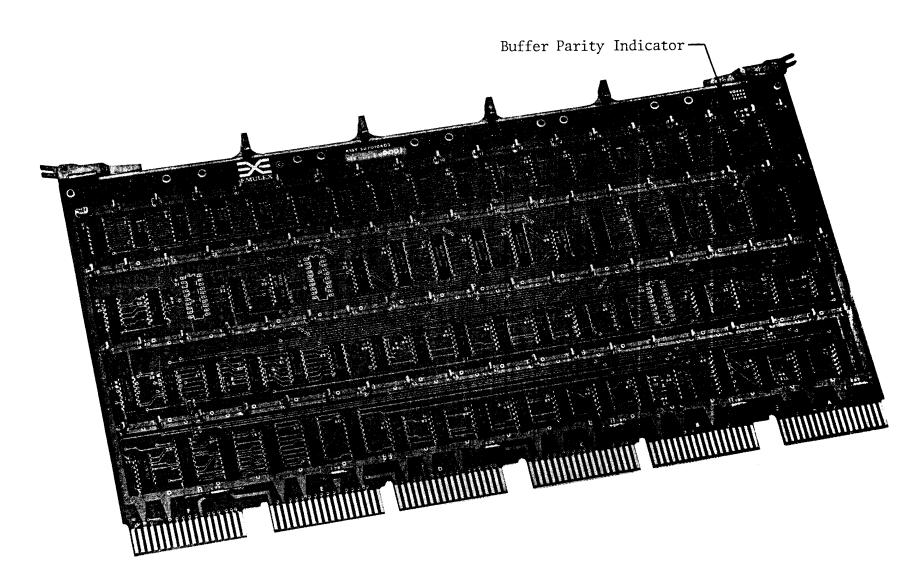

## 2.2.3 C Board

The C board of the controller is Part Number SU7010403 and SU7010406, and contains the 1K buffer and the Cache bus data interface including the Cache control and status information. The C board is shown in Figure 2-4. The board is a two sided pcb with board dimensions and backplane connector arrangement the same as the A board. The board plugs into slot 24, 28, 32, or 36 of the PDP-11 backplane which are used by the MDP board of the RH70. There are no switches or connectors on this board. A single LED indicator indicates when a parity error occurs in the buffer.

# 2.2.4 CST Board

The small interconnect board is used to pick up several RH70 signals in an otherwise unused RH70 slot and to retransmit them to one of the three hex boards. This board is inserted into the D, E, and F connectors of slot 25, 29, 33, or 37 which are normally used by the CST board of the RH70. The board is shown in Figure 2-5.

SC71 A Board Figure 2-2

SC71 B Board Figure 2-3

SC71 C Board Figure 2-4

### 2.3 INTERFACES

### 2.3.1 Disk Interface

The controller's disk interface conforms to the Flat Cable Interface Specification for the SMD, MMD, and CMD (CDC Document No. 64712400). The controller has been tested with most drives using the SMD interface and is compatable with these drives electrically and in timing.

The following defines the electrical interface and the recommended cables.

### 2.3.1.1 Drivers and Receivers

The drivers for the A and B cables are MC3453, which are equivalent to the 75110A. The receivers are MC3450 quad differential receivers, which are equivalent to 75108 receivers. The lines of the A cable are terminated with 82 ohms to ground. The lines of the B cable are terminated with 56 ohms to ground.

### 2.3.1.2 A Cable

The 60-conductor A cable is daisy-chained to all drives and terminated at the last drive. The signals in this cable are listed in Table 2-3 along with their function when the control tag (Tag 3) is asserted. The A cable should be 30 twisted pair flat cable with an impedance of 100 ohms and an accumulative length of no greater than 100 feet.

### 2.3.1.3 B Cable

The 26-conductor B cable is radial to all drives and contains the data and clock signals. The signals and grounds in this cable are listed in Table 2-3. The B cable should be 26 conductor flat cable with ground plane and drain wire. The impedance should be 130 ohms and the length must not be greater than 50 feet.

### 2.3.2 Unibus Interace

The controller interfaces to the PDP-11/70 via the RH70 slot and not an SPC slot as with a Unibus type controller. The Unibus consists of 18 address lines and 16 bi-directional data lines, plus control signals for data and interrupt vector address transfer and for becomming bus master for interrupts.

## 2.3.2.1 BR (Interrupt) Priority Level

The controller is hardwired for BR5. The other three Bus Grant signals are jumpered through.

# Table 2-3 Disk Drive Connections

| Pins Lo/Hi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Signal                                                                                                                                                                                       | (Tag 3 Function)                                                                                                                                                                                                            | From/To                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 23,53<br>4,56<br>7,54<br>56,53<br>10,41<br>222<br>27<br>45,33<br>112,43<br>115,44<br>115,44<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115,45<br>115 | Unit Select Unit Select Unit Select Bit 0 Bit 1 Bit 2 Bit 3 Bit 4 Bit 5 Bit 6 Bit 7 Bit 8 Bit 9 Bit 10 Open Cable D Fault Seek Error On Cylinder Index Unit Ready Address Mark Busy (dual-pe | bit 0 bit 1 bit 2 bit 3  (Write Gate) (Read Gate) (Servo Offset Plus) (Servo Offset Minus) (Fault Clear) (AM Enable) (Return to Zero) (Data Strobe Early) (Data Strobe Late) (Release)  etect  Found ort only)  ted ce Hold | To T         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Write Data Write Clock Servo Clock Read Data Read Clock Seek End Unit Selected Index Sector                                                                                                  | i                                                                                                                                                                                                                           | To<br>To<br>From<br>From<br>From<br>From<br>From |

### 2.3.2.2 Register Address

DIP switches are provided on the A board for assigning the starting address of the address block to be used by the controller and the range of addresses. SW3 located at U94 selects a block of 64 word addresses. SW2 located at U72 selects the starting address in the block of 64. The high-order five bits of the Unibus address (A17-A13) are always decoded as 1-bits and the low-order two bits are "don't care" conditions. Table 2-4 shows the switches for establishing the starting address of a block of 32, 16, 8 or 4 registers. Table 2-5 gives the switch settings to establish the basic block size, while Table 2-6 gives switch settings for smaller block sizes. If SW2-5 is ON, SW2-6 must also be ON; if SW2-4 is ON, SW2-5 and SW2-6 must be ON. For example, placing SW2-7 ON with SW2-4, SW2-5 and SW2-6 all OFF, estblishes a register block size of 22 (32 - 10) registers.

### 2.3.2.3 Interrupt Vector Address

The DIP switch SW4 located at U77 sets the interrupt vector address. Bits 15-9 of the address are assumed to be zeros, so the vector address range is 0-774. The low-order two bits are also assumed to be zero, since the vector address must start on a double word address. Table 2-7 gives the switch assignments for the remainder of the vector address.

### 2.3.2.3 DCLO and INIT Signals

The DCLO and INIT signals both performed a controller clear. The self-test is performed only if DCLO has been asserted.

### 2.3.3 Cache Interface

The Cache Bus address and control signals are on the B board and allow for a 22-bit memory address and control for writing and reading a single or double word to or from memory. The Cache Bus 32-bit data interface is on the C board.

Table 2-4

Register Block Starting Address

| Unibus<br>Address Bit | Address<br>Switch | Comments           |

|-----------------------|-------------------|--------------------|

| A12                   | SW3-7             | Switch ON = 1      |

| A 1 1                 | SW3-6             | Switch OFF = $0$   |

| A10                   | SW3-5             |                    |

| A09                   | SW3-4             |                    |

| 80A                   | SW3-3             |                    |

| A07                   | SW3-2             |                    |

| A06                   | SW3-1             |                    |

| A05                   | SW2-3             | (SW2-6 ON)         |

| A04                   | SW2-2             | (SW2-6, -5 ON)     |

| A03                   | SW2-1             | (SW2-6, -5, -4 ON) |

Table 2-5 Register Block Size

| Block<br>Size | Switches ON       | Switches OFF        |

|---------------|-------------------|---------------------|

| 32            |                   | SW2-6, SW2-5, SW2-4 |

| 16            | sw-6              | SW2-5, SW2-4        |

| 8             | SW2-6, SW2-5      | SW2-4               |

| 4             | SW2-6, SW2-5, SW2 | _4                  |

Table 2-6

Register Block Limit

| Inhibit Function                     | Switch      | Function                          |

|--------------------------------------|-------------|-----------------------------------|

| A04 * A03<br>(Switch ON=Inhibit)     | SW2-8<br>ON | Subtract last 8 words from block  |

| A05*(A04+A03)<br>(Switch ON=Inhibit) | SW2-7<br>ON | Subtract last 10 words from block |

Table 2-7

Interrupt Vector Address Switches

| Unibus<br>Data Bit | Vector Address<br>Switch | Comments       |

|--------------------|--------------------------|----------------|

| D08                | SW1-8                    | Switch OFF = 0 |

| D07                | SW1-7                    | Switch ON = 1  |

| D06                | SW1-6                    |                |

| D05                | SW1-5                    |                |

| D04                | SW1-4                    |                |

| D03                | SW1-3                    |                |

| D02                | SW1-2                    | (not used)     |

# 2.4 DISK FORMAT

# 2.4.1 Disk Organization

The SC71/B1 handles only one logical RM drive per physical drive, Except one fixed heads of Winchester drives are involved. The number of cylinders and tracks for each drive can be configured by the Configuration PROM. The number of sectors is always 32.

# 2.4.2 <u>Sector Organization</u>

Figure 2-6 shows the sector format used by the controller. Each track of 20,160 bytes is divided into 32 sectors of 630 bytes. The four byte header is preceded by a preamble of 30 bytes ending in the sync byte and is followed by a two byte CRC. The 256 word data field is preceded by a preamble of 20 bytes ending in the sync byte, and is followed by four bytes of ECC. This format is compatible with that of the DEC RM02/RM03/RM05.

If the actual size of the useful data information is less than 256 words, the remainder of the data field will be filled with 0's until 256 words have been written. During disk formatting procedures, each data track is located and recorded with header information by means of the Write Header and Data command. A disk pack should be formatted and the format verified before any real data is written on it. Once formatted, individual or groups of sectors should not be reformatted unless absolutely necessary.

# 2.4.3 Header

# 2.4.3.1 <u>Header Description</u>

Figure 2-7 shows the header format, which consists of the following three words:

Word One -

This word contains the cylinder address. It also contains a 1-bit in bit 12 to identify 16-bit format to the software and 1-bits in bit positions 14 and 15 to identify a good sector.

Word Two -

The low-order five bits of this word contain the sector address. Each track on the drive contains 32 sectors. The least significant six bits of the upper byte of this word contain the track address.

Word Three -

This is the CRC word which is generated and checked by the controller logic. This word is not available to the software.

----- Sector Length 630 Bytes -----Data Field | ECC | Recovery Preamble Sync Header CRC Preamble Sync | ----30---- ----512-----4-Figure 2-6 Sector Format Header Word 1: 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Cylinder Address 1 1 0 1 0 Header Word 2: 07 06 05 04 03 02 01 00 13 12 11 10 09 80 Sector Address 0 0 0 0 0 Track Address Header Word 3: 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Figure 2-7 Header Format

Cyclic Redundancy Code (CRC)

# 2.4.3.2 Header Field Handling

After the drive reports that it is on cylinder, the controller locates the desired sector by means of the sector counters for each drive that are maintained in the controller. The controller compares the first two words of the header against the desired track, sector and cylinder and then checks the CRC word for errors. An error in the header field is indicated by turning on the appropriate error bit in the error register (format error, header compare error, bad sector error or CRC error). A header error is only valid when the sector count field of the RMLA register and the sector field of the RMDA have already matched. It is immaterial where a CRC error occurs in the header field since the controller cannot determine its location in the field. However, software may read the header to memory by means of a Read Header and Data command. The header compare may be inhibited by setting the HCI bit in the RMOF register.

# 2.5 GENERAL PROGRAMMING INFORMATION

# 2.5.1 Clearing the Controller

The controller has the following clearing methods:

- a. Controller Clear Controller Clear is performed by writing a 1-bit into the CLR bit (bit 5 of RMCS2) or Unibus INIT. This causes the following to be cleared:

- RMCS1 bits 0-6, 8-9, 12-15; RMCS2 bits 0-5, 7-15; RMBA; RMBAE; RMCS2 bits 4-15. Sets RMCS2 bit 6 and RMCS1 bit 7.

- In all drives: RMER1; RMER2; RMDA; RMAS ATA bit; RMEC2; RMDS ATA, ERR and LST bits; RMMR1 bits 0-2, 4-15. Sets bit 3 of RMMR1.

- b. Error Clear The Error Clear is performed by writing a 1-bit into the TRE bit (bit 14 of RMCS1). This causes a clearing of RMCS1 bits 13 and 14, and bits 8 through 15 of RMCS2. Also clears the SC bit (bit 15 of RMCS1) if RMAS=0.

- C. Drive Clear The Drive Clear is a command. (Code 11.)

This causes the following registers in the drive selected by U2-U0 to be cleared:

- RMER1; RMER2; RMAS ATA bit; RMEC2; RMDS ATA and ERR bits; RMMR1 bits 0-2, 4-15. Sets bit 3 of RMMR1.

# 2.5.2 <u>Interrupt Conditions</u>

The controller generates an interrupt on the following conditions:

- a. Upon termination of data transfer if interrupt enable is set when the controller becomes ready.

- b. Upon assertion of attention or occurence of a controller error (SC being set) while the controller is not busy and the interrupt enable is set.

- when the program writes 1 into IE and RDY at the same time.

Note that this can be done by Read-Modify-Write instructions

(BIS, BIC, etc.) which set the IE bit.

# 2.5.3 Termination of Data Transfers

A data transfer which has been successfully started may terminate in the following ways:

- a. Normal Termination Word count overflows to 0 and the controller becomes ready at the end of the current sector.

- b. Controller Error An error occurs in the RMCS2 register bits 8 through 15. Any of these errors sets TRE which terminates the data transfer immediately and makes the controller ready.

- c. Drive Error The ERR bit in the RMDS register and at least one bit in an RMER1 or RMER2 register are set. TRE is also set and the controller becomes ready. The ATA for the drive doing the data transfer becomes asserted.

- d. Program-Caused Abort By performing a Controller Clear or a RESET instruction, the program can cause an abort of any operation. Status and error information is lost when this is done, and the controller and drive become ready immediately.

# 2.5.4 Ready Bits

RDY is the ready indicator for the controller. When RDY = 1, the controller is ready to accept a data transfer command. RDY is reset when the controller is doing a data transfer command. DRY is the ready indicator for the selected drive and is the complement of the drive's GO bit. To successfully initiate a data transfer command, both of these bits must be asserted. However, a non-data transfer command (Search, Drive Clear) may be issued to a drive at any time DRY is asserted regardless of the state of the RDY bit.

When a data transfer command is successfully initiated, both RDY and DRY become negated. When a non-data transfer command is successfully initiated, only DRY bit becomes negated.

The assertion of RDY after the execution of a data transfer command will not occur until the DRY bit is set and the controller is done. RDY is asserted on the completion of the last memory cycle (or at the time of an abort condition) and the last disk transfer.

If any command other than Drive Clear is issued to a drive which has ERR asserted, the command is ignored by the drive. If a Data Transfer command is issued to a drive which has ERR asserted, the drive does not execute the command and the missed transfer error (MXF, bit 9 in RMCS2 register) is set.

## 2.6 <u>DUAL CONTROLLER OPERATION</u>

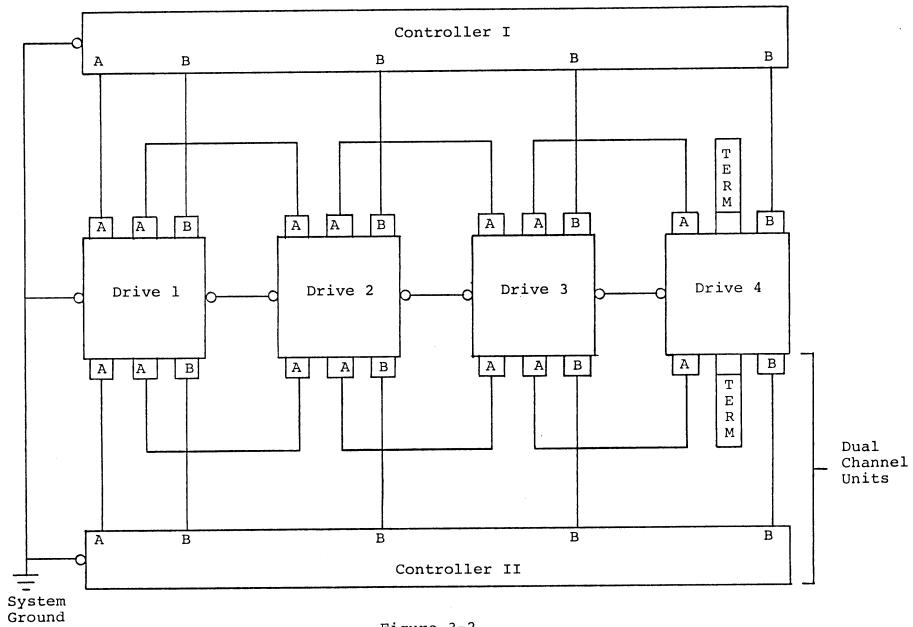

SMD drives may be equipped with a dual port option which provides the capability for two controllers (generally on separate computers) to access the drive. The SC71/B1 controller supports this type of operation as a standard feature. Most of the dual-port funtions of the DEC controller being emulated are supported, and those which are not should be transparent to a properly written dual-port driver.

# 2.6.1 Dual-Port Drives

The two drive ports are known as Channel I and Channel II. Each channel has a disable switch which disables the port and prevents the computer from having access to it. Access to the drive in dual-port operation is switched back and forth between the two controllers under program control of the two computers involved in a manner described in the following sections. Table 2-3 summarizes the register responses in dual-port operation.

# 2.6.2 <u>Unseized State</u>

The unseized state is when the drive is not connected to either controller. The CPU must issue a request for the controller to seize the drive. This request is done in one of the following ways:

- a. Writing into any drive register, including read-only registers.

- b. Reading any drive register except RMCS1.

- c. Writing a one-bit into the drive's ATA bit in RMAS.

# 2.6.3 <u>Seized State</u>

The drive is seized when it is logically connected to one of the controllers. At that time the DVA (RMCS1, bit 11) is set indicating that the drive is ready to communicate with the controller which has seized it. If the drive is seized by the other controller, the DVA bit is reset and all the drive registers read as 0's and any write to a register is ignored. Any attempt to seize a drive which is busy with the other port will cause the request to be remembered and acted upon when the drive is released

by the other controller.

### 2.6.4 Returning to the Unseized State

The drive is released and returned to the unseized state by issuing a release command. In addition, a one second timer in the controller will timeout and release the drive if one of the events listed in section 2.6.2 for seizing the drive is not performed periodically to keep resetting the timeout timer.

When the controller sees a previously busy drive becoming unseized, it checks its request flag. If the drive had been previously requested while busy on the other port, the controller will seize the drive, set the DVA bit and set the ATA causing an interrupt to the CPU if the IE bit is set. If the CPU does not respond to the attention within one second the drive will be released, but the ATA remains set.

### 2.6.5 DEC Compatability

The SC21/B controller differs from the equivalent DEC controller in three important areas. First, there is no neutral state. Since the controller does not have instantaneous access to all drives at the same time (a limitation of the daisy-chained A cable and the microprocessor organization of the controller), then if the drive is not currently seized the controller assumes it is busy on the other port. The DEC controllers can switch from neutral to seized state within the time required to do a single read or write of a drive register. In that case no ATA is set and the drive would appear to have been already seized.

Second, the release command is not instantaneous since the controller takes a few microseconds to execute the command. During this time the drive will appear to be still seized and the GO bit will be set.

Third, during a data transfer the timeout timers will not operate and the drives can not be polled to see if they are not busy. Therefore no drives are seized or released during the execution of a data transfer.