TC12/FS

(TS11 COMPATIBLE)

TAPE COUPLER

TECHNICAL MANUAL

3545 Harbor Boulevard Costa Mesa, California 92626 (714) 662-5600 TWX 910-595-2521

TC1251002 Rev E June, 1983

Copyright (C) 1983 by Emulex Corporation

The information in this manual is for informational purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in the manual.

Printed in U.S.A.

# TABLE OF CONTENTS

| Section | 1                                                                                                                                                                | INTRODUCTION                                                                                                                                                                                                                                                                        |                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|         | 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.3<br>1.4<br>1.4.1<br>1.4.2<br>1.4.3<br>1.5                                                                                     | SCOPE OVERVIEW General Description Coupler Modes PHYSICAL CHARACTERISTICS FEATURES Microprocessor Architecture Self-Test Efficient DMA DIAGNOSTICS OPERATING SYSTEMS                                                                                                                | 1-1<br>1-1<br>1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2                                                      |

| Section | 2                                                                                                                                                                | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                 |                                                                                                                  |

|         | 2.1<br>2.1.1<br>2.1.1.2<br>2.1.1.3<br>2.2<br>2.2.1<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.4.1<br>2.3.4.2<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5 | TC12 Coupler Board Connectors Switches Indicators ORGANIZATION Coupler Board TAPE TRANSPORT INTERFACE Connectors and Cable Input Circuits Output Circuits Signal Definitions Coupler to Formatter                                                                                   | 2-1<br>2-1<br>2-1<br>2-1<br>2-3<br>2-3<br>2-3<br>2-3<br>2-5<br>2-5<br>2-5<br>2-7<br>2-10<br>2-10<br>2-11<br>2-11 |

| Section | 3                                                                                                                                                                | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                              |                                                                                                                  |

|         | 3.1<br>3.1.1<br>3.1.2<br>3.1.2.1<br>3.1.2.2<br>3.1.2.3<br>3.1.3<br>3.1.3.1<br>3.1.4                                                                              | COUPLER REGISTERS  Base Address Register (TSBA)  Data Buffer Register (TSDB)  Normal Operation  Data Wraparound Using DATOB (odd)  Data Wraparound Using DATOB (even)  Status Register (TSSR)  Bootstrap Command  Extended Status Registers  Residual Frame Count Register  (RBPCR) | 3-1<br>3-2<br>3-2<br>3-3<br>3-3<br>3-3<br>3-6<br>3-7<br>3-7                                                      |

|         | 3.1.4.2          | Extended Status Register Zero (XSTO)  | 3-8             |

|---------|------------------|---------------------------------------|-----------------|

|         | 3.1.4.3          | Extended Status Register One (XST1)   | 3-10            |

|         | 3.1.4.4          | Extended Status Register Two (XST2)   | 3-1             |

|         | 3.1.4.5          | Extended Status Register Three (XST3) | 3-11            |

|         | 3.2              | PACKET PROCESSING                     | 3-12            |

|         | 3.2.1            | Command Packet/Header Word            | 3-15            |

|         | 3.2.2            | Command Packet Examples               | 3-19            |

|         | 3.2.2.1          | Get Status Command                    | 3-19            |

|         | 3.2.2.2          |                                       | 3-20            |

|         | 3.2.2.3          |                                       | 3-21            |

|         | 3.2.2.4          |                                       | 3-23            |

|         | 3.2.2.5          | Position Command                      | 3-24            |

|         | 3.2.2.6          |                                       | 3-25            |

|         | 3.2.2.7          |                                       | 3-25            |

|         | 3.2.2.8          | Initialize Command                    | 3-26            |

|         | 3.2.3            | Message Packet Header Word            | 3-27            |

|         | 3.2.4<br>3.3     | Message Packet Example                | 3-28            |

|         | 3.3.1            | OPERATIONAL INFORMATION               | 3-29            |

|         | 3.3.2            | Unibus Registers                      | 3-29            |

|         | 3.3.3            | Command and Message Packets           | 3-29            |

|         | 3.3.4            | Special Conditions and Errors         | 3-29            |

|         | 3.3.3            | Status Error Handling Notes           | 3-31            |

| Section | 4                | INSTALLATION                          |                 |

|         | 4.1              | INSPECTION                            | 4-1             |

|         | 4.2              | TAPE TRANSPORT PREPARATION            | 4 - 1           |

|         | 4.2.1            | Transport Placement                   | 4-1             |

|         | 4.2.2            | Address Selection                     | 4-1             |

|         | 4.3              | SYSTEM PREPARATION                    | 4-3             |

|         | 4.3.1            | Powering Down the System              | 4-3             |

|         | 4.4              | COUPLER SETUP                         | 4-3             |

|         | 4.4.1            | Coupler Modes                         | 4-3             |

|         | 4.4.2            | Coupler Address Selection             | 4-4             |

|         | 4.4.3            | Individual Transport Enabling         | 4-5             |

|         | 4.4.4            | Interrupt Vector Address              | 4-5             |

|         | 4.4.5            | Speed Selection for Tape Transports   | 4-7             |

|         | 4.4.6<br>4.4.6.1 | Option Switches                       | 4-7             |

|         | 4.4.6.1          | Density                               | 4-7             |

|         | 4.4.6.2          | Interblock Gap                        | 4-7             |

|         | 4.4.6.4          | VAX TSll Diagnostics                  | 4-8             |

|         | 4.4.0.4          | CDC Extended Status Command           | 4-8             |

|         | 4.5.1            | PHYSICAL INSTALLATION Slot Selection  | 4-8             |

|         | 4.5.2            | NPG Signal Jumper                     | 4-8             |

|         | 4.5.3            | Mounting                              | 4-8             |

|         | 4.6              | CABLING                               | 4-8<br>4-8      |

|         | 4.6.1            | Cabling the TCl2 Coupler to a         | 4-8<br>4-8      |

|         | _ ~ ~ ~          | Transport Formatter                   | 4 <sup></sup> 0 |

|          | 4.6.2.1<br>4.6.2.2<br>4.6.3<br>4.7<br>4.7.1<br>4.7.2<br>4.7.2.1<br>4.7.2.2 | Formatted Tape Transports Grounding TESTING Self-Test Diagnostics                      | 4-9<br>4-11<br>4-11<br>4-11<br>4-11<br>4-11 |

|----------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------|

| Appendix |                                                                            | TC12 OPTION SWITCHES                                                                   | 4-12                                        |

| nppendix | A                                                                          | TCIZ OFIION SWITCHES                                                                   |                                             |

| Appendix | В                                                                          | ADDRESS SELCTION FOR REVISION A BOARDS                                                 |                                             |

|          | B.1<br>B.2<br>B.3                                                          | INTRODUCTION TRANSPORT ENABLING ADDRESS SELCTION                                       | B-1<br>B-1<br>B-1                           |

| Appendix | С                                                                          | AUTOCONFIGURE AND VMS, RSTS/E AND RSX-11                                               | LM                                          |

|          | C.1<br>C.2                                                                 | INTRODUCTION DETERMINING THE CSR ADDRESS FOR USE                                       | C-1<br>C-1                                  |

|          | C.3                                                                        | WITH AUTOCONFIGURE DETERMINING THE INTERRUPT VECTOR ADDRESS FOR USE WITH AUTOCONFIGURE | C-2                                         |

|          | C.4                                                                        | A SYSTEM CONFIGURATION EXAMPLE                                                         | C-4                                         |

# LIST OF TABLES

| Table No.                                                                                           | <u>Title</u>                                                                                                                                                                                                                                                                                        |                                                         |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Table 1-1 Table 2-1 Table 2-2 Table 3-1 Table 3-2 Table 3-3 Table 4-1 Table 4-2                     | Termination Class Codes Unibus Starting Addresses Alternate Unibus Starting Address                                                                                                                                                                                                                 | 1-3<br>2-9<br>2-12<br>3-6<br>3-17<br>3-30<br>4-4<br>4-5 |

| Table A-1 Table A-2 Table A-3 Table A-4 Table B-1 Table B-2 Table C-1 Table C-2 Table C-3 Table C-4 | Selection TC12 Factory Switch Settings Option Switch SW1 Settings Option Switch SW2 Settings Option Switch SW3 Settings Tape Unit Selection Unibus Starting Address Selection SYSGEN Device Table Priority Ranking for Floating Vectors CSR and Vector Address Example Floating Address Computation | A-1<br>A-2<br>A-2<br>B-1<br>B-2<br>C-2<br>C-3<br>C-5    |

|                                                                                                     | LIST OF FIGURES                                                                                                                                                                                                                                                                                     |                                                         |

| Figure No.                                                                                          | <u>Title</u>                                                                                                                                                                                                                                                                                        |                                                         |

| Figure 2-1 Figure 2-2 Figure 3-1 Figure 3-2 Figure 4-1 Figure 4-2 Figure 4-3                        | TC12 Coupler Board TC12 Block Diagram Byte Swap Sequence, Forward Byte Swap Sequence, Reverse TC12 Coupler Assembly Vector Address Selection Tape Transport Cabling                                                                                                                                 | 2-2<br>2-4<br>3-18<br>3-18<br>4-2<br>4-6<br>4-10        |

# 1.1 SCOPE

This manual provides information related to the capabilities, design, installation and use of the TCl2/FS Tape Coupler. The manual also provides applicable diagnostic and applications information.

# 1.2 <u>OVERVIEW</u>

# 1.2.1 General Description

The TCl2 Magnetic Tape Coupler emulates the Digital Equipment Corporation TSll tape coupler. The coupler may function in one of two modes. The streaming mode is used to interface streaming tape transports with PDP-ll and VAX-ll computers. The formatted mode interfaces all stop/start tape transports having the industry standard (Pertec) interface to PDP-ll and VAX-ll computers. Both modes are software compatible with the TSll.

# 1.2.2 Coupler Modes

The TCl2 functions with both streaming and formatted tape drives. The mode of the coupler is determined by the setting of a minimal number of switches. Detailed switch settings may be found in Section 4. Below is a brief description of the two types of modes in which the coupler may function.

Formatted Tape Drive Mode: When enabled to function with formatted tape drives, the coupler will read and write DEC or IBM compatible 9-track PE (1600 bpi) or 9-track NRZI (800 bpi) formats. This mode accommodates transport speeds in a range of 12.5 to 125 ips. A maximum of four tape transports may be attached to the coupler with any mix of 9-track NRZI, PE or dual density.

Streaming Tape Drive Mode: The streaming mode is media compatible with tapes created on the DEC TS11. Tapes have 9-tracks at 1600 bpi. In streaming mode, the transport speed is typically 100 ips. In non-streaming mode transport speed is typically 25 ips (check manufacturer specs. for exact speed). The coupler shifts from non-streaming mode to streaming mode automatically if enough data to support the additional throughput is available. The shift is software transparent.

# 1.3 PHYSICAL CHARACTERISTICS

The TC12 is constructed on a single quad-size board which plugs directly into any PDP-11 or VAX-11 SPC slot. It is a four layer PCBA and it plugs into connectors C, D, E and F of the backplane. Two 50-wire flat cables connect the controller to the first tape transport. The board draws power from the PDP-11 backplane.

# 1.4 FEATURES

# 1.4.1 Microprocessor Architecture

The TCl2 design incorporates a high-speed eight-bit microprocessor to perform most of the functions of the controller. It is the microprocessor's flexiblity that allows the TSll to be emulated so completely and economically. In addition, it is the microprocessor design that allows the extensive self-test capability that the TCl2 provides.

### 1.4.2 Self-Test

The controller incorporates an extensive self-test capability. The self-test is executed every time the controller is powered on. It does not execute self-test with a bus INIT. The LED on the top of the PCBA is turned ON when the controller is cleared and is turned OFF if the coupler gets through the self-test. If the coupler does not properly execute the self-test, the LED remains ON and the coupler cannot be addressed by the CPU.

# 1.4.3 Efficient DMA

The coupler incorporates 64 bytes of data buffering and it transfers data to or from memory on a word basis, except for odd bytes at the start or end of the record.

# 1.5 DIAGNOSTICS

The TCl2 coupler executes the following DEC TSll diagnostics in both NRZI and PE modes:

### PDP-11:

ZTSH - Data Reliability

ZTSI - Coupler Repair Diagnostic (runs first three tests\*)

#### VAX-11:

EVMAA - Data Reliability

EVMAD - TSll Repair Diagnostic (does not run tests 5:10, 15, 16 and 18)

Note: Subtest 2 of EVMAA will report two data compare errors when running on the VAX-11/780. This is normal, even for a DEC TS11.

\*Requires minor patch

### 1.6 OPERATING SYSTEMS

The TCl2/FS Tape Coupler is fully compatible with all DEC operating systems.

# Table 1-1 General Specifications

FUNCTIONAL

Recording Standards IBM, ANSI, DEC

Number of Tracks

Recording Method Streaming: 3200 or 1600 BPI

and Density Formatted: 1600 or 800 BPI

Number of Emulations per

Coupler (tape units)

Tape Speeds (ips) 12.5 to 125

UNIBUS INTERFACE

Register Addresses Switch Selectable

Interrupt Vector Address Switch Selectable

Interrupt Priority Level BR5

Data Transfer Direct Memory Access (DMA) with word (16-bit) transfer, except for

odd byte at beginning or at end of

record.

PHYSICAL

Mounting Any SPC slot in standard DEC

system unit.

Cables Two 50-wire flat cables.

ELECTRICAL

Power +5V, 6 amps.

ENVIRONMENTAL

Operating Temperature 0°C to +55°C

Storage Temperature -10°C to +70°C

Humidity 10 to 90%, no condensation.

# 2.1 PHYSICAL DESCRIPTION

The TCl2 Tape Coupler is constructed on a single quad-size printed circuit board. This board contains all circuitry required to control either streaming or formatted tape transports using both NRZI and PE formats.

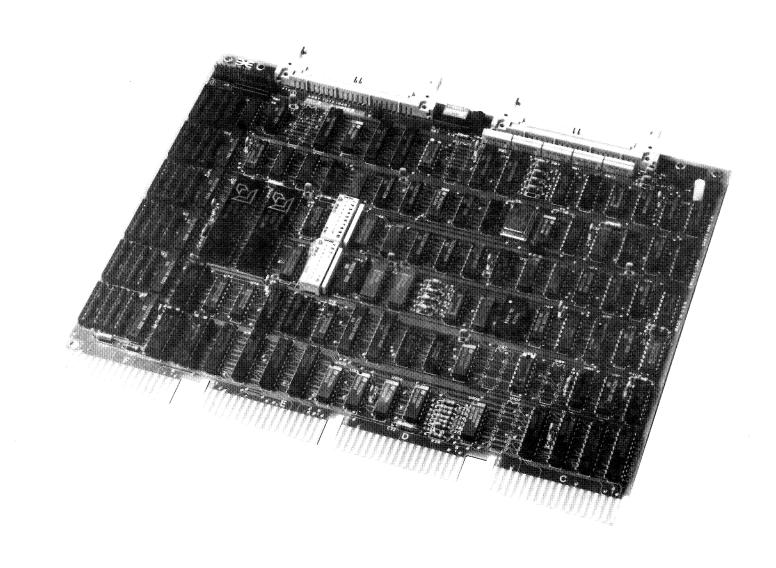

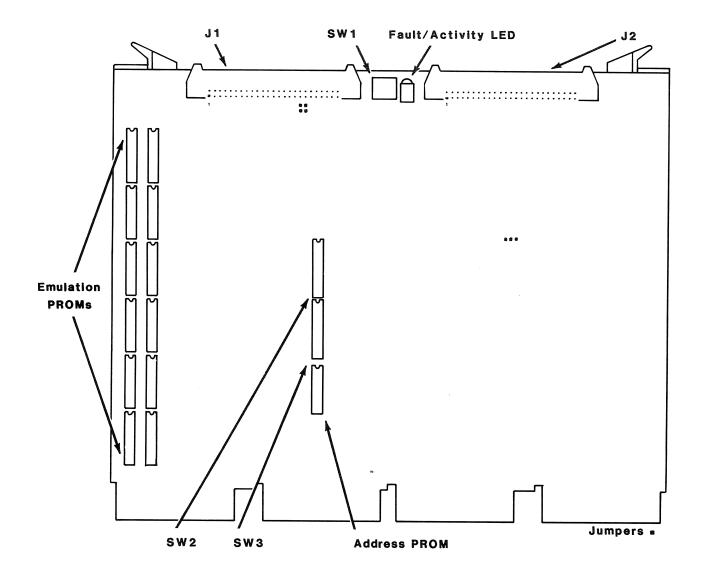

# 2.1.1 TC12 Coupler Board

The TCl2 Tape Coupler board is designated Part No. TCl210401. This board contains interface circuitry for both a DEC Unibus and a modified industry standard tape transport plus all other circuitry required for tape control and data transfer operations.

The TCl2 coupler board is shown in Figure 2-1. The board is a 4-layer PCB with power and ground planes on the inner layers and etch interconnects on the outer layers.

As a quad-sized PCBA, the board interfaces only to connector rows C, D, E, and F. The 18 pins of each connector row are designated A through V - excluding the letters G, I, O, and Q - from right to left; the top side pins are designated "1" and the bottom side pins are designated "2".

# 2.1.1.1 Connectors

The coupler is interfaced to the tape transport via two 50-pin connectors labled Jl and J2 at the top edge of the board.

There are two additional male connectors located on the board, designated J3 and J4. These are used for connecting a special test panel used for factory test and repair operations and are not intended for use in normal coupler operations.

# 2.1.1.2 Switches

The three DIP switches are for tape speed selection and coupler options.

# 2.1.1.3 Indicators

The LED located to the right of the two connectors is both a coupler fault and an activity indicator. It will flash during data transfer operations with the tape.

Figure 2-1 TC12 Coupler

# 2.2 ORGANIZATION

# 2.2.1 Coupler Board

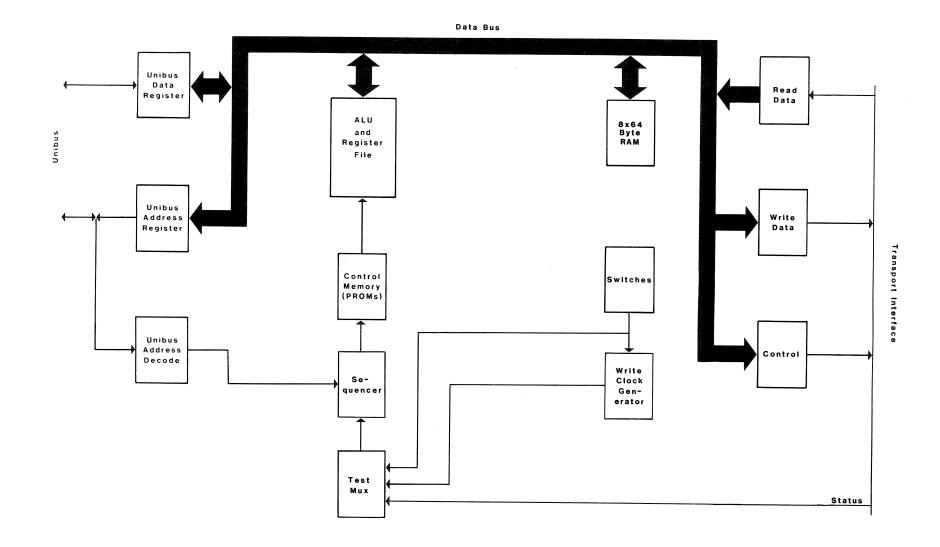

A block diagram showing the major functional elements of the TC12 coupler is shown in Figure 2-2. The coupler is organized around a eight-bit high-speed bipolar microprocessor. The ALU and register file portion of the microprocessor are implemented with two 2901 bit slice components. The microinstruction is 48 bits in length and the control memory of 2K words is implemented with twelve 2K x 4 PROMs.

All the device registers of the TCl2 coupler, the 64-word data buffer and working storage are contained in a 1K x 8 RAM.

The Write Data Register (WDR) holds the nine bits of data to the transport and the Read Data Register (RDR) receives the nine data bits from the transport. The Control Register latches internal microprocessor control signals as well as the external signals used to control the transport. The status signals from the transport are testable signals to the microprocessor.

The Unibus interface consists of a 16-bit bi-directional set of data lines and an 18-bit set of address lines. The Unibus interface is used for programmed I/O, CPU interrupts, and NPR data transfers. The microprocessor responds to all programmed I/O and carries out the I/O functions required for the addressed coupler register. The microprocessor also controls all NPR operations and transfers data between the Unibus data lines and the transport via its own internal buffer.

### 2.3 TAPE TRANSPORT INTERFACE

There is a slight difference in the tape transport interface when the TCl2 is functioning with a formatted tape drive rather than a streaming drive. Both interfaces are depicted in Table 2-1. In the few instances where pins have different functions with respect to the emulation (and therefore different mnemonics, HSPD/DEN, for example) the first mnemonic applies to the streaming tape transport interface and the second to the formatted tape transport interface. The definitions of all signal mnemonics are contained in paragraph 2.3.4, below. Both interfaces are based on the industry standard Pertec interface.

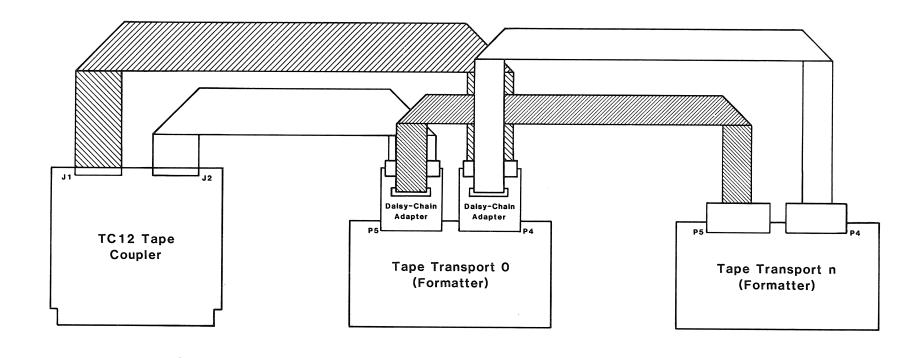

# 2.3.1 Connectors and Cable

The tape coupler uses two 50-conductor flat cables to interface to the transports. The cable should be a twisted pair with a maximum daisy-chained length of not over 30 feet. All wires should be 24 AWG minimum, and each pair should have not less than one twist per inch. Connectors are standard 50-pin flat cable connectors.

Figure 2-2 TC12 Block Diagram

# 2.3.2 <u>Input Circuits</u>

The input lines from the tape transport are terminated with a 220 ohm (5%) resistor to plus five volts, and a 330 ohm (5%) resistor to ground. All input circuits have low-level input voltage of 0.8 v maximum and a high level input voltage of 2.0 volt minimum. The input receivers are all 74LS type circuits.

# 2.3.3 Output Circuits

All output lines must be terminated at the far end of the daisy-chained cable with a 220 ohm (5%) resistor to plus five volts and a 330 ohm (5%) resistor to ground. Output driver circuits are 74LS374 TTL registers, except for some 7438 open collector gates.

# 2.3.4 <u>Signal Definitions</u>

# 2.3.4.1 Coupler to Formatter

#### Transport Address: TADO, TAD1

These lines determine which of up to four transports is selected by the coupler. TAD1 is the most significant bit.

#### Formatter Address: FAD

This signal selects one of two formatters. It is always zero for this emulation.

# Initiate Command: GO

A pulse which initiates any command specified by a combination of the command signals REVERSE, WRT, WFM, ERASE, EDIT, LGAP and/or HSPD.

#### Rewind Command: REWIND

A low level pulse of approximately one microsecond commands the selected transport to rewind to the load point.

#### Unload Command: UNL

A low level pulse of approximately one microsecond causes the selected tape transport to go off-line, rewind the tape, and when BOT is encountered, unload the tape onto the supply reel.

NOTE: Some tape drives do not support this feature and will go off-line without rewinding.

### Write: WRT

Write mode is specified when this signal is TRUE; read mode is specified when it is FALSE.

# Write File Mark: WFM

When this signal and WRT are TRUE, the transport will write a file mark on the tape.

#### **Erase: ERASE**

When ERASE and WRT are TRUE, the transport executes a dummy write command. The transport will go through all the operations of a normal write command but no data will be recorded. A length of tape will be erased equivelent to the length of the Dummy record (as defined by LWD). If ERASE, WRT and WFM are TRUE, the transport will execute a dummy write file mark command. A fixed length of tape of approximately 3.75 inches will be erased.

## High Speed: HSPD

If this signal is TRUE when a read or write command is issued, the transport will read or write at the high speed.

#### Last Word: LWD

When TRUE during a write or erase command, this signal indicates that the next character to be strobed into the transport (formatter) is the last character of the record.

#### On-Line: LOL

This signal causes the selected transport to go On-Line.

#### Reverse: REVERSE

When TRUE, this signal initiates reverse tape motion. When it is FALSE, forward tape motion is specified.

#### Edit: EDIT

This is a signal which, when TRUE duing a read reverse operation, modifies the read reverse stop delay to optimize head positioning for a subsequent edit operation. When EDIT and WRT are TRUE, the selected transport operates in the edit mode.

# Formatter Enable: FEN

When FALSE this signal causes the transport to be held in an initialized state.

# Write Data 7:0, Parity: WD7:WD0, WDP

These line transmit data to the transport. Line zero is the most significant. WDP carries the odd parity bit associated with each data word. The parity bit is generated by the coupler.

#### Long Gap: LGAP

When TRUE, this signal causes the transport to generate a 1.2 in. long IBG.

# Read Threshold Level 1: RTH1

This line is used only by transports with single gap heads to specify the operating level of the read threshold circuits. A TRUE level specifies selection of the high read threshold level, and a FALSE level specifies the normal read threshold.

#### Read Threshold Level 2: RTH2

This line is used only by transports with extra low read threshold capabilities. When TRUE, the extra low threshold is specified; when FALSE, the normal threshold is specified.

# Density: DEN

When used with a dual-mode transport, the TRUE level selects NRZI and the FALSE level selects P.E.

### 2.3.4.2 Formatter to Coupler

# Formatter Busy: FBY

When TRUE, this signal inhibits further commands to the formatter. The signal becomes TRUE on the trailing edge of GO when a command is issued by the coupler. FBY remains TRUE until a new command can be given.

### On-Line: ONL

A low level indicates that the selected tape transport is on-line and under control of the tape coupler.

### Ready: READY

A low level indicates that the selected tape transport is loaded and not rewinding.

### Rewinding: RWD

A low level indicates that the selected tape transport is engaged in a rewind operation or the load sequence following a rewind operation.

#### End of Tape: EOT

A low level indicates that the EOT tab on the tape is being sensed.

# Beginning of Tape: BOT

A low level indicates that the selected tape transport is sensing the BOT tab on the tape, has completed its initial load sequence, and the tape transport is not rewinding.

#### File Protect: FPT

A low level indicates that a reel of tape without a write enable ring installed is mounted on the transport.

#### Data Busy: DBY

This signal becomes TRUE after a command has been accepted by the transport. DBY remains TRUE until the data transfer is complete and the appropriate post record delay has expired.

## Hard Error: HER

A TRUE pulse of this signal indicates that an uncorrectable read error has occured and that the record should either be reread or rewritten.

#### Corrected Error: CER

A TRUE pulse of this signal indicates that a single track dropout has been detected and the formatter is performing an error correction.

# Identification: PEID

When TRUE, this signal indicates that a PE identification burst has been detected. When in 800 bpi mode (NRZI), this signal is TRUE when the read information being transmitted to the coupler is a cyclic redundancy check character (CRCC) or a longitudinal redundancy check character (LRCC). It is FALSE when data characters are being transmitted.

#### File Mark: FMK

This signal is pulsed when a file mark is detected on the tape during a read operation or during a write file mark operation in a read-after-write transport.

#### **High Speed Status: HSPS**

When TRUE, this signal indicates that the selected transport is in the 100 ips (streaming) mode. A FALSE level indicates that the transport is operating at low speed (start/stop).

### NRZI Mode: INRZ

This signal is TRUE when the transport is in 800 bpi mode (NRZI).

Table 2-1 Cable Interface

| Connector                                               | Sig<br>Pin                            | Grd<br>Pin                                             | Mnemonic  | Connector | Sig<br>Pin | Grd<br>Pin | Mnemonic |

|---------------------------------------------------------|---------------------------------------|--------------------------------------------------------|-----------|-----------|------------|------------|----------|

| Jl                                                      | 2                                     | 1                                                      | FBY       | Ј2        | 1          | 5          | RDP      |

|                                                         | 4                                     | 3                                                      | LWD       |           | 2          | 5          | RD0      |

|                                                         | 6                                     | 5                                                      | WD4       |           | 3          | 5          | RD1      |

|                                                         | 8                                     | 7                                                      | GO        |           | 4          | 5          | BOT      |

|                                                         | 10                                    | 9                                                      | WD0       |           | 6          | 5          | RD4      |

|                                                         | 12                                    | 11                                                     | WDl       |           | 8          | 7          | RD7      |

|                                                         | 14                                    | 13                                                     | Spare     |           | 10         | 9          | RD6      |

|                                                         | 16                                    | 15                                                     | LOL       |           | 12         | 11         | HER      |

|                                                         | 18                                    | 17                                                     | REVERSE   |           | 14         | 13         | FMK      |

|                                                         | 20                                    | 19                                                     | REWIND    |           | 16         | 15         | PEID     |

|                                                         | 22                                    | 21                                                     | WDP       |           | 18         | 17         | FEN      |

|                                                         | 24                                    | 23                                                     | WD7       |           | 20         | 19         | RD5      |

|                                                         | 26                                    | 25                                                     | WD3       |           | 22         | 21         | EOT      |

|                                                         | 28                                    | 27                                                     | WD6       |           | 24         | 23         | UNL      |

|                                                         | 30                                    | 29                                                     | WD2       |           | 26         | 25         | INRZ     |

|                                                         | 32                                    | 31                                                     | WD5       |           | 28         | 27         | READY    |

|                                                         | 34                                    | 33                                                     | WRT       |           | 30         | 29         | RWD      |

|                                                         | 36                                    | 35                                                     | LGAP/RTH2 | l         | 32         | 31         | FPT      |

|                                                         | 38                                    | 37                                                     | EDIT      |           | 34         | 33         | RDS      |

|                                                         | 40                                    | 39                                                     | ERASE     |           | 36         | 35         | WDS      |

|                                                         | 42                                    | 41                                                     | WFM       |           | 38         | 37         | DBY      |

|                                                         | 44                                    | 43                                                     | RTH1      |           | 40         | 39         | HSPS     |

|                                                         | 46                                    | 45                                                     | TAD0      |           | 42         | 41         | CER      |

|                                                         | 48                                    | 47                                                     | RD2       |           | 44         | 43         | ONL      |

| Jl                                                      | 50                                    | 49                                                     | RD3       |           | 46         | 45         | TAD1     |

|                                                         |                                       |                                                        |           |           | 48         | 47         | FAD      |

| 6000 WHITE COME COME GAME GAME AND AND STORE 600 PERSON | Callen (Marco Mosso Marco Mosso Mosso | COMP ESSON CORPUS ESSONS EXTERN EXTERN COSTACY MISSION |           | Ј2        | 50         | 49         | HSPD/DEN |

NOTE: When two mnemonics are given for a pin (HSPD/DEN, for example) the first applies to the streaming tape interface and the second to the formatted tape interface.

# Write Data Strobe: WDS

This signal is pulsed each time a data character is written onto tape. WDS samples the write data lines WDP, WD7:WD0 from the coupler and copies this information character by character into the formatter write logic. The first character should be available prior to the first write strobe pulse and succeeding characters should be set up within half a character period after the trailing edge of each write strobe.

#### Read Data Strobe: RDS

This signal consists of a pulse for each character of read information to be transmitted to the coupler. This signal should be used to sample the read data lines RDP, RD7:RD0.

# Read Data 7:0, Parity: RD7:RD0, RDP

Each character read from tape is made available by parallel sampling the read lines with RDS. Since the data remains on the read data lines for a full character period, corresponding RDS pulses are timed to occur after approximately the center of the character period.

### 2.4 UNIBUS INTERFACE

The coupler interfaces to the PDP-11 or VAX-11 Unibus via a Small Peripheral Coupler (SPC) connector. The Unibus consists of 18 address lines and 16 bi-directional data lines, plus control signals for data and interrupt vector address transfer and for becomming bus master. The signal connections of the SPC connector are shown in Table 2-2.

# 2.4.1 BR (Interrupt) Priority Level

The coupler is hardwired for BR5. The other three Bus Grant signals are jumpered through.

### 2.4.2 Register Addresses

The addresses which are assigned to the coupler's registers are selected from a range of four address groups. Each group contains contiguous starting addresses for four TS11 emulations. The emulations require only two Unibus register addresses a piece. See paragraph 4.4.2 for a list of the available addresses.

# 2.4.3 <u>Interrupt Vector Address</u>

The interrupt vector addresses for the four TS11 emulations provided by the TC12 are selectable. See paragraph 4.4.4 for a list of the available vector addresses.

# 2.4.4 DCLO and INIT Signals

The DCLO and INIT signals both perform a coupler clear. The self-test is performed only if DCLO has been asserted.

# 2.4.5 NPR Operations

All DMA data transfers are carried out under microprocessor control. A check is made for memory parity errors when doing a tape write operation. If an error is detected the Unibus Parity Error (UPE) error is set.

Table 2-2 SPC Unibus Connections

| Column | С      |     | 1                                     | D      |      | E    |      | F    |

|--------|--------|-----|---------------------------------------|--------|------|------|------|------|

| Pin    | 1      | 2   | 1                                     | 2      | 1    | 2    | 1    | 2    |

| A      | NPGIN  | +5V |                                       | +5V    |      | +5V  |      | +5V  |

| В      | NPGOUT | 1   |                                       |        |      | -15V |      | -15V |

| С      | PA     | GND |                                       | GND    | A12  | GND  |      | GND  |

| D      |        | D15 |                                       | BR7    | A17  | A15  | BBSY |      |

| E      |        | D14 |                                       | BR6    | MSYN | A16  |      |      |

| F      |        | D13 |                                       | BR5    | A02  | Cl   |      |      |

| H      | D11    | D12 |                                       | BR4    | A01  | A00  |      |      |

| J      |        | D10 |                                       |        | SSYN | CO   | NPR  |      |

| K      |        | D09 |                                       | BG7IN  | A14  | A13  |      |      |

| L      |        | D08 | INIT                                  | BG7OUT | All  |      |      |      |

| M      |        | D07 |                                       | BG6IN  |      |      | INTR |      |

| N      | DCLO   | D04 |                                       | BG6OUT | A08  |      |      |      |

| P      |        | D05 |                                       | BG5IN  | A10  | A07  |      |      |

| R      |        | D01 |                                       | BG50UT | A09  |      |      |      |

| S      | PB     | D00 |                                       | BG4IN  |      |      |      |      |

| T      | GND    | D03 | GND                                   | BG4OUT | GND  |      | GND  | SACK |

| U      |        | D02 |                                       |        | A06  | A04  |      |      |

| V      | ACLO   | D06 | 19 6000 6009 6000 dans dies time dass |        | A05  | A03  |      |      |

#### 3.1 COUPLER REGISTERS

This section describes and defines the TCl2 registers and packet processing. In addition, programming examples and packet formats are provided to illustrate basic TCl2 programming concepts.

The DEC TS11 supports only a single tape transport. Therefore, each tape transport supported by the system has a unique set of unibus registers and command/message buffers in CPU memory. The Emulex TC12 supports four tape transports. Thus, the TC12 is really emulating four TS11s with their attendant registers. It is, therefore, inaccurate to refer to TC12 when discussing registers because the four register sets that the 12 contains are not related. For example, initializing one of the subsystem emulations by writing to the appropriate TSSR register does not affect the other three emulations. Also, it is not necessary (nor possible) to separate coupler command or status from transport command or status because each register and command/message buffer set is dedicated to the individual transport. Consequently, when discussing an individual emulation we will use the term transport instead of using emulation, TC12 or TS11.

Device register usage is compatible with DEC TS11 register definitions. However, some additions have been made to provide extended functions.

The eight transport registers are:

TSBA (1) - Unibus Address Register

TSDB (1) - Unibus Data Buffer

TSSR (1) - Status Register

XST (5) - Extended Status Registers

Each transport has two Unibus word locations used as device registers. The base address, when written to, is the data buffer register (TSDB). When read, it is the bus address register (TSBA). The second device register (base address + 2) is the status register (TSSR). Writing to the TSSR causes a subsystem initialize command, and reading the TSSR reads device status.

The TSDB register is the only register written to during normal operations. DATO or word access must be used to properly write command pointers to the TSDB. DATOB or byte access to the TSDB causes maintenance functions.

Commands are not written to the transport's Unibus registers. Instead, command pointers, which point to a command packet somewhere in CPU memory space, are written to the TSDB register. The command pointer is used by the transport to retrieve the words

in the command packet. The words of the command packet tell the transport the function to be performed. They also contain any function parameters such as bus address, byte count, record count, and modifier flags.

# 3.1.1 Base Address Register (TSBA)

Read Only

The TSBA is a 16-bit register that is read at the transport's base address (17XXXX). It is a reflection of the least significant 16 bits of the 18-bit TSDB register. (TSDB bits 17 and 16 are displayed in TSSR bits 09 and 08, respectively.) The contents of TSBA are valid only after the termination of a command. (A command is initiated by loading a command packet address into TSDB.) The termination may be either with or without errors. The TSBA is the base address in the read only mode and it is not cleared on power up, subsystem INIT, or bus INIT. It can also be read at any time with or without the transport unit connected.

Upon completion of a command, the TCl2 deposits a message packet in a message buffer located in CPU memory. The TSBA may be read to determine the highest message buffer address plus two.

# 3.1.2 <u>Data Buffer Register (TSDB)</u>

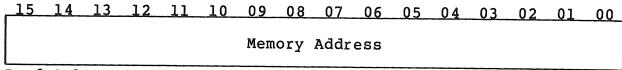

| 15 1 | 4 13 | 12 | 11_ | 10 | 09 | 0.8 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|------|------|----|-----|----|----|-----|----|----|----|----|----|----|----|----|

| 15 1 |      |    |     |    |    |     |    |    |    |    |    |    |    | 1  |

Write Only

The TSDB is an 18-bit register that is parallel loaded from the Unibus at the base address. The TSDB can be loaded when the transport is bus slave by three different types of transfers from a bus master. Two transfers are for maintenance purposes (DATOB to high byte and DATOB to low byte). The third transfer is for normal (word) operation (DATO). This register is write-only and is not cleared at power up, subsystem initialize or bus initialize. The transport responds with SSYN anytime the TSDB is written to.

# 3.1.2.1 Normal Operation

A command is issued to the transport by loading an 18-bit address into the TSDB using a DATO. The address is that of a command packet located somewhere in Unibus address space. The address is loaded into the TSDB using the following format. Bits <15:02> of the register are loaded with bits <15:02>, respectively, from the Unibus. Bits 16 and 17 of the address are loaded from bits 00 and

Ol, respectively, from the Unibus. Bit 00 and bit 01 of the address are automatically loaded with zeroes by the transport logic. Loading the TSDB register initiates a fetch by the transport of the command packet at the specified address. The command defined in the packet is then executed.

# 3.1.2.2 <u>Data Wraparound Using DATOB (odd)</u>

When TSDB is loaded by a DATOB to TSDB high byte (odd address), the following happens. Bits <07:00> of the register are loaded with bits <15:08>, respectively, from the Unibus. Bits <15:08> of the register are loaded with bits <15:08>, respectively, from the Unibus. Bits 16 and 17 of the register are loaded with bits 08 and 09 respectively, from the Unibus. The TSDB is then loaded into TSBA. This transfer will be executed anytime a DATOB to the TSDB high byte is done. IF SSR (see TSSR bit 07) is clear, an error (RMR TSSR bit 12) occurs, but the transfer is still executed and completed. The TSSR is not affected (except for SSR bit 07, which gets cleared). To use the tape transport again, the CPU must initialize the transport (that is, write the TSSR).

# 3.1.2.3 Data Wraparound Using DATOB (even)

When TSDB is loaded by a DATOB to TSDB low byte (even address), the following happens. Bits <15:00> of the register are loaded with bits <15:00>, respectively, from the Unibus. (Most PDP-11 CPUs assert all zeroes for bits <15:08> except for a MOVB; this sign extends bit 07. See the respective processor handbook for a MOVB instruction.) Bits 16 and 17 cannot be determined. The TSDB is then loaded into the TSBA. To use the tape transport again, the CPU must initialize the transport (that is, write the TSSR).

### 3.1.3 Status Register (TSSR)

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

SC UPE SPE RMR NXM NBA A17 A16 SSR OFL SIP 0 TC2 TC1 TC0 X

Read/Write

See Table 3-1 for definition of Termination Class (TC) Codes.

The TSSR is a 16-bit read/write register at base address 17XXXX+2. It can be read at any time with or without the transport unit connected. It can only be updated by the transport logic; it cannot be modified from the Unibus except indirectly. (SPE, UPE, RMR, NXM, and SSR bits are cleared when the TSDB is written by the host CPU.)

Any write function to the TSSR is decoded as a subsystem initialize. This resets the transport and coupler no matter what state they are in and causes an automatic load sequence returning the tape to BOT if the transport is on-line.

TSSR register bits 14 through 11 and 7 are cleared only on system power up, transport power up, subsystem initialize, or at the beginning of any write command to the TSDB register. Bits 15 and 07 are under control of the transport. These may be set or cleared independently of any transport operation. Bits 10 and <06:00> are controlled by the transport and reflect the subsystem status as indicated.

The TSSR register utilizes several bits to increase its status reporting capabilities. TSSR bits <03:01> report seven termination class status codes.

On fatal errors (termination class bits equal seven), if the need buffer address is not set (NBA=0), then the message may be valid. If the need buffer address is set (NBA=1), then there was no message.

The RMR bit will not affect the error class codes because RMR may occur on a bug free system. However, RMR wil set the special condition (SC). (You may have tried to perform the next command while the transport was outputting the ATTN MSG.) If RMR is seen in the TSSR, the CPU must have written the TSDB while the command was executing.

The TSSR may not reflect the current state of the hardware if ATTNS are not enabled and the message buffer is not released. (That is, the transport may be off-line while the TSSR shows on-line). To keep the TSSR up to date would violate message packet protocol.

TSSR is not cleared immediately after initialization. The microprocessor runs to complete an automatic load sequence. When tape is at BOT, TSSR updates.

#### Special Condition (SC) - Bit 15

When set, this bit indicates that the last command was not completed without incident. Specifically, either an error was detected or an exception condition occurred. An exception condition coud be a tape mark on read commands, reverse condition at BOT, EOT while writing, etc.

# Unibus Parity Error (UPE) - Bit 14

This bit is set by the transport when it detects a parity error in the memory data being transferred from the CPU memory. (Causes TC4 and TC5.)

#### Serial Bus Parity Error (SPE) - Bit 13

This bit is set by the transport when it detects a serial bus parity error on data received from the transport. (Causes TC7.)

# Register Modification Refused (RMR) - Bit 12

This bit is set by the transport when a command pointer is loaded into the TSDB and subsystem ready (SSR) is not set. This bit may be set on a bug free system if ATTN interrupts are enabled.

# Nonexistent Memory (NXM) - Bit ll

This bit is set by the transport when trying to transfer to or from a memory location which does not exist. It may occur when fetching the command packet, fetching or storing data, or storing the message packet. (Causes TC4 and TC5.)

# Need Buffer Address (NBA) - Bit 10

When set, this indicates that the transport needs a mesage buffer address. This bit is cleared during the set characteristics command if the transport gets valid data; it is always set after subsystem initialization.

# Bus Address Bits 17:16 (A17, A16) - Bits <09:08>

Al7 and Al6 (bits 09 and 08) display the values of bits 17 and 16 in the TSBA register.

# Subsystem Ready (SSR) - Bit 07

When set, this bit indicates that the transport is not busy and is ready to accept a new command pointer.

#### Off-Line (OFL) - Bit 06

When set, this bit indicates that the transport is off-line and unavailable for any tape motion commands.

#### Silo Parity Error (SIP) - Bit 05

This bit is set when the coupler detects a parity error on read data from the tape transport. (Causes TC7.)

# Termination Class: TC02, TC01, TC00 - Bits <02:01>

These bits act as an offset value when an error or exception condition occurs on a command. Each of the eight possible values of this field represents a particular class of errors or exceptions. The code provided in this field is defined in Table 3-1. The code is expected to be utilized as an offset into a dispatch table for handling the condition. These bits are valid only when special condition (SC) is set. Refer to special conditions and errors, paragraph 3.3.3 of this manual.

Table 3-1

Termination Class Codes

| TSSR<br>Bits<br><03:01> | TC Code | Description                                                                |

|-------------------------|---------|----------------------------------------------------------------------------|

| 000                     | 0       | Normal termination                                                         |

| 001                     | 1       | Attention condition                                                        |

| 010                     | 2       | Tape status alert                                                          |

| 011                     | 3       | Function reject                                                            |

| 100                     | 4       | Recoverable error (tape position = one record down from start of function) |

| 101                     | 5       | Recoverable error (tape not moved)                                         |

| 110                     | 6       | Unrecoverable error (tape position lost)                                   |

| 111                     | 7       | Fatal (Transport Data<br>Parity) error                                     |

|                         |         |                                                                            |

# 3.1.3.1 Bootstrap Command

The TCl2 has the ability to read the boot record of bootable tapes by use of a special command. This special command does not require that a command packet be constructed.

After power-up or bus INIT, writing the TSSR Register with the value 100001 twice will cause the TC12 to space over the first record on the tape and read the second record into the CPU, starting at location 000000. The mag tape will then stop. By starting the execution of the program at location 000000, the boot record will load the desired program from the tape.

The following bootstrap program is a sample; users may write their own program if preferred.

| Memory<br>Location | Content | Macro<br><u>Instructions</u> |       |              |  |  |  |  |  |  |

|--------------------|---------|------------------------------|-------|--------------|--|--|--|--|--|--|

| 2000               | 5000    | START:                       | CLR   | R0           |  |  |  |  |  |  |

| 2002               | 5300    | 5\$:                         | DEC   | R0           |  |  |  |  |  |  |

| 2004               | 1376    |                              | BNE   | 5\$          |  |  |  |  |  |  |

| 2006               | 12706   |                              | MOV   | #1070,SP     |  |  |  |  |  |  |

| 2010               | 1070    |                              |       |              |  |  |  |  |  |  |

| 2012               | 12701   |                              | MOV   | #172522,R1   |  |  |  |  |  |  |

| 2014               | 172522  |                              |       |              |  |  |  |  |  |  |

| 2016               | 12702   |                              | MOV   | #100001,R2   |  |  |  |  |  |  |

| 2020               | 100001  |                              |       |              |  |  |  |  |  |  |

| 2022               | 10211   |                              | MOV   | R2,(R1)      |  |  |  |  |  |  |

| 2024               | 10211   |                              | MOV   | R2,(R1)      |  |  |  |  |  |  |

| 2026               | 22711   | 10\$:                        | CMP   | #122204,(R1) |  |  |  |  |  |  |

| 2030               | 122204  |                              |       |              |  |  |  |  |  |  |

| 2032               | 01375   |                              | BNE   | 10\$         |  |  |  |  |  |  |

| 2034               | 12704   |                              | MOV   | #MESS+20,R4  |  |  |  |  |  |  |

| 2036               | 2062    |                              |       | ·            |  |  |  |  |  |  |

| 2040               | 05007   |                              | CLR   | PC           |  |  |  |  |  |  |

| 2042               | 46523   | MESS:                        | .WORD | 46523        |  |  |  |  |  |  |

|                    | 00001   |                              | .END  |              |  |  |  |  |  |  |

# 3.1.4 Extended Status Registers

Five additional registers are employed to provide additional status information: Residual Frame Count Register (RBPCR) and Extended Status Registers 0, 1, 2, and 3.

The Extended Status Registers are not read directly from the registers accessible at the Unibus interface. At the end of a command or by issuing a Get Status Command the message packet information is updated. The end message packet which results from the get status contains the extended status words. This means that a message buffer has to be defined to the subsystem before the extended status registers are available to the software.

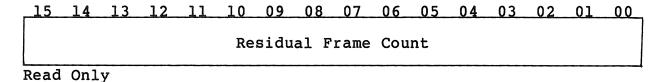

### 3.1.4.1 Residual Frame Count Register (RBPCR)

### Residual Frame Count - Bits <15:00>

This word contains the octal count of residual bytes, records, tape marks for read, space records and skip tape mark commands. The contents are meaningless for all other commands.

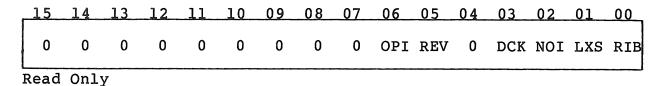

# 3.1.4.2 Extended Status Register Zero (XST0)

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

TKM RLS LET RLL WLE NEF ILC ILA MOT ONL IE VCK PED WLK BOT EOT

Read Only

See Table 3-1 for definition of Termination Class (TC) Codes.

### Tape Mark Detected (TMK) - Bit 15

This bit is set when a tape mark is detected during a read, space, or skip command and as a resut of the write tape mark or write tape mark retry commands. (Causes TC2.)

# Record Length Short (RLS) - Bit 14

This bit indicates one of the following three cases. The record length was shorter than the byte count for a read operation. A space record operation encountered a tape mark or BOT before the position count was exhausted. Or, the third possibility, a skip tape marks command was terminated by encountering BOT or a double tape mark (if skip tape marks command is enabled, see LET) before exhausting the position counter. (Causes TC2.)

# Logical End of Tape (LET) - Bit 13

This is set only on the skip tape marks command under two conditions: when either two contiguous tape marks are detected or when moving off BOT and the first record encountered is a tape mark. The setting of this bit will not occur unless this mode of termination is enabled through use of the set characteristics command. (Causes TC2.)

### Record Length Long (RLL) - Bit 12

When set, this bit indicates that the record read was longer than the byte count specified. (Causes TC2.)

### Write Lock Error (WLE) - Bit 11

When set, a TC3 indicates that a write operation was issued but the mounted tape did not contain a write enable ring. When set, TC6 indicates the WRT LOCK switch was activated during write operation.

# Non-Executable Function (NEF) - Bit 10

When set, this bit indicates that the command could not be executed due to one of the following conditions: The command specified reverse tape direction but the tape was already positioned at BOT. A motion command was issued without the clear volume check (CVC) bit being set while the volume check bit was set. A write command was issued when the tape did not contain a write enable ring [Write Lock Status (WLS)]. (Causes TC3.)

# Illegal Command (ILC) - Bit 09

This bit is set when a command is issued and either its command field or its command mode field contains codes not supported by the transport. (Causes TC3.)

# Illegal Address (ILA) - Bit 08

This bit is set if an address greater than 18 bits in length is loaded into TCDB Register or if that register overflows. (Causes TC3.)

# Capstan is Moving (MOT) - Bit 07

When set, this bit indiactes that the tape was moved during the previous operation. (Causes TC3.)

# On-Line (ONL) - Bit 06

When set, this bit indicates that the transport is on-line and operable. It causes a TCl on ATTN interrupt or a TC3 (non-executable) function if rejected because the transport was off-line.

# Interrupt Enable (IE) - Bit 05

This bit reflects the state of the interrupt enable bit supplied on the last command.

# Volume Check (VCK) - Bit 04

This bit is set when the transport changes state (on-line to off-line and vice versa). It is always set after initialization. (Causes TC3.)

# Phase Encoded Transport (PED) - Bit 03

When set, this bit indicates that the transport is capable of reading and writing only  $1600 \, \text{bit/in}$  phase encoded data. It should always be set.

# Write Locked (WLK) - Bit 02

When set, this bit indicates that the mounted tape reel does not have a write enable ring installed. Therefore the tape is write protected. (Causes TC3 and TC6.)

# Beginning of Tape (BOT) - Bit 01

When set, this bit indicates that the tape is positioned at the load point as denoted by the BOT refective strip on the tape. This causes TC2 if reversed in BOT, and TC3 if at BOT when a reverse command occurs.

### End of Tape (EOT) - Bit 00

This bit is set whenever the tape is positioned at or beyond the EOT reflective strip. It is not reset until the tape passes over the EOT reflective strip in the reverse direction under program control. System initialization always resets this bit (status on read, TC2 on a write). Manually moving EOT mark over the EOT sensor will not set or reset the EOT bit.

# 3.1.4.3 Extended Status Register One (XST1)

| _15_ | 14 | 13 | 12 | 11_ | 10 | 09 | 8 0 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|------|----|----|----|-----|----|----|-----|----|----|----|----|----|----|----|----|

| DLT  |    |    |    |     |    |    |     |    |    |    |    |    |    |    | 1  |

Read Only

See Table 3-1 for Temination Class (TC) code definitions.

# Data Late (DLT) - Bit 15

This bit is set when the I/O silo is full on a read or empty on a write. The conditions occur whenever the Unibus latency exceeds the transport's data transfer rate for a significant number of transfers. (Causes TC4.)

# Correctable Data (COR) - Bit 13

This bit is set if a single track error correction condition is detected during the execution of a read or write command.

# Trash in the Gap (TIG) - Bit 11

This bit is set when non-erased data is detected in a gap during a read, write, write tape mark, or erase command. It is always zero (invalid) unless SW3-8 is ON and a CDC streaming tape transport is in use. (Causes TCl and TC4.)

### Invalid Postamble (IPO) - Bit 05

This bit is set during read or write if any of the first 39 characters of the postamble are not read correctly. It is status on read. It is always zero (invalid) unless SW3-8 is ON and a CDC streaming tape transport is in use. IPO causes TC4 on a write.

#### Uncorrectable Data (UNC) - Bit 01

This bit is set when a parity error occurs without a corresponding dead track indication. This bit is a normal write error for any dead track. It is always zero (invalid) unless SW3-8 is ON and a CDC streaming tape transport is in use. (Causes TC3, TC4 and TC6.)

### Multitrack Error (MTE) Bit - 00

This bit is set if more than one dead track occurs in the preamble or in the data field. (Causes TC4 and TC5.)

# 3.1.4.4 Extended Status Register Two (XST2)

| 15   | 14   | 13 | 12 | 11                                      | 10 | 09 | 0.8 | 07                 | 06 | 05   | 04  | 03   | 02   | 01 | 00                                      |  |

|------|------|----|----|-----------------------------------------|----|----|-----|--------------------|----|------|-----|------|------|----|-----------------------------------------|--|

| ОЪМ  | SIP  | 0  | 0  | 0                                       | 0  | 0  | DTP | Dead Track <07:00> |    |      |     |      |      |    |                                         |  |

| OFM  | SIL  | U  | U  | U                                       | U  | U  | DIP |                    |    | Deau | TIa | CK < | 07:0 | U> | l                                       |  |

| Read | Only | Y  |    | *************************************** |    |    |     |                    |    |      |     |      |      |    | *************************************** |  |

See Table 3-1 for Termination Class (TC) Code definitions.

## Operation in Progress (OPM) - Bit 15

When set, this bit indiactes that the tape was moved during the previous operation.

# Silo Parity Error (SIP) - Bit 14

Set when the transport parity checker detects a parity error on read data from tape transport. (Causes TC7.)

# Dead Track Parity (DTP), Dead Track 7:0 (DT7:0) - Bits <08:00>

These bits indicate which tracks went dead, if any, during the last data transfer operation. They are always zero (invalid) unless SW3-8 is ON and a CDC streaming tape transport is in use.

#### 3.1.4.5 Extended Status Register Three (XST3)

#### Operation Incomplete (OPI) - Bit 06

This bit is set when a read, space, or skip operation has moved 25 feet of tape without detecting any data on the tape. It is also set by a write command when the read head fails to see data transitions after four feet of tape. (Causes TC6.)

### Reverse (REV) - Bit 05

This bit is set when the direction of current tape operation is reverse. For multifunction retry commands, if at least one of the commands is reverse, the bit is set.

### Density Check (DCK) - Bit 03

The current operation will be done. However, note that read, space, and skip operations will complete without error (if no other errors occur) to allow tapes with a bad IDB to be read. On a write command, when a bad IDB is sensed, tape position lost will occur. (Causes TC6.)

NOTE: If you append to a tape with a bad IDB, you will not receive any DCK error until a write.

### Noise Record (NOI) - Bit 02

This bit is set during a space operation when a burst of flux changes, which do not qualify as a record (but too many to ignore), are detected. (Causes TC6.)

# Limit Exceeded Statically (LXS) - Bit 01

This bit is set by tension arms that have actuated their limit switches; it remains set when tension arms are returned to normal position. It can be reset only by loading tape.

# Reverse Into BOT (RIB) - Bit 00

This bit is set when a read, space, skip, or reverse command already in progress encounters the BOT marker when moving tape in the reverse direction. Tape motion will be halted at BOT. (Causes TC2.)

### 3.2 PACKET PROCESSING

The packet protocol scheme allows each TSll emulation (transport) on the transport to provide a large amount of status and error information to the CPU while taking up only two words of Unibus address space. The packet protocol also prevents the transport from updating the error and status information asynchronously, that is, while the CPU is reading the error and status information.

NOTE: This section is not intended to detail all aspects of packet protocol or packet processing. It is intended to illustrate how these concepts are implemented in the transport subsystem.

To allow each transport to take up only two words of address space, we allow the CPU to define a set of locations in memory. These locations (command buffers) are used to tell the transport what operation to perform. The CPU also defines a set of locations (message buffers) in memory where the transport will put the error and status information. The CPU must give both the command buffer address and message buffer address to the transport. The CPU gives the command buffer address to the transport on every command. (The CPU writes the address of the command packet into the TSDB of the transport.) The CPU gives the message buffer address to the transport every time the CPU does a set characteristics command.

To prevent the transport from updating the message buffer while the CPU is reading that buffer, we have defined the concept of ownership. Both the command and message buffers can be owned. Each buffer may be owned by the transport or the CPU, but not by both simultaneously. Ownership of a buffer can only be transferred by the current owner.

There are four different combinations that transfer the ownership of the two buffers:

Command buffer - CPU to transport by the CPU; Command buffer - transport to CPU by the transport; Message buffer - CPU to transport by the CPU and Message buffer - transport to the CPU by the transport.

The CPU transfers ownership of the command buffer to the transport by writing the address of the command packet into the TSDB. This write clears the TSSR subsystem ready (SSR) bit.

The transport transfers ownership of the command buffer to the CPU by setting the acknowledge (ACK) bit in the message buffer. When the transport outputs the message buffer, the transport sets SSR in the TSSR to indicate that the message is in the message buffer. If the message buffer does not contain the ACK bit, the CPU will know that the transport did not see the last command buffer and the CPU still owns the command buffer. The command may be reissued by the CPU.

The CPU transfers ownership of the message buffer to the transport by setting the ACK bit in the command buffer. If the command buffer does not contain the ACK bit, the transport will know that the CPU did not see the last message buffer and the transport still owns the message buffer. The transport outputs the TSSR again (with the SSR bit up) and interrupts (if IE is set) without sending out a message.

The transport transfers ownership of the message buffer to the CPU in one of two ways. The first way is used after the end of a command: the transport sets the SSR bit in the TSSR to indicate that the command is done (and interrupts if IE is set). The second way is used during an attention (ATTN). SSR will already be up because an ATTN only happens when the transport is inactive. transport clears SSR, outputs the message, then sets SSR again and interrupts (if IE set). Note that if the CPU writes the TSDB while the SSR is clear during an ATTN, the register modification refused (RMR) error bit will be set and that command will be ignored. The ATTN message will not have the ACK bit set since the transport does not own the command buffer. Note that RMR may set in this way on a bug free system because the CPU happened to try to perform a command at the same time the transport wanted to perform an ATTN. All other settings of the RMR indicate a software bug. tried to do a command before the previous command was finished.) If the CPU command was lost because the transport was outputting an ATTN message, VOL CHK and INT ENB are not updated. If the CPU command was rejected (illegal command, etc.), VOL CHK and INT ENB are updated to the start of the rejected command.

When the transport is initialized, the TSSR is updated. At this time we define both the command and message buffers as belonging to the CPU. When the CPU wants to do a command (the first one must be a set-characteristics to set up the message buffer address), the CPU writes the address of the command buffer into the TSDB of the transport. This command must have the ACK bit set to give ownership of the message buffer to the transport. At this point, the transport owns both the command and message buffers.

The transport will execute the set characteristics command and send out a message to the message buffer address with the ACK bit set; this indicates that the transport has recognized the command and is finished with the command buffer. The transport will then set SSR and interrupt (if IE is set). At this point, the CPU owns both the message and command buffers again.

As you can see, the ownership of both buffers transfers simultaneously from CPU to transport and then from transport to CPU.

Now consider the case where ATTNs are enabled by the proper characteristics mode word and the transport wants to do an ATTN. An ATTN will only occur when the transport is not active. If the CPU owns both the command and message buffers, the transport must queue up the ATTN and not do anything until the CPU releases the message buffer on the next command. So when the CPU executes the next command (with the ACK bit set), the transport will output the ATTN message with the ACK bit zero; this indicates that the command was lost (except for the transfer of the message buffer ownership to the transport). The transport refuses to accept ownership of the command buffer. The CPU will then still own the command buffer (because the transport did not accept the command) and will also own the message buffer now filled with an ATTN message. If the CPU still wants to do the ignored command, the CPU must reissue the command (with the ACK bit set).

Now consider the case where the CPU wants to be notified of a change in status right away while the transport is inactive for a long period of time. To accomplish this, the transport must own the message buffer for that long period of time. Everything up to now has indicated that the transport gives up the message at the end of every command. The message buffer release command is a special command from the CPU. It tells the transport not to give ownership of the message buffer back to the CPU at the end of the command. The transport does not output a message at the end of the command but just outputs the TSSR (with the SSR bit set) and interrupts (if the proper characteristics mode word is set up). The transport then maintains ownership of the message buffer until an ATTN condition is seen. The transport then immediately clears SSR, outputs the message (with the ACK bit not set since the

transport is not responding to a command), and then sets SSR and interrupts (if IE is set). At that time the system is back to the state of the CPU owning both buffers. Another ATTN will not be done until the CPU does a command with the ACK bit set to release ownership of the message buffer containing the ATTN message.

Suppose the CPU has done a message buffer release command and wants to do another command but has not received an ATTN from the transport (so that the transport still owns the message buffer from the message buffer release command). The CPU can do a command without the ACK bit set in the command buffer. At the time of the command, the CPU does not own the message buffer so the CPU cannot release the message buffer. If the CPU does set the ACK bit, nothing will happen (except the CPU might miss an ATTN if the transport was sending out an ATTN at the same time that the CPU was doing a command).

Message packet protocol may be violated if the transport gets an error (NXM, memory parity, serial bus parity error, or I/O silo parity error) during the reading in of the message packet. When one of these errors occurs, the transport always sends out a failure message (because the packet is not reliable).

The system software should be written so it will not crash if the transport interrupts while the CPU is servicing another TCl2 interrupt. This may happen, but only if the transport should receive a fatal hardware error.

#### 3.2.1 Command Packet/Header Word

| <u> 15</u> | <u> 14</u>  |              | 12          |                 |   |   | <u>08</u> | 07                 |   | 0.5 | 04              |   |   |   | 00 |

|------------|-------------|--------------|-------------|-----------------|---|---|-----------|--------------------|---|-----|-----------------|---|---|---|----|

| CTL        |             | vice<br>ende |             | Command<br>Mode |   |   |           | Packet<br>Format l |   |     | Command<br>Code |   |   |   |    |

| ACK        | C<br>V<br>C | O<br>P<br>P  | S<br>W<br>B | 0               | 0 | М | М         | I<br>E             | 0 | 0   | 0               | С | С | С | С  |

The command packet header word is illustrated above and defined in paragraphs below. The command code and mode field definitions are given in Table 3-2.

## Acknowledge - Bit 15

This bit is set when a command is issued and the CPU owns the message buffer. It informs the transport that the message buffer is now available for any pending or subsequent message packets. This passes ownership fo the message buffer to the transport.

## Device Dependent Bits/Field - Bits <14:12>

The following shows how these three bits are implemented:

| Bit      | Name              | Definitions                                                                                    |

|----------|-------------------|------------------------------------------------------------------------------------------------|

| 14<br>13 | CVC<br>OPP<br>SWB | Clear volume check Opposite (reverse the execution sequence of the reread commands) Swap bytes |

|          |                   |                                                                                                |

## Command Mode Field - Bits <11:08>

This bit acts as an extension to the command code and mode field and allows specification of extended device commands (seek, rewind, erase, write tape mark, etc.). Command code and mode field are detailed in Table 3-2.

#### Packet Format #1 Field - Bits <07:05>

The following two values are defined in this field.

| Bit Values | Definition |                                       |

|------------|------------|---------------------------------------|

| 000<br>100 |            | interrupt disable<br>interrupt enable |

#### Command Code Field - Bits <04:00>

Refer to Table 3-2 for definition of the three LS bits of the code.

Bits 03 and 04 of the command code field determine the format and length of command packets. The command packet formats and lengths are as follows.

| Code<br>Bits | Definition                                              |

|--------------|---------------------------------------------------------|