# **UD33 DISK CONTROLLER TECHNICAL MANUAL** (MSCP COMPATIBLE)

3545 Harbor Boulevard Costa Mesa, California 92626 (714) 662-5600

FAX: (714) 241-0792 TLX: 183627

## EMULEX PRODUCT/MANUAL REVISION HISTORY

## PROM E93x1, Location U59

| PROM E93x<br>REVISION | DESCRIPTION                                 | MANUAL P/N   |

|-----------------------|---------------------------------------------|--------------|

| A,B,C                 | UD33 with optional diagnostics              | UD3351001-00 |

| D                     | UD33 with firmware-<br>resident diagnostics | UD3351002-00 |

This manual has been extensively revised to incorporate changes to support the Firmware-Resident Diagnostics (F.R.D.) that have been added to the Revision E controller firmware PROM. Due to the nature of these firmware changes, a UD33 with a Revision D and above firmware PROM will no longer operate with previously supplied diagnostic software. In addition, some of the ODT functions (NOVRAM loading commands and Format Drive command) previously available are no longer available.

All of the functionality that was provided by software diagnostics and ODT commands has been incorporated in F.R.D. Be certain that your manual revision is appropriate for the revision level of your controller firmware, as noted in the table above. This firmware is easily identified by the label on integrated circuit U59 on the UD33.

### **WARNING**

This equipment generates, uses and can radiate radio frequency energy, and if not installed and used in accordance with the technical manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of Federal Communications Commission (FCC) Rules, which are designed to provide reasonable protection against such interference when operating in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Copyright (c) 1988, 1990 Emulex Corporation

The information in this manual is for information purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in the manual.

Printed in U.S.A.

<sup>1</sup> The small x indicates the PROM's revision level letter: A, B, C, etc.

| Section | Title                                | Page       |

|---------|--------------------------------------|------------|

| ONE     | GENERAL DESCRIPTION                  |            |

| 1.1     | INTRODUCTION                         | 1-1        |

| 1.2     | SUBSYSTEM OVERVIEW                   | 1-2        |

| 1.2.1   | Mass Storage Control Protocol (MSCP) | 1-2        |

| 1.3     | PHYSICAL ORGANIZATION OVERVIEW       | 1-3        |

| 1.4     | SUBSYSTEM COMPONENTS                 | 1-4        |

| 1.4.1   | Subsystem Options                    | 1-5        |

| 1.5     | FEATURES                             | 1-5        |

| 1.5.1   |                                      | 1-5        |

| 1.5.2   | Microprocessor Design                | 1-5        |

| 1.5.3   | Firmware-resident Diagnostics        | 1-6        |

| 1.5.4   |                                      | 1-6        |

| 1.5.5   | Self-test                            | 1-6        |

| 1.5.6   | Error Control                        | 1-6        |

|         | Host-initiated Bad Block Replacement | 1-0<br>1-7 |

| 1.5.7   | Seek Optimization                    | 1-7<br>1-7 |

| 1.5.8   | Command Buffer                       |            |

| 1.5.9   | Adaptive DMA                         | 1-7        |

| 1.5.10  | Rotational Position Sensing (RPS)    | 1-7        |

| 1.6     | COMPATIBILITY                        | 1-8        |

| 1.6.1   | Operating Systems                    | 1-8        |

| 1.6.2   | Hardware                             | 1-8        |

| TWO     | CONTROLLER SPECIFICATION             |            |

| 2.1     | OVERVIEW                             | 2-1        |

| 2.2     | GENERAL SPECIFICATION                | 2-1        |

| 2.3     | ENVIRONMENTAL SPECIFICATION          | 2-3        |

| 2.4     | PHYSICAL SPECIFICATION               | 2-3        |

| 2.5     | ELECTRICAL SPECIFICATION             | 2-4        |

| THREE   | PLANNING THE INSTALLATION            |            |

| 3.1     | OVERVIEW                             | 3-1        |

| 3.2     | MSCP SUBSYSTEM CONFIGURATION         | 3-1        |

| 3.2.1   | Architecture                         | 3-1        |

| 3.2.2   | Peripheral Numbering                 | 3-2        |

| 3.2.3   | Paripharal Canacities                | 3-2        |

| 3.3     | Peripheral Capacities                | 3-2        |

| 3.4     | THE UD33 MSCP-CLASS SUBSYSTEM        | 3-3        |

| 3.4.1   |                                      | 3-4        |

| J.4.1   | Logical Unit Numbers                 | J-4        |

| Section | Title                                           | Page         |

|---------|-------------------------------------------------|--------------|

| 3.4.2   | UD33 MSCP-Class Subsystem Logical Configuration | 3-5          |

| 3.4.2.1 | Logical Devices                                 | 3-5          |

| 3.4.2.2 | Device Numbers                                  | 3-7          |

| 3.5     | OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES  | 3-8          |

| 3.5.1   | RSTS/E Operating Systems (v8.0 and above)       | 3-10         |

| 3.5.1.1 | Adding MSCP Support                             | 3-10         |

| 3.5.2   | RT-11 Operating Systems (v5.1 and above)        | 3-10         |

| 3.5.2.1 | Installing a Single MSCP Controller             | 3-11         |

| 3.5.2.2 | Installing Multiple MSCP Controllers            | 3-11         |

| 3.5.2.3 | Disk Partitioning                               | 3-12         |

| 3.5.3   | RSX-11M Operating Systems (v4.0 and above)      | 3-14         |

| 3.5.3.1 | Installing a Single MSCP Controller             | 3-14         |

| 3.5.3.2 | Installing Multiple MSCP Controllers            | 3-14         |

| 3.5.4   | RSX-11M-PLUS Operating Systems (v2.1 and above) | 3-17         |

| 3.5.4.1 | Installing a Single MSCP Controller             | 3-17         |

| 3.5.4.2 | Installing Multiple MSCP Controllers            | 3-17         |

| 3.5.5   | VMS Operating Systems (v3.2 and above)          | 3-20         |

| 3.5.6   | Ultrix-11 Operating Systems (V3.0 and above)    | 3-23         |

| 3.5.6.1 | Sysgen                                          | 3-23         |

| 3.5.6.2 | Special Files                                   | 3-24         |

| 3.5.6.3 | Newfs                                           | 3-25         |

| 3.5.6.4 | Volcopy                                         | 3-26         |

| 3.5.6.5 | Copying a Bootstrap                             | 3-26         |

| 3.5.7   | Ultrix-32m Operating Systems                    | 3-26         |

| 3.5.7.1 | The Kernel                                      | 3-26         |

| 3.5.7.2 | Special Files                                   | 3-27         |

| 3.5.7.3 | Autoconfigure                                   | 3-27         |

| 3.5.7.4 | Disk Partitions                                 | 3-28         |

| 3.5.7.5 | Disk Partition Modifications                    | 3-28         |

| 3.5.7.6 | Default Partition Modifications                 | 3-28         |

| 3.5.7.7 | Newfs                                           | 3-29         |

| 3.5.7.8 | Suggestions/Warnings                            | 3-29         |

| FOUR    | INSTALLATION                                    |              |

| 4.1     | OVERVIEW                                        | 4-1          |

| 4.1.1   | Subsystem Configurations                        | $\bar{4}$ -1 |

| 4.1.2   | Dip Switch Types                                | 4-3          |

| 4.1.3   | Maintaining FCC Class A Compliance              | 4-3          |

| 4.2     | INSPECTION                                      | 4-4          |

| 4.2.1   | UD33 Disk Controller Inspection                 | 4-4          |

| 4.3     | DISK CONTROLLER SETUP                           | 4-4          |

| 4.3.1   | Disk Controller Bus Address                     | 4-7          |

| 4.3.2   | Interrupt Vector Address                        | 4-8          |

|         | 1                                               |              |

| Section   | Title                                                | Page |

|-----------|------------------------------------------------------|------|

| 4.3.3     | Options                                              | 4-8  |

| 4.3.3.1   | MSCP Device Number                                   | 4-8  |

| 4.3.3.1.1 | First Logical Unit Number for an Alternate UD33      | 4-8  |

| 4.3.3.2   | DMA Burst Delay                                      | 4-9  |

| 4.3.3.3   | Adaptive DMA Mode                                    | 4-9  |

| 4.3.3.4   | index and Sector                                     | 4-10 |

| 4.4       | PHYSICAL INSTALLATION                                | 4-10 |

| 4.4.1     | System Preparation                                   | 4-10 |

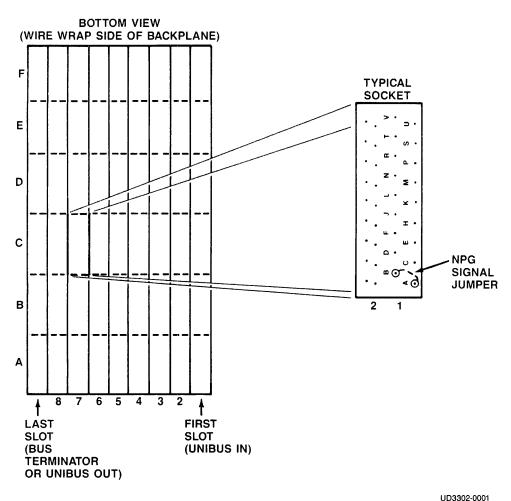

| 4.4.2     | Slot Selection                                       | 4-10 |

| 4.4.3     | NPG Signal Jumper                                    | 4-11 |

| 4.4.4     | Mounting                                             | 4-13 |

| 4.5       | SMD DISK DRIVE PREPARATION                           | 4-13 |

| 4.5.1     | Drive Placement                                      | 4-13 |

| 4.5.2     | Local/Remote                                         | 4-13 |

| 4.5.3     | Sectoring                                            | 4-13 |

| 4.5.4     | Drive Numbering                                      | 4-14 |

| 4.5.5     | Index and Sector Signals                             | 4-14 |

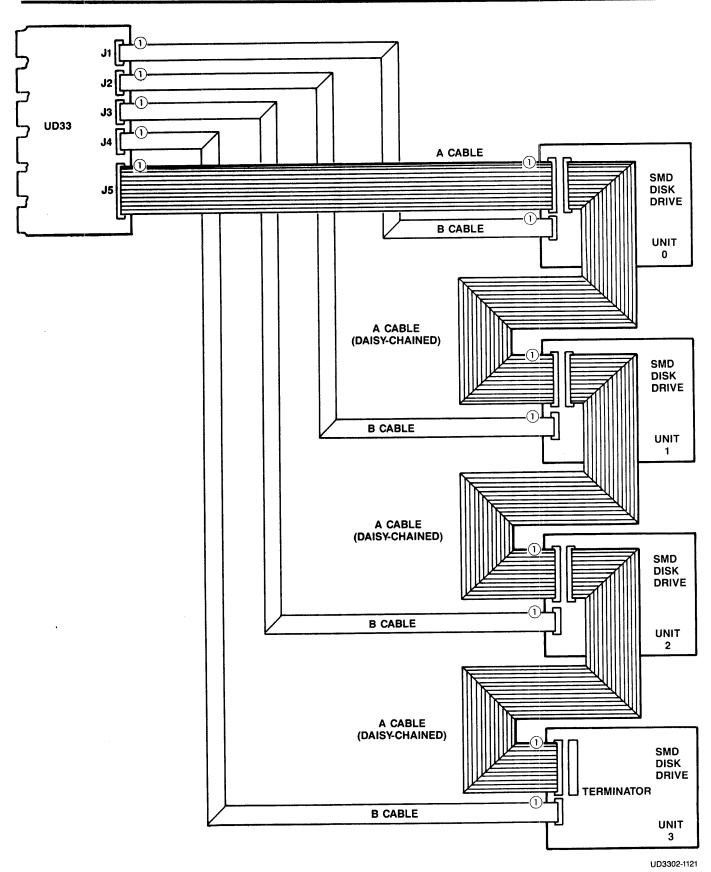

| 4.6       | CABLING                                              | 4-14 |

| 4.7       | NOVRAM LOADING, DISK FORMATTING, AND TESTING         | 4-27 |

| 4.7.1     | F.R.D. Conventions                                   | 4-28 |

| 4.7.2     | Starting F.K.D. on a VAX                             | 4-29 |

| 4.7.3     | Starting F.R.D. on a PDP-11 System                   | 4-36 |

| 4.7.4     | Terminating F.K.D                                    | 4-36 |

| 4.8       | F.R.D. OPTIONS                                       | 4-37 |

| 4.8.1     | Option 1 - Self-test Loop                            | 4-38 |

| 4.8.2     | Option 2 - Format                                    | 4-38 |

| 4.8.3     | Option 3 - Verify                                    | 4-38 |

| 4.8.4     | Option 4 - Format and Verify                         | 4-39 |

| 4.8.5     | Option 5 - Data Reliability Test                     | 4-39 |

| 4.8.6     | Option 6 - Format, Verify, and Data Reliability Test | 4-39 |

| 4.8.7     | Option 7 - Read Only Test                            | 4-40 |

| 4.8.8     | Option 8 - List Known Units                          | 4-40 |

| 4.8.9     | Option 9 - Replace Block                             | 4-41 |

| 4.8.10    | Option 10- Display NOVRAM                            | 4-41 |

| 4.8.11    | Option 11- Edit/Load NOVRAM                          | 4-41 |

| 4.9       | DRIVE CONFIGURATION PARAMETERS                       | 4-42 |

| 4.9.1     | Adaptive DMA Threshold                               | 4-42 |

| 4.9.2     | Type Code                                            | 4-42 |

| 4.9.3     | Number of Units of this Type                         | 4-42 |

| 4.9.4     | Number of Sectors per Track                          | 4-42 |

| 4.9.5     | Number of Heads                                      | 4-43 |

| 4.9.6     | Number of Cylinders                                  | 4-43 |

| 4.9.7     | Number of Spare Sectors per Track                    | 4-43 |

| 4.9.8     | Number of Alternate Cylinders                        | 4-43 |

| 4.9.9     | Configuration Bits, High Limit and Low Limit         | 4-43 |

| Section    | Title                                          | Page |

|------------|------------------------------------------------|------|

| 4.9.10     | Dual Port Options                              | 4-45 |

| 4.9.10.1   | Single Port Mode (Config type 0)               | 4-45 |

| 4.9.10.2   | Dynamic Dual Port Mode (config type 1)         | 4-46 |

| 4.9.10.3   | Static Dual Port Mode (config type 3)          | 4-46 |

| 4.9.10.3.1 | Failover Requirements                          | 4-46 |

| 4.9.10.4   | Firmware Resident Diagnostics (F.R.D.) Support | 4-46 |

| 4.9.10.5   | Logical Drive Splits                           | 4-46 |

| 4.9.11     | Split Code                                     | 4-47 |

| 4.9.12     | Starting Head Offset                           | 4-47 |

| 4.9.13     | Cylinder Offset                                | 4-47 |

| 4.9.14     | Removable Media                                | 4-48 |

| 4.9.15     | Gap 0, 1, and 2 Parameters                     | 4-48 |

| 4.9.16     | Spiral Offset                                  | 4-48 |

| 4.10       | OPERATION                                      | 4-49 |

| 4.10.1     | Indicators                                     | 4-49 |

| FIVE       | TROUBLESHOOTING                                |      |

| 5.1        | OVERVIEW                                       | 5-1  |

| 5.2        | SERVICE                                        | 5-1  |

| 5.3        | FAULT ISOLATION PROCEDURE                      | 5-2  |

| 5.4        | POWER-UP SELF-DIAGNOSTIC                       | 5-4  |

| 5.5        | FATAL ERROR CODES                              | 5-5  |

| SIX        | REGISTERS AND PROGRAMMING                      |      |

| 6.1        | OVERVIEW                                       | 6-1  |

| 6.2        | OVERVIEW OF MSCP SUBSYSTEM                     | 6-1  |

| 6.3        | PROGRAMMING                                    | 6-2  |

| 6.3.1      | Command Support                                | 6-2  |

| 6.3.1.1    | Minimal Disk Subset                            | 6-2  |

| 6.3.1.2    | Diagnostic and Utility Protocol (DUP)          | 6-2  |

| 6.4        | REGISTERS                                      | 6-3  |

| 6.5        | BOOTSTRAP COMMAND                              | 6-5  |

| Section                                                                                                | Title                                                                                                                                                                                      | Page                                                        |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| SEVEN                                                                                                  | FUNCTIONAL DESCRIPTION                                                                                                                                                                     |                                                             |

| 7.1<br>7.2                                                                                             | OVERVIEW                                                                                                                                                                                   | 7-1<br>7-1                                                  |

| EIGHT                                                                                                  | INTERFACES                                                                                                                                                                                 |                                                             |

| 8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.4.1<br>8.3.4.2 | OVERVIEW UNIBUS INTERFACE Interrupt Priority Level Register Address NPR Operations UD33 SMD DISK DRIVE INTERFACE I/O Cables A Cable I/O Signal Processing Tag/Bus Signals Discrete Signals | 8-1<br>8-3<br>8-3<br>8-3<br>8-4<br>8-4<br>8-4<br>8-6<br>8-6 |

| APPENDI                                                                                                | CES                                                                                                                                                                                        |                                                             |

| A                                                                                                      | AUTOCONFIGURE, CSR, AND VECTOR ADDRESSES                                                                                                                                                   |                                                             |

| A.1<br>A.2<br>A.3<br>A.4                                                                               | OVERVIEW  DETERMINING THE CSR ADDRESS FOR USE WITH AUTOCONFIGURE  DETERMINING THE VECTOR ADDRESS FOR USE WITH  A SYSTEM CONFIGURATION EXAMPLE                                              | A-1<br>A-1<br>Λ-3<br>A-6                                    |

| В                                                                                                      | PROM REMOVAL AND REPLACEMENT                                                                                                                                                               |                                                             |

| B.1<br>B.2                                                                                             | OVERVIEW EXCHANGING PROMS                                                                                                                                                                  | B-1<br>B-1                                                  |

| С                                                                                                      | DISK DRIVE CONFIGURATION PARAMETERS                                                                                                                                                        |                                                             |

| C.1<br>C.2                                                                                             | OVERVIEWPARAMETER VALUES                                                                                                                                                                   | C-1<br>C-1                                                  |

| D                                                                                                      | SPECIAL CONSIDERATIONS FOR LARGE CAPACITY DRIVES                                                                                                                                           |                                                             |

| D.1                                                                                                    | SPECIAL CONSIDERATIONS FOR LARGE CAPACITY DRIVES                                                                                                                                           | D-1                                                         |

## LIST OF FIGURES

| 1-1          | O D D D D G D D D D D D D D D D D D D D             | -3         |

|--------------|-----------------------------------------------------|------------|

| 1-2          | UD33 Disk Controller                                | -4         |

| 2-1          | UD33 Disk Controller Dimensions                     | -4         |

| 3-1          | DEC MSCP Subsystem Configuration                    | -3         |

| 3-2          | UD33 Subsystem Configuration 3-                     | -4         |

| 3-3          | Sample SHOW CONFIGURATION                           | 21         |

| 3-4          | CONFIGURE Command Listing                           | 22         |

| 4-1          |                                                     | -2         |

| 4-2          |                                                     | -3         |

| 4-3          |                                                     | <b>-</b> 5 |

| 4-4          | NPG Jumper Location                                 |            |

| 4 <b>-</b> 5 | Drive Cabling                                       |            |

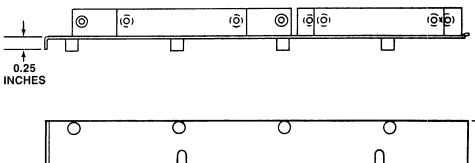

| 4-6          | Cable I/O Adapter Panel 4-2                         |            |

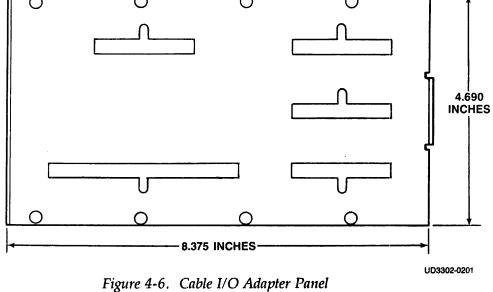

| 4-0<br>4-7   | Rack-Mount Panel.                                   |            |

| 4-7<br>4-8   |                                                     |            |

| 4-0<br>4-9   |                                                     |            |

| 4-9<br>5-1   |                                                     | 40<br>-3   |

| 7-1          |                                                     | -0<br>-2   |

| / <b>-</b> 1 | UD33 Block Diagram                                  | -∠         |

|              | LIST OF TABLES                                      |            |

|              |                                                     | _          |

| 1-1          |                                                     | -3         |

| 1-2          |                                                     | -4         |

| 2-1          |                                                     | -1         |

| 2-2          |                                                     | -3         |

| 2-3          | J - $1$                                             | -3         |

| 2-4          |                                                     | -4         |

| 3-1          |                                                     | -7         |

| 3-2          | Device Names                                        | -9         |

| 4-1          |                                                     | -6         |

| 4-2          |                                                     | -7         |

| 4-3          |                                                     | -7         |

| 4-4          | MSCP Device Number for the First Drive on a UD33 at |            |

|              | an Alternate Address 4                              | -9         |

| 4-5          | Unshielded Cables                                   | 16         |

| 4-6          | Shielded Cables and Cable I/O Adapter Panels        | 20         |

| 4-7          | VAX Initialization Command Sequences4-3             | 30         |

| 4-8          | VAX and UBA Memory Map Register Addresses           | 31         |

| 4-9          | VAX and UBA I/O Base Addresses 4-3                  | 33         |

| 4-10         | UD33 Base Address Offsets (IP Register)4-3          | 34         |

| 4-11         | Available F.R.D. Upload Codes                       | 34         |

| 4-12         | PDP-11 Offsets                                      | 36         |

| 5-1          |                                                     | 5-2        |

| 5-2          |                                                     | -4         |

| 5-3          |                                                     | 5-5        |

| 5-4          |                                                     | 5-6        |

| 6-1          |                                                     | 5-4        |

| 8-1          | UNIBUS Interface Pin Assignments                    | 3-2        |

| 8-2          | SMD-E Interface Connections                         | 3-5        |

| 8-3          |                                                     | 3-7        |

| 8-4          | B Cable Signal Functions 8-                         | 11         |

## LIST OF TABLES

| A-1 | SYSGEN Device Table                             | A-2 |

|-----|-------------------------------------------------|-----|

| A-2 | Priority Ranking for Floating Vectors Addresses | A-4 |

| A-3 | CSR and Vector Address Example                  | A-6 |

| A-4 | Floating Address Computation                    | Λ-7 |

| C-1 | Drive Configuration Parameter Values            | C-1 |

### **EMULEX PRODUCT WARRANTY**

CONTROLLER WARRANTY: Emulex warrants for a period of twelve (12) months from the date of shipment that each Emulex controller product supplied shall be free from defects in material and workmanship.

CABLE WARRANTY: All Emulex provided cables are warranted for ninety (90) days of shipment.

The above warranties shall not apply to expendable components such as fuses, bulbs, and the like, nor to connectors, adaptors, and other items not a part of the basic product. Emulex shall have no obligation to make repairs or to cause replacement required through normal wear and tear or necessitated in whole or in part by catastrophe, fault or negligence of the user, improper or unauthorized use of the product, or use of the product is such a manner for which it was not designed, or by causes external to the product, such as but not limited to, power failure or air conditioning. Emulex's sole obligation hereunder shall be to repair or replace any defective product, and, unless otherwise stated, pay return transportation cost for such replacement.

Purchaser shall provide labor for removal of the defective product, shipping charges for return to Emulex and installation of its replacement. THE EXPRESSED WARRANTIES SET FORTH IN THIS AGREEMENT ARE IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING WITHOUT LIMITATION, ANY WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, AND ALL OTHER WARRANTIES ARE HEREBY DISCLAIMED AND EXCLUDED BY EMULEX. THE STATED EXPRESS WARRANTIES ARE IN LIEU OF ALL OBLIGATIONS OR LIABILITIES ON THE PART OF EMULEX FOR DAMAGES, INCLUDING BUT NOT LIMITED TO SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES ARISING OUT OF, OR IN CONNECTION WITH THE USE OR PERFORMANCE OF THE PRODUCT.

RETURNED MATERIAL: Warranty claims must be received by Emulex within the applicable warranty period. A replaced product, or part thereof, shall become the property of Emulex and shall be returned to Emulex at Purchaser's expense. All returned material must be accompanied by a RETURN MATERIALS AUTHORIZATION (RMA) number assigned by Emulex.

### 1.1 Introduction

The UD33 Disk Controller, designed and manufactured by Emulex Corporation, is an MSCP-compatible controller that interfaces SMD disk drives with DEC's UNIBUS. This manual is designed to help you install and use your UD33 Disk Controller. It assumes that you have some knowledge of hardware configuration, UNIBUS architecture and terminology, and interpretations of error messages and device register contents. The contents of the eight sections and four appendices are described as follows:

- **Section 1 (General Description):** This section contains an overview of the UD33 Disk Controller.

- Section 2 (Controller Specification): This section contains the specification for the UD33 Disk Controller.

- Section 3 (Planning the Installation): This section contains the information necessary to plan your installation, including MSCP subsystem and operating system considerations.

- Section 4 (Installation): This section contains the information needed to set up and physically install the controller, including switch settings and cabling. It also describes the firmware-resident diagnostics and contains instructions for loading drive configuration parameters into the NOVRAM.

- Section 5 (Troubleshooting): This section describes fault isolation procedures that can be used to pinpoint trouble spots.

- Section 6 (Registers and Programming): This section describes the UD33's UNIBUS registers and presents an overview of the Mass Storage Control Protocol (MSCP).

- **Section 7 (Functional Description):** This section describes the controller architecture.

- Section 8 (Interfaces): This section describes the controller, UNIBUS and SMD interfaces.

- Appendix A (Autoconfigure): This appendix describes the DEC algorithm for the assignment of CSR addresses and vector addresses.

- Appendix B (PROM Removal and Replacement): This appendix contains instructions to remove and replace the firmware so that the user can upgrade the UD33 Disk Controller in the field.

- Appendix C (Disk Drive Configuration Parameters): This appendix contains configuration parameters for supported SMD disk drives.

- Appendix D (Special Considerations for Large Capacity Drives): This

appendix contains information specifically concerning large capacity disk

drives.

# 1.2 Subsystem Overview

The UD33 Disk Controller connects high-capacity mass storage peripherals to the UNIBUS in computers manufactured by Digital Equipment Corporation (DEC). The UD33 implements DEC's Mass Storage Control Protocol (MSCP) to provide a software-transparent interface for the host DEC computer. To provide traditional Emulex flexibility in peripheral selection, the UD33 uses the industry standard SMD interface as its peripheral interface. The UD33 supports the extended cylinder addressing functions of the SMD-E (extended) interface. SMD-E and SMD-O interfaces are electrically and logically compatible. For more information on the UD33's SMD interface, see subsection 8.3.

# 1.2.1 Mass Storage Control Protocol (MSCP)

MSCP is a software interface designed to lower the host computer's mass storage overhead by offloading much of the work associated with file management into an intelligent mass storage subsystem. In concert with SMD compatible peripherals, the UD33 provides just such a subsystem. The UD33 relieves the host CPU of many file maintenance tasks. The UD33 Disk Controller performs these MSCP functions: error checking and correction, bad block replacement, seek optimization, command prioritizing and ordering, and data mapping.

This last feature is, perhaps, the most important. This feature allows the host computer's operating system software to store data in logical blocks that are identified by simple logical block numbers (LBNs). Thus, the host does not need to have detailed knowledge of the peripheral's geometry (cylinders, tracks, sectors, etc.). This feature also makes autoconfiguration a simple matter. During system start-up, the host operating system queries the subsystem to find its capacity (the number of logical blocks that the subsystem can store).

1-2

Because the host operating system does not need to have detailed knowledge of its mass storage subsystem, the complexity of the operating system itself has been reduced. This reduction comes about because only one or two software modules are required to allow many different subsystems to be connected to a host.

# 1.3 Physical Organization Overview

The UD33 Disk Controller is a modular, microprocessor-based disk controller that connects directly to the host computer's UNIBUS backplane. The microprocessor architecture ensures excellent reliability and compactness.

The UD33 is contained on a single hex-wide printed circuit board assembly (PCBA) that plugs directly into a UNIBUS backplane slot.

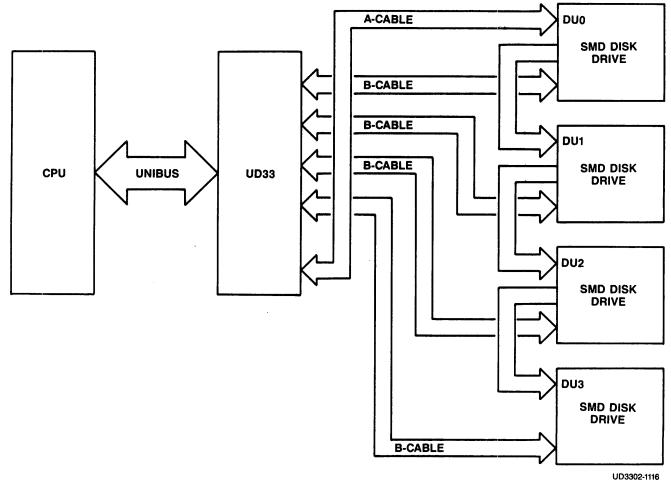

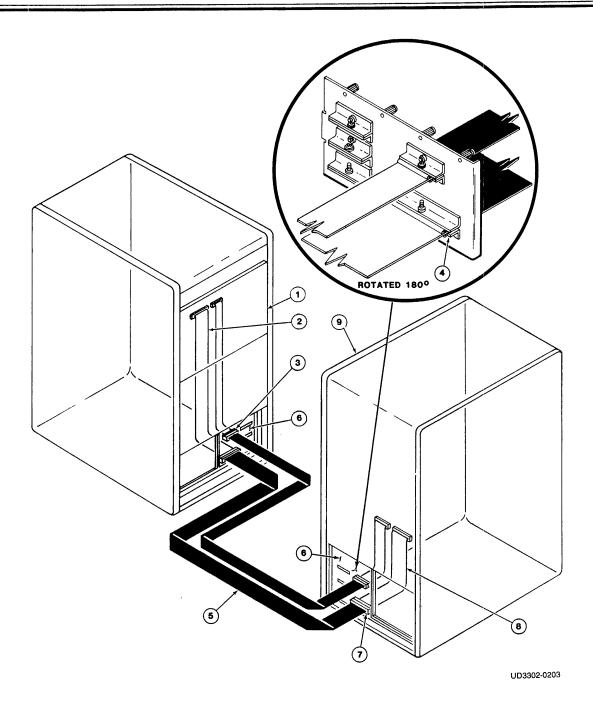

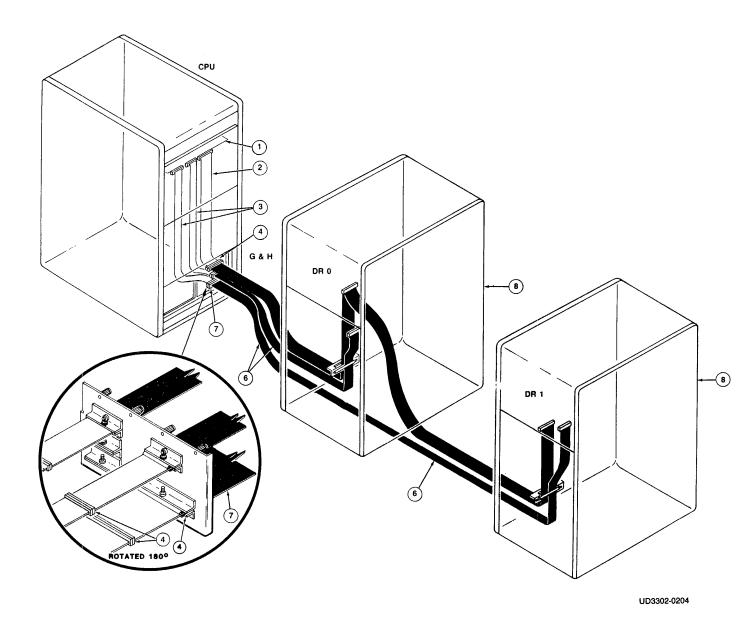

The UD33 supports up to four physical or eight logical disk drives. Aggregate data storage capacities are limited only by the capacities of the peripherals. Figure 1-1 shows one possible SMD configuration.

Figure 1-1. UD33 Subsystem Configuration

# 1.4 Subsystem Components

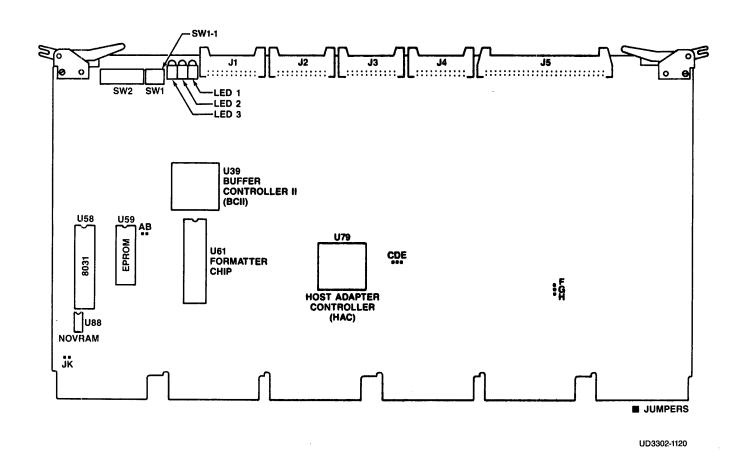

The UD33 Disk Controller, with appropriate peripherals, provides a DEC MSCP-compatible mass storage subsystem. The UD33 is pictured in Figure 1-2. The UD33 is identified by a top level assembly tag that is glued to the 8031 microprocessor chip on the PWB. The UD33 top level assembly number is given in Table 1-1 along with the part numbers of the items that are delivered with the UD33.

Table 1-1. Basic Contents

| Itm | Qty | Description           | Part Number  |

|-----|-----|-----------------------|--------------|

| 1 2 | 1   | UD33 Disk Controller  | UD3310201-02 |

|     | 1   | UD33 Technical Manual | UD3351002-00 |

UD3302-1117

Figure 1-2. UD33 Disk Controller

## 1.4.1 Subsystem Options

Table 1-2 lists the options that can be ordered to tailor your UD33 to your particular application. Cables are required but must be ordered separately.

Table 1-2. UD33 Options

| Option                    | Description                        |  |

|---------------------------|------------------------------------|--|

| SU111120x1                | SMD A-Cable, unshielded            |  |

| SU111120x <sup>1</sup>    | SMD B-Cable, unshielded            |  |

| SU7811212-0n <sup>1</sup> | SMD A-Cable, shielded              |  |

| SU7811219-0n <sup>1</sup> | SMD A-Cable, extension             |  |

| SU7811213-0n <sup>1</sup> | SMD B-Cable, shielded              |  |

| SU7811218-0n <sup>1</sup> | SMD-B Cable, extension             |  |

| SU1110201-00              | Cable I/O Adapter Panel            |  |

| CU2220301-00              | Rack-Mount Panel                   |  |

| SU7813104-00              | Peripheral Cable Adapter Panel Kit |  |

### 1.5 Features

The following features enhance the usefulness of the UD33 Disk Controller.

## 1.5.1 Microprocessor Design

The UD33 design incorporates an eight-bit, high-performance CMOS microprocessor to perform all controller functions. The microprocessor approach provides a reduced component count, high reliability, easy maintainability, and the microprogramming flexibility that allows MSCP to be implemented without expensive, dedicated hardware.

# 1.5.2 Firmware-resident Diagnostics

The UD33 disk controller firmware incorporates a self-contained set of disk preparation and diagnostic utilities. These utilities are contained in UD33 Revision D and above firmware. Controllers with this firmware are easily identified by a label on the PROM in location U59.

These utilities allow the user to communicate directly with the UD33 via a firmware-resident terminal driver that is compatible with either CRT or hardcopy devices connected to a UNIBUS console port. These firmware-resident diagnostics (F.R.D.) provide several important disk preparation functions, including the ability to:

- Configure the controller NOVRAM

- Format the drive

- Test the disk surface and replace defective blocks, and

- Perform reliability testing of the attached disk subsystem.

## 1.5.3 Custom Configuration Capability

An onboard NOVRAM can be programmed for four independent physical drive configurations. Using the firmware-resident utilities, you can control drive parameters, such as gap size and the number of sectors per track.

### 1.5.4 Self-test

The UD33 incorporates an internal self-test routine which exercises all parts of the microprocessor, the onboard memory, the disk formatter chip, the Buffer Controller II (BCII), and the Host Adapter Controller (HAC). Although this test does not completely test all circuitry, successful execution indicates a very high probability that the disk controller is operational. If the UD33 fails the self-test, it leaves three light-emitting diodes (LEDs) ON and sets an error bit in the Status and Address (SA) register (base address plus two).

### 1.5.5 Error Control

The disk controller presents error-free media to the operating system by correcting soft errors and retrying operations without intervention by the host.

## 1.5.6 Host-initiated Bad Block Replacement

The UD33 uses DEC-compatible, host-initiated bad block replacement to dynamically replace any defective blocks that occur during the life of the system. For maximum reliability, the UD33 reports even corrected single bit errors as candidates for replacement.

### 1.5.7 Seek Optimization

The UD33 is able to pool the various seeks that need to be performed and determine the most efficient order in which to do them. This is an especially important feature in heavily loaded systems. The disk controller's ability to arrange seeks in the optimal order saves a great deal of time and makes the entire system more efficient.

### 1.5.8 Command Buffer

The UD33 contains a buffer that is able to store 13 MSCP commands. This large buffer allows the subsystem to achieve a higher throughput and to operate at a very efficient level.

### 1.5.9 Adaptive DMA

During each DMA data transfer burst, the UD33 monitors the UNIBUS for other pending DMA requests and suspends its own DMA activity to permit other DMA transfers to occur. The host processor programs the DMA burst length during the MSCP initialization sequence or the UD33 defaults to 16 words per burst. In addition, the UD33 firmware design includes a switch-selectable DMA burst delay to avoid data-late conditions on other slower devices that may be on a given system. Because of these adaptive DMA techniques, the UD33 ensures that CPU functions, including interrupt servicing, are not locked out for excessive periods of time by high-speed disk transfers.

## 1.5.10 Rotational Position Sensing (RPS)

This feature increases the performance of the disk subsystem during data transfer when two or more drives are active. RPS allows the controller to determine which drive is closest to the sector involved in the data transfer. By not waiting for a particular drive to find the sector necessary to begin the operation, the controller increases the overall throughput to the subsystem.

RPS is programmable via the F.R.D. The performance gain is seen only when two or more drives are used simultaneously. Single-drive subsystems should have RPS disabled.

## 1.6 Compatibility

This section describes the operating systems and hardware components that are compatible with the UD33.

## 1.6.1 Operating Systems

The UD33 implements MSCP. Emulex supports its implementation of MSCP beginning with the indicated version of the following DEC operating systems:

| Operating<br>System | Version |

|---------------------|---------|

| VMS                 | 3.2     |

| RSTS/E              | 8.0     |

| RSX-11M             | 4.1     |

| RSX-11M-PLUS        | 2.1     |

| RT-11               | 5.1     |

| Ultrix-11           | 3.0     |

| Ultrix-32m          | 1.1     |

### 1.6.2 Hardware

The UD33 Disk Controller complies with DEC UNIBUS protocol.

The disk drives supported by the UD33 are not media-compatible with comparable DEC MSCP products.

The UD33 Disk Controller supports hard-sectored disk drives that use the SMD interface. The UD33 also supports the extended cylinder addressing functions of the SMD-E interface. Disk transfer rates of up to 3.0M bytes per second are supported. Emulex has certified the following disk drives for full support:

- CDC 9710-80

- CDC 9715-340

- CDC 9715-515

- CDC 9720

- CDC 9771 XMD

- CDC 9772 XMD

- CDC 9772-13 XMD

- CDC 9720 EMD-368

- CDC 9720 EMD-500

- CDC 9720 EMD-850

- Fujitsu M2333

- Fujitsu M2344

- Fujitsu M2351A

- Fujitsu M2361A

- NÉC 2362

- NEC 2363

- Toshiba MK-186FB

- Toshiba MK-286FC

#### 2.1 Overview

This section contains the general, environmental, physical, and electrical specifications for the UD33 Disk Controller.

| Subsection                      | Title                                                                                                      |

|---------------------------------|------------------------------------------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Overview General Specification Environmental Specification Physical Specification Electrical Specification |

#### 2.2 **General Specification**

Table 2-1 contains a general specification for the UD33 Disk Controller.

Table 2-1. UD33 General Specifications

| Parameter                         | Description                                                                                            |                                                                                                                            |

|-----------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| FUNCTION                          | Providing mass data storage to Digital Equipment<br>Corporation (DEC) computers that use the<br>UNIBUS |                                                                                                                            |

| Logical CPU Interface             | Emulates DEC's Mass Storage Control Protocol (MSCP)                                                    |                                                                                                                            |

| Diagnostics                       | Embedded diagnostics                                                                                   |                                                                                                                            |

| Operating System<br>Compatibility | VMS<br>RSTS/E<br>RSX-11M<br>RSX-11M PLUS<br>RT-11<br>Ultrix-11<br>Ultrix-32m                           | V3.2 and above<br>V8.0 and above<br>V4.1 and above<br>V2.1 and above<br>V5.1 and above<br>V3.0 and above<br>V1.1 and above |

(continued on next page)

Table 2-1. UD33 General Specifications (continued)

| Parameter                              | Description                                               |

|----------------------------------------|-----------------------------------------------------------|

| CPU I/O Technique                      | Direct Memory Access (DMA), including adaptive techniques |

| INTERFACE                              |                                                           |

| CPU Interface                          | Standard UNIBUS interface                                 |

| Device Base Address                    |                                                           |

| Standard<br>Alternates                 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$      |

| Vector Address                         | NOVRAM Programmable (normally set to 154)                 |

| Priority Level                         | BR5                                                       |

| Bus Loading                            | 1 dc Load, 2.5 ac Loads                                   |

| Peripheral Interface                   | SMD-E (Extended) up to 24 MHz<br>SMD-O                    |

| Number of Physical<br>Drives Supported | 4                                                         |

| Drive Sectoring                        | Hard Sectored                                             |

| Maximum Cable Lengths                  |                                                           |

| A Cable (daisy-chain)                  | 50 ft. (15 m.) cumulative                                 |

| B Cable (radial)                       | 50 ft. (15 m.)                                            |

| Firmware Diagnostic<br>Access Path     |                                                           |

| VAX                                    | Standard console terminal                                 |

# 2.3 Environmental Specification

Table 2-2 contains the environmental specifications for the UD33 Disk Controller.

Table 2-2. UD33 Environmental Specifications

| Parameter             | Description                                                                                                          |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|

| OPERATING TEMPERATURE | 10°C (50°F) to 40°C (104°F), where maximum temperature is reduced 1.8°C per 1000 meters (1°F per 1000 feet) altitude |

| RELATIVE HUMIDITY     | 10% to 90% with a maximum wet bulb of 28°C (82°F) and a minimum dewpoint of 2°C (3.6°F)                              |

| COOLING               | 6 cubic feet per minute                                                                                              |

| HEAT DISSIPATION      | 82 BTU per hour                                                                                                      |

# 2.4 Physical Specification

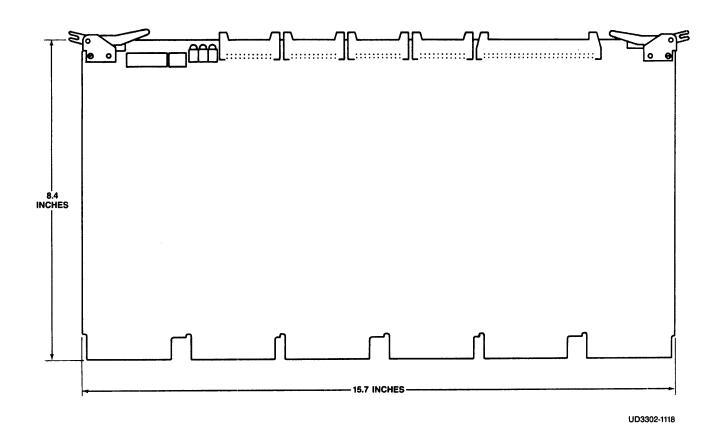

Table 2-3 contains the physical specifications for the UD33 Disk Controller.

Table 2-3. UD33 Physical Specifications

| Parameter       | Description                                                            |

|-----------------|------------------------------------------------------------------------|

| PACKAGING       | Single, hex-wide, four-layer PCBA                                      |

| Dimensions      | 15.7 by 8.40 inches<br>13.172 by 22.09 centimeters<br>(see Figure 2-1) |

| Shipping Weight | 4 pounds                                                               |

#### **Electrical Specification** 2.5

Table 2-4 lists and describes the electrical specification for the UD33 Disk Controller.

Table 2-4. UD33 Electrical Specification

| Parameter | Description                                                                        |

|-----------|------------------------------------------------------------------------------------|

| POWER     | +5 Vdc <u>+</u> 5%, 2.6 amperes (A) MAX<br>-15Vdc <u>+</u> 5%, 1.7 amperes (A) MAX |

Figure 2-1. UD33 Disk Controller Dimensions

### 3.1 Overview

This section is designed to help you plan the installation of your UD33 Disk Controller. Taking a few minutes to plan the configuration of your subsystem before beginning its installation should result in a smoother installation with less system downtime. This section contains UD33 application examples and configuration procedures. The subsections are listed in the following table:

| Subsection                      | Title                                                                                                                             |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Overview MSCP Subsystem Configuration A DEC MSCP Subsystem The UD33 MSCP Subsystem Operating Systems, Device and Vector Addresses |

|                                 |                                                                                                                                   |

## 3.2 MSCP Subsystem Configuration

The following paragraphs describe MSCP Subsystem concepts, including architecture, unit numbering, capacities, and related concepts.

### 3.2.1 Architecture

MSCP is a protocol designed by DEC for mass storage subsystems using Digital Storage Architecture (DSA). In an MSCP mass storage subsystem, DSA comprises three functional and physical layers:

- Host Layer. An MSCP class-driver in the host system receives requests from the operating system and then relays data and commands to the controller in MSCP message packets.

- Controller Layer. The MSCP controller communicates with both the

host layer and the mass storage layer. The controller transmits MSCP

message packets to and from the host MSCP class-driver and performs

data-handling functions for the mass storage devices. The UD33

functions as the controller layer.

Mass Storage Layer. The mass storage peripheral devices communicate with the MSCP controller and send or receive data as specified by the MSCP controller.

MSCP defines the form of the message packets that are exchanged by the host and the MSCP controller. The UD33 implements MSCP in mass storage subsystems using SMD as the peripheral interface.

### 3.2.2 Peripheral Numbering

Each MSCP peripheral on the system is identified to the operating system by an MSCP device name. An MSCP device name consists of a device class identifier and a unit number. The device class is indicated by a two-letter prefix; MSCP disk devices are indicated by the prefix DU.

With the exception of VMS systems, DEC operating systems require that all MSCP peripherals on a system have different MSCP device numbers, even if they are managed by separate MSCP controllers at separate UNIBUS device addresses. For example, under RSX-11M-PLUS, if there are three peripherals on the first MSCP controller (at 772150<sub>8</sub>), then the first peripheral on the second MSCP controller (in floating CSR address space) is numbered DU3.

## 3.2.3 Peripheral Capacities

The capacity of peripherals in an MSCP subsystem is measured in logical blocks. Each logical block contains 512 bytes of data. The MSCP controller can report the capacity of a peripheral to the operating system. For example, a Fujitsu M2361A disk drive supported by the UD33 is able to store 1,122,116 blocks.

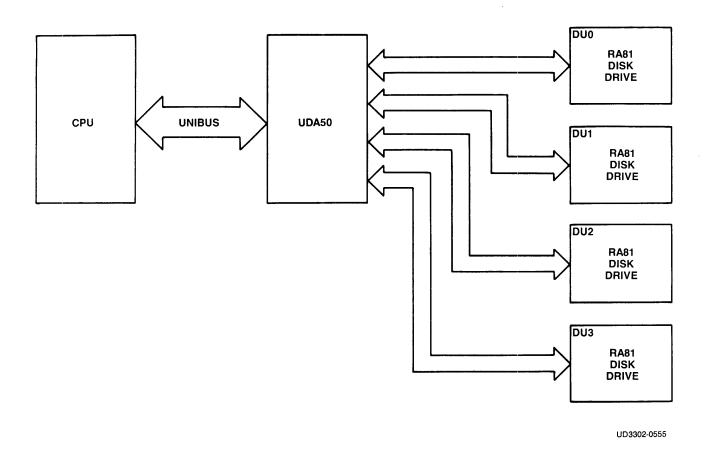

# 3.3 A DEC MSCP Subsystem

Figure 3-1 shows the organization of a typical DEC MSCP subsystem for the UNIBUS. The MSCP host and controller functions are combined in a single piece of hardware, in this example the DEC UDA50. The UDA50 supports RA series hard disk drives. The UDA50 plugs directly into the UNIBUS and is attached to disk drives via a disk-drive-native interface.

Figure 3-1. DEC MSCP Subsystem Logical and Physical Configuration

# 3.4 The UD33 MSCP-Class Subsystem

Figure 3-2 illustrates a typical UD33 MSCP-class subsystem. As with the DEC implementation, the UD33 is connected directly to the UNIBUS; however, the UD33 uses the SMD peripheral interface to communicate with up to four disk drives.

# A-CABLE DUO SMD DISK DRIVE B-CABLE B-CABLE DU1 B-CABLE SMD DISK UNIBUS **UD3**3 CPU DU2 SMD DISK DRIVE DU3 SMD DISK B-CABLE UD3302-1116

repeat 1-1

Figure 3-2. UD33 Subsystem Configuration

The MSCP subsystem provided by the UD33 is essentially analogous to the DEC MSCP subsystem. As in the DEC subsystem, the UD33 MSCP-class controller connects directly to the UNIBUS. As an MSCP-class controller, the UD33 receives requests from the host, optimizes the requests, generates SMD commands to perform the operations, transfers data to and from the host, transfers data to and from the device, and buffers data as necessary. When the command is complete, the controller sends a response to the host.

The UD33 also performs all of the functions of the peripheral controller, including serialization and descrialization of data. The UD33 connects to the peripherals it supports via the SMD interface.

## 3.4.1 Logical Unit Numbers

As noted in subsection 3.2.2, most DEC operating systems do not allow any MSCP disk devices on one system to have the same unit number, even though they may be controlled by separate MSCP controllers at different base addresses.

DEC MSCP-class drives can accept unit identification plugs that define addresses from 0 to 255. Disk drives controlled by the UD33 do not have this flexibility; the UD33 can detect only four unique drive addresses at its SMD interface -- 0, 1, 2, and 3. To prevent a unit-number conflict between the UD33's drives and another MSCP controller's drives, the UD33 employs switches to change the drive logical unit number that is reported to the operating system.

### Example 3-1

An MSCP controller at a standard base address is supporting four disk drives; a UD33 at an alternate base address is supporting three disk drives. An offset of 4 is specified for the first drive on the UD33. This causes the UD33 disk with address 0 to be reported to the operating system as logical unit number (LUN) 4. The UD33 disk 1 is reported as LUN 5, and UD33 disk 2 is reported as LUN 6.

The offset for the logical unit number is specified by using switches SW1-2 through SW1-4 on the UD33.

### 3.4.2 UD33 MSCP-Class Subsystem Logical Configuration

This subsection explains the algorithm used by the UD33 to map logical MSCP-class peripherals onto the physical disk drives provided by the UD33 subsystem.

### 3.4.2.1 Logical Devices

The phrase "logical MSCP disk drive" refers to the disk drive as it appears to the operating system. That is, the operating system associates a disk drive of known type (in this case, an MSCP disk drive) with a unit number and a capacity. The UD33 MSCP-class controller presents that information to the operating system after initialization on command.

Because the MSCP controller is responsible for establishing the relationship between unit number and capacity, it is possible for the controller to divide its physical disk drives into more than one logical unit. For example, if a physical disk drive has a capacity of 1,402,832 blocks, the MSCP controller can divide that capacity into two parts of 701,416 blocks each. (Each part may have a different capacity.) Each part is then assigned a separate unit number, and the unit number and capacity of each part is presented to the operating system.

The operating system then sees the two parts as separate disk drives, even though the data is actually stored on the same physical drive. The two parts are called logical disk drives, and the numbers that identify them are called MSCP unit numbers.

A drive configuration that supports multiple logical units is specified by the data that is stored in the configuration Nonvolatile Random Access Memory (NOVRAM). Information for programming the configuration NOVRAM is given in Section 4, INSTALLATION. The field that causes a drive to be divided into multiple logical units is called the Split Code. There are four types of split codes: no split, cylinder split, head split, and reverse head split:

- When no split is specified, the entire physical drive is one logical drive.

- Cylinder split codes divide a physical drive by cylinders. A Starting Cylinder Offset field in the NOVRAM specifies the first cylinder of the second logical drive. For example, a Fujitsu M2351A, which has 842 cylinders, might be divided so that the first logical unit is assigned cylinders 0 through 420 and the second logical unit assigned cylinders 421 through 841. In this example, the Starting Cylinder Offset has a value of 421.

- Head split codes divide the drive by data heads. A Starting Head Offset field in the NOVRAM specifies the first head of the second logical drive. When the drive is split by data heads, each logical drive has its own platter(s). For example, a CDC 9457 LMD might be divided so that Drive 0 is assigned heads 0 and 1, and Drive 1 is assigned heads 2 and 3. The Starting Head Offset has a value of 2. In this example, the CDC 9457 removable media is assigned logical unit number (LUN) 0 and the fixed media assigned LUN 1.

- Reverse head split codes also divide the drive by data heads, but assign the lower numbered heads to drive 1 and the higher numbered heads to drive 0. If you entered a reverse split code for the previous CDC 9457 example, Drive 0 is assigned heads 2 and 3 and Drive 1 is assigned heads 0 and 1. The Starting Head Offset has a value of 2. One advantage of the reverse head split codes is that you may use a fixed media unit as your system disk without modifications to the operating system.

For minimum effect on access time, Emulex recommends the use of head split vs. cylinder split.

### 3.4.2.2 Device Numbers

The drives supported by the UD33 are assigned MSCP device names by the operating system. As described earlier, an MSCP device name consists of a device class prefix and a device unit number. Drives are assigned MSCP device numbers beginning with zero (0). The conventions for numbering multiple MSCP drives vary by operating system.

Under RSX-11M, RSX-11M-PLUS and RT-11, DU0 is assigned to the first drive on the first MSCP controller, where "first" means the controller located at the standard base address. Unit number 1 would be the second drive on the first controller, etc. If there are two MSCP controllers on the system, the units installed on the second begin numbering at n+1, where n equals the highest unit number of the first MSCP controller.

RSTS/E requires that drives supported by a standard MSCP controller be numbered starting at 0 and drives supported by an alternate MSCP controller be numbered starting at 4.

Because MSCP device names under VMS designate the supporting MSCP controller, the unit numbering is less restricted. For example, two drives which are supported by a standard MSCP controller might be DUA0 and DUA1 and a third drive supported by an alternate MSCP controller might be DUB0.

Table 3-1 is an MSCP unit numbering example under the RSX-11M operating system which shows the MSCP number versus the actual physical addresses assigned to all the components. The physical disk drive (unit number 0) of the second controller is split into two logical units. Note that two device names are associated with that drive.

Table 3-1. Subsystem Configuration Example

| UD33<br>Address      | Device Description           | Drive<br>Unit<br>Number | Device<br>Name |

|----------------------|------------------------------|-------------------------|----------------|

| 772150               | Fujitsu M2361A               | 0                       | DU0            |

|                      | Fujitsu M2361A               | 1                       | DU1            |

| 760334<br>(Floating) | CDC 9772 XMD<br>(head split) | 0                       | DU2<br>DU3     |

|                      | Fujitsu M2351A               | 1                       | DU4            |

### NOTE

All of the MSCP peripherals supported by the UD33 use the same device identifier - RA81. Unique device identifiers are not available to the host.

# 3.5 Operating Systems, Device and Vector Addresses

Before the installation of any peripheral device can be considered complete, the computer's operating system must be made aware of the new resource. The information provided in this section is intended to supplement your DEC operating system resources and to be used as an aid in planning the installation of your UD33. Be aware that not all DEC operating systems support the maximum eight logical drives permitted by the UD33.

An operating system can be made aware of a new resource in three ways:

- The operating system can poll the computer's I/O device address space.

- The device can be manually connected using CONNECT or CONFIGURE statements.

- The user can tell the operating system about a device during an interactive SYSGEN procedure.

The first technique is referred to as autoconfigure, and it is essentially automatic. The second technique requires that CONNECT statements be placed in a special command file that is executed each time the computer is bootstrapped. The third technique, interactive SYSGEN, creates a configuration file that the operating system references when the system is bootstrapped. All techniques accomplish the same result: they associate a specific device type with a bus address and interrupt vector.

Most recent versions of DEC operating systems use autoconfigure to some extent, and try to follow the same rules. The RT-11 operating system does not use autoconfigure, but can locate devices that reside at a standard address. There are some differences among operating systems, however, especially with regard to MSCP controllers at alternate UNIBUS addresses. The following paragraphs address these differences for each supported operating system. This discussion includes information on choosing appropriate UNIBUS device addresses and interrupt vectors for the subsystem. No instructions are provided for programming the chosen address into the UD33. See subsection 4.3 for detailed switch setting information.

MSCP-class controllers contain two registers that are visible to the UNIBUS I/O page. They are the Initialization and Polling (IP) register (base address) and the Status and Address (SA) register (base address plus 2). The terms IP register, CSR address, UNIBUS address and base address all refer to the same register. All of the operating systems described in the following subsections use the standard UNIBUS address of 772150<sub>8</sub> for the first controller on the host system.

Vector addresses for MSCP controllers are not selected by using switches on the controller, but are programmed into the controller during the Initialization process. Many operating systems select the vector address automatically. If an operating system requires manual input of the vector, the procedure notes that fact.

Again, although DEC has attempted to standardize treatment of peripherals by operating systems, some differences do exist. Table 3-2 lists and describes the device names assigned to MSCP devices under different operating systems. Two controller names and two drive names are given to indicate the numbering scheme.

Controller **Drives Supported** Operating System First, Second by First Controller RSTS/E RU0, RU1 DU0, DU1 DU0, DU1 RSX-11M DUA, DUB DU0, DU1 RSX-11M-PLUS RT-11 Port0, Port1 DU0, DU1 **VMS** PUA, PUB DUA0, DUA1 Ultrix-11 uda0, uda1 ra0, ra1 Ultrix-32 uda0, uda1 ra0, ra1

Table 3-2. Device Names

The information regarding operating systems in these subsections is subject to change. The following discussions are based on three assumptions:

- This is the first pass that is being made through SYSGEN; therefore, no saved answer file exists. Answer N (no) to questions such as "Use as input saved answer file?"

- Your host system configuration conforms to the standard UNIBUS device configuration algorithm (otherwise autoconfigure results are not reliable).

- You are generating a mapped version of the operating system on the appropriate hardware (unless you are using RT-11).

#### RSTS/E Operating Systems (v8.0 and above) 3.5.1

RSTS/E scans the hardware to determine configuration each time the system is bootstrapped. The scanning program is called INIT.SYS and it relies on the same hardware configuration conventions as do the other DEC operating systems.

The RSTS/E operating system can support two MSCP controllers. The first MSCP controller must be located at the standard UNIBUS address, 7721508. According to DEC documentation, the second unit should be located in floating address space. For an alternate UD33, Emulex suggests specifying a UNIBUS address of  $760334_8$  using the HARDWARE option of the INIT.SYS program.

The INIT.SYS program uses a user-specified table, located in the currently installed monitor, to make exceptions to the autoconfigure algorithm. This table is modified by the HARDWARE option of the INIT.SYS program. Use of this table allows an MSCP controller to be placed at virtually any address on the I/O page. Note that this table must be reset any time a new monitor is installed. Emulex suggests using a UNIBUS address of 7603348 for an alternate UD33. An MSCP controller must be located at the standard address to be a bootstrap device.

Interrupt vector addresses are assigned to the MSCP controllers by INIT.SYS and programmed into the devices during initialization.

#### 3.5.1.1 Adding MSCP Support

Support for an MSCP controller must be included in a monitor at SYSGEN time. To include support for an MSCP controller in a RSTS/E monitor, respond to the SYSGEN question "number of MSCP controllers" with the number of MSCP controllers on the system.

Units connected to MSCP controllers will be accessible to an on-line RSTS/E system only after the monitor is successfully SYSGENed and installed with the INSTALL suboption of the INIT.SYS program, and the units have been successfully initialized with the DSKINT suboption of INIT.SYS.

#### RT-11 Operating Systems (v5.1 and above) 3.5.2

The RT-11 Operating System supports up to four MSCP controllers with up to 256 devices (total) on the four controllers. The following paragraphs discuss the UNIBUS and vector addresses for MSCP controllers under RT-11 in host systems with only one MSCP controller and in those with more than one controller. Disk partitioning, a unique feature of RT-11 that is applicable regardless of the number of controllers, is also discussed.

### 3.5.2.1 Installing a Single MSCP Controller

If your host system includes only one MSCP controller, install it with a UNIBUS address of 772150<sub>8</sub>. RT-11 will find and install the handler (driver) for that controller. In single MSCP controller configurations, it is not necessary to run SYSGEN. You may use one of the pregenerated monitors that are provided with the RT-11 Distribution. Emulex recommends that you modify the system start-up command file, STARTx.COM, to properly partition the disk drives. See subsection 3.5.2.3.

### 3.5.2.2 Installing Multiple MSCP Controllers

If your host system includes more than one MSCP controller, you may either modify the MSCP handler as described in the *RT-11 Software Support Manual* or you may perform a SYSGEN. The following procedure describes the SYSGEN technique (user input is in **boldface** print):

1. Initiate SYSGEN:

#### IND SYSGEN<return>

Answer the next group of questions appropriately.

2. Indicate that you want the system to use the start-up command file when booting:

Do you want the start-up indirect file (Y)?

### Y<return>

The start-up command file is required to allow additional MSCP controller UNIBUS bus addresses to be specified and to partition the disks consistently when the system is bootstrapped. Answer the next set of questions appropriately.

3. Indicate that you want MSCP support when the Disk Options question appears:

Enter the device name you want support for [dd]:

#### DU<return>

4. Indicate the number of MSCP controllers on your system in response to this question:

How many ports are to be supported (1)?

### 2<return>

RT-11 refers to individual MSCP controllers or controllers as ports. Each port has its own UNIBUS and vector addresses.

Specify support for all other devices in your host system configuration as well. Indicate that there are no more devices by entering a period:

6. You must specify the addresses of all MSCP controllers (ports) using the SET CSR keyboard command. To ensure that this is done consistently and automatically on power-up, you must add the commands to the system start-up command file, STARTx.COM. The x stands for the monitor that is being used, where x is S, F, or X for single-job, foreground/ background, or extended memory, respectively. Edit the command file to include the following statements:

| SET | DU  | CSR=772150        | (Default)  |

|-----|-----|-------------------|------------|

| SET | DU  | $CSR2 = 760334_8$ | (Floating) |

| SET | DU  | VECTOR=154        | (Default)  |

| SET | וומ | VEC2=300          |            |

The UNIBUS for the second device can be any unused address in the I/O page which is supported by UD33 address switch settings; the vector address can be any unused address in the vector page. Default statements are not required.

7. Complete SYSGEN according to the DEC documentation.

### 3.5.2.3 Disk Partitioning

RT-11 is unable to handle drives with a capacity of more than 65,535 blocks (33.5M bytes). To allow drives with larger capacities to be used, RT-11 allows individual physical drives to be partitioned into multiple logical drives. This is done by assigning as many logical drive names (DU0, DU1, etc.) to a physical drive as that drive can support. The statements that make that assignment should be placed in the system start-up command file. This ensures that the drives are automatically partitioned every time the system is bootstrapped and that the partitions are always the same. Use the following procedure to determine the total number of logical drives to be assigned to each physical drive.

- 1. Determine the drive configuration(s) that you intend to use. You need to know the LUN of each logical drive and the data storage capacity (in logical blocks) of each logical unit. Refer to Appendix C for the logical block capacity of supported SMD drives. If the UD33 is at an alternate UNIBUS address (not 772150<sub>8</sub>), then you must specify an MSCP device number by using switches SW1-2 through SW1-4.

- 2. Divide the capacity for each MSCP unit by 65,535. If the result is a number greater than 1, then that MSCP unit should be partitioned into multiple logical units. (The last partition on a disk may be smaller than 65,535 blocks.) Round the result up to the nearest whole number. That whole number equals the number of logical disks into which that MSCP unit should be partitioned.

- 3. You must then include a series of statements in the system start-up command file, STARTx.COM, that assigns logical names to each partition. Each statement has the following format:

```

SET DUn UNIT=y PART=x PORT=z

```

where  $\mathbf{n}$  is the logical device name,  $\mathbf{y}$  is the physical MSCP unit number,  $\mathbf{x}$  is the partition number, and  $\mathbf{z}$  is the controller number (specify the controller number when two or more controllers are present; do not specify the port when only one controller is present). If you partition any drives, you must do this for each partition on each drive, including drives that can hold only one partition.

Example:

You have selected a Fujitsu M2351A drive that has a capacity of 787,156 blocks.

$$\frac{787,156}{65,535}$$

= 12.01 (13 logical units)

Dividing the unit capacities by 65,535 and rounding the result up to the nearest whole number gives the number of logical units into which each should be partitioned.

You assign logical names to the partitions beginning with DU0. For the previous example, the assignments are made as follows:

```

SET DUO UNIT=O PART=O

SET DU1 UNIT=O PART=1

SET DU2 UNIT=O PART=2

SET DU3 UNIT=O PART=3

SET DU4 UNIT=O PART=4

SET DU5 UNIT=O PART=5

SET DU6 UNIT=O PART=6

SET DU7 UNIT=O PART=7

```

Modify the system start-up command file to include the disk partitioning statements.

## 3.5.3 RSX-11M Operating Systems (v4.0 and above)

RSX-11M SYSGEN is an interrogative program that allows a complete, running RSX-11M system to be configured for a particular hardware environment. SYSGEN is well documented in the *RSX-11M System Generation and Installation Guide*, and you are expected to rely primarily on that manual. This explanation is provided only to remove some ambiguities that the installation of the UD33 may present.

SYSGEN supports autoconfigure, and MSCP controllers are detected by autoconfigure; however, autoconfigure detects only the MSCP-class controller that is located at the standard UNIBUS address. Additional MSCP-class controllers at alternate addresses must be attached to the operating system manually.

## 3.5.3.1 Installing a Single MSCP Controller

If you have only one UD33, install it at the standard address (772150 $_8$ ) and use autoconfigure to connect your peripherals. The procedure given in the *RSX-11M System Generation and Configuration Guide* is adequate for this purpose.

## 3.5.3.2 Installing Multiple MSCP Controllers

If you have two MSCP controllers, say a DEC MSCP controller and a UD33, you must perform a complete manual initialization. We recommend that the DEC MSCP controller be installed at the standard UNIBUS address. Locating the UD33 at the alternate UNIBUS address does not prevent its being used as the system device. Both MSCP controllers are connected to the operating system by using the following procedure.

- Invoke SYSGEN.

- > SET /UIC=[200,200]<return>

- > @SYSGEN<return>

- 2. To indicate that you want to use autoconfigure, answer Y (yes) to the following question:

- \* Autoconfigure the host system hardware?

[Y/N]: Y<return>

- 3. To indicate that you do not want to override autoconfigure results, answer **N** (no) to this question:

\*Do you want to override Autoconfigure results? [Y/N]: N<return>

Answer the rest of the questions in the SETUP section appropriately, and continue to the next section, TARGET CONFIGURATION. In TARGET CONFIGURATION, the defaults presented for the first group of questions should be accurate for your system because autoconfigure was requested.

4. In response to the question regarding devices, indicate that you have two MSCP-class controllers:

\* Devices: DU=2<return>

Devices: .<return>

This entry supersedes the value of 1 that autoconfigure has determined. Typing a period (.) terminates device input.

Continue through the next four sections, HOST CONFIGURATION, EXECUTIVE OPTIONS, TERMINAL DRIVER OPTIONS, and SYSTEM OPTIONS, answering questions appropriately.

5. When you reach the PERIPHERAL OPTIONS section, SYSGEN asks you questions that pertain only to the MSCP devices on your system. (Unless you indicated that you wished to override other autoconfigure results when you responded to the Devices question, SYSGEN asks questions on those devices.)

The first question requests information about the controller's interrupt vector address, UNIBUS address, the number of DU-type disk drives (there is no default value for this parameter), the number of command rings, and the number of response rings. The question is asked twice, once for controller 0 and once for controller 1, because we have specified two DU-type controllers. The dialogue uses the abbreviation contr to indicate controller.

\* DU contr 0 [D:154,172150,,4,4] 154,172150,3,4,4<return>

The standard vector address for MSCP controllers is  $154_8$ . The vector for a second unit should be allocated from floating vector address space. Any unused vector between  $300_8$  and  $774_8$  can be allocated. See Appendix A for a description of DEC's algorithm for assigning floating vectors.

The standard UNIBUS bus address for MSCP controllers is  $772150_8$ . Emulex recommends that second unit be located in floating UNIBUS address space. See Appendix A for a description of the DEC algorithm for assigning floating addresses.

The number of DU-type disk drives depends on the configuration that you have selected for the UD33, or on the number of drives that are attached to a DEC MSCP controller.

When you select a configuration for the UD33, you are taking into account the number of physical disk drives that you are attaching to the UD33's SMD interface. When you select a configuration, you are also specifying a logical arrangement for the UD33 MSCP-class subsystem. Some configurations split one physical drive into two logical drives to make file management easier. You determine the configuration of each SMD disk drive when you program the UD33's NOVRAM (see subsections 4.7, 4.8, and 4.9).

The following types of disk drives can be attached to DEC MSCP controllers:

- RX50

- RD51

- RD52

- RD53

- RC25

- RA series

The RC25 has both fixed and removable hard media; count an RC25 as two drives.

RSX-11M supports up to eight command and eight response rings; the number of command and response rings that you specify depends on your application. Four command and four response rings are reasonable and adequate for most applications. In most instances, further information is not required to install the UD33.

- 6. SYSGEN then asks you to specify the type of disk drive(s) on each controller:

- \* DU contr 0 unit 0. is an RA60/80/81/RC25/RD51/RX50 [D:RA81]<return>

For the DEC MSCP controller, indicate the appropriate peripherals.

For the UD33, indicate that you have one RA81 for each logical disk drive.

RSX-11M does not tolerate gaps in sequence; the unit numbers must be contiguous. In addition, the unit numbers specified for each controller must be the same as those reported by the controller during initialization.

Complete the SYSGEN procedure according to DEC documentation.

#### 3.5.4 RSX-11M-PLUS Operating Systems (v2.1 and above)

RSX-11M-PLUS SYSGEN is an interrogative program that allows a complete, running RSX-11M-PLUS system to be configured for a particular hardware environment. SYSGEN is well documented in the RSX-11M-PLUS System Generation and Installation Guide, and you are expected to rely primarily on that manual. This explanation is provided only to remove some ambiguities that the installation of the UD33 may involve.

SYSGEN supports autoconfigure, and MSCP controllers are detected by autoconfigure; however, autoconfigure detects only the MSCP-class controller that is located at the standard UNIBUS address. Additional MSCP-class controllers at alternate addresses must be attached to the operating system manually.

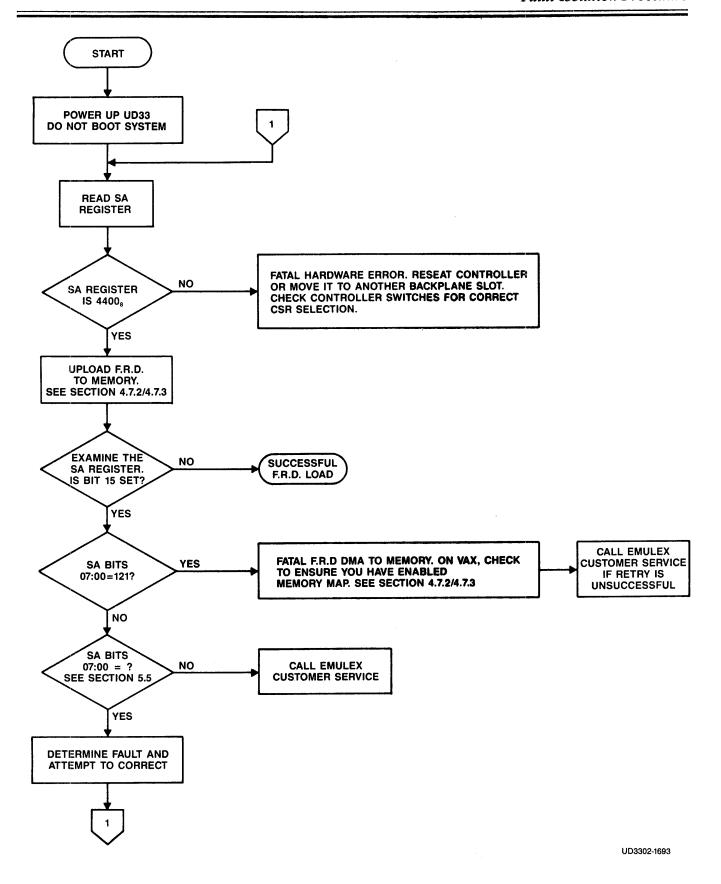

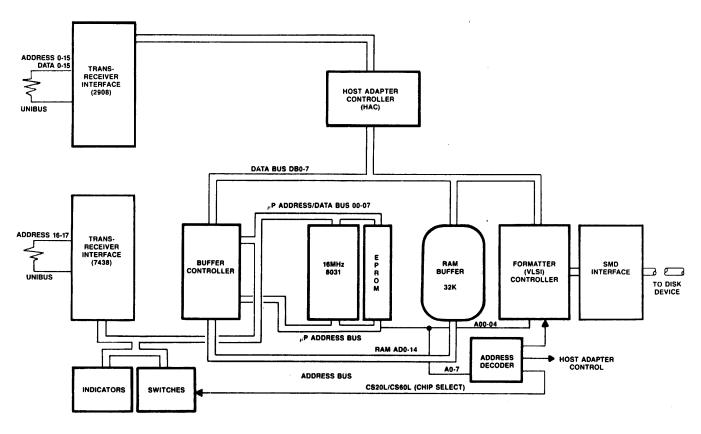

#### 3.5.4.1 Installing a Single MSCP Controller