# SPARC/CPU-54 Reference Guide

P/N 220991 Revision AA May 2003

## Copyright

The information in this publication is subject to change without notice. Force Computers, GmbH reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance, or design.

Force Computers, GmbH shall not be liable for technical or editorial errors or omissions contained herein, nor for indirect, special, incidental, or consequential damages resulting from the furnishing, performance, or use of this material. This information is provided "as is" and Force Computers, GmbH expressly disclaims any and all warranties, express, implied, statutory, or otherwise, including without limitation, any express, statutory, or implied warranty of merchantability, fitness for a particular purpose, or non-infringement.

This publication contains information protected by copyright. This publication shall not be reproduced, transmitted, or stored in a retrieval system, nor its contents used for any purpose, without the prior written consent of Force Computers, GmbH.

Force Computers, GmbH assumes no responsibility for the use of any circuitry other than circuitry that is part of a product of Force Computers, GmbH. Force Computers, GmbH does not convey to the purchaser of the product described herein any license under the patent rights of Force Computers, GmbH nor the rights of others.

Copyright© 2003 by Force Computers, GmbH. All rights reserved.

The Force logo is a trademark of Force Computers, GmbH. SENTINEL is a registered trademark of Force Computers, GmbH.

IEEE is a registered trademark of the Institute for Electrical and Electronics Engineers, Inc.

PICMG, CompactPCI, and the CompactPCI logo are registered trademarks and the PICMG logo is a trademark of the PCI Industrial Computer Manufacturer's Group.

MS-DOS, Windows95, Windows98, Windows2000 and Windows NT are registered trademarks and the logos are a trademark of the Microsoft Corporation.

Intel and Pentium are registered trademarks and the Intel logo is a trademark of the Intel Corporation.

SPARC is a registered trademark, the SPARC logo is a trademark and UltraSPARC is a registered trademark of SPARC International. Inc.

PowerPC is a registered trademark and the PowerPC logo is a trademark of International Business Machines Corporation.

AltiVec is a registered trademark and the AltiVec logo is a trademark of Motorola, Inc.

Sun, Sun Microsystems, the Sun logo, SPARCengine Ultra, Solaris, Open Boot, SunVTS are trademarks or registered trademarks of SUN Microsystems, Inc.

The Linux Kernel is Copyright© Linus B. Torvalds under the terms of the General Public License (GPL).

GoAhead ia a registered trademark of GoAhead Software, Inc. and SelfReliant and Self Availability are trademarks of GoAhead Software. Inc

LynxOS and BlueCat are registered trademarks of LynuxWorks, Inc.

Tornado, VxWorks, Wind, WindNavigator, Wind River Systems, Wind River Systems and design, WindView, WinRouter and Xmath are registered trademarks or service marks of Wind River Systems, Inc.

Envoy, the Tornado logo, Wind River, and Zinc are trademarks or service marks of Wind River Systems, Inc.

Sony is a registered trademark of Sony Corporation, Japan

Ethernet is a trademark and Xerox is a registered trademark of Xerox Corporation

Other product names mentioned herein may be trademarks and/or registered trademarks of their respective companies.

#### World Wide Web: www.fci.com

24-hour access to on-line manuals, driver updates, and application notes is provided via SMART, our SolutionsPLUS customer support program that provides current technical and services information.

# Headquarters

#### The Americas

Force Computers Inc. 4211 Starboard Drive Fremont, CA 94538 U.S.A.

Tel.: +1 (510) 445-6000 Fax: +1 (510) 445-5301 Email: support@fci.com

#### **Europe**

Force Computers GmbH Lilienthalstr. 15 D-85579 Neubiberg/München Germany

Tel.: +49 (89) 608 14-0 Fax: +49 (89) 609 77 93 Email: support-de@fci.com

#### **Asia**

Force Computers Japan KK Shibadaimon MF Building 4F 2-1-16 Shiba Daimon Minato-ku, Tokyo 105-0012 Japan

Tel.: +81 (03) 3437 6221 Fax: +81 (03) 3437 6223 Email: support-de@fci.com

# **Contents**

# Using This Guide Other Sources of Information Safety Notes Sicherheitshinweise

# 1 Introduction

| Features            | 1-3   |

|---------------------|-------|

| CPU                 |       |

| Memory              | . 1-4 |

| OpenBoot            | . 1-4 |

| Block Diagram       | 1-5   |

| CPU Board Variants  | 1-6   |

| SPARC/CPU-54        | . 1-6 |

| SPARC/CPU-54T       | . 1-7 |

| Standard Compliance | 1-8   |

SPARC/CPU-54 v

| Product Nomenclature                               |

|----------------------------------------------------|

| Installation                                       |

| Action Plan                                        |

| Requirements                                       |

| Environmental Requirements                         |

| Power Consumption                                  |

| Software Requirements                              |

| Hardware and Software Upgrades and Accessories 2-8 |

| Memory Modules                                     |

| IO-54                                              |

| SPARC/IOBP-54                                      |

| Solaris Driver Package                             |

| Setting the SCSI Termination2-10                   |

| SCSI 1 Termination                                 |

| SCSI 2 Termination                                 |

| Switch Settings 2-12                               |

| Board Installation 2-16                            |

| Backplane Configuration                            |

| Installing the CPU Board                           |

| Removing the CPU Board                             |

| Powering Up                                        |

| Boot Devices OTP PROM and Flash EPROM              |

| Installing Solaris                                 |

| Solaris 8                                          |

2

vi SPARC/CPU-54

# **3 Controls, Indicators, and Connectors**

| Tonic Panier of the SPARC/CPU-34        |      |

|-----------------------------------------|------|

| EDs                                     |      |

| Geys                                    |      |

| Reset                                   |      |

| Abort                                   |      |

| Mode                                    |      |

| Connectors Ethernet                     |      |

| Serial I/O                              |      |

| Keyboard/Mouse                          |      |

| SCSI                                    | 3-9  |

| On-Board Connectors of the SPARC/CPU-54 | ۶    |

| OpenBoot Firmware                       |      |

|                                         | 4.0  |

| ntroduction                             |      |

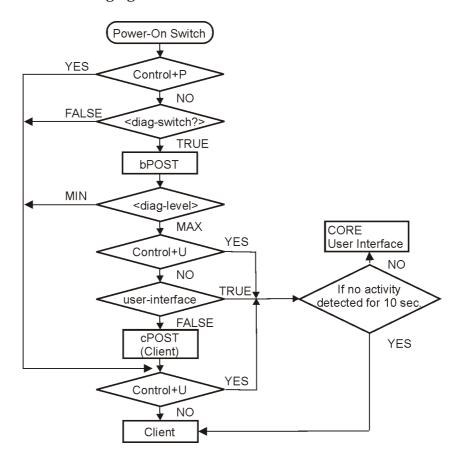

| CORE Worldow                            | _    |

| CORE Workflow                           |      |

| POST                                    |      |

| DpenBoot                                |      |

| Optional Boot Parameters                |      |

| Boot Devices                            |      |

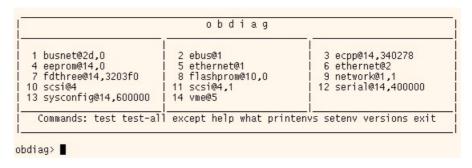

| DBDIAG                                  |      |

| /xWorks Support                         |      |

|                                         |      |

| NVRAM Boot Parameters                   | 4-14 |

| Diagnostics                             |      |

| SCSI Bus                                |      |

| All SCSI Buses                          |      |

| Single Device                           |      |

| Group of Devices                        |      |

| 2.046 0. 201.000                        |      |

| Clock                                   | 4-17 |

| Clock                                   |      |

SPARC/CPU-54 vii

|   | Displaying System Information                                                                                                                                                        |    |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | ID PROM                                                                                                                                                                              |    |

|   | Resetting the System4-2                                                                                                                                                              | 1  |

|   | Activating OpenBoot Help4-2                                                                                                                                                          | 2  |

| 5 | Maps and Registers                                                                                                                                                                   |    |

|   | Address Map5-                                                                                                                                                                        | 3  |

|   | Status and Control Register5-                                                                                                                                                        | 4  |

|   | User LED 1 Control Register                                                                                                                                                          | -6 |

|   | Control Register 5-                                                                                                                                                                  | 8  |

|   | Control and Status Register5-                                                                                                                                                        | 9  |

|   | Watchdog Timer and Temperature Control Register       5-1         Watchdog Timer and Temperature Control Status Register       5-1         Watchdog Timer Trigger Register       5-1 | 0  |

|   | SYSFAIL and ACFAIL Interrupt Control Register5-1                                                                                                                                     | 2  |

|   | Reset Status Register                                                                                                                                                                | 3  |

|   | System Configuration Identification Register5-1                                                                                                                                      | 4  |

|   | Seven-Segment LED Display Control Register5-1                                                                                                                                        | 4  |

|   | Switch Status Register                                                                                                                                                               | 6  |

viii SPARC/CPU-54

|     | Switch 4 and 5 Status Register       | 5-17   |

|-----|--------------------------------------|--------|

|     | Switch 800 Status Register           | 5-18   |

|     | Timer Register                       | . 5-19 |

|     | Timer Control Register               | 5-19   |

|     | Timer Initial Control Register L     | 5-20   |

|     | Timer Initial Control Register U     | 5-20   |

|     | Timer Counter Status Register L      |        |

|     | Timer Counter Status Register U      | 5-20   |

|     | RS-422 Control and Status Register   | . 5-21 |

|     | Ethernet Control and Status Register | . 5-22 |

| Α   | Troubleshooting                      |        |

| В   | Battery Exchange                     |        |

| Inc | dex                                  |        |

| Pro | oduct Error Report                   |        |

|     |                                      |        |

SPARC/CPU-54 ix

X SPARC/CPU-54

# **Tables**

| Introd  | uction           |                                                                            |

|---------|------------------|----------------------------------------------------------------------------|

| Table   |                  | Standard Compliance1-8                                                     |

| Table   | 2                | Product Nomenclature                                                       |

| Table   | 3                | Excerpt from the SPARC/CPU-54 Ordering Information for CPU Boards 1-10     |

| Table   | 4                | Excerpt from the SPARC/CPU-54 Ordering Information for Memory Modules 1-10 |

| Table   | 5                | Excerpt from the SPARC/CPU-54 Ordering Information for Accessories 1-11    |

| Install | ation            |                                                                            |

| Table   | 6                | Environmental Requirements                                                 |

| Table   | 7                | Maximum Power Consumption                                                  |

| Table   | 8                | Maximum Power Consumption with SPARC/MEM-54 Installed2-6                   |

| Table   | 9                | Switch Settings2-13                                                        |

| Table   | 10               | Customizing Solaris 8                                                      |

| Table   | 11               | Required Solaris Package for Solaris 8                                     |

| Table   | 12               | Devices and Their Appropriate Drivers2-21                                  |

| Table   | 13               | Hardware Node Assignment                                                   |

| Table   | 14               | Instance Number Assignment for SPARC/CPU-54                                |

| Table   | 15               | Flash Segmentation and Write Protection                                    |

| Contr   | ols, Indicators, | and Connectors                                                             |

| Table   | 16               | Description of Front Panel LEDs                                            |

| Table   | 17               | On-Board Connectors                                                        |

| Table   | 18               | P2 Backplane Connector Signals3-10                                         |

SPARC/CPU-54 xi

#### **OpenBoot Firmware**

| Table 19         | Boot Parameters                                             |

|------------------|-------------------------------------------------------------|

| Table 20         | Device Alias Definitions for SCSI#14-6                      |

| Table 21         | Device Alias Definitions for SCSI#2 4-9                     |

| Table 22         | Other Device Alias Definitions                              |

| Table 23         | OBDIAG Commands                                             |

| Table 24         | Setting Configuration Parameters 4-14                       |

| Table 25         | Diagnostic Routines                                         |

| Table 26         | Commands to Display System Information                      |

| Maps and Registo | ers                                                         |

| Table 27         | PCI Addresses Considered by the PCI-to-EBus2 Controller     |

| Table 28         | System Configuration Register Overview                      |

| Table 29         | User LED 1 Control Register5-6                              |

| Table 30         | User LED 2 Control Register5-                               |

| Table 31         | Control Register                                            |

| Table 32         | Control and Status Register                                 |

| Table 33         | Watchdog Timer and Temperature Control Status Register 5-10 |

| Table 34         | Watchdog Timer Trigger Register                             |

| Table 35         | SYSFAIL and ACFAIL Interrupt Control Register               |

| Table 36         | Reset Status Register                                       |

| Table 37         | System Configuration Register                               |

| Table 38         | Seven-Segment LED Display Control Register 5-14             |

| Table 39         | Serial Protocol Status Register                             |

| Table 40         | Rotary Switch Status Register 5-10                          |

| Table 41         | Rotary Switch Settings                                      |

| Table 42         | Switch 4 and 5 Status Register                              |

| Table 43         | Switch 800 Status Register                                  |

| Table 44         | Timer Control Register                                      |

| Table 45         | Timer Initial Control Register L                            |

| Table 46         | Timer Initial Control Register U                            |

| Table 47         | Timer Counter Control Register L                            |

| Table 48         | Timer Counter Control Register L                            |

| Table 49         | RS-422 Control and Status Register 5-2                      |

| Table 50         | Ethernet Control and Status Register                        |

|                  |                                                             |

xii SPARC/CPU-54

# **Figures**

| Introdu          | iction         |                                                      |       |

|------------------|----------------|------------------------------------------------------|-------|

| Figure<br>Figure |                | Function Blocks                                      |       |

| Figure           |                | SPARC/CPU-54                                         |       |

| Figure           |                | SPARC/CPU-54T                                        |       |

| Installa         | ation          |                                                      |       |

| Figure           | 5              | SCSI Termination Concept of SPARC/CPU-54 and IOBP-54 | 2-11  |

| Figure           | 6              | Location of Switches on Board's Top Side             | 2-12  |

| Figure           | 7              | Location of Switches on Board's Bottom Side          | 2-13  |

| Contro           | ls, Indicators | , and Connectors                                     |       |

| Figure           | 8              | SPARC/CPU-54 Front Panel                             | . 3-3 |

| Figure           | 9              | Front Panel LEDs                                     | . 3-4 |

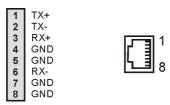

| Figure           | 10             | Twisted-Pair Ethernet Connector Pinout               | . 3-6 |

| Figure           | 11             | Serial A+B Connector Pinout RS-232                   | . 3-7 |

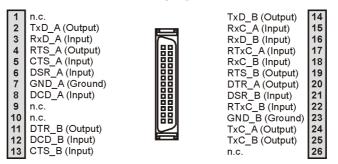

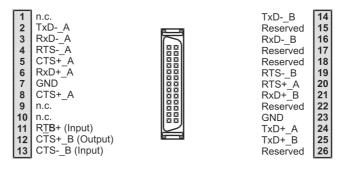

| Figure           | 12             | 26-Pin Serial A+B Connector Pinout RS-422            | . 3-7 |

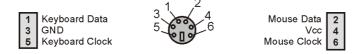

| Figure           | 13             | Keyboard/Mouse Connector Pinout SUN-Type Function    | . 3-8 |

| Figure           | 14             | Keyboard/Mouse Connector Pinout PS/2-Type Function   | . 3-8 |

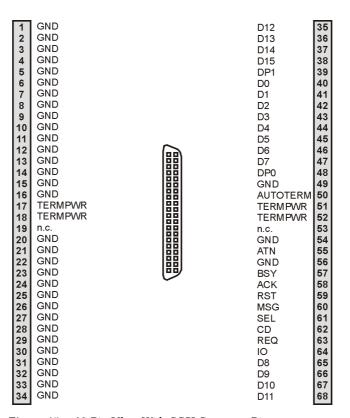

| Figure           | 15             | 68-Pin Ultra-Wide SCSI Connector Pinout              | . 3-9 |

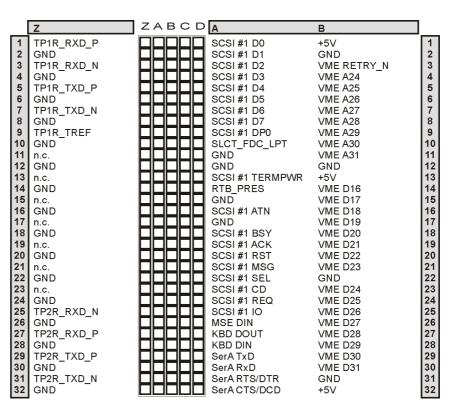

| Figure           | 16             | P2 VMEbus Connector Pinout Rows Z-B                  | 3-11  |

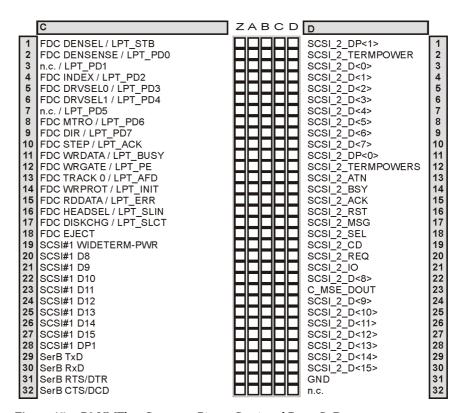

| Figure           | 17             | P2 VMEbus Connector Pinout Continued Rows C+D        | 3-12  |

SPARC/CPU-54 xiii

#### **OpenBoot Firmware**

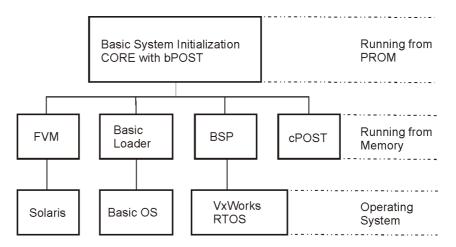

| Figure 18 | System Overview                  | 4-4          |

|-----------|----------------------------------|--------------|

| Figure 19 | OBDIAG Main Menu                 | 4-11         |

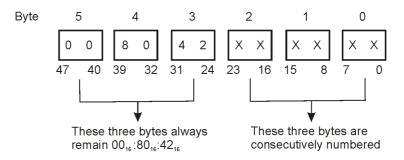

| Figure 20 | 48-bit (6-byte) Ethernet Address | <b>4-19</b>  |

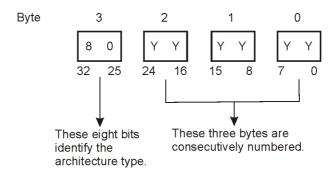

| Figure 21 | 32-bit (4-byte) Host ID          | <b>4-1</b> 9 |

xiv SPARC/CPU-54

# **Using This Guide**

This Reference Guide is intended for users qualified in electronics or electrical engineering. Users must have a working understanding of Peripheral Component Interconnect (PCI), VMEbus, and telecommunications.

#### **Conventions**

| Notation               | Description                                                                                            |  |

|------------------------|--------------------------------------------------------------------------------------------------------|--|

| 1234                   | All numbers are decimal numbers except when used with the notations described below                    |  |

| 00000000 <sub>16</sub> | Typical notation for hexadecimal numbers (digits are 0 through F), e.g. used for addresses and offsets |  |

| $0000_{2}$             | Same for binary numbers (digits are 0 and 1)                                                           |  |

| X                      | Generic use of a letter                                                                                |  |

| n                      | Generic use of numbers                                                                                 |  |

| n.nn                   | Decimal point indicator is signaled                                                                    |  |

| Bold                   | Character format used to emphasize a word                                                              |  |

| Courier                | Character format used for on-screen output                                                             |  |

| Courier+Bold           | Character format used to characterize user input                                                       |  |

| Italics                | Character format for references, table, and figure descriptions                                        |  |

| <text></text>          | Typical notation used for variables and keys                                                           |  |

| [text]                 | Typical notation for optional parameters                                                               |  |

|                        | Repeated item                                                                                          |  |

|                        | Ranges                                                                                                 |  |

| Note:                  | No danger encountered. Pay attention to important information marked using this layout                 |  |

| Caution                | Possibly dangerous situation: slight injuries to people or damage to objects possible                  |  |

SPARC/CPU-54 xv

# **Revision History**

| Order<br>No. | Revision | Date          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 212466       | AA       | February 2001 | Preliminary Installation Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 21466        | AB       | May 2001      | Corrected "Expansion" page -xxi; Removed interfaces section in chapter 1; Removed block diagram of I/O board, infor mation on I/O-board installation, connector pinouts of I/O-board and created separate Installation Guide for I/O-board; Corrected Eth 1 and Eth 2 in Figure 1 "Function Blocks" page 1-3; Removed table "Interfaces on the CPU Board" on page 1-4; Corrected Figure 2 "Block Diagram of the CPU Board" page 1-5; Corrected power consumption of SMEM board in Table 7 "SPARC/CPU-54 Maximum Power Consumption" page 2-6; Added "Software Requirements" page 2-7; Corrected safety note in "SPARC/IOBP-54" page 2-9; Corrected switch settings of SW4-1, SW4-2, SW5-2, and SW5-4 in Table 10 "Switch Settings" page 2-11; Added "Solaris Driver Package" page 2-10; Corrected boot flash writing information in "Booting" page 2-16; Corrected "Installing Solaris" page 2-17; Corrected "Setting the SCSI Termination" page 2-22; Corrected Figure 6 "SCSI Termination Concept of SPARC/CPU-54 and IOBP-54" page 2-24; Corrected pinout of Figure 11 "26-Pin Serial A+B Connector Pinout RS422" page 3-8; |

xvi SPARC/CPU-54

| Order<br>No. | Revision | Date           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 212466       | AB       | May 2001       | Corrected pinout 19 and 62 in Figure 14 "68-Pin Ultra-Wide SCSI Connector Pinout" page 3-10; Corrected Table 18 "On-Board Connectors" page 3-11 and Table 19 "P2 Backplane Connector Signals" page 3-11; Corrected pinout row Z in Figure 15 "P2 VMEbus Connector Pinout Rows Z-B" page 3-12 and row D in Figure 16 "P2 VMEbus Connector Pinout Continued Rows C+D" page 3-13; Corrected "CORE" page 4-3; Corrected introduction to CORE commands in "CORE Commands" page 4-6; Corrected screen shot in "Boot Devices" page 4-7; Added "POST" page 4-6; Added the "OBDIAG" page 4-10; Corrected "Diagnostics" page 4-15; Editorial changes |

| 212466       | AC       | June 2001      | Corrected SW4-3 and SW4-4 in Table 10 "Switch Settings" page 2-11;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 212466       | AD       | July 2001      | Added information on VxWorks in "VxWorks Support" page 4-13;<br>Added information on PCI Control Register on page 4-18;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 212466       | AE       | August 2001    | Added the "Sicherheitshinweise" chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 212466       | AF       | September 2001 | Revised "Safety Notes" page xix and "Sicherheitshinweise" page xxiii;<br>Added information on the execution of the CORE firmware in "POST" page 4-6;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

SPARC/CPU-54 xvii

| Order<br>No. | Revision | Date         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 216116       | AA       | June 2002    | Modified "Safety Notes" page xxi and "Sicherheitshinweise" page xxv; modified Figure 2 "Block Diagram of the CPU Board" page 1-5; replaced EN 50081/2 with EN 55022/4 in Table 1 "Standard Compliance" page 1-8; modified and updated section "Ordering Information" page 1-9; removed table "Qualified Memory Modules" and accompanying safety note in section "Memory Modules" page 2-8; modified section "Setting the SCSI Termination" page 2-10; corrected description of switch SW5-4 in Figure 5 "SCSI Termination Concept of SPARC/CPU-54 and IOBP-54" page 2-11; modified description of switches 4-3, 4-4, 5-4, 7-1 and 7-2 in Table 9 "Switch Settings" page 2-13; added Figure 7 "Location of Switches on Board's Bottom Side" page 2-13; modified sections "Boot Devices OTP PROM and Flash EPROM" page 2-18 and "User Application" page 2-18; added information on problem with VMEbus read errors and Solaris 8 version 4/01 to "Installing Solaris" page 2-19 and the "Troubleshooting" chapter; moved section "Battery Exchange" to Appendix B; changed Table 15 "Flash Segmentation and Write Protection" page 2-23; added description of Ethernet LEDs in Table 16 "Description of Front Panel LEDs" page 3-4; modified section "PCI Control Register"; modified section "OBDIAG" page 4-10; added chapter "Maps and Registers" page 5-1 from Reference Guide with following modifications: corrected description of signal ID[30] in "System Configuration Identification Register" page 5-14; modified description of bits 0-4 in Table 42 "Switch 4 and 5 Status Register" page 5-17; modified description of the RS-422 Control and Status register page 5-21 |

| 220063       | AA       | January 2003 | Changed document type to "Reference<br>Guide"; added note on EN 55022 non-com-<br>pliance to sections "EMC" page xxi, "EMV"<br>page xxv, "Standard Compliance" page 1-8,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

xviii SPARC/CPU-54

| Order<br>No. | Revision | Date     | Description                                                                                              |

|--------------|----------|----------|----------------------------------------------------------------------------------------------------------|

| 220991       | AA       | May 2003 | Corrected pinout of RS-422 interface<br>Added information on termination when<br>using RS-422 interfaces |

SPARC/CPU-54 xix

# **Other Sources of Information**

For further information refer to the following documents:

| Company                                  | www.                    | Document                                                                                  |

|------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------|

| Force Computers                          | forcecomputers.com      | SPARC/CPU-54 OpenBoot Enhancements<br>Programmer's Guide (P/N 216134) <sup>1)</sup>       |

|                                          |                         | SPARC/IO-54 Installation Guide<br>(P/N 214901)                                            |

|                                          |                         | SPARC/IOBP-54 Installation Guide (P/N 213170)                                             |

|                                          |                         | SPARC/MEM-54 Installation Guide (P/N 214000)                                              |

| IEEE Standards<br>Department             | ieee.com                | IEEE P1386 Standard Mechanics for a Common Mezzanine Card Family: CMC                     |

| National Semiconductor                   | national.com            | PC87307/PC97307 Plug and Play Compatible Super I/O, Preliminary Specification, March 1998 |

| PCI Special Interest Group               | pcisig.com              | PCI Local Bus Specification Rev2.1                                                        |

| PICMG<br>PCI Special Inter-<br>est Group | picmg.org<br>pcisig.com | PCI Local Bus Specification Rev2.2                                                        |

| SUN Microsystems                         | sun.com                 | UltraSPARC-IIE, Draft Datasheet, Aug 25<br>1999                                           |

|                                          |                         | PCIO (Cheerio, STP2003) Preliminary<br>Datasheet, March 1997                              |

|                                          |                         | Cheerio Specification, May 1996                                                           |

| Tundra                                   | tundra.com              | Universe II User's Guide 1997                                                             |

|                                          |                         | Universe II Manual Addendum, Rev2,<br>Jun 21, 1999                                        |

| VITA                                     | vita.com                | VME64 Standard ANSI/VITA 1-1994                                                           |

| VITA                                     | vita.com                | VME64 Extensions Draft Standard, Draft<br>1.8, Jun 13, 1997                               |

<sup>1)</sup> Only available via SMART. If you do not have a S.M.A.R.T. account, you can download the PDF file via a Public S.M.A.R.T. Access Account from Force Compters Internet Site. To get an account, click on the blue button labeled "log on S.M.A.R.T." and sign up by entering the form.

XX SPARC/CPU-54

## **Safety Notes**

This section provides safety precautions to follow when installing, operating, and maintaining the SPARC/CPU-54.

We intend to provide all necessary information to install and handle the SPARC/CPU-54 in this Reference Guide. However, as the product is complex and its usage manifold, we do not guarantee that the given information is complete. If you need additional information, ask your Force Computers representative.

The SPARC/CPU-54 has been designed to meet the standard industrial safety requirements. It must not be used except in its specific area of office telecommunication industry and industrial control.

Only personnel trained by Force Computers or persons qualified in electronics or electrical engineering are authorized to install, maintain, and operate the SPARC/CPU-54. The information given in this manual is meant to complete the knowledge of a specialist and must not be taken as replacement for qualified personnel.

#### **EMC**

The board has been tested in a standard Force Computers system and found to comply with the limits for a Class A digital device in this system, pursuant to part 15 of the FCC Rules, EN 55022 Class A respectively. These limits are designed to provide reasonable protection against harmful interference when the system is operated in a commercial, business or industrial environment.

Note: The board is not compliant to EN 55022 if you connect a SCSI device to the SCSI connector on the front panel.

The board generates and uses radio frequency energy and, if not installed properly and used in accordance with this Reference Guide, may cause harmful interference to radio communications. Operating the system in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his own expense.

If you use the board without a PMC module, cover empty slots with blind panels to ensure proper EMC shielding. If boards are integrated into open systems, always cover empty slots.

SPARC/CPU-54 xxi

#### Installation

Electrostatic discharge and incorrect board installation and removal can damage circuits or shorten their life. Therefore:

- Before installing or removing the board, read the "Action Plan" section page 2-3.

- Before touching boards or electronic components, make sure that you are working in an ESD-safe environment.

- When plugging the board in or removing it, do not press on the front panel but use the handles.

- Before installing or removing an additional device or module, read the respective documentation.

- Make sure that the board is connected to the VME backplane via all assembled connectors and that power is available on all power pins.

#### **Power Up**

If an unformatted floppy disk resides in a floppy drive connected to the SPARC/CPU-54 during power up, the SPARC/CPU-54 does not boot and the OpenBoot prompt does not appear. Therefore, never boot the SPARC/CPU-54 with an unformatted floppy disk residing in a floppy drive connected to the SPARC/CPU-54.

#### **Operation**

While operating the board ensure that the environmental and power requirements are met.

Do not operate the SPARC/CPU-54 outside the specified environmental limits. High humidity and condensation may cause short circuits. Make sure the product is completely dry and there is no moisture on any surface before applying power. Do not operate the product below 0°C.

When operating the board in areas of electromagnetic radiation ensure that the board is bolted on the VME system and the system is shielded by enclosure.

Make sure that contacts and cables of the board cannot be touched while the board is operating.

The switch settings have to be checked and changed before the board installation. Do not set/reset the switches during operation. Otherwise, the board is damaged.

xxii SPARC/CPU-54

#### Replacement/Expansion

Only replace or expand components or system parts with those recommended by Force Computers. Otherwise, you are fully responsible for the impact on EMC and the possibly changed functionality of the product.

Check the total power consumption of all components installed (see the technical specification of the respective components). Ensure that any individual output current of any source stays within its acceptable limits (see the technical specification of the respective source).

#### **System Controller**

If more than one system controller is active in the VMEbus system, the board or other VMEbus participants can be damaged. Therefore, always ensure that only one CPU board is configured as system controller in the VMEbus system.

#### **RJ-45 Connector**

An RJ-45 connector is used for both telephone and twisted pair Ethernet (TPE) connectors. Mismatching the two connectors may destroy your telephone as well as your SPARC/CPU-54. Therefore:

- TPE connectors have to be clearly marked as network connectors.

- The TPE bushing of the system has to be connected only to safety extra low voltages (SELV) circuits.

- The total length of the electric cable connected to a TPE bushing must not exceed 100 meters.

SPARC/CPU-54 xxiii

#### **Battery**

If a lithium battery on the board has to be exchanged, observe the following safety notes:

- Exchanging the battery always results in data loss of the devices which use the battery as power backup. Therefore, backup affected data before exchanging the battery.

- Incorrect exchange of lithium batteries can result in a hazardous explosion.

- Exchange the battery before seven years of actual battery use have elapsed.

- Always use the same type of lithium battery as is already installed.

- Use appropriate tools to remove the battery.

- When installing the new battery, ensure that the dot marked on top of the battery covers the dot marked on the chip.

#### **Environment**

Always dispose of old boards according to your country's legislation, if possible in an environmentally acceptable way.

xxiv SPARC/CPU-54

#### Sicherheitshinweise

Dieser Abschnitt enthält Sicherheitshinweise, die bei Einbau, Betrieb und Wartung des SPARC/CPU-54 zu beachten sind.

Wir sind darauf bedacht, alle notwendigen Informationen zum Einbau und zum Umgang mit dem SPARC/CPU-54 in diesem Handbuch bereit zu stellen. Da es sich jedoch bei dem SPARC/CPU-54 um ein komplexes Produkt mit vielfältigen Einsatzmöglichkeiten handelt, können wir die Vollständigkeit der im Handbuch enthaltenen Informationen nicht garantieren. Falls Ihnen Informationen fehlen sollten, wenden Sie sich bitte an Ihren Vertreter von Force Computers.

Das SPARC/CPU-54 erfüllt die für die Industrie geforderten Sicherheitsvorschriften und darf ausschließlich für Anwendungen in der Telekommunikationsindustrie und im Zusammenhang mit Industriesteuerungen verwendet werden.

Einbau, Wartung und Betrieb dürfen nur von durch Force Computers ausgebildetem oder im Bereich Elektronik oder Elektrotechnik qualifiziertem Personal durchgeführt werden. Die in diesem Handbuch enthaltenen Informationen dienen ausschließlich dazu, das Wissen von Fachpersonal zu ergänzen, können dieses jedoch nicht ersetzen.

#### **EMV**

Das Board wurde in einem Force Computers Standardsystem getestet. Es erfüllt die für digitale Geräte der Klasse A gültigen Grenzwerte in einem solchen System gemäß den FCC-Richtlinien Abschnitt 15 bzw. EN 55022 Klasse A. Diese Grenzwerte sollen einen angemessenen Schutz vor Störstrahlung beim Betrieb des Boards in Geschäfts-, Gewerbe- sowie Industriebereichen gewährleisten.

Anmerkung: Das Board erfüllt den Standard EN 55022 nicht, wenn Sie ein SCSI-Gerät am SCSI-Stecker der Frontblende anschließen.

Das Board arbeitet im Hochfrequenzbereich und erzeugt Störstrahlung. Bei unsachgemäßem Einbau und anderem als in diesem Handbuch beschriebenen Betrieb können Störungen im Hochfrequenzbereich auftreten. Wird das Board in Wohngegenden betrieben, ist der Benutzer verpflichtet, entstehende Störungen auf seine Kosten beheben zu lassen.

SPARC/CPU-54 xxv

Wenn Sie das Board ohne ein PMC Modul verwenden, schirmen Sie freie Steckplätze mit einer Blende ab, um einen ausreichenden EMV Schutz zu gewährleisten. Wenn Sie Boards in Systeme einbauen, schirmen Sie freie Steckplätze mit einer Blende ab.

#### Installation

Elektrostatische Entladung und unsachgemäßer Ein- und Ausbau des Boards kann Schaltkreise beschädigen oder ihre Lebensdauer verkürzen. Beachten Sie deshalb die folgenden Punkte:

- Bevor Sie Boards oder elektronische Komponenten berühren, vergewissern Sie sich, dass Sie in einem ESD-geschützten Bereich arbeiten.

- Lesen Sie vor Ein- oder Ausbau des Boards den Abschnitt "Action Plan" auf Seite 2-3.

- Drücken Sie bei Ein- oder Ausbau des Boards nicht auf die Frontblende, sondern benutzen Sie die Griffe.

- Lesen Sie vor dem Ein- oder Ausbau von zusätzlichen Geräten oder Modulen das dazugehörige Benutzerhandbuch.

- Vergewissern Sie sich, dass das Board über alle Stecker an die VME Backplane angeschlossen ist und alle Spannungskontakte mit Strom versorgt werden.

#### **Booten**

Befindet sich während des Bootens eine unformatierte Diskette in einem mit dem SPARC/CPU-54 verbundenen Diskettenlaufwerk, bootet das SPARC/CPU-54 nicht, und die OpenBoot-Eingabeaufforderung erscheint nicht. Booten Sie deshalb niemals das SPARC/CPU-54, wenn sich eine unformatierte Diskette in einem mit dem SPARC/CPU-54 verbundenen Diskettenlaufwerk befindet.

xxvi SPARC/CPU-54

#### **Betrieb**

Achten Sie darauf, dass die Umgebungs- und die Leistungsanforderungen während des Betriebs eingehalten werden.

Betreiben Sie das SPARC/CPU-54 nur innerhalb der angegebenen Grenzwerte für die relative Luftfeuchtigkeit und Temperatur, da durch hohe Luftfeuchtigkeit und Kondensation Kurzschlüsse entstehen können. Stellen Sie vor dem Einschalten des Stroms sicher, dass sich auf dem SPARC/CPU-54 kein Kondensat befindet, und betreiben Sie das SPARC/CPU-54 nicht unter 0°C.

Wenn Sie das Board in Gebieten mit elektromagnetischer Strahlung betreiben, stellen Sie sicher, dass das Board mit dem VME System verschraubt ist und das System durch ein Gehäuse abgeschirmt wird.

Stellen Sie sicher, dass Anschlüsse und Kabel des Boards während des Betriebs nicht berührt werden können.

Prüfen und ändern Sie die Schalterstellungen bevor Sie das Board installieren. Ändern Sie die Stellungen während des Betriebs, kann das Board beschädigt werden.

#### Austausch/Erweiterung

Verwenden Sie bei Austausch oder Erweiterung ausschließlich von Force Computers empfohlene Komponenten und Systemteile. Andernfalls sind Sie für mögliche Auswirkungen auf EMV und geänderte Funktionalität des Produktes voll verantwortlich.

Überprüfen Sie die gesamte aufgenomme Leistung aller eingebauten Komponenten (siehe die technischen Daten der entsprechenden Komponente). Stellen Sie sicher, dass die Ausgangsströme jedes Verbrauchers innerhalb der zulässigen Grenzwerte liegen (siehe die technischen Daten des entsprechenden Verbrauchers).

#### **System Controller**

Bei mehr als einem aktiven System Controller im VMEbus System kann das SPARC/CPU-54 oder andere VMEbus Boards beschädigt werden. Vergewissern Sie sich deshalb, dass nur ein CPU Board im VMEbus System als System Controller konfiguriert ist.

SPARC/CPU-54 xxviii

#### **RJ-45 Stecker**

Das CPU Board ist mit RJ-45 Steckern ausgestattet. Dieser Stecker wird sowohl für Telefonanschlüsse als auch für Netzwerkkabel (Twisted Pair Ethernet - TPE) verwendet. Die Verwechslung dieser Anschlüsse kann sowohl das Telefon als auch das Board zerstören. Beachten Sie deshalb die folgenden Punkte:

- Vergewissern Sie sich, dass Anschlüsse deutlich als Netzwerkanschlüsse gekennzeichnet sind.

- Schließen Sie TPE-Stecker/Netzwerkstecker Ihres Systems nur an Sicherheitskleinspannungskreise (SELV) an.

- Vergewissern Sie sich, dass die an einem TPE-Anschluss angeschlossene Leitung eine Gesamtlänge von 100 Metern nicht überschreitet.

Falls Sie Fragen haben, wenden Sie sich an Ihren Systemadministrator.

#### **Batterie**

Achten Sie beim Austausch der Batterie auf folgende Hinweise:

- Fehlerhafter Austausch von Lithium-Batterien kann zu lebensgefährlichen Explosionen führen.

- Der Austausch der Batterie bringt immer einen Datenverlust bei den batteriegepufferten Komponenten mit sich. Sichern Sie deshalb vor dem Batteriewechsel die betroffenen Daten.

- Tauschen Sie die Batterie aus, bevor sieben Jahre reiner Betriebsdauer verstrichen sind.

- Es darf nur der Batterietyp verwendet werden, der auch bereits eingesetzt ist.

- Verwenden Sie zum Batteriewechsel geeignetes Werkzeug.

- Installieren Sie die Batterie so, dass der Punkt auf der Batterie den Punkt auf dem Chip bedeckt.

#### Umweltschutz

Entsorgen Sie alte Boards gemäß der in Ihrem Land gültigen Gesetzgebung, wenn möglich umweltfreundlich.

xxviii SPARC/CPU-54

# 1

# Introduction

Introduction Features

#### **Features**

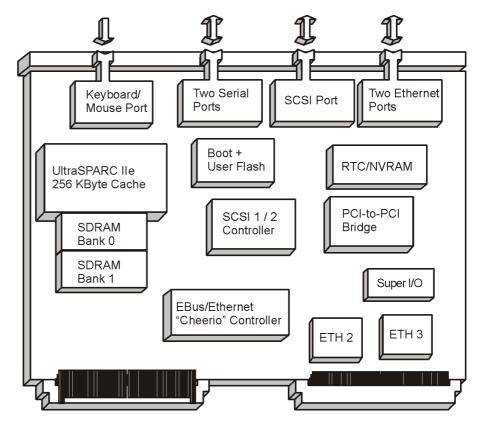

The SPARC/CPU-54 is the successor of the SPARC/CPU-50. It is a single-board computer with a processor frequency of 500 MHz and is designed in the 6U VMEbus form factor. It includes a PCI bus subsystem with 32-bit/33 MHz. On-board are:

- Hardware monitor for observing board temperature

- OpenBoot diagnostics

- Universe II PCI-to-VMEbus

- PCIO chip with interfaces to the Ebus

- Ethernet "Cheerio" controller

- Program-readable registers for board information block (BIB)

- System configuration registers

The figure shows the major function blocks of the SPARC/CPU-54.

Figure 1: Function Blocks

SPARC/CPU-54 1 - 3

Features Introduction

#### **CPU**

The UltraSPARC-IIe CPU with 500 MHz has sensors for observing the CPU on-die temperature and provides the following features:

- Four-way superscalar processor

- SPARC V9 Architecture with the VIS instruction set

- 64-bit data path and 44-bit address pointers

- 16 KByte instruction cache

- 16 KByte non-blocking primary data cache

- 256 KByte L2-Cache memory

#### **Memory**

Memory features include:

- 128 to 512 MByte on-board SDRAM

- 128 to 1536 MByte SDRAM memory module

- 1 MByte boot PROM

- Internal memory controller support of up to 2 GB SDRAM

- · Supports up to 4 MByte user flash

#### **OpenBoot**

OpenBoot serves as a boot device and provides the setup for the VME-bus interface. For further details, refer to the "OpenBoot Firmware" section on page 4-1.

1 - 4 SPARC/CPU-54

Introduction Block Diagram

# **Block Diagram**

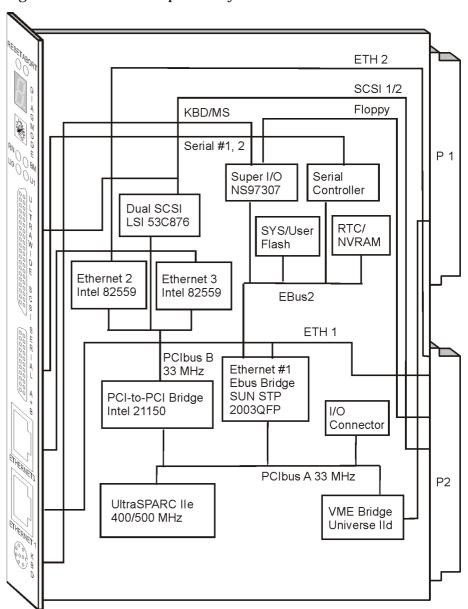

The block diagram shows how the devices of the SPARC/CPU-54 work together and which data paths they use.

Figure 2: Block Diagram of the CPU Board

SPARC/CPU-54 1 - 5

CPU Board Variants Introduction

#### **CPU Board Variants**

The SPARC/CPU-54 is available as CPU board and also in combination with the I/O-54. If combined with the I/O-54, the SPARC/CPU-54 is called SPARC/CPU-54T and allows the installation of PMC modules.

#### SPARC/CPU-54

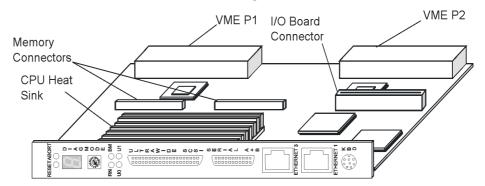

The SPARC/CPU-54 consists of a single-slot CPU board.

Figure 3: SPARC/CPU-54

1 - 6 SPARC/CPU-54

Introduction CPU Board Variants

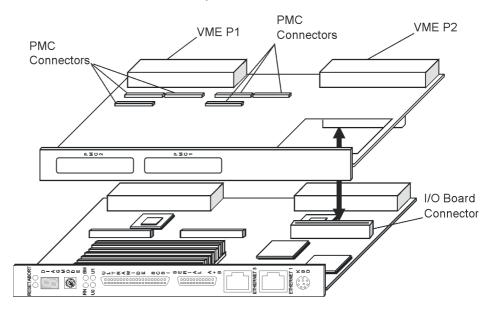

#### SPARC/CPU-54T

The SPARC/CPU-54T consists of a single-slot CPU board and a single-slot I/O-54, which allows to mount two PMC modules. For further information on the I/O board, refer to the *IO-54 Installation Guide*.

Figure 4: SPARC/CPU-54T

SPARC/CPU-54 1 - 7

Standard Compliance Introduction

# **Standard Compliance**

The CPU board was designed to comply with the standards listed below.

Note: The board is not compliant to EN 55022 if you connect a SCSI device to the SCSI connector on the front panel.

Table 1:

Standard Compliance

| Standard                                                                 | Description                                                                                                                                                                   |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEC 68-2-1/2/3/13/14                                                     | Climatic environmental requirements. The SPARC/CPU-54 can only be used in an restricted temperature range (see Table 6 "Environmental Requirements" on page 2-4) for details. |

| IEC 68-2-6/27/32                                                         | Mechanical environmental requirements                                                                                                                                         |

| EN 609 50/UL 1950<br>(predefined Force system);<br>UL 94V-0/1            | Legal safety requirements                                                                                                                                                     |

| EN 55022,<br>EN 55024,<br>FCC Part 15 Class A                            | EMC requirements on system level                                                                                                                                              |

| ANSI/IPC_A-610 Rev. C<br>ANSI/IPC-7711<br>ANSI/IPC-7721<br>ANSI-J-001003 | Manufacturing requirements                                                                                                                                                    |

| ISO 8601                                                                 | Y2K compliance                                                                                                                                                                |

1 - 8 SPARC/CPU-54

Introduction Ordering Information

# **Ordering Information**

When ordering board variants, upgrades, and accessories, use the order numbers given below.

## **Product Nomenclature**

In the following table you find the key for the product name extensions. **Table 2:** *Product Nomenclature*

| SPARC/CPU-54(T)/mmm-sss-c-uu |                                |  |  |

|------------------------------|--------------------------------|--|--|

| mmm                          | SDRAM capacity in MByte        |  |  |

| SSS                          | CPU speed in MHz               |  |  |

| c                            | L2-cache                       |  |  |

| uu                           | User flash EPROM size in MByte |  |  |

Ordering Information Introduction

## **Order Numbers**

The table below is an excerpt from the board's ordering information. Ask your local Force Computers representative for the current SPARC/CPU-54 ordering information.

**Table 3:** Excerpt from the SPARC/CPU-54 Ordering Information for CPU Boards<sup>1)</sup>

| Order No. | SPARC/CPU-54     | Description                             |

|-----------|------------------|-----------------------------------------|

| 110540    | /128-500-1-4/R2  | 128 MByte CPU board memory (2 banks,    |

|           |                  | 64 MBit devices); 500 MHz CPU with      |

|           |                  | 256 KByte Cache; 4 MByte user flash     |

| 110541    | /512-500-1-4/R2  | 512 MByte CPU board memory (2 banks,    |

|           |                  | 256 MBit devices); 500 MHz CPU with     |

|           |                  | 256 KByte Cache; 4 MByte user flash     |

| 110542    | T/128-500-1-4/R2 | 128 MByte CPU board memory (2 banks,    |

|           |                  | 256 MBit devices); 500 MHz CPU with     |

|           |                  | 256 KByte cache; 4 MByte user flash and |

|           |                  | I/O-54 (two PMC slots)                  |

| 110543    | T/512-500-1-4/R2 | 512 MByte CPU board memory (2 banks,    |

| 110010    |                  | 256 MBit devices); 500 MHz CPU with     |

|           |                  | 256 KByte cache; 4 MByte user flash and |

|           |                  | I/O-54 (two PMC slots)                  |

<sup>1)</sup> Status: May 2003

**Table 4:** Excerpt from the SPARC/CPU-54 Ordering Information for Memory Modules <sup>1)</sup>

| Order No. | SPARC/       | Description                                   |

|-----------|--------------|-----------------------------------------------|

| 107463    | /MEM-54/128  | 128 MByte memory (2 banks, 64 MBit devices)   |

| 107464    | /MEM-54/512  | 512 MByte memory (2 banks, 256 MBit devices)  |

| 107465    | /MEM-54/1024 | 1024 MByte memory (4 banks, 256 MBit devices) |

| 107466    | /MEM-54/1536 | 1536 MByte memory (6 banks, 256 MBit devices) |

<sup>1)</sup> Status: May 2003

1 - 10 SPARC/CPU-54

Introduction Ordering Information

**Table 5:** Excerpt from the SPARC/CPU-54 Ordering Information for Accessories <sup>1)</sup>

| Order No. | SPARC/                        | Description                                                              |

|-----------|-------------------------------|--------------------------------------------------------------------------|

| 108771    | IOBP-54/3                     | 3-row I/O panel for the CPU-54 and I/O-54 with 3-row P2 connector pinout |

| 108772    | IOBP-54/5                     | 5-row I/O panel for the CPU-54 and I/O-54 with 5-row P2 connector pinout |

| 108773    | /CPU-54/AccKit/3              | IOBP-54/3 with cables                                                    |

| 108774    | /CPU-54/AccKit/5              | IOBP-54/5 with cables                                                    |

| 105608    | /Sol/Drv/Rel.2.x              | Solaris driver package                                                   |

| 107470    | Tornado 2.0 BSP for<br>CPU-54 | Tornado 2.0 board support package                                        |

<sup>1)</sup> Status: May 2003

Ordering Information Introduction

1 - 12 SPARC/CPU-54

# 2

# Installation

Installation Action Plan

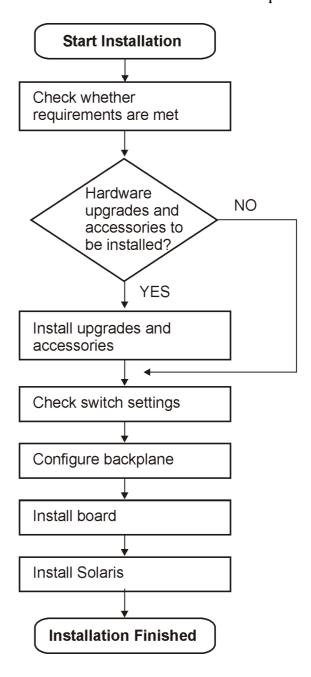

## **Action Plan**

In order to install the board, the following steps are necessary and will be described in further detail in the sections of this chapter.

Requirements Installation

# Requirements

In order to meet the environmental requirements, the CPU board has to be tested in the system in which it is to be installed.

Before you power up the board, calculate the power needed according to your combination of board upgrades and accessories.

## **Environmental Requirements**

The environmental conditions must be tested and proven in the used system configuration. The conditions refer to the surrounding of the board within the user environment.

Note: Operating temperatures refer to the temperature of the air circulating around the board and not to the actual component temperature.

## Caution

- To ensure that the operating conditions are met, forced air cooling is required within the chassis environment.

- Do not operate the SPARC/CPU-54 outside the specified environmental limits. High humidity and condensation may cause short circuits. Make sure the product is completely dry and there is no moisture on any surface before applying power. Do not operate the product below 0°C.

Table 6: Environmental Requirements

| Feature        | Operating                                                   | Non-Operating                                      |

|----------------|-------------------------------------------------------------|----------------------------------------------------|

| Temperature    | 0°C to +55°C                                                | -40°C to +85°C                                     |

| Forced airflow | 300 LFM (linear feet per minute)                            | -                                                  |

| Temp. change   | +/- 0.5°C/min                                               | +/- 1.0°C/min                                      |

| Rel. humidity  | $5\%$ to $95\%$ non-condensating at $+40^{\circ}\mathrm{C}$ | $5\%$ to $95\%$ non-condensating at $+40^{\circ}C$ |

| Altitude       | -300 m to + 3,000 m                                         | -300 m to +13,000 m                                |

2 - 4 SPARC/CPU-54

Installation Requirements

| Table 6: Environmenta | l Requirements ( | cont.) |

|-----------------------|------------------|--------|

|-----------------------|------------------|--------|

| Feature                                  | Operating             | Non-Operating                                  |

|------------------------------------------|-----------------------|------------------------------------------------|

| Vibration<br>10 to 15 Hz<br>15 to 150 Hz | 2 mm amplitude<br>2 g | 5 mm amplitude<br>5 g                          |

| Shock                                    | 5g/11 ms halfsine     | 15g/11 ms halfsine                             |

| Free fall                                | 100 mm / 3 axes       | 1200 mm / all edges and corners (packed state) |

## **Power Consumption**

The SPARC/CPU-54 power consumption depends on the installed hardware accessories. In the following table you will find typical examples of power consumption without any accessories installed. If you want to install accessories on the SPARC/CPU-54, the load of the respective accessory has to be added to the used SPARC/CPU-54 variant. For information on the accessories' power consumption, refer to the documentation delivered together with the respective accessory or consult your local Force Computers representative for further details.

The installation of the SPARC/CPU-54 requires:

- +5V power supply

- Minimum airflow meeting the thermal requirements (see Table 6 "Environmental Requirements" on page 2-4)

- One slot of a VMEbus backplane with P1 and P2 connectors

The installation of the SPARC/CPU-54T requires:

- +5V and +12V power supply

- Minimum airflow meeting the thermal requirements (see Table 6 "Environmental Requirements" on page 2-4)

- Two slots of a VMEbus backplane with P1 and P2 connectors

Requirements Installation

The power supply has to meet the requirements given in the tables below.

**Table 7:** Maximum Power Consumption

| CPU Board                     | +5V  | +12V  | Major Components                                     |

|-------------------------------|------|-------|------------------------------------------------------|

| SPARC/CPU-54/<br>128-400-1-4  | 4.5A | n.a.  | CPU-54 400 MHz, 128 MByte<br>SDRAM                   |

| SPARC/CPU-54/<br>512-500-1-4  | 5.0A | n.a.  | CPU-54 500 MHz, 512 MByte<br>SDRAM                   |

| SPARC/CPU-54T/<br>128-400-1-4 | 6.0A | 500mA | CPU-54 400 MHz, 128 MByte<br>SDRAM, including I/O-54 |

| SPARC/CPU-54T/<br>512-500-1-4 | 7.5A | 500mA | CPU-54 500 MHz, 512 MByte<br>SDRAM, including I/O-54 |

**Table 8:** Maximum Power Consumption with SPARC/MEM-54 Installed

| MEM Board         | + <b>5V</b> | +12V | Major Components  |

|-------------------|-------------|------|-------------------|

| SPARC/MEM-54/128  | 1A          | n.a. | 128 MByte, SDRAM  |

| SPARC/MEM-54/1536 | 1.3A        | n.a. | 1536 MByte, SDRAM |

## Caution

In order to protect its components, the SPARC/CPU-54 only powers up if the 5V supply voltage is stable and within its limits. The SPARC/CPU-54T only powers up if the 5V and 12V supply voltages are stable and within their limits. This is in compliance with the VMEbus specification. However, there are systems which are not fully VMEbus-compliant. The power supplies of these systems do not turn on the 12V supply if the 5V supply has not been loaded before. Use a VMEbus board in the system which loads the 5V to prevent such systems from running into a power-up deadlock.

2 - 6 SPARC/CPU-54

Installation Requirements

## **Software Requirements**

If you wish to use one of the SPARC/CPU-54 devices listed below you need to install the Force Computers Solaris Driver Package Version 2.11 or higher:

- Intel 82559 Ethernet device

- Universe II PCI-to-VMEbus bridge

- On-board Flash memory

- Temperature sensors, LEDs, seven-segment display, watchdog and floppy ejection

For information on which drivers have to be installed and on the driver package itself, refer to the "Installing Solaris" section on page 2-19 and to the *Solaris Driver Package Installation Guide*.

# Hardware and Software Upgrades and Accessories

The following upgrades and accessories are available for the SPARC/CPU-54:

- SPARC/MEM-54 memory module

- IO-54

- IOBP-54

- Solaris Driver Package

## **Memory Modules**

The main memory capacity is adjustable via installation of the Force Computers memory module SPARC/MEM-54. The following memory module variants are available:

- SPARC/MEM-54/128 with 128 MByte additional memory

- SPARC/MEM-54/512 with 512 MByte additional memory

- SPARC/MEM-54/1024 with 1024 MByte additional memory

- SPARC/MEM-54/1536 with 1536 MByte additional memory

For installation information, see the SPARC/MEM-54 Installation Guide.

#### **IO-54**

The SPARC/CPU-54T includes an I/O board, the SPARC/IO-54, which can be plugged onto the CPU board. The SPARC/IO-54 serves as a carrier board and provides connectors for two PMC modules

Note: The I/O board has to be mounted on the CPU board before the CPU board is installed into the system.

For further information, refer to the IO-54 Installation Guide.

2 - 8 SPARC/CPU-54

## SPARC/IOBP-54

As a separate price list item an I/O back panel is available for the CPU board, the SPARC/IOBP-54. It is part of the SPARC/CPU-54/AccKit3/5 Accessory Kit. The SPARC/IOBP-54 provides access to the CPU board's user I/O interfaces via industry standard connectors.

Note: The IOBP has to be connected to the CPU board after it has been installed in the system.

For further information, refer to the *IOBP-54 Installation Guide*.

#### Caution

- The SPARC/IOBP-54 is especially designed for the SPARC/CPU-54. Do not use any other I/O back panels on the SPARC/CPU-54. Otherwise, the board may be damaged.

- The IOBP-54 provides automatic SCSI termination. Therefore, SW5-2 on the CPU board must be configured appropriately to disable the corresponding backplane SCSI termination.

## **Solaris Driver Package**

Force Computers provides a Solaris driver package which supports the following devices and features of the SPARC/CPU-54:

- Intel 82559 Ethernet device

- Universe II PCI-to-VMEbus bridge

- On-board flash memory

- Temperature sensors, LEDs, seven-segment display, watchdog and floppy ejection

If you wish to use one of these devices you need to install the Force Computers Solaris Driver Package Version 2.11 or higher.

For information on which drivers have to be installed and on the driver package itself, refer to the "Installing Solaris" section on page 2-19 and to the *Solaris Driver Package Installation Guide*.

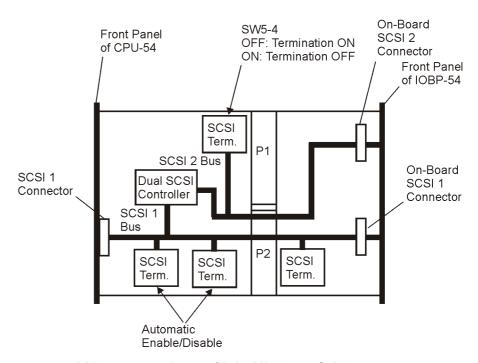

## **Setting the SCSI Termination**

The SPARC/CPU-54 provides two Ultra Wide SCSI buses. SCSI 1 is accessible via the front panel and the backplane via the IOBP-54. SCSI 2 is available via the backplane via the IOBP-54. The SPARC/CPU-54 enables and disables the SCSI termination automatically according to the board's position in the SCSI bus, if switch SW5 is set to the respective default settings.

## **SCSI 1 Termination**

The SCSI 1 bus is available via the front panel connector and via the VMEbus P2 connector and the IOBP-54. By default, switch SW5-2 is set to OFF and switch SW5-3 is set to ON to enable automatic termination of the SCSI bus 1. To guarantee proper termination, leave switches in the mentioned position.

Caution

Only connect the SCSI cable at its end connectors and never at its middle connectors. Otherwise, data may be lost.

## **SCSI 2 Termination**

#### Caution

If you use a flat ribbon T-cable at the SCSI 2 bus, the termination of SCSI 2 has to be set manually to prevent data transmission errors. Before installing the board, check Figure 5 "SCSI Termination Concept of SPARC/CPU-54 and IOBP-54" on page 2-11 whether this applies to your planned configuration.

The SCSI 2 bus is only available via the VMEbus P2 connector and can only be terminated manually. The following options apply:

- The SCSI 2 connector on the IOBP is connected to SCSI devices. The switch SW5-4 must be set to the OFF position which enables the termination on the CPU board.

- The SCSI 2 connector on the IOBP is connected to SCSI devices, but a flat ribbon T-cable is used. The switch SW5-4 must be set to the ON position which disables the termination on the CPU board.

2 - 10 SPARC/CPU-54

The figure below shows the SCSI bus termination concept on the SPARC/CPU-54 and the IOBP-54.

Figure 5: SCSI Termination Concept of SPARC/CPU-54 and IOBP-54

Switch Settings Installation

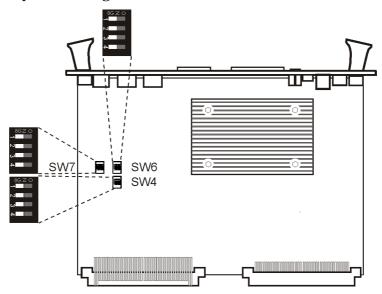

# **Switch Settings**

## Caution

The switch settings have to be checked and changed before the board installation. Do not set/reset the switches during operation. Otherwise, the board is damaged.

The SPARC/CPU-54 provides five configuration switches: SW4, SW5, SW6, SW7, and SW800. Switches SW4, SW6 and SW7 are located on the top side (see figure below).

Figure 6: Location of Switches on Board's Top Side

2 - 12 SPARC/CPU-54

Installation Switch Settings

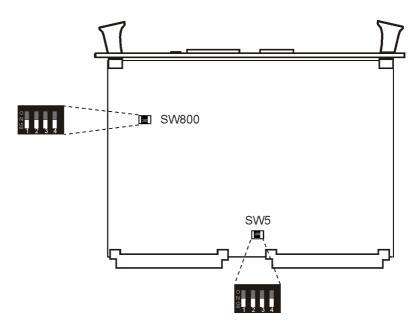

The switches SW5 and SW800 are located on the bottom side of the board.

Figure 7: Location of Switches on Board's Bottom Side

Table 9:

Switch Settings

| Switch     | No. | Description                                |

|------------|-----|--------------------------------------------|

| SW4        | 1   | Abort key control                          |

| 8G ZO      |     | OFF (default): ABORT key enabled           |

| N <b>E</b> |     | ON: ABORT key disabled                     |

| ω          | 2   | Reset key on front panel control           |

| 4          |     | OFF (default): RESET key enabled           |

|            |     | ON: RESET key disabled                     |

|            | 3   | Flash EPROM write protection               |

|            |     | OFF (default): Flash EPROM write protected |

|            |     | ON: Flash EPROM write enabled              |

|            | 4   | Reserved                                   |

Switch Settings Installation

Table 9:

Switch Settings (cont.)

| Switch                                                                          | No. | Description                                                                                                                       |

|---------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|