# SYS68K/WFC-1

# USER'S MANUAL

Third Edition April 1986 PART NO. 800009

FORCE COMPUTERS Inc./GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted. Copyright by FORCE Computers®

## <u>NOTE</u>

The information in this document has been carefully checked and is believed to be entirely reliable. FORCE COMPUTERS makes no warranty of any kind with regard to the material in this document, and assumes no responsibility for any errors that may appear in this document. FORCE COMPUTERS reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance or design.

FORCE COMPUTERS assumes no responsibility for the use of any circuitry other than circuitry which is part of a product of FORCE COMPUTERS GmbH/Inc.

FORCE COMPUTERS does not convey to the purchaser of the product described herein any license under the patent rights of FORCE COMPUTERS GmbH/Inc. nor the rights of others.

FORCE COMPUTERS Inc. 727 University Avenue Los Gatos, CA 95030 U.S.A. Phone : (408) 354 34 10 Telex : 172465 FAX : (408) 395 77 18

FORCE COMPUTERS GmbH Daimlerstrasse 9 D-8012 Ottobrunn/Munich West Germany

Phone : (089) 600 91-0 Telex : 524190 forc-d FAX : (089) 609 77 93

FORCE COMPUTERS FRANCE Sarl ll, rue Casteja 92100 Boulogne France

Phone : (1) 4620 37 37 Telex : 206 304 forc-f Fax : (1) 4621 35 19

Table of Contents

,

Page

|       |                                  | Paye |

|-------|----------------------------------|------|

| 1.Ø   | General Information              | 8    |

| 2.0   | General Operation                | . 11 |

| 2.1   | Features of the SYS68K/WFC-1     | 12   |

| 3.Ø   | Hardware Overview                | 13   |

| 3.1   | Global Base Address Selection    | 13   |

| 3.2   | Address Modifier Decoding        | 16   |

| 3.3   | Interrupt Jumpering              | 18   |

| 3.4   | Connectors Organisation          | 22   |

| 3.5   | Winchester Drive Control Signals | 24   |

| 3.6   | Winchester Control Connectors    | 26   |

| 3.7   | Winchester Drive Data Connector  | 27   |

| 3.8   | Floppy Drive Signals             | 28   |

| 3.9   | Floppy Drive Control Connector   | 29   |

| 3.10  | Run/Local Switch                 | 31   |

| 3.11  | LED Indicators                   | 31   |

| 3.12  | Access Times                     | 33   |

| 4.Ø   | SYS68K/WFC-1 Register Set        | 4Ø   |

| 4.1   | Register Set Basics              | 40   |

| 4.2   | Address Map                      | 40   |

| 4.3   | Data Register                    | 41   |

| 4.4   | Error Register                   | 41   |

| 4.4.1 | Diagnostic Errors                | 43   |

| 4.5   | Precomponsation Register         | 43   |

| 4.6   | Sector Count Register            | 43   |

| 4.7   | Sector Number Register           | 44   |

| 4.8   | Cylinder Number Register         | . 44 |

| 4.9   | Size Drive Head Register         | 44   |

۰.

Table of Contents contd.

Page

| 4.10    | Status Register            | 47 |

|---------|----------------------------|----|

| 4.11    | Command Register           | 48 |

| 4.12    | Interrupt Vector Registers | 48 |

| 5.Ø     | Commands                   | 49 |

| 5.1     | General                    | 49 |

| 5.2     | Commands Summary           | 49 |

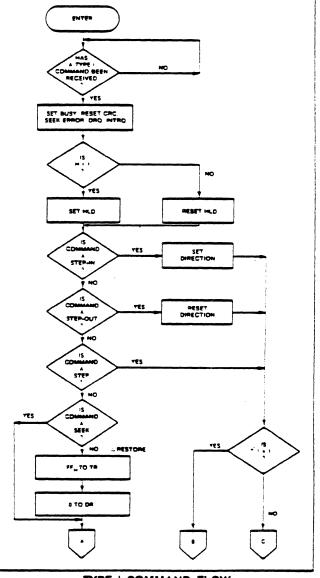

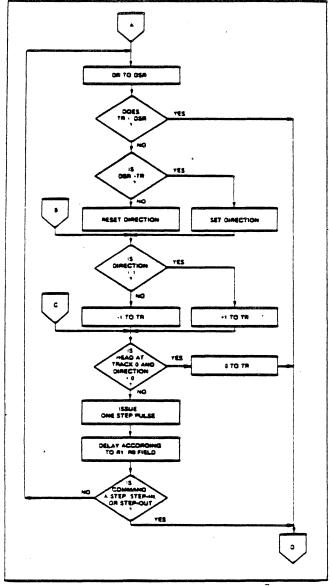

| 5.3     | Type I Commands            | 51 |

| 5.3.1   | Test                       | 51 |

| 5.3.2   | Restore                    | 51 |

| 5.3.3   | Seek                       | 52 |

| 5.4     | Type II Comands            | 52 |

| 5.4.1   | Read Sector                | 52 |

| 5.4.1.1 | DMA Read                   | 53 |

| 5.4.1.2 | Normal Completion          | 53 |

| 5.5     | Type III Comands           | 53 |

| 5.5.1   | Write Sector               | 54 |

| 5.5.2   | Format Track               | 54 |

| 6.Ø     | Programming                | 55 |

| 6.1     | General                    | 55 |

| 6.2     | Setting Register Set       | 55 |

| 6.2.1   | Cylinders and Tracks       | 56 |

| 6.3     | Type I Command Programming | 56 |

| 6.3.1   | Use of Busy Bit            | 57 |

| 6.3.2   | Use of Interrupts          | 57 |

| 6.3.3   | Use of the Error Bit       | 57 |

| 6.4     | Type II Commands           | 58 |

| 6.4.1   | DMA Mode                   | 58 |

# Table of Contents contd.

| 6.5      | Type II ( | Command Programmi | ng                                   | 59  |

|----------|-----------|-------------------|--------------------------------------|-----|

| 6.5.1    | Formattir | Jà                |                                      | 59  |

| 6.5.2    | Interleav | ving              |                                      | 60  |

| 6.6      | Programmi | ing Examples      |                                      | 61  |

| 6.6.1    | Read Sect | cor               |                                      | 61  |

| 6.6.2    | Write Sec | ctor              |                                      | 62  |

|          |           |                   |                                      |     |

| APPENDIX | K "A"     | Specification of  | the SYS68K/WFC-1                     | A-1 |

| APPENDIX | К, "В"    | Address Map of th | he SYS68K/WFC-1                      | B-1 |

| APPENDIX | K "C"     | SYS68K/WFC-1 Com  | ponent Part List                     | C-1 |

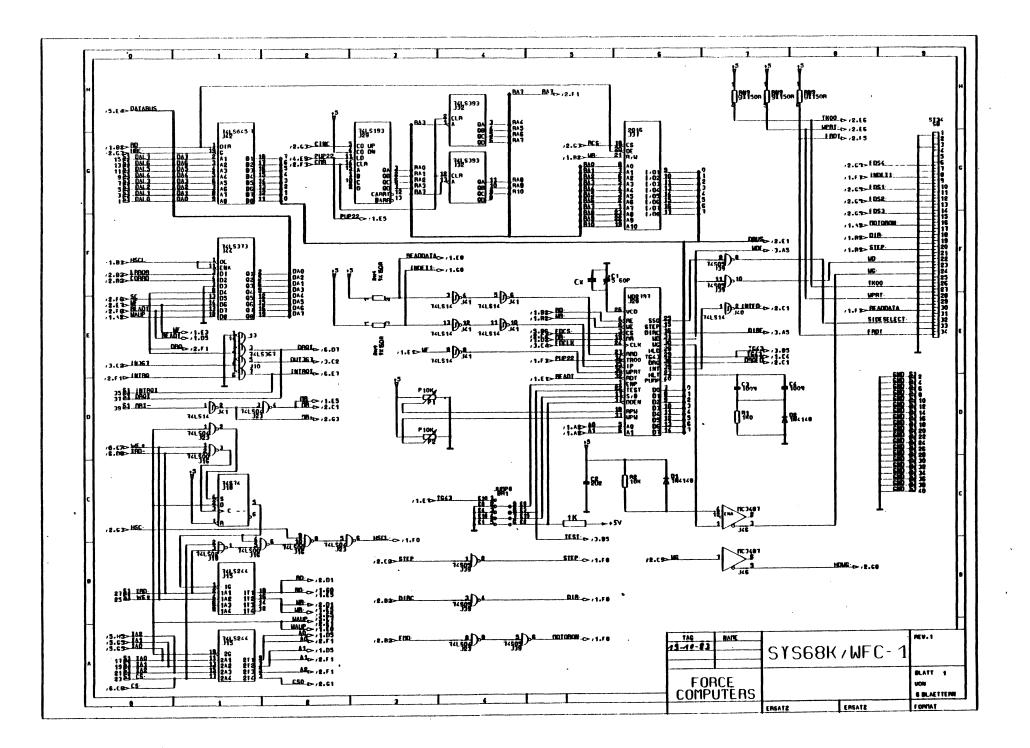

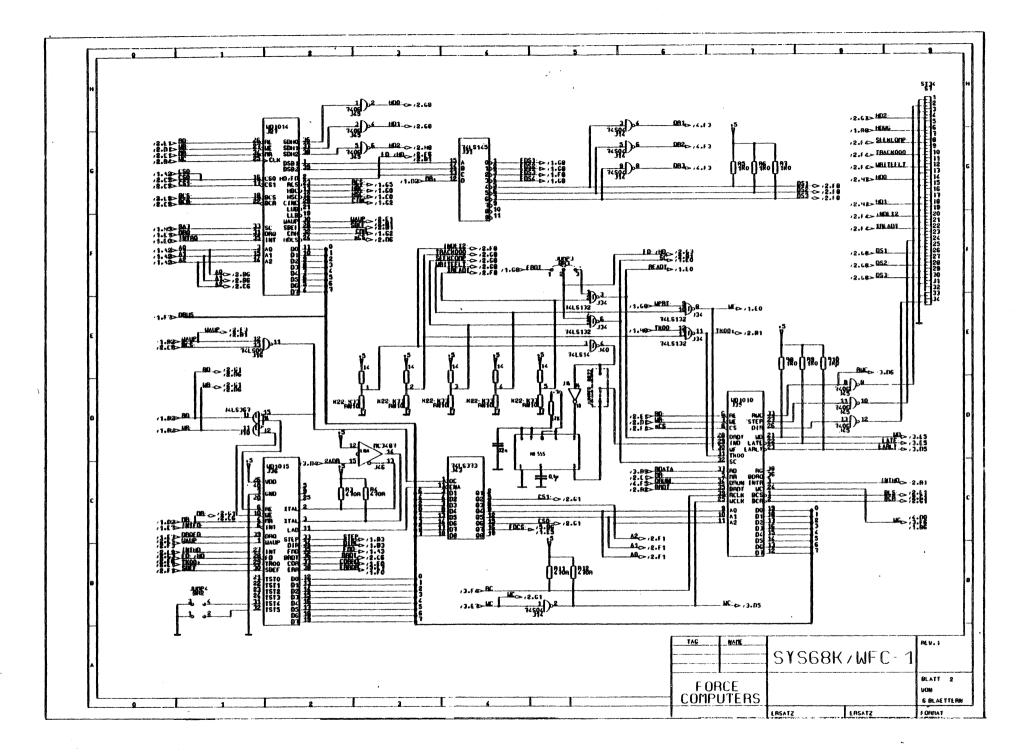

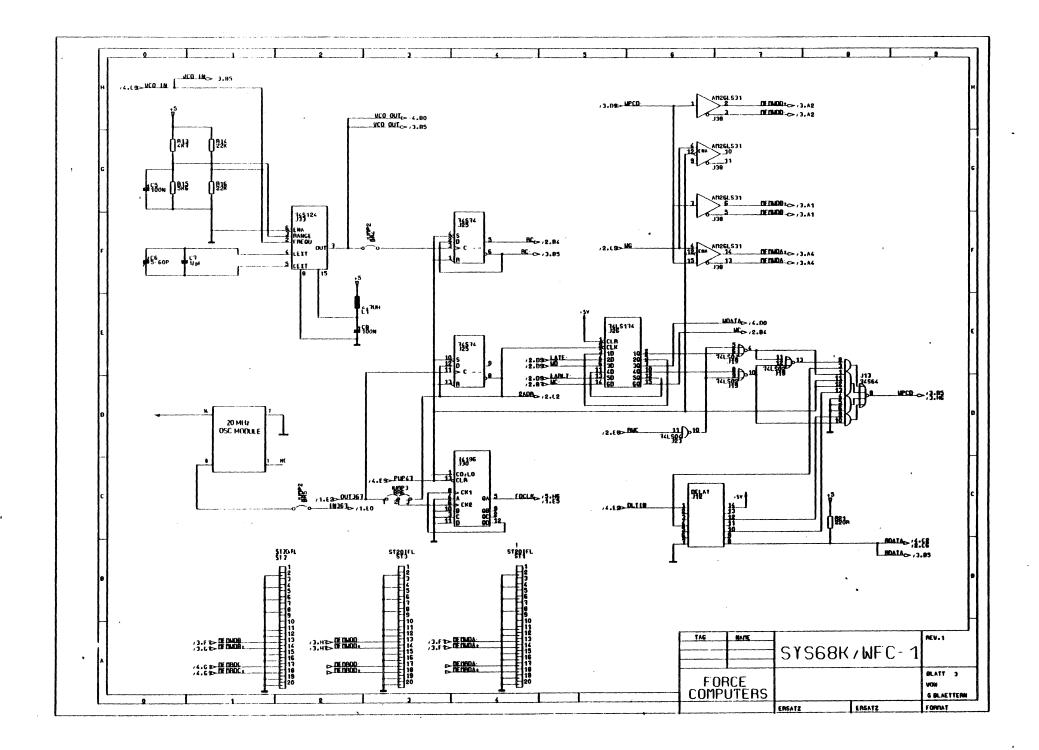

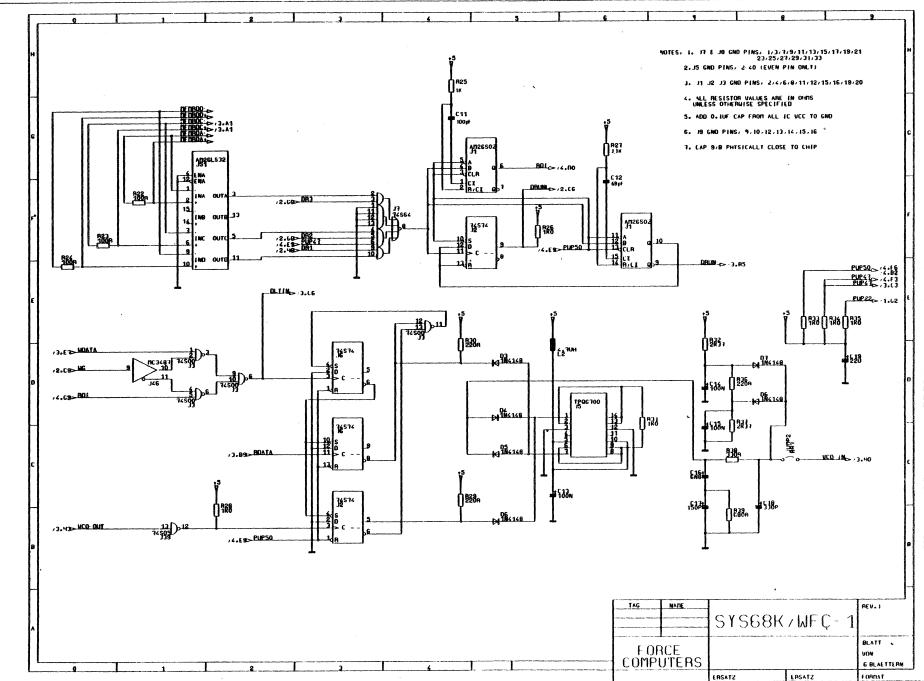

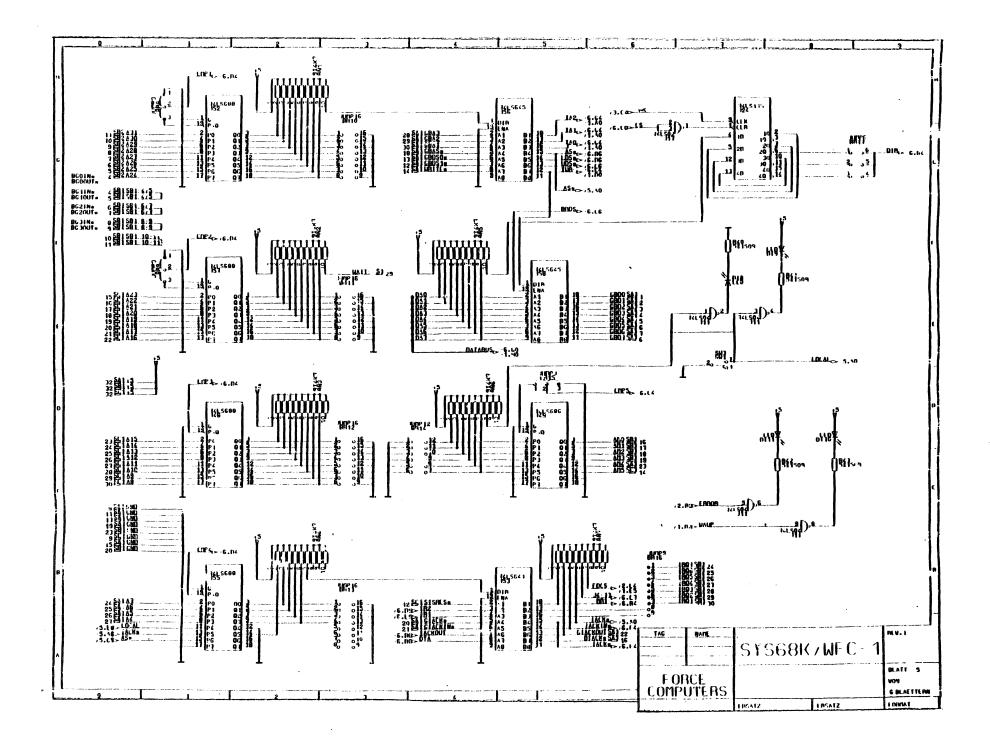

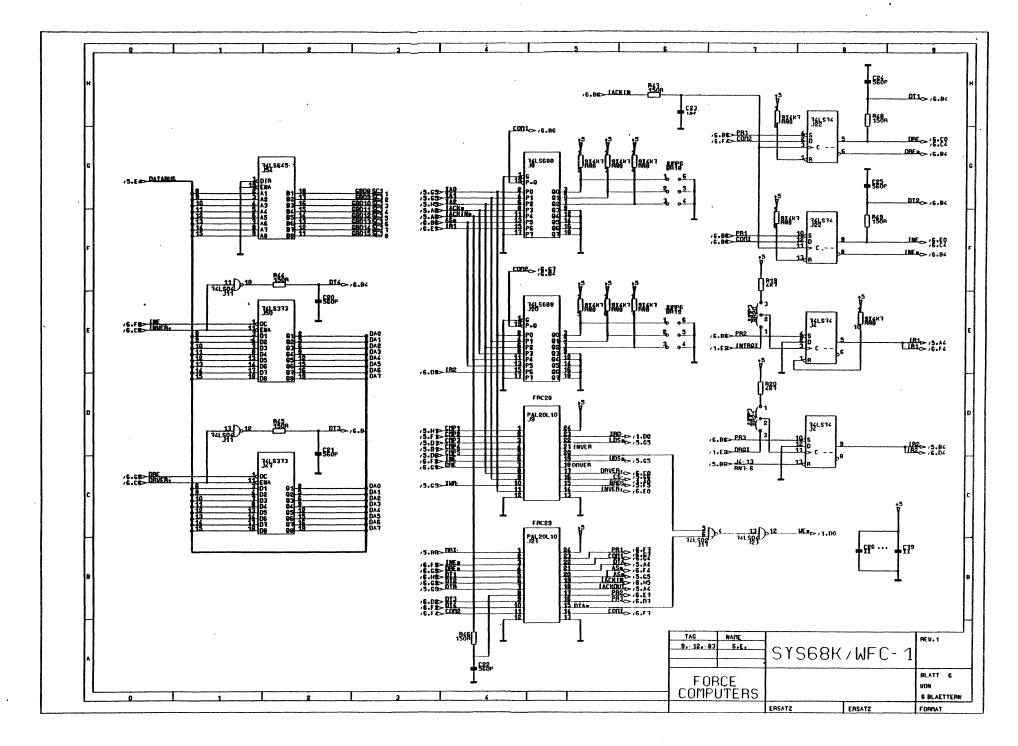

| APPENDIX | K "D"     | Circuit Schematic | cs                                   | D-1 |

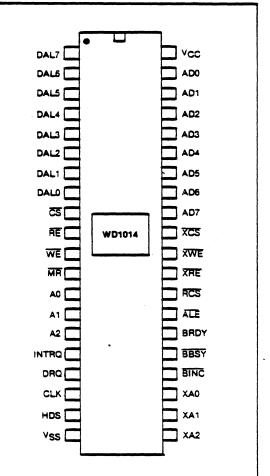

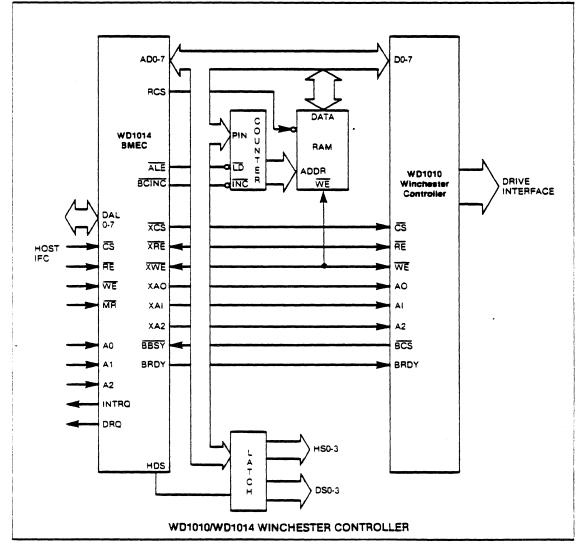

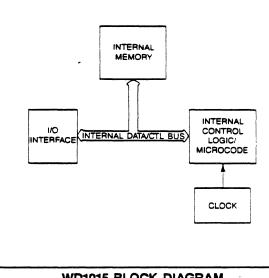

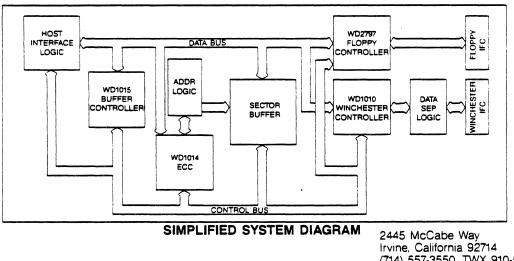

| APPENDI  | К "Е"     | 1                 | WD1010<br>WD1014<br>WD1015<br>WD2797 | E-1 |

APPENDIX "F" List of Tested Winchester/Floppy Drives F-1

# List of Figures

# Page

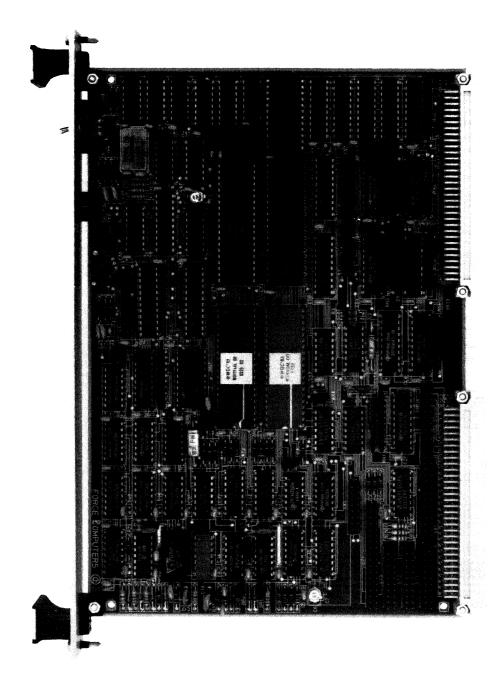

| Fig.l  | Photo of Board                             | 9  |

|--------|--------------------------------------------|----|

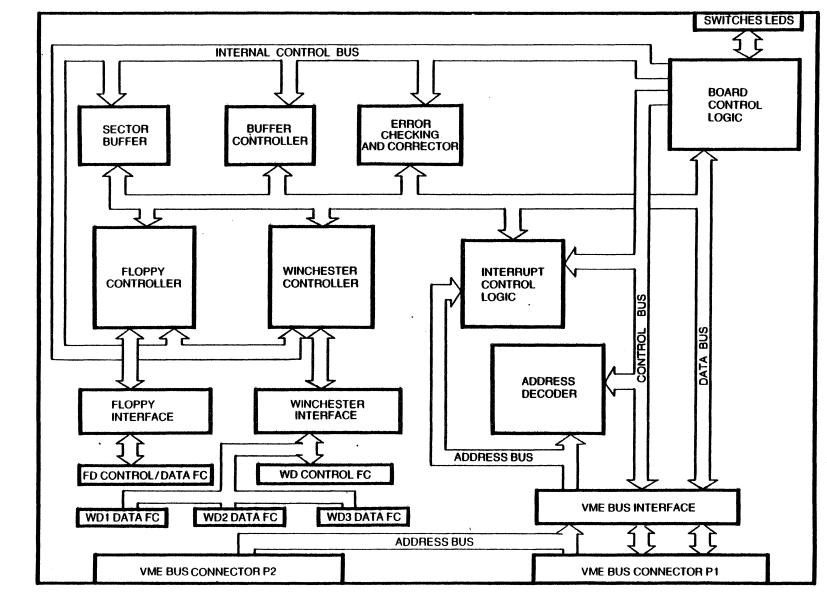

| Fig.2  | Board Block Diagram                        | 10 |

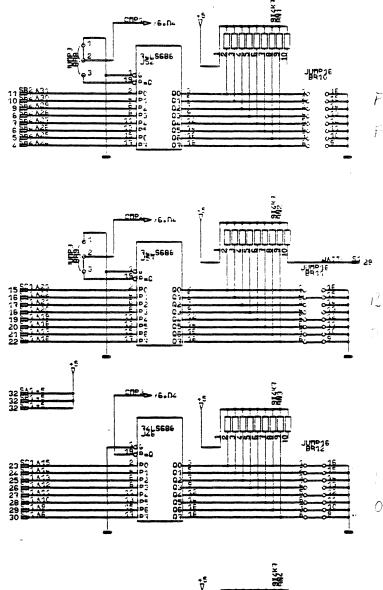

| Fig.3  | Jumper Field for Base Address Selection    | 14 |

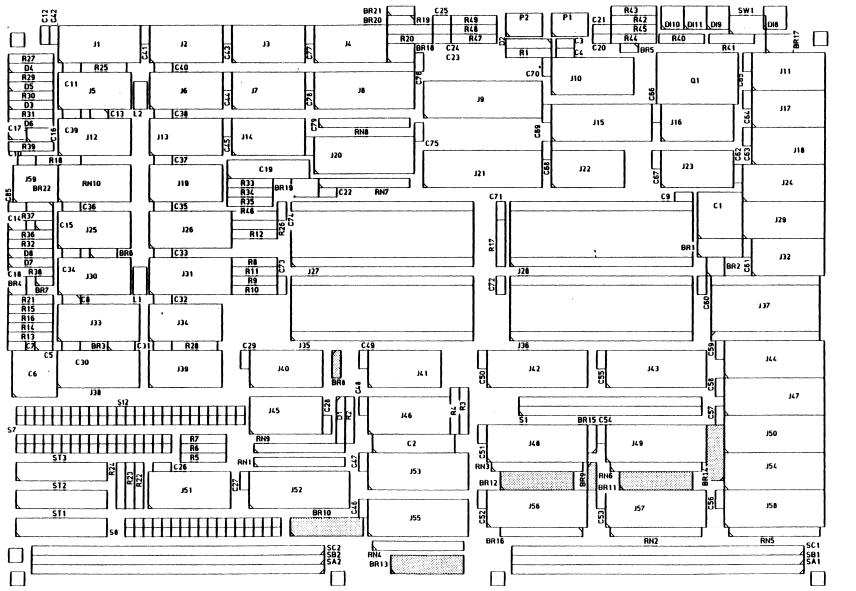

| Fig.4  | Location of the Base Address Jumper Fields | 15 |

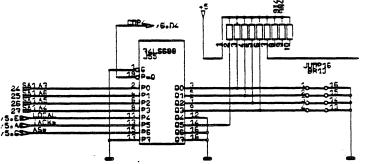

| Fig.5  | AM Jumper Fields                           | 17 |

| Fig.6  | Interrupt Jumper Fields                    | 2Ø |

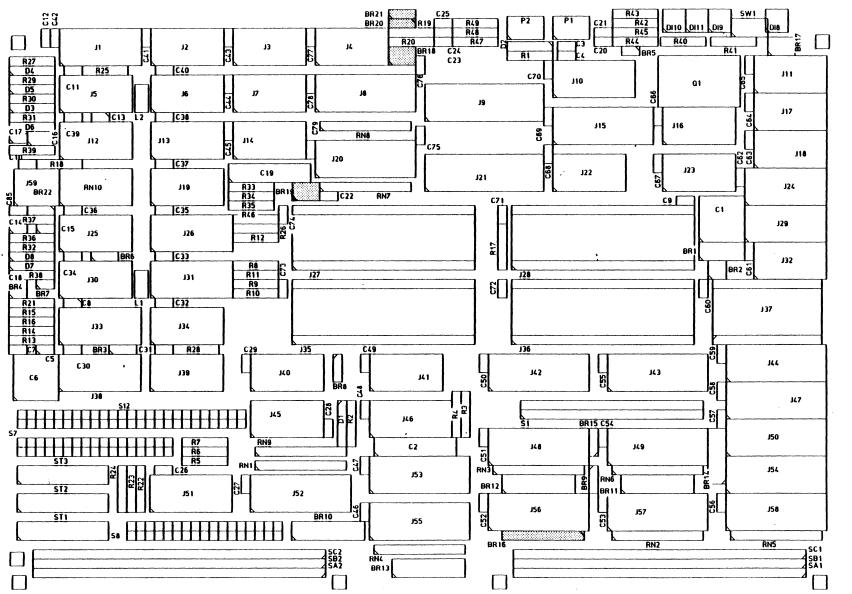

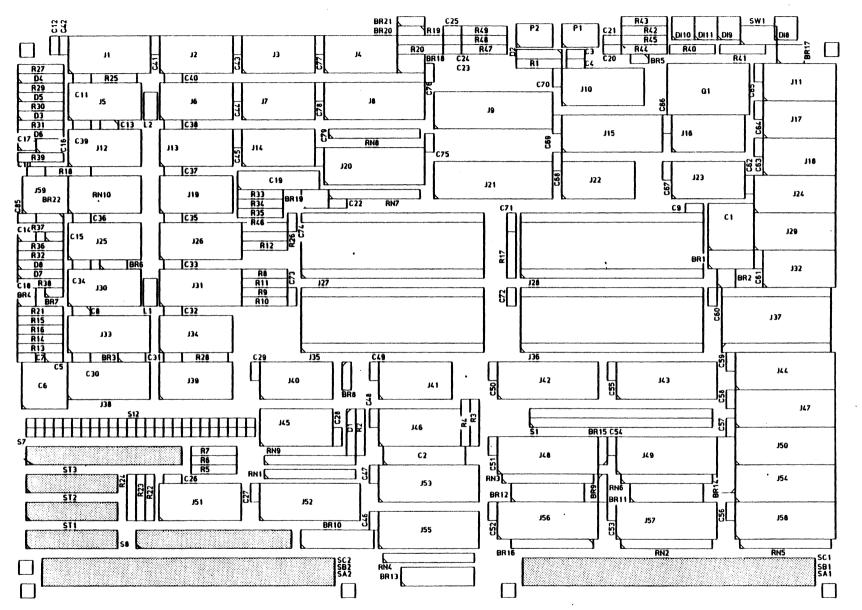

| Fig.7  | Location of the Interrupt Jumper Fields    | 21 |

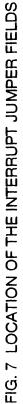

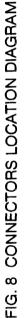

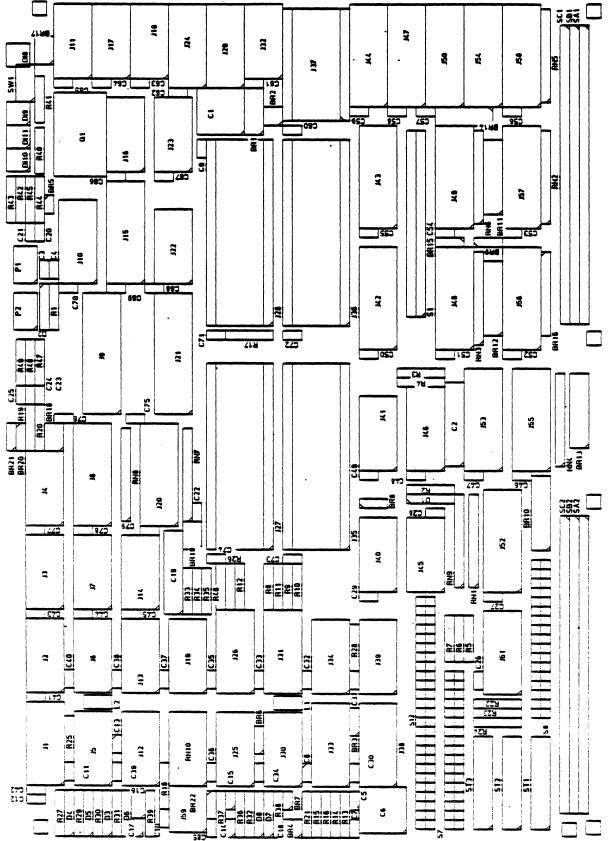

| Fig.8  | Connectors Location Diagram                | 23 |

| Fig.9  | Front Panel of the SYS68K/WFC-1            | 32 |

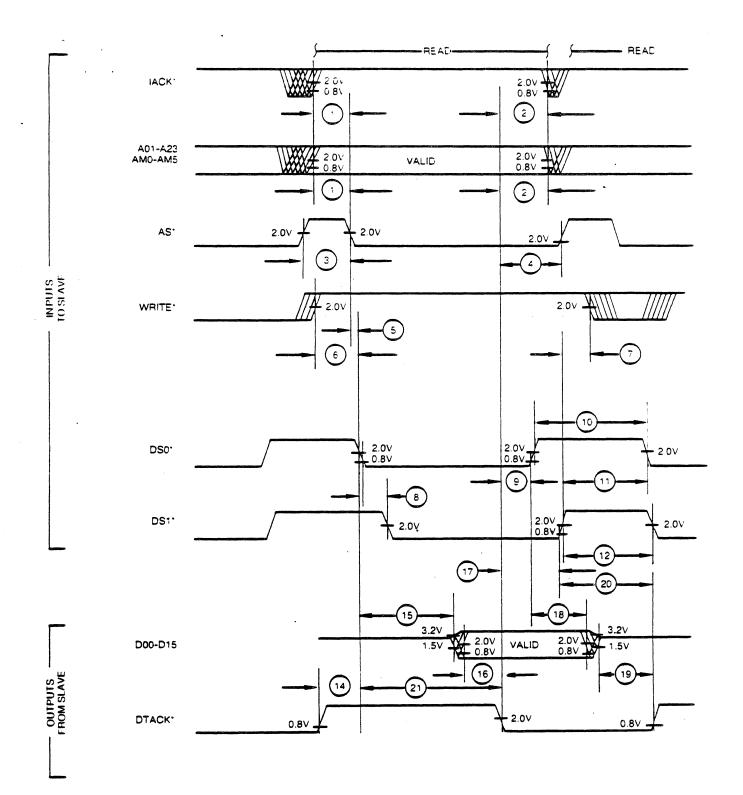

| Fig.10 | Data Transfer Bus Read Cycle Timing        | 34 |

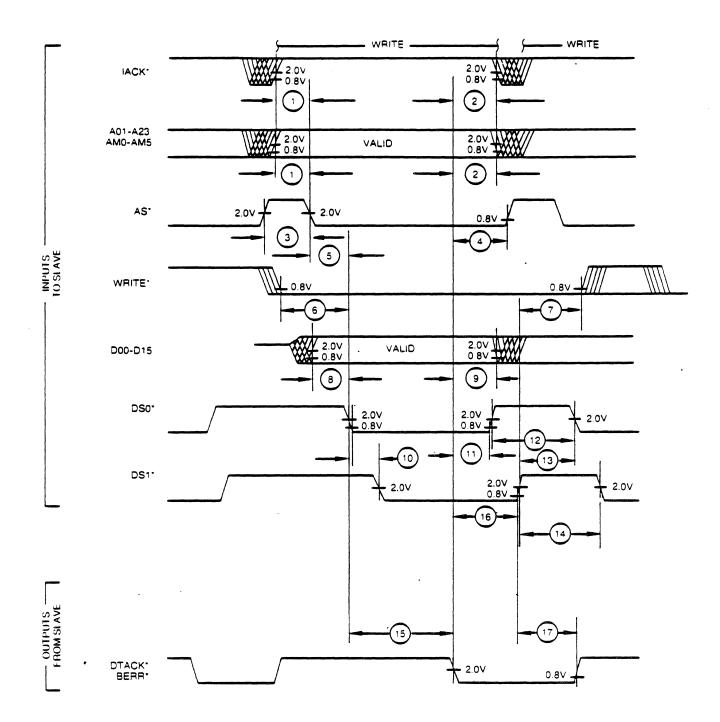

| Fig.ll | Data Transfer Bus Write Cycle Timing       | 37 |

# List of Tables

| Table | 1  | Address Modifier Codes                                | 19 |

|-------|----|-------------------------------------------------------|----|

| Table | 2  | Winchester Drive Control Connector Pin<br>Description | 26 |

| Table | 3  | Winchester Drive Data Connector Pin<br>Description    | 27 |

| Table | 4  | Floppy Drive Control Connector Pin<br>Description     | ЗØ |

| Table | 5  | Data Transfer Bus Read Time Values                    | 35 |

| Table | 6  | Data Transfer Bus Write Time Values                   | 38 |

| Table | 7  | SYS68K/WFC-l Address Map                              | 40 |

| Table | 8  | Error Register Bits                                   | 41 |

| Table | 9  | Size Drive Head Register                              | 45 |

| Table | 10 | Command Types                                         | 5Ø |

| Table | 11 | Stepping Rates                                        | 5Ø |

| Table | 12 | Interleave Table                                      | 61 |

### 1.0 General Information

The SYS68K/WFC-1 is a high performance VMEbus interface controller board to control 5 1/4" Floppy and Winchester drives.

The SYS68K/WFC-1 board has been developed to serve as a controller board for high speed data transfers to and from 5 1/4" Floppy and Winchester drives via a 1 KByte FIFO buffer. The board can communicate with a DMA controller to provide maximum bus transfer speed and is able to generate interrupts for complete operation, error operation and data request.

The VMEbus allows easy system design with extended I/O, RAM, CPU, ROM, and DMA cards.

This manual provides a general operating description of the SYS68K/WFC-1 hardware. Follow manufacturer's installation instructions for use and trouble shooting.

# FIG. 1 PHOTO OF BOARD

SYS68K/WFC-1

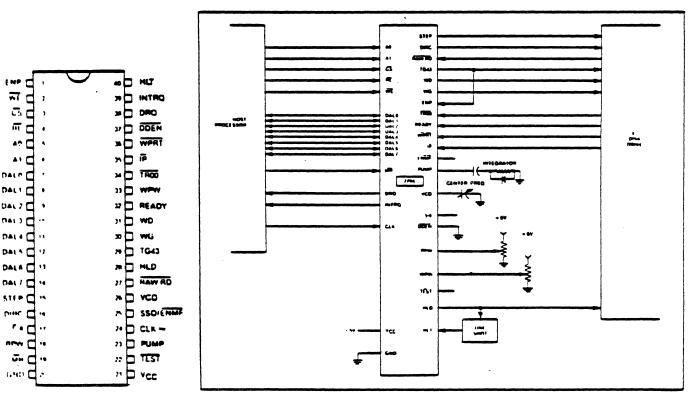

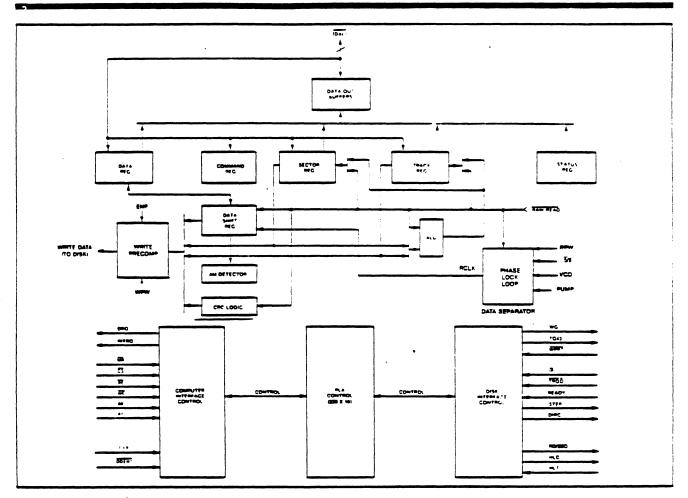

FIG. 2 BOARD BLOCK DIAGRAM SYS68K/WFC-1

рŢ

## 2.Ø General Operation

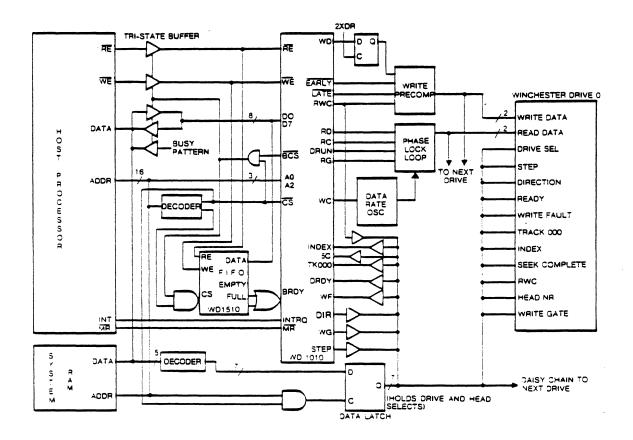

The SYS68K/WFC-1 consists of a set of devices specifically designed for control of Winchester and Floppy disk drives. The heart of the control logic is the Control Processor Buffer Manager (WD1015) that manages the on-board static RAM sector buffer (2048-word by 8-bit). All bytes of data written to and read from disk are first stored on this sector buffer. When the buffer is full, the data is transferred, on command, to its intended destination.

The WD1Ø15, besides controlling the data flow between host, sector buffer, and disk controllers, also translates the host Winchester command format to Floppy disk format when addressing the Floppy Disk Controller (WD2797). This permits the host to maintain a single command format (Winchester) while in effect controlling two different disk command formats (Winchester vs. Floppy). This is possible, since the SDH register is used to select either type of drive.

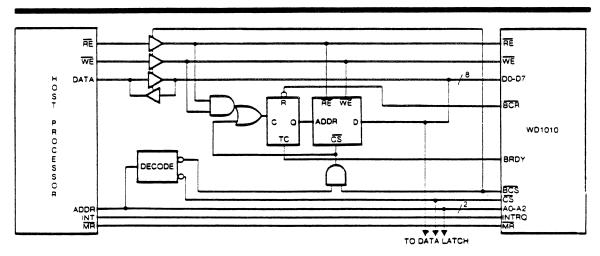

The WD1015 maintains the current copies of necessary host command data in the task files; a set of register physically located in the Winchester Disk Control device (WD1010) and the Error Detection and Support logic device (WD1014).

The WDlØlØ is the link between the host processor (via sector buffer) and the Winchester disk drives. During transfer of data from the host to the WDlØlØ, the WDlØl4 computes a 4-byte ECC which is appended to the end of the data being transferred to the WDlØlØ and recorded on the disk. During data transfers from WDlØlØ to the host (via the sector buffer), the WDlØl5 uses the ECC syndrome to validate the data. Retries and corrections are attempted automatically in case of corrupted data.

The WD1015 performs error correction in conjunction with the WD1014 on data transferred to the disk. While the WD1015 controls the operation of the on-board error-correction logic, the WD1014 generates and checks the Error Correction Code (ECC) if SDH bit 7 = 0. Thus the WD1014 also provides the WD1015 with its real-time control capability.

If CRC format Winchester disks are used, CRC is selected by the WD1010 by setting SDH7 = 0. CRC for the floppy disk is performed by the WD2729, a device that furnishes all control functions for floppy disk drives, including necessary data seperation and write precompensation. SDH7 must be set to zero for floppy disk operation.

# 2.1 Features of the SYS68K/WFC-1

- Fully VMEbus compatible

- Jumper selectable base address with address modifier

- Generation at two different interrupts

- Jumper selectable interrupt level

- Software programmable interrupt vectors

- Three VMEbus options (A31:D16), (A23:D16), (A15:D16) jumper selectable

- User selectable 5.25" Winchester or Floppy operation

- Controls up to 3 Winchester ST506 Interface and up to 4 Floppy drives SA450 compatible

On-board data separation circuitry

- On-board write precompensation for floppy and hard disks

- On-board sector buffer supports up to 1 KByte sectors

- Programmable sector sizes 128, 256, 512, or 1024 bytes

- Automatic track formatting on hard and floppy disks

- Multiple sector operations on all disks

- Data rates up to 5 Mbits/sec on hard disk

- Single burst error correction up to 5 bits on hard disk data

- CRC generation/verification for data and all I.D. fields

- Automatic retries on all errors with simulated completion

- ECC diagnostic commands included (READLONG & WRITELONG)

- Internal diagnostics

- 16 different stepping rates for both hard and floppy drives

## 3.Ø Hardware Overview

# 3.1 Global Base Address Selection

The SYS68K/WFC-1 controller board contains a set of jumper fields for the global base address selection.

This board contains also two jumper fields, BR8 and BR9, for the VMEbus options (A15-D16), (A23-D16) and (A31-D16), (see Fig. 3).

The following table shows the connection of BR8 and BR9 for these options :

| BR8         | BR9         |         |   |

|-------------|-------------|---------|---|

| CONNECTIONS | CONNECTIONS | OPTIONS |   |

| 1 to 2      | l to 2      | A15:D16 |   |

| 1 to 2      | 2 to 3      | A23:D16 |   |

| 2 to 3      | 2 to 3      | A32:D16 | X |

No other combination is allowed, as it may cause errors in the system.

The address signals A31-A4 are used for the global base address selection. Fig.3 shows the jumper location and the default setting during manufacturing ( $\$B\emptyset1\emptyset\emptyset\emptyset$ ) for the A23:D16 option. For all of these jumper fields, jumper in means  $\emptyset$  for the corresponding signal and jumper out means 1 for the corresponding signal. Fig. 4 shows the physical location of these jumpers on the SYS68K/WFC-1 board.

FIG. 3 BASE ADDRESS JUMPER FIELDS

•

# 3.2 Address Modifier Decoding

The address modifier (AM) signals of the VMEbus may be used for additional decoding in parallel to the address signals.

Table 1 lists the combination of the AM signals and the relevant functions.

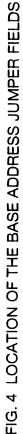

The BR15 may be jumpered so that these signals are not decoded (don't care). If BR15 pin 1 is connected to pin 2, then the AM decoding is enabled. If BR15 pin 2 is connected to pin 3, then the AM decoding is disabled.

The BR14 jumper field includes the AM code and Fig. 5 shows an example for supervisor data decoding. Fig. 4 shows the physical location of the BR14, BR15 jumper field on the SYS68K/WFC-1 board.

.

FIG. 5 AM JUMPER FIELDS EXAMPLE FOR STANDARD SUPERVISORY DATA ACCESS

## 3.3 Interrupt Jumpering

The SYS68K/WFC-1 controller board can generate two different interrupts. The first interrupt, IR1, is for operation complete and error operation.

The second interrupt, IR2, is for data request by read, write and format operations, if the controller board needs data or has to send data.

Both interrupts can be enabled and disabled seperately and can be jumpered on each interrupt level on the VMEbus.

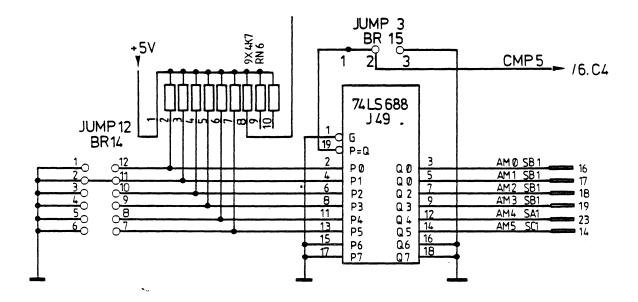

IR1 can be enabled via BR20 through connection pin 1 to 2 and IR2 via BR21 through connection pin 2 to 3.

If BR20 pin 2 is connected to pin 3, then the operation complete interrupt is disabled. If BR21 pin 1 is connected to pin 2, then the data request interrupt is disabled.

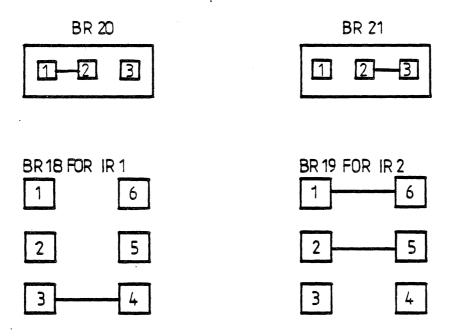

The interrupt request level can be selected via jumper field BR16.

Fig. 6 shows the jumper fields and an example for enabled interrupts for a connection to the interrupt level 3 for IRl and to the interrupt request level 4 for IR2. BR18 and BR19 must be selected to the corresponding level (see Fig. 6). Fig. 7 shows the physical location of these jumpers on the controller board.

The interrupt default setting by manufacturing is disabled and only programmed I/O is allowed.

| ILEXADECIMAL |   | AC | DDR | ES | S M | ODI | FIER | · FUNCTION                               | DEFINED     |

|--------------|---|----|-----|----|-----|-----|------|------------------------------------------|-------------|

| CODE         |   | 5  | 4   | 3  | 2   | 1   | 0    |                                          | BY          |

| 3F           |   | Η  | Н   | Н  | Н   | Н   | н    | Standard Supervisory Ascending Access    | VMEbus Spec |

| 3E           |   | Η  | Н   | Н  | Н   | Н   | L    | Standard Supervisory Program Access      | VMEbus Spec |

| 3D           |   | H  | Н   | Н  | Н   | L   | Н    | Standard Supervisory Data Access         | VMEbus Spec |

| 3C           |   | Η  | Н   | Н  | Н   | L   | L    | Undefined                                | Reserved    |

| 3B           |   | Η  | Н   | Н  | L   | Н   | Н    | Standard Non-Privileged Ascending Access | VMEbus Spec |

| 3A           |   | Н  | Н   | Н  | L   | Н   | L    | Standard Non-Privileged Program Access   | VMEbus Spec |

| 39           |   | Н  | H   | H  | Ĺ   | L   | H    | Standard Non-Privileged Data Access      | VMEbus Spec |

| 38           |   | Н  | H   | H  | Ē   | L   | L    | Undefined                                | Reserved    |

| 30-37        |   | H  | H   | 1  | x   | x   | x    | Undefined                                | Reserved    |

| 2F           |   | H  | 1   | H  | H   | H   | H    | Undefined                                | Reserved    |

| 2E           |   | H  | ī   | H  | Н   | H   | L    | Undefined                                | Reserved    |

| 2D           |   | H  | Ľ   | Н  | H   | L   | H    | Short Supervisory I/O Access             | VMEbus Spec |

| 2C           |   | H  | Ē   | H  | H   | L   | L    | Undefined                                | Reserved    |

| 2B           |   | H  | L   | Н  | L   | H   | Ĥ    | Undefined                                | Reserved    |

| 2A           |   | H  | Ē   | H  | L   | H   | L    | Undefined                                | Reserved    |

| 29           |   | H  | Ī   | Н  | L   | L   | Ĥ    | Short Non-Privileged I/O Access          | VMEbus Spec |

| 28           |   | Н  | ī   | H  | I.  | Ē   | L    | Undefined -                              | Reserved    |

| 20 - 27      |   | Н  | Ĩ.  | L  | x   | x   | x    | Undefined                                | Reserved    |

| 10 – 1F      |   | 1  | H   | x  | X   | X   | X    | Undefined                                | User        |

| OF           |   |    | 1   | H  | H   | H   | Ĥ    | Extended Supervisory Ascending Access    | VMEbus Spec |

| OE           |   | L  | Ē   | H  | H   | H   | L    | Extended Supervisory Program Access      | VMEbus Spec |

| OD           |   | L  | Ē   | Н  | H   | L   | H    | Extended Supervisory Data Access         | VMEbus Spec |

| 0C           | 1 | 1  | Ē   | Н  | Н   | Ē   | Ĺ    | Undefined                                | Reserved    |

| OB           |   | L  | L   | H  | L   | Ĥ   | Ĥ.   | Extended Non-Privileged Ascending Access | VMEbus Spec |

| OA OA        |   |    | L   | Ĥ  | Ē   | H   | L    | Extended Non-Privileged Program Access   | VMEbus Spec |

| 09           | l |    | Ē   | H  | Ē   | L   | H    | Extended Non-Privileged Data Access      | VMEbus Spec |

| 08           |   |    | Ē   | H  | Ē   | Ē   | L    | Undefined                                | Reserved    |

| 00 - 07      | 1 | 1  | 1   | 1  | X   | x   | x    | Undefined                                | Reserved    |

The AM codes are Valid if BH15 is connected from 10 1 to Pin 2.

19

| BR 16 |       |

|-------|-------|

|       | IRQ 7 |

|       | IRQ6  |

|       | IRQ 5 |

|       | IRQ 4 |

|       | IRQ 3 |

|       | IRQ 2 |

|       | IRQ 1 |

|       |       |

| 9 IR1 |       |

# 3.4 Connectors Organisation

The SYS68K/WFC-1 has seven connectors for user applications :

- Two VMEbus connectors SX1 and SX2

- S7 Winchester drive control connector

- S8 Floppy drive control connector

- ST1, ST2, ST3 Winchester high speed data connectors

$ST1 = LUN \emptyset$

ST2 = LUN 1

ST3 = LUN 2

The drive control cables are daisy-chained to each of the three Winchester drives. The three drive data connectors carry differential signals and are radially connected.

The following diagram shows the physical location of the connectors on the SYS68K/WFC-1 board.

#### 3.5 Winchester Drive Control Signals

The Winchester Drive Control connector S7 is a relatively lowspeed bus, daisy chained to each of the Winchester drives in the system. To properly terminate the open collector outputs from the SYS68K/WFC-1, the last drive in the daisy chain should have a 220/3300Hm line termination resistor pack installed. All other drives shoud have no termination. Drive control signals are as follows :

- RWC\* When the Reduce Write Current (RWC\*) line is activated with write gate, a lower write current is used to compensate for greater bit-packing density on the inner cylinders. The RWC\* line is activated when the cylinder number is greater than or equal to four times the contents of the write precomp register. This output is valid only during write and format commands.

- WG\* The Write Gate\* signal enables the disk write data circuitry.

- SC\* Seek Complete\* line informs the SYS68K/WFC-1 that the head of the selected drive has reached the desired cylinder and has stabilized. Since Seek Complete\* is not checked after a seek command, overlapped seeks are allowed.

- TR000\* Track 000\* indicates that the R/W heads are positioned on the outermost cylinder. This line is sampled before each step pulse is issued.

- WF\* Write Fault\* informs the SYS68K/WFC-1 that some fault has occurred on the selected drive. The SYS68K/WFC-1 will not execute commands when this signal is true.

- HS2-HSØ\* Head Select lines (HS2-HSØ)\* are used by the SYS68K/WFCl to select a specific R/W head on the selected Winchester drive.

- IND\* Index\* is used to indicate the index point for synchronization during formatting and as a time-out mechanism for retries. This signal abould pulse once every rotation of the disk.

- RDY\* Ready\* informs the SYS68K/WFC-1 that the desired drive is selected and that its motor is up to speed. The SYS68K/WFC-1 will not execute commands unless this line is true.

- STEP\* Step\* is pulsed once for every cylinder to be stepped. The direction of the step will be determined by the direction line. The Step\* pulse period is determined by the internal Winchester stepping rate register during implied seek operations, or explicitly during seek commands. During auto-restore, the step pulse period is determined by the seek complete time from the drive.

- DS1-DS3\* These three Drive Select\* lines (DS1-DS3) are used to select one of three possible drives.

- DIRIN\* Direction-In\* determines the direction of motion of the R/W head when the step line is pulsed. A high on this line defines the direction as OUT, and a low defines the direction as IN.

# 3.6 5.25" Winchester 34-Pin Drive Control Connector

This drive control connector S7 is a 34-pin vertical header on  $\emptyset.10$ -inch centers. Cabling should be flat ribbon or twisted-pair cable less than 10 feet long. The cable pinouts are given in Table 2.

| Signal<br>Ground | Signal<br>Pin | I/O | Signal Name     |

|------------------|---------------|-----|-----------------|

| 1                | 2             | 0   | RWC*            |

| 3                | 4             | 0   | Head Select 2*  |

| 5                | 6             | О   | Write Gate*     |

| 7                | 8             | I   | Seek Complete*  |

| 9                | 10            | ,I  | TRØØØ*          |

| 11               | 12            | I   | Write Fault*    |

| 13               | 14            | 0   | Head Select Ø*  |

| 15               | 16            |     | NC              |

| 17               | 18            | 0   | Head Select 1*  |

| 19               | 2Ø            | . I | Index*          |

| 21               | 22            | I   | Ready*          |

| 23               | 24            | . 0 | Step*           |

| 25               | 26            | 0   | Drive Select 1* |

| 27               | 28            | 0   | Drive Select 2* |

| 29               | 3Ø            | 0   | Drive Select 3* |

| 31               | 32            |     | NC              |

| 33               | 34            | 0   | Direction-In*   |

|                  | <br>          |     |                 |

Table 2. Winchester Drive Control Connector Pin Description

## 3.7 Winchester Drive Data Connector

Three data connectors (ST1-ST3) allow data to pass between the SYS68K/WFC-1 and each Winchester disk drive. All lines associated with the transfer of data between a drive and the SYS68K/WFC-1 are differential in nature and may not be multiplexed. The three Winchester drive data connectors are 20-pin vertical headers on 0.10" centers. Cabling should be either flat ribbon or twisted-pair cables, less that 10 feet long. Cable pinouts are given in Table 3.

| Table 3. | Winchester | Drive | Data | Connector | Pin | Description |

|----------|------------|-------|------|-----------|-----|-------------|

|          |            |       |      |           |     |             |

| Signal<br>Ground |     | I/O | Signal Name     |

|------------------|-----|-----|-----------------|

| 2                | 1 . |     | NC              |

| 4                | 3   |     | NC              |

| 6                | 5   |     | NC              |

| 8                | 7   |     | NC              |

|                  | 9   |     | NC              |

|                  | 1Ø  |     | NC              |

| 11               |     |     | GND             |

| 12               |     |     | GND             |

|                  | 13  | 0   | MFM Write Data  |

|                  | 14  | 0   | MFM Write Data* |

| 15               |     |     | GND             |

| 16               |     |     | GND             |

|                  | 17  | I   | MFM Read Data   |

|                  | 18  | I   | MFM Read Data*  |

| 19               |     |     | GND             |

| 2Ø               |     |     | GND             |

## 3.8 Floppy Drive Signals

The Floppy Drive Control Connector S8 is a relatively low-speed bus, daisy chained to each of the floppy drives in the system. To properly terminate each TTL-level output signal from the SYS68K/WFC-1, the last drive in the daisy chain should have line terminations as specified by the drive manufacturer. The other drives should not have any terminations. Drive control signals for the floppy disks are functionally similar to those for the hard disks, except that all data is transferred via one connector instead of the seperate connectors used for the Winchester drives. Floppy drive signals are as follows :

- IND\* The index\* line contains a reference index pulse once every disk rotation to indicate the beginning of a track.

- DS3-DSØ\* These four Drive Select\* lines (DS3-DSØ) are used to select one of four possible drives.

- MO\* The Motor-On\* line is used to directly control the dc spindle motor of the floppy drive. If Motor-On Mode (MOM) = Ø (user selectable jumper option), then a 40 nsec delay occurs, otherwise a one-second delay occurs after Motor-On and before any reading or writing is attempted. If the floppy drive is not accessed for ~3 seconds, the motor is turned off by the WD1015. Also, the drives supported must be configured so that the R/W heads are loaded when the motor is turned on. This is usually available as an option on most drives.

- DIRIN\* The Direction-In\* line determines the direction of motion of the R/W head when the step line is pulsed. A high on this line defines the direction as OUT, and a low defines the direction as IN.

- STEP\* The Step\* line is pulsed once for each cylinder to be stepped. The direction of the step will be determined by the direction line. The step pulse period is determined by the internal floppy stepping rate register during implied seek operations, auto restore, or explicitly during seek and restore commands. During any restore operation, the stepping rate period is limited to 8ms minimum.

- WD\* The Write Data\* interface line provides data to be written on the disk. This line is enabled by write gate being active.

- WG\* The Write Gate\* output signals enable disk write data circuitry.

- TR000\* TR000\* indicates that the R/W heads are positioned on the outermost cylinder. This line is sampled before each step is issued.

- WP\* The Write Protect\* interface signal provided by the drive indicates to the SYS68K/WFC-1 that a writeprotected disk is installed. When write protect is active, no data can be written to the disk by the SYS68K/WFC-1.

- RD\* The Read Data\* line provides the "raw data" (clock and data together) as detected by the drive logic.

- SS\* Selects Side\* of floppy disk to be written or read.

# 3.9 5.25" Floppy 34-pin Drive Control Connector

This floppy drive control connector S8 is a 34-pin vertical header on  $\emptyset$ .l $\theta$ -inch centers. Cabling should be flat ribbon or twisted-pair cable, less than 2 $\emptyset$  feet long. The cable pinouts are given in Table 4.

| Signal<br>Ground | Signal<br>Pin | 1/0 | Signal Name      |

|------------------|---------------|-----|------------------|

| 1                | 2             | æ   | NC               |

| 3                | 4             | -   | NC               |

| 5                | 6             | 0   | Drive Select Ø * |

| 7                | 8             | I   | Index *          |

| 9                | lØ            | 0   | Drive Select l * |

| 11               | 12            | 0   | Drive Select 2 * |

| 13               | 14            | 0   | Drive Select 3 * |

| 15               | 16            | 0   | Motor On *       |

| 17               | 18            | 0   | Direction In *   |

| 19               | 2Ø            | 0   | Step *           |

| 21               | 22            | 0   | Write Data *     |

| 23               | 24            | 0   | Write Gate *     |

| 25               | 26            | I   | Track 000 *      |

| 27               | 28            | I   | Write Protect *  |

| 29               | 3Ø            | I   | Read Data *      |

| 31               | 32            | 0   | Side Select *    |

| 33               | 34            | -   | NC               |

|                  |               |     |                  |

.

-

# 3.10 The Run/Local Switch

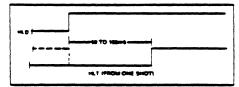

The switch on the front panel (see Fig.9) is used to set the board into RUN or LOCAL mode. In the RUN mode normal access to the on-board registers can be performed and the green RUN LED is turned on.

No access to the on-board registers can be forced in LOCAL mode, since the board is isolated from the bus. This is indicated by the red LOCAL LED on the front panel (see Fig. 9).

## 3.11 The LED Indicators

The front panel of the SYS68K/WFC-1 contains two additional LEDs, BUSY LED and ERROR LED.

The BUSY LED is turned on if the board is busy and a command is being executed.

The ERROR LED indicates that an error has occurred in the execution of a command. The ERROR LED is turned off only when a new command is being executed.

|                                          | SYS68K<br>WFC-1                             |                                                                                                                                       |

|------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| LED 1<br>SW 1<br>LED 2<br>LED 3<br>LED 4 | O RUN<br>O R/L<br>O LDC<br>OERROR<br>O BUSY | <ul> <li>RUN indicator</li> <li>RUN/LOCAL switch</li> <li>LOCAL indicator</li> <li>ERROR indicator</li> <li>BUSY indicator</li> </ul> |

|                                          | FORCE                                       |                                                                                                                                       |

# FIG. 9 THE FRONT PANEL OF THE SYS68K/WFC-1

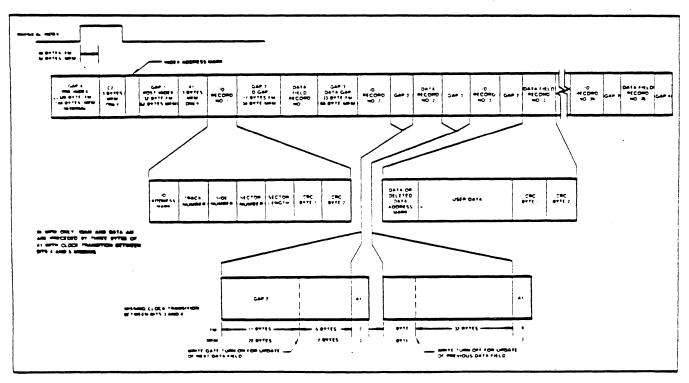

# 3.12 Access Times

A Read/Write access to the SYS68K/WFC-1 can be performed under the following conditions :

The SYS68K/WFC-1 contains a jumper BR17 which can specify the speed of read and write operation to the board. The Read/Write access time is default 450ns and can be slowed by setting the jumper in the second or third position. The following table shows the three different access times :

| BR17 Connections | Access Time   |

|------------------|---------------|

| 1 to 6           | 450ns default |

| 2 to 5           | 65Øns         |

| 3 to 4           | 85Øns         |

|                  |               |

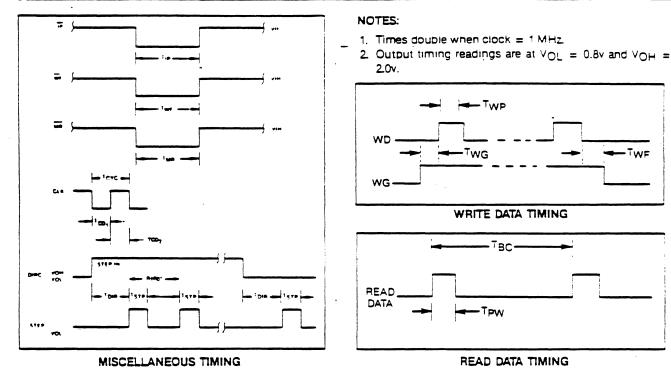

Fig. 10 shows the detailed Read Timing Diagram and Table 5 lists the time values.

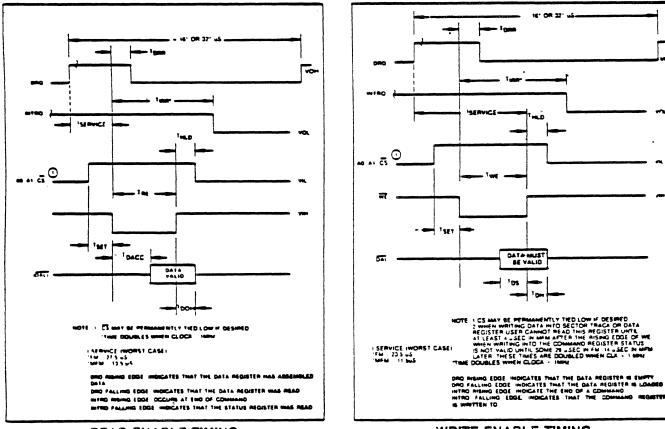

Fig. 11 shows the detailed Write Timing Diagram and Table 6 lists the time values.

FIG. 10 DATA TANSFER BUS READ CYCLE (SLAVE TIMING)

| Number | Parameter                                      | (Note<br>Min. |     | Notes |

|--------|------------------------------------------------|---------------|-----|-------|

| 1      | Axx and AMx valid and IACK* high<br>to AS* low | 10            |     | E     |

| 2      | DTACK* low to invalid address<br>IACK* low     | Ø             |     | D     |

| 3      | AS* High                                       | ЗØ            |     | E     |

| 4      | DTACK* low to AS* high                         | Ø             |     | D     |

| 5      | AS* to DS"A"* skew                             | -1Ø           |     | E     |

| 6      | WRITE* valid to DS"A"* low                     | lØ            |     | Е     |

| 7      | DS"B"* high to invalid WRITE*                  | Ø             |     | Е     |

| 8      | DS"A"* to DS"A"* skew                          |               | 2Ø  | E     |

| 9      | DTACK* low to DS"A"* high                      | Ø             |     | D     |

| 10     | DA"A"* high                                    | ЗØ            |     | E     |

| 11     | DS"B"* high to DS"A"* low                      | ЗØ            |     | E     |

| 12     | DS"B"* high                                    | 3Ø            |     | E     |

| 13     |                                                |               |     |       |

| 14     | DTACK*/BERR* high to DS"A"* low                | Ø             |     | D     |

| 15     | DS"A"* low to Active data bus                  | Ø             |     | С     |

| 16     | Data valid to DTACK* low                       | Ø             |     | в     |

| 17     | DTACK* low to DS"B"* high                      | Ø             |     | D     |

| 18     | DS"A"* high to invalid data                    | Ø             |     | с     |

| 19     | Data bus released to DTACK*/BERR*<br>high      | Ø             |     | В     |

| 2Ø     | DS"B"* high to DTACK*/BERR* high               | Ø             |     | С     |

| 21     | DS"B"* low to DTACK* low                       | 23Ø           | 25Ø | В     |

### Table 5. - Data Transfer Bus Read Time Values

.

35

.

#### Notes:

A. All times given are in nanoseconds.

- B. The SYS68K/WFC-l guarantees this timing between two of its outgoing signal transitions.

- C. The SYS68K/WFC-1 waits for the incoming signal edge from the MASTER before changing the level of its outgoing signal.

- D. This is a guarantee that the MASTER will not change the incoming signal until the SYS68K/WFC-1 changes its outgoing signal.

- E. The SYS68K/WFC-1 is guaranteed this timing between two of its incoming signal transitions.

FIG. 11 DATA TRANSFER BUS WRITE CYCLE (SLAVE TIMING)

| Number | Parameter                                      | •     | Note A<br>Max. | • |

|--------|------------------------------------------------|-------|----------------|---|

| l      | Axx And AMx valid and IACK* high<br>to AS* low | lØ    |                | D |

| 2      | DTACK* low to invalid address or<br>IACK* low  | Ø     |                | C |

| 3      | AS* high                                       | 3Ø    |                | D |

| 4      | DTACK* low to AS* high                         | Ø     |                | С |

| 5      | AS* to DS"A" skew                              | -10   |                | D |

| 6      | WRITE* valid to DS"A"* low                     | ıø    |                | D |

| 7      | DS"B"* high to invalid WRITE*                  | Ø     |                | D |

| 8      | Data valid to DS"A"*low                        | lØ    |                | D |

| 9      | DTACK* low to invalid data                     | Ø     |                | С |

| lØ     | DS"A"* to DS"B"* skew                          |       | 2Ø             | D |

| 11     | DTACK*/BERR* low to DS"A"* high                | Ø     |                | С |

| 12     | DS"A"* high                                    | ЗØ    |                | D |

| 13     | DS"B"* high to DS"A"* low                      | 3Ø    |                | D |

| 14     | DS"B"* high                                    | 3Ø    |                | D |

| 15     | DS"A"* low to DTACK* low                       | 23Ø   | 25Ø            | В |

| 16     | DTACK*/BERR* low to DS"B"* high                | Ø     |                | С |

| 17     | DS"B"* high to DTACK*/BERR* high               | Ø     |                | В |

| 18     | DS"A" to BERR* low on Parity Erro              | or 30 | 48Ø            |   |

|        |                                                |       | •              |   |

Table 6. - Data Transfer Bus Write Time Values

#### Notes:

- A. All times given are in nanoseconds.

- B. The SYS68K/WFC-1 must wait for the incoming signal edge from the MASTER before changing the level of its outgoing signal.

- C. This is a guarantee that the Bus MASTER will not change the incoming signal until the SYS68K/WFC-1 changes its outgoing signal.

- D. The SYS68K/WFC-1 is guaranteed this timing between two of its incoming signal transitions.

- E. The SYS68K/WFC-l guarantees this timing between two of its outgoing signal transitions.

#### 4.0 SYS68K/WFC-1 Register Set

#### 4.1 Register Set Basics

The SYS68K/WFC-1 performs all disk functions through a set of registers. The registers are loaded with parameters such as sector number, cylinder number, etc., prior to issuing a command. Individual registers are selected via Al-A3 for both types of drives. There are only Read-Only/Write-Only Registers and a FIFO Buffer for data.

#### 4.2 SYS68K/WFC-1 Address Map

Table 7. shows the available registers and the default SYS68K/WFC-1 Address Map.

| Address Default | Read Register   | Write Register                        |

|-----------------|-----------------|---------------------------------------|

| BØ1000          |                 | Complete Interrupt<br>Vector Register |

| BØ1ØØ1          | Data Register   | Data Register<br>Data Reg Interrupt   |

| BØ1ØØ3          | Error Register  | Vector Register<br>Write Precomp*     |

| BØ1ØØ5          | Sector Count    | Sector Count                          |

| BØ1ØØ7          | Sector Number   | Sector Number                         |

| BØ1ØØ9          | Cylinder Low    | Cylinder Low                          |

| BØ1ØØB          | Cylinder High** | Cylinder High**                       |

| BØ1ØØD          | Size/Drive/Head | Size/Drive/Head                       |

| BØ1ØØF          | Status Register | Command Register                      |

\* not used on floppies

\*\* LSB of cylinder high, if set to 1 permits a 48 tpi floppy disk to be read on a 96 tpi floppy disk system.

#### 4.3 Data Register

This register is the user's window to the on-board full sector buffer. It contains the next byte of data to be written to or read from the internal sector buffer. When the DRQ (Data Request) bit is asserted, the second buffer contains data to be read during a Type II command, or is awaiting data to be written during a Type III command. If the SYS68K/WFC-1 is interfaced using programmed I/O, data transfers to this register can be implemented using programmed block moves. This register may not be read from or written to except in the context of a valid command.

#### 4.4 Error Register

This register contains specific fault information pertaining to the last command executed. This register is only valid if the error bit in the status register is set. The error register is read only. Table 8 shoes the error register bits.

#### Table 8 - Error Register Bits

| Bit | Error Register      |

|-----|---------------------|

|     |                     |

| 7   | Bad Block Detect    |

| 6   | Uncorrectable Error |

| 5   |                     |

| 4   | ID not found        |

| 3   |                     |

| 2   | Aborted Command     |

| 1   | TRØØØ Error         |

| Ø   | DAM not found       |

|     |                     |

- DAM NOT FOUND Will be set during a read sector command, if, after successfully identifying the ID field, the data address mafk has not been detected within 16 bytes of ID field.

- TRØØØ ERROR Will be set during a restore command if the track ØØØ line has not been asserted by the drive, after all stepping pulses have been issued. The Winchesters are issued a maximum of 1023 stepping pulses and the floppies a maximum of 256 stepping pulses.

- ABORTED COMMAND Indicates that a valid command has been received that cannot be executed based on status information from the drive, i.e. drive not ready, seek complete not asserted, or write fault. Interrogation of the status register by the host may be performed to determine the cause of this failure.

- ID NOT FOUND When set, this bit indicates that an ID field containing a specified cylinder, head, sector number or sector size has not been found after all the retries have been executed.

- UNCORRECTABLE Indicates that an ECC or CRC error has been ERROR encountered in a data field during a read sector command and the error was uncorrectable.

- BAD BLOCK DETECT Indicates that a bad block mark has been detected in the specified ID field. If the command issued was a write sector command, write gate may be pulsed but the sector will not be written If generated from a read sector command, the data field will not be read. Note that bad block may not be detected if there is a flaw in the ID field.

#### 4.4.1 Diagnostic Errors

On power-up, or when specifically commanded to, the SYS68K/WFC-1 will run a series of internal diagnostic tests. When an error is encountered, the diagnostic routine is terminated. A binary error code is set in the error register without the error bit of the status register being set. The diagnostic routines are exercised in the following order :

| Error Code | Major Functional Failure |

|------------|--------------------------|

| 5          | WD1015 error             |

| 4          | WD1014 or bus error      |

| 3          | Sector buffer error      |

| 2          | WD1010 error             |

| 1          | WD2797 error             |

| Ø          | Pass-board is functional |

#### 4.5 Write Precompensation Register

The write precompensation register holds the cylinder number where the RWC line will be asserted and write compensation logic is to be turned on. This write-only register is loaded with the cylinder number divided by 4 to achieve a range of 1024 cylinders. For example, if write precompensation is desired for cylinder 128 (80 Hex) and higher, this register must be loaded with 32 (20 Hex). The writer precompensation delay is fixed at 12 nanoseconds from nominal.

This register is not used for floppy disk drives. Floppy disk write precompemsation is contained in WD2797.

#### 4.6 Sector Count

The sector count register is used in read sector, write sector, and format commands to implement multiple sector handling with one command. The value of zero implies a transfer of 256 sectors (any size). For read and write multiple sector commands, the sector count is decremented, and the sector number is incremented after each sector transfer to or from the buffer. During a format command, this register is loaded with the number of sectors to be formatted and decremented as each sector is formatted until it reaches zero. During format, sector numbers are specified using interleave tables loaded in the sector buffer. The sector count is a Read/Write Register.

#### 4.7 Sector Number

This register is loaded with the desired sector number prior to a read or write command. The sector number register may be read or written to by the host.

#### 4.8 Cylinder Number

These two registers form the cylinder number where the head is to be positioned on a seek, read, or write command. The two least significant bits of the cylider high register form the most significant bits if the cylider number as illustrated below:

|                 | С | yli | nde | r H | igh |   |   |   | С | yli | nde | r L | WO |   |   |   |

|-----------------|---|-----|-----|-----|-----|---|---|---|---|-----|-----|-----|----|---|---|---|

| Register bits : | 7 | 6   | 5   | 4   | 3   | 2 | 1 | Ø | 7 | 6   | 5   | 4   | 3  | 2 | 1 | Ø |

| Cylinder bits : |   |     |     |     |     |   | 9 | 8 | 7 | 6   | 5   | 4   | 3  | 2 | 1 | ø |

When bit  $\emptyset$  of the cylinder high register (bit 8 of cylinder register) is set to a 1 during floppy operation, 48 tpi disks can be used in 96 tpi disk drives for all commands. When this bit is set to  $\emptyset$ , only 96 tpi disks can be used.

#### 4.9 SDH Register

This register contains the ECC/CRC sector size, drive select, and head select bits. The SDH register is a Read/Write Register organized as shown in Table 9.

The SDH register is used to select either the Winchester or the floppy disk drives as implied by bits 3 and 4 shown in Table 9. If either bit is set to zero, then one of the hard disks is selected, and bits  $\emptyset$ , 1, and 2 are used to select one of eight heads.

When bits 3 and 4 are both set to 1, then a floppy disk will be selected. Bits  $\emptyset$ , 1, and 2 are used to select one of four drives with side select  $\emptyset$  or 1 as shown.

Whenever different drives are to be accessed, the SDH register must be updated by the host prior to a command being issued.

The ECC/CRC bit is only supported for the Winchester Disk Controller, therefore the host must be set to SDH bit  $7 = \emptyset$  for all floppy commands. If SDH bit 7 is set to 1 by a Winchester operation, then the Error Correction Mode is supported. If this bit is cleared (= $\emptyset$ ), then a CRC generation and verification for data and all I.D. fields is supported.

## Table 9. - Size Drive Head Register

|          | <b></b>     | • • • • • • |  |                 |   |    |                   |   | - , |

|----------|-------------|-------------|--|-----------------|---|----|-------------------|---|-----|

| Bit      | 7           | 6           |  | 4               | 3 | 2  | 1                 | Ø | _   |

| Function | CRC/<br>ECC | Sec<br>Size |  | Drive<br>Select |   | Dr | ad/<br>ive<br>ect |   |     |

SDH Bits 6 & 5

.

| Bit<br>6 | Bit<br>5 | Sector Size |

|----------|----------|-------------|

| Ø        | Ø        | 256 Bytes   |

| Ø        | 1        | 512 Bytes   |

| 1        | Ø        | 1024 Bytes  |

| 1        | 1        | 128 Bytes   |

SDH Bits 2, 1 & Ø Hard Disk

| Bit<br>2 | Bit<br>1 | Bit<br>Ø | Head Selected<br>Hard Disk                   |

|----------|----------|----------|----------------------------------------------|

|          |          |          |                                              |

| ø        | Ø        | Ø        | Head Ø                                       |

| Ø        | Ø        | 1        | Head 1                                       |

| Ø        | 1 1      | Ø        | Head 2                                       |

| Ø        | ll       | 1        | Head 3                                       |

| 1 1      | Ø        | Ø        | Head 4                                       |

| 1 1      | Ø        | 1        | Head 5                                       |

| -1       | 1        | ø        | Head 6                                       |

| 1        | 1        | 1        | Head 7                                       |

| 1        |          |          |                                              |

|          |          |          | 10 කම කා |

| _ |     |     |                     |

|---|-----|-----|---------------------|

| 1 |     |     |                     |

| i | Bit | Bit | Drive Selected      |

| İ | 4   | 3   | (decoded & latched) |

| 1 |     |     |                     |

|   | _   |     |                     |

|   | Ø   | Ø   | Drive Sel 1         |

|   | Ø   | 1 . | Drive Sel 2         |

|   | 1   | Ø   | Drive Sel 3         |

|   | 1   | 1   | Floppy Dr Sel       |

|   |     | ł   |                     |

|   |     |     |                     |

SDH Bits 4 & 3

SDH Bits 2, 1 & Ø Floppy Disk

| <br>  Bit<br>  2                | Bit<br>1                             | Bi±<br>Ø                             | <br>  Floppy Drive &  <br>  Head Select                                                                                         |

|---------------------------------|--------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Ø<br>Ø<br>Ø<br>1<br>1<br>1<br>1 | Ø<br>Ø<br>1<br>1<br>Ø<br>Ø<br>1<br>1 | Ø<br>1<br>9<br>1<br>9<br>1<br>9<br>1 | $FD1 - HS\emptyset$ $FD1 - HS1$ $FD2 - HS\emptyset$ $FD2 - HS1$ $FD3 - HS\emptyset$ $FD3 - HS1$ $FD4 - HS\emptyset$ $FD4 - HS1$ |

#### 4.10 Status Register

After execution of a command, the status register is loaded with status information pertaining to the command executed. The host must read this register to ascertain successful execution of the command. The status register is a read-only register; it cannot be written to by the host. If the BUSY bit is set, no other bits in this register are valid.

| Bit | Status Register |

|-----|-----------------|

|     |                 |

| 7   | Busy            |

| 6   | Drive Ready     |

| 5   | Write Fault     |

| 4   | Seek Complete   |

| 3   | Data Request    |

| 2   | Corrected Data  |

| 1   | Not used        |

| Ø   | Error           |

|     |                 |

Status register bits are shown as follows :

ERROR

When set, indicates that one or more bits are set in the error register. It provides an efficient means of checking for an error condition by the host. This bit is reset on receipt of a new command.

CORRECTED This bit indicates that an error correction has been DATA successfully completed on the data field just read from the Winchester disk. For multiple mode operations, this bit indicates one or more data fields have been successfully corrected. If an uncorrectable error occurs, the command is terminated with the appropriate bit being set in the error register.

- DATA REQUEST When set, it indicates that the sector buffer is ready to accept data or contains data to be read by the host. The data request bit is reset when the sector buffer has been fully read or written. Normally, the host need not consult this bit to determine if a byte should be transferred.

- SEEK COMPLETE Indicates the condition of the seek complete line on the selected Winchester drive. For floppy drives, this line is asserted when the SDH register is reloaded.

- WRITE FAULT/ Indicates the condition of the write fault line on WRITE PROTECT a selected Winchester drive. The SYS68K/WFC-1 will not execute any command if this bit is set. If a write-protected disk is sensed in a selected floppy drive during a write operation, the write fault bit will be set. The command will then be aborted and no writing will take place.

- READY Indicates condition of ready line on drive. SYS68K/WFC-1 will not execute any commands unless the ready bit is set. Normally, this line is asserted for floppy drives when the SDH register selects any floppy drive. A user available jumper BR3 option can be implemented if the READY line is available from the floppy drive.

- BUSY After issuing a command, or initialising SYS68K/WFC-1 internal diagnostics, this bit will be set, indicating that the SYS68K/WFC-1 is busy executing a command. No other bits or registers are valid when this bit is set.

#### 4.11 Command Register

All commands are loaded into this register after all other registers have been set.

The command register is a Write Only Register.

#### 4.12 Interrupt Vector Registers

The SYS68K/WFC-1 controller board contains two write only interrupt vector registers. The first interrupt vector register is for the complete interrupr and the second one for the data request interrupt. The registers are free programmable and the address is described in the address map.

#### 5.Ø Commands

#### 5.1 General

The SYS68K/WFC-1 executes six, easy-to-use, macro.commands. Most commands feature automatic "implied" seek, which means the host system need not tell the SYS68K/WFC-1 where the R/W heads of each drive are nor when to move them. The controller automatically performs all retries on error encounters, including data ECC Errors. If the R/W head mis-positions, the SYS68K/WFC-1 will automatically perform a restore and a re-seek. If the error is completely unrecoverable, the SYS68K/WFC-1 will simulate a normal completion to simplify the host's software.

The commands executed by the SYS68K/WFC-1 are mapped to the commands supported by the two disk controllers. The format of the SYS68K/WFC-1 commands is the same as that of the WD1010 commands. The on-board WD1015 buffer manager translates this format for the WD2797, transparent to the user. Error correction is only supported for the Winchester disk controller, therefore, the host must set SDH bit 7 = 0 for all the commands when a floppy disk is selected.

Commands are executed by loading the command byte into the command register while the controller is not busy. The host must observe the following simple protocol:

- The registers must be loaded prior to issuing a command. Only parameters that change from the previous command need be entered.

- For any write/format operations, the sector buffer must be filled with the appropriate data before the command can be executed by the SYS68K/WFC-1.

No command will execute if the seek complete or ready lines are false, or the write fault line is true. Normally it is not necessary to poll these signals before issuing a command. If a command is received, that is not defined in Table 10., undefined results will occur.

#### 5.2 SYS68K/WFC-1 Command Summary

Commands have been divided into three types as summarized in Table 10.

### Table 10 - Command Types

| Туре                                                                                                             | Command                                                                | 7                     | 6                     | 5 | 4                     | Bits<br>3 | 2       | 1 | Ø       |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------|-----------------------|---|-----------------------|-----------|---------|---|---------|

| I<br>I<br>II<br>III<br>III                                                                                       | Test<br>Restore<br>Seek<br>Read Sector<br>Write Sector<br>Format Track | 1<br>Ø<br>Ø<br>Ø<br>Ø | Ø<br>Ø<br>1<br>Ø<br>1 |   | 1<br>1<br>0<br>1<br>1 |           | r2<br>M | - | rØ<br>Ø |

| $M = Multiple Sector$ $M = \emptyset$ : Single Sector $D = Read Interrupt$ $D = \emptyset$ : Programmed I/O Mode |                                                                        |                       |                       |   |                       |           |         |   |         |

| M = 1 : Multiple Sector<br>D = 1 : DMA Mode                                                                      |                                                                        |                       |                       |   |                       |           |         |   |         |

Table 11. r3-rØ Stepping Rate

>

| r3-rØ | Winchester Disk | Drives | Floppy Disk | Drives |

|-------|-----------------|--------|-------------|--------|

| ØØØØ  | approx. 35      | us     | approx. 15  | us     |

| ØØØ1  | .5              |        | 1.0         | ms     |

| ØØ1Ø  | 1.0             | ms     | 2.0         | ms     |

| ØØ11  | 1.5             | ms     | 3.0         | ms     |

| Ø1ØØ  | 2.0             | ms     | 4.0         | ms     |

| Ø1Ø1  | 2.5             | ms     | 5.0         | ms     |

| Ø11Ø  | 3.0             | ms     | 6.Ø         | ms     |

| Ø111  | 3.5             | ms     | 8.0         | ms     |

| 1000  | 4.0             | ms     | 1Ø          | ms     |

| 1001  | 4.5             | ms     | 12          | ms     |

| iøıø  | 5.0             | ms     | 14          | ms     |

| 1011  | 5.5             | ms     | 16          | ms     |

| 1100  | 6.0             | ms     | 18          | ms     |

| 11Ø1  | 6.5             | ms     | 2Ø          | ms     |

| 1110  | 7.Ø             | ms     | 25          | ms     |

| 1111  | 7.5             | ms     | 40          | ms     |

|       |                 |        |             |        |

. .

.

#### 5.3 Type I Commands

Type I commands do not effect transfer of data between the host and the SYS68K/WFC-1, but merely position the R/W heads of the selected drive or run diagnostics. The restore and seek commands have explicit stepping rate fields. The lower four bits of these commands form the stepping rate for the drives.

#### 5.3.1 Test Command

Bit code: 1 Ø Ø 1 Ø Ø Ø Ø

The test command is used to run internal diagnostics for checking SYS68K/WFC-1 board function. It is mainly employed to isolate faults in the board logic. This command is always executed on a RESET. Any faults are reported as error codes.

#### 5.3.2 Restore

#### Bit code: Ø Ø Ø 1 R3 R2 R1 RØ

The restore command is used to calibrate the position of the R/W head on each drive by stepping the head outward until the TRØØØ line goes true. Upon receipt of the restore command, the BUSY bit in the status register is set. Cylinder High and cylinder Low Registers are cleared. For Winchester operation, the actual stepping rate is determined by the Seek Complete period. For floppy operation, a minimum stepping pulse of 8 msec. is used. However, the stepping rate field specified by the host is saved internally for use in all future implied seeks. The state of seek complete, ready and write fault are sampled, and if an error condition exists, the aborted command bit in the error register is set, the error bit in the status register is set, an interrupt is generated, and the BUSY bit is cleared.

Regardless of errors encountered, the internal head position register for the selected drive is cleared. The TRØØØ line is sampled. If TRØØØ is true, an interrupt is generated and the BUSY bit is reset. If TRØØØ is not true, stepping pulses at a rate determined by the stepping rate field are issued until the TRØØØ line is activated. When TRØØØ is activated, the busy bit is reset and interrupt is issued. If the TRØØØ line is not activated within 1024 stepping pulses, the TRØØØ error bit in the error register and the error bit in the status register are set, the BUSY bit is reset and an interrupt is issued.

#### 5.3.3 Seek

#### Bit code: Ø 1 1 1 R3 R2 R1 RØ

The seek command positions the R/W head at a certain cylinder. It is primarily used to start two or more concurrent seeks on drives that support buffered stepping. Note that the seek complete line is not sampled after the seek command so that multiple seek operations may be started using drives with buffered seek capability.

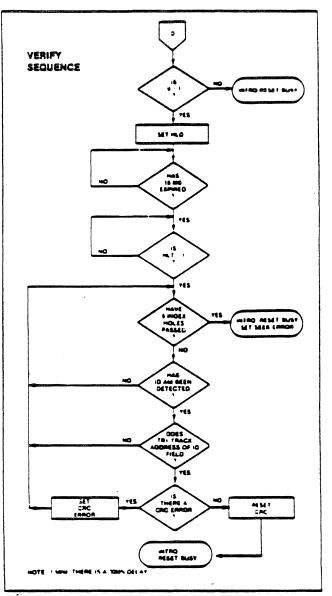

#### 5.4 Type II Commands

Type II commands characteristically transfer blocks of data from the SYS68K/WFC-1 buffer to the host. This type of command has an implicit stepping rate as set by the last restore or seek command.

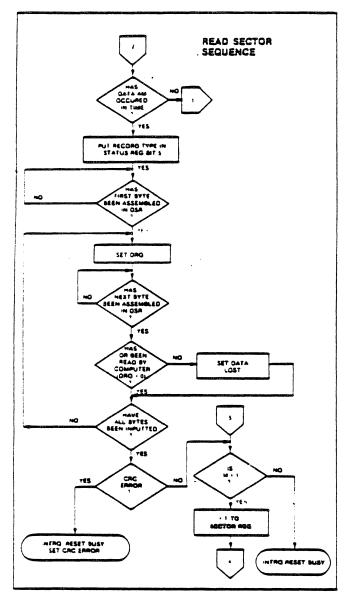

#### 5.4.1 Read Sector

#### Bit code: Ø Ø 1 Ø D M Ø Ø

The read sector command is used to enable the host computer to read a sector of data from the disk. If ECC is enabled, ECC bytes are recomputed by the SYS68K/WFC-1. After the buffer is full, the recorded ECC bytes are compared to the recomputed check bytes to generate the syndrome bytes. If the syndrome is nonzero, errors have occurred. Error correction is invoked by the WD1Ø15 if two consecutive syndromes match, otherwise a maximum of retries is attempted by the WD1015. If the data is 8 correctable, the WD1015 makes the correction and passes the data in the buffer to the host. If, after eight retries, the syndromes do not match, the SYS68K/WFC-1 sends an error status to the host along with the status from the WD1010. Multiple sector read commands are modified to single sector commands and are issued a multiple number of times. The status and error registers are updated for every block of data transferred.

During a floppy read sector operation only CRC is used with the data fields. If a CRC error occurs in the data field, the WD1015 buffer manager attempts a maximum of 8 retries and reports the error only if it persists. Regardless of the drive accessed (Winchester or Floppy), CRC is used on all ID fields.

D = DMA Read Mode

$\emptyset$  = Programmed I/O Mode 1 = DMA Mode

The DMA bit is used to position INTRQ in relation to DRQs during the read sector command. If the DMA bit is reset  $(D=\emptyset)$ , the interrupt will occur along with the DRQ. This allows the programmed I/O host to intervene and transfer the data from the sector buffer. For programmed I/O, multiple transfer is not permitted  $(M=\emptyset)$ . If the DMA bit is set (D=1), then the interrupt will occur only after the system DMA controller has transferred the entire buffer of data. This mode is always used with multiple sector transfers.

#### 5.4.1.2. Normal Completion

A normal completion occurs when the SYS68K/WFC-1 encounters no errors. The BUSY bit is reset. The status of the DMA bit in the command byte is examined. If this bit is reset (D=0; programmed I/O mode), an interrupt is issued at this time. DRQ is set until all bytes of data have been read from the buffer. (Note: It is recommended that programmed I/O transfers should take place as a block move without consulting the DRQ bit in the Status Register). After all the data have been moved from the buffer, the DMA bit in the command byte is consulted again. If this bit is set (D=1; DMA mode) then an interrupt will be issued.

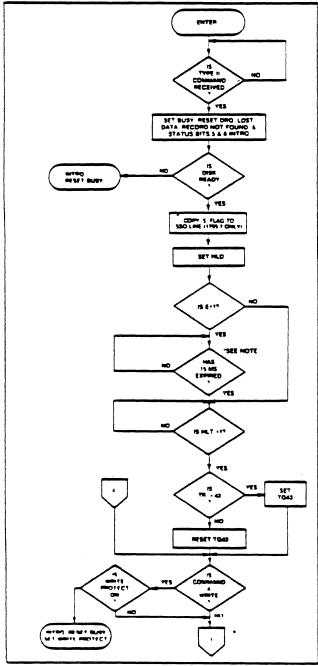

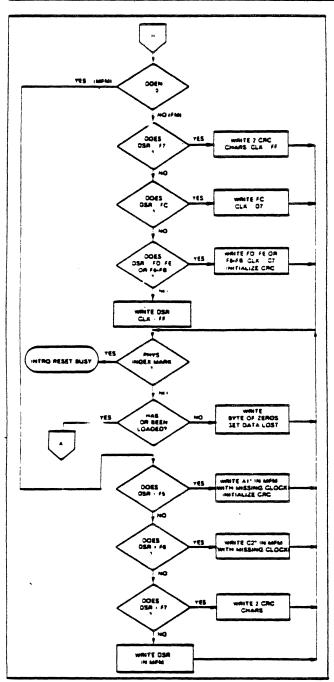

#### 5.5 Type III Commands

This type of command is characterized by a transfer of a block of data from the host to the SYS68K/WFC-1 buffer. These commands have implicit stepping rates as set by the last restore or seek command.

The command will not be executed by the SYS68K/WFC-1 controller unless the buffer has been completely filled by the host.

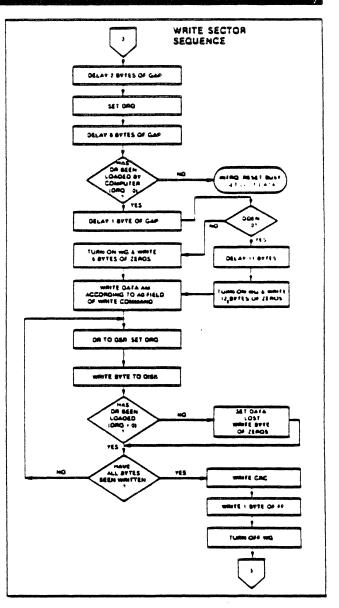

#### 5.5.1 Write Sector

Bit code: Ø Ø l l Ø M Ø Ø

The Write Sector command is used to write a sector of data from the host computer to the disk. Upon receipt of the write command, the controller sets DRQ until the entire sector length of data has been written into the buffer. (Note: It is recommended that programmed I/O transfers should take place as a block move without consulting the DRQ bit in the Status Register.)

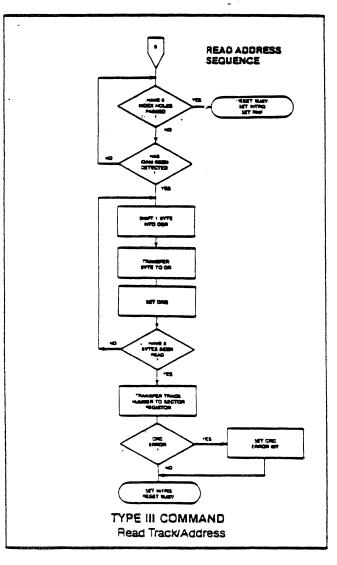

#### 5.5.2 Format Track

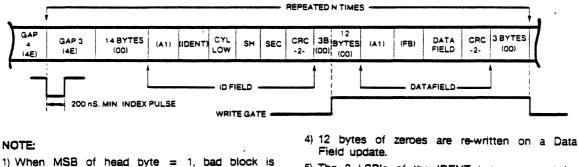

The format command is used for initializing the ID and data fields on a particular disk. Upon receipt of the format command, the controller sets the DRQ for the interleave table to be written to the buffer. In all cases, the number of bytes transferred to the buffer must correspond to the current sector size.

When the buffer has been completely filled, the specified number of sectors are written and the DRQ is reset. The data field is written with  $\emptyset\emptyset$  for the hard disks and E5 (hex) for the floppies. ECC or CRC bytes are automatically computed and written.

Once the index is found, a number of ID and data fields are written to the disk. As each sector is written, the sector count register is decremented and consequently must be updated before each format operation.

#### 6.Ø Programming

#### 6.1 General

Users will find programming the SYS68K/WFC-1 relatively simple as a substantial amount of intelligence formerly required by host computers has been incorporated into the SYS68K/WFC-1 board.

The SYS68K/WFC-l performs all needed retries, 'even on head positioning errors. If there is an error in the data field, the SYS68K/WFC-l will attempt to correct it.

Most commands feature automatic "implied" seek, which means that seek commands need not be issued to perform basic read/write functions. The SYS68K/WFC-1 keeps track of the head position up to eight read/write head assemblies, eliminating the need for the host system to maintain track tables.

All transfers to and from disk are through an on-board sector buffer. This means that data transfers are fully interruptable and can take place at any speed that is convenient to the system designer. In the event of an unrecoverable error, the SYS68K/WFC-1 simulates a normal completion so that special error recovery software is not needed.

#### 6.2 Setting Register Set

Before any of the six macro commands may be executed, a set of parameter registers must be set up. For most commands, this informs the controller board of the exact location on the disk where the data involved in the transfer is located or will be placed. For a normal read or write sector operation, the sector number, the size/drive/head, the cylinder number, and the command registers (usually in that order) will be written.

Note that although most of these registers are readable as well as writeable, they normally are not read from. Read capability for them is provided, however, so that error-reporting routines can determine physically where an error occurred without recalculating the sector, head, and cylinder parameters.

Since all parameters can be recalled by the SYS68K/WFC-1, it is recommended that task file parameters be stored in the SYS68K/WFC-1 as they are calculated. This will save the programmer a few instructions and microseconds by not maintaining two copies of the same information.

#### 6.2.1 Cylinders and Tracks

Since most hard-disk drives contain more than one head per positioner, it is more efficient to step the R/W head assemblies of most disk drives by cylinders, not tracks. In other words, the disk drive software should be designed to read or write all data that are directly accessible by all the heads on a position before stepping to a new cylinder.

The following table shows an example :

| Physical<br>Cylinder                          | Logical<br>Head<br>Number                          | Physical<br>Head Side | Physical<br>Platter |

|-----------------------------------------------|----------------------------------------------------|-----------------------|---------------------|

| 25                                            | 3                                                  | Тор                   | В                   |

| 26                                            | Ø                                                  | Bottom                | A                   |

| 26                                            | 1                                                  | Top.                  | A ·                 |

| 26                                            | 2                                                  | Bottom                | В                   |

| 26                                            | 3                                                  | Тор                   | В                   |

| 27                                            | Ø                                                  | Bottom                | A                   |

| )<br>මෙම මහ මෙම මෙම මෙම මෙම මෙම මෙම මෙම මෙම ම | 80 63 68 68 68 69 69 69 69 69 69 69 69 69 69 69 69 |                       |                     |

#### 6.3 Type I Command Programming

Test, Restore and seek are Type I commands that position the R/W heads of the selected drive and set the implied stepping-rate register. No data is transferred to or from the data register. To execute a Type I command, the system software must perform the following functions in the order shown:

1. Set up register set and issue command with stepping rate.

- 2. Wait for interrupt or for BUSY bit in status register to be reset.

- 3. Check error bit in status register for proper completion.

#### 6.3.1 Use of BUSY Bit

Smaller, single-user systems can sense the completion of a command by polling the BUSY bit of the status register. This bit (bit 7) is set whenever the controller starts a disk operation or internal diagnostics, and is reset whenever the controller is ready to communicate with the host computer.

The BUSY bit is located in the same place as the sign bit of many computers to simplify the polling process.

One way to poll this bit using 68000 code is as follows:

| WAIT: | MOVE. B | STATUS, DO ; | Input Status Register |

|-------|---------|--------------|-----------------------|

|       | BTST    | #7, DO ;     | Is Bit 7 Zero         |

|       | BNE     | WAIT ;       | Wait for BUSY Bit     |

#### 6.3.2 Use of Interrupts

Another, more efficient way of notifying the CPU that the SYS68K/WFC-1 has completed a command is through interrupts. The IR1 line on the board makes a high-to-low transition whenever the disk controller requires CPU intervention. This allows the host CPU to run other tasks while the SYS68K/WFC-1 is reading or writing data to the disk. Only if this mode is used, the control logic is able to force interrupts to the VME bus.

#### 6.3.3 Use of the Error Bit

As the SYS68K/WFC-1 simulates normal completions when errors have been encountered, the only way to determine error status is to check the error bit in the status register. The error bit is so located that it can be easily tested. The contents of the error register are not valid unless the error bit is set.

One way to check the Error bit using 68000 code is as follows:

| MOVE.B | STATUS, DO | ; Get Status          |   |

|--------|------------|-----------------------|---|

| BTST   | # 1, DO    | ; Is Error Bit Set    |   |

| BNE    | ERROR      | ; Jump if Error Found | đ |

#### 6.4 Type II Command Programming

The only Type II command is the read sector command. This command is characterized by the transfer of a block of data from the SYS68K/WFC-1 buffer to the host. The command features implied seek with an implicit stepping rate. To execute a Type II single-sector command in programme I/O mode, the system software must perform the following functions in the order shown:

- 1. Set up register set and issue command with DMA bit reset.

- 2. Wait for interrupt or for BUSY bit in status register to be reset.

- Perform a block move from SYS68K/WFC-1 buffer to system memory.

- 4. Check error bit in status register for proper completion.

Note: Steps 3 and 4 above can be reversed.

To execute a Type II single or multiple sector command in DMA mode with interrupts, the system software does the following:

- 1. Set up register set and issue command with DMA bit set.

- Set up DMA controller and wait for data request (DMA controller will move data from SYS68K/WFC-1 to memory).

- 3. Wait for interrupt from SYS68K/WFC-1.

- 4. Check error bit in status register for proper completion.

- Note: The above sequence is preferred, but steps 1 and 2 above can be reversed.

#### 6.4.1 DMA Mode

The DMA mode bit (D) in the foregoing read sector examples is a special bit in the command byte used to optimize the SYS68K/WFC-1 interrupts during programmed I/O and DMA operations. If the DMA bit is reset (D= $\emptyset$ ), the interrupt will come before the buffer is transferred. This allows a programmed I/O host to intervene and transfer the buffer of data. If the DMA bit is set (D=1), then the interrupt will occur only after the data has been transferred. This allows the host to go uninterrupted until the entire buffer has been transferred.

#### 6.5 Type III Command Programming

Write sector and format are Type III commands. These commands are characterized by the transfer of a block of data from the host to the SYS68K/WFC-1 buffer. Like the Type II commands, these commands feature implied seek with an implicit stepping rate. To execute a single sector Type III command in programmed I/O mode, the system software must go through the following functions in the order indicated:

- 1. Set up register set and issue command.

- Perform block move from system memory to SYS68K/WFC-1 buffer (SYS68K/WFC-1 will attempt to write a sector or format).

- 3. Wait for interrupt or for BUSY bit in status register to be reset.

- 4. Check error bit in status register for proper completion.

To execute a single or multiple sector Type III command in DMA mode with interrupts, the system software goes through the following steps:

- 1. Set up register set and issue command.

- Set up DMA controller and wait for DRQ interrupt (DMA controller will move data from memory to SYS68K/WFC-1). SYS68K/WFC-1 will attempt to write sector or format.

- 3. Wait for interrupt from SYS68K/WFC-1.

- 4. Check error bit in status register for proper completion.

Note: Steps 1 and 2 above can be reversed.

#### 6.5.1 Formatting

The format command is very similar to the write sector command, except that the sector buffer is filled with interleave and bad block information instead of with user data. Two bytes will be written to the buffer for each sector to be formatted.

The first (lower) byte will be either a 00 or an 80 in Hex. If the lower byte is a 00, the sector is marked as good. If the lower byte is an 80, and there is any attempt to read it or write to it, the sector will set the bad block bit in the status register.

The second (upper) byte is the logical sector number of the next sector to be formatted. This number will be recorded on the disk. The sector number register is not used during format.

#### 6.5.1 Formatting

On a 32-sector-per-track disk, 32 pairs of bytes containing formatting information must be supplied to the drive during each format operation. To start the format operation, the buffer must be completely filled, even if the sector table is not as long as the buffer. This means that on a 32-sector-per-track disk, with 64 bytes of formatting information supplied, if the sector size is 256 bytes, then 192 bytes of garbage must be passed to the controller to start the format operation.

As the contents of the sector buffer do not imply how many sectors are to be formatted, a dedicated register is provided. This Sector Count register must be loaded with the number of sectors to be formatted before every format operation.

#### 6.5.2 Interleaving

If sequential sectors on the disk are to be read, the next sector will pass by the read/write head before a read or write can be set up. The disk will then have to make a complete rotation to pick up this next sector. If an attempt is made to read all 32 sectors on a particular track, it requires 32 rotations or about a half a second per 8K bytes. This performance can be significantly improved by interleaving, a technique that allows the system to read or write more than one sector per rotation.

Suppose the system takes less than three sector times (3 times 32 rotational periods with 256 byte sectors) to digest the data that it has read and to set up the next read operation. This means that if the second logical sector can be physically placed four sectors away from the first one, the controller will be able to read it without much delay. This four-to-one interleave factor will allow a potential reading of the entire track in only four rotations. In the example given, the throughput will be increased by a factor of eight.

The simplest way to determine the optimum interleave for any particular system is through experimentation. If the system maintains its directories or virtual memory-swapping areas in a certain place on the disk, it sometimes makes sense to have more than one interleave.

To simplify driver software, the SYS68K/WFC-1 will automatically map logical sectors to physical sectors to achieve interleave. This logical-to-physical map is recorded during the format operation on each track of the disk in the ID fields of the sectors. Table 12. is an example of an interleave table for a 32-sector track with 4:1 interleave and no bad blocks.

#### 6.5.2 Interleaving

The first byte in each byte-pair in Table 12 is set to 00. This marks each block as a "good" block. The second byte of each byte-pair is the logical sector number. The first byte pair in Table 12. represents the first logical sector of the track. The underlined byte pair represents the second logical sector.

# Table 12.Interleave Table with 32 Sectorsand 4:1 Interleave

| 1 | ØØ | ØØ | ØØ | Ø8 | ØØ | lØ | ØØ | 18 |   |

|---|----|----|----|----|----|----|----|----|---|

| 1 | ØØ | Øl | ØØ | Ø9 | ØØ | 11 | ØØ | 19 |   |