#### MEMORANDUM

TO:

DISTRIBUTION

DATE: September 20, 1983

FROM:

Dave Nudelman 2

SUBJ:

Central Logic Bus Interface

Manual Specification

There will be a meeting to review the Central Logic Bus Interface Manual Specification on Monday, September 26, 1983, at 11:00 a.m. in the Engineering Conference Room.

Please review this document before the meeting and be ready to discuss it. If you are unable to attend the meeting and have comments on the CLB spec, please call me at x438 or send someone from your group to the meeting.

DN:cm Att.

## DISTRIBUTION

Mohan Asnani Peter Chen Kevin Conry Cal Eberle Ed Empson Mike Johnson Dan Jones Peter Lowell Pradip Morparia Don Morris Liz Myers Tim Myers Dick Nisley Pat Patrick Hub Steenbakkers Sam Tam Huba Toth Jim Wall Rob Warnock

|     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | NO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | FORTUNE SYSTEMS CORPORATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | CENTRAL LOGIC BUS<br>INTRERFACE MANUAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *** | entropy.  The second of the se |

|     | This is a proprietary FORTUNE SYSTEMS CORPORATION document and does not imply any commitment to supply or support any product or service mentioned herein. This document is not to be reproduced and is subject to change without notice.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | APPROVAL SIGNATURES:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | (Date)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | (Date)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | (Date)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | (Date)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# TABLE OF CONTENTS

Section 1 General Description ......

| Conne<br>Board                                                                                                                                               | Mechanical Specifications                                                                                                                                                                                                                                                                                                                                           | 7<br>7<br>7<br>8                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Centra<br>Power I<br>Interro<br>DMA Pro                                                                                                                      | Logical Specifications                                                                                                                                                                                                                                                                                                                                              | 17<br>17<br>21<br>22<br>26<br>29                                                           |

| Central<br>Receive:                                                                                                                                          | Electrical Specifications                                                                                                                                                                                                                                                                                                                                           | 32<br>32<br>33<br>34                                                                       |

|                                                                                                                                                              | LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                     |                                                                                            |

| Figure 1. Figure 2. Figure 3. Figure 4. Figure 5. Figure 6. Figure 7. Figure 9. Figure 10. Figure 11. Figure 12. Figure 13. Figure 14. Figure 15. Figure 16. | Central Logic Bus Connector Pinout I/O Printed Circuit Board Dimensions Back Plate Dimensions Piggy Back board connection to I/O board Mother Board Printed Circuit Board Dimensions Air Flow 32/16 System 32/16 System 32/16 System 32/16 System Power Fail Timming Interrupt Acknowledge Logic Interrupt Acknowledge Timing DMA Read DMA Write I/O Read I/O Write | 6<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>21<br>23<br>24<br>27<br>28<br>30<br>31 |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                     |                                                                                            |

|                                                                                                                                                              | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                      | •                                                                                          |

| Table 1. Table 2. Table 3. Table 4.                                                                                                                          | Timming Parameters                                                                                                                                                                                                                                                                                                                                                  | 25<br>32<br>33<br>34                                                                       |

## General Description

Remote spaces before punctuation

This document describes the Central Logic Bus (CLB) of the Fortune Systems 32/16 computer. It is divided into four parts; Section 1 which provides a general description of the Central Logic Bus; Section 2 which provides mechanical specifications, Section 3 which provides logical specifications, and Section 4 which defines electrical specifications. Figure 1, at the end of this section, shows the Central Logic Bus connector and pinouts.

The medinal specification includes a decription of the size of the option boards, the location of connectors, and the numbering of pins on the connector. The logical interface discusses the various siginals on the CLB and their rules of protocol and timing. The electrical specification includes voltage levels, D.C (current) asnd A.C. (capacitance) loading.

Additional documents which should be procured as supplements to this document are as follows:

CPU, MMU, Motherboard Hardware Spec

Hardware Design Specification Basic System

In-House Software Documentation Guidelines

Power Supply Specification

Printed Circuit Layout Guidelines

Voltage Sense Module Hardware Design Specification

The CLB is the primary control and data transfer path within the Fortune system central logic subassembly. The major logic components such as processor, memory subsystem, and device controllers are interconnected through the CLB (The memory array cards interface to the memory controller, which is in turn connected to the CLB).

The CLB was targeted to support a set of devices with a high aggregate transfer rate: 6 MHz 68000 CPU (24 Mb/s), Ethernet port (10 Mb/s), high speed Winchester disks (5-10 Mb/s), and bit-mapped display (15 Mb/s).

The CLB is a system bus, not a processor bus. It is based on synchronous system timing, with multi-master control of transfers, and with centralized arbitration logic. Each master (processor or DMA controller) ordinarily holds the CLB just long enough for one trasfer of a byte or word to or from some CLB address. Bus arbitration is pipelined one cycle ahead to eliminate delay switching from master to master. Synchronous timing control permits simple control logic in each master.

The basic bus timing is generated by a bus subsystem controller. Certain types of access may involve cycles which are extended by one or more bus cycles, such as a byte write when using ECC with memory.

Because the processor is the most latency-sensitive device, the arbitrator assumes that the processor is about to use the next cycle, and enables the processor's address buffers by default. This technique saves one clock cycle in the usual case of continual processor memory references since the processor gives no early warning that it is about to use the bus. The arbitration logic processes the DMA requests in parallel during each clock cycle and determunes which controller has the highest priority. This way the arbitration amounts to a binary decision: the processor, or "the other". The identity of "the other" will have been set during the preceding bus clock time. Once the processor has granted the bus, the timing is the same as any other device.

Slave devices are of two kinds: "fast," and "slow". Ordinarily, the main system memory (RAM) is the only fast device. All of the internal and standard CLB option card I/O device registers are slow devices.

The processor may be slowed down but must not be stopped during disk and network activity. Other devices in the system such as serial ports must each have service at least once per millisecond. With one COMM/A option plus the built-in port, if all the serial ports are at 9600 baud, this amounts to six such devices, since full-duplex transfers are possible. Both disk and Ethernet transfers can take in excess of one millisecond of continuous transfer time, causing unrecoverable lost data overruns on the serial ports. The disk and Ethernet transfers can get overruns/underruns occasionally, but with human interfaces this is not acceptable.

These devices have very low latency times since heavy local buffering is not used. Full buffering has negative system throughput implications, since the system latency to get at a data block would have to include an added transfer time from the buffer to main memory. Also, too much buffering on high speed devices causes an undesirable stuttering effect since the data burst from each device draining its buffer causes the next device to fill its buffer.

The combination of tight latency and high throughput requirements dictated that the CLB is not simply a buffered copy of the processor chip pins. These requirements can easily be met with a multi-ported memory architecture, as long as the memory cycle time is less than one-half of the processor cycle time. This is desirable to avoid heavy interference from as few as one of the DMA devices transferring.

In contrast , memory cycle times as long as 0.8 times the processor cycle time would give adequate performance under heavy disk/Ethernet load, but could not also accommodate display traffic. During the design of the CLB it was determined that DMA cycles would not be shorter than 3/4 of a processor cycle. For this reason, the display was separately buffered. As a result, any memory system that can satisfy the processor's access time requirements without wait states can also meet the cycle time demands of the DMA load expected.

For slower devices such as floppy disks the fully buffered approach is reasonable. Analysis of the 68000instruction code sequences for block transfers shows the effective bus overhead of the software transfer is about 2.3 times the bus overhead of a true DMA transfer (as seen by the part of the processor not involved in the transfer). Of this amount a factor of 2 is applied since true DMA transfers (to devices on a private controller bus) only take one memory cycle for each word moved while memory-to-memory block transfers take two cycles per word. The remaining factor 1.15 is is applied since the best usable code sequences for block transfers only use about 85% of the bus cycles for data. The remainder are instruction fetches.

The issue of whether the serial ports should be DMA or not is not based on data transfer rates but on the amount of read-time intelligence needed for the various protocols and on the pre-interrupt overhead of the processor. SIO latency and throughput requirements are modest, when compared to disk or Ethernet. The buffered disk or network ports only give one interrupt per block transfer, and a buffered display gives no interrupts at all.

Main memory is implemented using 64K-bit MOS dynamic memory devices in the memory array. The array cards interface to, and are controlled by , the memory subsystem controller which provides timing signals, and address multiplexing. Each array card provides 128 Kbytes or 256 Kbytes of memory, and up to 4 array cards may be plugged into the system.

The memory controller contains all of the logic needed to interface the memory array cards to the CLB. This includes the address decode and multiplexing logic, refresh control, and optional error correcting logic. The controller contains several error save registers that are accessible to the processor in I/O address space. These registers allow the operating system to record the failing memory location, isolate the error to a single memory chip, and verify that the error correcting logic is working properly.

The memory system performance is optimized (together with the CLB arbitrator) around 16-bit word read operations by the processor, since the vast majority of all system memory cycles will be processor instruction and data fetches. A 16-bit processor write operation, or any 16-bit operation from other bus masters, proceeds at full processor/device speed. The memory controller also allows 8-bit byte write operations.

| FUNCTION             | NMEMONIC P   | IN & | STA | TE MNEMONIC  | FUNCTION             |

|----------------------|--------------|------|-----|--------------|----------------------|

| +12 Volt Power       | +12 volts    | 1    | 2   | +12 volts    | +12 Volt Power       |

| -12 Volt Power       | -12 volts    | 3    | 4   | -12 volts    | -12 Volt Power       |

| +5 Volt Power        | +5 volts     | 5    | 6   | +5 volts     | +5 Volt Power        |

| Siginal Ground       | ground       | 7    | 8   | CLBA1+       | CLB Address 1        |

| CLB Address 2        | CLBA2+       | 9    | 10  | CLBA3+       | CLB Address 3        |

| CLB Address 4        | CLBA4+       | 11   | 12  | CLBA5+       | CLB Address 5        |

| CLB Address 6        | CLBA6+       | 13   | 14  |              | CLB Address 7        |

| CLB Address 8        | CLBA8+       | 15   | 16  | CLBA9+       | CLB Address 9        |

| CLB Address 10       | CLBA10+      | 17   | 18  | CLBAll+      | CLB Address ll       |

| CLB Address 12       | CLBA12+      | 19   | 20  |              | CLB Address 13       |

| CLB Address 14       | CLBA14+      | 21   | 22  | CLBA15+      | CLB Address 15       |

| CLB Address 16       | CLBA16+      | 23   | 24  | CLBA17+      | CLB Address 17       |

| CLB Address 18       | CLBA18+      | 25   | 26  | CLBA19+      | CLB Address 19       |

| CLB Address 20       | CLBA20+      | 27   | 28  | CLBA21+      | CLB Address 21       |

| CLB Address 22       | CLBA22+      | 29   | 30  | CLBA23+      | CLB Address 23       |

| +12V ( for CRT only  | ) +12v       | 31   | 32  | +12v         | +12V (for CRT only)  |

| Signal Ground        | ground       | 33   | 34  | CLBD0+       | CLB Data 0           |

| CLB Data 1           | CLBD1+       | 35   | 36  |              | CLB Data 2           |

| CLB Data 3           | CLBD3+       | 37   | 38  | CLBD4+       | CLB Data 4           |

| CLB Data 5           | CLBD5+       | 39   | 40  | CLBD6+       | CLB Data 6           |

| CLB Data 7           | CLBD7+       | 41   | 42  | CLBD8+       | CLB Data 8           |

| CLB Data 9           | CLBD9+       | 43   | 44  | CLBD10+      | CLB Data 10          |

| CLB Data ll          | CLBD11+      | 45   | 46  | CLBD12+      | CLB Data 12          |

| CLB Data 13          | CLBD13+      | 47   | 48  |              | CLB Data 14          |

| CLB Data 15          | CLBD15+      | 49   | 50  | ground       | Signal Ground        |

| System Reset         | CLBRESET-    |      | 52  | spare        |                      |

|                      | spare        | 53   | 54  | CLBIO3-      | CLB Int. Req. 3      |

| CLB Int. Req. 4      | CLBIO4-      | 55   | 56  | T2+          |                      |

| CLB Read/Write       | CLBR/W       | 57   | 58  |              | CLB Address Strope   |

| CLB Upr. Data Strobe | CLBUDS-      | 59   | 60  |              | CLB Lwr. Data Strobe |

| Signal Ground        | ground       | 61   | 62  | CLBCLK+      | CLB Clock            |

| Signal Ground        | ground       | 63   | 64  | spare        |                      |

| CLB Data Bus Error   | CLBPERR-     | 65   | 66  | CLBPFL-      | CLB Power Fail       |

| CLB Int. Ack. In 3   | CLBINTACKI3- | 67   | 68  |              |                      |

| CLB Int. Ack. In 4   | CLBINTACKI3- | 69   | 70  | CLBINTACKO4- | CLB Int. Ack. Out 4  |

| CLB Bus Request      | CLBBR-       | 71   | 72  | CLBBG-       | CLB Bus Grant        |

| CLB Board Present    | CLBPRESENT-  | 73   | 74  |              | CLB I/O Select       |

| +5 Volt Power        | +5 volts     | 75   | 76  | +5 volts     | +5 Volt Power        |

| Signal Ground        | ground       | 77   | 78  | ground       | Signal Ground        |

| Signal Ground        | ground       | 79   | 80  | ground       | Signal Ground        |

Figure 1. CENTRAL LOGIC BUS CONNECTOR PINOUT

#### SECTION 2

#### MECHANICAL SPECIFICATIONS

$$\operatorname{\textbf{This}}$$  section describes the mechanical specifications of the CLB .

#### Connector

The connector used is a 2x40 pin PC edge connector with 0.1" pin spacing . Typical part number for the connector ( mounted on the mother board ) is Amp # 530843-9 .

#### Board Dimensions

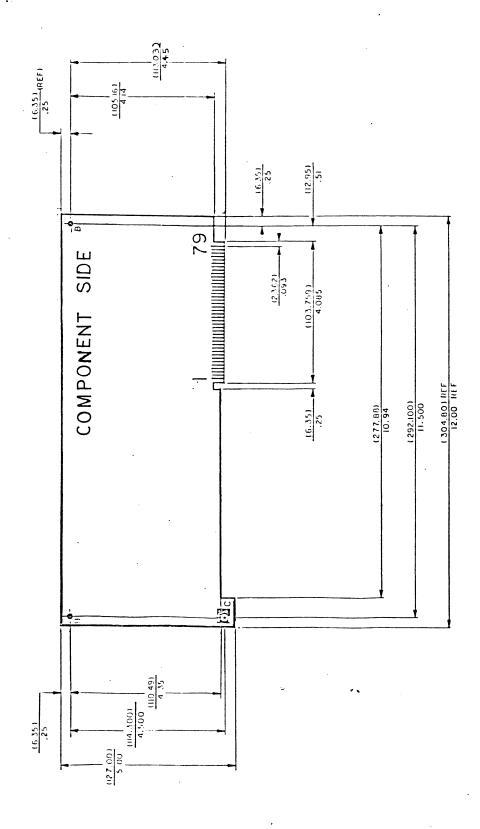

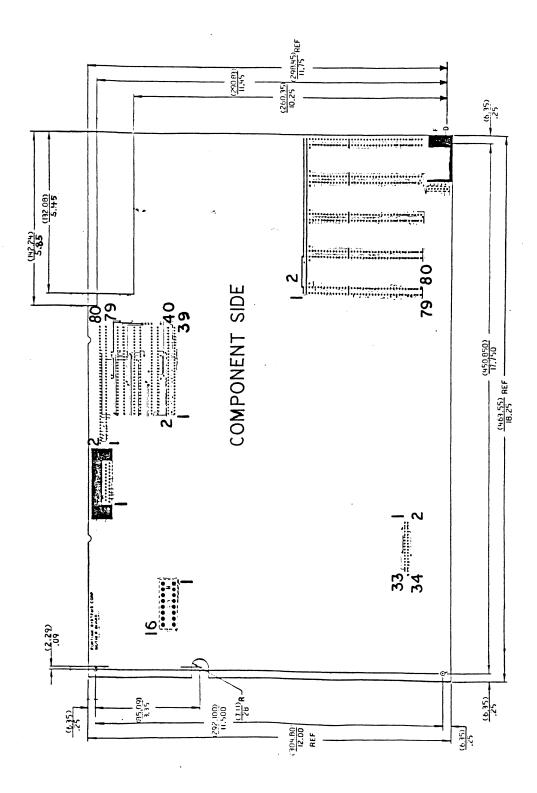

Physical dimensions for the I/O board is shown in figure 2. (Fortune drawing # 1000443 , page 9)

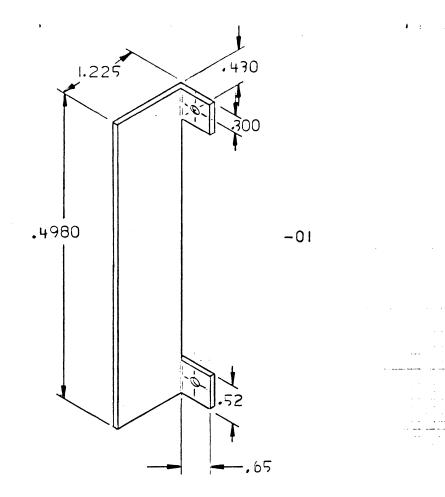

Physical demensions for the I/O plate are shown in figure 3 . ( page 10 )

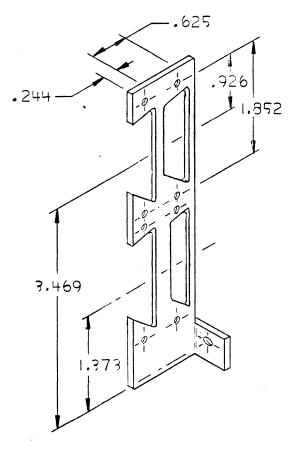

Physical example of a I/O board , a I/O Plate and a Piggyback board are shown in figure 4. (page 11)

Physical dimensions for the mother board is shown in figure 5. (Fortune drawing # 1001176 , page 12)

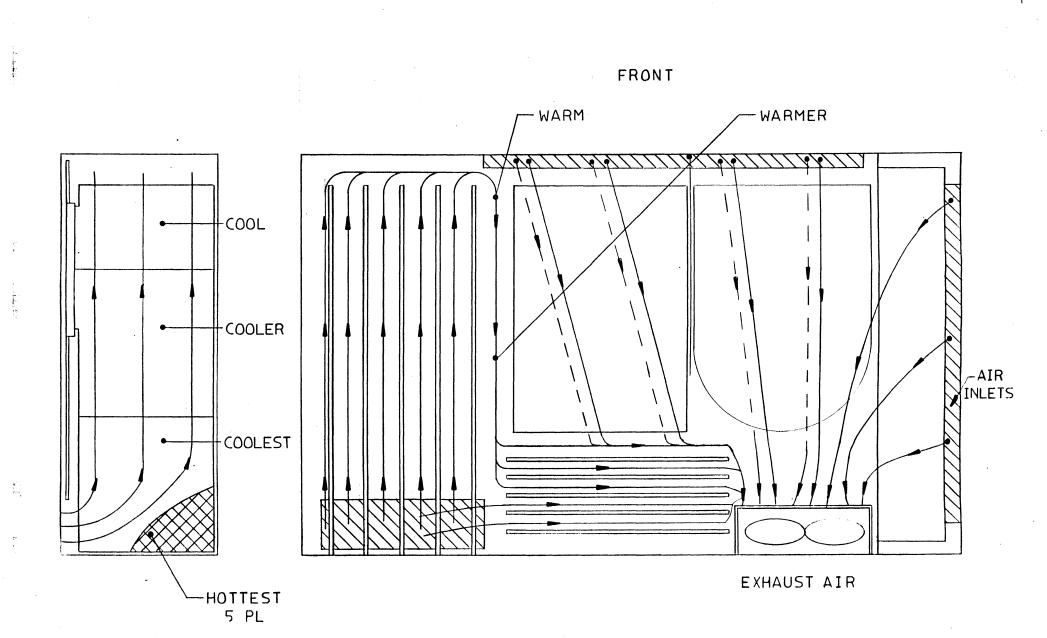

Example of the air flow in the 32/16 is shown in figure 6. (page 13)

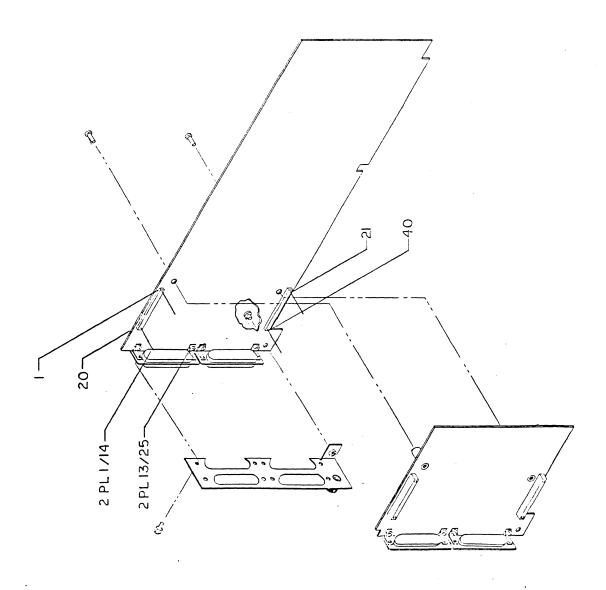

Physical example of a Fortune 32/16 system is shown in figures 7 (page 14), 8 (page 15), and 9 (page 16).

#### Fabrication Notes

The following fabrication notes apply to the board shown in figure 2 .

- 1. Materal: fl-gfm .062 c 1/1 AIA or equivalent.

- 2. Holes: Copper plate all holes (unless otherwise specified in hole schedule) to a minimum thickness of .001. Upon plating the holes, the surface will have a total copper thickness of two ounces.

- 3. all holes are to be drilled from component side and within .003 of pad center with no breakout . Finished diameter to be within +.003-.002 unless otherwise specified .

- 4. Tooling holes are to be drilled to within .002 of center . They will be unplated .

- 5. Maximum allowable line reduction due to pits , dents , and nicks to be 30%

- 6. Any line run or pad shall not vary in with or diameter more than +.003-.002 due to processing .

- 7. Minimum annular ring to be .004.

- 8. Registration between patterns shall not exceed + or .005 when measured across any diagonal .

- 9. Finish: 60/40 tin/lead plate to a total thickness of .0003/.0007 (maximum allowable deviation of tin lead composition to be 50/50).

- 10. Reflow is required. The tin/lead will be bright and shiny and pulled down to base laminate with all line edges covered.

- 11. Connector finigers: .000015 minimum gold plate over .000100 minimum low stress nickel. Blades to be beveled 30 deg.  $\times$  .025 to .031 both sides and 45 deg.  $\times$  .062 both ends.

- 12. All interior corner radii to be .06 nominal . All finished boards shall be marked with manufacturer's logo and board type designation as specified by UL which meets flammability rating of 94V-2 or better.

- 13. Apply solder mask to both sides using white expoxy ink to component side .

-04

ALL OTHER

TEATURES SAME

AS -01 EXCEPT

UPPER TAB

NOT REQD •

¥ SOR- KLES BY -00001 7 2 ø

۵ U 4  $\mathbf{z}$ FORTUNE SYSTEMS TO BE SANCARION OF BEING SANCARION 91 6hCOOO1 ۵ 7 ٣ Ŋ Ø

#### SECTION 3

#### Logical Specification

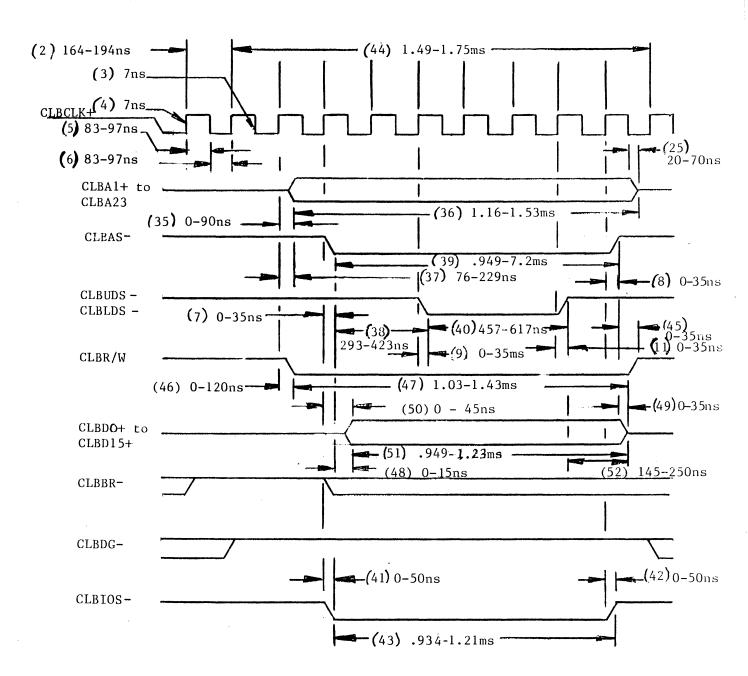

The following paragraphs define each of the siginal lines on the CLB. Eather a + or a - follows the name of each siginal , and indicates a positive true (+) or a negative true (-) condition . Figures 7-ll present the relative timing considerations . Numbers in brackets  $[\ n\ ]$  show the corresponding pin number .

CLBA1+ to CLBA23+ [ 8-30 ]

These 23 lines are used by the bus master device to select the slave device address to transfer to or from which data will be transferred . This can be either a memory location or a device register . For the 32/16 cpu CLBA21+ ,CLBA22+ and CLBA23+ are tied together .

The 24th address bit, AO, is specified by the presence of one or both of UDS and LDS (Upper/Lower Data Strobe). This is defined later under CLBUDS-, CLBLDS-.

Bus addresses between 0000000 hex and lfffff hex are assumed to be RAM or fast devices , and use the fast ram timing. Addresses between 780000 hex and 7fffff hex are assumed to be slow I/O devices, and use the special slow I/O timing.

During interrupt acknowledge cycles, Al-A3 contain the interrupt level number being acknowledged, and A4-A23 are all ones.

CLBD0+ to CLBD15+ [ 34-49 ]

These 16 lines transfer data between master and slave devices . For word transfers, all 16 lines are used. For byte transfers, CLBD8 - CLBD15 are used for even addresses (CLBUDS active), and CLBD0 - CLBD7 are used for odd addresses (CLBLDS active).

CLBAS- [ 58 ]

Bus address strobe is used by the master to indicate to the slave that valid addresses, device address decodes, and read/write controls are present on the bus. Slow-cycle devices that must know before CLBUDS/CLBLDS that they are going to be accessed may use address strobe as an indication. See note 1.

This line is unique to each of the five option slots (A-E), and indicates (when CLBAS is true) that the address on CLBAl+ to CLBA23+ is selecting the range of addresses assigned to the particular option slot. The CLBIOS- lines are valid only with CLBAS- active (low). The I/O Select line for option slot "A" is true for addresses between 7A0000 hex and 7AFFFF hex, for option slot "B" the addresses are from 7B0000 hex to 7BFFFF hex, etc. Each option thus has a 64 Kbyte address space for software driver ROMS, buffer RAMs, and various I/O register addresses. The only fixed addresses within this range are for the beginning of the software driver ROM, which must begin at relative location zero (7n0000 hex where n=slot A, B, C, D, or E) within the option slot's address space. See note 1.

CLBUDS- , CLBLDS- [ 59 ,60 ]

CLBUDS- (upper data strobe) and CLBLDS- (lower data strobe) are used by the bus master to indicate to the addressed slave device that the transfer is to begin. For fast (RAM) cycles, CLBUDS-/CLBLDS- will be presented concurrently with CLBAS+. For slow (I/O register) cycles, CLBUDS-/CLBLDS- will be preceded and followed by CLBAS+. Refer to the timming figures for the correct timing of these signals. See note 1.

CLBR/W- [ 57 ]

This signal indicates that the current bus cycle is either a "read "or a " write " . When low , it indicates a transfer of data from the current bus master to the addressed slave device. When high , it indicates a transfer data from the slave device to bus master . For byte trasfers (only one of CLBUDS or CLBLDS are true), the content of the unaddressed byte of the CLB DATA lines is unspecified. See note 1.

CLBI03-,CLBI04- [ 54 , 55 ]

These low-true levels indicate an interrupt request to the 68000 CPU on priority levels 3 and 4, respectively. These are "wired-OR" connections, and should be driven

#### CLBINTACKI3-, CLBINTACKI4- [ 67 , 69 ]

These two low-true signals are input to an I/O controller to indicate that; the CPU is acknowledging an interrupt on priority level 3 or 4, and signal that the device controller should place an interrupt vector on CLBDO - CLBD7 if this device was requesting an interrupt. A daisy-chain priority scheme is used with board slot E having top priority and board slot A having lowest priority. See Interrupt Acknowledge Protocol section .

### CLBINTACK03-, CLBINTACK04- [ 68 , 70 ]

If the signals (CLBINTACKI3-, CLBINTACKI4-) are received and the device controller was not requesting an interrupt on priority level 3 or 4, respectively, the corresponding CLBINTACKxx- line should be asserted so that devices in option slots further down the daisy-chain can respond to the interrupt acknowledgement. See Interrupt Acknowledge Protocol section .

## CLBBRO- to CLBR4- [ 71 ]

This low-true signal indicates to the bus arbitration circuitry that the device is requesting to become bus master. This signal is not wired-OR, and is unique to the option slot. CLBBR4- is highest priority while CLBBRO- is lowest priority. This signal must be asserted synchronously with CLBCLK.

## CLBBG0- to CLBG4- [ 72 ]

This low-true signal is unique to each option slot, and is asserted by the system bus arbitrator when this option has; requested to be bus master, the option is the highest priority device requesting, and the bus is available. The device controller must immediately place onto the bus the DMA address, address strobe, upper and/or lower data strobe, write (if a write cycle), and data (if a write cycle). The option board with the highest interrupt priority has the lowest priority in becoming the bus master. The option board with the lowest interrupt priority has the highest priority to becoming the bus master. This signal is synchronous with bus clock.

| SIGINAL                                                          | SLOI             |

|------------------------------------------------------------------|------------------|

| CLBR0-/CLBG0-<br>CLBR1-/CLBG1-<br>CLBR2-/CLBG2-<br>CLBR3-/CLBG3- | E<br>D<br>C<br>B |

| CLBR4-/CLBG4-                                                    | · A              |

CLBPERR-

[ 65 <u>1</u>

This low-true signal is sampled by the bus master during a DMA READ to determine if the data on the CLB DATA BUS has had a data error that has not been corrected by the system. See the DMA read timing figure.

This 5.5296 MHz square wave generates the timing signals in the device controller to maintain synchronous characteristics required for conforming to the various bus protocols. All control signals (execpt as noted) sent to or from a device on the CLB must be synchronous with clock. The only exception is the interrupt request lines (CLBIO3- and CLBIO4-) which may be asynchronous since the CPU contains synchronizers for these signals. Note that some signals are referenced to the positive going edge of the clock signal, while others are referenced to the negative going edge. Refer to the timing diagrams for specifics on each signal. See note 1.

CLBRESET-

[ 51 ]

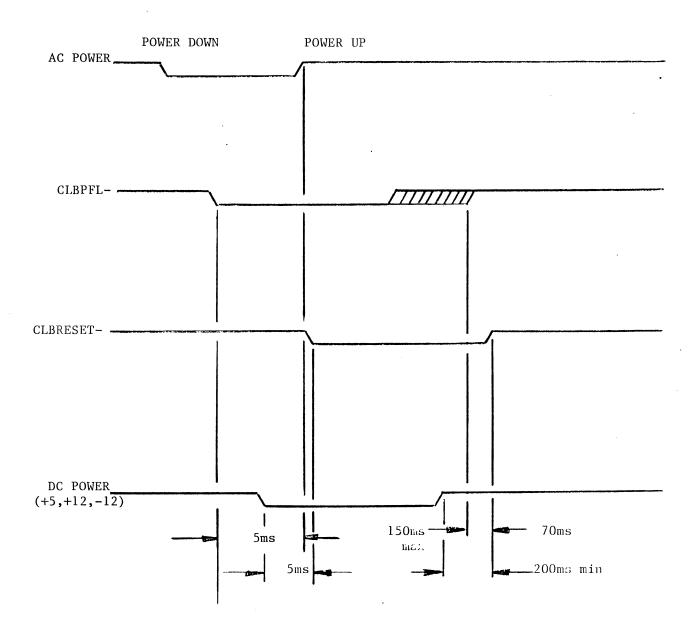

This low-true signal indicates that the I/O device controller should reset itself to a known and consistent state. Reset must clear any interrupt requests or bus request, and must cause the device control logic to cease actively driving the bus (address, data, and controls). If there is a vlotage senes module in the system then see the power fail timing figure.

CLBPRESENT-

[ 73 ]

This pin must be connected to logic ground on the device option board. It signals to the CPU and the interrupt acknowledge daisy-chain circuitry that there is an option board plugged into this slot.

CLBPFL-

[ 66 ]

This low-true signal provides a warning that a power fail condition is about to occur. This signal will become active about 5 msec prior to actual power failure. This signal is used by any device (disk, tape) that requires early warning so they may complete a write, and so they will not start a write with this condition. This siginal may go down and back up a number of times before power failure. If there is a vlotage senes module in the system then see the power fail timing figure 10 page 21.

**CLBSPARE**

[ 52 , 53 , 64 ]

These signal pins are not currently connected. They are reserved for future definition by Fortune Systems Corporation.

+5, +/-12, GROUND

[ 56 , 75 , 76 , 1 , 2 , 3 , 4 , 7 , 31 , 32 , 33 , 50 , 61 , 63 , 77 , 78 , 79 , 80 ]

These signals supply operating voltages for the device controller option boards. There are nine connections for ground, four for +5 volts, and two each for +/-12, thus ensuring a noise-free environment on the option board. Each of the like signals should be connected in a mesh configuration on the option board to further reduce the possibility of unwanted noise. Note see I/O Power Distribution section .

T2+

[ 56 ]

This siginal , Timing pulse 2 , is not to be used by  $\ensuremath{\text{I}}/0$  boards .

(NOTE 1 See section on Recivers, Drivers , and Termination .)

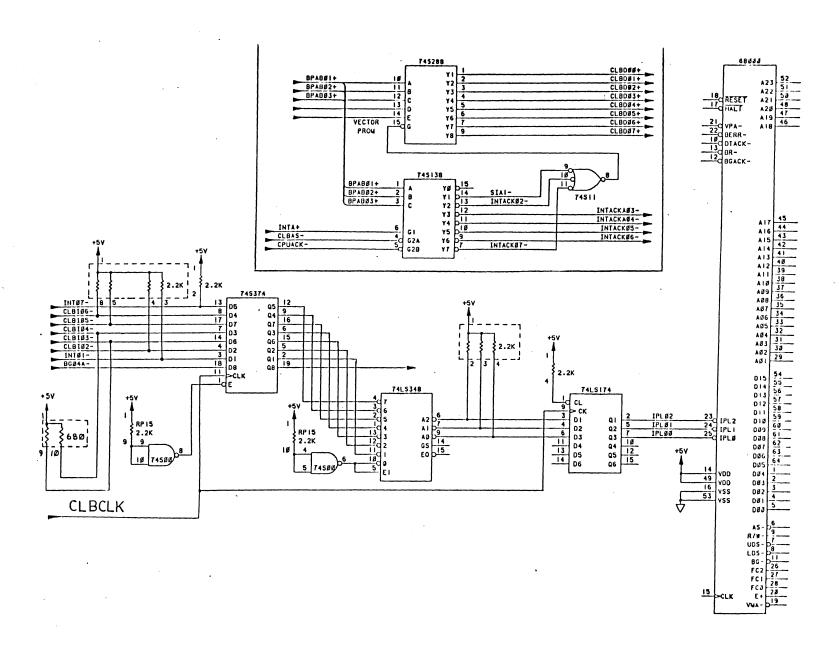

### Interrupt Acknowledge Protocol

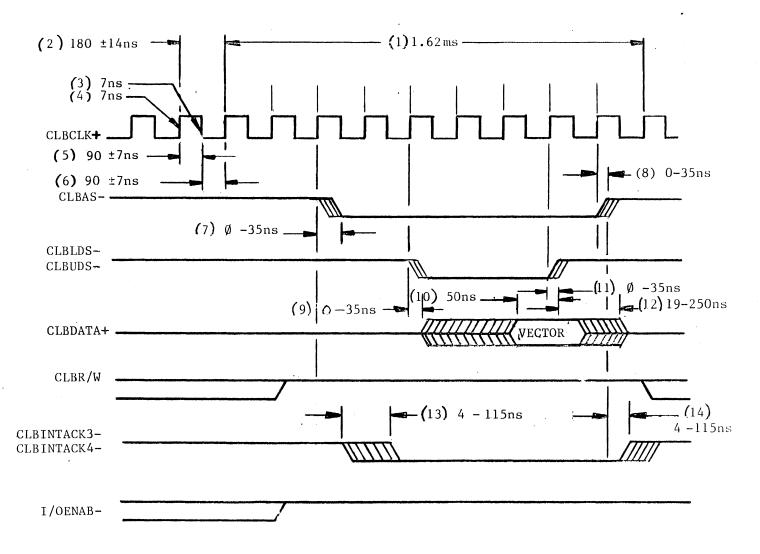

The interrupt protocol on the CLB allows asynchronous interrupts to be issued by I/O controllers to the microprocessor at any time. Interrupt acknowledge timing is a synchronous process initiated by the microprocessor. The interrupt acknowledge sequence is as follows:

- Interrupt request is recived by the processor. The processor will compare the interrupt level in the status register and wait for the current instruction to complete. If the priorty of the pending interrupt is greater than the processor priority, the processor will then ask for a CLB cycle.

- 2. The CLBR/W line will become active (high) as late as CLB cycle 1 depending on what the previous process happened to be across the CLB. This line high conditions the CLB for a read (interrupt vector) from an interrupting I/O controller.

- 3. During CLB cycle 2, CLBAS-, CLBINTACK3- or CLBINTACK4- become active (low) and I/OENAB- becomes active (high). Each I/O controller upon detection of CLBAS- becoming active determines whether to block CLBINTACK3- or CLBINTACK4- or to pass it on to the next I/O controller with lower priority. While CLBAS- is active, no I/O controller is allowed to block CLBINTACK3- or CLBINTACK4- signal unless the controler is the one intrrupting.

- 4. For the decision required above , and with the worst case of four I/O controller boards prior to the last I/O controller board (25 ns delay maximum per board), CLBINTACK3- or CLBINTACK4will be valid at the beginning of CLB cycle 4.

- 5. During CLB cycle 4, CLBLDS- and CLBUDS- will become active(low). The I/O controller that had blocked the CLBINTACK3- or CLBINTACK4must place its interrupt vector on CLBDO to CLBD7 no later than 20ns into CLB cycle 6. The interrupt vector must remain on CLBDO to CLBD7 until at least 19 ns after CLBUDS- or CLBLDS- becomes inactive and no later than the middle of CLB cycle 7.

- 6. At the beginning of CLB cycle 8, CLBAS-, CLBINTACK3- or CLBINTACK4-, and I/OENAB- become inactive. The interrupt acknowledge process is now complete.

| <b>a</b>     |                   |                                                                          |               |                |                  |

|--------------|-------------------|--------------------------------------------------------------------------|---------------|----------------|------------------|

|              | Symbol            | Parameter                                                                | Min.          | TYP.           | Max.             |

| (1)          | tia               | Interrupt Acknowledge Time                                               | 1.49ms        | 1.62ms         | 1.75ms           |

| (2)          | tcy               | Clock Cycle                                                              | 164ns         | 180ns          | 194ns            |

| (3)          | tcf               | Clock Fall Time                                                          |               |                | 7ns              |

| (4)          | tcr               | Clock Rise Time                                                          |               |                | 7ns              |

| (5)          | tch               | Clock With High                                                          | 83ns          | 90ns           | 97ns             |

| (6)          | tcl               | Clock With Low                                                           | 83ns          | 90ns           | 97ns             |

| (7)          | tchasl            | Clock High to Address Strobe Low                                         | 0ns           |                | 35ns             |

| (8)          | tchash            | Clock HIGH to Address Strobe High                                        | 0ns           |                | 35ns             |

| (9)          | tchdsl            | Clock High to Data Strobe Low                                            | 0ns           |                | 35ns             |

|              | tdvdsh            | Data Valid to Data Strobe High                                           | 50ns          |                |                  |

|              | tchdsh            | Clock High to Data Strobe High                                           | 0ns           |                | 35ns             |

|              | tdshdi            | Data Strobe High to Data Invalid                                         | 19ns          |                | 250ns            |

| (13)         |                   | Adress Strope Low to Int. Ack. Low                                       | 4ns           |                | 115ns            |

| (14)         |                   | Adress Strobe Inactive to Int. Invalid                                   | 4ns           |                | 115ns            |

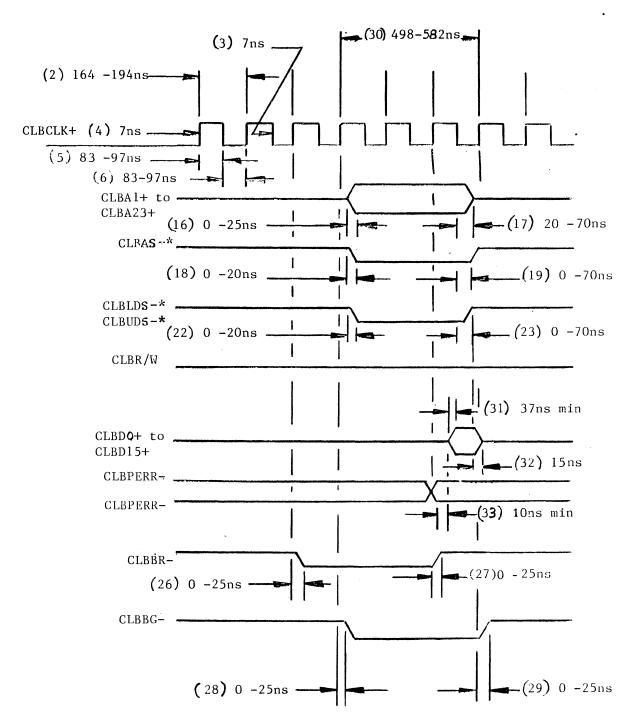

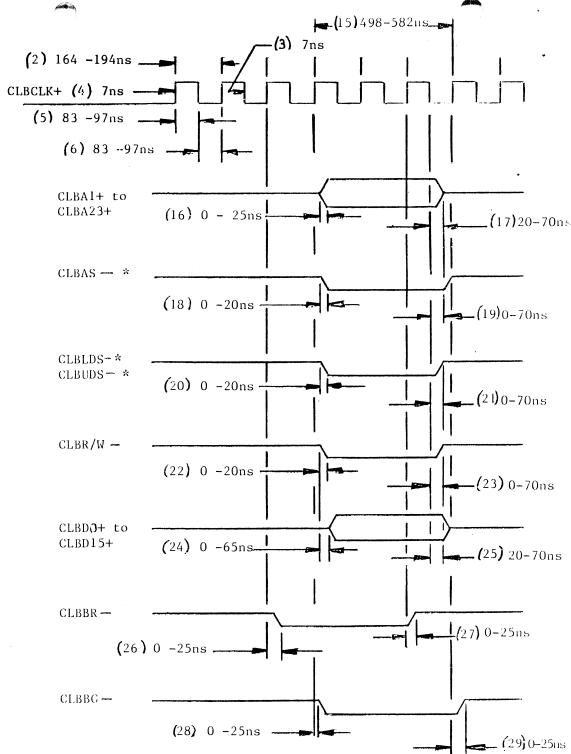

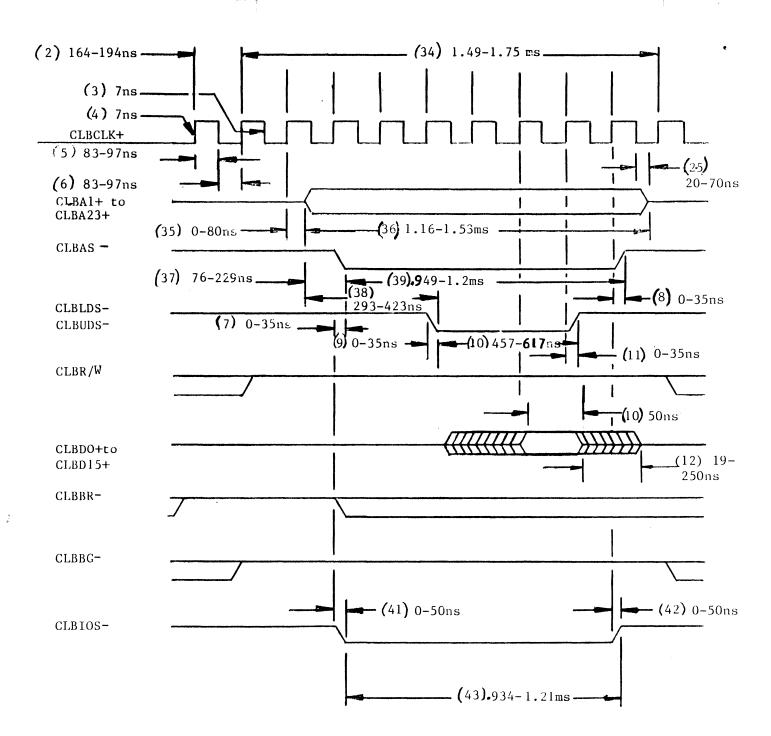

| (15)         | _                 |                                                                          | 498ns         | 5 <b>4</b> 0ns | 582ns            |

| (16)         |                   | Bus Grant to Address Valid                                               | 0ns           |                | 25ns             |

| (17)         | tclai             |                                                                          | 20ns          |                | 70ns             |

| (18)         | tbgas             |                                                                          | 0ns           |                | 20ns             |

| (19)<br>(20) | tclash            | Clock Low to Address Strobe high<br>Bus Grant to Data Strobe Valid       | Ons<br>Ons    |                | 70ns<br>20ns     |

| (21)         | tbgdsv<br>tcldsi  | Clock Low to Data Strobe Invalid                                         | Ons           |                | 70ns             |

| (21)         | tbgrwv            | Bus Grant to Read Write Valid                                            | Ons           |                | 20ns             |

| (23)         | tclrwi            | Clock Low to Read Write Invalid                                          | Ons           |                | 70ns             |

| (24)         |                   | Bus Grant to Data Valid                                                  | 0ns           |                | 65ns             |

| (25)         |                   | Clock Low to Data Invalid                                                | 20ns          |                | 70ns             |

| (26)         | tchbr             | Clock High to Bus Request                                                | 0ns           |                | 25ns             |

| (27)         | tchbri            | Clock High to Bus Request Invalid                                        | 0ns           |                | 25ns             |

| (28)         | tchbg             | Clock High to Bus Grant                                                  | 0ns           |                | 25ns             |

| (29)         | tchdgi            | Clock High to Bus Grant Invalid                                          | 0ns           |                | 25ns             |

| (30)         | tdmarcy           |                                                                          | <b>49</b> 8ns | 540ns          |                  |

| (31)         | tdvcl             | Data Valid to Clock Low                                                  | 37ns          |                |                  |

| (32)         | tdsldi            | Data Strobe Low to Data Invalid                                          | 15ns          |                |                  |

| (33)         | tbecl             | Bus Error to Clock Low                                                   | 10ns          |                |                  |