Four-Phase Systems

System IV/70

Computer Reference Manual

Four-Phase Systems, Inc. 10420 North Tantau Avenue Cupertino, California 95014

Document Number SIV/70-11-1C

Stock Number 33C

Issue A: 1 November 1970 Issue B: 1 April 1971 Issue C: 1 October 1972

Specifications subject to change.

Copyright 1972, 1971, 1970 Four-Phase Systems, Inc.

All rights reserved.

Price: \$4.50

# System IV/70

# Computer Reference Manual

### LIST OF EFFECTIVE PAGES

#### THIS PUBLICATION CONTAINS 110 PAGES CONSISTING OF THE FOLLOWING:

Issue

Page Number

Page Number Issue Inside Front Cover (Blank). . ---Title Page . . . . . . . . . . . . 1 Oct 72 A . . . . . . . . . . . . . . . 1 Oct 72 i thru iv . . . . . . . . . . . . . . . . 1 Oct 72  $1{-}1 \quad \dots \quad \dots \quad 1 \text{ Oct } 72$ 1-2 (Blank) . . . . . . . . . 1 Oct 72 2-1 thru 2-2 . . . . . . . . 1 Oct 72 3-1 thru 3-10 . . . . . . . . 1 Oct 72 4-1 thru 4-24 ..... 1 Oct 72 5-1 thru 5-17 . . . . . . . . 1 Oct 72 5-18 (Blank) . . . . . . . . 1 Oct 72 6-1 thru 6-5 . . . . . . . . 1 Oct 72 6-6 (Blank) . . . . . . . . . 1 Oct 72 7-1 thru 7-3 . . . . . . . . 1 Oct 72 7-4 (Blank) . . . . . . . . . 1 Oct 72

8-1 thru 8-9 . . . . . . . . 1 Oct 72 8-10 (Blank) . . . . . . . . 1 Oct 72 9-1 thru 9-7 . . . . . . . . 1 Oct 72 9-8 (Blank) . . . . . . . . . 1 Oct 72 A-1 thru A-4 ..... 1 Oct 72

B-2 (Blank) . . . . . . . . . . 1 Oct 72 C-1 thru C-5..... 1 Oct 72 C-6 (Blank) . . . . . . . . . 1 Oct 72 D-1 ..... 1 Oct 72 D-2 (Blank) . . . . . . . . . 1 Oct 72 User's Comments . . . . . . . - - -Reply Card . . . . . . . . . . . - - -Inside Back Cover (Blank) . . ---Back Cover . . . . . . . . . . . . - - -

The asterisk indicates pages changed, added, or deleted by the current change. The portion of the text affected by the current change (or the portion of the text changed for this issue) is indicated by a vertical line in the outer margins of the page.

# **Contents**

| 1 | Introduction                                                                                                                                                                                                                                                                                                        |                                                                                                                     |   | Logical Instructions                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 2 | System Organization                                                                                                                                                                                                                                                                                                 |                                                                                                                     |   | Control Instructions                                                                                                                                                                                                                                                                                                                                                                                                           | 4-23                                                                                           |

|   | Introduction                                                                                                                                                                                                                                                                                                        | 2-1                                                                                                                 | 5 | String Manipulation Instructions                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                |

|   | Control Logic                                                                                                                                                                                                                                                                                                       | 2-1<br>2-1<br>2-1<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2                                                  |   | Whole Word Stack Instructions                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                |

| 2 | Machine Language Programming                                                                                                                                                                                                                                                                                        |                                                                                                                     | 6 | Input/Output System and Instructions                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                |

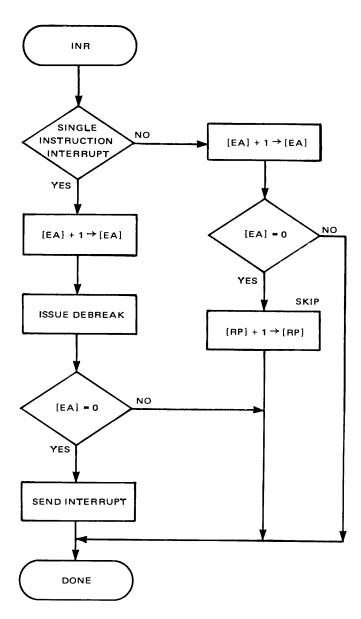

|   | Introduction                                                                                                                                                                                                                                                                                                        | 3-1<br>3-1<br>3-2<br>3-3<br>3-3<br>3-3<br>3-3<br>3-4<br>3-4<br>3-4<br>3-5<br>3-5<br>3-5<br>3-5<br>3-5<br>3-5<br>3-5 | 7 | Peripheral Unit I/O. Organization Device Address Peripheral Units I/O Instructions Execution of I/O Instructions External Command and External Sense I/O. Console Keys Input Interrupt System and Instructions Priority Interrupt Levels Interrupt Processing Normal Interrupt Processing Single Instruction Processing Indirect Interrupt Processing Interrupt Controls Non-Interruptable Instructions Interrupt Instructions | 6-1<br>6-2<br>6-2<br>6-2<br>6-4<br>6-5<br>6-5<br>7-1<br>7-1<br>7-2<br>7-2<br>7-2<br>7-2<br>7-3 |

|   | B3 Interface                                                                                                                                                                                                                                                                                                        | 3-5<br>3-7<br>3-7                                                                                                   | 8 | Assembly Language Programming General                                                                                                                                                                                                                                                                                                                                                                                          | 8-1                                                                                            |

|   | Condition Codes Arithmetic Trap  Programming for the Video/Keyboard Video Display Keyboard Instruction Descriptions                                                                                                                                                                                                 | 3-7<br>3-8<br>3-8<br>3-8<br>3-9<br>3-9                                                                              |   | Assembler Programming Programs and Routines Program Elements Statements Symbols Expressions                                                                                                                                                                                                                                                                                                                                    | 8-1<br>8-1<br>8-1<br>8-1<br>8-1<br>8-2                                                         |

| 4 | Word Oriented Instructions                                                                                                                                                                                                                                                                                          |                                                                                                                     |   | Assembler Language Coding                                                                                                                                                                                                                                                                                                                                                                                                      | 8-2<br>8-4                                                                                     |

|   | Load/Store Instructions Fixed-Point Arithmetic Instructions Floating Point Instructions Comparison Instructions Shift Instructions Branch and Skip Instructions Unconditional Branch Instructions Conditional Branch Instructions Branch and Count Instructions Skip Instructions Register-to-Register Instructions | 4-8 $4-9$ $4-12$ $4-12$ $4-14$ $4-15$ $4-16$                                                                        | 9 | Sequence of Events Assembler Instructions General Data Control Directives Assembler Control Directives Error Conditions  System Operation Introduction Manual Data Display and Entry Register Data Display                                                                                                                                                                                                                     | 8-5<br>8-5<br>8-5<br>8-6<br>8-7<br>8-9<br>9-1<br>9-1<br>9-1                                    |

1 October 1972 i

Contents SIV/70-11-1C

| Memory Data Display                     | 9-1 | Using the Interrupt Switch                     | 9-5 |

|-----------------------------------------|-----|------------------------------------------------|-----|

| Register Data and Condition Code Entry  | 9-1 | Halting and Clearing Errors                    |     |

| Memory Data Entry                       | 9-1 | Automatically Entering a Word into a Register. |     |

| Program Execution                       | 9-2 | Tape Drive Operating Procedures                | 9-6 |

| Automatic Execution                     | 9-2 | Loading Tape                                   | 9-6 |

| Manual Execution                        | 9-2 | Unloading Tape                                 |     |

| Repeated Instruction Execution          | 9-2 | Controls and Indicators                        |     |

| Initializing the System                 | 9-4 |                                                |     |

| Turning Power On                        | 9-4 |                                                |     |

| Bootstrap Loading for Systems With a    |     | A System IV/70 Character Set                   |     |

| BOOT Switch                             | 94  | B Assembler Directives                         |     |

| Bootstrap Loading for Systems Without a |     | C Machine Instructions                         |     |

| BOOT Switch                             | 9-4 | C Machine Instructions                         |     |

| Miscellaneous Procedures                | 9-5 | D Powers of 2 and 8                            |     |

|                                         |     |                                                |     |

1 October 1972

ii

# Illustrations

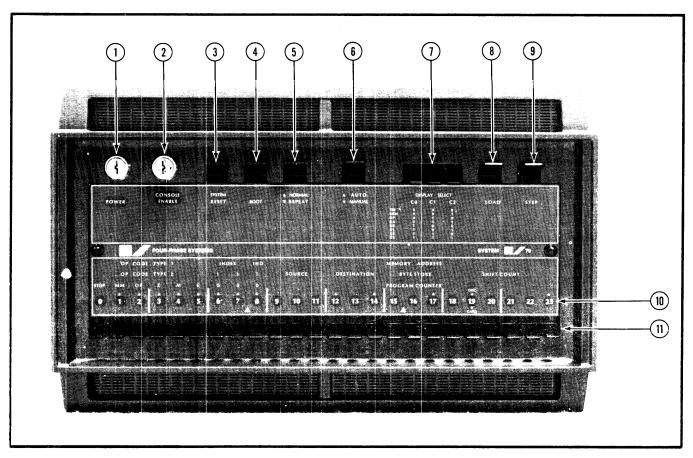

|            | System IV/70 Console and Video Display                                           |             | 6-1 | Peripheral Unit I/O Structure               | 6-1 |  |  |

|------------|----------------------------------------------------------------------------------|-------------|-----|---------------------------------------------|-----|--|--|

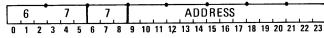

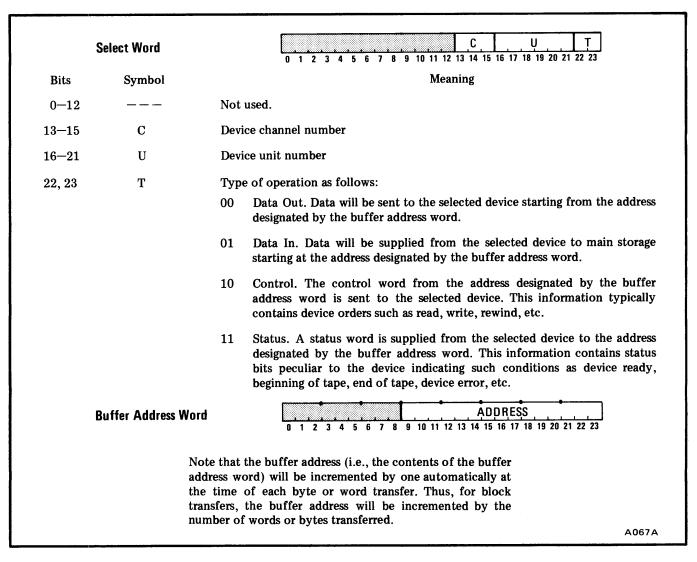

| 2-1        | Terminals                                                                        | iv          | 6-2 | Select Word and Buffer Address Word Formats | 6-3 |  |  |

|            | Architecture                                                                     | 2-1         | 8-1 | System IV/70 Assembler Language Coding      |     |  |  |

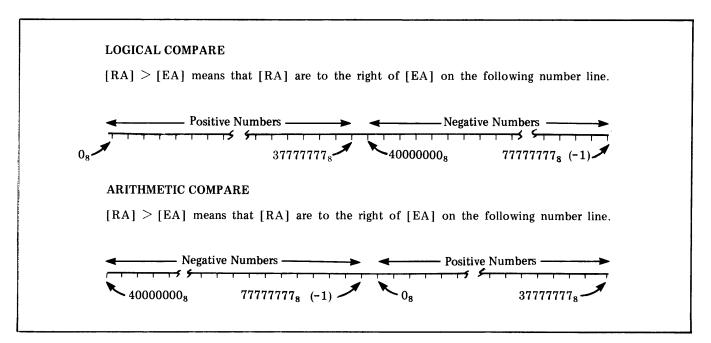

| 4-1        | Logical and Arithmetic Compare                                                   | 4-8         |     | Form                                        | 8-3 |  |  |

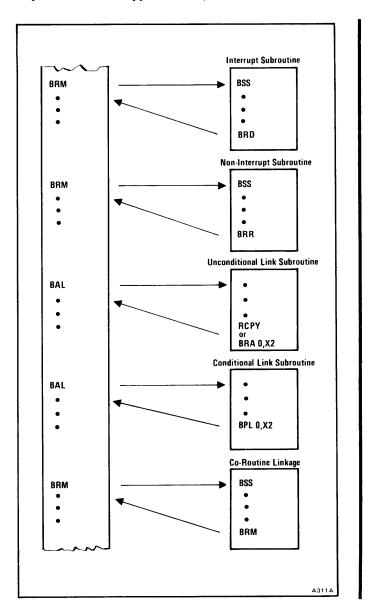

| 4-2        | Branching to Subroutines                                                         | 4-12        | 8-2 | Assembler Output Listing                    | 8-5 |  |  |

| 5-1        | Character Byte Control, Shift Count, and                                         |             | 9-1 | Console Controls and Indicators             | 9-2 |  |  |

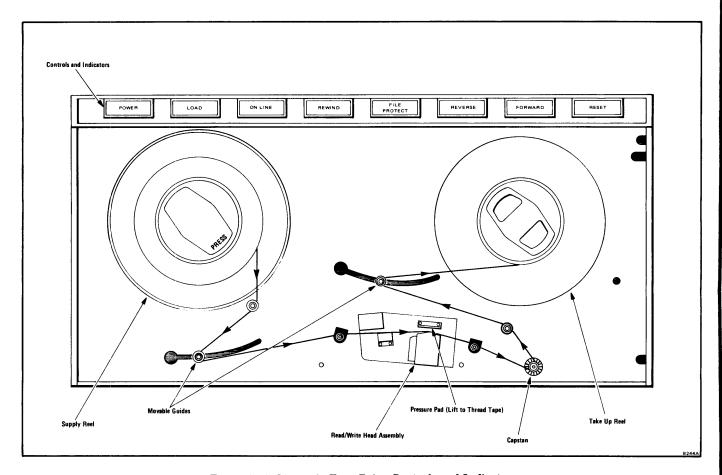

|            | Linkage Tables                                                                   | 5-4         | 9-2 | Magnetic Tape Drive Controls and Indicators | 9-7 |  |  |

| 5-2        | ${\bf Character\ Manipulation\ Instruction\ Operands\ .}$                        | 5-5         |     |                                             |     |  |  |

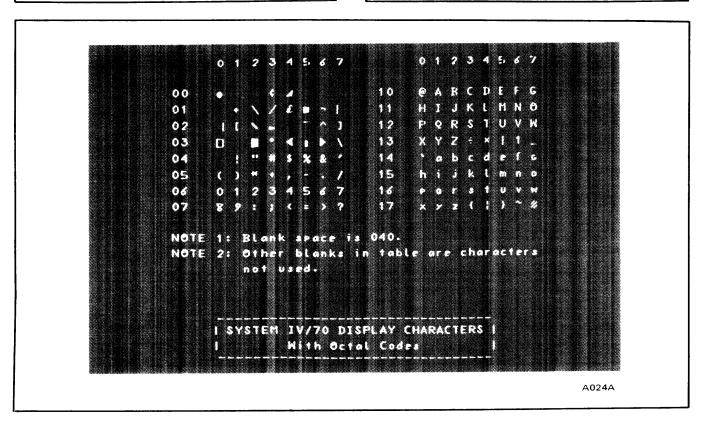

| 5-3        | Character List Processing Instructions                                           | 5-12        | A-1 | System IV/70 Display Characters             | A-4 |  |  |

|            |                                                                                  |             |     |                                             |     |  |  |

|            |                                                                                  | Tabl        | es  |                                             |     |  |  |

|            | Notation and Special Usages                                                      | <b>Tabl</b> |     | Condition Codes for Logical and Arithmetic  |     |  |  |

|            | Notation and Special Usages                                                      |             | 4-1 | Comparisons                                 |     |  |  |

| 3-1<br>3-2 |                                                                                  | 3-1         | 4-1 |                                             |     |  |  |

| 3-1<br>3-2 | Significance of Modification Field  Example of Indexing and Indirect Addressing. | 3-1<br>3-3  | 4-1 | Comparisons                                 |     |  |  |

1 October 1972

Frontispiece SIV/70-11-1C

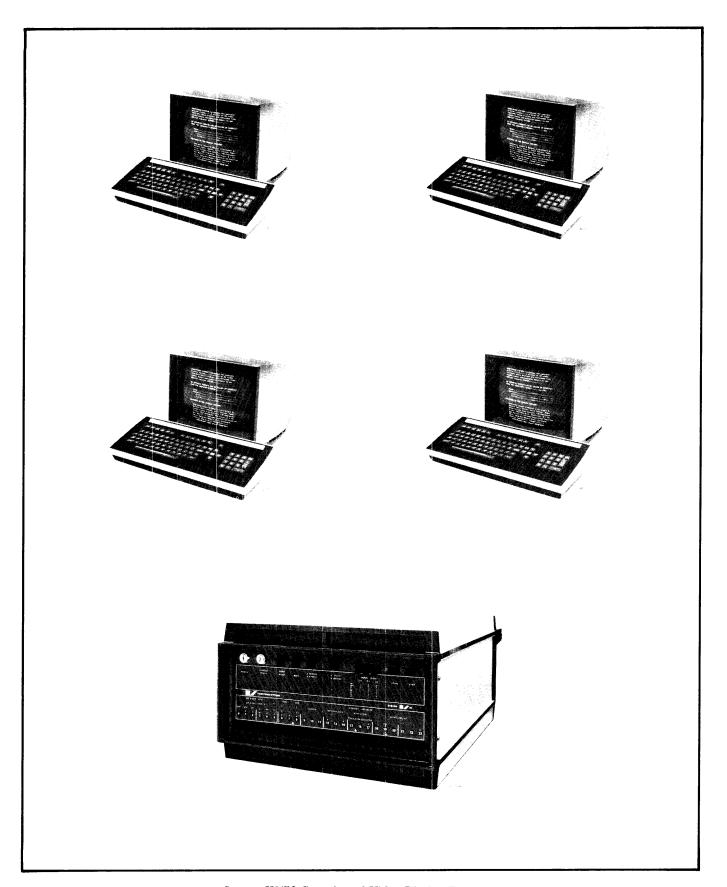

System IV/70 Console and Video Display Terminals

# Section 1 Introduction

System IV/70 is a computer-based data display and processing system designed for data entry and retrieval to and from data bases and computing systems. It interfaces with IBM 360/370 Systems locally or remotely through System IV/70 foreground communications packages without requiring the modification of IBM software. Subsets of this package completely simulate IBM 2848/2260 and 3270 data station complexes.

The System IV/70 consists of a Processing Unit, up to 32 Video Display Terminals, and peripheral devices.

The System IV/70 Processing Unit is a character-oriented medium-scale computer with a 2.0 microsecond cycle time and semiconductor main frame memory. Two units are available, the 7001 and 7002. The 7001 has a memory size expandable from 12K to 24K 8-bit bytes in 6K byte increments; the 7002 has a memory size of 48K, 72K, or 96K bytes. Both are addressable to 96K bytes. Under software control, parity is calculated on every memory write and checked on every read.

Both the 7001 and 7002 have a repertoire of 113 machine instructions including decimal arithmetic, binary fixed-point and floating-point arithmetic, translate-test, supervisor trap, register-to-register, interrupt control, list processing with push-pop stacks, and variable length character string manipulation. The Decimal Option expands the 7002 instruction set to 119 instructions. Representative operation speeds are:

| • | Character move                   | $40 \mu s + 2.7 \mu s/byte$ |

|---|----------------------------------|-----------------------------|

| • | Character compare                | $28 \mu s + 4 \mu s/byte$   |

| • | Decimal add or subtract          | $36 \mu s + 5.3 \mu s/byte$ |

| • | Binary add, subtract, or compare | $16 \ \mu s/24 \ bits$      |

The Computer Input/Output structure includes eight I/O channels, each of which may service up to 64 devices, and eight levels of nested hardware priority interrupt. All types of I/O transfer are handled with a single I/O instruction.

A maximum I/O rate of up to 375,000 bytes/second may be reached for block transfers, and up to 39,000 bytes/second for interrupt system transfers.

Each Video Display Terminal consists of a Video Display Unit (screen) and a separate Keyboard Unit. The Video Display Unit offers up to 1944 characters per screen in formats of 48 or 81 characters per line with 6, 12, or 24 lines per screen. The character set is augmented ASCII with 7 x 9 dot matrix. All video display is under computer control; refresh and display of keyboard-entered or program-generated characters are automatic. Standard features include split screen, protected display areas, and transmission of selected display data, all under software control. The Keyboard Unit produces 173 character codes including control and function codes. A standard adding machine keyboard is also included. Optional Keyboards offer special keytops for particular applications. Standard edit capability includes character insert and delete, line insert and delete, roll up/down, tab, erase, and ten cursor control functions, all under software control.

Standard peripherals include removable cartridge disc drives, asynchronous and bisynchronous communications interfaces, IBM-compatible magnetic tape drives, high-speed printers, and a card reader. Standard software packages include foreground video-display control packages including an advanced key-to-disc data entry system, a 2260/2848 simulator package, terminal communications software, disc operating system with sort and other utility programs, and a video-oriented COBOL compiler.

The 7002 Processing Unit offers all the proven features of the standard model 7001 with larger memory size and extra features. The 7002 is available with a standard 48K byte memory or an optional 72K or 96K bytes. Other optional features include 81 character by 24 line video displays (which may be intermixed with 81 by 12 displays), a lightpen for menu search on the video display, dual intensity screens with software control of intensity and blanking, and an audible keyboard alarm under software control.

# Section 2 System Organization

#### INTRODUCTION

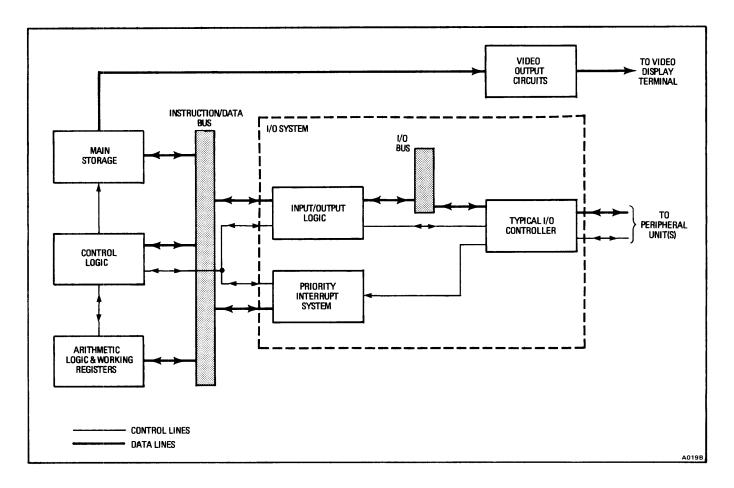

The System IV/70 Processing Unit is organized into Control Logic, Arithmetic Logic, Main Memory, the Input/Output system, and the Video Output Circuits. See Figure 2-1 for this configuration.

#### **CONTROL LOGIC**

The Control Logic initiates and controls all functions related to implementation of the computer program instructions. All these functions take place under control of a microprogram, which is stored in read only memory and which generates control signals for all the subsystems of the computer. These signals control inputting (both through peripherals and the control panel), processing, testing, storing, and outputting of data and instructions.

#### **ARITHMETIC LOGIC**

The Arithmetic Logic performs all data processing functions, under control of the microprogram. Processing of numeric, character, and logical data; setting of condition codes; and generation of addresses are among the functions of this subsystem. The Arithmetic Logic interacts with the Control Logic in the performance of data processing functions. The eight programmer-addressable working registers (R0, R1, RP, RA, RB, X1, X2, and X3) are contained in the Arithmetic Logic.

#### **MAIN MEMORY**

The Processing Unit's main storage consists of large-scale-integrated circuit random-access memory. The memory is all directly addressable by the Control Logic, which controls data transfer in and out of memory.

Figure 2-1. Simplified Block Diagram of System Architecture

1 October 1972 2—1

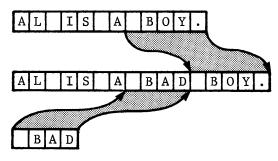

#### **INPUT/OUTPUT SYSTEM**

The I/O system consists of the priority interrupt system, the I/O logic, the I/O controllers, and the peripheral units.

#### **Priority Interrupt System**

A nested priority system is provided with eight levels of priority and 64 chained unit addresses within each level. Each level of interrupt is connected to an I/O channel of the same number; a unique memory address is also accessible from each level to facilitate software processing of input and output over the various channels. The priority interrupt levels are truly nested, in that a level of lower priority may be interrupted during its processing by one of higher priority. These interruptions do not upset the processing of any level or of the background program. Section 5 discusses the priority interrupt structure in detail.

#### I/O Logic

The I/O logic responds to the I/O controllers, the Control Logic, and the interrupt system to switch I/O functions and channel and unit addresses in an orderly manner. Data to and from the I/O controllers is channeled through the I/O logic.

#### I/O Controllers

Each I/O device interfaces with a controller, which performs buffering, switching, and serial/parallel processing to relate the peripherals to the I/O interface. Controllers also generate interrupt signals to initiate data transfers. Each controller is designed to interface its device or devices to the computer; up to 18 controllers can be used with one System IV/70 Processing Unit.

#### **Peripheral Units**

The computer can interface (using the appropriate con-

troller) with any conventional input/output device, being fast enough to handle any widely-used data rate and flexible enough for any format. In addition, a 173-character code keyboard is used with each video display to form a highly flexible two-unit terminal. The keyboard interfaces with its own controller, which can service numerous keyboards.

#### VIDEO OUTPUT CIRCUITS

The Video Output Circuits receive information stored in Main Memory every other memory cycle as the result of a continual scanning process which cycles through all of memory. However, only selected areas of the memory are gated through the Video Output Circuits to be displayed at the video terminals. The addresses of these locations are listed under the table, "Dedicated Memory Locations" in Section 3.

For the 7001 Processing Unit, the first four 3072-byte blocks of memory can support up to eight 24-line, 48 character-per-line screens or eight 12-line, 81 character-per-line screens. For the 7002 Processing Unit, the first 16 3072-byte blocks of memory can support up to 32 24-line, 48 character-per-line screens or 16 24-line, 81 character-per-line screens. Using fewer lines per screen allows up to four screens to be supported by each video display area up to a maximum of 32 screens per system.

In general, the output is under computer program control: if the contents of any memory location in the dedicated area is changed, the display will be changed correspondingly. Although the software assembler and loader for System IV/70 are designed to facilitate relocatable programming, they are designed so that absolute code may be included with relocatable code. Thus, programmed transfers of data into the dedicated areas will automatically display data for the user.

2-2 1 October 1972

# Section 3 Machine Language Programming

#### INTRODUCTION

This section covers machine language programming in detail. Topics are Formats, Instructions, Hardware Organization, Programming for the Video/Keyboard, and Instruction Descriptions. "Formats" deals with data and instruction formats, emphasizing the formats needed by the machine language as contrasted with assembly language formats. For the assembly language see Section 8. "Instructions" describes the various fields used in instructions. "Hardware Organization" describes hardware details needed by the machine language programmer: dedicated addresses, specialized usages, constant and variable registers, and the like are emphasized. "Instruction Descriptions" explains the format used to describe the machine language instructions. The instructions themselves are covered in the following four sections. Table 3-1 defines notation used in specialized or conventional ways in this discussion.

#### **FORMATS**

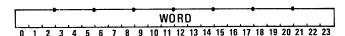

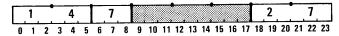

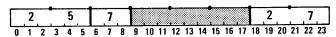

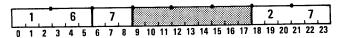

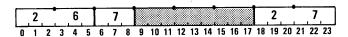

Formats for data and instruction words are based on the computer's 24-bit word with the bit-positions being numbered from 0 (leftmost or most significant) through 23 (rightmost or least significant).

This information format is used to represent both data and instructions. Instructions always occupy a single 24-bit word; numeric data may occupy single, double, or triple word formats; and character data may be manipulated in blocks of up to 256 words. For readability and convenience, the bits of a word are sometimes marked off in groups of three and expressed in octal digits. The 24-bit word then becomes eight octal digits.

Table 3-1. Notation and Special Usages

| NOTATION                | MEANING                                                                                                                                                                                         |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X                       | A symbol or name specifying a register or memory location.                                                                                                                                      |

| [X]                     | The contents of the memory location or register specified by X. [X] is a number and may specify a memory location or a register. Read [RA] as "the contents of RA."                             |

| [RA] <sub>9-23</sub>    | Bits 9 through 23 of the contents of RA.                                                                                                                                                        |

| [[X]]                   | The contents of the memory location specified by the contents of the memory location or register specified by X. Read [[RA]] as "the contents of the location specified by the contents of RA." |

| → or ←                  | Replacement symbol. Read $EA \rightarrow [RA]$ or $[RA] \leftarrow EA$ as "the effective address replaces the contents of RA" (or "the effective address is loaded into RA").                   |

| $\cap$                  | "Intersection" or restrictive operator. Also called logical AND; equivalent to • in some notations.                                                                                             |

| U                       | "Union" or permissive operator. Also called logical OR; equivalent to + in some notations.                                                                                                      |

| 0                       | XOR or differential operator. Also called exclusive OR; equivalent to $\oplus$ in some notations.                                                                                               |

| $\overline{\mathbf{x}}$ | The inverse of X; read "not X" or "X-bar."                                                                                                                                                      |

1 October 1972 3–1

# Section 3 Machine Language Programming

#### **Data Formats**

#### CHARACTER DATA

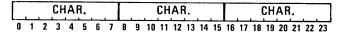

Characters, including decimal numbers, are represented by 8-bit bytes. Three characters can be packed to a single computer word.

The internal character code used is ASCII and is shown in Appendix A.

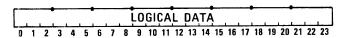

#### LOGICAL DATA

Logical data is represented by full 24-bit words. The logical operations treat all the bits of the word in the same manner, as contrasted with arithmetic operations which treat the most significant bit (bit 0) as a sign bit.

#### ARITHMETIC DATA

All arithmetic data is represented in 2's complement form with bit position 0 as the sign bit; 0 means positive and 1 negative. Therefore, in positive numbers ones are significant bits and in negative numbers zeros are significant bits. Arithmetic shifting operations do not affect the sign bit: these operations shift around the 0 bit. Arithmetic data is of two kinds: (1) fixed point or integer, and (2) floating point or fraction-and-exponent.

#### **Fixed Point Data**

Fixed-point numbers are stored as 23-bit integers with the binary point assumed to be to the right of the least significant bit. The computer operates on these numbers arithmetically in a two's complement number system. Each 23-bit number has the equivalent precision of just under seven decimal digits; i.e., from  $-2^{23}$  (= -8,388,608) to  $+2^{23}$  -1 (= 8,388,607).

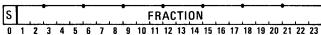

#### Floating Point Data

The computer accommodates two number formats for floating point arithmetic: standard and extended. Both formats consist of a fraction (or mantissa) and an exponent (power of two multiplier, or characteristic). The arithmetic registers used to store data during the execution of each floating point instruction are noted in the description of that instruction.

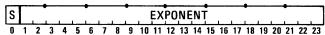

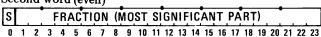

STANDARD FORMAT. The number is stored in consecutive memory locations with the first word (fraction) in an even location.

#### Second word

The fractional part of a standard (single-precision), floating point number is a 24-bit proper fraction, with the leading bit being the sign and the assumed binary point just to the left of the most significant magnitude bit. The floating-point exponent (power of two) is a 24-bit integer with a leading sign bit. The standard hardware operates on both fraction and exponent in two's complement form.

Single-precision, floating-point numbers have just under seven decimal digits of precision and a decimally equivalent exponent range of  $\pm$  10<sup>2</sup>,5<sup>25</sup>,2<sup>23</sup> (= 10<sup>2<sup>23</sup></sup> x log 2).

Single-precision, floating-point numbers are normally generated from the corresponding decimal numbers using the DCS assembler directive.

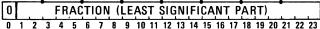

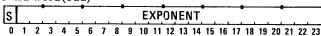

EXTENDED FORMAT. An additional 23 binary bits of fraction are added to the representation by employing a three word format which is stored in three consecutive memory locations, the first being odd.

First word (odd)

Second word (even)

Third word (odd)

Extended-precision, floating-point numbers have just under fourteen decimal digits of precision and a decimally equivalent exponent range of  $\pm$  10<sup>2</sup>,5<sup>2</sup>5,2<sup>2</sup>3.

Extended-precision, floating-point numbers are normally generated from the corresponding decimal numbers using the DCD assembler directive.

#### SPECIAL DATA

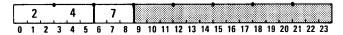

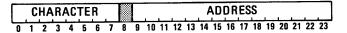

Certain instructions use data expressed in other specialized ways. These special formats are described under the instructions that use them, and summarized below:

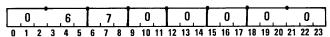

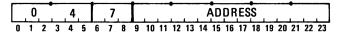

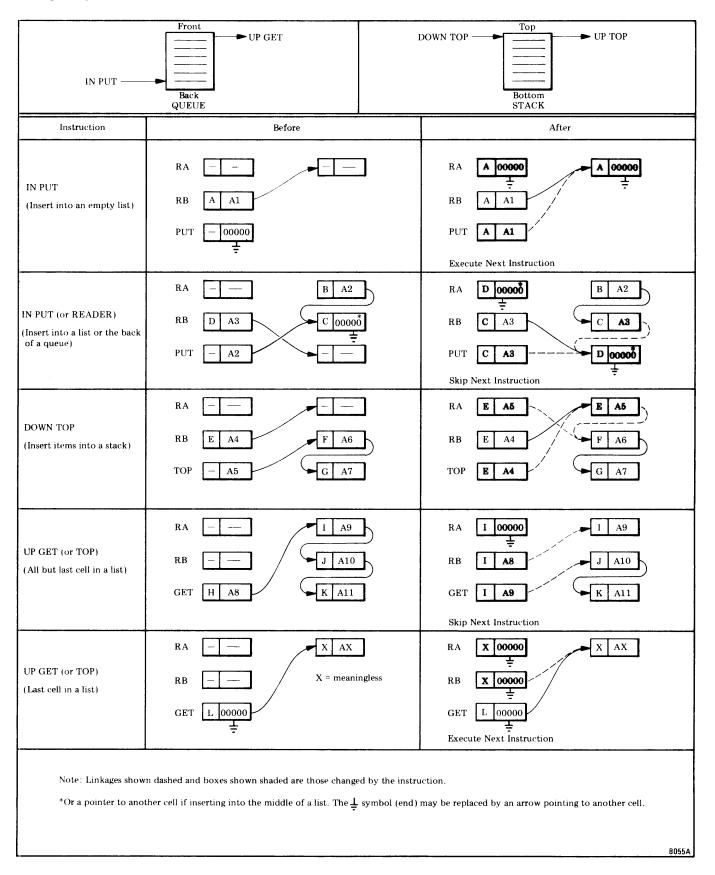

#### **List Processing Instructions**

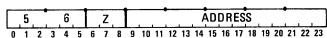

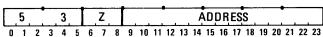

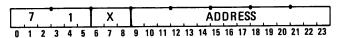

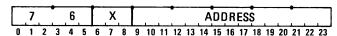

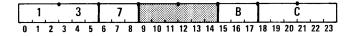

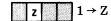

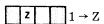

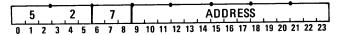

These instructions use a character and an address:

| Γ | CHARACTER |   |   |   |   |   |   |   | ADDRESS |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---|-----------|---|---|---|---|---|---|---|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0 | 1         | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9       | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

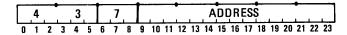

**Character Manipulation and Input Pack Instructions**

These instructions use a format with sign bit, byte control, and count:

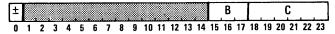

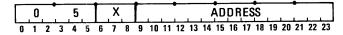

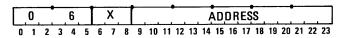

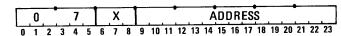

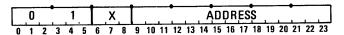

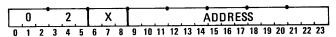

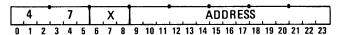

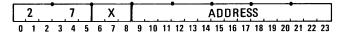

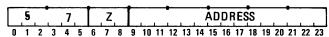

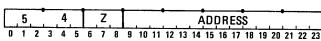

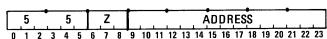

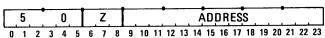

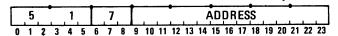

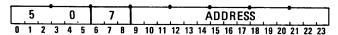

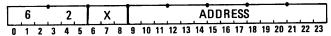

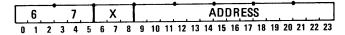

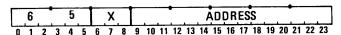

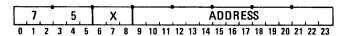

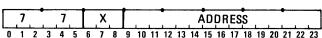

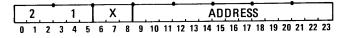

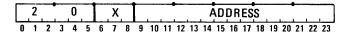

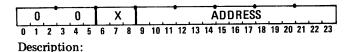

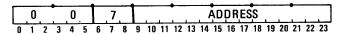

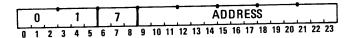

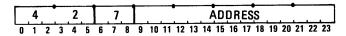

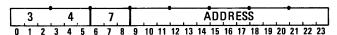

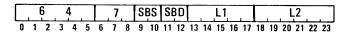

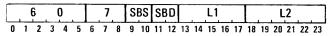

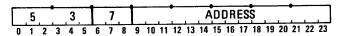

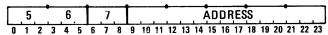

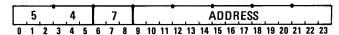

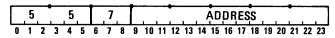

#### Instruction Format

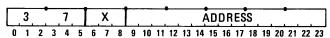

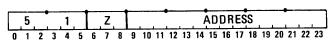

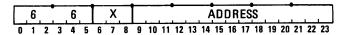

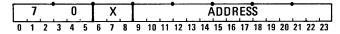

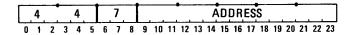

For purposes of defining instruction formats, the word is divided into 8 octal digits (3 bits each). It is organized as follows: op code, 2 digits; modification field, 1 digit; and operand field, 5 digits.

| Γ | OP CODE |   |   |   | N | 101 | p. |   | OPERAND |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---|---------|---|---|---|---|-----|----|---|---------|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| _ |         | 1 | 2 | 3 | 4 | - 5 | 6  | 7 | 8       | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

#### OP CODE FIELD

This 2-digit field contains the code that designates the operation to be performed; the instruction repertoire is approximately doubled by interpreting the code differently when there is a  $7_8$  in the modification field.

Table 3-2. Significance of Modification Field

| Contents of<br>Mod Field                                                                      | Significance                               |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|--------------------------------------------|--|--|--|--|--|--|--|

| 0                                                                                             | Not indexed and directly addressed.        |  |  |  |  |  |  |  |

| 1                                                                                             | Not indexed and indirectly addressed.      |  |  |  |  |  |  |  |

| 2                                                                                             | Indexed using X1 and directly addressed.   |  |  |  |  |  |  |  |

| 3                                                                                             | Indexed using X1 and indirectly addressed. |  |  |  |  |  |  |  |

| 4                                                                                             | Indexed using X2 and directly addressed.   |  |  |  |  |  |  |  |

| 5                                                                                             | Indexed using X2 and indirectly addressed. |  |  |  |  |  |  |  |

| 6                                                                                             | Indexed using X3 and directly addressed.   |  |  |  |  |  |  |  |

| 7                                                                                             | Not address modifiable.†                   |  |  |  |  |  |  |  |

| † Note that the hardware does not allow for indirect addressing when X3 is used for indexing. |                                            |  |  |  |  |  |  |  |

#### MODIFICATION FIELD

This octal digit aids in designating the operation to be performed as described above, and designates the type of address modification (if any) as shown in Table 3–2. Address modification includes indexing and indirect addressing. Indexing can be performed using any of the three machine index registers X1, X2, or X3. See "Memory Reference Instructions" for details.

#### OPERAND FIELD

This field specifies the information that the programmer must supply for proper execution of the particular instruction. The five octal digits may include memory reference (reference address), shift count, register control, and byte control, depending on the particular instruction. Since an address is 15 bits in length, instructions with an address will not have any other operand information; instructions that contain an address have a type 1 format. All other instructions, except decimal option instructions, have type 2 formats. For full discussion of the operand field for any instruction, see the discussion of that instruction.

#### INSTRUCTIONS

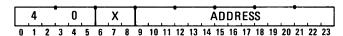

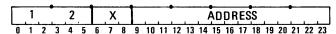

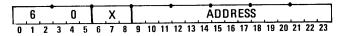

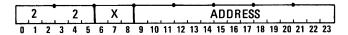

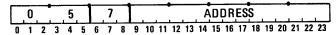

There are three types of instructions: memory-reference instructions (type 1 format), non-memory-reference instructions (type 2 format), and decimal option instructions.

#### **Memory Reference Instructions**

Memory reference instructions are either address modifiable or non-address modifiable. In non-address-modifiable instructions (mod field = 0 or  $7_8$ ), the reference address in the operand field is the final or effective address (EA). The contents of this address, [EA], are fetched before the instruction is executed. Since the reference address contains 15 bits, any word in memory (up to 32,768 words) may be directly addressed without the need for indexing or indirect addressing.

In address modifiable instructions (mod field  $\neq 0$  or  $7_8$ ) the reference address is modified by either indexing, indirect addressing, or both. The result of these address modifications is to transform the original reference address into an effective address. The effective address is defined as the final address computed for an instruction.

If both indexed and indirect addressing are specified for an instruction, indexing will be done before indirect addressing.

#### **INDEXING**

The programmer may specify any of the three arithmetic registers X1, X2, or X3 to be the index register (see Table 3-2 for mod field options). The 15 least-significant bits of the contents of this designated index register are then treated as a 15-bit displacement value.

# Section 3 Machine Language Programming

This displacement value is added to the reference address to obtain a new address. Only the least significant 15 bits of the sum are kept. This newly developed address is called the indexed address. Indexing is designated in CODE assembly language (see Section 8) by a tag field after the address; i.e., LDB VALUE, X1.

#### INDIRECT ADDRESSING

Indirect addressing, which is limited to one level, is specified when octal 1, 3, or 5 is found in the mod field of an instruction.

If the [mod field] =  $1_8$ , then the contents of the reference address are fetched. The address field of this newly fetched word (bits 9-23) becomes the effective address, whose contents are fetched before execution.

If the [mod field] =  $3_8$  or  $5_8$ , the reference address is indexed to produce an indexed address; the contents of the indexed address are then fetched. The address field of this fetched word contains the effective address.

The CODE assembly program recognizes an \* (asterisk) after the instruction mnemonic as the symbolic designation for indirect addressing, i.e., LDB\* VALUE.

Table 3-3 illustrates the effect of indexing and indirect addressing. The operation code used is 03 for LDA.

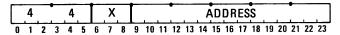

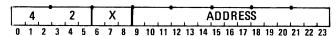

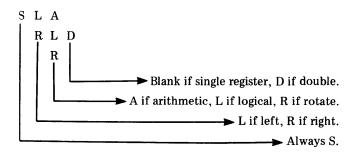

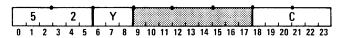

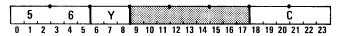

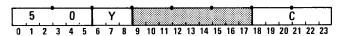

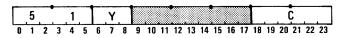

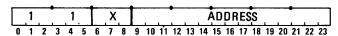

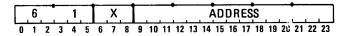

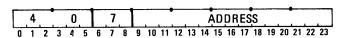

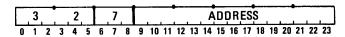

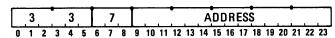

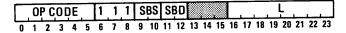

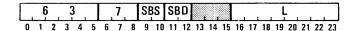

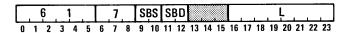

#### **Non-Memory Reference Instructions**

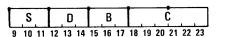

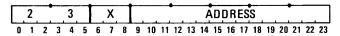

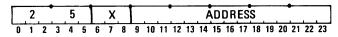

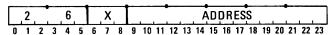

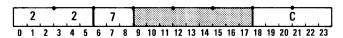

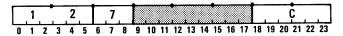

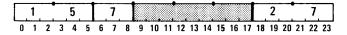

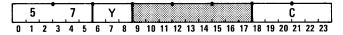

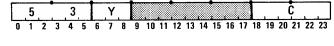

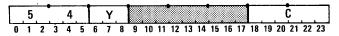

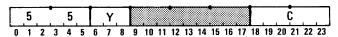

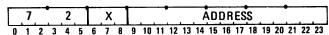

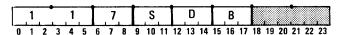

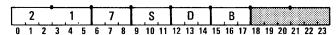

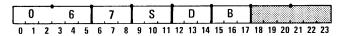

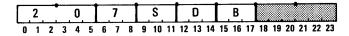

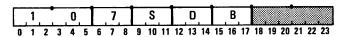

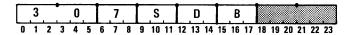

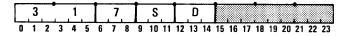

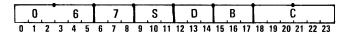

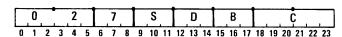

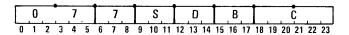

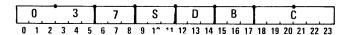

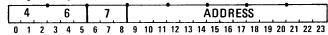

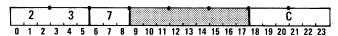

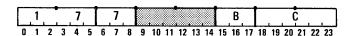

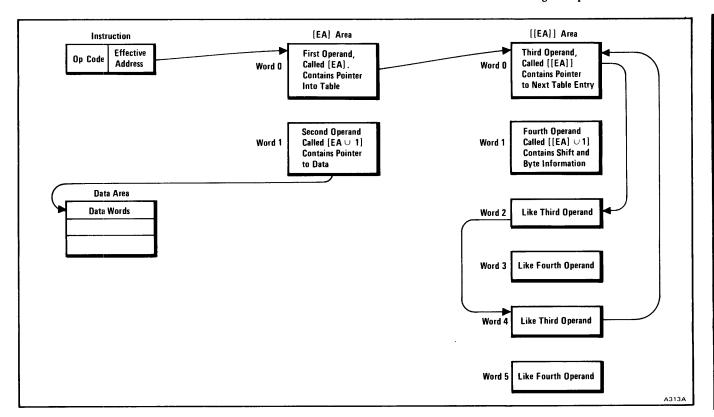

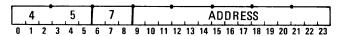

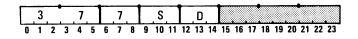

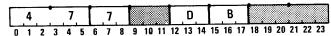

The operand field may be used to specify other than address information; when no address is given, the instruction has a type 2 format. In this case the operand field is used to specify: source and destination registers, byte control, count, or nothing.† The generalized format is as follows:

#### where:

S = Source register field

D = Destination register field

B = Byte control field

C = Count

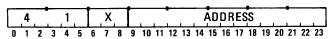

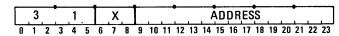

#### SOURCE AND DESTINATION FIELD

The digits in these fields specify any of the eight programmer-addressable registers located in the Arithmetic Logic. (See "Arithmetic Logic" below for a description of these registers.) They are used (with few exceptions) by instructions which operate on two registers in a source-todestination manner; i.e., the contents of the source register replace or modify the contents of the destination register (in general, the source register will be unmodified after execution; the destination register is usually changed). Note that it is always legal to use the same register as both source and destination in an instruction. R0 and R1 are normally not specified as destination registers because they are sources of numeric constants and not storage registers. If either of these is specified as a destination, no operation will result except that appropriate condition codes will be set or reset, just as if the instruction had been executed normally. Source (bits 9-11) and destination (bits 12-14) are specified in Table 3-5.

Note that caution must be exercised in using the RP as destination: RP contains the program counter, and any change in the program counter is equivalent to a branch in the program.

Table 3-3. Example of Indexing and Indirect Addressing

| Location | Contents | Symbolic       | Effect                                                               |

|----------|----------|----------------|----------------------------------------------------------------------|

| X1       | 00000001 |                |                                                                      |

| 1000     | 00001001 |                |                                                                      |

| 1001     | 00101002 |                |                                                                      |

| 1002     | 00001003 |                |                                                                      |

| 1003     | 00000002 |                |                                                                      |

| 2000     | 03001000 | LDA 01000      | $[01000] = 00001001 \rightarrow [RA]$                                |

| 2001     | 03201000 | LDA 01000, X1  | $01000 + 1 = 01001; [01001] = 00101002 \rightarrow [RA]$             |

| 2002     | 03101000 | LDA*01000      | $[[01000]] = [01001] = 00101002 \rightarrow [RA]$                    |

| 2003     | 03301000 | LDA* 01000, X1 | $01000 + 1 = 01001; [[01001]] = [01002] = 00001003 \rightarrow [RA]$ |

<sup>†</sup> Certain instructions require no operand information. See the discussion of each instruction for this specification.

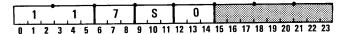

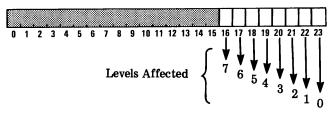

#### BYTE CONTROL FIELD

Many instructions offer the programmer the option of specifying which bytes of the word are to be affected by the instruction. The word is broken, for this purpose, into three 8-bit bytes labeled byte 0 (most significant), byte 1 (middle), and byte 2 (least significant). Instructions that allow byte control perform the operation first, then apply byte control on the word at the time it is stored in the destination register. Thus, unselected bytes remain unchanged. Byte control is mapped into the word rather than encoded: bit 15 set means byte 0 is affected, bit 16 corresponds to byte 1, and bit 17 corresponds to byte 2.

#### COUNT OR SHIFT COUNT FIELD

Certain instructions employ a counter to determine the number of operations desired, e.g., shift counter or the number of significant bits in a fixed-point multiplication or division. The count field is always the least significant six bits (2-digit octal) of its instruction; thus the largest count that can be entered is  $2^6$  -1 =  $63_{10}$ .

Note that the shift instructions are the only instructions which allow indexing or indirect addressing to be used in generating a Count Field. Thus the shift count of these instructions is modified in the same way as the memory address of other instructions, i.e., it may be direct, indirect, indexed, or both indexed and indirect, as defined by the mod field of the instruction. After modification is complete the least significant six bits of the result are used as the shift count.

#### **Decimal Option Instructions**

These instructions use special formats unique to the hardware that processes them. See the discussions of these instructions in Section 5 for details.

#### HARDWARE ORGANIZATION

As explained in Section 2, the computer system is logically divided into Main Storage or Memory, Control Logic, Arithmetic Logic, and the I/O System. The I/O System is covered in Section 6; this section notes salient features of the Main Storage and the Central Processing Unit, which contains Arithmetic Logic and Control Logic.

#### Main Storage

Main Storage on the 7001 can be 12K, 18K, or 24K bytes (4K, 6K, or 8K 24-bit words). On the 7002 it can be 48K, 72K, or 96K bytes (16K, 24K, or 32K words). The 15 bits in the address (operand) field of the instruction field allows addressing of  $2^{15} = 32,768_{10}$  words of memory (ranging from  $0_8$  through  $77777_8$ ) without need of a base or index register or indirect addressing. These addresses are usually referred to by using a 5-digit octal number. If an attempt is

made to address non-existent memory (i.e., if too large a memory address is generated), garbage will result for the 7001. For the 7002, the last four octal digits (bits 12-23) will be used to address the first 4K words on a read; on a write the information will not be written into memory.

Odd parity is calculated on each memory write and parity is checked on each read. The parity circuits are disabled by SYSTEM RESET and controlled by the EXCT instruction (see Section 6). Control codes are  $14_8$  = enable parity,  $15_8$  = disable parity,  $16_8$  = select odd parity check,  $17_8$  = select even parity check (for diagnostic purposes only). A parity error halts the computer and activates Machine Malfunction, which is a bit displayed in position 1 of RP in MANUAL mode.

Certain memory locations are used for specified purposes and hence are considered dedicated; although the programmer may write into these areas, care must be exercised to be sure that the special functions are not disturbed. See Table 3-4.

#### **Central Processing Unit**

The CPU contains the facilities for controlling the operational sequence of instructions (the control logic function), for communicating with external devices and storage (the B3 interface function), and for performing arithmetic and logical processing of data (the arithmetic logic function).

#### **CONTROL LOGIC**

The control logic function provides the necessary means of guiding the CPU and the I/O through the operations required for execution of instructions. Implementation of system control is accomplished using random logic and a Microprogram Command Generator (MCG). The random logic performs a number of random operations and tests such as preparing the next instruction op code; handling source, destination, and byte control; and storing and testing of the status bits. The MCG controls the execution of each instruction using a stored microprogram composed of 1024 48-bit words. Each instruction is thus performed using a number of microsteps, each of which is controlled by one of the 48-bit words of the microprogram.

#### **B3 INTERFACE**

Data transfers between I/O, Main Storage, and the CPU, and within the CPU take place over B3, a bidirectional data bus that ties the various functions together. B3 also interfaces with the lights on the Control Panel: the lights display the contents of B3 at all times. When operating in the MANUAL mode, the operator views the contents of a register or a memory location via B3, for the microprogram is configured to maintain the contents of the location specified by the DISPLAY SELECT switches on B3.

1 October 1972 3-5

Table 3-4. Dedicated Memory Locations

| Octal Location | Function                                         | Octal Location                                     | Function                                         |  |  |  |  |  |

|----------------|--------------------------------------------------|----------------------------------------------------|--------------------------------------------------|--|--|--|--|--|

| 00000          | Interrupt level 0                                | 00012                                              | Interrupt level 5                                |  |  |  |  |  |

| 00002          | Interrupt level 1                                | 00014                                              | Interrupt level 6                                |  |  |  |  |  |

| 00004          | Interrupt level 2                                | 00016                                              | Interrupt level 7                                |  |  |  |  |  |

| 00006          | Interrupt level 3                                | 00041                                              | Arithmetic Trap, Supervisory Trap                |  |  |  |  |  |

| 00010          | Interrupt level 4                                | 00011                                              | inionicole rup, supervisory rup                  |  |  |  |  |  |

| 7001, 48 Chara | cter/Line Video Systems†                         | 7001, 81 Character/Line Video Systems <sup>†</sup> |                                                  |  |  |  |  |  |

| 00060-00657    | Video display area A                             | $00140\text{-}00732^{\ddagger}$                    | Video display area A                             |  |  |  |  |  |

| 01060-01657    | Video display area B                             | $00740 \cdot 01532^{\ddagger}$                     | Video display area B                             |  |  |  |  |  |

| 02060-02657    | Video display area C                             | $02140-02732^{\ddagger}$                           | Video display area C                             |  |  |  |  |  |

| 03060-03657    | Video display area D                             | 02740-03532 <sup>‡</sup>                           | Video display area D                             |  |  |  |  |  |

| 04060-04657    | Video display area E                             | $04140-04732^{\ddagger}$                           | Video display area E                             |  |  |  |  |  |

| 05060-05657    | Video display area F                             | 04740-05532 <sup>‡</sup>                           | Video display area F                             |  |  |  |  |  |

| 06060-06657    | Video display area G                             | 06140-06732 <sup>‡</sup>                           | Video display area G                             |  |  |  |  |  |

| 07060-07657    | Video display area H                             | 06740-07532 <sup>‡</sup>                           | Video display area H                             |  |  |  |  |  |

|                | <u> </u>                                         | <u> </u>                                           |                                                  |  |  |  |  |  |

| 7002, 48 Chara | cter/Line Video Systems†                         | 7002, 81 Charac                                    | cter/Line Video Systems†                         |  |  |  |  |  |

| 00060-00657    | Video display area 000                           | $00140-00732^{\ddagger}$                           | Video display area 00                            |  |  |  |  |  |

| 01060-01657    | Video display area 001                           | $00740 - 01532^{\ddagger}$                         | Video display area 01                            |  |  |  |  |  |

| 02060-02657    | Video display area 002                           | $02140 - 02732^{\ddagger}$                         | Video display area 02                            |  |  |  |  |  |

| 03060-03657    | Video display area 003                           | $02740 - 03532^{\ddagger}$                         | Video display area 03                            |  |  |  |  |  |

| 04060-04657    | Video display area 004                           | $04140 \cdot 04732^{\ddagger}$                     | Video display area 04                            |  |  |  |  |  |

| 05060-05657    | Video display area 005                           | $04740 - 05532^{\ddagger}$                         | Video display area 05                            |  |  |  |  |  |

| 06060-06657    | Video display area 006                           | $06140-06732^{\ddagger}$                           | Video display area 06                            |  |  |  |  |  |

| 07060-07657    | Video display area 007                           | 06740-07532 <sup>‡</sup>                           | Video display area 07                            |  |  |  |  |  |

| 10060-10657    | Video display area 010                           | 10140-10732 <sup>‡</sup>                           | Video display area 010                           |  |  |  |  |  |

| 11060-11657    | Video display area 011                           | 10740-11532 <sup>‡</sup>                           | Video display area 011                           |  |  |  |  |  |

| 12060-12657    | Video display area 012                           | 12140-12732 <sup>‡</sup>                           | Video display area 012                           |  |  |  |  |  |

| 13060-13657    | Video display area 013                           | 12740-13532 <sup>‡</sup>                           | Video display area 013                           |  |  |  |  |  |

| 14060-14657    | Video display area 014                           | 14140-14732 <sup>‡</sup>                           | Video display area 014                           |  |  |  |  |  |

| 15060-15657    | Video display area 015                           | 14740-15532 <sup>‡</sup>                           | Video display area 011                           |  |  |  |  |  |

| 16060-16657    | Video display area 016                           | 16140-16732 <sup>‡</sup>                           | Video display area 016                           |  |  |  |  |  |

| 17060-17657    | Video display area 017                           | 16740-17532 <sup>‡</sup>                           | Video display area 010<br>Video display area 017 |  |  |  |  |  |

| 20060-20657    | Video display area 020                           | 20140-20732‡                                       | Video display area 020                           |  |  |  |  |  |

| 21060-21657    | Video display area 021                           | 20740-21532 <sup>‡</sup>                           | Video display area 021                           |  |  |  |  |  |

| 22060-22657    | Video display area 022                           | 22140-22732 <sup>‡</sup>                           | Video display area 022                           |  |  |  |  |  |

| 23060-23657    | Video display area 023                           | 22740-23532 <sup>‡</sup>                           | Video display area 023                           |  |  |  |  |  |

| 24060-24657    | Video display area 024                           | 24140-24732 <sup>‡</sup>                           | Video display area 024                           |  |  |  |  |  |

| 25060-25657    | Video display area 024<br>Video display area 025 | 24740-25532 <sup>‡</sup>                           | Video display area 025                           |  |  |  |  |  |

| 26060-26657    | Video display area 026                           | 26140-26732 <sup>‡</sup>                           | Video display area 025<br>Video display area 026 |  |  |  |  |  |

| 27060-27657    | Video display area 020<br>Video display area 027 | 26740-27532 <sup>‡</sup>                           | Video display area 020<br>Video display area 027 |  |  |  |  |  |

| 30060-30657    | Video display area 030                           | 30140-30732 <sup>‡</sup>                           | Video display area 030                           |  |  |  |  |  |

| 31060-31657    | Video display area 031                           | 30740-31532 <sup>‡</sup>                           | Video display area 031                           |  |  |  |  |  |

| 32060-32657    | Video display area 032                           | 32140-32732 <sup>‡</sup>                           | Video display area 032                           |  |  |  |  |  |

| 33060-33657    | Video display area 033                           | 32740-33532 <sup>‡</sup>                           | Video display area 033                           |  |  |  |  |  |

| 34060-34657    | Video display area 034                           | 34140-34732 <sup>‡</sup>                           | Video display area 034                           |  |  |  |  |  |

| 35060-35657    | Video display area 035                           | 34740-35532 <sup>‡</sup>                           | Video display area 035                           |  |  |  |  |  |

| 36060-36657    | Video display area 036                           | 36140-36732 <sup>‡</sup>                           | Video display area 036                           |  |  |  |  |  |

| 37060-37657    | Video display area 037                           | 36740-37532 <sup>‡</sup>                           | Video display area 030<br>Video display area 037 |  |  |  |  |  |

| 01000-01001    | viuco dispiay alea 051                           | 00140-01002                                        | video dispiay alea 001                           |  |  |  |  |  |

<sup>†</sup> Video systems with 40 or 80 characters/line are achieved by programming blanks in the appropriate character positions.

<sup>&</sup>lt;sup>‡</sup> There are 5 unused memory locations at the end of each video line for 81 character/line systems. For example, the characters for the first line of area A occupy locations 00140-00172 while the second line of characters occupies locations 00200-00232.

#### ARITHMETIC LOGIC

The arithmetic logic performs all logical, arithmetic, and shift operations on data. Of special interest to the programmer are the working registers, the condition codes, and the arithmetic trap.

#### Working Registers

There are eight programmer-addressable registers; six are flexible storage registers and the other two are sources of numeric constants  $0_2$  and  $1_2$ . See Table 3–5.

#### **Condition Codes**

Four condition codes (CC) are used to indicate the results of the various arithmetic logic operations. The status of the condition codes are checked using various branch and skip instructions.

The condition codes are overflow (O), zero (Z), minus (M), and carry (C). If the condition code is a 1, the condition is true; otherwise the condition code is 0 and the condition is false.

Some instructions do not alter the condition codes (see the description of each instruction for the condition codes affected). Therefore, the current value remains unchanged until altered by the appropriate instruction. An exceptional case is the overflow CC, which may be set by a number of arithmetic and shift operations, but may only be reset by the BOF instruction, which tests this CC specifically; restoration of a 1 or 0 to this CC is also possible using the BRR or BRD returns from a subroutine.† The reason for this is that an arithmetic overflow usually indicates that a data error has occurred and that all arithmetic computation from this point forward is incorrect or at least suspect. Thus, after any series of arithmetic steps that could conceivably create an overflow, a BOF should be given to allow branching to a diagnostic routine designed to clear up the problem.

Note that the MCC instruction can be used to set the condition codes on the basis of the contents of any memory location, and RCC similarly will set the condition codes on the basis of the contents of a working register. Also, the operator may change the condition codes from the console, using RP and the data keys (see Section 9 for this procedure).

OVERFLOW CC. The overflow CC permits the detection of erroneous arithmetic results that may occur during the execution of a program. The overflow CC is reset only by a BOF instruction that tests it and is set whenever the carryouts of bit positions 0 and 1 are different from each other on a shift-left-arithmetic instruction or an addition, subtraction, or comparison. The significance of this condition for an addition or subtraction is that the number generated is too large for the register.

The significance of overflow for a shift left arithmetic is that the most significant data bit has been shifted out of the left side of the register; significant data has been lost.

ZERO CC. The zero CC is set to 1 by certain instructions if the result of the operation was all zeros; if the result was not all zeros the CC is set to 0. All arithmetic and logical operations affect this CC.

MINUS CC. The minus CC is set to 1 by certain instructions if the result of the operation was minus; this condition is defined to be true if bit 0 of the register is a 1. If the result was not minus, the CC is set to 0.

CARRY CC. When arithmetic operations are performed, a carry can develop out of the zero position (in subtraction, a borrow is interpreted as a carry). In this event the carry CC is set to 1.

Table 3-5. Programmer-Addressable Registers

| Symbol | Code | Uses                                                                                                                                                                                                                                                                    |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0     | 0    | Source of constant 0. This is a read-only register.                                                                                                                                                                                                                     |

| R1     | 1    | Source of constant 1 (00000001 <sub>8</sub> ). This is a read-only register.                                                                                                                                                                                            |

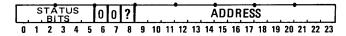

| RP     | 2    | Program Register. Bits 9-23 contain the program counter, which holds the address of the next instruction to be executed. Bits 0-5 are used, in manual mode only, to hold and display the status bits, which include stop, machine malfunction, and the condition codes. |

| RA     | 3    | Accumulator. Used for arithmetic, logic, and shift operations.                                                                                                                                                                                                          |

| RB     | 4    | Extended Accumulator. Used as an extension to RA in certain arithmetic operations. Available as a program scratch pad.                                                                                                                                                  |

| X1     | 5    | Index Register 1. A hardware index register for address modification and arithmetic operations. Also available as a program scratch pad.                                                                                                                                |

| X2     | 6    | Index Register 2. Same as X1 but also serves as a link register for subroutine usage by the BAL instruction.                                                                                                                                                            |

| Х3     | 7    | Index Register 3. Same as X1.                                                                                                                                                                                                                                           |

<sup>†</sup> Overflow may also be reset from the console when not under program control. See Section 9 for this procedure.

1 October 1972 3-7

# Section 3 Machine Language Programming

INTERPRETATION OF CONDITION CODES. In comparison instructions, an arithmetic subtraction is performed and the result is not saved; but the overflow, minus, zero, and carry condition codes are affected. See "Comparison Instructions" in Section 4 for details on the uses of the condition codes.

#### Arithmetic Trap

Certain arithmetic error conditions will create an arithmetic trap to Main Storage location  $41_8$ ; this location should contain an instruction which branches to a program that will test the preceding operation and discover the problem. Conditions that will create a trap include:

- An attempt to convert 40000000<sub>8</sub> (the largest negative number a single word can hold) to a positive number.

This will occur if 40000000 is in RA at the beginning of a fixed point multiplication instruction.

- A division operation where the absolute value of the part of the numerator in RA is equal to or greater than the absolute value of the denominator [X2].

- In floating point arithmetic, any manipulation that attempts to create an exponent with absolute value greater than 2<sup>23</sup>.

- Execution of the TRAP instruction.

# PROGRAMMING FOR THE VIDEO/KEYBOARD Video Display

The computer can accommodate up to 32 individual terminal stations, each consisting of a video screen and alphanumeric keyboard. Each display is controlled by the CPU's responses to inputs (both character codes and control codes) from the corresponding keyboard. The keyboard input character and the corresponding display outputs are shown in Appendix A. Character generation and refresh is accomplished using direct memory access output from the computer's main memory, so that memory buffers in each terminal are not required. The specific output areas that are displayed are listed in "Dedicated Memory Areas" above. The part of video display area memory that will appear on any given screen can be varied by the hardware and will be selected at the time the system is designed. The particular format selections are an integral part of the system specification and the programmer will have this information available when programming for his particular system.

Note that video-display-area memory may be used by the programmer for instructions or data, as well as for display characters. Caution should be used, however, since any instructions or data appearing in display locations will be transformed to visual information, byte by byte, causing meaningless display.

Dual intensity and hardware blanking under software control are provided as two separate options on the video display terminals for the 7002. With these options, the hardware recognizes certain patterns of bits as intensity controls and varies the brightness of the characters on the screen accordingly. With this feature, an attribute character stored in a given dedicated location affects characters that follow, with wraparound from one line to the next and from the bottom right to the top left of the screen. This feature is under control of the EXCT instruction; if EXCT with an operand of 11 (octal 13) is given or if SYSTEM RESET is pressed, no attribute characters will have any effect and the operation is identical to the 7001. The intensity will be "bright". If the DATA IV/70 system option is selected at time of manufacture and EXCT with an operand of 9 (011) is given, the 5-10-31 system goes into effect. If the 3270 system option is selected at time of manufacture and the EXCT operand is 10 (012), the 300 system goes into effect.

5-10-31 System. Under this scheme, specific codes function as attribute characters. When such a character is placed on the screen, it will appear as a blank, but any data to the right will take on the video attribute specified, until another attribute character is encountered. The codes are as follows:

| Code        | Meaning         |

|-------------|-----------------|

| 05 or 0205  | Blank           |

| 010 or 0210 | Normal          |

| 031 or 0231 | Extra intensity |

are interpreted as attribute controls, with the rest of the bits in the character being subject to use by the software as the programmer requires. Thus, if any character with the specified bit pattern appears on the screen, that character will be blanked and any character to its right will take on the video attribute specified, until another character with any of the specified attribute bits is encountered. The pattern of bits is as follows:

Bit Position 0 1 2 3 4 5 6 7 Usage 1 1 x x y z x x

A 1 indicates that the bit must be a 1 for intensity control. An x indicates don't care; the software may interpret these bits as required. The yz are the intensity control bits: 00 or 01 = normal, 10 = extra intensity, 11 = blank.

The way the cursors display is also affected by the 300 system. ASCII 032 is the usual large block cursor used with much Four-Phase supported software. ASCII 05 or 0205 are the same cursor, but function as an attribute character, blanking data to the right. ASCII 010 or 0210 are the block cursor but function as attribute characters, forcing "normal" display to

the right. Similarly, 031 and 0231 display as the block cursor and force "extra intensity" to the right. These six characters are identical in effect to other attribute characters except that they appear as block cursors instead of blanks.

The video attribute system wraps around automatically within each dedicated video area. For example, half screens or quarter screens within the same video area are all affected the same by a single attribute character occurring in any of the dedicated memory locations of that area. In general, when the variable intensity feature is used with half or quarter screens it will be necessary to control the intensities of each screen separately.

If a single attribute character is placed on the screen, its effect lingers even if it is replace by a non-attribute character. The only restriction is that the character must remain on the screen for 1/60 of a second. If more than one attribute character is on the screen and the characters are removed, the last character scanned is the one whose effect lingers, even if it is not the last one removed. Thus, the user should wait 1/60 of a second before removing the last attribute character in a series.

#### Keyboard

Whenever a key on the keyboard is pressed, the keyboard controller generates an interrupt which must be serviced using the IOID instruction (see "Indirect Interrupt" in Section 7). The controller will present the device address of the keyboard terminal generating the interrupt; the program will then branch to the location specified by the IOID instruction and the device address. This location should contain an IO instruction for accepting the keyboard code from the least significant eight bits of the data bus and then storing it in a buffer area. The program must then move the character into the appropriate memory area for display (character code) or present it to a control program (control code).

#### INSTRUCTION DESCRIPTIONS

The following four sections describe the instructions that may be executed by the computer. Section 4 covers the conventional binary Word-Oriented Instructions. Section 5 covers the Character String Manipulation Instructions, including the Decimal Option. Section 6 discusses the Input/Output Instructions and the operation of the computer's I/O interfaces. Section 7 deals with the Priority Interrupt System Instructions. Each instruction is described separately, including all options, formats, etc. The form of each description is as follows:

#### **Assembly Language Format**

The assembly language form of each instruction comes first in the description. It contains three fields: label, mnemonic, and operand. The label field is always optional and, if used, assigns to label the Main Storage location of the instruction. The mnemonic field contains the name of the instruction exactly as the assembly language expects to see it; if more than one mnemonic refers to the same instruction, this will be footnoted. An asterisk (\*) after the mnemonic may be used to indicate indirect addressing. The operand field contains from zero to four subfields depending upon the nature of the instruction. If any operand is optional or if default options are provided, this will be noted under "Description." The contents of the operand field are numerically coded in the contents of bits 9-23 of the machine language version of the instruction (see below). If the instruction format is type 1, the operand field will contain a symbolic address reference. Indexing is indicated by adding ",Xn" where n is 1, 2, or 3 after the symbolic address reference. If the format is type 2, the operand field may contain source register, destination register, byte control, and count information.

In the operand field the following conventions apply:

| Symbol     | Name of Field              |

|------------|----------------------------|

| Expression | Symbolic address reference |

| S          | Source register            |

| D          | Destination register       |

| В          | Byte control               |

| C          | Count                      |

#### Name

Descriptive name of the instruction, in one or two lines.

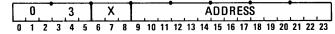

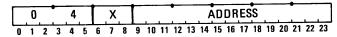

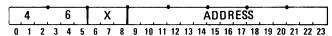

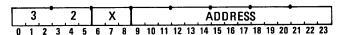

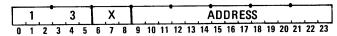

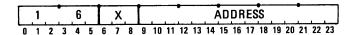

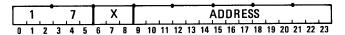

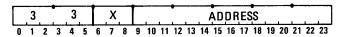

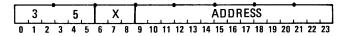

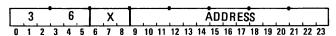

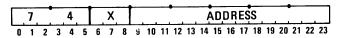

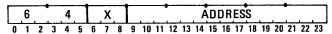

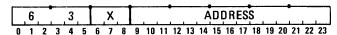

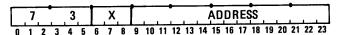

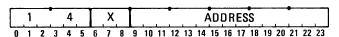

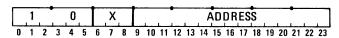

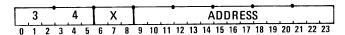

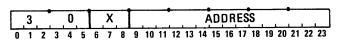

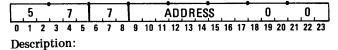

#### Machine Language Format

Every machine language instruction consists of a 24-bit word divided into three fields: op code field, modification field, and operand field. The op code is the 6-bit code used by the computer to initiate a particular instruction; two instructions may have the same op code, but the modification field and/or the operand field will be different. The modification field will contain a one-digit octal number with the significance as previously described under "Modification Field." Thus, X in the modification field implies that address modification is allowed; 7 in the modification field means either type 2 format or no address modification, as applicable.

1 October 1972 3–9

# Section 3 Machine Language Programming

The Operand Field will contain up to five octal digits with significance as previously noted under "Operand Field," but expressed in a form readable by the computer. The S (Source) and D (Destination) subfields actually contain numerical register codes, addressing the working registers as follows:

| Code | Register |

|------|----------|

| 0    | R0       |

| 1    | R1       |

| 2    | RP       |

| 3    | RA       |

| 4    | RB       |

| 5    | X1       |

| 6    | X2       |

| 7    | X3       |

Note that the assembly language will recognize either the name or the numerical code of the register, and that the machine language actually responds only to the binary equivalent of the octal number.

Similarly, the byte control subfield (bits 16-18) are mapped onto the three bytes of the word in a binary fashion, but written in octal:

| Code | Binary Equivalent | Bytes Affected |

|------|-------------------|----------------|

| 0    | 000               | none           |

| 1    | 001               | 2              |

| 2    | 010               | 1              |

| 3    | 011               | 1,2            |

| 4    | 100               | 0              |

| 5    | 101               | 0,2            |

| 6    | 110               | 0,1            |

| 7    | 111               | 0,1,2          |

The count subfield (2-digit octal) may appear in assembler language as an octal or decimal number or as an expression.

If the format of the instruction is type 1, the operand field will contain the binary address referred to by the symbolic expression in the assembly language version of the instruction. This address is usually written as a 5-digit octal integer.

#### Description

The instruction will be described in detail from an operational viewpoint. Sequences of operations and decision logic will be covered.

#### **Examples**

Illustrative examples, with interpretations as needed, will be given for key instructions.

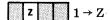

#### **Condition Codes**

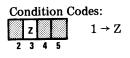

Condition codes are overflow, zero, minus, and carry. Instructions that alter any of these will be noted. Where a condition code is not altered, it is shown shaded in the box.

#### **Execution Equations**