# FOX 1

# Hardware System Overview and Reference Manual

VOLUME 2

COMPUTER REFERENCE MANUAL

# Hardware System Overview and Reference Manual

VOLUME 2 COMPUTER REFERENCE MANUAL

**Preliminary**

The information contained in this document is general in nature and not intended for specific application purposes. The Foxboro Company reserves the right to make changes in specifications shown herein and to make product changes at any time without notice or obligation.

Copyright 1972 by The Foxboro Company

#### **HISTORY**

| <u>Date</u> | Issue    | <u>Copies</u> |

|-------------|----------|---------------|

| 3-72        | Original | 800           |

#### Preface

This publication is a comprehensive description of the FOX 1 hardware system and the hardware system components. It can be used as an introductory textbook for hardware system analysts, engineers, and machine-language programmers learning the basic equipment structure and operation. It can also be used as a "quick look-up" reference manual for basic machine functions. Details of hardware logic and maintenance, or software that drives and utilizes the features of the hardware units are not in this book. Details of FOX 1 hardware configuration and operation at the machine-language level are presented here.

Volume 1 of this manual presents system overview information describing the FOX 1 hardware components, the system hardware configurations, and the participation of each hardware component in system functions. In general, sections on system hardware components are described in terms of a functional description, physical description, standard and optional features, interface considerations, and specifications.

Volumes 2, 3, and 4 present reference-level information describing the FOX 1 system hardware components (units). To simplify location of specific information, Volume 2 describes the computer components, Volume 3 describes the computer-peripheral type components, and Volume 4 describes the process-oriented type components. Volume 2 is divided into sections related to functions of the computer or to elements of the computer subsystem performing a specific task. Volumes 3 and 4 are divided into sections for each system hardware component. Individual sections describe each of these components in terms of a functional summary, block diagram discussion, instruction complement, and any other basic information peculiar to the subject component.

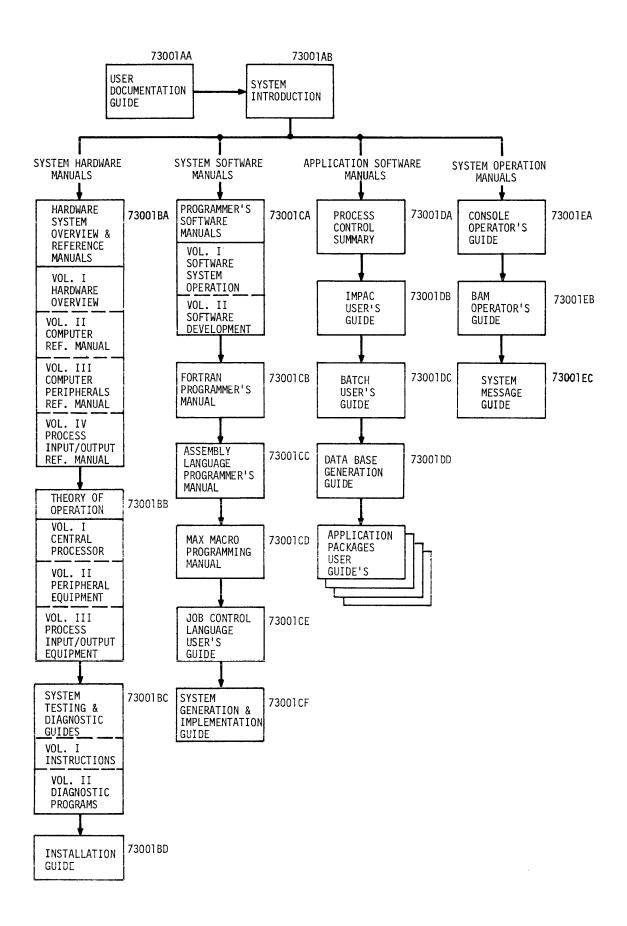

#### DOCUMENTATION STRUCTURE

Readers should be aware of the relationship between this document and other books in the FOX 1 anthology, as described in the FOX 1 User Documentation Guide, 73001AA.

The FOX 1 Hardware System Overview and Reference Manuals, 73001BA, are divided into four volumes which may or may not be bound under separate covers. Each volume is subdivided into modular, topical sections (equivalent to chapters). Pages are assigned a two-part number in which the section number precedes and is separated from the page sequence number by a hyphen. All headings and paragraphs are assigned a two-part number in which the section number precedes and is separated from a sequence number by a decimal point. The span of these numbers is indicated at the top of each page, allowing subjects to be referenced (such as in the index) not only by page, but also by paragraph number.

Tables and illustrations bear a three-part designation consisting of the volume number, the section number, and the sequence number, all separated by hyphens.

Information contained herein is preliminary in nature, being printed in advance of exhaustive formal technical and corporate review; it is subject to change without notice.

#### SYMBOLS AND NOTATION

Logic equations, in the descriptions of programmed instructions and throughout this manual, use the following symbols and notation. All abbreviations used in this book are not listed here, but are defined with their first use.

| Symbol Or<br>Notation | <u>Interpretation</u>                                                                                                                                                   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α                     | The A register (accumulator) or its contents.                                                                                                                           |

| A, E                  | The combined contents of both the A and E registers in double-word format.                                                                                              |

| CPI                   | The central processor indicator register or its contents.                                                                                                               |

| CPS                   | The central processor status register or its contents.                                                                                                                  |

| DISP <sub>e</sub>     | The displacement field of relative instructions extended left to form a 15-bit address.                                                                                 |

| E                     | The arithmetic extender register or its contents.                                                                                                                       |

| EA                    | The effective address register, its contents, or the location specified by the effective address.                                                                       |

| EA1                   | The effective address derived from the first word of a two-word instruction.                                                                                            |

| EA2                   | The effective address derived from the second word of a two-word instruction.                                                                                           |

| (EAdp)                | The contents of the location specified by the effective address expanded to form a double-precision floating-point number.                                              |

| (EA, EA + 1)          | The contents of two consecutive memory locations, the first of which has the address specified by the effective address of an instruction.                              |

| EAF                   | Final computed effective address.                                                                                                                                       |

| EAI                   | Intermediate effective address. (An effective address that has received some, but not all, of the arithmetic operations required to compute a final effective address.) |

| EMB                   | The executive mode bit (bit 00) of the privilege and level register.                                                                                                    |

| FNC                   | The memory-protection fence register or its contents.                                                                                                                   |

| FNV                   | The fence violation bit (bit 14) of the central processor status register.                                                                                              |

| Symbol Or<br>Notation | <u>Interpretation</u>                                                                                                   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| FPL                   | The floating-point long indicator (bit 01) of the central processor indicator bit.                                      |

| FP0                   | The floating-point overflow indicator (bit 19) of the central processor status register.                                |

| FPU                   | The floating-point underflow indicator (bit 00) of the central processor indicator register.                            |

| IR                    | The instruction register or its contents.                                                                               |

| IR06-08               | The mode field of the instruction register or its contents.                                                             |

| IR'06-08              | The mode field of an indirect vector.                                                                                   |

| IR12 <b>-</b> 23e     | The displacement field of relative instructions extended left to form a 15-bit address (same as ${\sf DISP}_{\sf e}$ ). |

| IR'09-23              | The indirect address supplied by an indirect vector.                                                                    |

| OV                    | The overflow indicator (bit 18) of the central processor status register.                                               |

| PC                    | The program counter register, its contents, or the location specified by the program count.                             |

| PL                    | The privilege and level register or its contents.                                                                       |

| RMP                   | The register manipulation privilege indicator (bit 01) of the privilege and level register.                             |

| SHC                   | The shift counter or its contents.                                                                                      |

| XA                    | The index A register or its contents.                                                                                   |

| XB                    | The index B register or its contents.                                                                                   |

| XC                    | The index common register or its contents.                                                                              |

| XE                    | The index executive register.                                                                                           |

| хт                    | The index top-of-stack register or its contents.                                                                        |

| Symbol Or<br>Notation | Interpretation                                                                                                               |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------|

| (XT)OLD               | The former or initial contents of the index top-of-stack register.                                                           |

| <b>→</b>              | Is copied into, or replaces the contents of.                                                                                 |

| B → A                 | The contents of the B register are transferred into, or replace the contents of, the A register.                             |

| PC + 1 → PC           | The contents of the PC are incremented by one.                                                                               |

| (EA) → A              | The contents of the EA specify a location whose contents are transferred into the A register.                                |

| +                     | The arithmetic sum or the logical inclusive OR operation.                                                                    |

| -                     | The arithmetic difference or the logical inversion (when placed immediately after a line or register symbol) operation.      |

| <del>0</del>          | The logical exclusive OR operation.                                                                                          |

| &                     | The logical AND operation.                                                                                                   |

| A23 → E00             | Bit 23 of register A is shifted (right) into bit 00 of register E.                                                           |

| XA → (EA09-23)        | The contents of the XA register are transferred into bits 09 through 23 of the location specified by the contents of the EA. |

| 0 → (EA00-08)         | Zeros are transferred into bits 00 through 08 of the location specified by the contents of the EA.                           |

# **Contents**

# Section 1. INTRODUCTION

# Section 2. FUNCTIONAL HARDWARE

| Storage . |                              | • | • | 2-1  |

|-----------|------------------------------|---|---|------|

| Core      | Memory                       | • | • | 2-1  |

|           | Core Capacity                | • | • | 2-2  |

|           | Memory Allocation Features   | ٠ | • | 2-2  |

|           | Dedicated Core Locations     | • | • | 2-2  |

| Drum      | Memory                       |   | • | 2-2  |

|           | Program Swapping             | • | • | 2-4  |

|           | Program Relocation           | • |   | 2-4  |

| Prog      | ram Address Registers        |   | • | 2-4  |

| Ü         | Instruction Register         | • |   | 2-6  |

|           | Shift Counter                |   |   | 2-11 |

|           | Effective Address Register   |   | • | 2-11 |

|           | Program Counter              |   |   | 2-12 |

|           | Index Common                 | • |   | 2-12 |

|           | Index Executive              |   |   |      |

|           | Index Top-of-Stack           |   |   | 2-14 |

|           | Index A                      |   |   |      |

|           | Index $B$                    |   |   | 2-15 |

| Prog      | ram Control Registers        |   |   | 2-15 |

| Ŭ         | Memory Protection Fence      |   |   | 2-15 |

|           | Privilege and Level Register |   |   | 2-17 |

|           | Address Stop Registers       |   |   | 2-27 |

| Arit      | hmetic Registers             | • |   | 2-23 |

|           | Accumulator                  |   |   | 2-23 |

|           | Arithmetic Extender          |   |   |      |

|           | Central Processor Indicator  |   |   | 2-25 |

|           | B Register                   |   |   |      |

|           | T Register                   | • |   | 2-27 |

| Sust      | em Control Registers         |   |   | 2-28 |

| -5        | Central Processor Status     |   |   | 2-28 |

|           | Software Interrupt Status    |   |   | 2-3  |

|           | Interrupt Flip-Flops         |   |   |      |

|           | Mark Register                |   | • | 2-32 |

|           | Word Switch Register         |   | • | 2-33 |

| Bus       | Sustem                       | • | • | 2-33 |

| 200       | System                       |   |   | 2-33 |

|           |                              |   |   |      |

|           | (Control Section)            | • | • | 2-38 |

| Memo      | ry Control Unit              |   |   |      |

|           | Logic Components             |   |   | 2-34 |

| Projection Contract                      |   |    |    | 0 24          |

|------------------------------------------|---|----|----|---------------|

| Priority Control                         | • | •  | •  | 4-34          |

| Cycle Control                            | • | •  | •  | 2-34          |

| Cycle Control                            | • | •  | •  | 2 <b>-</b> 36 |

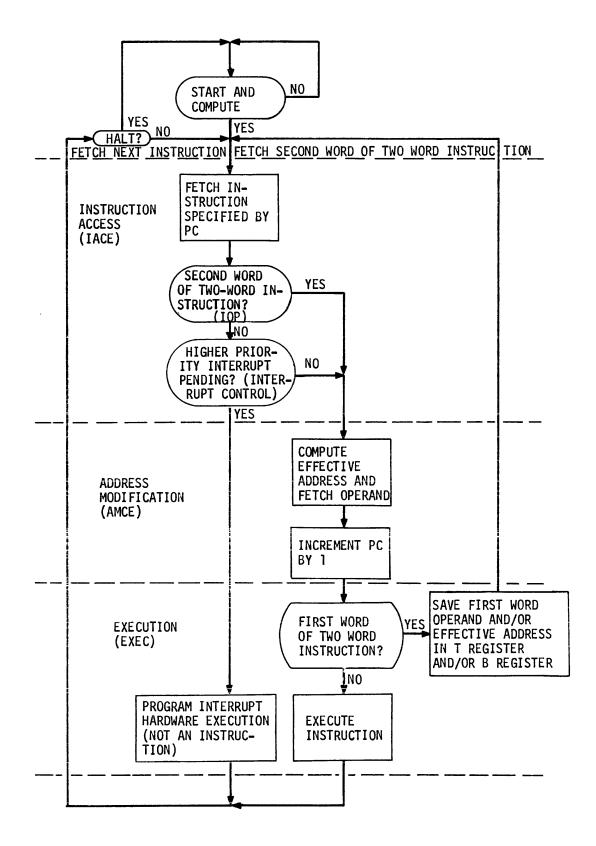

| Instruction Access                       | • | •  | •  | 2-36          |

| Address Modification                     |   | •  |    | 2-37          |

| Instruction Execution                    |   |    |    | 2-37          |

| Execution Sequence States                |   |    |    | 2-37          |

| Major State Loop                         | • |    | Ĭ. | 2-39          |

| Two-Word Instructions                    | • | •  | •  | 2_30          |

| System Control                           | • | •  | •  | 2_10          |

| Program Trtanmint                        | • | •  | •  | 2 40          |

| Program Interrupt                        | • | •  | •  | 0 40          |

| Programmed Halt                          | • | •  | •  | 2-40          |

| Compute Operational State                | • | •  | •  | 2-41          |

| Halt Operational State                   | • | •  | ٠  | 2-41          |

| WSR Loop State                           | • | •  | •  | 2-42          |

| Manual Memory Control Operational States | 3 | •  | •  | 2-42          |

|                                          |   |    |    |               |

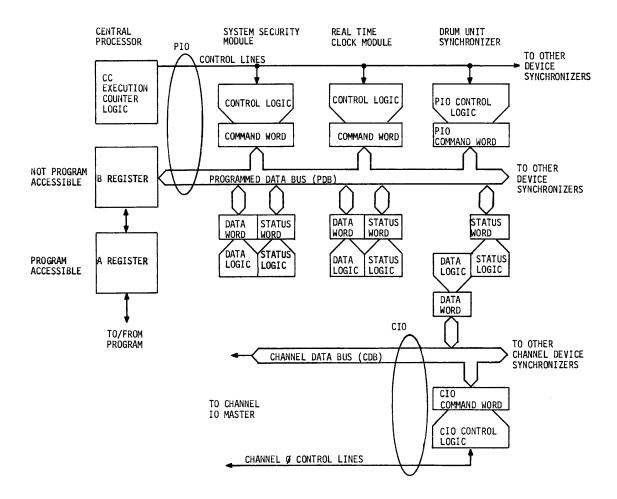

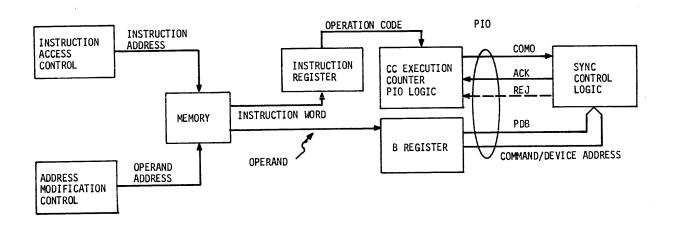

| Programmed Input/Output                  |   |    |    | 2-42          |

| PIO Component Hardware                   |   |    |    | 2-43          |

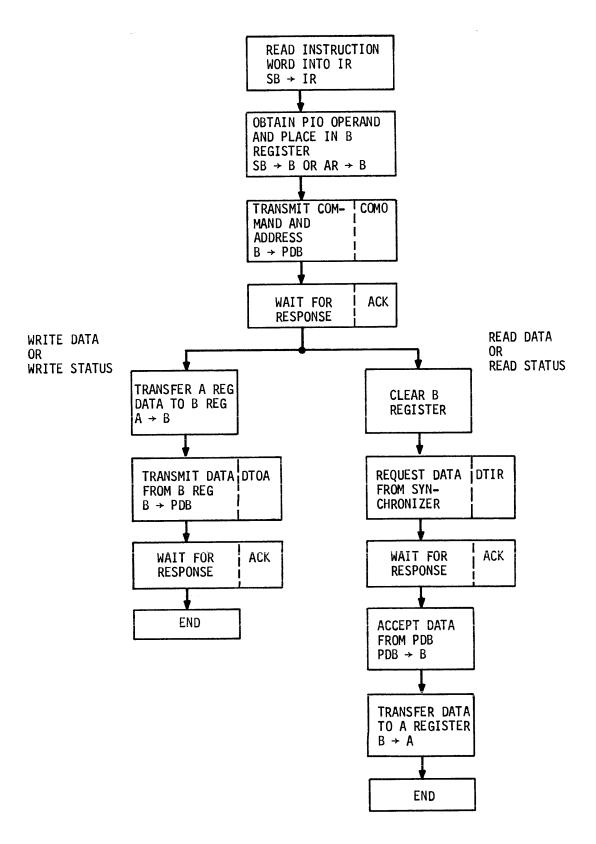

| General Description                      |   | •  |    | 2-44          |

| Command Sequence                         | • | Ĭ. | •  | 2-47          |

| Data Transfer Sequence                   |   |    |    |               |

| DIO Commanda                             | • | •  | •  | 9 10          |

| PIO Commands                             | • | •  | •  | 2 40          |

| IO Privilege                             | • | •  | •  | 2-49          |

| Detailed Sequence Description            | • | •  | •  | 2-49          |

|                                          |   |    |    |               |

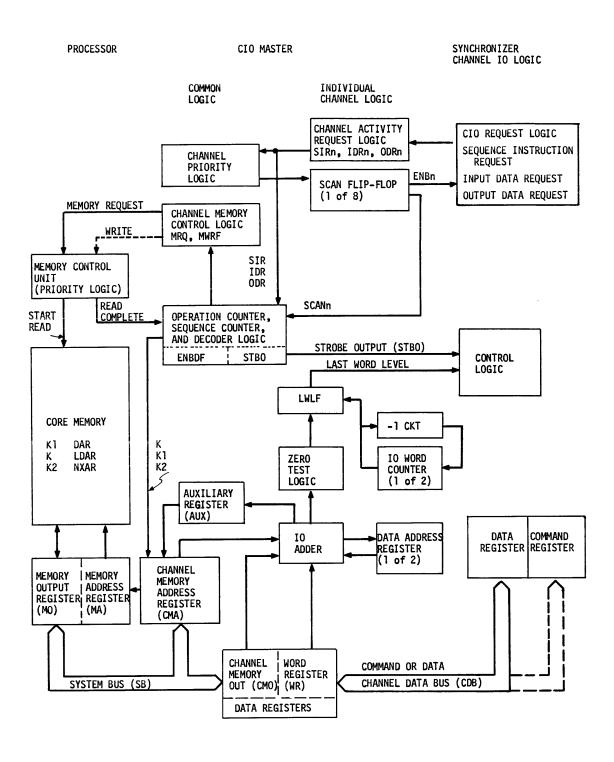

| Channel Input/Output                     | • | •  | ٠  | 2-54          |

| CIO Component Hardware                   | ٠ | •  | ٠  | <b>2-</b> 56  |

| General Functional Description           | • | •  | •  | 2-56          |

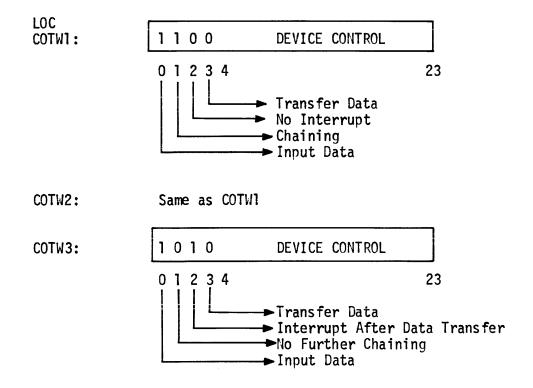

| CIO Command Format                       |   | •  |    | 2-61          |

| Input Output Requests                    |   |    |    |               |

| Operation Notes                          |   |    |    |               |

| Channel IO Interrupt                     |   |    |    | 2-66          |

| Channel IO Timing                        | Ī |    |    | 2-67          |

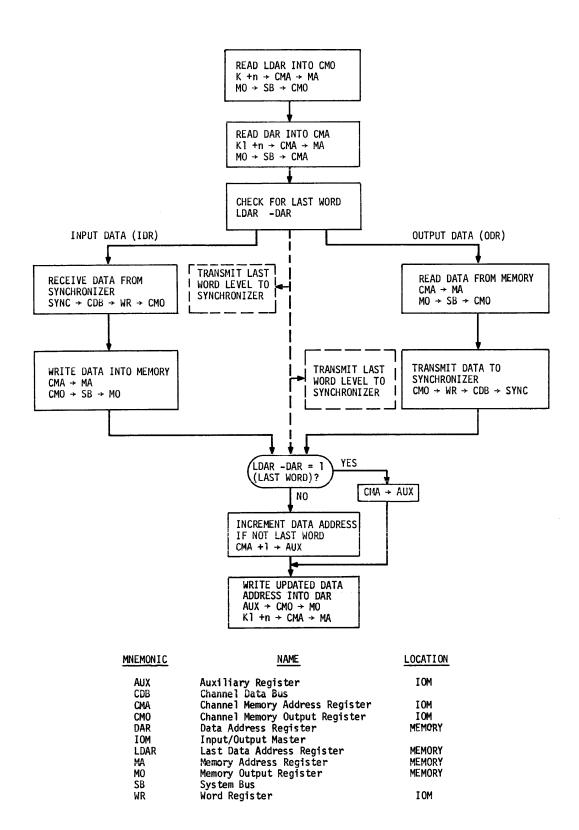

| Detailed Functional Description          | • | •  | •  | 2-67          |

| IO Master Control Logic                  |   |    |    |               |

| Channel Solvetion                        | • | •  | •  | 2-07          |

| Channel Selection                        | • | •  |    |               |

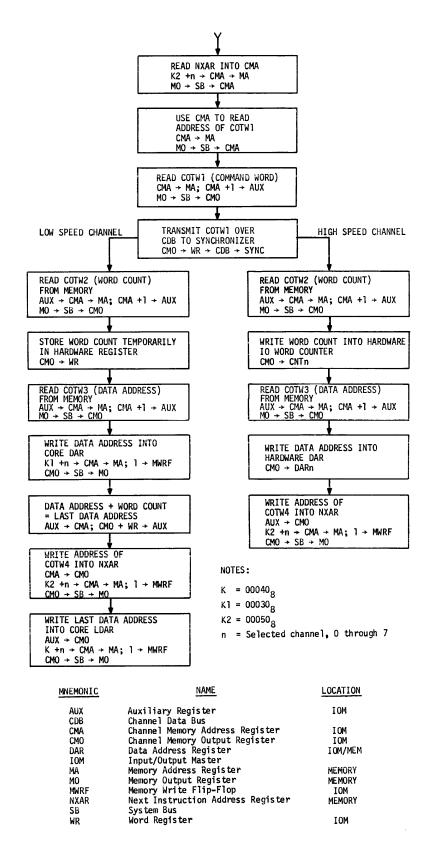

| Low Speed Channels                       | * | •  | •  | 2 <b>-</b> 69 |

| Sequence Instruction Request, High Speed |   |    |    |               |

| Channel                                  | • | •  | ٠  | 2 <b>-</b> 69 |

| Sequence Instruction Request, Low Speed  |   |    |    |               |

| Channel                                  | • | •  | •  | 2-71          |

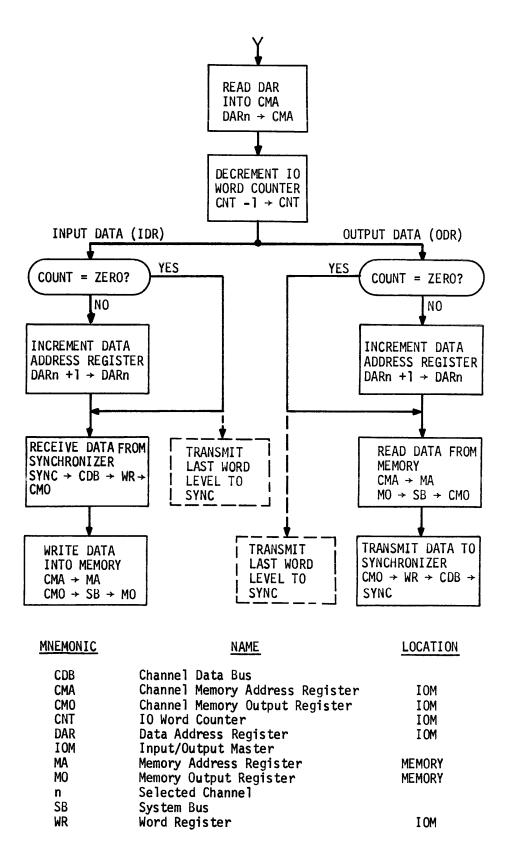

| Input Data Request, High Speed Channel   | • | •  | •  | 2-72          |

| Input Data Request, Low Speed Channel .  |   | •  | •  | 2-74          |

| Output Data Request, High Speed Channel  |   |    |    |               |

| Output Data Request, Low Speed Channel   |   |    |    |               |

| - · · · · · · · · · · · · · · · · · · ·  |   |    |    |               |

# Section 3. FORMATS AND ADDRESSING

|            | Memory Words                                |

|------------|---------------------------------------------|

|            | Instruction Words $\dots$ 3-2               |

|            | Absolute Instruction Format                 |

|            | Absolute Addressing                         |

|            | Absolute Direct Mode                        |

|            | Absolute Indirect Mode 3-6                  |

|            | Literal Instruction Format                  |

|            | Literal Class 1                             |

|            | Literal Class 2                             |

|            | Literal Class Special                       |

|            | Relative Instruction Format                 |

|            | Base Relative Addressing                    |

|            | Zero Base                                   |

|            | Program Counter Base                        |

|            | Index Common Base                           |

|            | Index Top-Of-Stack Base                     |

|            | Index Executive Base                        |

|            | Index Executive base                        |

|            | Index Relative Addresses                    |

|            | Index A                                     |

|            | Index B                                     |

|            | Relative Indirect Addressing                |

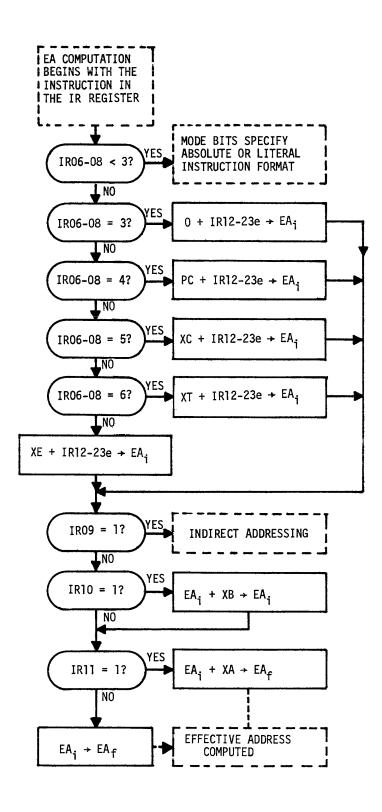

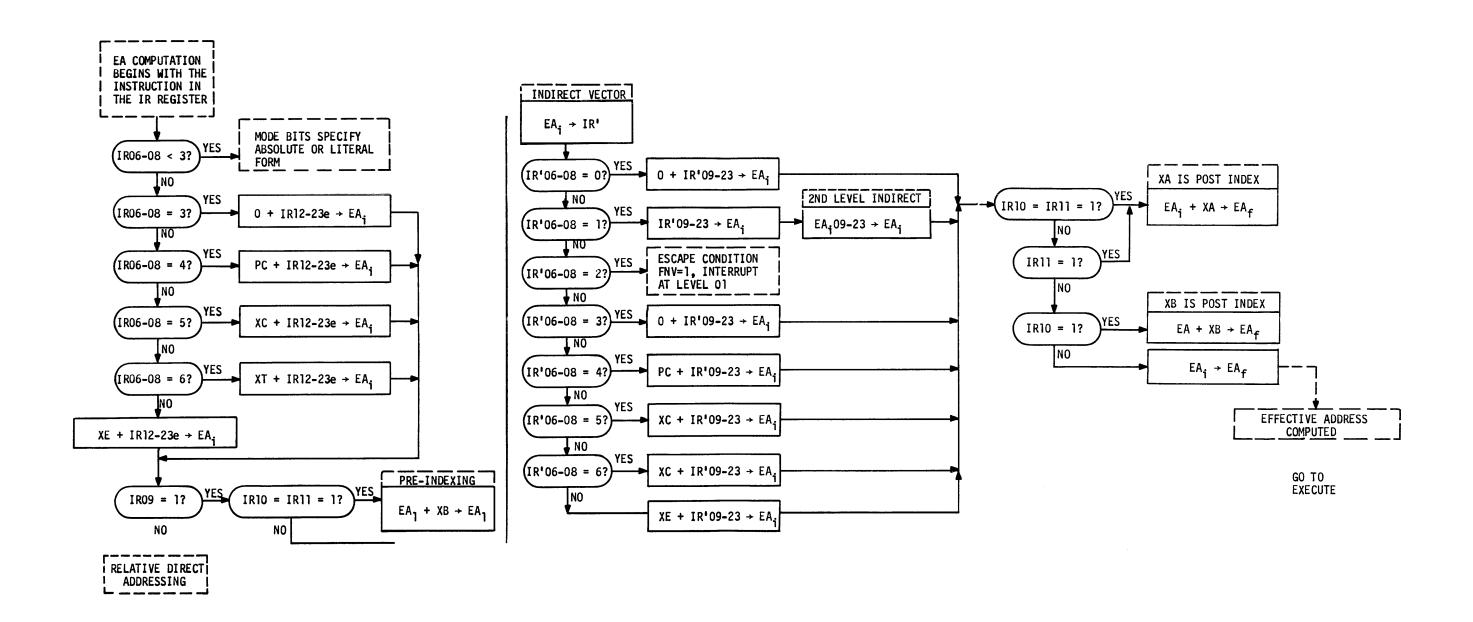

|            | Computing EA for Relative Instructions 3-21 |

|            | Relative Direct EA Computation 3-21         |

|            | Relative Indirect EA Computation 3-25       |

|            | Two-Word Instructions 3-29                  |

|            | Data Words                                  |

|            | Bit Data                                    |

|            | Character Data                              |

|            | Numeric Data                                |

|            | Fixed Point Numbers                         |

|            | Single-Precision Fixed Point Format 3-32    |

|            | Double-Precision Fixed Point Format 3-32    |

|            | Floating Point Numbers 7 25                 |

|            | Floating Point Numbers                      |

|            | Single-Precision Floating Point Format 3-36 |

|            | Double-Precision Floating Point Format 3-39 |

| Section 4. | INSTRUCTION REPERTOIRE                      |

|            |                                             |

|            | Load Instructions                           |

|            | Load A Register (LDA)                       |

|            | Load E Register (LDE)                       |

|            |                                             |

| Load Long (LDL)                           | • |   |   |   | • | 4-6         |

|-------------------------------------------|---|---|---|---|---|-------------|

| Load Long (LDL)                           | • | • | • | • | • | 4-7         |

|                                           |   |   |   |   |   |             |

| Store Instructions                        | • | • | • | • | • | 4-8         |

| Store A Register (STA)                    | • | • | • | • | • | 4-8         |

| Store E Register (STE)                    | • | • | • | • | • | <b>4-</b> 9 |

| Store Long (STL)                          | • |   | • | • | • | 4-9         |

| Masked Store (MST)                        | • |   | • |   | • | 4-9         |

| Masked Store (MST)                        | • | • | • | • | • | 4-10        |

|                                           |   |   |   |   |   |             |

| Logical Instructions                      | • | • | ٠ | ٠ | ٠ | 4-11        |

| Logical AND (AND)                         | ٠ | • | • | • | ٠ | 4-11        |

| Inclusive OR (IOR)                        | • | • | ٠ | • | • | 4-12        |

| Exclusive OR (XOR)                        | • | • | • | • | • | 4-13        |

| Rotate, Shift, and Normalize Instructions |   |   |   |   | _ | 4-14        |

| Rotate Operations                         | • | • | • | • | • | 4_74        |

| Shift Operations                          | • | • | • | • | • | 4-15        |

| Normalize Operations                      | • | • | • | • | • | 4_15        |

| Rotate Left E Register (RLE)              | • | • | • | • | • | 4_16        |

| Chiff and Dotate (CUF)                    | • | • | • | • | • | 1.17        |

| Shift and Rotate (SHF)                    | • | • | • | • | • | 1 10        |

| Rotate Right Short (RRS)                  | • | • | • | • | • | 4-10        |

| Rotate Right Long (RRL)                   | • | • | • | • | • | 4-19        |

| Rotate Left Short (RLS)                   | • | • | • | • | • | 4-19        |

| Rotate Left Long (RLL)                    | • | • | • | • | • | 4-20        |

| Shift Right Short - Arithmetic (ARS)      |   | • | • | ٠ | • | 4-21        |

| Shift Right Short - Logical (LRS) .       |   |   |   |   |   |             |

| Shift Left Short - Arithmetic (ALS)       | • | • | • | • | • | 4-22        |

| Shift Left Short - Logical (LLS) .        | • | • | • | • | ٠ | 4-23        |

| Shift Right Long - Arithmetic (ARL)       | • | • | • | • | • | 4-23        |

| Shift Right Long - Logical (LRL) .        |   |   | • |   |   | 4-24        |

| Shift Left Long - Arithmetic (ALL)        |   |   |   |   |   |             |

| Shift Left Long - Logical (LLL)           |   |   |   |   |   |             |

| Normalize Short (NMS)                     |   |   |   |   |   |             |

| Normalize Long (NML)                      | • |   | • | • | • | 4-29        |

|                                           |   |   |   |   |   | 4 20        |

| Fixed Point Arithmetic Instructions       |   |   |   |   |   |             |

| Add Short (ADD)                           | • | • | • | • | • | 4-33        |

| Add Long (ADL)                            | • | • | • | • | • | 4-34        |

| Subtract Short (SUB)                      | • | ٠ | • | • | • | 4-35        |

| Subtract Long (SBL)                       | • | ٠ | • | • | • | 4-36        |

| Divide (DIV)                              | • | • | • | ٠ | ٠ | 4-38        |

| Multiply (MPY)                            | • | • | • | • | • | 4-40        |

| Floating Point Arithmetic Instructions    | _ |   |   |   |   | 4_40        |

| Floating Point Add Short (FAS)            | • | • |   |   |   | 4_48        |

| Floating Point Add Long (FAL)                  |

|------------------------------------------------|

| Index Control Instructions  Load Index A (LXA) |

| Branch Instructions                            |

| Linkage Instructions                           |

| Compare With Memory Instruction 4-97           |

| Bit Manipulation Instruction                   |

| Byte Manipulation Instruction                  |

| Special Instructions                           |

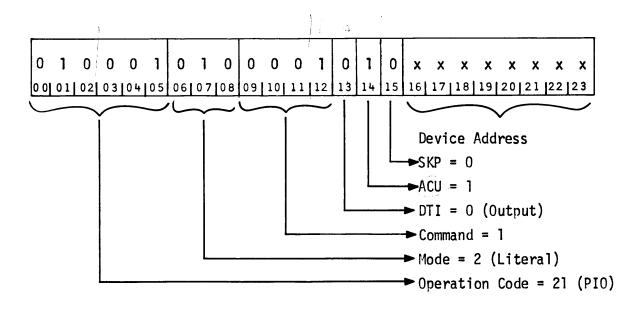

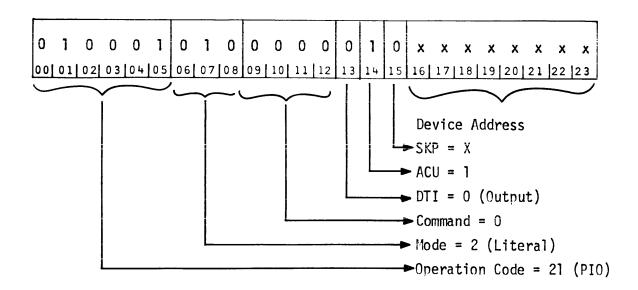

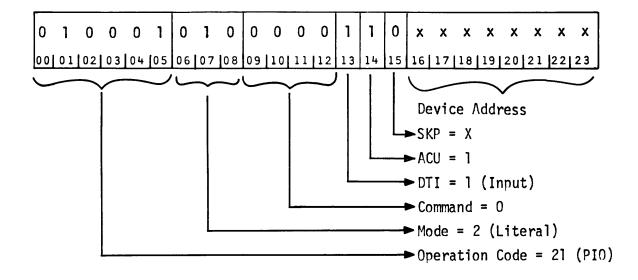

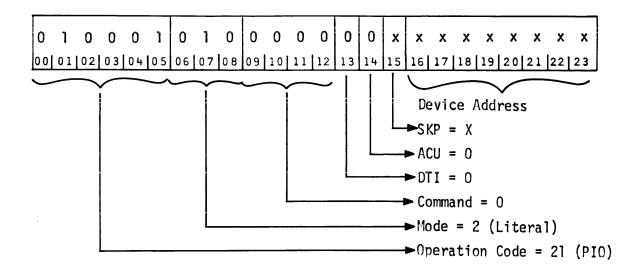

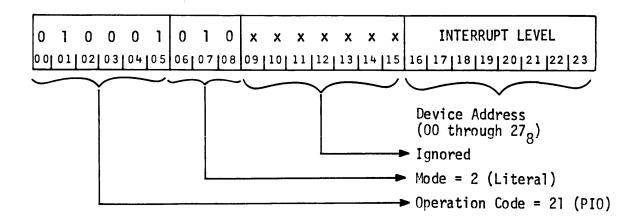

|             | Programmed Input Output Instruction                                                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 5   | INTERRUPT STRUCTURE                                                                                                                                                               |

| 30001011 3. |                                                                                                                                                                                   |

|             | Program Priorities                                                                                                                                                                |

|             | Interrupt Dedicated Memory5-5                                                                                                                                                     |

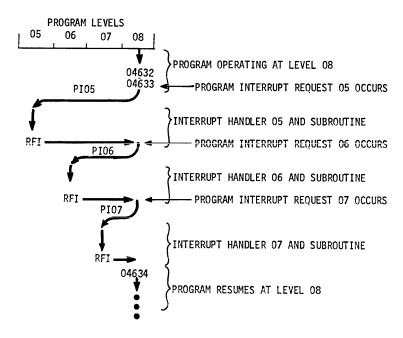

|             | Interrupt Hardware Action 5-6                                                                                                                                                     |

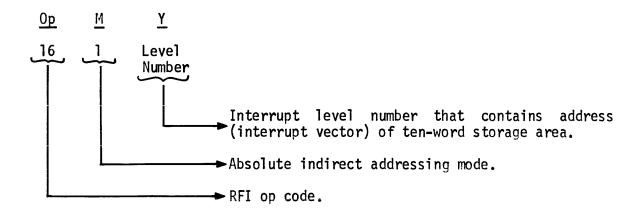

|             | Return From Interrupt                                                                                                                                                             |

|             | Interrupt Classes                                                                                                                                                                 |

| Section 6.  | OPERATING PROCEDURES                                                                                                                                                              |

|             | Power Distribution Unit Operation 6-1 Controls and Indicators 6-1 Power Turn-On 6-1 Transferring to Standby Power 6-4 Power Turn-Off 6-4 Central Processor Off-Line Operation 6-4 |

|             | Control Panel                                                                                                                                                                     |

|             | Control Panel Procedures 6-12                                                                                                                                                     |

|            | System Start Up                                                              |

|------------|------------------------------------------------------------------------------|

|            | Paper Tape IO Requests 6-26 Operating Procedures 6-28 Operating Summary 6-30 |

| Section 7. | DRUM                                                                         |

|            | Drum Status Register                                                         |

|            | Drum Addressing                                                              |

|            | Speed of Operations                                                          |

|            | Drum Instruction Repertoire                                                  |

|            | Drum Operation                                                               |

|            | Pressure System                                                              |

| Section 8. | REAL TIME CLOCKS                                                             |

|            | Functional Description 8-1                                                   |

|            | Functional Summary                                                           |

|             | Clock Addresses                            |

|-------------|--------------------------------------------|

|             | Clock Instruction Repertoire               |

|             | Clock Instruction Summary 8-12             |

| Section 9.  | SYSTEM SECURITY                            |

|             | Synchronizer Logic                         |

|             | Security Check Logic                       |

|             | Stall Alarm Logic                          |

|             | Power Failure/Restart Logic                |

|             | Thermal Alarm Logic                        |

|             | Process Control Status Logic               |

|             | System Flunk Line                          |

|             | Instruction Repertoire                     |

|             | Read Interrupt Level Status (RILS 00) 9-14 |

|             | Write Data (WDA SSEC) 9-15                 |

|             | Read Data (RDA SSEC)                       |

|             | Operating Procedures                       |

| Appendix A. | FOX 1 SYSTEM CHARACTER SET                 |

| Appendix B. | INSTRUCTION SUMMARY                        |

| Appendix C. | PROGRAMMING EXAMPLES                       |

| Appendix D. | ARITHMETIC NOTATION                        |

| INDEX       |                                            |

| xvi Con     | tents                                      |

#### FIGURES

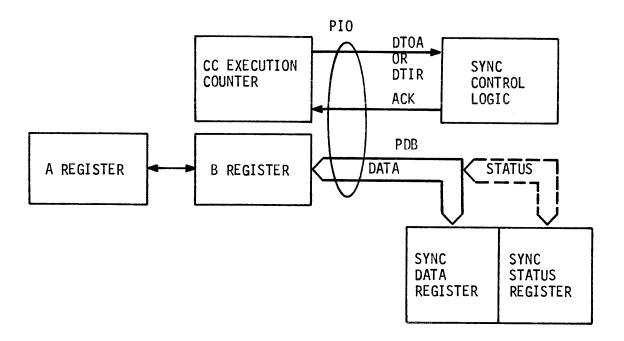

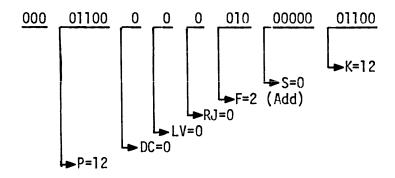

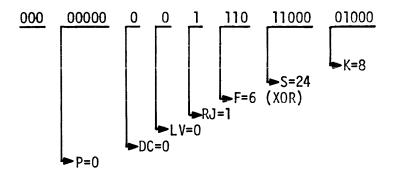

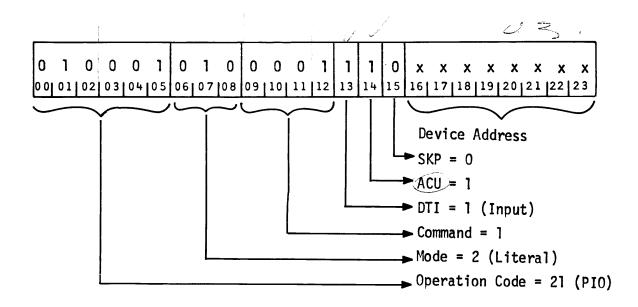

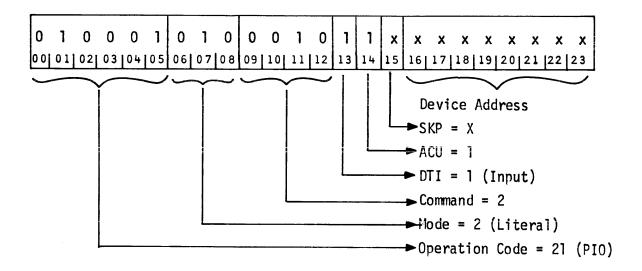

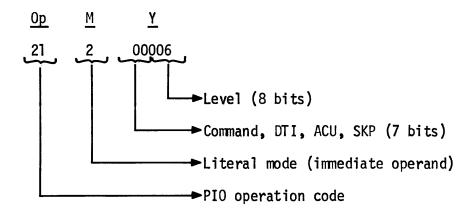

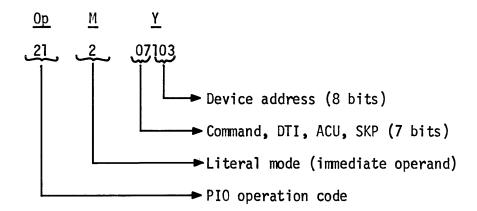

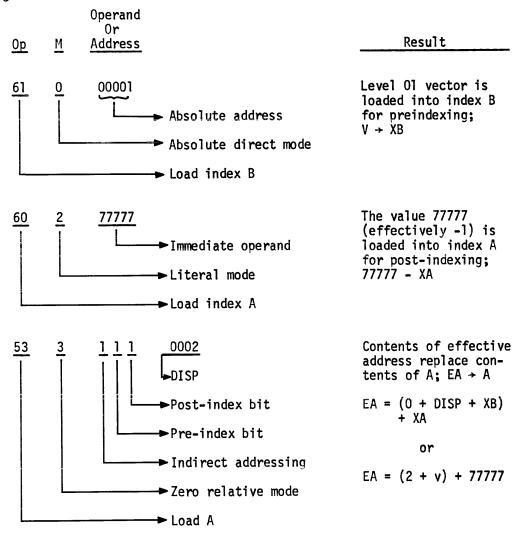

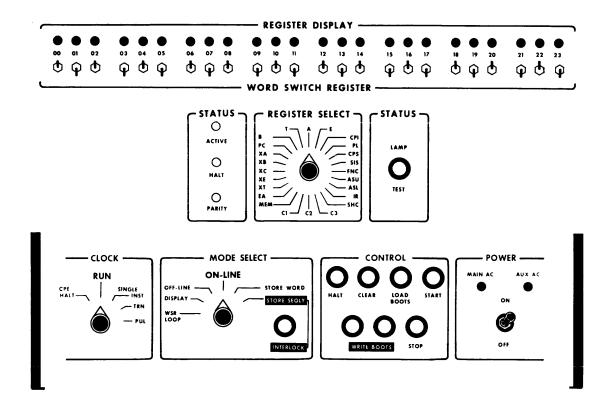

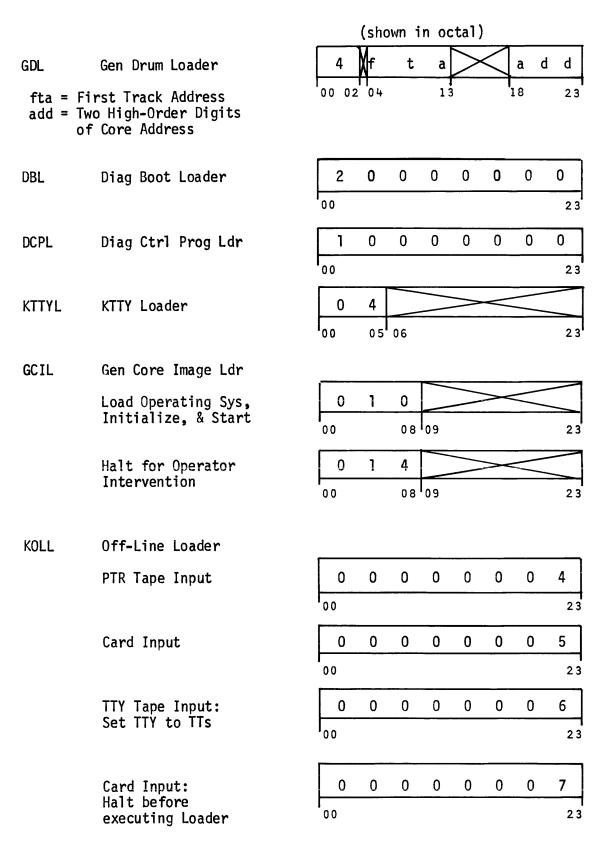

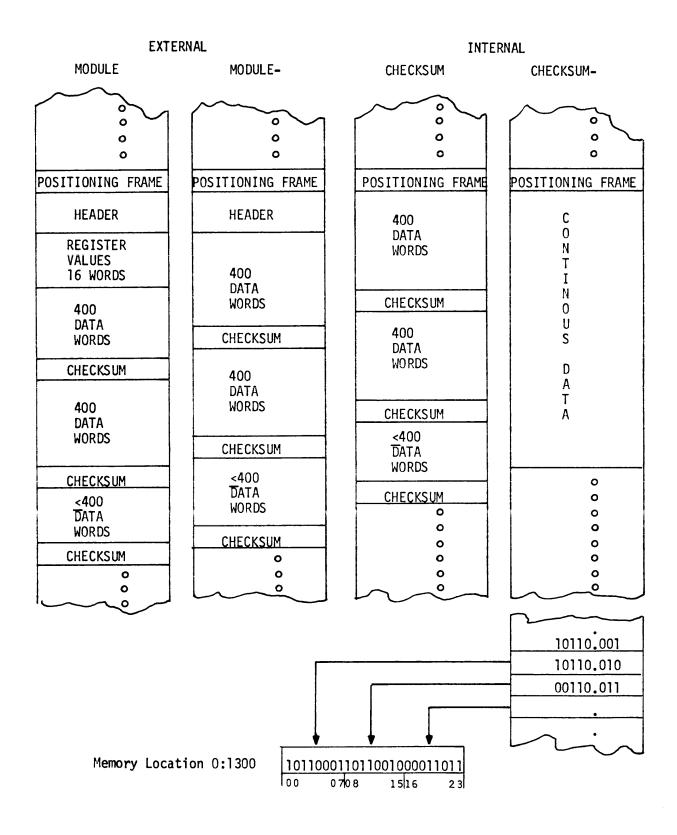

| 2-1-1. 2-2-1. 2-2-2. 2-2-3. 2-2-4. 2-2-5. 2-2-6. 2-2-7. 2-2-8. 2-2-9. 2-2-10. 2-2-11. 2-2-12. 2-3-1. 2-3-2. 2-3-4. 2-4-1. 2-4-2. 2-4-3. 2-6-1. 2-6-2. 2-6-3. 2-6-4. | Central Processor Simplified Block Diagram Central Processor Block Diagram Memory Control Unit Major State Control PIO Data and Control Paths PIO Instruction and Operand Format, Literal Mode PIO Instruction and Operand Format, Non-Literal Mode PIO Command Block Diagram PIO Data Transfer Block Diagram PIO Read/Write Sequence CIO Data and Control Paths Sequence Instruction Request, High/Low Speed Channel Imput/Output Data Sequence, High Speed Channel Imput/Output Data Sequence, Low Speed Channel Computation of EA for Absolute Instructions Relative Direct EA Computation Typical Memory Map Computation of EA for Relative Indirect Instruction Normalize Short Flow Diagram Interrupt and RILS Action Interrupt Action Example Central Processor Control Panel C1, C2, and C3 Register Display Identification WSR Settings for Drum Track Zero Loader Programs KTTY Paper Tape Formats |     | 2-7<br>2-35<br>2-38<br>2-46<br>2-46<br>2-47<br>2-48<br>2-50<br>2-70<br>2-73<br>2-76<br>3-5<br>3-13<br>3-15<br>3-23<br>4-30<br>4-136<br>5-9<br>6-6<br>6-9<br>6-18 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                     | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                                                                                                                                                                  |

| 2-2-1.                                                                                                                                                              | Dedicated Memory Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • • | 2-3<br>2-9                                                                                                                                                       |

| 2-2-2.<br>2-2-3.                                                                                                                                                    | Addressable Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • • | 2-17                                                                                                                                                             |

| 2-2-3.<br>2-2-4.                                                                                                                                                    | Operational States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                                                                                                                                                                  |

| 2-2-5.                                                                                                                                                              | PIO Control Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | • • | 2-45                                                                                                                                                             |

| 2-2-6.                                                                                                                                                              | Standard IO Device Address Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                                                                                                                                                                  |

| 2-2-7.                                                                                                                                                              | Unassigned Standard IO Device Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 2-52                                                                                                                                                             |

| 2-2-7.                                                                                                                                                              | Summary of PIO Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • • | 2-55                                                                                                                                                             |

| 2-2-9.                                                                                                                                                              | IO Master and Channel Logic Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •   | 2-57                                                                                                                                                             |

| 2-2-9.                                                                                                                                                              | Channel IO Bus (59 Lines)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 2-58                                                                                                                                                             |

| 2-2-10.                                                                                                                                                             | Channel IO Operations Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 2-68                                                                                                                                                             |

| 2-3-1.                                                                                                                                                              | Floating Point Short Notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 3-38                                                                                                                                                             |

| 2-3-2.                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 3-42                                                                                                                                                             |

| 4-0-4.                                                                                                                                                              | Floating Point Long Notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • • | 0 <del>- 4</del> 6                                                                                                                                               |

| 2-4-1. | CWM Extended Mnemonics                         |

|--------|------------------------------------------------|

| 2-4-2. | Secondary Op Code Bit Specifications 4-106     |

| 2-4-3. | BIT Instruction Extended Mnemonics 4-107       |

| 2-4-4. | PIO Instruction Extended Mnemonics 4-12:       |

| 2-4-5. | Instructions Listed By Execution Counter 4-137 |

| 2-5-1. | Interrupt Priority Assignment 5-12             |

| 2-5-2. | Standard Hardware Interrupts                   |

| 2-6-1. | PDU Controls and Indicators 6-2                |

| 2-6-2. | Auxiliary Bootstrap Program                    |

| 2-6-3. | KTTY Operator Request Formats                  |

# 1/INTRODUCTION

The FOX 1 central processor integrates, synchronizes, and controls the functions of all other components of the system. Triggered by an internal real-time clock or external process events, foreground programs in the processor scan process instrumentation inputs, perform control algorithm calculations, and transmit the results to process control devices. Background programs perform data processing and software development tasks on a time-available basis. Advanced hardware design features provide reliable real-time processing, extensive general purpose capability, and rapid, efficient switching between foreground and background work.

#### Some of these features are:

- a. Word-oriented memory, 24-bit (plus parity)

- b. Information manipulation on single words, double words, bytes (variable size), and bits.

- c. Expandable memory from 16,384 to 32,768 words, in increments of 8,192 or 16,384 words.

- d. Automatic shutdown and startup procedures, and memory protection for power fail-safe operation.

- e. Flexible addressing techniques:

- (1) Direct addressing of all 32,768 words (without need of indirect, indexing, or displacement addressing).

- (2) Immediate addressing of operands (space- and timesaving).

- (3) Two-level indexing (preindexing, postindexing, or both).

- (4) Two-level indirect addressing.

- f. Sixteen addressable hardware registers for arithmetic and control operation.

- g. Selective register and memory protection.

- h. Address stop capability (optional) for on-line program debugging.

- i. Privileged assignment of system resources.

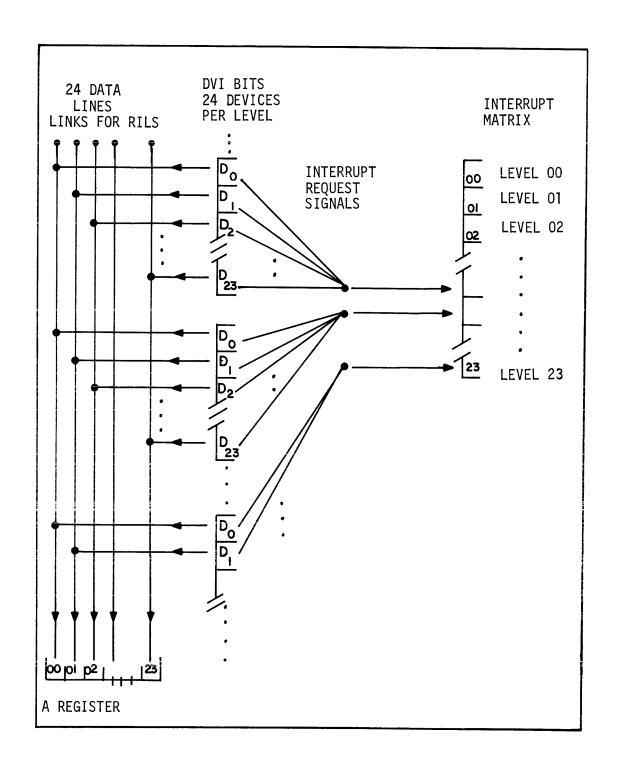

- j. Priority interrupt system offering 12 standard or 24 optional priority interrupt levels. Each level is capable of handling software, hardware, and IO interrupts simultaneously. Up to 24 devices may be assigned to each interrupt level.

- k. Automatic, rapid-context switching for fast interrupt service.

- 1. A trapping system that enables use of operating system resources without interference with real-time operation.

- m. Multiple real-time clocks for timing programmed events.

- n. Complete and powerful instruction repertoire consisting of the following:

- (1) Bit and byte manipulation.

#### 1-2 Introduction

- (2) Multiple word data transfers.

- (3) Register-to-register operation.

- (4) Fixed point arithmetic operations, in single-word and double-word data formats, with overflow detection and control.

- (5) Floating point arithmetic operations in long and short data formats, with overflow, underflow, and normalization control.

- (6) All floating point arithmetic operations are performed in double-precision form for greater accuracy. Single-precision operands are converted to double-precision format; the arithmetic is performed; then the results are rounded and returned to single-precision format.

- (7) Logical arithmetic operations (AND, OR, exclusive OR, masked store).

- (8) Arithmetic operations in byte manipulation.

- (9) Comparison operations, on fixed point and floating point data.

- (10) Shifting operations on both long and short data: arithmetic, logical, and normalize.

- (11) Push-down stack manipulating instructions for dynamic control of memory allocation, subroutine calls, and subroutine exits.

- o. Complete IO system, providing the following features:

- (1) Programmed IO control of all IO operations.

- (2) Privileged IO usage on basis of need.

- (3) Up to 24 devices assigned to each interrupt level.

- (4) Eight IO channels (two high-speed, six low-speed) with direct access to memory.

- (5) IO command chaining for uninterrupted channel IO transfers.

- (6) IO status checking without activity disturbance.

- (7) Direct IO without use of channels.

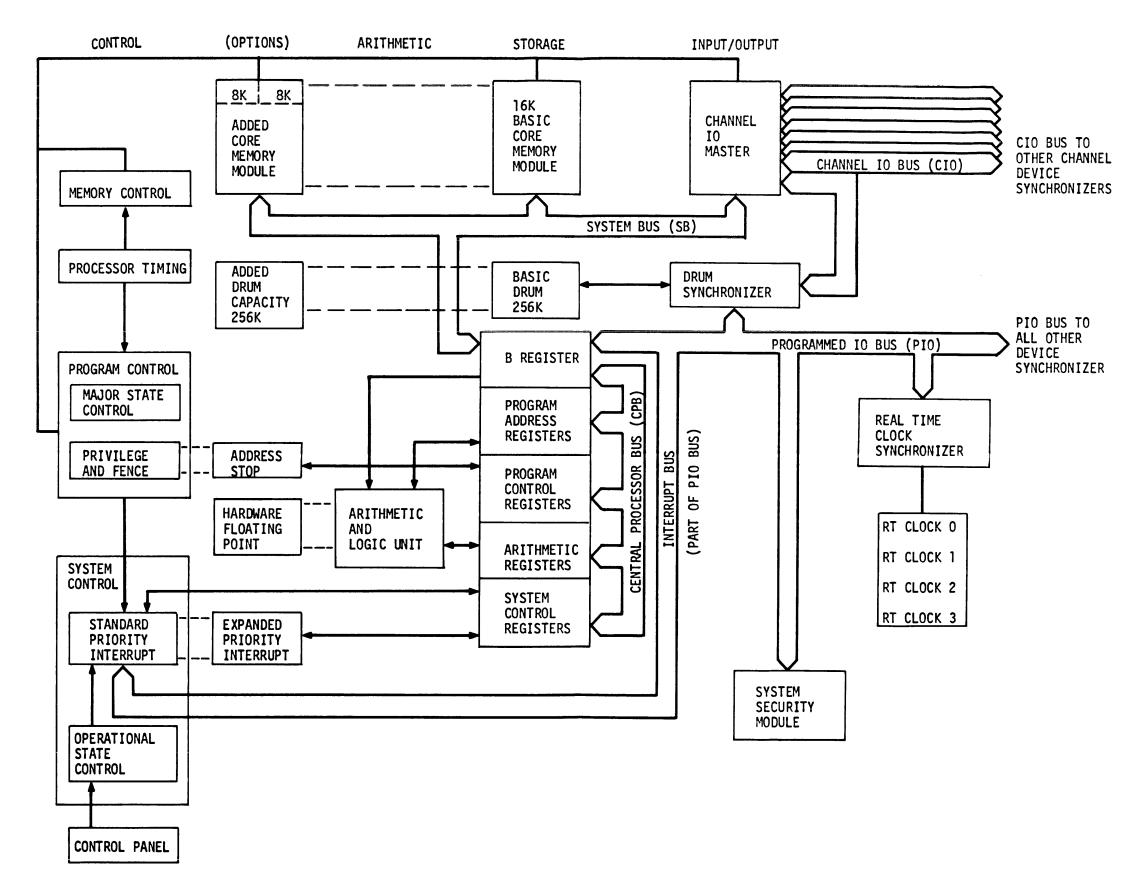

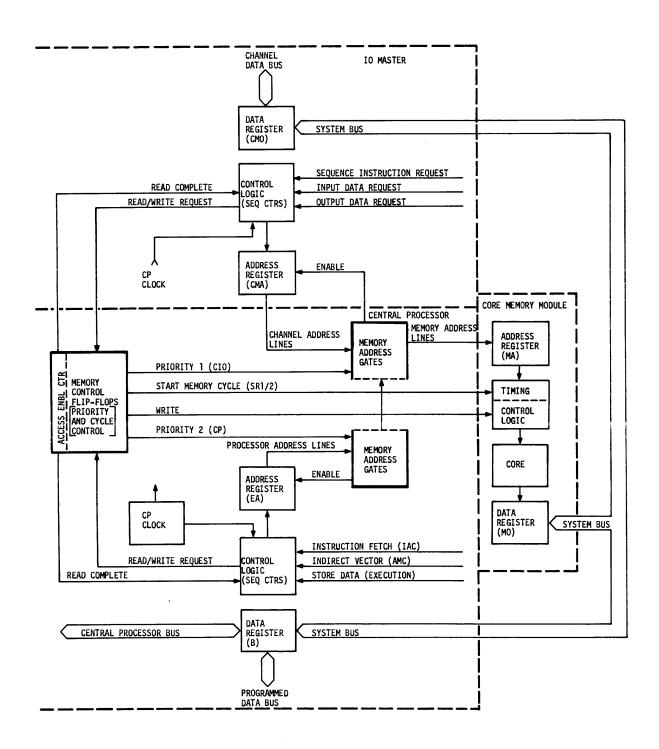

The major elements of the FOX 1 central processor, as show in Figure 2-1-1, are:

- a. A heirarchical storage system consisting of

- (1) A core memory optionally expandable from the basic 16,384 words to 24,576 or 32,768 words.

- (2) A drum memory providing 256 or 512 tracks (1024 words per track) of bulk data storage.

- (3) Hardware registers (16 of which are program addressable) to store address and control information pertinent to individual programs, and data in process.

Figure 2-1-1. Central Processor Simplified Block Diagram

- (4) A bus system interconnecting storage media, the processor, and the input/output subsystem.

- b. A processor that controls all system activity, including the following:

- (1) Memory Access Control -- priority allocation and cycle control.

- (2) Program Control -- major state control.

- (3) System Control -- operational state control and priority interrupt.

- c. An input/output section including:

- (1) Programmed IO -- one common data bus using the processor's arithmetic registers to receive or transmit data.

- (2) Channel IO -- using up to eight dedicated data channels interfacing with an IO master control unit that provides direct memory access.

# 2/FUNCTIONAL HARDWARE

#### STORAGE

Core memory stores the operating system software and several user programs, drum memory provides a bulk storage<sup>1</sup> pool for additional programs and data, and hardware registers contain program operating limits, address modification constants, and arithmetic operands and results. All media use the same 24-bit data word length, but core and drum also store a parity bit for each word. Parity is checked at the storage interface -- the parity bit is not transmitted to the processor or channel IO master.

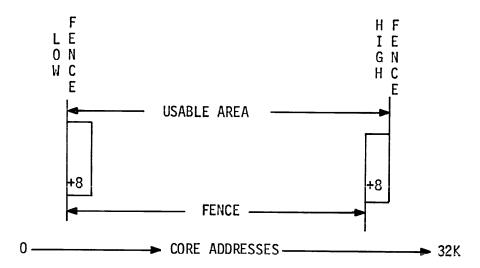

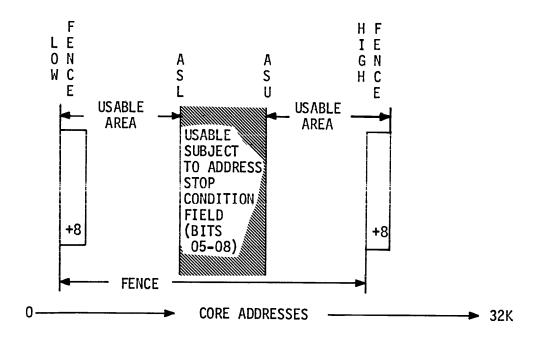

A storage protection system limits the area of core available to individual programs (memory fence and address stop protection) and requires an appropriate privilege to use the drum (system IO privilege) or to alter the contents of addressable registers (executive mode bit or register manipulation privilege, software interrupt privilege, or trace control privilege, depending upon the specific register involved).

#### Core Memory

Core memory operates asynchronously from the processor logic, performing a full cycle (read and restore, or clear and write) operation in 960 nanoseconds. Data read from memory are available to the processor or channel IO master 640 nanoseconds after the start of the memory cycle.

<sup>&</sup>lt;sup>1</sup>Bulk storage operations mentioned here as being performed by the drum can, at times, be performed by the disk. The optional disk memory subsystem is described in detail in Volume 3, Section 6.

<u>Core Capacity</u> - Storage capacity of the basic 2 1/2 D, 22-mil ferritecore memory is 16,384 words, and can be expanded optionally to 24,576 words or 32,768 words. Memory locations are identified by octal numbers from 00000 through 37777 for 16K words, through 57777 for 24K words, or through 77777 for 32K words. All memory locations can be directly addressed. Indirect-addressing, relative-addressing, and addressing facilities are provided to simplify address manipulation and to make programs relocatable.

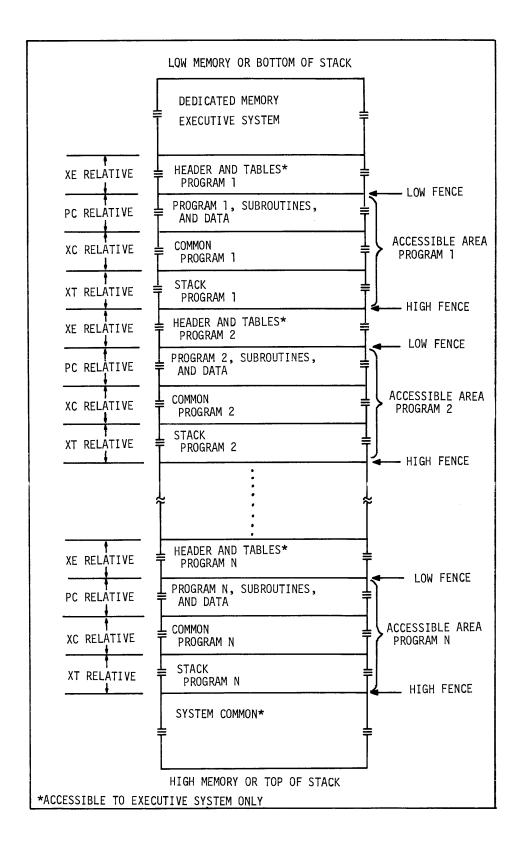

Memory Allocation Features - The central processor hardware provides very flexible methods for allocating memory areas for software systems operations. These methods are a combination of hardware and software address manipulation, using the index top-of-stack register (XT register), the index common register (XC register), and the index executive register (XE register). (Refer to the description of these registers under Program Address Registers.)

<u>Dedicated Core Locations</u> - Areas of core memory are reserved for, or dedicated to, special use as shown in Table 2-2-1. Sixteen programaddressable CP hardware registers are assigned addresses 77760 through 77777. In systems containing 32K of memory, the processor is inhibited from accessing the last 16 core locations. (Channel IO master access to these locations -- although permitted -- is of no practical use, since the processor cannot access them for IO error correction.)

#### Drum Memory

The following deals with the drum only as an extension of the storage capacity of core memory. Details of drum hardware and programming are covered in Section 7 of this volume.

#### 2-2 Functional Hardware

Table 2-2-1. Dedicated Memory Allocation

| OCTAL<br>ADDRESS FIELD | DECIMAL<br>LOCATIONS | USAGE                                                                              |

|------------------------|----------------------|------------------------------------------------------------------------------------|

| 00000 to 00027         | 24                   | Interrupt Block Vectors                                                            |

| 00030 to 00031         | 2                    | Nondedicated Memory                                                                |

| 00032 to 00037         | 6                    | IO Data Address Registers for CIO<br>Low-Speed Channels*                           |

| 00040 to 00041         | 2                    | Nondedicated Memory                                                                |

| 00042 to 00047         | 6                    | <pre>IO Last Address Registers for CIO Low-Speed Channels**</pre>                  |

| 00050 to 00057         | 8                    | IO Next Instruction Address Registers for ALL CIO Channels; provides IO Linkage*** |

| 00060                  | 1                    | Nondedicated Memory                                                                |

| 00061                  | 1                    | Floating Point Temporary Storage                                                   |

| 00062 to 00067         | 6                    | Nondedicated Memory                                                                |

| 00070                  | 1                    | Restart Trap                                                                       |

| 00071 to 00077         | 7                    | Nondedicated Memory                                                                |

| 00100                  | 1                    | Fence Violation Trap (BSP, BSR)                                                    |

| 00101                  | 1                    | Literal Trap (BSP, BSR)                                                            |

| 00102 to 77757         |                      | Nondedicated Memory****                                                            |

| 77760 to 77767         | 8                    | Protected Registers                                                                |

| 77770 to 77777         | 8                    | Unprotected Registers                                                              |

#### NOTES

$<sup>\</sup>star$ Used to store memory address of first transmitted word.

<sup>\*\*</sup>Computed from IO data address register, plus word count (address of last word used in data transmission).

<sup>\*\*\*</sup>Indirect pointers to channel IO command and three-word information block (set by program).

<sup>\*\*\*\*</sup>Depending upon memory size, this block is 16,302 words, 24,494 words, or 32,686 words, yielding a total nondedicated memory size of 16,314 words, 24,506 words, or 32,698 words.

Drum memory provides rapid access to relatively large amounts of data. Two choices of drum capacity are available: 256 tracks or 512 tracks (1 track = 1024 words). The use of 50 or 60 cycle primary power determines drive motor speed, fixing the time required for one drum revolution at 20.4 milliseconds or 16.7 milliseconds, respectively. During one drum revolution, 1024 words (one track) can be read or written. Thus, the continuous data rate (up to one track) is one computer word transmitted every 15.2 microseconds. The average track access time is 8.3 milliseconds (one-half revolution). Since channel IO transfers data to or from the drum by direct memory access, other program instructions can be executed while a drum transfer is taking place.

Program Swapping - FOX 1 programs may be separated into core-resident and drum-resident. The operating system and associated tables, common subroutines, and time-critical foreground (process control) programs are core-resident. But the majority of the programs are drum-resident, read into core before execution time by the operating system.

<u>Program Relocation</u> - Space in core memory is partitioned to receive drumresident programs of several different priorities. If the core partition for the priority level of a given program is not available immediately prior to its execution, the operating system reassigns the program to an available partition of lower priority. Therefore, all programs controlled by the operating system must be relocatable.

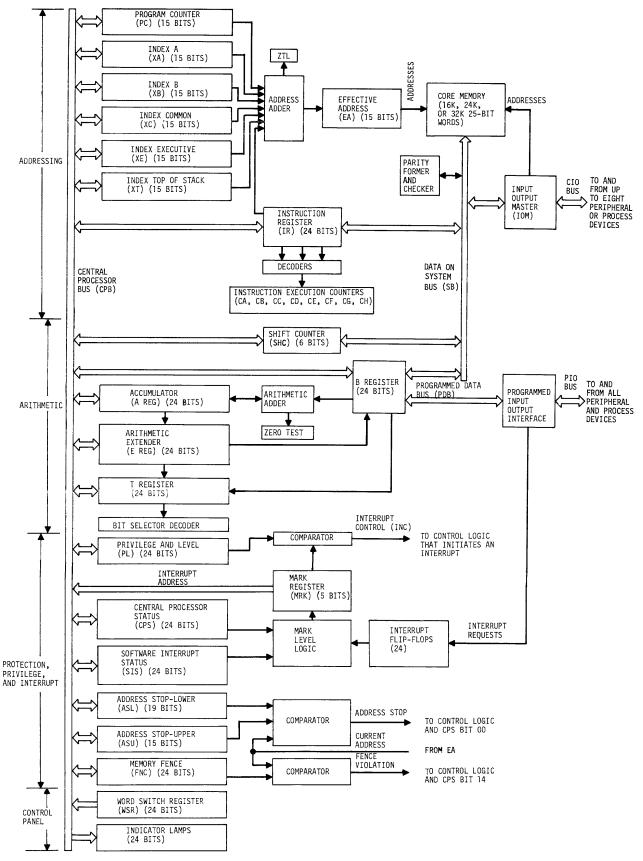

#### Program Address Registers

In contrast to core and drum, which provide general purpose storage, most registers are limited to specific types of information. Therefore, register storage can be separated according to use into four groups:

#### 2-4 Functional Hardware

- a. Program Address Registers: those registers involved in address arithmetic or supplying operating parameters for individual instructions or programs.

- b. Program Control Registers: those registers containing operating limits for individual programs.

- c. Arithmetic and Logic Registers: those registers involved in computation or decision logic.

- d. System Control Registers: those registers controlling the multiprogramming environment.

Operating system software and relocation hardware use the registers in the first group, the program address registers, to make programs fully relocatable. Relative addressing uses the contents of one of four dedicated base registers as a reference point for locating program instructions, common operating data, initialization data, or subroutine linkage information. The address field of a relocatable instruction can provide a displacement up to  $\pm 2048$  from the value designated by the base register. Either of two index registers can be used to change the sum of base value and displacement up to  $\pm 16,384$ .

Nine registers (two of which are also counters) make up the program address group. The six relocation registers in the group are directly addressable by the program; only the XE requires a register privilege to permit changing its contents. The three nonaddressable registers included in this group are:

- a. Instruction Register

- b. Shift Counter

- c. Effective Address Register

The following six address modification registers are program addressable:

- d. Program Counter

- e. Index Common

- f. Index Executive

- g. Index Top-of-Stack

- h. Index A

- i. Index B

Addressing, arithmetic, and control registers are shown in detail in Figure 2-2-1, and their characteristics summarized in Table 2-2-2.

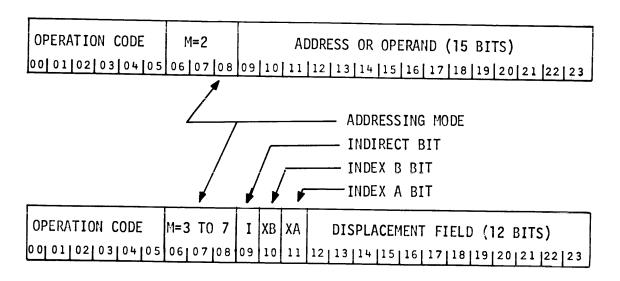

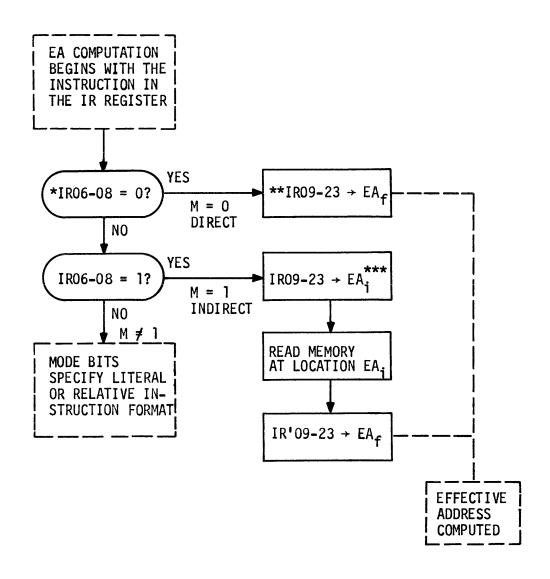

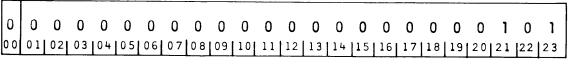

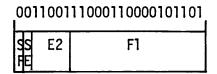

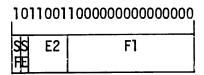

<u>Instruction Register (IR, Not Addressable, 24 Bits)</u> - Hardware directs the instruction word read from core into the instruction register (IR), which, in turn, is separated into three sub-registers: the D register, containing the 6-bit operation code, the M register, containing the 3-bit mode field; and the address register (AR), containing a 15-bit field.

| _ | D                     | M        | AR                                                                       |

|---|-----------------------|----------|--------------------------------------------------------------------------|

|   | OPERATION CODE        | M=0 OR 1 | ADDRESS FIELD (15 BITS)                                                  |

| 0 | 0 0 1 0 2 0 3 0 4 0 5 | 06 07 08 | 09   10   11   12   13   14   15   16   17   18   19   20   21   22   23 |

Figure 2-2-1. Central Processor Block Diagram

The D register is decoded to answer the following questions:

- a. Is a memory operand access (MOA) required for this instruction?

- b. If the literal mode is specified, is the value in the AR an operand (literal class 1), or an address (class 2)? For class 1 literals (operands), bit 09 of the AR is left-propagated to form a 24-bit signed data word in the B register. Class 2 literals, memory (or register) addresses, are left at 15 bits. Literals used in subroutine linkage or long form floating point instructions are placed in a third category, class special.

- c. Which execution counter controls this instruction?

- d. Which control lines provided by the selected execution counter are appropriate to this specific instruction?

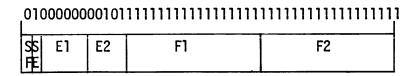

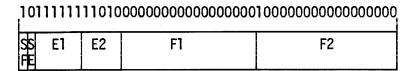

For absolute modes, the M register indicates whether AR contains a direct address (M = 0), an indirect address (M = 1), or a literal value (M = 2). For relative modes, the M register indicates the source of the value to be added to the contents of the AR: PC (M = 4), XC (M = 5), XT (M = 6), or XE (M = 7). When M = 3, a value of 00000 is added to AR.

For absolute modes 0 and 1, AR contains a 15-bit memory (or register) address; for relative modes 3 through 7, the AR is subdivided into four fields: I, the indirect bit, which identifies the contents of AR as the address of an address; XB, the bit specifying the use of the XB index register for address computation; and XA, the bit specifying the use of the XA index register. The remaining 12-bit value represents a signed displacement from the base reference. AR provides one of the inputs to the address adder during effective address computation.

Table 2-2-2. Addressable Registers

| USE NAME                         |                                         | MNEMONIC | SIZE<br>(IN BITS) | ADDRESS | INTERRUPT ACTION     |                  | ECTION      | FORMAT AND BIT POSITION ASSIGNMENT                                                                                    |  |  |  |  |  |

|----------------------------------|-----------------------------------------|----------|-------------------|---------|----------------------|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 031                              | MAPIL                                   | MACMONIC | (IN B113)         | ADDRESS | (S=SAVED I=INITIAL.) | PRIVILEGE        | 1 VIOLATION | 00   01   02   03   04   05   06   07   08   09   10   11   12   13   14   15   16   17   18   19   20   21   22   23 |  |  |  |  |  |

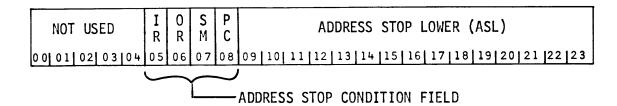

| PROGRAM                          | Address Stop<br>- Lower                 | ASL      | 19                | 77760   |                      | ТСР              | RPV         | * * * * * I O S P ADDRESS STOP (Lower)                                                                                |  |  |  |  |  |

| TESTING                          | Address Stop<br>- Upper                 | ASU      | 15                | 77761   |                      | ТСР              | RPV         | * * * * * * * * * * * ADDRESS STOP (Upper)                                                                            |  |  |  |  |  |

| OPERATING<br>SYSTEM              | Index Execu-<br>tive                    | ΧE       | 15                | 77762   |                      | RMP              | RPV         | * * * * * * * * * INDEX EXECUTIVE                                                                                     |  |  |  |  |  |

| MANUAL<br>CONTROL                | Word Switch                             | WSR      | 24                | 77763   |                      | Read Only        | None        | + + + + + + + + + + + + + + + + + + +                                                                                 |  |  |  |  |  |

| CVCTFM                           | Software In-<br>terrupt Status          | SIS      | 24                | 77764   |                      | RMP, SIP         | RPV, SIV    | Software Interrupt Status                                                                                             |  |  |  |  |  |

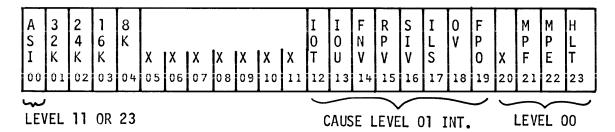

| SYSTEM<br>CONTROL                | Central Pro-<br>cessor Status           | CPS      | 24                | 77765   |                      | RMP              | RPV         | A 3 2 1                                                                                                               |  |  |  |  |  |

|                                  | Memory Fence                            | FNC      | 24                | 77766   | S I                  | RMP              | RPV         | HIGH FENCE LOW FENCE                                                                                                  |  |  |  |  |  |

| INDIVIDUAL<br>PROGRAM<br>CONTROL | Privilege<br>and Level                  | PL       | 24                | 77767   | S I                  | RMP <sup>2</sup> | RPV         | E R S S C N T A I LOWEST HIGHEST INTERRUPT STATUS B P P O O O P E O UL LL IS                                          |  |  |  |  |  |

|                                  | Program<br>Counter                      | PC       | 15                | 77770   | S I                  | None             | None        | * * * * * * * * PROGRAM COUNTER                                                                                       |  |  |  |  |  |

| ADDRESS                          | Index Common                            | хс       | 15                | 77771   | S I                  | None             | None        | * * * * * * * * INDEX COMMON                                                                                          |  |  |  |  |  |

| MODIFICATION                     | Index<br>Top-of-Stack                   | ΧТ       | 15                | 77772   | S I                  | None             | None        | * * * * * * * * * INDEX TOP-OF-STACK                                                                                  |  |  |  |  |  |

|                                  | Index B                                 | ΧВ       | 15                | 77773   | S I                  | None             | None        | * * * * * * * * * INDEX B                                                                                             |  |  |  |  |  |

|                                  | Index A                                 | XA       | 15                | 77774   | S                    | None             | None        | * * * * * * * * INDEX A                                                                                               |  |  |  |  |  |

| ARITHMETIC                       | Accumulator<br>(Arithmetic<br>Register) | A        | 24                | 77775   | S                    | None             | None        | ACCUMULATOR                                                                                                           |  |  |  |  |  |

| AND<br>LOGIC                     | Arithmetic<br>Extender                  | E        | 24                | 77776   | S                    | None             | None        | ARITHMETIC EXTENDER                                                                                                   |  |  |  |  |  |

|                                  | Central<br>Processor<br>Indicator       | CPI      | 5                 | 77777   | S                    | None             | None        | F F B B B B U T O T O T O T O T O T O T O T O T O T                                                                   |  |  |  |  |  |

<sup>\*</sup>Indicates bits that cannot be changed by any instruction. Also, if a register containing \* is used as an operand, the value of \* is 0. †Indicates bits that can be read but not altered.

$^{1}\text{EMB}$  = 1 grants all privilege.  $^{2}\text{SPL}$  instruction can change IS within UL  $\leq$  IS  $\leq$  LL.

Shift Counter (SHC, Not Addressable, 6 Bits) - As a register, the shift counter extends the capacity of the IR during instruction access for the following types of information:

- a. Secondary operation code (micro-code) for the Bit and Compare With Memory instructions.

- b. Number of words to be moved by the Move Multiple instruction.

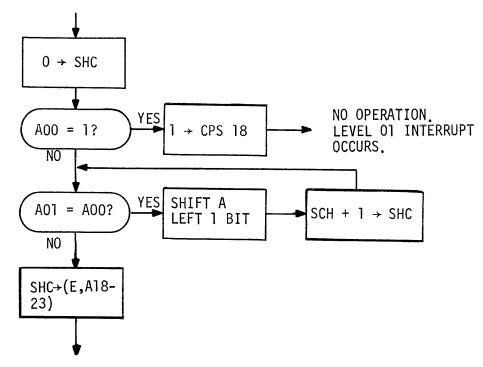

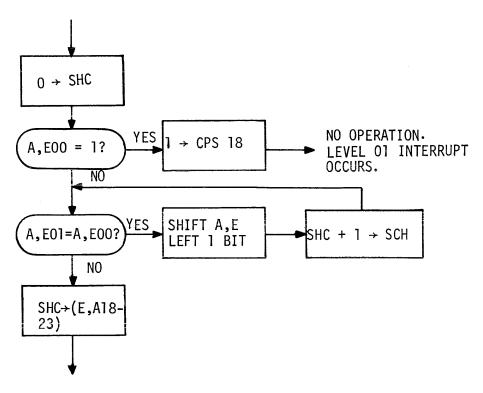

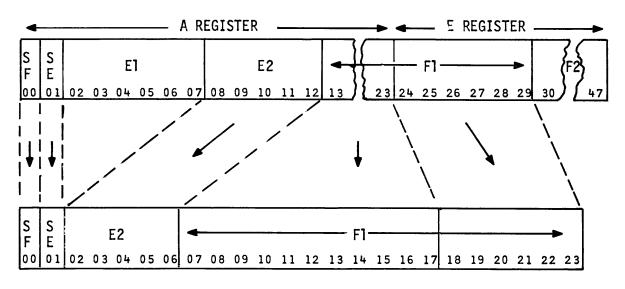

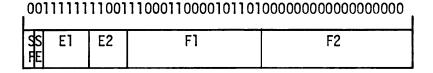

During instruction execution, SHC, used as a counter, performs the following functions:

- a. Counts the number of bit positions shifted during the execution of Shift, Rotate, Bit, and Byte instructions.

- b. Counts the number of words handled during execution of the Move Multiple instruction.

- c. Controls the execution of arithmetic or logic operations that shift data in the A or E registers (the only addressable registers capable of shifting data).

- d. Times bus exchanges during execution of the Programmed IO instruction to detect any abnormal delay.

Effective Address Register (EA Register, Not Addressable, 15 Bits) - The effective address register is the result register for the address adder, and supplies the address lines to the memory module for all memory access by the processor. Comparators in the fence and address stop logic check the output of the EA. The contents may be transferred between EA and PC directly, or through the central processor bus (CPB). At the end of each instruction execution,  $PC \rightarrow EA$  (direct transfer) provides the memory

module with the address for the next instruction. In the execution of a branch operation,  $EA \rightarrow CPB \rightarrow PC$  provides the starting point for a new sequence of instructions. (The branch address remains in the EA, as well, supplying memory with the address for the first instruction in the new sequence.)

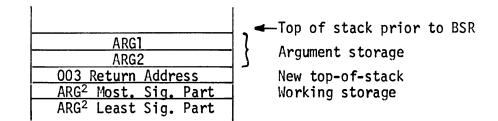

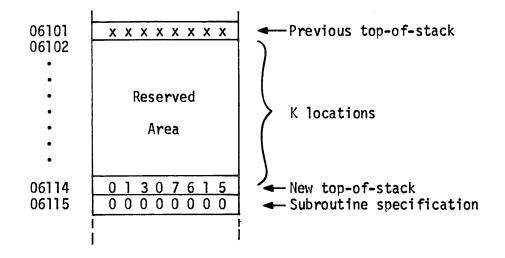

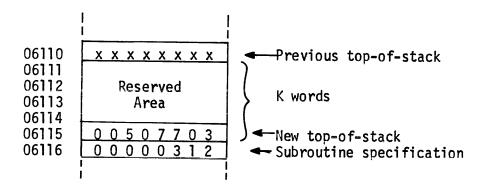

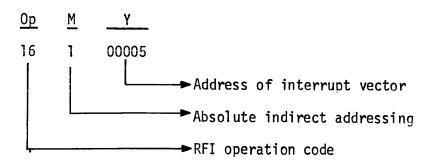

<u>Program Counter (PC Register, 77770, 15 Bits)</u> - The PC register controls the sequence in which instructions are fetched from memory. At the end of each address modification state, the PC is incremented by one. During each execution state, the PC retains the address of the next instruction word. PC is used as a base register for effective address computation when the value of the instruction mode field is 4.