# M243XL

# Magnetic Tape Subsystem Formatter Theory of Operation

|                                                                                                                | REVISION RECORD |                                                                                         |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|

| Edition                                                                                                        | Date published  | Revised contents                                                                        |  |  |  |  |  |

| 01                                                                                                             | Dec., 1982      |                                                                                         |  |  |  |  |  |

| 02                                                                                                             | Feb., 1985      | Pages i~v, 1-1, 1-2, 3-11, 4-2, 4-3, 4-23, 4-94, 4-95, 4-97, 4-98, 4-137, 5-17, 7-1~7-6 |  |  |  |  |  |

| 0 2 A                                                                                                          | Deć 1985        | Edit all pages                                                                          |  |  |  |  |  |

| Maria de la companya |                 |                                                                                         |  |  |  |  |  |

|                                                                                                                |                 |                                                                                         |  |  |  |  |  |

|                                                                                                                |                 |                                                                                         |  |  |  |  |  |

| ÷                                                                                                              |                 |                                                                                         |  |  |  |  |  |

|                                                                                                                |                 |                                                                                         |  |  |  |  |  |

|                                                                                                                |                 |                                                                                         |  |  |  |  |  |

|                                                                                                                |                 |                                                                                         |  |  |  |  |  |

|                                                                                                                | Specification   | No.: B03P-5280-0360A                                                                    |  |  |  |  |  |

Comments concerning this manual to one of the following addresses:

FUJITSU LIMITED

International Marketing

Marunouchi 1-6-1, Chiyoda-ku, Tokyo 100 JAPAN

TEL:

03-216-3211

03-214-7174, 03-216-9353 FAX:

J22833 TLX:

Cable:

"FUJITSULIMITED LIMITED"

FUJITSU AMERICA INC.

3055 Orchard Drive, San Jose, California 95134-2017, U.S.A.

TEL: FAX:

408-946-8777 408-945-1318 230-176207

TLX: TWX:

**FUJITSU EUROPE LIMITED**

TEL:

FAX: TLX:

1-629-9826

1-408-0043

FAX:

910-338-2193

54 Jermyn Street, London SW1Y 6NQ, ENGLAND

263871 FT ERP G

FUJITSU ELECTRONIK GmbH

Sonnen Straße 29, D-8000 München 2, F.R. GERMANY

TEL: FAX: 89-592891 ~ 4 89-592895

TLX:

41-521-3994

FUJITSU NORDIC AB

Kungsgaton 44, 111 35 Stockholm, SWEDEN

TEL:

8-231125 8-106865

TLX:

54-13411

FUJITSU ITALIA S.p.A.

Via Lazzaroni, 4, 20124 Milano, ITALIA

TEL: 2-607-3601 2-688-6637

TLX:

350142 FJITLY I

FUJITSU AUSTRALIA LIMITED

41 McLaren Street, North Sydney, N.S.W. 2060, AUSTRALIA

TEL: FAX: 2-922-1822 2-922-2653

TLX:

54-13411

The contents of this manual is subject to change without prior notice.

All Rights Reserved, Copyright ● 1983, 1985 FUJITSU LIMITED

# LIST OF EFFECTIVE PAGES

| PAGE               | REV  | PAGE         | REV | PAGE         | REV | PAGE           | REV      | PAGE         | REV      | PAGE     | REV      |

|--------------------|------|--------------|-----|--------------|-----|----------------|----------|--------------|----------|----------|----------|

| COVER              | 02A  | 4-12         | 01  | 4-55         | 01A | 4-98           | 02A      | 4-141        | 01A      | 5-30     | 01       |

| BLANK              |      | 4-13         | 01  | 4-56         | 01A | 4-99           | 01A      | 4-142        | 01       | 5-31     | 01A      |

| i                  | 02A  | 4-14         | 01A | 4-57         | 01A | 4-100          | 01A      | 4-143        | 01       | 5-32     | 01       |

| BLANK              |      | 4-15         | 01A | 4-58         | 01A | 4-101          | 01A      | 4-144        | 01       | 5-33     | 01A      |

| iii                | 02A  | 4-16         | 01A | 4-59         | 01  | 4-102          | 01A      | 4-145        | 01A      | 5-34     | 01A      |

| BLANK              |      | 4-17         | 01  | 4-60         | 01A | 4-103          | 01       | 4-146        | 01A      | 6-1      | 01A      |

| ٧                  | 02A  | 4-18         | 01A | 4-61         | 01A | 4-104          | 01       | 4-147        | 01A      | BLANK    |          |

| vi                 | 02.  | 4-19         | 01A | 4-62         | 01A | 4-105          | 01A      | 4-148        | 01       | 7-1      | 02A      |

| vii                | 02A  | 4-20         | 01A | 4-63         | 01A | 4-106          | 01       | 4-149        | 01A      | 7-2      | 02A      |

| BLANK              |      | 4-21         | 01A | 4-64         | 01A | 4-107          | 01       | 4-150        | 01A      | 7-3      | 02A      |

| 1-1                | 02A  | 4-22         | 01A | 4-65         | 01A | 4-108          | 01       | 4-151        | 01A      | 7-4      | 02A      |

| 1-2                | 02A  | 4-23         | 02A | 4-66         | 01A | 4-109          | 01       | 4-152        | 01       | 7-5      | 02A      |

| 1-3                | 01A  | 4-24         | 01  | 4-67         | 01A | 4-110          | 01       | 4-153        | 01       | 7-6      | 02A      |

| BLANK              |      | 4-25         | 01A | 4-68         | 01A | 4-111          | 01A      | BLANK        |          |          |          |

| 2-1                | 01A  | 4-26         | 01A | 4-69         | 01A | 4-112          | 01       | 5-1          | 01A      |          |          |

| 2-2                | 01 A | 4-27         | 01A | 4-70         | 01A | 4-113          | 01A      | 5-2          | 01       |          |          |

| 2-3                | 01A  | 4-28         | 01  | 4-71         | 01  | 4-114          | 01       | 5-3          | 01A      | 1        |          |

| 2-4                | 01A  | 4-29         | 01  | 4-72         | 01A | 4-115          | 01       | 5-4          | 01       |          |          |

| 2-5                | 01   | 4-30         | 01A | 4-73         | 01A | 4-116          | 01A      | 5-5          | 01A      |          |          |

| 2-6                | 01A  | 4-31         | 01A | 4-74         | 01A | 4-117          | 01       | 5-6          | 01A      | ŀ        |          |

| 2-7                | 01   | 4-32         | 01A | 4-75         | 01A | 4-118          | 01A      | 5-7          | 01A      |          |          |

| 2-8                | 01   | 4-33         | 01A | 4-76         | 01A | 4-119          | 01A      | 5-8          | 01A      |          |          |

| 3-1                | 01   | 4-34         | 01A | 4-77         | 01A | 4-120          | 01A      | 5-9          | 01A      |          |          |

| 3-2                | 01A  | 4-35         | 01A | 4-78         | 01A | 4-121          | 01A      | 5-10         | 01A      |          |          |

| 3-3                | 01A  | 4-36         | 01  | 4-79         | 01A | 4-122          | 01       | 5-11         | 01A      |          |          |

| 3-4                | 01A  | 4-37         | 01  | 4-80         | 01A | 4-123          | 01A      | 5-12         | 01A      |          |          |

| 3-5                | 01   | 4-38         | 01  | 4-81         | 01A | 4-124          | 01       | 5-13         | 01A      |          |          |

| 3-6                | 01   | 4-39         | 01  | 4-82         | 01A | 4-125          | 01A      | 5-14         | 01A      |          |          |

| 3-7                | 01A  | 4-40         | 01  | 4-83         | 01A | 4-126          | 01A      | 5-15         | 01A      |          |          |

| 3-8                | 01A  | 4-41         | 01  | 4-84         | 01A | 4-127          | 01       | 5-16         | 01A      |          |          |

| 3-9                | 01   | 4-42         | 01A | 4-85         | 01A | 4-128          | 01A      | 5-17         | 02A      |          |          |

| 3-10               | 01   | 4-43         | 01A | 4-86         | 01A | 4-129          | 01A      | 5-18         | 01A      |          |          |

| 3-11               | 02A  | 4-44         | 01A | 4-87         | 01A | 4-130          | 01       | 5-19         | 01A      |          |          |

| BLANK              |      | 4-45         | 01A | 4-88         | 01A | 4-131          | 01A      | 5-20         | 01A      |          |          |

| 4-1                | 01A  | 4-46         | 01A | 4-89         | 01A | 4-132          | 01A      | 5-21         | 01       |          |          |

| 4-2                | 02A  | 4-47         | 01A | 4-90         | 01A | 4-133          | 01A      | 5-22         | 01A      |          |          |

| 4-3                | 02A  | 4-48         | 01A | 4-91         | 01A | 4-134          | 01A      | 5-23         | 01       |          |          |

| 4-4                | 01A  | 4-49         | 01A | 4-92         | 01A | 4-135          | 01A      | 5-24         | 01A      |          |          |

| 4-5                | 01A  | 4-50<br>4-51 | 01A | 4-93<br>4-94 | 01A | 4-136<br>4-137 | 01       | 5-25<br>5-26 | 01A      | 1        |          |

| 4-6<br>4-7         | 01A  | 4-51<br>4-52 | 01A | 4-94         | 02A | 4-137          | 02A      | 5-20         | 01A      |          |          |

| 4- <i>7</i><br>4-8 | 01A  | 1            | 01A | 4-95<br>4-96 | 02A | 4-138          | 01A      | 5-27         | 01A      | 1        | 1        |

| 4-8<br>4-9         | 01A  | 4-53         | 01A | 4-96<br>4-97 | 01A | 4-139          | 01A      | 5-28         | 01       | 1        | 1        |

| 4-9<br>4-10        | 01A  | 4-54         | 01A | 4-3/         | 02  | 4-140          | 01       | 3-23         | 01A      | 1        | 1        |

| 4-10               | 01A  |              | }   |              |     |                |          |              |          | J        | 1        |

| 7-11               | 01A  |              |     |              |     |                | <u> </u> | <u></u>      | <u> </u> | <u> </u> | <u> </u> |

# CONTENTS

|                                      | Page       |

|--------------------------------------|------------|

| CHAPTER 1 INTRODUCTION               | 1-1        |

| 1.1 Functions                        | 1-1        |

| 1.2 Unit Types                       | 1-1        |

| 1.3 Characteristics                  | 1-2        |

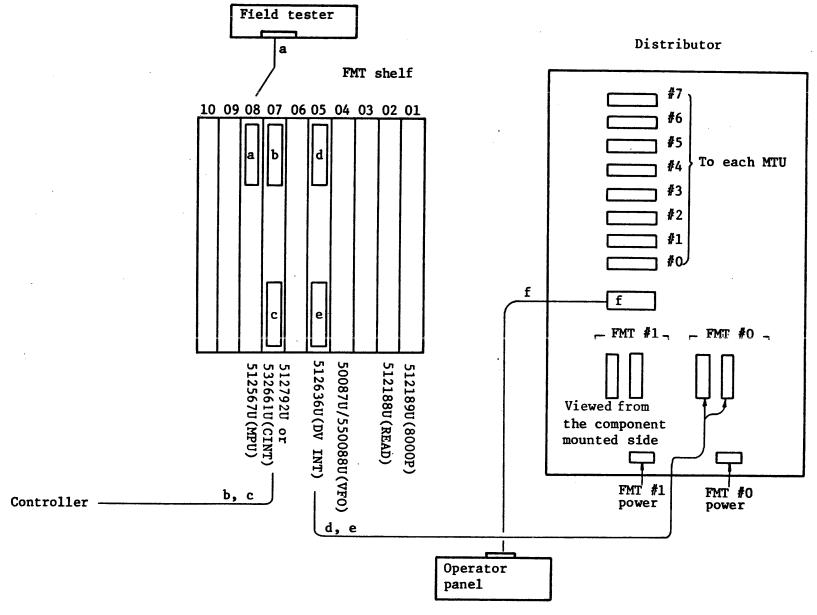

| 1.4 Configuration                    | 1-3        |

| 1.4 Configuration                    | 1-3        |

| CHAPTER 2 COMMAND OPERATION          | 2-1        |

| 2.1 Outline                          | 2-1        |

| 2.2 Commands                         | 2-1        |

| 2.3 Drive Status Bytes               | 2-6        |

| 2.5 Dilve beacus byces               | 2 0        |

| CHAPTER 3 INTERFACE DESCRIPTION      | 3-1        |

| 3.1 Controller/Formatter Interface   | 3-1        |

| 3.1.1 Signal lines                   | 3-1        |

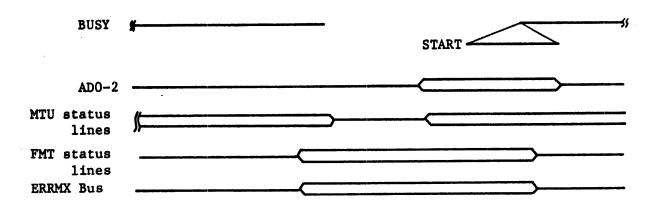

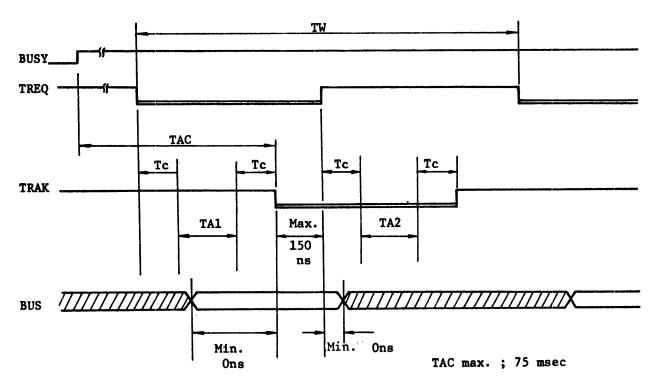

| 3.1.2 Interface sequence             | 3-1        |

| 3.2 FMT-MTU Interface                | 3-7        |

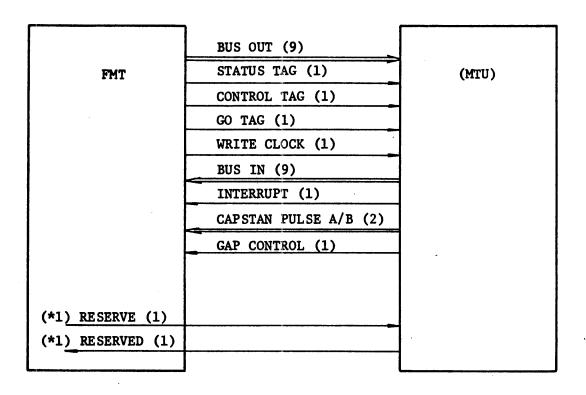

| 3.2.1 Interface signal lines         | 3-7        |

| 5.2.1 Interface signal lines         | 3-7        |

| CHAPTER 4 FUNCTIONAL DESCRIPTION     | 4-1        |

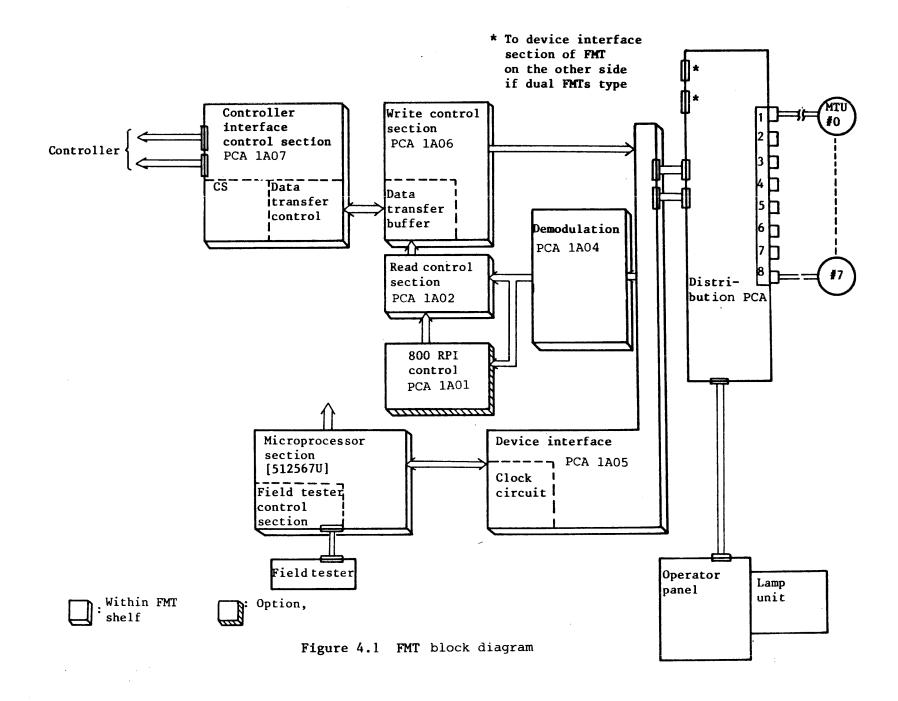

| 4.1 Outline                          | 4-1        |

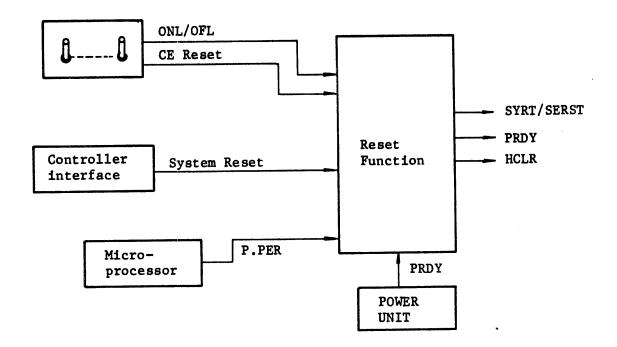

| 4.2 Reset System                     | 4-4        |

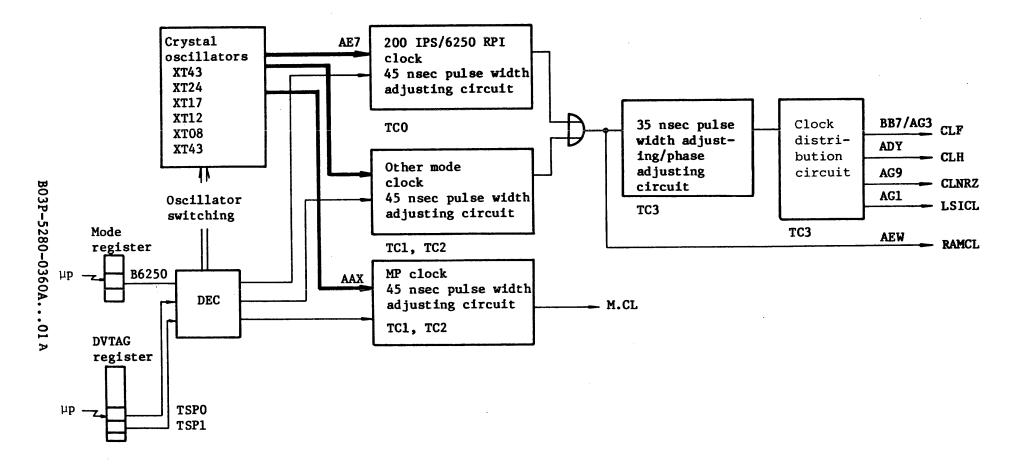

| 4.3 Clock System                     | 4-5        |

| 4.4 Microprocessor                   | 4-3<br>4-8 |

|                                      | 4-8        |

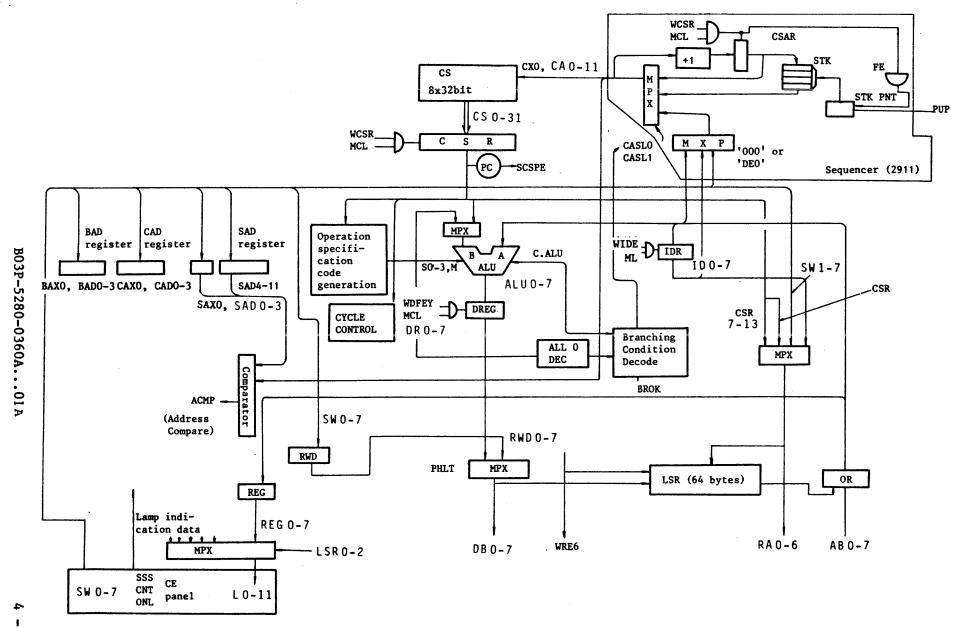

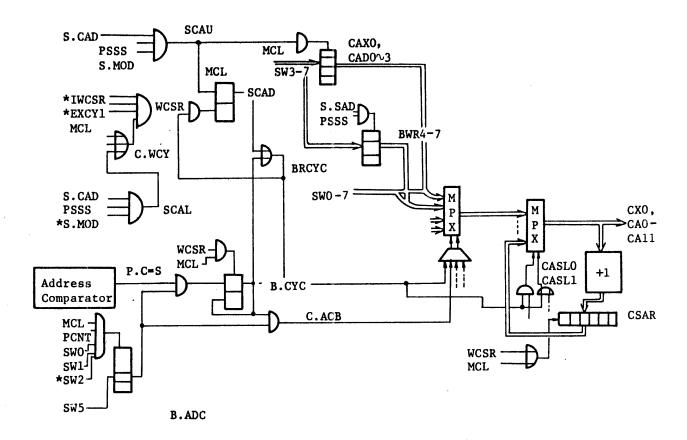

| 4.4.1 Microprocessor configuration   |            |

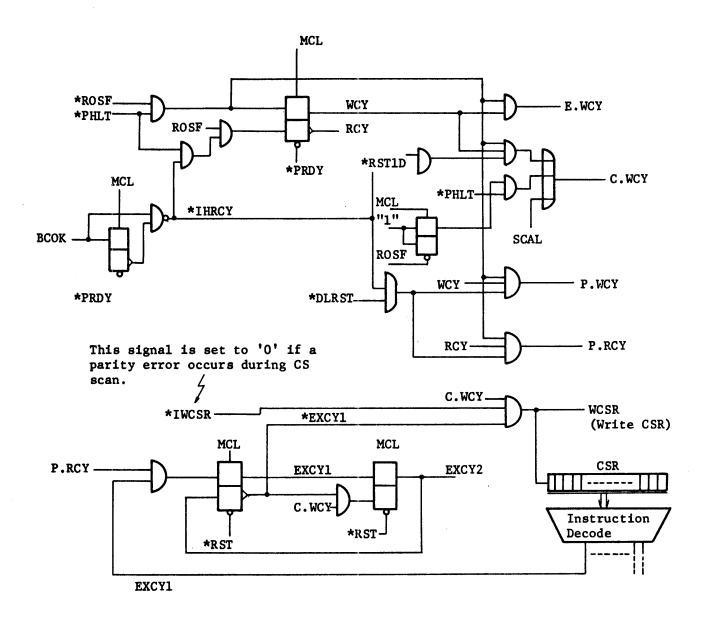

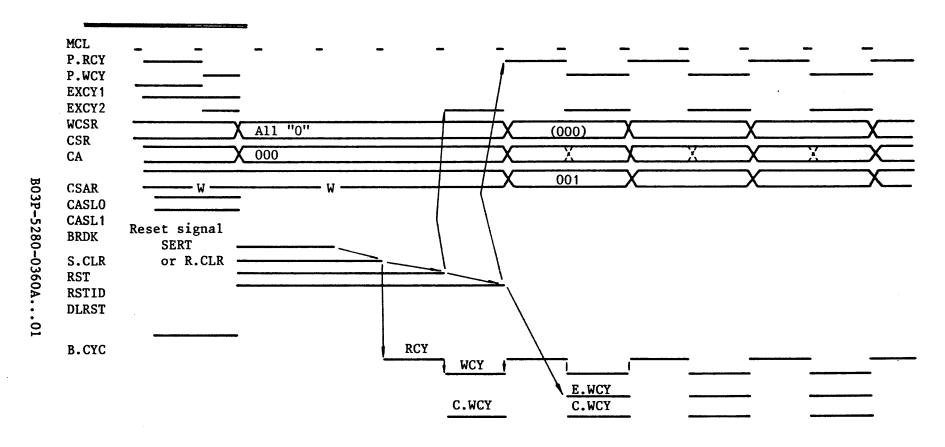

| 4.4.2 Processor cycle control        | 4-10       |

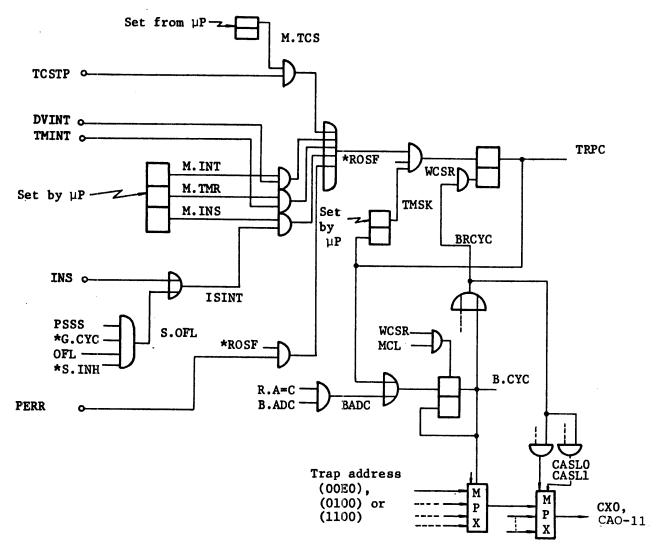

| 4.4.3 Interrupt (Trap)               | 4-14       |

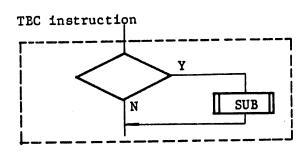

| 4.4.4 Field tester controller        | 4-16       |

| 4.4.5 Micro program instructions     | 4-22       |

| 4.5 Registers                        | 4-42       |

| 4.5.1 LSR                            | 4-43       |

| 4.5.2 EXR                            | 4-46       |

| 4.6 Controller Interface Control     | 4-96       |

| 4.6.1 Command initiation             | 4-96       |

| 4.6.2 Formatter status lines         | 4-99       |

| 4.6.3 Error multiplex bus lines      | 4-100      |

| 4.6.4 TU status lines                | 4-102      |

| 4.7 Data Transfer Control            | 4-104      |

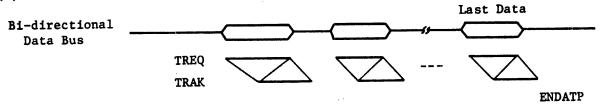

| 4.7.1 Write end LWR command          | 4-105      |

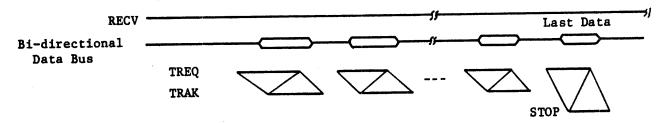

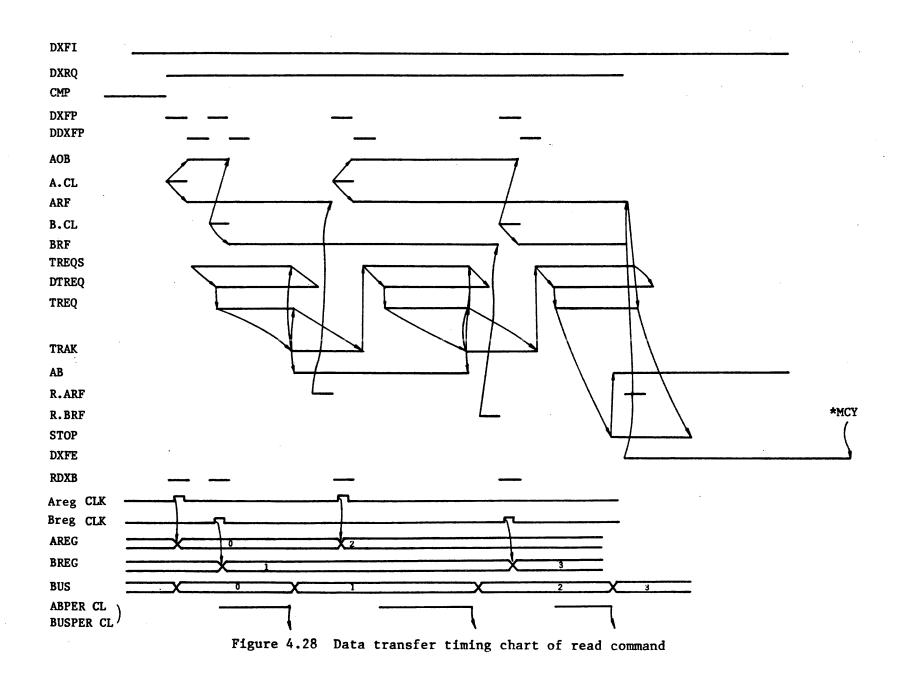

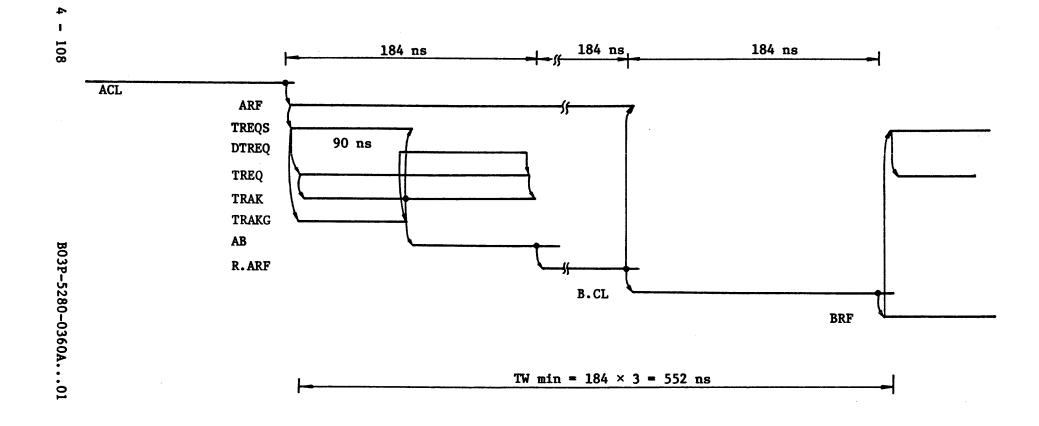

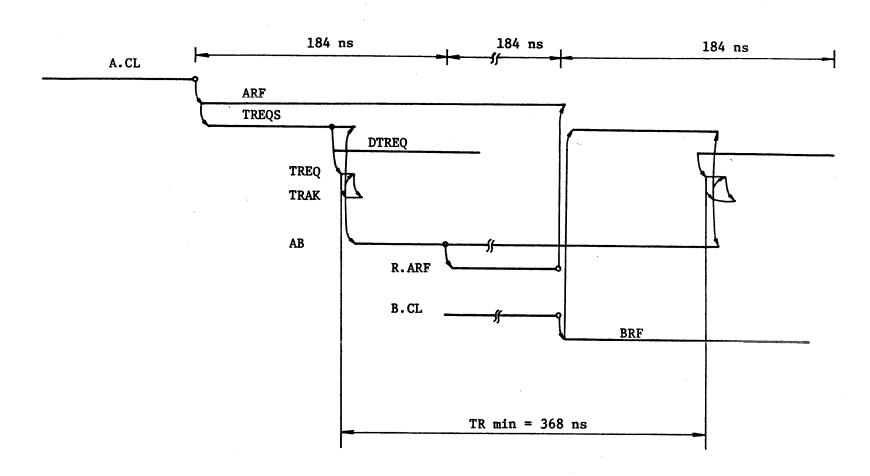

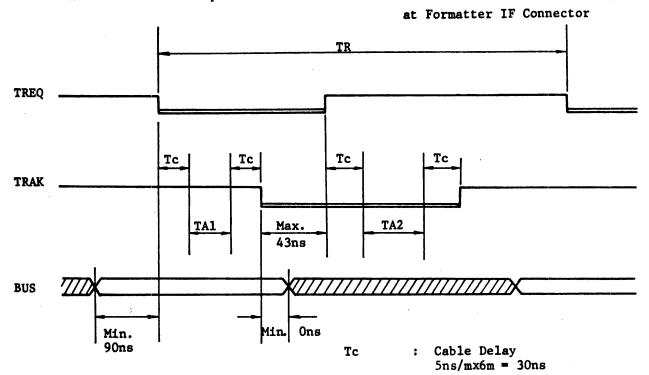

| 4.7.2 Read and read backward command | 4-105      |

| 4.8 Write Control                    | 4-111      |

| 4.8.1 Format/Deformat clock          | 4-111      |

| 4.8.2 Start write operation          | 4-113      |

| 4.8.3 Format control                 | 4-113      |

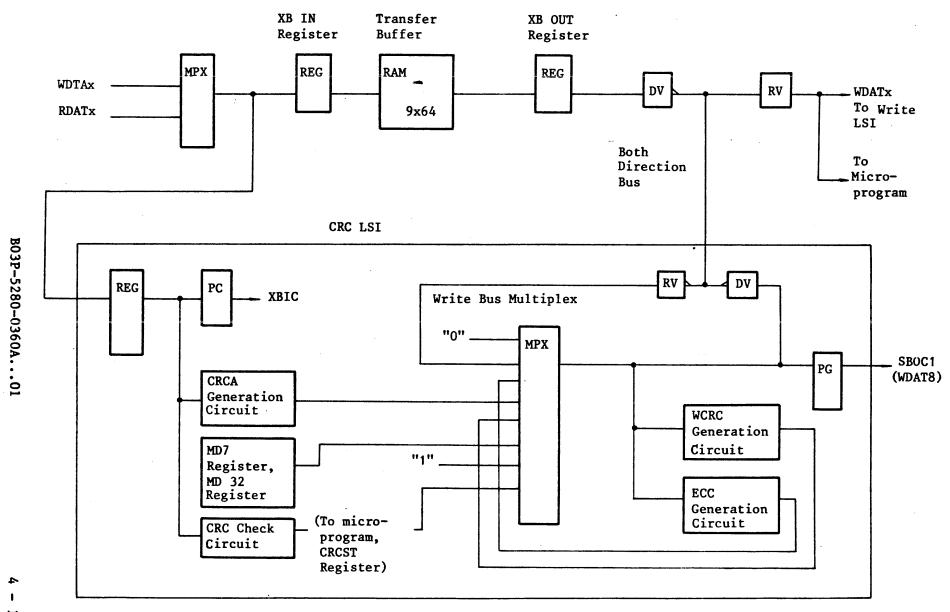

| 4.8.4 Data bus                       | 4-116      |

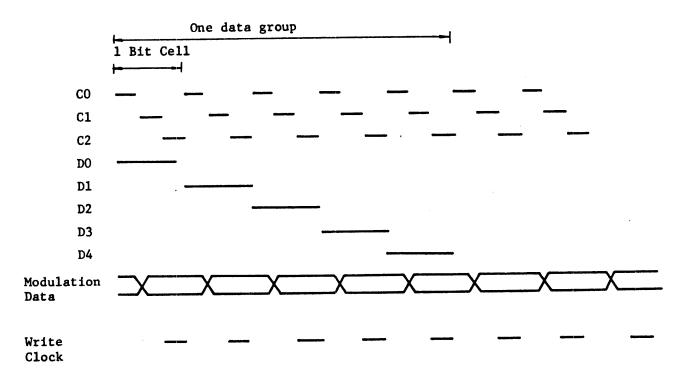

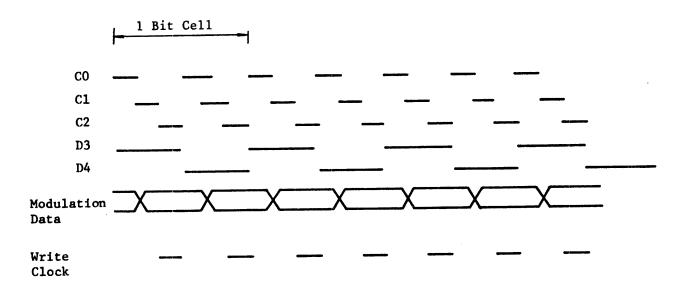

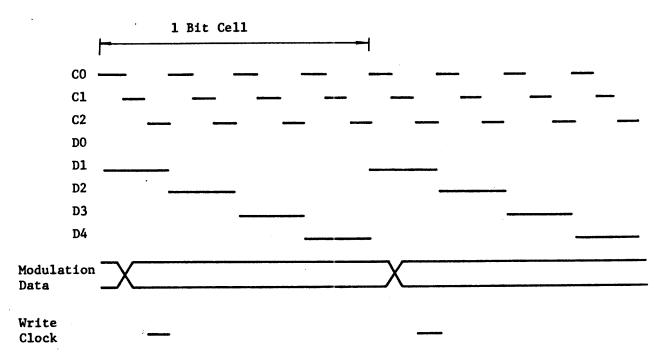

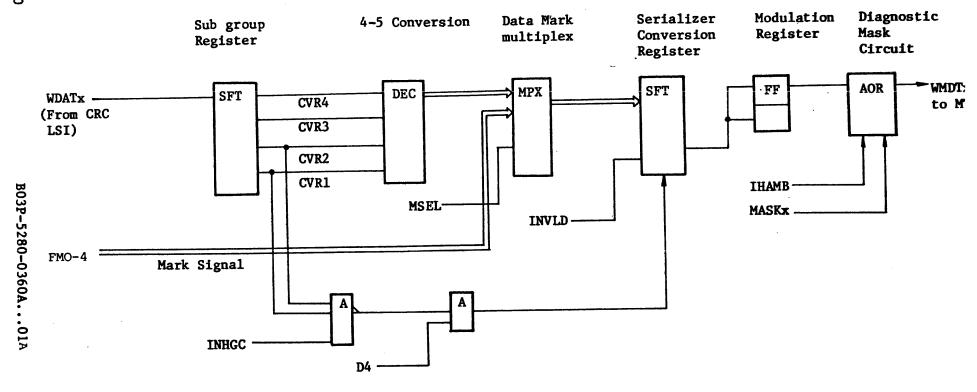

| 4.8.5 Write modulation circuit       | 4-118      |

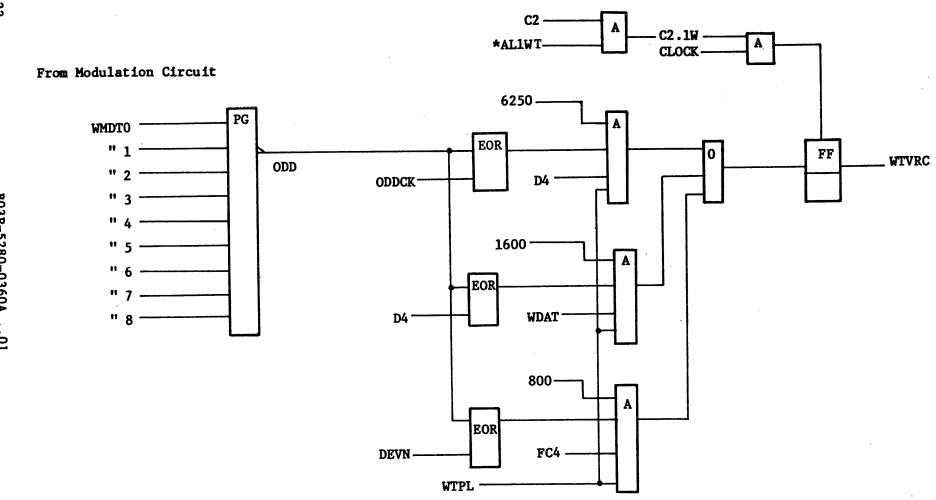

| 4.8.6 Write VRC check                | 4-121      |

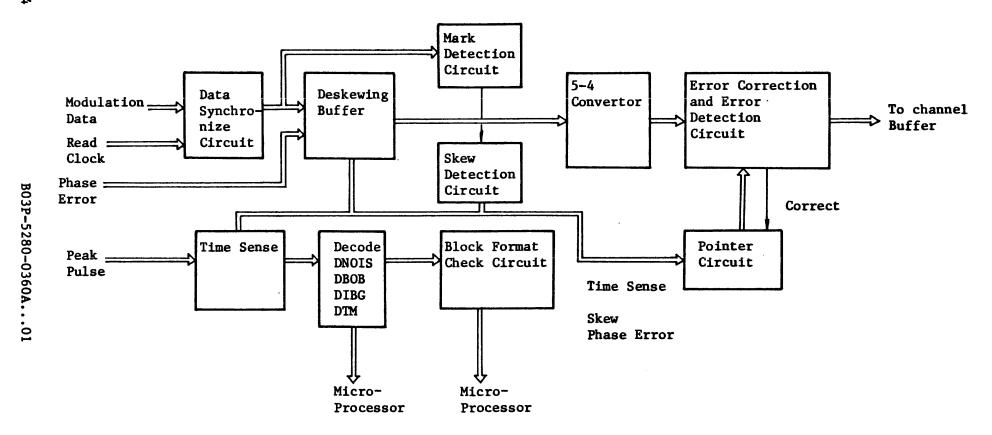

| 4.9 Read Control                     | 4-123      |

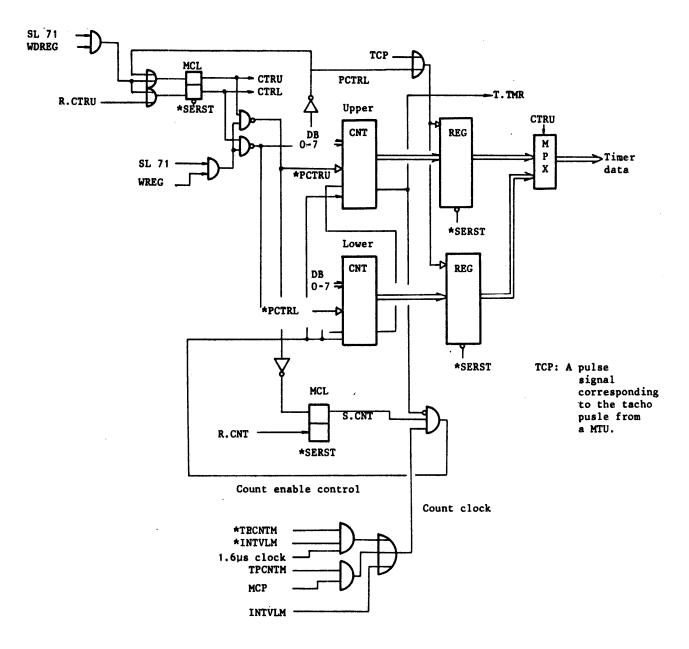

| 4.9.1 Time sense                     | 4-125      |

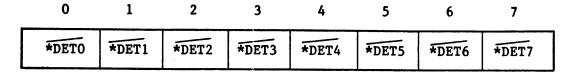

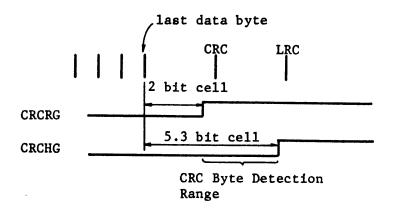

| 4.9.2 Block format check             | 4-125      |

| 4.9.3 Basic read timing              | 4-128      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-131      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.9.5 Skew control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-131      |

| 4.9.6 Error correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-132      |

| 4.9.7 Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-134      |

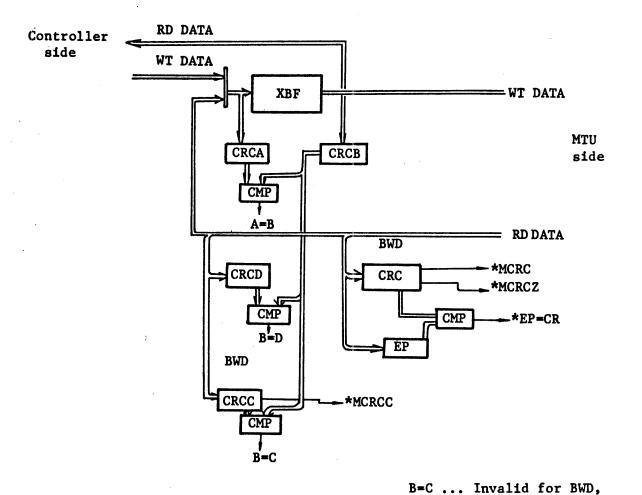

| 4.9.8 Data flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-135      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-137      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-138      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-141      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-141      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-145      |

| ··                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-146      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-146      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-147      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-150      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-150      |

| •••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-153      |

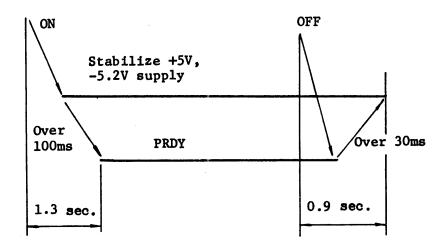

| 4.13.3 Power ready signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-153      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| CHAPTER 5 MICROPROGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-1        |

| 5.1 Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-1        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-3        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-3        |

| • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-5        |

| * * * * =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-5        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-8        |

| •••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-8        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-8        |

| ••• •••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-0<br>5-9 |

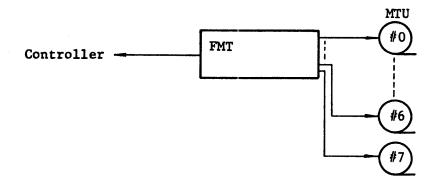

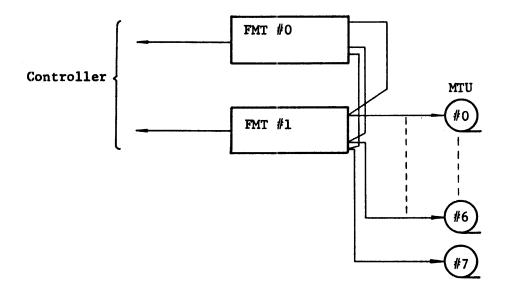

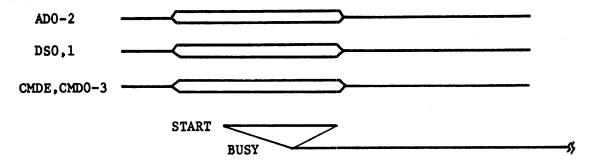

| 5.7 Machine Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |