# SLAVE EMULATOR HARDWARE REFERENCE MANUAL

2302-5003-01

ADVANCE ADVANCE TRUMENTAL INSTRUMENTAL

# SLAVE EMULATOR HARDWARE REFERENCE MANUAL

# 2302-5003-01

October 1982

Kontron Electronics, Inc. 5730 Buckingham Parkway Culver City, CA 90230

# REVISION HISTORY

| <u>Title</u>                                | Number    | Date  | Notes       |

|---------------------------------------------|-----------|-------|-------------|

| Slave Emulator Hardware<br>Reference Manual | 2302-5003 | 10/82 | 2nd Edition |

|                                             |           |       |             |

| RELATED PUBLICATIONS                        |           |       |             |

| ADS Installation And Maintenance            | 2300-5003 |       |             |

| Floppy Disk Drives                          | 2300-5007 |       |             |

| EPROM Programmer                            | 2300-5035 |       |             |

| Slave Logic Analyzer                        | 2302-5012 |       |             |

| Slave Emulator Reference Manual             | 2302-5000 |       |             |

Copyright 1982 by Kontron

# CORRECTION

In our current system configuration, the Kontron Logic Analyzer (KLA) unit or the Kontron Development System (KDS) unit replaces the ADS console as the host unit. The Kontron Slave Emulator (KSE) replaces the Slave Emulator.

Figures 1-1 and 1-3 of this document still show the older ADS console, and the Slave Emulator chassis. These illustrations will be updated in the next revision of this manual. Until then, please substitute the new equipment designations for the old names. The informational content of the illustrations is otherwise accurate.

# PREFACE

The scope of this manual is limited to the basic Slave Emulator. Microprocessor specific systems are defined in the <u>Supplements</u> to this manual.

Chapter 1, Introduction, describes the Emulator Control Unit hardware and specifications.

Chapter 2, Emulator Setup And Checkout, describes preliminary checks, system interconnections, and limited Emulator Control Unit system test.

Chapter 3, <u>Maintenance</u>, characterizes preventive maintenance, troubleshooting information, and disassembly instructions. Diagrams and supporting data are included.

Chapter 4, Theory Of Operation, narrates the function of Emulator boards such as the interface processor, breakpoint, and memory boards.

Please note that a **Documentation Reply Card** is inserted at the back of this manual. When you complete and return it, you help us produce better documentation for you.

A User Registration Card is included in the set of manuals you receive with your Kontron system. When you complete and return the User Registration Card, you ensure that you will receive all updates and new information for your configuration.

## WARNING

This equipment generates, uses and can radiate radio frequency energy. If not installed and used in accordance with this instruction manual, it may cause interference to radio communications. As temporarily permitted by regulation, it has not been tested for compliance with the limits for Class A computing devices pursuant to Subpart J of Part 15 of the FCC rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference, in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

# CONTENTS

# CHAPTER 1 - INTRODUCTION

| 1.1 | PURPOSE AND SCOPE                               | 1-1  |

|-----|-------------------------------------------------|------|

| 1.2 | OVERVIEW                                        | 1-1  |

|     | 1.2.1 Slave Vs Traditional In-Circuit Emulation | 1-1  |

|     | 1.2.2 Emulation Objectives                      | 1-1  |

|     | 1.2.3 Target System Substitution                | 1-2  |

|     | 1.2.4 The Emulation System                      | 1-2  |

| 1.3 | HARDWARE DESCRIPTION                            | 1-2  |

|     | 1.3.1 Emulator Cabinet                          | 1-2  |

|     | 1.3.2 Emulator Probe                            | 1-2  |

|     | 1.3.3 Emulator Boards                           | 1-4  |

|     | 1.3.4 External Probe                            | 1-4  |

|     | 1.3.5 Internal Emulator Cabling                 | 1-6  |

| 1.4 | SPECIFICATIONS                                  | 1-8  |

|     | 1.4.1 Emulator Cabinet                          | 1-8  |

|     | 1.4.2 External Probe                            | 1-9  |

|     | 1.4.3 Performance Prologue                      | 1-10 |

# CHAPTER 2 - INSTALLATION AND CHECKOUT

| 2.1 | INSTALLATION DOCUMENTS                    | 2-1              |

|-----|-------------------------------------------|------------------|

| 2.2 | INSPECTING AND SETTING UP THE SYSTEM      | 2-1              |

| 2.3 | CONFIGURATION REQUIREMENTS                | 2-2              |

|     | 2.3.1 ADS Configuration                   | 2-2              |

|     | 2.3.2 Emulator Configuration Requirements | 2-2              |

| 2.4 | SYSTEM INTERCONNECTIONS                   | 2-2              |

| 2.5 | GETTING STARTED                           | 2-4              |

|     | 2.5.1 Conventions                         | 2-4              |

|     | 2.5.2 Powering Up The System              | 2-4              |

|     | 2.5.3 Initializing The Emulator           | 2 <del>-</del> 5 |

|     | 2.5.4 Switch Emulator                     | 2-7              |

|     | 2.5.5 Debugger Commands                   | 2-9              |

| 2.6 | EXTERNAL PROBE FUNCTIONAL DESCRIPTION     | 2-16             |

|     |                                           |                  |

PAGE

# CHAPTER 3 - MAINTENANCE

| 3.1 | SYSTEM MAINTENANCE AND TROUBLESHOOTING | 3-1 |

|-----|----------------------------------------|-----|

|     | 3.1.1 Emulator Malfunctions            | 3-1 |

|     | 3.1.2 Floppy Disk Unit Malfunctions    | 3-2 |

|     | 3.1.3 ADS Malfunctions                 | 3-2 |

| 3.2 | EMULATOR TROUBLESHOOTING CHARTS        | 3-2 |

| 3.3 | DISASSEMBLY INSTRUCTIONS               | 3-5 |

|     | 3.3.1 Rear Panel Removal               | 3-6 |

|     | 3.3.2 Board Removal                    | 3-7 |

|     | 3.3.3 Enclosure Cover Removal          | 3-8 |

|     | 3.3.4 Front Panel/Power Supply Removal | 3-9 |

# CHAPTER 4 - THEORY OF OPERATION

| 4.1 | SCOPE                                         | 4-1  |

|-----|-----------------------------------------------|------|

| 4.2 | GENERAL DESCRIPTION                           | 4-1  |

| 4.3 | SUBSTITUTING THE EMULATION PROCESSOR FOR THE  |      |

|     | TARGET SYSTEM'S PROCESSOR                     | 4-2  |

| 4.4 | MONITORING THE EMULATION PROCESSOR            | 4-2  |

|     | 4.4.1 Logic Analyzer Board                    | 4-2  |

|     | 4.4.2 Breakpoint Board                        | 4-3  |

|     | 4.4.3 Emulator Personality Board              | 4-3  |

|     | 4.4.4 Simulation Memory                       | 4-3  |

| 4.5 | CONTROLLING THE EMULATION PROCESSOR           | 4-3  |

|     | 4.5.1 Emulator Personality Board              | 4-4  |

|     | 4.5.2 Interface Processor Board               | 4-4  |

| 4.6 | EMULATION TECHNIQUES                          | 4-5  |

|     | 4.6.1 Initialization                          | 4-5  |

|     | 4.6.2 The Execute Command                     | 4-5  |

|     | 4.6.3 The Halt Command                        | 4-6  |

|     | 4.6.4 Storing Data and Screen Updating        | 4-6  |

|     | 4.6.5 Single Step                             | 4-7  |

|     | 4.6.6 Memory Mapping                          | 4-7  |

|     | 4.6.7 External Control Lines                  | 4-9  |

|     | 4.6.8 Breakpoints                             | 4-10 |

| 4.7 | BACKPLANE CONNECTIONS TO THE EMULATOR BUS     | 4-10 |

| 4.8 | INTERFACE PROCESSOR BOARD                     | 4-14 |

|     | 4.8.1 Z80 Processor                           | 4-14 |

|     | 4.8.2 Bus Interface Unit                      | 4-14 |

|     | 4.8.3 Emulator Bus Addressing for IP Accesses | 4-15 |

|     | 4.8.4 Emulator Bus Arbitration                | 4-16 |

|     | 4.8.5 Bus Fault Timer                         | 4-17 |

|     | 4.8.6 Direct IP Access To Simulation Memory   | 4-17 |

|     | 4.8.7 Memory Mappers                          | 4-19 |

|     |                                               |      |

|         |         | 4.8.8 Dynamic RAM Refresh                                | 4-19  |

|---------|---------|----------------------------------------------------------|-------|

|         |         | 4.8.9 PROMS                                              | 4-20  |

|         |         | 4.8.10 I/O Lines                                         | 4-20  |

|         |         | 4.8.11 Serial Ports                                      | 4-21  |

|         |         | 4.8.12 System Interrupts                                 | 4-21  |

|         |         | 4.8.13 System Address Latches                            | 4-21  |

|         |         | 4.8.14 PIO Latches                                       | 4-22  |

|         |         | 4.8.15 Backplane Address Bits                            | 4-22  |

|         | 4.9     | EXTERNAL PROBE                                           | 4-22  |

|         | 4.10    | BREAKPOINT BOARD                                         | 4-25  |

|         |         | 4.10.1 General Description                               | 4-25  |

|         |         | 4.10.2 Registers And Ports                               | 4-26  |

|         |         | 4.10.3 System Addresses                                  | 4-28  |

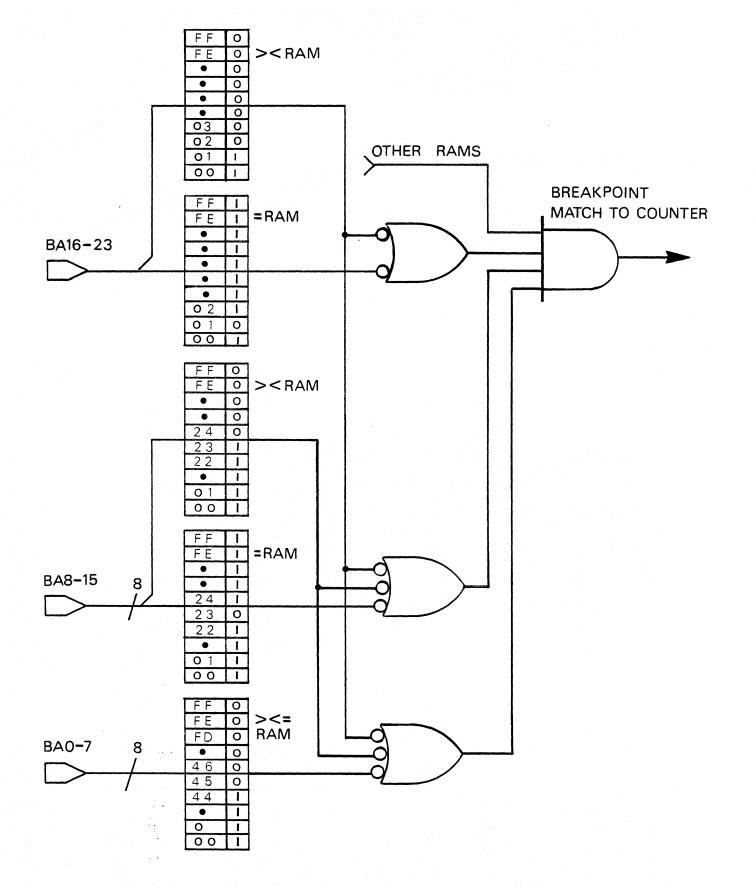

|         |         | 4.10.4 Operation of Breakpoint RAMs                      | 4-30  |

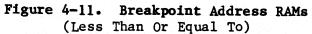

|         |         | 4.10.5 Breakpoint Counters                               | 4-33  |

|         |         | 4.10.6 Breakpoint Mode Register                          | 4-33  |

|         |         | 4.10.7 Interface Processor Breakpoint Interrupt          | 4-35  |

|         | 4.11    | LOGIC ANALYZER                                           | 4-36  |

|         |         | 4.11.1 Logic Analyzer Operation                          | 4-37  |

|         |         | 4.11.2 External Controls                                 | 4-38  |

|         |         | 4.11.3 Logic Analyzer Initialization                     | 4-39  |

|         |         | 4.11.4 Time/Cycle Counter Operation                      | 4-39  |

|         | 4.12    | SIMULATION MEMORY                                        | 4-40  |

|         |         | 4.12.1 Block Mappers                                     | 4-41  |

|         |         | 4.12.2 Word/Byte Memory Configuration                    | 4-42  |

|         | 4.13    | DYNAMIC MEMORY                                           | 4-42  |

|         |         | 4.13.1 Block Mappers                                     | 4-42  |

|         | •       | 4.13.2 Memory Array                                      | 4-43  |

|         |         | 4.13.3 Control Logic                                     | 4-43  |

|         |         | 4.13.4 Parity Generation and Checking                    | 4-44  |

|         |         | 4.13.5 Refreshing                                        | 4-44  |

|         |         | 4.13.6 Write Protect and Internal/External Memory        |       |

|         |         | Mappers                                                  | 4-44  |

|         | 4.14    | ••                                                       | 4-45  |

|         |         | 4.14.1 Programming The Block Mappers                     | 4-45  |

|         |         | 4.14.2 Write Protect and Internal/External Memory Mapper | 4-45  |

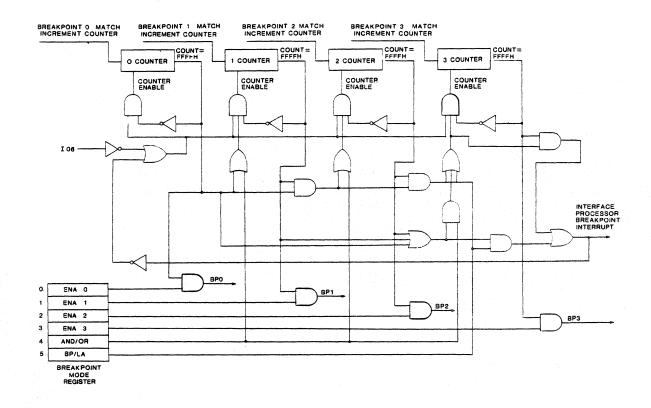

|         | 4.15    | EMULATOR PERSONALITY                                     | 4-46  |

|         |         | 4.15.1 Test Memory                                       | 4-46  |

|         |         | 4.15.2 Emulator Bus Arbitration                          | 4-46  |

|         |         | 4.15.3 Pre-Fetch Tracking                                | 4-47  |

|         |         | 4.15.4 Timing Signals                                    | 4-47  |

|         |         | 4-15.5 Mapping                                           | 4-47  |

|         | APPEND  | IX                                                       | A-1   |

|         |         |                                                          | -<br> |

|         | INDEX   |                                                          | I-1   |

|         |         |                                                          |       |

| KONTRON | SERVICE | NUMBERS                                                  |       |

# ILLUSTRATIONS

| FIGURE |                                     | PAGE |

|--------|-------------------------------------|------|

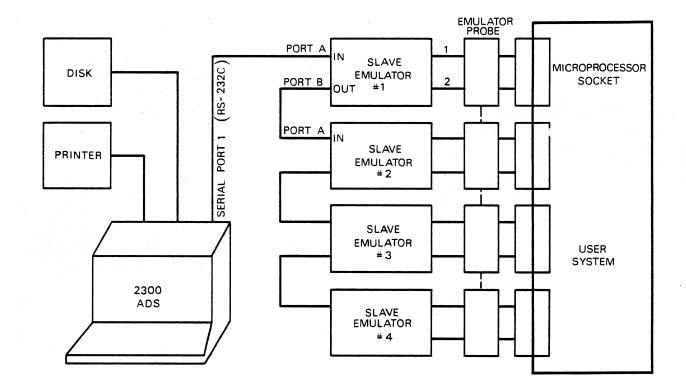

| 1-1    | Multi-Emulation Station             | 1-3  |

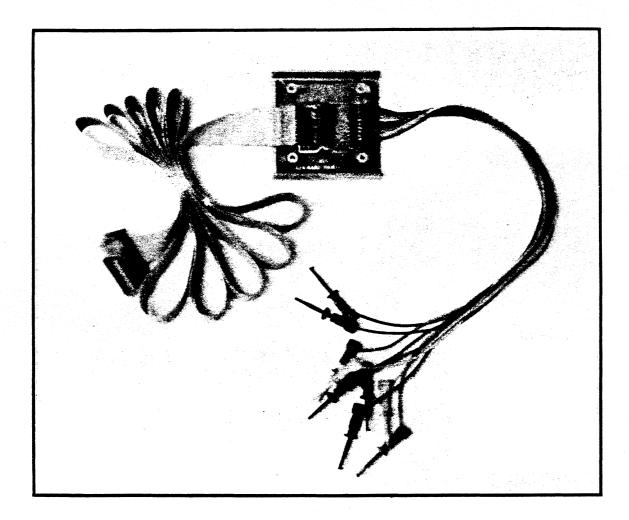

| 1-2    | External Probe                      | 1-5  |

| 1-3    | Internal Cabling                    | 1-7  |

| 1-4    | Buffer Circuit                      | 1-11 |

|        |                                     |      |

| 2-1    | System Interconnections             | 2-3  |

| 2-2    | Emulator Executive Display          | 2-6  |

| 2-3    | Enter SW1                           | 2-7  |

| 2-4    | Switch Command Display              | 2-8  |

| 2 1    | Executive Test Symptoms             | 3-3  |

| 3-1    |                                     | 3–4· |

| 3-2    | Switch Display Symptoms             | 3-5  |

| 3-3    | Exploded View<br>Rear Panel Removal | 3-6  |

| . 3-4  |                                     | 3-7  |

| 3-5    | Board Removal                       | 3-8  |

| 3-6    | Enclosure Cover Removal             | 3-0  |

| 3-7    | Front Panel Details                 | 3-3  |

|        |                                     |      |

| 4-0    | Slave Emulator Block Diagram        | 4-0  |

| 4-1    | Memory Mapping                      | 4-8  |

| 4-2    | Buffer Control                      | 4-9  |

| 4-3    | Emulator Bus                        | 4-11 |

| 4-4    | Interface Processor - BIU Timing    | 4-18 |

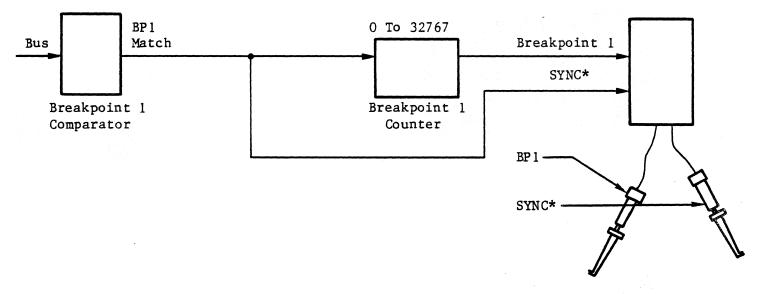

| 4-5    | SYNC*/Breakpoint 1                  | 4-23 |

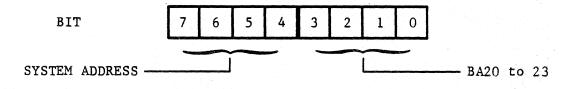

| 4-6    | System Address Register             | 4-25 |

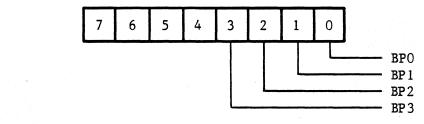

| 4-7    | Breakpoint Status Register          | 4-27 |

| 4-8    | Address And Data Lines              | 4-27 |

Ġ.

FIGURE

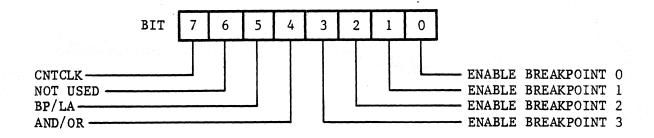

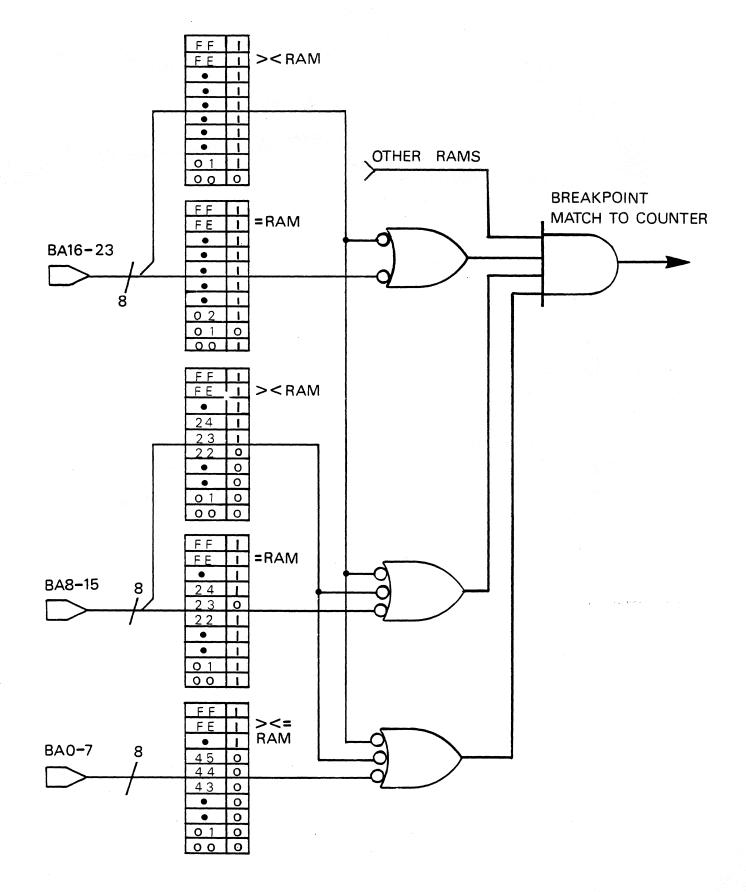

| 4-9  | Breakpoint Mode Register               | 4-29 |

|------|----------------------------------------|------|

| 4-10 | Breakpoint Address RAMs (Greater Than) | 4-31 |

| 4-11 | Breakpoint Address RAMs (Less Than)    | 4-32 |

| 4-12 | Breakpoint Control Logic               | 4-34 |

| 4-13 | Buffers/Transceivers                   | 4-48 |

# TABLES

| TABLE |                 |  | PAGE |

|-------|-----------------|--|------|

| 1-1   | Internal Cables |  | 1-6  |

| 4-1   | Buffer Control  |  | 4-43 |

# INTRODUCTION

### 1.1 PURPOSE AND SCOPE

The purpose of this manual is to acquaint the user with Kontron's Slave Emulator. Information is given on installation, checkout, maintenance and theory of operation.

#### 1.2 OVERVIEW

### 1.2.1 SLAVE VERSUS TRADITIONAL IN-CIRCUIT EMULATION

Traditional in-circuit emulation is less than ideal. Often, the processor under test is restrained from running at full speed, or some of its memory is tied up by the emulation hardware, or the system under test must be halted to conduct debugging operations. These limitations are removed when using slave in-circuit emulation, because the multiprocessor, and the multiple bus organization of the Kontron Slave Emulator allows full-speed emulation of 8-bit, or 16-bit microprocessors.

Note that from this point on, throughout this manual, the Kontron Slave Emulator is referred to as the Emulator.

### 1.2.2 EMULATION OBJECTIVES

The two main objectives of the emulation process are:

- a. Substitution of an Emulation Processor for the target system's processor.

- b. Enabling the user to monitor and control the target system. This is accomplished by surrounding the Emulation Processor with controlling circuitry.

# 1.2.3 TARGET SYSTEM SUBSTITUTION

The Emulator substitutes an identical processor for the target system's processor. To eliminate critical physical distances, this Emulation Processor is housed in a small portable chassis called a Probe, which is connected by a short cable to the target system's vacant microprocessor socket. The signals into and out of the Emulation Processor can be easily relayed from the Probe to the target system's socket.

#### 1.2.4 THE EMULATION SYSTEM

The Development System consists of a 2300 Console with keyboard and CRT display, a dual floppy disk system, supporting software/firmware, and other parts.

One of the advantages of Slave Emulation is the ability to emulate up to four microprocessors simultaneously through one Development System. This provides a low-cost and efficient means to emulate a multiprocessor environment. Up to four processors can be monitored, and controlled from one station. All Emulators can be synchronously halted 'from a single event in any of the Emulators or a combination of several events in one or more of the Emulators. This is a powerful debugging tool in a multiprocessor environment. See Figure 1-1, Multi-Emulation Station.

#### 1.3 HARDWARE DESCRIPTION

#### 1.3.1 EMULATOR CABINET

Within the Emulator cabinet is an eight slot card cage which must have a minimum of three boards installed: an Interface Processor Board, a Breakpoint Board, and a Personality Board. The maximum number of boards is eight, adding an optional Logic Analyzer, and up to four Simulation Memory boards. When changing to a different Emulator configuration, access to the boards is through the rear panel.

### 1.3.2 EMULATOR PROBE

The probe is a buffer device which brings the Emulation Processor as close as possible to the target system to prevent loss of signal integrity. It is microprocessor dependent, and serves as the interface between the microprocessor being emulated, and the Emulator Personal Board. A more detailed explanation of the Emulator Probe is given in Chapter 4, and also in each of the microprocessor specific supplements to this manual.

Figure 1-1. Multi-Emulation Station

### 1.3.3 EMULATOR BOARDS

The Emulator holds a maximum of eight boards. Each board, with its component side up, can be inserted into any one of the eight interchangeable slots in the card cage. The backplane of the card cage is a parallel bus system, designed to bring information from the microprocessor and the target system to the Emulator.

The basic boards and minimum configuration shipped with the Emulator include:

- 1. Interface Processor Board The IP responds to commands from the console, controls the Emulation Processor and returns data to the user.

- 2. Breakpoint Board The Breakpoint board has four hardware breakpoints that can break on parameters such as address, data, memory, I/O, execution/fetch, and a pass counter.

- 3. **Personality Board (Microprocessor specific)** This board is the interface between the emulated processor's bus and the Slave Emulator. In addition, it directly controls all emulation processes.

Optional boards are Simulation Memory, Dynamic Memory when supported, and a Logic Analyzer. Simulation Memory is available from 16K to 512K bytes of memory. The functions of these boards, and the entire system are described in Chapter 4.

The addition of the Simulation Memory Board and the Logic Analyzer board to the Slave Emulator configuration allows debugging without involving the target system memory. Simulation Memory board can simulate ROM, without having to program ROMs.

Logic Analyzer simplifies troubleshooting by providing detailed waveform display and cycle data display. This allows the user to view bus data during program execution.

#### 1.3.4 EXTERNAL PROBE

The External Probe, see Figure 1-2, External Probe, is a multifunction device that works together with the Breakpoint, and optionally with the Logic Analyzer. It brings in four external signals, called external lines in the breakpoint parameters, from any TTL compatible source. These external lines can be used as breakpoint qualifiers or they can be traced by the Logic Analyzer.

Breakpoint triggers for breakpoints 0, 1, and 2 are brought out to the External Probe for use by another External Probe from another Emulator. These triggers are used for synchronous breakpoints in a multi-processor environment or as a complex trigger for an oscilloscope or other test instrument. Chapter 4 Section 4.9 details the functions of the External Probe.

Figure 1-2. External Probe

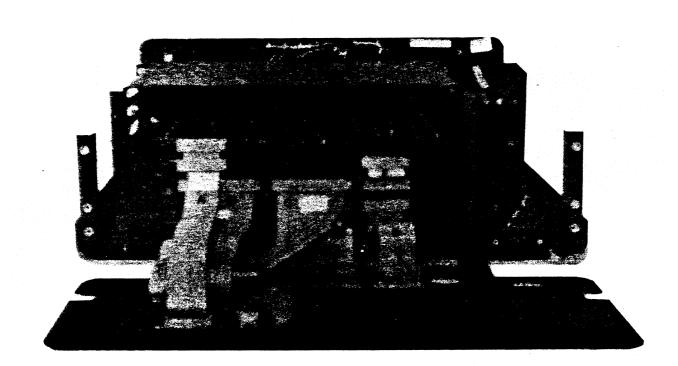

# 1.3.5 INTERNAL EMULATOR CABLING

The internal Emulator cabling system is shown in Figure 1-3, Internal Cabling. This is a view of the Emulator with the top enclosure cover and rear panel removed. Five boards are shown with six sets of separate cables. These boards are, from top to bottom, the Breakpoint, the Logic Analyzer, the Personality, the Interface Processor, and the Memory.

Table 1-1 identifies the internal cables used in the Emulator.

| <u>Cable</u> | Part Number | Usage                                                                       |

|--------------|-------------|-----------------------------------------------------------------------------|

| A            | 2302-0225   | Breakpoint board to Logic<br>Analyzer board to LOGIC<br>ANALYZER connector. |

| В            | 2302-0221   | Personality board to PROBE I connector.                                     |

| С            | 2302-0222   | Personality board to<br>PROBE II connector.                                 |

| D            | 2302-0226   | Interface Processor to<br>PORT B connector.                                 |

| E            | 2302-0026   | Interface Processor board<br>to PORT A connector.                           |

| F            | 2302-0234   | Logic Analyzer board to<br>Personality board.                               |

Table 1-1. Internal Cables

Figure 1-3. Internal Cabling

# 1.4 SPECIFICATIONS

# 1.4.1 EMULATOR CABINET

Outline Dimensions:

| Width:  | 16.1" | (40.64cm) |

|---------|-------|-----------|

| Height: | 7.6"  | (19.3cm)  |

| Length: | 18.2" | (46.23cm) |

Weight: 40 lbs (18kg)

Cooling: Forced air

Operating Ambient Temperature: 0 to 40 C (32 to 104 F)

Storage Ambient Temperature: -50 to 125 C (-58 to 257 F)

Power system:

Input AC line voltage:

a. 90-130 VACb. 200-260 VAC

Input line voltages are a factory option.

Input current:

Less than 5 amps @ 115vac Less than 2.5 amps @ 230vac

Single phase 3-wire system

47 - 440 Hz

Note that the Emulator's power system is preset, at the factory, to your specifications.

Power Dissipation: 350 watts maximum

Circuit Protection:

110 vac, 5 amps circuit breaker (switch on front panel)

220 vac, 2.5 amps circuit breaker (switch on front panel)

3 amps fuse (internal power supply)

# 1.4.2 EXTERNAL PROBE

Outline Dimensions:

Width: 2.75" (6.985cm) Height: .625" (1.5875cm) Length: 2.75" (6.985cm)

Weight: 7 ounces (198gm) Cooling: Convection air Operating Ambient Temperature: 0 to 40 C (32 to 104 F) Storage Ambient Temperature: -50 to 125 C (-58 to 257 F) All inputs and outputs are TTL compatible.

#### 1.4.3 PERFORMANCE PROLOGUE

The most important link in any Emulator is the interface between the user's target system and the Emulator. Systems are designed with the assumption that a microprocessor will reside on board. The introduction of a length of cable and buffer circuitry (the Emulator) between the microprocessor and its socket may create problems. Wirewrapped prototypes, if not carefully laid out, can be very noisy. The introduction of a length of cable may make the system inoperable. It is important therefore that prototypes have a good power and ground grid. Wirewrapped boards should have the power and ground system soldered down. Systems operating within the guidelines of standard TTL logic will not encounter problems with an Emulator. Problems may be encountered with noisy systems.

CAUTION: The Emulator may not be used with a target which is floating with respect to ground. This float is measured as the voltage between target ground and chassis ground. The Emulator is referenced to standard earth ground. The Emulator power supply returns are attached to the chassis ground. Thus the microprocessor plug ground pins are referenced to chassis ground. IF THE TARGET IS FLOATING WITH RESPECT TO EARTH GROUND, SEVERE DAMAGE TO THE EMULATOR PROBE AND TARGET MAY OCCUR.

#### Signal Pulse Delays

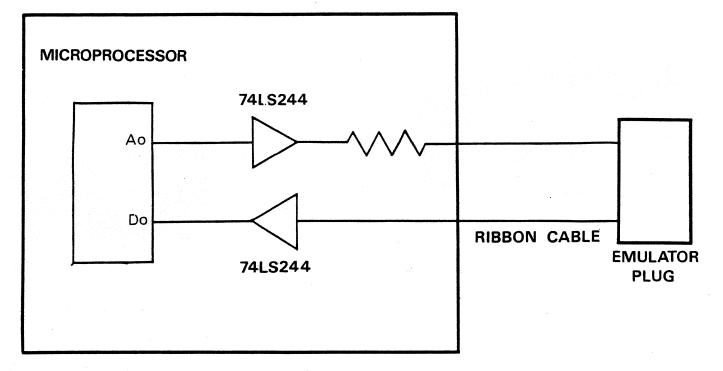

Each signal at the Emulator Plug is buffered in both directions in the Emulator Probe. A signal such as AO in Figure 1-4, Buffer Circuit, delivered to the Emulator Plug through the buffer tends to arrive typically 9 to 10 nanoseconds later. There is a similar delay in the signal shown as DO in Figure 1-4,, going to the microprocessor from the target system. For request/response operations such as memory reads, these delays are additive, and can result in a total delay of 9 to 18 nanoseconds. Detailed timing specifications are given in the supplement for each subsystem.

Microprocessor signal specifications are commonly referenced to clock edges. The clock is also delayed in passing from the target system to the microprocessor. To compensate for these delays, some Emulators, such as the 8086, have an adjustable clock delay generator designed into the Emulator Probe.

EMULATOR PROBE

# **INSTALLATION AND CHECKOUT**

# 2.1 INSTALLATION DOCUMENTS

Included in the shipment are four important installation documents:

Cover Letter Installation/Quality Report Configuration Checklist User Registration Card

The top half of the Installation/Quality Report is filled in by Kontron before the equipment leaves the factory. The bottom half of this form is filled in by Kontron installation personnel at the customer site. Additional comments can be made by the customer in the spaces provided at the bottom of the form, and then signed off.

The configuration checklist describes all the equipment included with each shipment from Kontron. This form is signed and dated by factory representatives. A complete list of the items sent in the shipment is provided for the customer to check off when the system is received. In case of any discrepancy, contact your Kontron representative.

#### 2.2 INSPECTING AND SETTING UP THE SYSTEM

After removing the Emulator from the carton, save all packaging materials in case the system requires shipping at a later date. An inventory of the shipment received should be taken immediately after all parts are removed from their shipping containers. Inspect the equipment for evidence of shipping damage to housing, panel controls, or cables.

Notify your Kontron representative of any problems found during the receiving inspection.

#### 2.3 CONFIGURATION REQUIREMENTS

If the Emulator being installed will be used in an already operational Development System that was previously set up for the Emulator, or has been just received from the factory, the configuration of the boards need not checked. If the Development System has not been used for emulation previously, it should be setup according to the following requirements.

#### 2.3.1 ADVANCED DEVELOPMENT SYSTEM CONFIGURATION

For Emulator operation, the system configuration must include, as a minimum, 64K bytes of memory, a Z80 board, and an MPIO board.

#### 2.3.2 EMULATOR CONFIGURATION REQUIREMENTS

The Emulator boards must be configured for the microprocessor being emulated. These are set correctly at the factory for the Emulator Subsystem. However, they will require reconfiguration if the the Personality board in the Emulator is changed. Correct configuration for each microprocessor is given in the specific Hardware Supplement for that processor.

#### 2.4 SYSTEM INTERCONNECTIONS

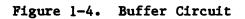

To install a single Emulator refer to Figure 2-1, System Interconnections, and connect the subsystems together as follows:

- a. <u>RS-232 Cable</u>. Connect one end to Port A (input) on the Emulator; the other to Serial 1 on the Developement System. Screw the connectors in place.

- b. Probe. Connect the two 50-pin connectors (the 72-inch cables) from the Emulator Probe box to Probe 1 and Probe 2 keyed connectors, on the Emulator.

Note that if more than one Emulator is being installed on the same console, the Emulators must be daisy chained as follows:

Output Port A of Emulator 1 to input Port B of Emulator 2, and Output Port A of Emulator 2 into Port B of Emulator 3 etc., up to four Emulators.

Figure 2-1. System Interconnections

#### 2.5 GETTING STARTED

The following checkout procedures which are performed without a target system, will acquaint you with some of the most commonly used Emulator commands. If any problems are found while executing this procedure, contact your local representative for further assistance.

## 2.5.1 CONVENTIONS

The following conventions are used to key-in characters, statements, and commands.

| LETTERS      | Commands and statements are composed of letters and<br>special characters. They are typed in uppercase and<br>must be exactly as shown. |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| SPECIAL KEYS | If a special character key is required, it will be enclosed in angle brackets.                                                          |

|              | Example 1: <return> means press the RETURN key on the keyboard.</return>                                                                |

Example 2: JM<RETURN> means key-in the letters JM, then press the RETURN key.

Note that the angle brackets should not be typed. They only show syntax and are not part of any command or required input.

BLANKS

No BLANKS are allowed within system commands.

#### 2.5.2 POWERING UP THE SYSTEM

- a. Set the ON/OFF power switch at the rear of the system to ON.

- b. Set the ON/OFF power switch on the front panel of the disk drive to ON.

- c. Set the ON/OFF power switch on the front panel of the Emulator to ON.

If the following procedure, or any portion of it fails, refer to Chapter 3, MAINTENANCE.

## 2.5.3 INITIALIZING THE EMULATOR

The Emulator must be set to a starting position in every case, regardless of processor type. The response to the initializing procedure is the same, except the type of microprocessor displayed changes according to the Emulator personality used. An example of the procedure, using the 8086, follows:

- a. Press the <RESET> button on the Emulator.

- b. Insert the 8086 Emulator System File diskette (Part No. 2300-6081-02) into Drive 0.

- c. Enter JS<RETURN>.

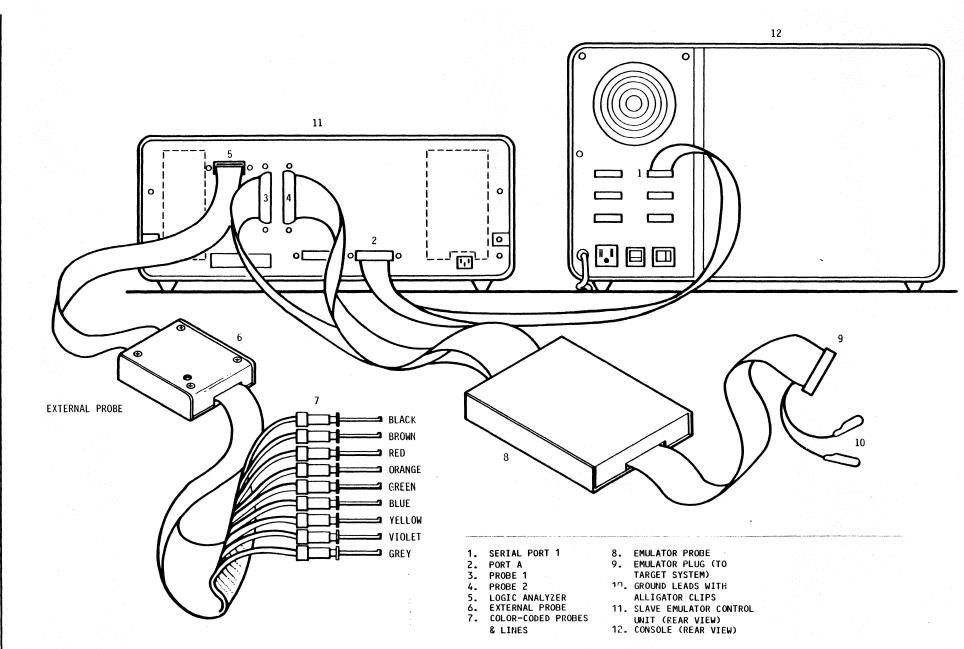

This command invokes the Emulator Debugger and displays the Executive on the console screen. See Figure 2-2, Emulator Executive Display. The status of each Emulator attached to the system is displayed. In this example, one Emulator is attached. It is identified as 8086v1 and is shown in a halted state. Two Emulator executive commands are displayed. Notice that the first two letters are highlighted. These two letters are the only ones which must be keyed in when entering commands.

Emulator Executive Vn.n Emulator 1 8086v1 Halted Emulator Executive Commands are: SWitch display to Emulator (0-8) SEt dialog modes Specify screen write options ; (display comment)

Vn.n = The software/hardware version number now being tested, and changes with new software releases.

Figure 2-2. Emulator Executive Display

## 2.5.4 SWITCH EMULATOR

The switch command SW activates the specified Emulator and causes it to display its status on the console.

n = 0 reactivates the Emulator Executive.

n from 1 through 8 activates the specified Emulator to be interrogated.

1. Enter SW1. Figure 2-3 shows the correct display for this command.

Emulator Executive Vn.n

Switch display to Emulator (0-8) 1 [Confirm]

Emulator 1 8086v1 Halted

Emulator Executive commands are:

SWitch display to Emulator (0-8)

SEt dialog modes

Specify screen write options

; (display comment)

Vn.n = The software/hardware version number now being tested, and changes with new software releases.

Figure 2-3. Enter SW1

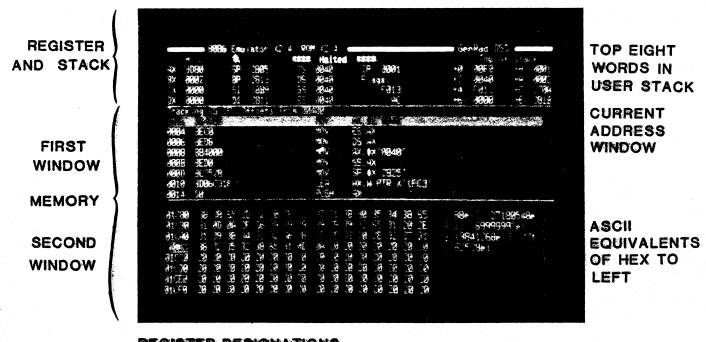

2. Enter <RETURN>. Figure 2-4, Switch Command Display shows the correct display for this command. In this display, the screen is divided into two major parts, REGISTERS AND STACK and MEMORY. In the REGISTERS AND STACK, all registers and a portion of the stack are displayed. The MEMORY portion is subdivided into CURRENT ADDRESS WINDOW, FIRST WINDOW, SECOND WINDOW, and an ASCII display of hexadecimal equivalents.

# REGISTER DESIGNATIONS

| AX - | Accumulator | SP - Stack Pointer       | CS - Code Segment        |

|------|-------------|--------------------------|--------------------------|

| BX - | Base        | <b>BP - Base</b> Pointer | DS - Data Segment        |

| CX - | Count       | SI - Source Index        | 98 - Stack Segment       |

| DX - | Data        | DI - Destination         | ES - Extra Segment       |

|      |             | Index                    | IP - INSTRUCTION POINTER |

Figure 2-4. Switch Command Display

#### 2.5.5 DEBUGGER COMMANDS

When in the debugger mode, commands can be entered in any order. The commands available can be referenced at any time by entering a <?> or <HELP>. Either command will display the help file, which lists all commands. In addition, once a command has been entered, a <?> can be entered again for additional information on the current command.

- 1. To begin, enter the Edit Simulation Memory Command EDS<RETURN>. The display will switch to the Simulation Memory configuration map. If Simulation Memory was not ordered or included in your unit, this procedure cannot be executed. The Simulation Memory Map indicates the number of blocks available, the size of the blocks (8K, 32K or 64K), and where they are presently mapped. When the system is initialized, all blocks are mapped contiguously from 0. Make sure that there is at least 16K bytes of Simulation Memory available. The Debugger prompts the block which you choose to relocate. The next prompt would be what starting address you want to relocate it to. In this manner, Simulation Memory blocks can be relocated to any 8K or 32K byte block boundary within the microprocessor's address space. In this checkout procedure the aim is to check on the current status of Simulation Memory without altering it. Press the <CAN> key to return to the Debugger display.

- 2. The counterpart to Edit Simulation Memory command is Edit Target Memory. Enter EDT<RETURN>. The display will switch to the Target Memory map. This map indicates which memory spaces are internal and which are external. Blocks of memory as small as 256 bytes can be mapped internally or externally by answering the series of prompts. When the system is initialized, it maps all of the memory spaces internally. If there is no target system connected, all of the memory space would be mapped internally. Press the <CAN> key to return to the Debugger.

- 3. All of the registers in the top window can be altered by the SEt command. Enter SEt, then the desired register mnemonic, and then the value. In this case set the program counter or instruction pointer to 500 (The program counter/instruction pointer is hereafter referred to as program counter). Notice that as you select the register, it is highlighted in reverse video, and then is altered to the value entered. At the same time, the upper memory window is updated to display the values at the program counter. When the Emulator is initialized, the top window will track the program counter.

- 4. One of the memory window options is to display from an offset or absolute address. The Emulator, when emulating segmented microprocessors such as the 8086, will initialize with the offset mode enabled in the upper window. To enable the offset mode the command WIndow is used and the option OFfset is selected. The offset value for the memory window is set using the OFfset command.

- 5. Programs can be stored into memory in two ways. They can be loaded down from disk or they can be entered via the keyboard. In this example we will store a short loop by using the STore command. The STore command will store data in bytes starting at the current memory location. The current memory location is indicated in one of the memory windows by the reverse video display across the entire memory window. In this case data will be stored at 500. In the next step, proceed to the section for the microprocessor you are emulating.

- 6. A. 8086

The 8086 has a code segment register. The upper memory window will track the instruction pointer and code segment registers. Set the code segment register CS to 0000. To do this use the SEt register command. Enter SEt register CS=0000.

Store the following bytes.

Enter SToreFF CO A3 50 05 EB F9 <RETURN><RETURN>

Notice that the upper memory window now has the above opcode displayed in both machine code and disassembled shown below.

| 500 | FFCO   | INC | AX               |

|-----|--------|-----|------------------|

| 502 | A35005 | MOV | W PTR X`0550',AX |

| 505 | EBF9   | JMP | SHORT X`0500'    |

Proceed to step 7.

#### B. 68000

The 68000 has a Trace bit that will generate an interrupt after every instruction if it is set in the Status Register SR. Set the Status Register to 2700 by entering SEt register 2700 <RETURN> to disable the Trace bit.

Store the following "vtes.

## Enter STore52 80 31 CO 05 50 60 F8 <RETURN> <RETURN>

Notice that the upper memory window now has the above opcode displayed in both machine code and disassembled as shown below.

| 500 | 5280     | ADDQ.L | #1,D0     |

|-----|----------|--------|-----------|

| 502 | 31C00550 | MOVE.W | D0,000500 |

| 506 | 60F8 BRA | 000500 |           |

Proceed to step 7.

C. Z8000

Set the Fcw by entering SEt register Fcw 4000.

Store the following bytes.

Enter SToreA9 10 6F 01 65 50 5E 08 05 00 <RETURN> <RETURN>

Notice that the upper memory window now displays the machine code and its disassembly as shown below.

| 500 | A910 INC | R1,#1 |         |

|-----|----------|-------|---------|

| 502 | 6F010550 | LD    | 0550,R1 |

| 506 | 5E080500 | JP    | UN,0500 |

Proceed to step 7.

D. 6502

Store the following bytes.

Enter SToreEE 05 50 AD 05 50 4C 00 05 <RETURN> <RETURN>

Notice that the upper memory window displays the machine code and its disassembly as shown below.

| 500 | EE0550 | INC | 5005 |

|-----|--------|-----|------|

| 503 | AD0550 | LDA | 5005 |

| 506 | 4C0005 | JMP | 0500 |

Proceed to step 7.

E. 6809

Store the following bytes.

Enter STore4C B7 05 50 20 FA <RETURN> <RETURN>

Notice that the upper memory window now displays the machine code and its disassembly as shown below.

| 500 | 4C     | INC | Α    |

|-----|--------|-----|------|

| 501 | B70550 | STA | 0550 |

| 504 | 20FA   | BRA | 0500 |

Proceed to step 7.

F. Z80

Store the following bytes.

Enter STore3C 3A 50 05 C3 00 05 <RETURN> <RETURN>

Notice that the upper memory window displays the machine code and its disassembly as shown below.

Show disassembled Z80 code.

Proceed to step 7.

- 7. When executing a program, several memory windows can be tracked. The number of memory windows (1 to 4), and their orientation is selected by the SCreen command. This command selects 8 memory window display formats. To find out what the optional formats are, enter SC?. The display will switch to the screen format help display. Press the <CAN> key to return to the Debugger display. When initialized the Emulator selects format 2.

- 8. While the Emulator is executing, the memory windows are updated every time a command string is completed or a breakpoint is reached. To update the screen periodically a <RETURN> can be entered to force updating. Memory windows can track a specific location or track at a register. By entering Display expression, the memory window will track a specific memory space. Display @ expression is used to track a register. These commands are implemented on the current memory window. The current memory window is selected by pressing the <TAB> key. In this example the top memory window is tracking the program counter and the bottom window is displaying above and below 0000.

- 9. Each memory window can display memory data in two formats: hexadecimal or symbolic. This is selected by the WIndow command. In this example the upper window is displaying in the symbolic format and the lower window is in the hexadecimal format.

- 10. The program counter is now at 500 and the upper memory window is tracking the program counter at 500. The EXecute command can now be invoked and the Emulator will begin execution at the program counter. Enter EXecute <RETURN>. The message Running will appear at the message line on the display. Press the <RETURN> key several times and notice that the program counter, the incremented register, and the upper memory window are updated with each stroke of the return key.

- 11. The Halt command forces the Emulator to cease execution of user's code and updates the Debugger display to the point where the processor is halted. Enter Halt<RETURN> Notice that the message line now reads Halted and that the program counter and upper window display are now updated to the next instruction to be executed.

- 13. The *(STEP)* key will execute one instruction at the current program counter. Press the *(STEP)* key and notice the message Completed Single Step appears at the message line. Notice also that the program counter and upper memory window have advanced to the next instruction.

The four hardware breakpoints give complex breaking options. Enter (Breakpoint 1,). The screen will switch to the breakpoint 1 status display. On the left hand side of the screen are the options and on the right hand side of the screen are the current parameter settings for breakpoint 1. Count indicates the number of passes over the breakpoint before a break occurs. Set Count to 32767 by entering (Count 32767).

Address and data can be set to a specific value or X for don't care. Set address to 500 by entering (Address 500). Data should be left at don't care for this example.

External lines are the four external lines from the External Probe. In this example they are set at don't care.

Instruction/Data indicates whether the breakpoint should break on the fetch or the execution of the specified address. For prefetching processors like the 8086, this makes a significant difference since the microprocessor can fetch ahead as many as six bytes. When breaking on an instruction, it should be set to Instruction. When breaking on a data move as in a peripheral access, it should be set to Data. In this example it is set to Instruction.

Read/Write specifies the direction of data flow for the breakpoint.

Memory/IO indicates that the break will occur during a memory or I/O cycle. For some microprocessors like the 68000, which has no I/O cycles, this parameter is meaningless, and it is ignored. For this example, it is left at Memory.

Halt/Snapshot indicates whether the processor will halt or continue execution after the breakpoint is reached. In this example, it is left at Halt.

Breakpoint 1 should now be set as follows:

| Count            | = | 32767 |

|------------------|---|-------|

| Add              | = | 00500 |

| Data             |   | XXXX  |

| Ext Line         | = | XXXX  |

| Instruction/Data | - | I     |

| Read/Write       | = | R     |

| Memory/IO        | = | M     |

| Halt/Snapshot    |   | H     |

|                  |   |       |

2302-5003-01

- 14. Execute the program by entering the EXecute command. Notice the message Stopped at Breakpoint 1 appears on the message line. The program counter and the upper memory window will display the next instruction to be executed by the Emulator. Since prefetch and breakpoint characteristics of different microprocessors are different, each microprocessor will halt at a different point.

- 15. The breakpoints can be cleared individually using the RESEt command or all breakpoints can be cleared using the CLear command.

The preceding 15 steps have been an introduction to some of the commands as they might be used without a target system. Three more steps are required to begin emulation with a target system.

- 1. The Emulator Plug is inserted in place of the microprocessor on the target system. Use caution when plugging the Emulator probe into the target system. Placing the plug in backwards can damage the probe, or cause the target power supply to short to the probe's ground. Care should be taken that pins are not bent and that the Plug is inserted in the correct orientation.

- 2. Some or all of the microprocessor's address space must be mapped externally to gain access to the desired portions of target memory. This is done using the **EDit target memory** command.

- 3. Each Emulator Subsystem has target system control lines to the Emulation Processor. These can be enabled, or disabled under the ENable control lines command. It may be necessary to enable some or all of the control lines to the target system depending on the microprocessor and the target system. For example, if the target memory to be accessed is slow, and requires the use of a wait line, this line should be enabled under the ENable control lines command. When you choose to ignore all interrupts, and DMA processing, leave the ENable control lines disabled.

Additional processor specific information is given in the Supplement for each of the Emulator Subsytems. The Debugger chapter of the Development Manual provides detailed descriptions of all commands.

## 2.6 EXTERNAL PROBE FUNCTIONAL DESCRIPTION

The External Probe performs two functions. First function is to provide external breakpoint triggers. These triggers can then be used as a complex trigger for oscilloscopes, or passed on to another Emulator to provide synchronous breakpoints in a multiprocessor emulation environment. The second function of the External Probe is to input four external, TTL compatible conditions to the Breakpoint Board for external break conditioning, and to the Logic Analyzer to be traced with the other Emulation Processor functions.

The External Probe is described in complete detail in Section 4.9.

## MAINTENANCE

#### 3.1 SYSTEM MAINTENANCE AND TROUBLESHOOTING

Preventive maintenance is not required on the Emulator as a whole, or on any subsystem unit. When a malfunction does occur, troubleshooting and analysis should first be attempted on a system level. This can best be done by using the system software to examine or interrogate the various units, observing the resulting console displays (and/or ha.d copy if available), then proceeding to correct the operational defect. There are several operational checks to determine if proper procedure has been violated resulting in an error. In addition to the procedures following, please refer to Section 2 in the Supplement for possible errors in configuration or application. Emulator troubleshooting requires the user to be familiar with total system software and ADS Console programming operations.

## 3.1.1 EMULATOR MALFUNCTIONS

The Emulator unit requires no operational mechanical or electrical preventive maintenance. If trouble develops immediately after any part of the Emulator has been disconnected, or disassembled, recheck the work done.

Error symptoms may have causes outside the Emulator unit. These could be hardware-originated, software-originated, or both. Check to see that the Emulator Probe and Emulator Personality boards are compatible. The software revision number on the Emulator Executive must match the Interface Processor board PROMs. Check the Hardware Supplement Section 2 for correct board configurations.

If any board is suspected as the source of trouble, check first to make sure that all IC's are snug in their sockets.

Check all boards, cables and connectors for a tight fit.

Check that the individual straps on each of the boards is correct.

## 3.1.2 FLOPPY DISK UNIT MALFUNCTIONS

Preventive Maintenance. Procedures for preventive maintenance are detailed in the FutureData INSTALLATION AND MAINTENANCE MANUAL (2300-5003-01).

## 3.1.3 ADS MALFUNCTIONS

ADS malfunctions, maintenance techniques, and troubleshooting information are found in the FutureData INSTALLATION AND MAINTENANCE MANUAL (2300-5003-01).

## 3.2 EMULATOR TROUBLESHOOTING CHARTS

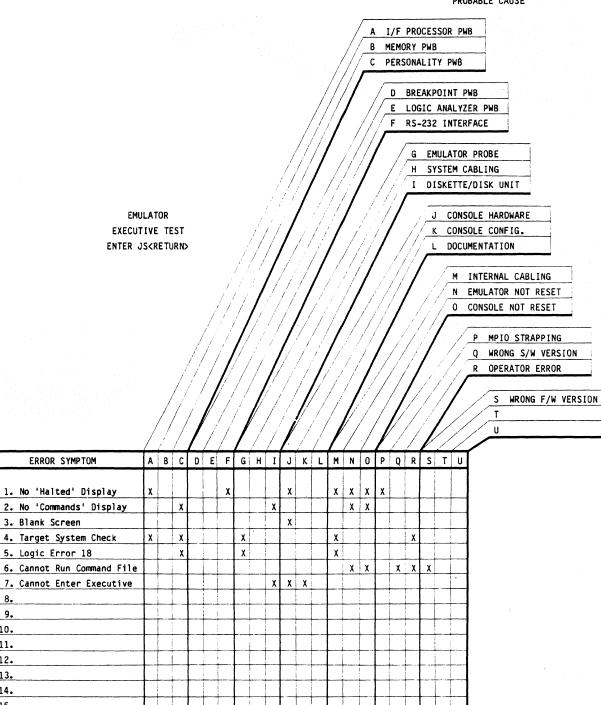

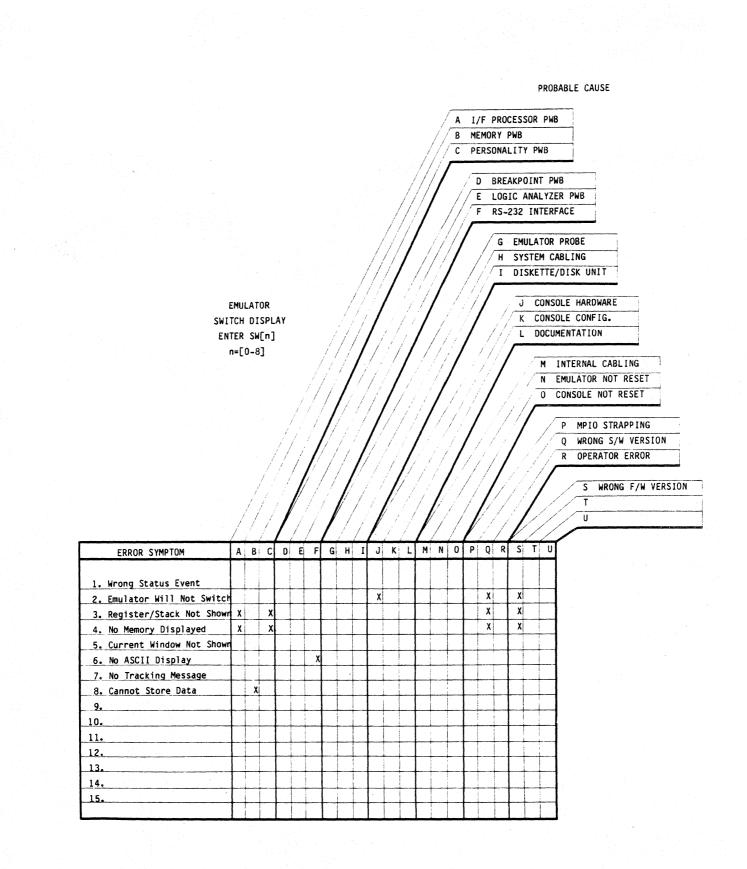

Each of the following generalized charts is correlated with the Emulator checks performed in Chapter 2.

PROBABLE CAUSE

Figure 3-1. Executive Test Symptoms

8. 9. 10. 11. 12. 13. 14. 15.

Figure 3-2. Switch Display Symptoms

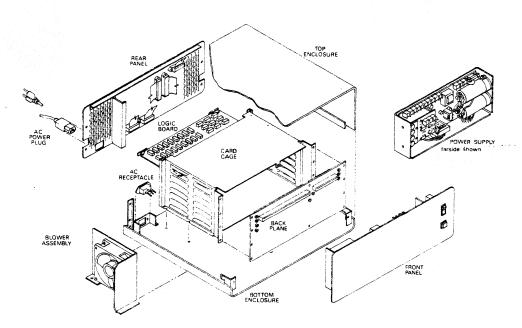

## 3.3 DISASSEMBLY INSTRUCTIONS

Major subassemblies can be readily removed from the main frame. These subassemblies are:

- a. rear panel

- b. enclosure cover

- c. front panel with power supply

The customer should avoid disassembly beyond that described in this manual, especially during the warranty period. Only Kontron Service Representatives should attempt further detailed disassembly of this equipment. Figure 3-3, Exploded View, depicts the Emulator subassembly.

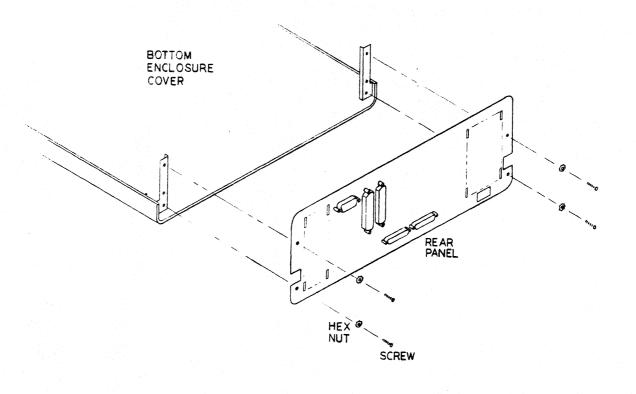

## 3.3.1 REAR PANEL REMOVAL

To reconfigure the Emulator, it is necessary to remove the rear panel. Refer to Figure 3-4, Rear Panel Removal.

- a. Set the ac ON/OFF power switch to OFF and unplug the ac line cord at both ends.

- b. Remove all flat cables from their rear panel connectors. When unscrewing jack-screws, alternate between screws so that both connectors stay parallel.

- c. Remove the four screws shown in the illustration. The rear panel can now be removed.

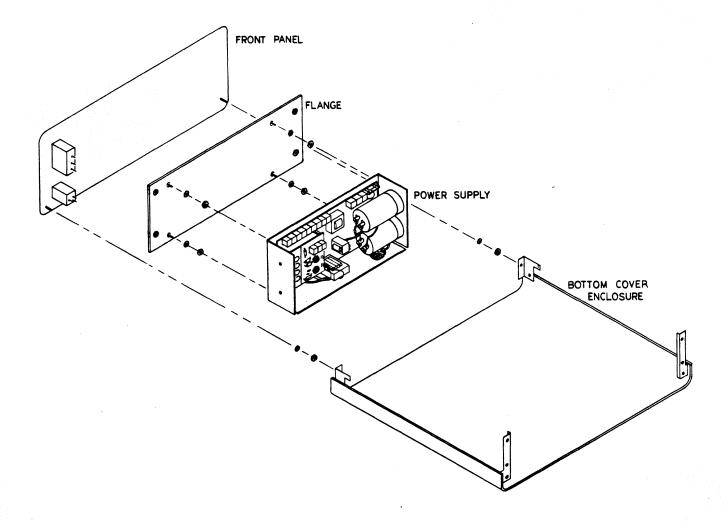

## 3.3.2 BOARD REMOVAL

Removing logic boards is a simple operation. Refer to Figure 3-5, Board Removal.

Position thumbs on the board ejectors and pull back, rotating the ejectors outward until the board is pulled away from the Emulator backplane connector. Gently slide the board all the way out.

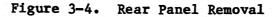

## 3.3.3 ENCLOSURE COVER REMOVAL

Refer to Figure 3-6, Enclosure Cover Removal. It is not usually necessary to open up the interior of the Emulator except to replace the power supply fuse.

First, the rear panel must be removed as shown in Section 3.3.1. Then, remove the two screws holding the top cover to the corner brackets as shown in the illustration, Lift and pull back from the rear as shown. Notice the cover-locking guides at the front sides of the chassis.

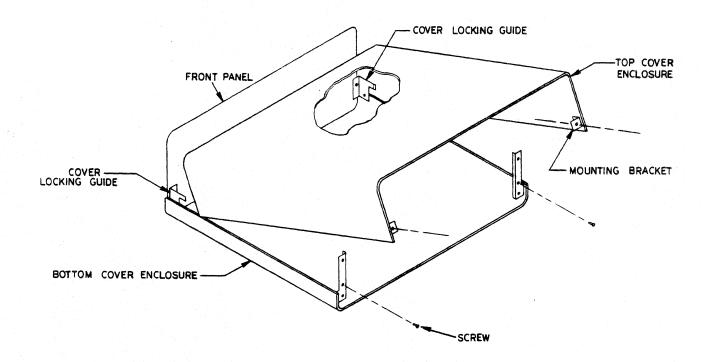

## 3.3.4 FRONT PANEL/POWER SUPPLY REMOVAL

Refer to Figure 3-7, Front Panel Details.

- a. Label or mark all wires and wire cables on strip terminals, ON/OFF switch, and RESET switch. Remove the wires and wire cables.

- b. Remove the two hexagonal nuts, shown in the illustration, from the front mounting flange on the bottom enclosure. Remove the front panel.

- c. Remove the four hexagonal nuts holding the power supply mounting flange to the front panel. Remove the power supply assembly from the front panel.

- d. Remove the hexagonal nuts holding the power supply to the flange.

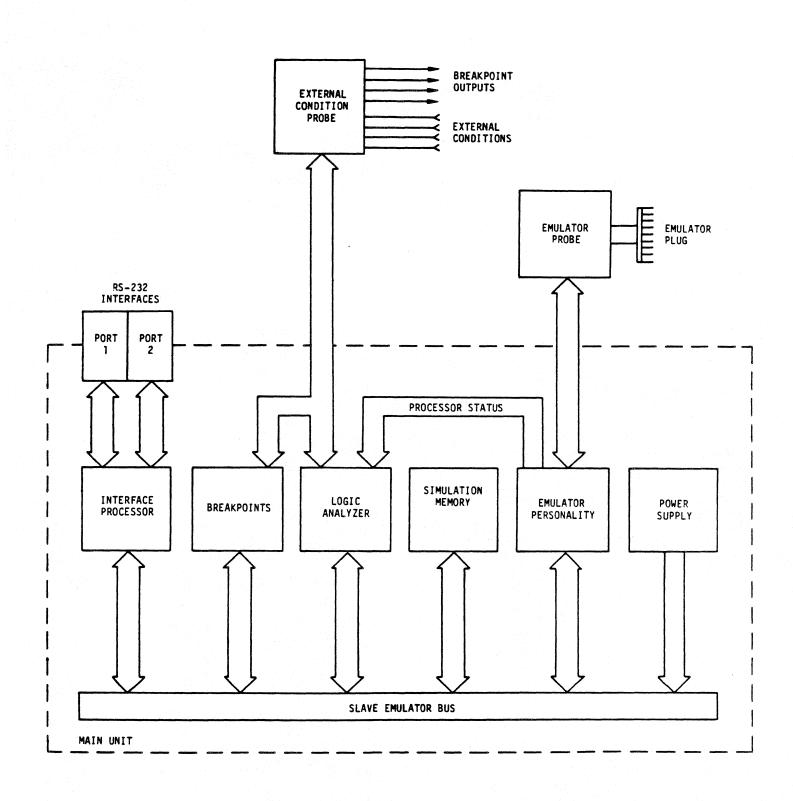

Figure 4-0 Slave Emulator Block Diagram

2302-5003-01

# THEORY OF OPERATION

## 4.1 SCOPE

This chapter describes all of the major functions of the Emulator and each logic board.

## 4.2 GENERAL DESCRIPTION

In the past, practical in-circuit emulation equipment did not allow the processor under test to run at full speed, or it partially limited the use of the microprocessor memory by the emulation equipment. Also, the system under test had to be halted to conduct debugging operations. These limitations are solved with the 2302 Emulator. Rather than using a single bus, the Emulator employs a multiprocessor, multiple bus organization that permits full-speed emulation of 8-bit, or 16-bit microprocessors.

The Emulator works in conjunction with Kontron's 2300 Series Advanced Development System (ADS). Communication takes place over a 19.2-kb/s RS-232C serial interface. Up to four Emulators may be daisy-chained to a single development system. Each Emulator includes a 4MHz Z80-based Interface Processor as the main processing unit.

Every Emulator has a separate Probe which contains the processor to be emulated. The user can add optional boards to get additional memory, or a Logic Analyzer. Each Emulator may uses a different Emulator subsystem, which has a different Personality Board that plugs into the Emulator back plane cardcage, and an external Emulator Probe which places critical components close to the user's prototype.

The target system's microprocessor is removed and the Emulator Probe is plugged into the vacant socket. This Probe module contains a processor of the same type as the one just removed from the target system. The Emulator substitutes this proxy processor -- called an Emulator Processor -- for the target system's processor. Thus the Emulator's first function is to imitate the target system's processor. Its second function is to provide the user control over the emulation. This is accomplished by surrounding the Emulation Processor with controlling circuitry which is used to monitor and control the Emulation Processor.

The Emulator therefore performs these three functions:

- 1. Substitute an Emulation Processor for the target system's processor.

- 2. Provide the user the ability to monitor the Emulation Processor.

- 3. Provide the user the ability to control the Emulation Processor.

#### 4.3 SUBSTITUTING THE EMULATION PROCESSOR FOR THE TARGET SYSTEM'S PROCESSOR

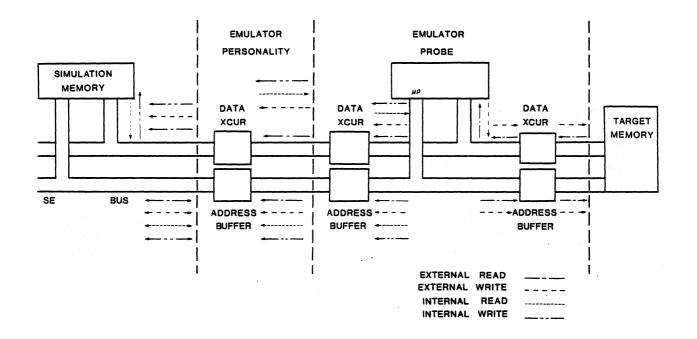

The Emulator Subsystem -- consisting of Emulator Personality board and Probe board -- substitutes an identical processor for the target system's processor. To eliminate critical physical distances, this Emulation Processor is housed in the Probe, which is connected by a short cable to the target system's vacant microprocessor socket. The signals into and out of the Emulation Processor are relayed from the Probe to the target system's socket.

## 4.4 MONITORING THE EMULATION PROCESSOR

Controlling the Emulation Processor requires the ability to monitor it. The Emulator contains three boards concerned with this task. They are:

- 1. The Logic Analyzer Board (optional).

- 2. The Breakpoint Board.

- 3. The Emulator Personality Board.

#### 4.4.1 LOGIC ANALYZER BOARD

The Logic Analyzer works together with the Breakpoint Board to provide up to 256 bus cycles of information. This information includes all address and data lines, four external lines from the External Probe which the user selects, and control lines from the microprocessor. The Logic Analyzer is always in operation, recording all bus cycles even when not in use. The Logic Analyzer is halted by breakpoints defined by the user. The Analyzer also contains a timer which can be activated by Breakpoint 1 and halted by Breakpoint 2. This timer can record elapsed time between two events in 100's of nanoseconds, microseconds, or number of bus cycles.

#### 4.4.2 BREAKPOINT BOARD

The Breakpoint Board provides four hardware breakpoints. Hardware breakpoints are used so that the user's code is not altered as would be necessary with software breakpoints. Four hardware points also provide the user with increased versatility in specifying the number of passes over a breakpoint, whether to break on a read or write cycle, and in specifying the address or the data on which to break, without interfering with the user's code

## 4.4.3 EMULATOR PERSONALITY BOARD

This board examines the internal registers of the Emulation Processor, records the contents of these registers in Test Memory area, and allows user access to this information.

## 4.4.4 SIMULATION MEMORY

Simulation Memory is provided for use in target system development or debugging. The Emulator does not use the Simulation Memory to perform any of its functions. Depending on the memory options selected, up to four Simulation Memory Boards may be placed in the Emulator, to provide from 16-kilobytes to 512-kilobytes of memory. This memory can be edited into 8-kilobyte blocks and mapped internally into any area of the emulated processor's address space, or externally to the target memory, down to 256-kilobyte boundaries. Simulation memory is provided to be used together with, or in place of the user's target memory. Simulation memory may also be write-protected to simulate ROM.

## 4.5 CONTROLLING THE EMULATION PROCESSOR

Although there are three boards in the Emulator concerned with monitoring the Emulation Processor, only the Personality Board has direct control over it. The Emulator interface is separated into two sections to minimize the physical and electrical distances between the Emulator and the target being developed. The bulk of the Emulator interface is housed on the Personality Board. The rest of the interface is in the Emulation Probe which is attached to the Personality Board by two 50-connector cables. The probe is plugged into the microprocessor socket of the system being emulated.

## 4.5.1 EMULATOR PERSONALITY BOARD

The Emulator Personality board is designed to perform the following functions:

- 1. Examine registers of the Emulation Processor.

- 2. Change the contents of registers.

- 3. Read and write to memory locations.

- 4. Read and write to I/O ports.

- 5. Enable or disable target control of the microprocessor.

- 6. Run or halt the microprocessor.

This last function adds to the ability of the Emulator to imitate the target system's microprocessor.

#### 4.5.2 INTERFACE PROCESSOR BOARD

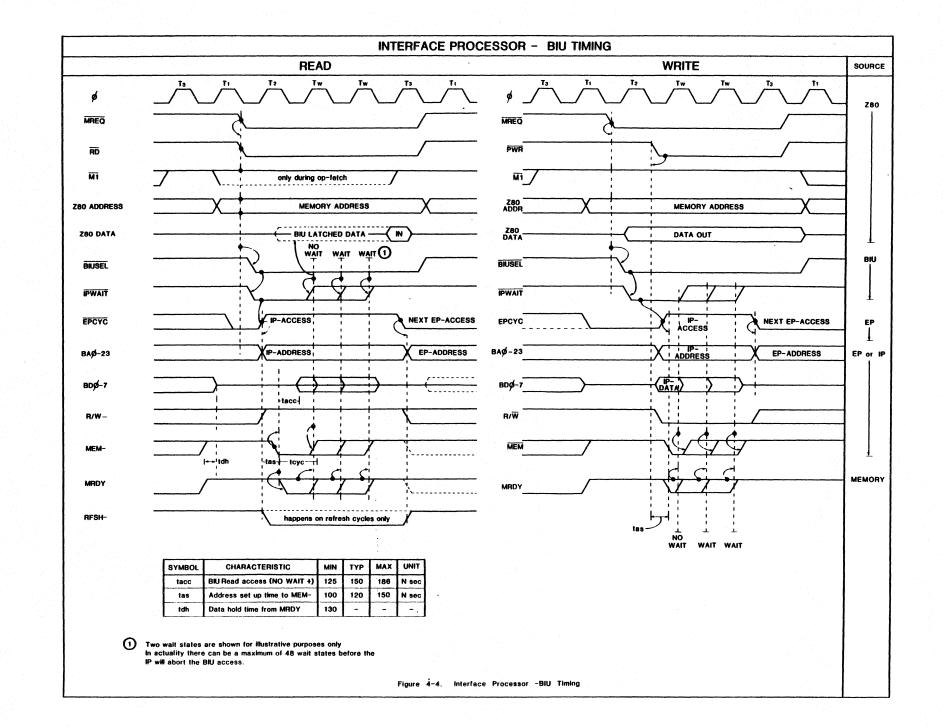

The Interface Processor board controls all the other boards in the Emulator, and communicates with the ADS controlling the Emulator. This board contains a Z80 microprocessor running at 4MHz, 16K of dynamic RAM, two serial I/O ports, and 16K of ROM.

All communication with the user comes from the ADS into Serial Port 1. For example, when the user examines the contents of the Logic Analyzer, the command to do so, and the information retrieved from the Logic Analyzer are relayed to the user through the Interface Processor. When communicating with any one board, the information is transmitted from the user through the Interface Processor to the specific board.

One of the important functions of the Interface Processor is the handling of "test" programs. These are the short programs which the Emulation Processor executes allowing user control over the Emulation Processor. When the Emulation processor is asked to execute a test program, the information picked up by the test program is relayed to the user through the Interface Processor. The test programs are stored in the 16K of dynamic RAM on the Interface Processor. When the Emulation Processor is interrupted, the appropriate test programs are loaded down into a small memory space on the Personality board called the Test Memory. If a data gathering test program is executed, the results of the program are stored in Test Memory. When requested by the user, information in Test Memory is picked up, and relayed to the ADS by the Interface Processor.

## 4.6 EMULATION TECHNIQUES

## 4.6.1 INITIALIZATION

Initialization is the process which prepares the Emulator hardware for emulation. This includes clearing all of the breakpoints, disabling the Logic Analyzer, mapping the Emulation Processor's address space internally to the Emulator, disabling all external Emulation Processor control lines, and "capturing" the Emulation Processor.

Capturing the Emulation Processor means to stop it from whatever it is doing (usually executing user code) and to give control of it to the Emulator. The Interface Processor (IP) commands the Emulator Personality (EP) to capture the Emulation Processor through one of its I/O control lines. The EP then begins the capture sequence through the use of a sequencer (state machine). Each Personality Board has to utilize a different technique, depending on the Emulation microprocessor involved, for capturing the processor. Some Personality Boards use a non-maskable interrupt and others substitute an instruction onto the data bus.

When execution of the interrupt or the substituted instruction begins, a small block of memory, called Test Memory (TM) on the EP, is mapped into the address space of the Emulation Processor. Execution then begins within the TM which has been previously loaded with a program by the IP.

TM can be various sizes and locations depending on the microprocessor under emulation. There are several small programs run by the Emulation Processor while executing out of TM. Each program gathers a specific type of information about the Emulation Processor or the target system.

As each test program is completed in TM, the IP is notified by an Emulator Personality Interrupt (EPI) which is generated by hardware as the Emulation Processor executes a specific portion of Test Memory code. The Emulation Processor is then halted using a jump to self or HALT instruction. The IP can then load additional programs into TM. Once the Test Memory is loaded, the Emulation Processor is forced to jump to the beginning of the test program. The Emulation Processor executes the program, another EPI is sent to the IP, and the Emulation Processor executes a jump to self. This process continues until all initial information is received by the IP. The IP sends this information back to the ADS and waits for additional commands.

## 4.6.2 THE EXECUTE COMMAND

Once the Emulator is initialized, and all emulation parameters have been set, the user is ready to execute. Before execution begins, the Emulation Processor is at a jump to self instruction as it does at the completion of each test program from TM. When the user issues an execute command, the IP changes the jump to self instruction that the Emulation Processor is executing to a jump relative. It then executes one or two instructions that are another jump relative or a return from interrupt. The sequencer on the EP detects this operation and tracks the Emulation Processor as it begins to fetch the code pointed to by the jump relative or the return from interrupt. When the first op-fetch of user code is made, the sequencer disables Test Memory out of the Emulation Processor's address space and execution of user's code begins.

## 4.6.3 THE HALT COMMAND

When the user issues a halt command, the Emulation Processor is not actually halted. It is captured by the EP. During the capture sequence, Emulation Processor's status is saved either by stacking it in Test Memory, or by hardware found on the EP. At the same time some, external control lines (interrupts) are disabled. This prevents loss of control by the Emulator. Once the Emulation Processor has been captured by the EP, an EPI is sent to the IP.

If the EP fails to capture the Emulation Processor from user control, a target system check message is displayed on the screen. Failure to capture the processor is usually caused by an Emulation Processor that has crashed. The causes of target system check messages are hard to determine, and often microprocessor specific. These are discussed in the Supplements for each microprocessor. Lack of power on the target, or the failure of target execution because of a bad code are a couple of possibilities.

The IP then loads Test Memory with test programs for the Emulation Processor to execute. These test programs are used to update the information displayed on the screen. When all test programs are completed, the Emulation Processor remains in the halt loop until another command is received from the user.

## 4.6.4 STORING DATA AND SCREEN UPDATING

Storing data and updating the screen while the Emulation Processor is executing user code are accomplished in the same manner as halting and then executing. If a user desires to alter memory, or to change a register, or to update the screen by pressing the return key, or to use snapshot breakpoints, the same technique is used. The Emulation Processor is captured, test programs are run in Test Memory by the Emulation Processor to alter registers, and to change or read memory, then execution is continued.

## 4.6.5 SINGLE STEP

Single stepping is essentially an execute command followed immediately by a halt command. The sequencer on the EP tracks the Emulation Processor as it exits TM code and begins to execute user code. As the first instruction is completed, the Emulation Processor is forced to execute from TM by the sequencer and effectively halts.

#### 4.6.6 MEMORY MAPPING

There are two types of memory mapping used for emulation: (A) Simulation Memory Mapping and (B) Internal/External Address Space Mapping.

A. Simulation Memory Mapping

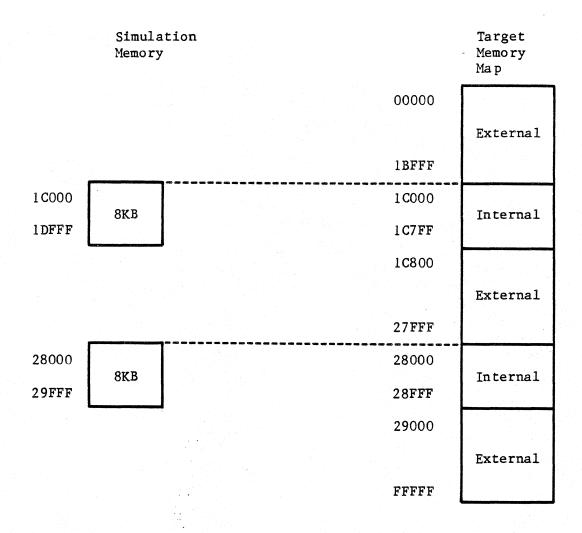

Simulation memory is optional memory within the Emulator which can be used in place of the user's target memory or by itself when executing code entirely within the Emulator. Memory is available on 16 Kbyte static, 32 Kbyte static, 64 Kbyte dynamic, and 128 Kbyte dynamic boards. Both of the static memories can be further divided into 8 Kbyte blocks and the 128 Kbyte dynamic memory into 32 Kbyte blocks. The 64 Kbyte memory is designed to work with some 8-bit 64 Kbyte microprocessors, and is therefore one contiguous memory. The blocks of Simulation Memory can be mapped anywhere within the address space of the microprocessor. This mapping function is accomplished by a high speed RAM on each of the memory boards. As mapping commands are given by the user, the IP configures the mapping RAM on the Simulation Memory boards. When emulation is in progress, each of the mapping RAMs monitors the Emulator address bus. When a bus cycle is executed within a memory block's mapped space, it is enabled for that cycle.

B. Internal/External Address Space Mapping

Internal refers to the mapping function of the address space within the Emulator. External refers to the mapping function of the address space within the target system. This address space mapping function can be on the IP, or on the Simulation Memory board depending on the configuration. Mapping is controlled by high speed RAM that is configured by the IP as the user edits the target system's address space. The internal/external address space mapper, which is called the target system map on the Emulator, can define whether an address is internal or external down to 256-byte blocks.

An example of how the mappers work together is shown in Figure 4-1, Memory Mapping. Let us assume the user wants to simulate target memory from 1C000 to 1C7FF and from 28000 to 28FFF and has one 16-kilobyte memory board. All other memory is to be mapped to the target system. First, Simulation Memory must be mapped to the appropriate areas. Since there is 16 Kbyte of Simulation Memory, both 8 Kbyte blocks are used. One block is placed at 1C000 and the other at 28000. Then target memory is mapped externally from 00000 to 1BFFF, 1C800 to 27FFF and 29000 to FFFFF. The target system mapper has priority over the simulation mapper and makes the decision to fetch from external or internal memory regardless of how Simulation Memory is mapped. If the target is mapped internally where there is no Simulation Memory, a floating bus will be read.

#### Figure 4-1. Memory Mapping

The decision to access data internally, or externally is made on a cycle by cycle basis. As the Emulation Processor puts out the address, the target memory mapper sends a signal to the EP and to the Emulator probe to switch all transceivers and buffers in the appropriate direction for the Emulation Processor to transmit or receive data. Figure 4-2, Buffer Control indicates the data flow and buffer control for each type of access.

Figure 4-2. Buffer Control

## 4.6.7 EXTERNAL CONTROL LINES

All input control lines from the target system to the Emulation Processor on the Emulator Probe are gated through an enable/disable control. These are inputs such as interrupt lines, halt, reset, and bus arbitration. The user can control these lines while the target is under emulation using the enable command. When the Emulation Processor is executing from Test Memory, the Emulator controls and overrides the user's definitions in order to prevent the target sytem from affecting the Emulator Durcessor. Bus arbitration control lines are not distilled by the Emulator during Test Memory execution if the user has enabled them.

## 4.6.8 BREAKPOINTS

Breakpoints function in the same manner as the halt instruction. When a breakpoint is reached, an interrupt is sent to the IP (breakpoint) and to the Emulator Personality board. The Personality board interrupts execution of user code as it does when halting and then issues an interrupt (EPI) to the IP. The IP, receiving both the EPI and breakpoint, forces the execution of test programs by the Emulation Processor to update the screen. If the breakpoint was specified as halt after break, the Emulation Processor remains in a halt loop. If a snapshot breakpoint is specified, user execution continues as with the execute command.

## 4.7 BACKPLANE CONNECTIONS TO THE EMULATOR BUS

The backplane of the Emulator cardcage consists of eight pairs of connectors; P1 with 86 pins, and P2 with 60 pins. The designation A indicates the component side of the board and the designation B the solder side. The eight slots on the cardcage backplane are identical, and any board can be plugged into any slot on the backplane, within the internal cabling limitations of the Emulator as described in Section 1.3.5.

Figure 4-3, Emulator Bus shows the bus system found on the backplane. +5 volts, and +12 volts is supplied on the bus with grounds distributed on approximately every fifth pin on both sides of each board.

| •            | PlA |                | P1B    |          | P2A |         | P2B |

|--------------|-----|----------------|--------|----------|-----|---------|-----|

| GND          | 1   | GND            | 1      | GND      | 1   | GND     | 1   |

| +5V          | 2   | +5V            | 2      | SAO+     | 2   | SA1+    | 2   |

| +5 <b>V</b>  | 3   | +5V            | 3      | SA2+     | 3   | SA3+    | 3   |

| +12V         | 4   | +12V           | 4      | BP 1+    | 4   | BP 2+   | 4   |

| LAS-         | 5   | BA25           |        | BP3+     | 5   | BP4+    | 5   |

| GND          | 6   | GND            | 5<br>6 | BP 10UT- | 6   | DI 4 1  | 6   |

| BA24         | 7   | GND            | 7      |          |     |         |     |

|              |     | <b>T</b> 4 0 0 |        | EP I-    | 7   |         | 7   |

| BA22         | 8   | BA23           | 8<br>9 | MAP-     | 8   |         | 8   |

| BA20         | 9   | BA21           |        |          | 9   | BP30UT- | 9   |

| BA18         | 10  | BA19           | 10     | SYS+     | 10  | RSTPB-  | 10  |

| BA16         | 11  | BA17           | 11     | BP2OUT-  | 11  | BP3IN-  | 11  |

| GND          | 12  | GND            | 12     | BP1IN-   | 12  | BP40UT- | 12  |

| BA14         | 13  | BA15           | 13     | BP2IN-   | 13  | BP4IN-  | 13  |

| BA12         | 14  | BA13           | 14     | 1000     | 14  | 1001    | 14  |

| BA10         | 15  | BA1 1          | 15     | 1002     | 15  | 1003    | 15  |

| BA08         | 16  | BA09           | 16     | 1002     | 16  | 1005    | 16  |

|              |     |                |        | 1004     |     |         |     |

| GND          | 17  | GND            | 17     |          | 17  | 1007    | 17  |

| BA06         | 18  | BA07           | 18     | 1008     | 18  |         | 18  |

| BA04         | 19  | BA05           | 19     | 1010     | 19  | 1011    | 19  |

| BA02         | 20  | BA03           | 20     | I012     | 20  | I013    | 20  |

| BAOO         | 21  | BA01           | 21     | I014     | 21  | I015    | 21  |

| GND          | 22  | GND            | 22     | I016     | 22  | 1017    | 22  |

| BD14         | 23  | BD1 5          | 23     | I018     | 23  | 1019    | 23  |

| BD12         | 24  | BD13           | 24     | 1020     | 24  | 1021    | 24  |

| BD10         | 25  | BD13<br>BD11   | 25     | 1020     | 25  | 1021    | 24  |

| BD10<br>BD08 | 26  |                |        |          |     |         |     |

|              |     | BD09           | 26     | 1024     | 26  | 1025    | 26  |

| GND          | 27  | GND            | 27     | 1026     | 27  | 1027    | 27  |

| BDO 6        | 28  | BD07           | 28     | 1028     | 28  | 1029    | 28  |

| BDO 4        | 29  | BD0 5          | 29     | 1030     | 29  | 1031    | 29  |

| BDO2         | 30  | BD03           | 30     | GND      | 30  | GND     | 30  |

| BD00         | 31  | BDO 1          | 31     |          | •   |         |     |

| GND          | 32  | GND            | 32     |          |     |         |     |

| BHE+         | 33  | BYTE+          | 33     |          |     |         |     |

| EPCYC-       | 34  | R/W-           | 34     |          |     | ,       |     |

|              | 35  | HLDA-          | 35     |          |     |         |     |

| CND          |     |                |        |          |     |         |     |

| GND          | 36  | MRDY+          | 36     |          |     |         |     |

| MEM-         | 37  | GND            | 37     |          |     |         |     |

| GND          | 38  | GND            | 38     |          |     |         |     |

| IPWAIT-      | 39  |                | 39     |          |     |         |     |

|              | 40  |                | 40     |          |     |         |     |

| +5V          | 41  | +5V            | 41     |          |     |         |     |

| +5V          | 42  | +5V            | 42     |          |     |         |     |

| GND          | 43  | GND            | 43     |          |     |         |     |

|              |     |                | 73     |          |     |         |     |

•

Figure 4-3. Emulator Bus

#### Signal Descriptions

| BAOO to BA25 | This is the address bus. Both the interface processor and |

|--------------|-----------------------------------------------------------|

|              | the Emulation Processor under emulation (on the Emulator  |

|              | probe) have access to this bus. The Emulation Processor   |

|              | has priority on the bus. The IP uses the bus for all      |

|              | transactions concerning the Test Memory, Breakpoint, Bus  |

|              | Analyzer trace setup and data, and memory mapping. The    |

|              | Emulation Processor uses the bus to access Simulation     |

|              | Memory. In the descriptions below, a "-" indicates that   |

|              | the signal is active low.                                 |

BD00 to BD15 This is the data bus. Its use is the same as the address bus described above.

LAS- Logic Analyzer Strobe. The negative edge of this signal strobes trace information into the Logic Analyzer, and is also the strobe for breakpoint comparisons on the Breakpoint Board. Sourced from the EP board.

BHE Byte High Enable. Enables the upper byte from Simulation or Test Memory onto data lines BD8-BD15. Sourced from the IP or EP.

EPCYC- Emulator Personality Cycle. Indicates that the Emulation Processor is the bus master. This signal is asserted high for IP cycles. Sourced from the EP board.

MEM- Memory Cycle. Indicates a memory cycle is in progress on the bus. Sourced from the IP or EP.

IPWAIT Interface Processor Waiting. Indicates to the Emulator Personality Board that the IP is requesting the bus. The EP will hold off the bus to the Emulation Processor and give it to the IP by asserting EPCYC high for one IP bus cycle. Sourced from the IP.

BYTE Indicates that the bus cycle in progress is a byte cycle and data should be placed on the BD00-BD07 lines. Sourced from the IP or the EP.

R/W- Indicates the type of cycle being conducted by the IP or the Emulation Processor. Low indicates a write cycle. Sourced from the IP or EP.

HLDA- Unused; reserved.

PRTY- Indicates a parity error in Simulation Memory. Generates an interrupt to the IP.

- RFSH- Refresh indicates a refresh cycle is in progress. Generated by the IP to refresh Simulation Memory.

- MRDY Memory Ready indicates memory access time is satisfied. Sourced from any memory device on the bus to the IP or the EP.

- SAO to SA3 System address used by the Interface Processor to access Emulator system functions such as the Logic Analyzer trace buffers.

- BP1 to BP4 Breakpoint interrupts from the Breakpoint board these signals indicate that a breakpoint has been reached. This signal triggers the EP's sequencer to capture the Emulation Processor.

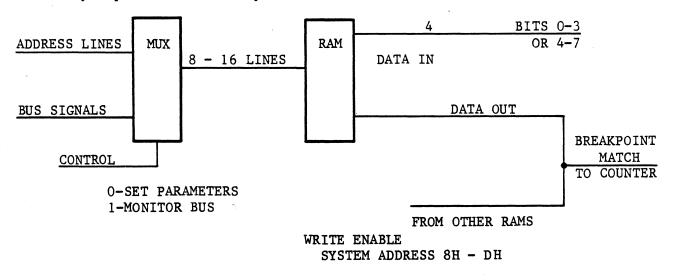

- EPI- Emulator Personality Interrupt. Generated by the EP hardware to indicate the Emulation Processor has reached a specified point in test memory execution.