# CAUTION

# DON'T DO ANYTHING BEFORE YOU READ THIS DOCUMENT!

/A4 100 0100=0000 1D5 0101=0000 200 0102=0000 620 0103=0000 10FF 0104=0000 73FE 0105=0000 18BF 0106=0000 9900 0107=0000 72E 0108=0000 73F8

how to use your GA-16/220

**\$-HDBK- 40**4

Keep It

## how to use your GA-16/220

#### **SENERAL AUTOMATION**

1055 South East Street Anaheim, California 92805 (714) 778-4800 TWX 910-591-1695

© 1979, General Automation, Inc.

Prepared on GA Econotext system-

#### **RECORD OF REVISIONS**

Title: How To Use Your GA-16/220

Document Number: 38A00525A

| DATE   | ISSUE          |

|--------|----------------|

| Oct 79 | Original Issue |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

#### 88A00525A-B

#### FOREWORD

The following documents, pertinent to the operation and configuration of the  ${\rm GA-16/220}$ , may be referenced for additional information.

| Document Number | <u>Title</u>                                                                    |

|-----------------|---------------------------------------------------------------------------------|

| 38A00508A       | GA-16/110/220 System Reference Manual                                           |

| 88A00509A       | GA-16/110/220 Maintenance Manual                                                |

| 94A01519A       | Reference Manual for Peripheral T&Vs on GA Series                               |

| 94A01531A       | GA-16/220/330 Stand-Alone Utilities Manual                                      |

| 94A01555A       | System Generation and Operator Interface for RTOS, RTX or DBOS on a $GA-16/220$ |

| 94A01563A       | System Generation and Operator Interface for FSOS on a GA-16/220                |

#### 88A00525A-B

#### TABLE OF CONTENTS

| Section  | Title                                                                                                                                                                                                                                                                                                                       | Page                                                                         |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 1        | INTRODUCTION                                                                                                                                                                                                                                                                                                                | 1-1                                                                          |

| 2        | 2.1 HARDWARE OVERVIEW.  2.1.1 CPU-1 MODULE.  2.1.2 CPU-2 MODULE.  2.1.3 MEMORY BOARDS.  2.1.4 MEMORY PARITY PROTECT (MPP) MODULE.  2.1.5 CROM MODULE.  2.1.6 SYSTEM CONSOLE INTERFACE (SCI) MODULE.  2.1.7 IPL ROMS.                                                                                                        | 2-1<br>2-1<br>2-1<br>2-1<br>2-2<br>2-4<br>2-4<br>2-5<br>2-6<br>2-7           |

| 4        | 3.1 MODULE (BOARD) INSTALLATION. 3.2 SWITCH SETTINGS. 3.2.1 SWITCH AND INDICATOR CONFIGURATION 3.2.2 INITIAL SWITCH SETTINGS. 3.3 INITIAL POWER-UP. 3.4 EXECUTING THE CPU T&V.  ADDITIONAL DOCUMENTATION. 4.1 ADDITIONAL T&VS AND UTILITY PROGRAMS 4.1.1 CPU RELATED T&VS. 4.1.2 PERIPHERAL T&V. 4.2 STAND-ALONE UTILITIES. | 3-1<br>3-1<br>3-2<br>3-16<br>3-17<br>3-17<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1 |

|          | LIST OF APPENDICES                                                                                                                                                                                                                                                                                                          |                                                                              |

| Appendix | Title                                                                                                                                                                                                                                                                                                                       | Page                                                                         |

| В        | TEST AND VERIFY PROGRAMS (T&V)                                                                                                                                                                                                                                                                                              | 1 − 1<br>3 − 1<br>1 − 1                                                      |

#### 88A00525A-3

#### LIST OF ILLUSTRATIONS

Title

Page

Number

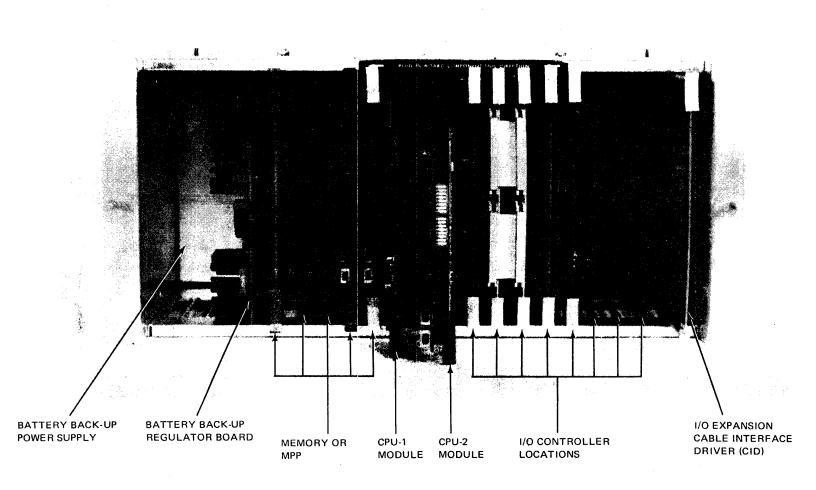

| 2-1    | Jumbo Chassis (Front View)                                | 2-8          |

|--------|-----------------------------------------------------------|--------------|

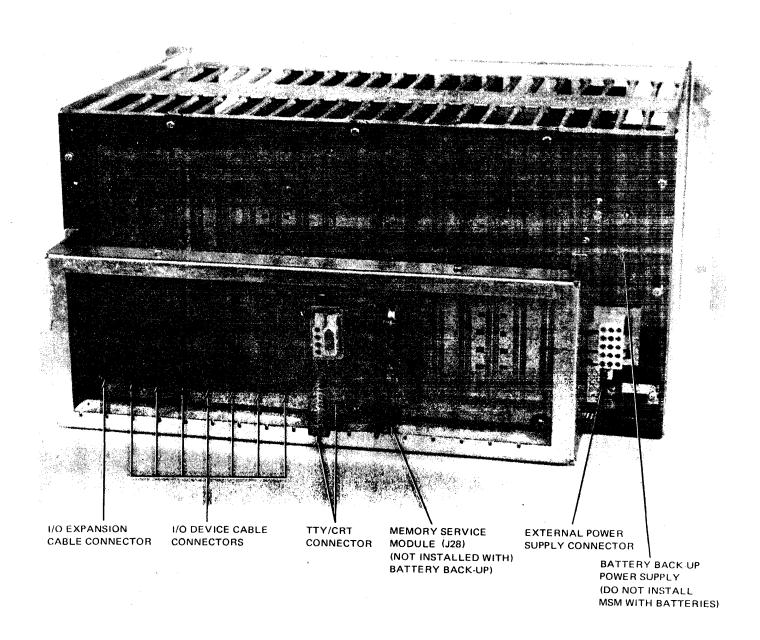

| 2-2    | Jumbo Chassis (Rear View)                                 | 2-9          |

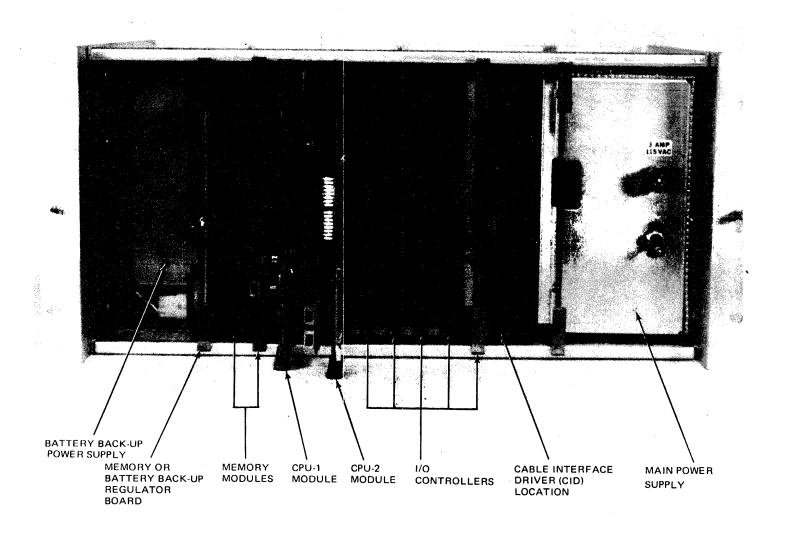

| 2-3    | Compact Chassis (Front View)                              | 2-10         |

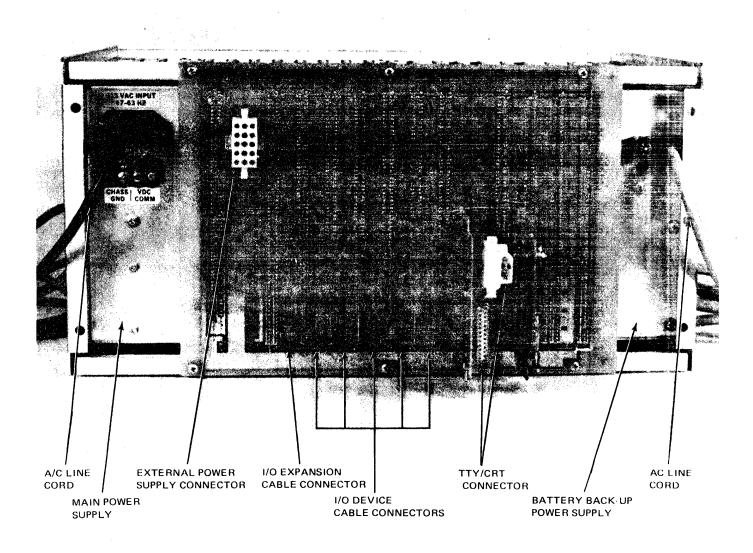

| 2-4    | Compact Chassis (Rear View)                               | 2-11         |

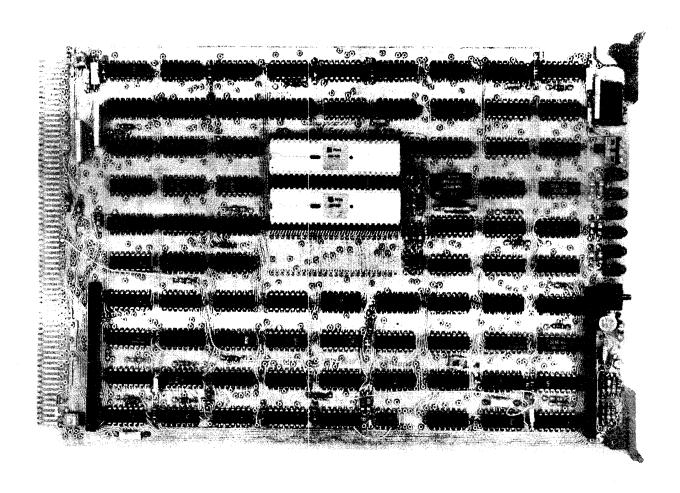

| 2-5    | CPU-1 Module (Without Piggyback Module)                   | 2-12         |

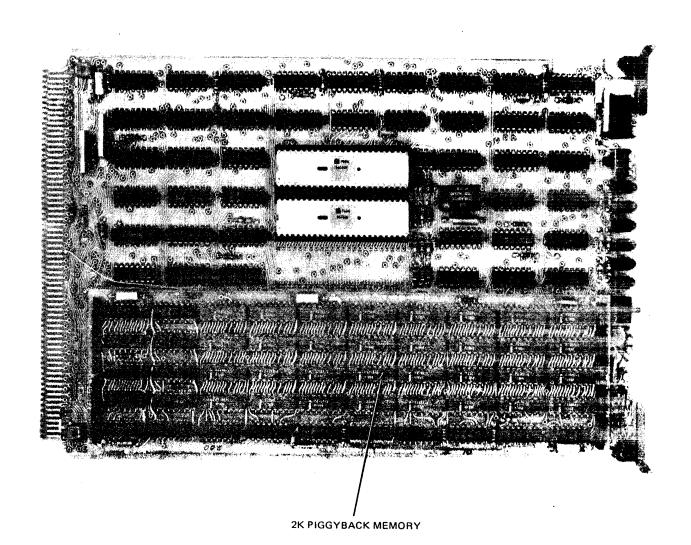

| 2-6    | CPU-1 Module (With Piggyback Memory)                      | 2-13         |

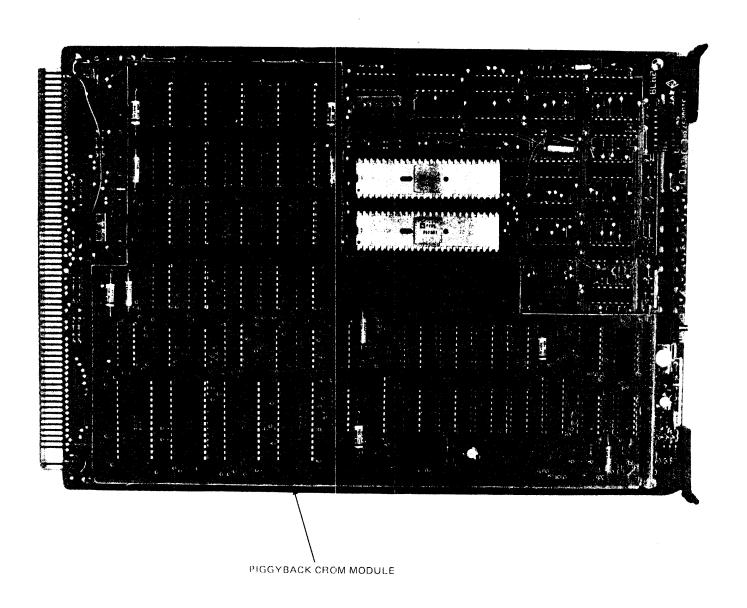

| 2-7    | CPU-1 Module 31D02573A31 (With Piggyback CROM)            | 2-14         |

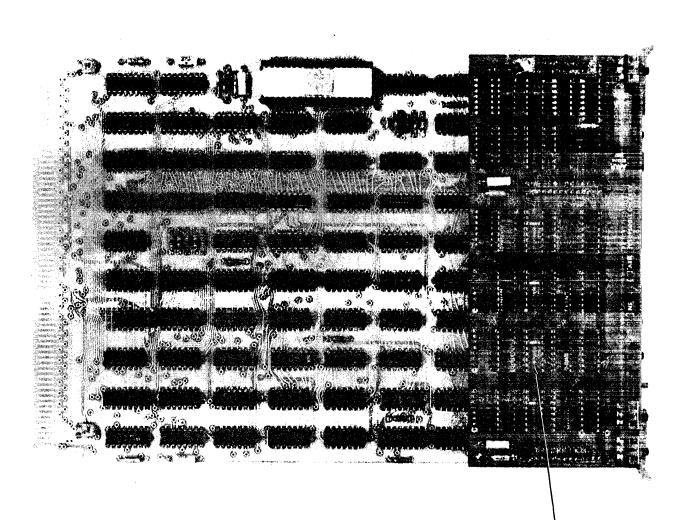

| 2-3    | CPU-2 Module (Without SCI)                                | 2-15         |

| 2-9    | CPU-2 Module (With SCI)                                   | 2-16         |

| 2-10   | 8K Memory Board                                           | 2-17         |

| 2-11   | Memory Address Map                                        | 2-18         |

| 2-12   | 16K Memory Board                                          | 2-20         |

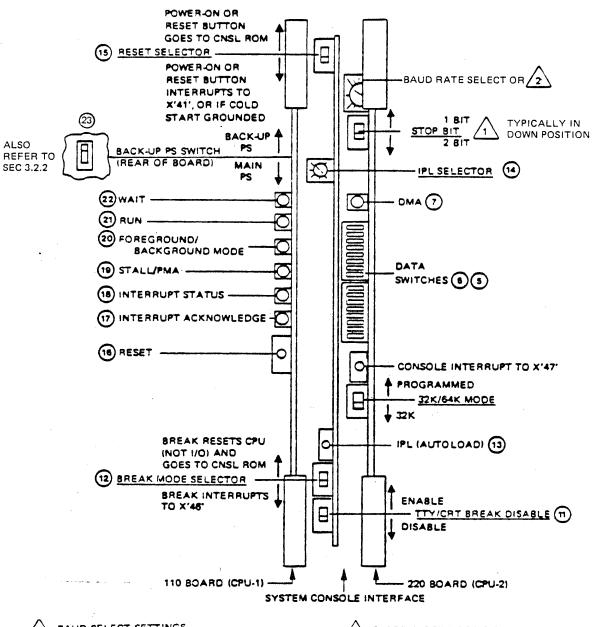

| 3-1    | Late Model CPU Boards, 31D02573A and 31D02574A            | 3∸3          |

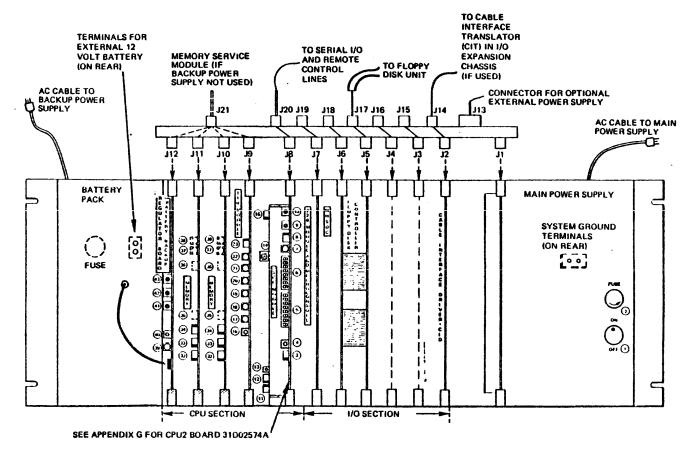

| 3-2    | GA-16/220 System in Compact Chassis (No MPP)              | 3-4          |

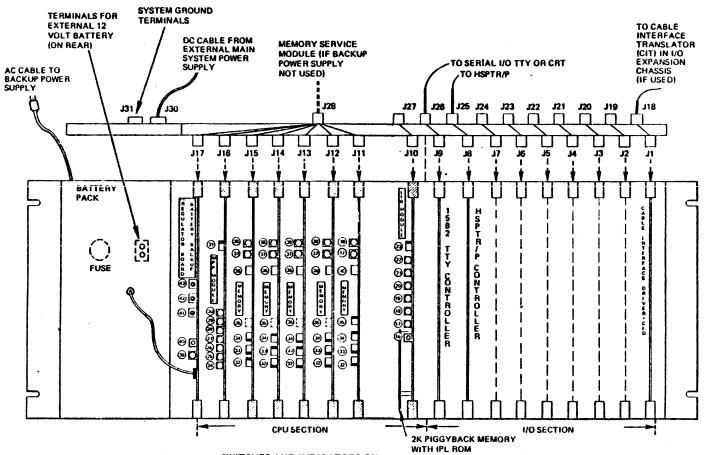

| 3-3    | GA-16/220 System in Jumbo Chassis (With MPP)              | 3-6          |

| A-1    | GA-16/220 System in Compact Chassis (No MPP)              | A-2          |

| A-2    | GA-16/220 System in Jumbo Chassis (With MPP)              | A-4          |

|        | LIST OF TABLES                                            |              |

| Number | Title                                                     | Page         |

| 3-1    | Connector Assignments for Compact Chassis Computer System | 3-5          |

| 3-2    | Connector Assignments for Jumbo Chassis Computer System   | 3-7          |

| 3-3    | GA-16/220 Controls and Indicators                         | 3-8          |

| 3-4    | IPL Selector Switch on SCI Module (GA-16/220)             | 3-15         |

| A-1    | Connector Assignments for Compact Chassis,                | J 13         |

|        | GA-16/220 Computer System                                 | Δ <b>-</b> 3 |

| A-2    | Connector Assignments for Jumbo Chassis,                  | n-3          |

|        | GA-16/220 Computer System                                 | A-5          |

### introduction

The purpose of this document is to briefly describe the configuration and operation of the GA-16/220 Computer System to the new user.

This document presents the information required to install and bring the GA-16/220 to a fully-operational state. The user should also read the applicable reference manuals and documentation for the individual system.

To avoid delays and possible damage to the hardware, the installation and start-up procedure presented herein must be followed.

### system configuration 2

#### 2.1 HARDWARE OVERVIEW

Current production models of the GA-16/110/220 may use either the Jumbo or Compact chassis. (Refer to Appendix A for early configuration system drawings.) Figures 2-1 through 2-4 show the Jumbo and Compact Chassis and identify circuit board slots and major assemblies.

#### 2.1.1 CPU-1 MODULE

The CPU-1 Module (Figures 2-5, 2-6 and 2-7), the heart of the GA-16/220, is a high-speed, microprogrammed LSI microprocessor. The CPU-1 module contains a CROM/RALU chip set that provides the arithmetic and logical operation capabilities of the processor and the microcode instructions.

#### 2.1.2 CPU-2 MODULE

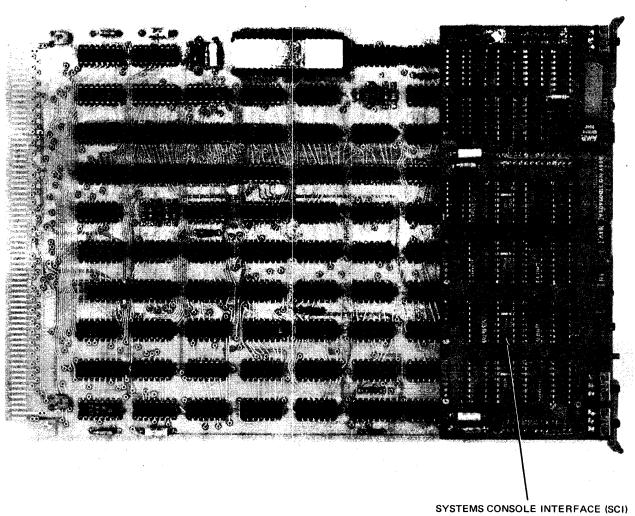

The CPU-2 Module (Figures 2-8 and 2-9) contains the Direct Memory Access (DMA) port, a Serial I/O Controller for a CRT/TTY, the one millisecond (lms) Real-Time Clock, the console interrupt logic, and mini-rocker type manual data entry switches.

#### 2.1.3 MEMORY BOARDS

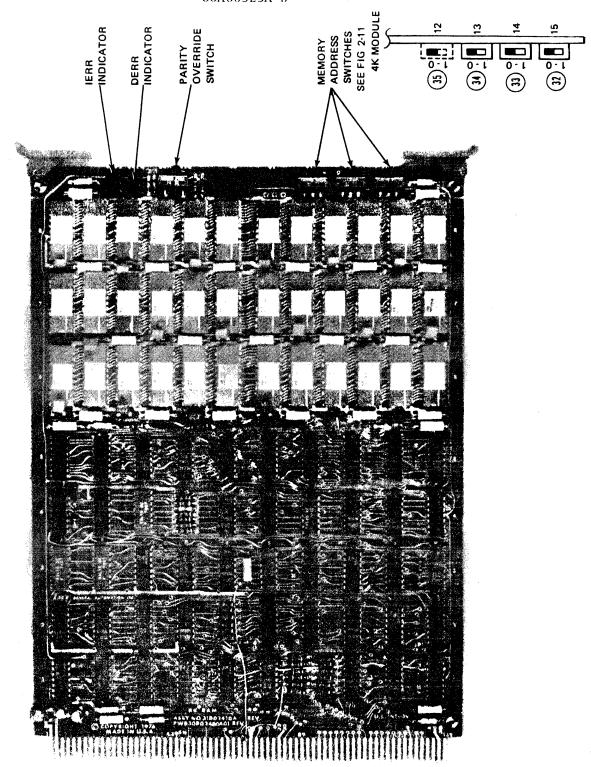

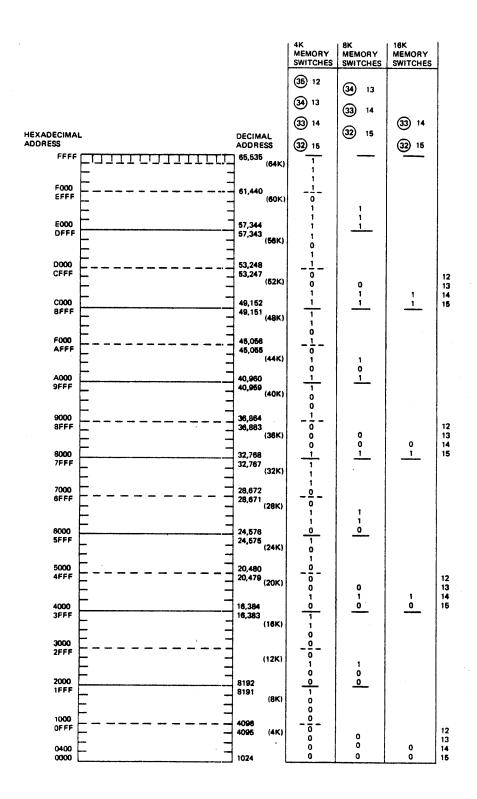

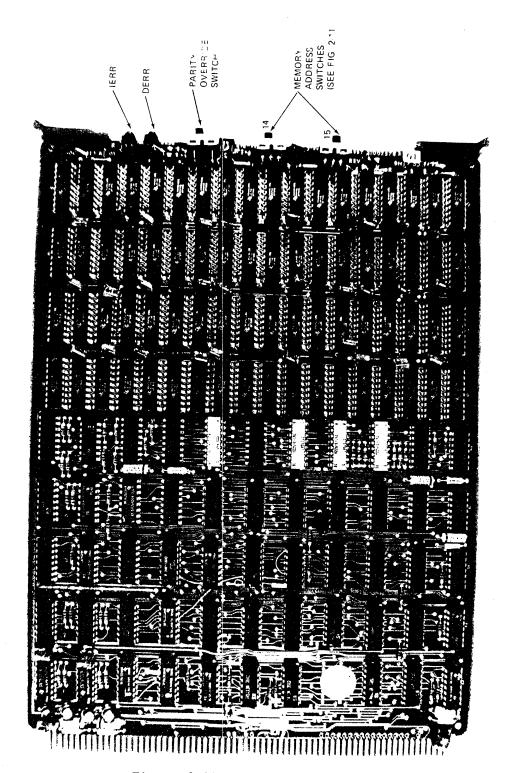

The GA-16/220 computer may be equipped with several types of memory modules (circuit boards). The standard memory module is a dynamic random-access (RAM) memory of 4K, 8K or 16K capacity (see Figures 2-10 and 2-11). The 4K, 8K and 16K modules are identical in size and have a similar switch and indicator configuration; Figure 2-11 shows the address switch configuration. Memory modules are available in the conventional 16-bit word length or in an 18-bit word length for parity error detection (usually used in conjunction with a Memory Parity Protect Module). A Parity Override switch is provided to disable parity error detection, if desired.

#### NOTE

If parity override is not enabled, a parity error will result in a stall condition on data fetches or a repeated attempt to execute instruction with instruction fetches. Indicator lights DERR and IERR are provided to indicate these conditions and are operative if Memory Parity Protect (MPP) is not installed.

In addition to the standard memory, PROM/RAM boards are available as piggyback-mounted options on the CPU-1 Module (see Figure 2-6). The standard piggyback is a 2K static RAM that is set for a start address of 0 or 8K by strapping on the piggyback assembly. (The dynamic RAM requires a periodic refresh write cycle or memory contents are lost; the static RAM does not require the refresh.)

Because RAM memories are solid-state, they require continuous power in order to hold their contents. To ensure that power is maintained, a battery back-up power supply consisting of a rechargeable battery pack and a battery charger may be installed; and an external battery may be connected across the battery pack. If no battery back-up supply is installed, a memory service module (MSM) must be installed in the J-21 connector (Compact Chassis) or the J-28 Connector (Jumbo Chassis) at the rear of the Master Interconnect Board (MIB).

Slide switches on the memory board front edge (refer ahead to Figures 3-2 and 3-3) must be set to provide contiguous address boundaries for the memory boards. The 4K module can be set to beginning addresses on any 4K boundary up to 60K, the 8K module can be set on 8K boundaries up to 56K, and the 16K module can be set on boundaries to 48K.

Figure 2-11 contains a core map that shows how the slide switches are used to set address boundaries.

#### NOTE

The conventions shown in Figure 2-11 are typical of core map representations throughout this manual. Low addresses are shown at the bottom and high addresses at the top. Unless otherwise specified, locations on core map are in hexadecimal numbering system. Hexadecimal locations in text will always be represented as K'nnnn' which corresponds to the CAP-16 assembler convention for defining a hexadecimal number.

The jumbo chassis in Figure 3-3 is shown with four 16K memory boards. The address switches, 32 and 33, are shown set for contiguous boundaries, as follows:

START ADDR

Board in J13 = 00 to 16K

J14 = 16K to 32K

J15 = 32K to 48K

J16 = 48K to 64K

In general, memory must be contiguous from zero and addresses must be provided from X'0040' through X'007F' for the vectored interrupt system to work properly. All address assignments are completely independent of the physical location of the memory module within the CPU chassis.

Contiguous memory space cannot be achieved with an odd number of 4K memory modules unless these modules are paired to make 8K blocks with the odd module assigned to the highest address block in the system.

In like manner, the user of the 2K piggyback memory module cannot provide contiguous memory when combined with a single 4K module or when placed in a system with more than 8K of memory (other than piggyback). This situation is due to the fact that the piggyback memory is limited to starting addresss of either zero or 8K.

Other types of memories that may be installed in a GA-16/220 system include preprogrammed read-only-memories; or a combination of ROM and RAM configured to a user's requirements. In addition to the 2K static RAM, a 64-word IPL ROM (refer to Figure 2-6) may also be installed on the piggyback module; however, the 64-word IPL ROM is not used when the SCI is installed on the CPU-2 module (refer to Figure 2-9).

#### 2.1.4 MEMORY PARITY PROTECT (MPP) MODULE

The MPP module is an option which may be installed in a GA-16/220 system. The MPP provides the system programmer with the capability of protecting selected areas of memory from being changed by a CPU write operation (program protect) or by direct memory write from a DMA or MHSDC controller (DMA protect). The MPP module contains the indicators necessary for identifying memory protect violations, parity errors, and multiple errors. Parity error detection requires the violations, parity errors, and multiple errors. Parity error detection requires the installation of 18-bit memory modules. The MPP module also contains the logic necessary for initiating either a CPU stall condition or a program interrupt via vector X'42' when parity errors occur. The STALL switch is preset before the module is installed to select which action will occur.

For a detailed explanation of the MPP module, refer to the GA-16/110/220 System Reference Manual, Section 5.

#### 2.1.5 CROM MODULE

A CROM module, 31D03005A can be used with the GA-16/220 to enhance the 220 operation when using GA-16/440 software. The CROM module is mounted on CPU-1 board, 31D02573A31, in a piggyback fashion, in the same manner as the RAM memory module (Figure 2-7). CPU-1 board, 31D02573A31 is available as a production item, or a 31D02573A01 CPU-1 board can be converted to the -31 version by installing an ECO (field modification is feasible). Early production models of the CPU-1 board were not assigned the 2573 number, and these boards can not be upgraded to accept the CROM module.

Installation of the CROM piggyback prevents use of the 2K RAM piggyback memory module but poses no other constraints. An installed CROM module is ready to operate, there are no switch settings (unless different capacity memory boards are used) and no software preparation. Although the basic 220 operates successfully with 440 software, using extended instruction software simulation, overhead penalties reduce system efficiency. The new CROM ensures optimum performance.

### 2.1.6 SYSTEM CONSOLE INTERFACE (SCI) MODULE 700 570 600

The system console interface module (Figure 2-9), is an optional module which is plugged into the CPU-2 module. It contains a 256-word, random-access-memory (RAM) and a 512-word, read-only-memory (ROM) that provides an interactive utility program. This program, called the console ROM or SCI program, uses the teletype/CRT capabilities of the CPU-2 module. Using the SCI program, an operator at a TTY/CRT may perform a wide range of utility operations, including the following:

- 1. Display and change registers.

- 2. Display and change memory locations.

- 3. Reset I/O.

- 4. Step through a program in memory.

- 5. Start a program in memory.

- 6. Load or punch a binary program tape.

- 7. Set program traps.

- 8. Set program bias.

A detailed description of the SCI operator commands and system response is contained in the GA-16/110/220 System Reference Manual, Section 3.6. The controls and indicators on the SCI module are described in Table 3-3. The SCI module may also contain an Initial Program Load (IPL) ROM which is described in the following section.

#### 2.1.7 IPL ROMS

GA offers, as normal options, the following Initial Program Load (IPL) ROMs:

Single-device IPL - This IPL runs on a dedicated GA-16/110 and mounts on a 2K piggyback memory. It is a complete, 64-word, mini PGS loader requiring no preamble on the media being loaded. It is an absolute, load-and-go binary loader with checksum.

Version 1 - TTY

Version 2 - High-speed, paper tape reader

2. Multi-device IPL - This IPL ROM is mounted on the GA-16/220 System Console Interface Module. It consists of a 256-word program which provides bootstrap loaders for the TTY, high-speed paper tape reader, card reader, floppy disk, moving arm disk (both fixed and removable platter), and headper-track disk (refer to Table 3-4 for device select list). Each of these bootstrap loaders accesses its designated peripheral to bring a PGS loader into RAM. (The PGS loader must be in the zero sector of a disk or in the preamble of tapes and card decks.) The PGS loader then automatically loads the program and data which must be in the PGS format; i.e., relocatable with checksum and designated start address as described in Section 3.5.1 of the GA-16/110/220 System Reference Manual.

#### 2.1.8 POWER SUPPLIES

Three types of power supply may be used with a GA-16/220 system.

- 1. A built-in supply, for use with self-contained systems, is installed in the compact chassis (Figure 2-3). This supply requires 115V, 47-63Hz input at 230 watts maximum. Its outputs are +5V at 8A (convection cooled) or 18A (fan cooled), +15V at 2A, and 15V at 1A.

- 2. An external supply, which is used for larger GA-16/220 systems, is installed with the jumbo chassis (Figure 2-2). (An external supply may also be used with a compact chassis, if desired.) The external supply input is 115V or 230V, 47-63Hz at 500 watts maximum. Outputs are +5V at 30A, +15V at 5A, and -15V at 5A.

- 3. Battery back-up power supply is used to supply ±5V and +12V to the memory modules (including the 2K piggyback memory), and to switch to batteries (to preserve the contents of memory) when the AC input power stops. A provision is available which permits using an external battery for a greater back-up life span. A manual cutoff switch (40) in Figures 3-1 and 3-2) permits an operator to deliberately disconnect the battery supply; but only when AC power is off.

An indicator 39 monitors memory power. When battery back-up is not installed, a circuit board, designated the memory service module (MSM), must be

inserted in the J-21 or J-28 connector at the rear of the MIB chassis (Figures 2-2, 2-4, 3-1, and 3-2).

Figure 2-1. Jumbo Chassis (Front View)

Figure 2-2. Jumbo Chassis (Rear View)

Figure 2-3. Compact Chassis (Front View)

Figure 2-4. Compact Chassis (Rear View)

Figure 2-5. CPU-1 Module (Without Piggyback Module)

Figure 2-6. CPU-1 Module (With Piggyback Memory)

Figure 2-7. CPU-1 Module 31D02573A31 (With Piggyback CROM)

SYSTEMS CONSOLE INTERFACE (SCI) WITH IPL

Figure 2-8. CPU-2 Module (Without SCI)

WITH IPL

Figure 2-9. CPU-2 Module (With SCI)

Figure 2-10. 8K Memory Board

Figure 2-11. Memory Address Map (Sheet 1 of 2)

#### 88A00525A-B

#### NOTES:

- Each small division represents 400 hexadecimal (X'400') or 1024 decimal (in common terminology, 1K) words of memory.

- 2 4K boundaries are represented by dashed lines.

- 3 8K boundaries are represented by solid lines.

- 4 Hexadecimal and decimal addresses shown specify both lower and upper addresses of each 4K block of memory.

- The decimal number in parenthesis represents the commonly used terminology for defining memory capacity (i.e., a 16K system actually has16,384 words, or an addressing range from 0 through 16,383 words, decimal; or X'0' through X'3FFF' when expressed in hexadecimal).

- 6 Memory switch settings are shown in the order they appear on the memory module, top to bottom. As shown in Figures 3-2 and 3-3) The up position of the switch is 1.

- Memory addresses X'00' through X'C1' are dedicated to the interrupt vector locations or are reserved for Series 16 operating systems which may be used.

- On a GA-16/220, the upper 1K of each memory mode, locations X'7C00' through X'7FFF' when in 32K mode or locations X'FC00' through X'FFFF' when in 64Kmode, is reserved for the SCI Console ROM and IPL ROM. These locations are independent of the amount of memory implemented by memory modules; however, if a memory module is set to include the reserved locations, those locations are not usable by that memory module.

- A 2K static RAM and a 64-word IPL ROM may be installed on the CPU-1 board. This memory, also referred to as the "piggyback" memory, physically occupies the first 2K of memory +64 words or 2K of memory beginning at the 8K boundary (set by jumpers). The static RAM memory module may not be set to a boundary which includes the locations of the piggyback memory.

Figure 2-11. Memory Address Map (Sheet 2 of 2)

Figure 2-12. 16K Memory Board

### start-up procedure 3

This start-up procedure applies to a GA-16/220 system having a System Console Interface (SCI) module, a minimum of 8K of memory, and a TTY or CRT operator input/output device. For operating procedures for systems having configurations other than stated here, refer to the special documentation supplied with the individual system.

#### NOTE

To load the CPU Test and Verify (T&V) program (referenced later in this document) a TTY, with a paper tape reader, or a high-speed paper tape reader must be installed in the system.

#### CAUTION

DO NOT APPLY PRIMARY POWER UNTIL INSTALLATION OF COMPONENT PARTS IS VERIFIED AS CORRECT.

#### 3-1 MODULE (BOARD) INSTALLATION

Prior to applying primary power to the GA-16/220, verify that all the individual boards (CPU, memory, I/O controllers, etc.), are correctly installed in the chassis as shown in Figures 3-1 or 3-2 (or Appendix A). A correctly seated board will be completely vertical (no skew) and solid in its connector on the Master Interconnect Board (MIB).

All modules must have the <u>COMPONENT SIDE TO THE LEFT</u> (when viewed from the front) to avoid possible damage to the board.

#### 3.2 SWITCH SETTINGS

Table 3-3 contains descriptions of the controls and indicators for the GA-16/220 system. The user must gain familiarity with a few "key" controls and indicators to make the system operational (i.e., execute the CPU T&V). These key switch settings are described in Section 3.2.2. For more sophisticated operation, or maintenance, the user should be familiar with all controls and indicators.

#### 3.2.1 SWITCH AND INDICATOR CONFIGURATION

The switches and indicators are shown on Figures 3-1, 3-2 and 3-3. Switch and indicator configuration on the CPU-1 and CPU-2 boards will depend upon the type of CPU boards that are installed. There is a difference between the early model CPU-1 and CPU-2 boards and the later model boards. The late model CPU-1 and CPU-2 boards, 31D02573A and 31D02574A, embody the following changes:

cPU-1 (31D02573A) - The Battery Backup Power Supply Switch 23 faces the rear of the board and is located between board coordinates D1 and E1. On the 31D02573A CPU-1 board, the backup power supply position on this switch is UP. This switch must be set in the backup power supply position if a battery backup supply is installed. If a battery backup power supply is not installed, this switch must be set in the DOWN position. (It is important that the user distinquish between the late model 31D02573A CPU-1 board and the early model boards having numbers 31D02274A and 31D02422A.) In the early model CPU-1 boards, the backup power supply switch must be in the UP position if a backup supply is not installed and in the DOWN position if it is installed.

#### CAUTION

If AC power is off with the backup power supply in the main power supply position and a battery backup supply is installed, the battery will drive the main +5V CPU circuit. The result: a rapidly discharged battery and possible damage to the backplane etch.

- CPU-2 (31D02574A) a. A rotary hex-position switch 2 selects 1 of 15 available baud rates for serial I/O devices.

- b. A STOP BIT select switch \( \bigl) selects a one- or a two-bit "STOP BIT" for serial I/O. Unless otherwise specified, the STOP BIT switch should be in the DOWN position to select a two-bit "STOP BIT".

- c. The TTY BAUD, 9600, and 110 (8, 9, and 10) baud rate controls described for the early model CPU-2 board are not present on the late model 31D02574A board.

Figures 3-2 and 3-3 show the complete switch and indicator configuration for a GA-16/220 with early model CPU boards. Figure 3-1 shows the switch and indicator configuration for the late model CPU-1 and CPU-2 boards.

Figures 3-2 and 3-3 show 8K memory boards; each 8K board has three address boundary switches. The number of address boundary switches on a memory board depends upon the board capacity. This is demonstrated in Figure 2-11.

| ~ | UD SELEC<br>SWITCH<br>SETTING | CT SETTINGS<br>BAUD<br>RATE | SWITCH<br>SETTING | BAUD | PLACE IN DOWN POSITION TO SELECT 2-BIT STOP BIT WHEN USING A TTY OR MOST |

|---|-------------------------------|-----------------------------|-------------------|------|--------------------------------------------------------------------------|

|   | 0                             | NOT USED                    | 9                 | 1200 | OTHER SERIAL I/O DEVICES.                                                |

|   | 1                             | 50                          | A                 | 1800 |                                                                          |

|   | 2                             | 75                          | 8                 | 2400 |                                                                          |

|   | 3                             | 110                         | C                 | 3800 |                                                                          |

|   | 4                             | 134.5                       | ٥                 | 4800 |                                                                          |

|   | 5                             | 150                         | E                 | 7200 |                                                                          |

|   | 6                             | 300                         | F                 | 9600 |                                                                          |

|   | 7                             | 600                         |                   |      |                                                                          |

|   | R                             | 900                         |                   |      |                                                                          |

Figure 3-1. Late Model CPU Boards, 31D02573A and 31D02574A

MPP)

Figure

SWITCHES AND INDICATORS ON CPU-1 AND CPU-2 ARE FOR EARLY MODEL BOARDS. FIGURE 3-1 SHOWS LATE MODEL CPU-1 (31002573A) AND CPU-2 (31002574A) BOARDS.

Table 3-1. Connector Assignments for Compact Chassis Computer System

|          | Front/Module (220)                                                                       |                   | Rear/Interface (220)                                                                            |

|----------|------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------|

| J1<br>J2 | Main power supply Cable Interface Driver (CID)                                           | -                 | AC input connector and system grounding terminals on power supply.                              |

| J3<br>J4 | I/O controllers or shorting boards.                                                      | J13               | Connector for optional external power supply cable.                                             |

| J5<br>J6 | Shorting boards are used in empty slots between controllers or CID to maintain interrupt | J14               | Cable to I/O expansion chassis (6-foot maximum).                                                |

|          | chain continuity.                                                                        | J15<br>J16        | Paddleboards and cables interfacing controllers (in                                             |

| J7 )     | MHSDC controller, if used, should go into J7.                                            | J17<br>J18<br>J19 | J3 through J7) to peripheral devices.                                                           |

| J8       | CPU-2 module with optional System Console Interface.                                     | J20               | Serial I/O paddleboard with connector to TTY or CRT also                                        |

| J9       | CPU-1 module with optional piggyback memory.                                             |                   | provides access to cold-start (CLDS-) jumpers and remote control lines (IPLSW-, PFD-,           |

| J10      | Memory module, DMT controller, or Memory Parity Protect                                  | ·                 | RSET-, RUN-).                                                                                   |

| }        | module.                                                                                  | J21               | Memory Service Module if battery                                                                |

| J12      | J12 also used for battery backup regulator board.                                        |                   | backup power supply is not used. J21 also may be used as interface for external DMT controller. |

| -        | Backup power supply battery pack (use regulator board in J12).                           | -                 | AC cord for backup power supply.                                                                |

|          |                                                                                          | -                 | Terminals for external 12-volt battery on rear of battery pack.                                 |

SWITCHES AND INDICATORS ON CPU-1 AND CPU-2 ARE FOR EARLY MODEL BOARDS. FIGURE 3-1 SHOWS LATE MODEL CPU-1 (31D02673A) AND CPU-2 (31D02674A) BOARDS

Table 3-2. Connector Assignments for Jumbo Chassis Computer System

| Front/Module (220)                     |                                                                                                                                                           | Rear/Interface (220)                                 |                                                                                                                                                               |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1                                     | Cable Interface Driver (CID).                                                                                                                             | J18                                                  | Cable to I/O expansion chassis (6-foot maximum).                                                                                                              |

| J3<br>J4<br>J5<br>J6<br>J7<br>J8<br>J9 | Shorting boards are used in empty slots between controllers or CID to maintain interrupt chain continuity.  MHSDC controller, if used, should go into J9. | J19<br>J20<br>J21<br>J22<br>J23<br>J24<br>J25<br>J26 | Paddleboards and cables interfacing I/O controllers (in J2 thru J9) to peripheral devices.                                                                    |

| J10                                    | CPU-2 module with optional System Console Interface.  CPU-1 module with optional piggyback memory.                                                        | J27                                                  | Serial I/O paddleboard with connector for TTY or CRT. Also provides access to coldstart (CLDS-) jumper, and remote control lines (IPLSW-, PFD-, RSET-, RUN-). |

| J12<br>J13<br>J14<br>J15<br>J16        | Memory module, DMT controller or Memory Parity Protect module.  J17 also used for battery backup regulator board.                                         | J28                                                  | Memory Service Module if battery backup power supply is not used. J28 also may be used as interface for external DMT controller.                              |

| J17 <b>)</b><br>-                      | Backup power supply battery pack                                                                                                                          | J30                                                  | Power cable from external power supply.                                                                                                                       |

|                                        | (use regulator board in J17).                                                                                                                             | J31                                                  | System grounding terminals.                                                                                                                                   |

|                                        |                                                                                                                                                           | -                                                    | AC cord for backup power supply.  Terminals for external 12-volt battery on rear of battery pack.                                                             |

#### 88A00525A-B

Table 3-3. GA-16/220 Controls and Indicators (Sheet 1 of 7)

| Кеу      | Label                                       | Description and Function                                                                                                                                                                                                                                                                                         |

|----------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u> </u> | STOP<br>BIT<br>Figure 3-1<br>Only           | Selects one- or two-bit "STOP BIT" for serial I/O. A two-bit "STOP BIT" (switch in DOWN position) must be selected for TTY and most other serial I/O devices.                                                                                                                                                    |

| <u>2</u> | BAUD RATE<br>SELECTOR<br>Figure 3-1<br>Only | Selects 1 of 16 available baud rates for serial I/O. Refer to Figure 3-1. 110 baud should be selected for the TTY.                                                                                                                                                                                               |

| (PS)     | ON<br>OFF                                   | The main power switch causes power to be applied to CPU and I/O controllers. Power is also applied to memory modules, memory service module is installed.                                                                                                                                                        |

| (PS)     | FUSE                                        | The fuse holder allows replacement of main power supply fuse.                                                                                                                                                                                                                                                    |

| (CPU-2)  | 32K<br>PGM                                  | The 2-position switch selects memory addressing mode. When in the 32K position, program addressing limit is 32K words. When in the PROGRAM position, either 32K or 64K mode is selected by a program which sets the memory mode mask word.                                                                       |

| (CPU-2)  | CNSL<br>INT                                 | Console interrupt pushbutton, when pressed, causes a program interrupt through vector X'47' if, 1) the console interrupt bit in the internal mask word is set and, 2) the interrupt system is enabled.                                                                                                           |

| (CPU-2)  | 15→8                                        | These miniature binary switches are called the console switches.                                                                                                                                                                                                                                                 |

| (CPU-2)  | 7 → 0                                       | The console switches may be read by an RCSM or RCSR instruction in a program. This capability permits writing programs which allow data entry and control via these switches. When switch is in position labeled OPEN, bit is set to 0.                                                                          |

| (CPU-2)  | DMA ACK                                     | This indicator may blink periodically when direct memory access cycle stealing is occurring. It may illuminate continuously if very high DMA activity is in progress or if there is a malfunction. In a GA-16/220 system, DMA activity is controlled by the multiple high-speed data channel (MHSDC) controller. |

Table 3-3. GA-16/220 Controls and Indicators (Sheet 2 of 7)

| Key     | Label                                    | Description and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | TTY BAUD<br>Figures<br>3-2 & 3-3<br>Only | Does not apply to late model CPU-2 board (31D02474A). The 2-position switch changes the baud rate of the built-in serial I/O controller to accommodate either a teletype (Model 33 automatic send receive, ASR, or equivalent) at 110 baud or a CRT terminal at 110 or 9600 baud.                                                                                                                                                                                                                                                                                                                                                                          |

| (CPU-2) | 9600<br>Figures<br>3-2 & 3-3<br>Only     | Does not apply to late model CPU-2 board (31D02574A). This screw adjustment permits fine adjustment of the 9600 baud transmission rate. It is adjusted only when the BAUD switch (8) is in the 110 position.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (CPU-2) | 110<br>Figures<br>3-2 & 3-3<br>Only      | Does not apply to late model CPU-2 board (31D002574A). This screw adjustment permits fine adjustment of the 110 baud transmission rate. It is adjusted only when the BAUD switch 8 is in the 110 position.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (SCI)   | BKDS*                                    | Break Disable Switch - The 2-position switch enables or disables the TTY break capability. When switch is in the break-disable (BKDS) position, TTY breaks are ignored. When in the other position, TTY break is enabled so when a TTY operator presses the BREAK key on a teletype or CRT (provided unit is equipped with this key) either a processor (CPU) reset or an interrupt occurs, depending on the setting of the BKINT switch 12.                                                                                                                                                                                                               |

| (SCI)   | BKINT*                                   | Break Mode Switch - The 2-position switch sets the break mode for TTY or CRT, provided BKDS switch (1) is set so that break mode is enabled. When BKINT switch is set to break-interrupt position (BKINT), a TTY break causes a non-inhibitable interrupt, via vector location X'46' (provided CPU is not operating under the SCI Console ROM program or the IPL ROM). Registers and status are saved in locations in the SCI program RAM. When switch is not in the BKINT position, a TTY break initiates a break reset, which causes control to be transferred to the Console ROM and registers and status are not saved. I/O controllers are not reset. |

<sup>\*</sup>Label refers to switch position. See description for function PL name.

Table 3-3. GA-16/220 Controls and Indicators (Sheet 3 of 7)

| Key     | Label   | Description and Function                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| (SCI)   | IPL     | Pushbutton initiates initial program load (IPL). When pressed, control is passed to the IPL ROM installed on the SCI module, and program loading occurs from a peripheral device. Selection of the peripheral device is accomplished by setting the IPL SEL switch (14) to the appropriate position for the IPL device installed with the system. This function may be remotely controlled, via IPLSW line, or at auto-restart with cold start line at ground. |  |  |

| (SCI)   | IPL SEL | The IPL selector switch is a 16-position rotary switch. The switch is used to preselect which I/O device will be the source of an IPL when the IPL switch (13) is pressed. Load-and-go operation is selectable for all devices; while load-and-stop operation may be selected for teletype, high-speed paper tape reader, or card reader. Table 3-4 specifies the device selections.                                                                           |  |  |

| (SCI)   | CNSL*   | (Reset Selector). The 2-position switch determines both the function of the CPU RESET button (16) and an autorestart operation, when power is applied. When in the console position (CNSL), the CPU and I/O are reset and control is transferred to the Console ROM. If in the other position the status of the cold-start line, (CLDS) determines the operations as described for RESET push button on the CPU-1 module (16).                                 |  |  |

| (CPU-1) | RESET   | Pushbutton resets the CPU and the I/O system, and causes control to be transferred in accordance with the Reset Selector Switch (Console Mode) as follows:  Reset-Selector Switch Console Mode: Control is transferred to the Console ROM program.  Non-Console Mode: Control is transferred via auto-restart vector (Location X'41') to the contents of X'41'. (Provided CLDS- line is not grounded.)                                                         |  |  |

| (CPU-1) | IACK    | Interrupt acknowledge indicator blinks when control has passed to a routine, via an interrupt vector. It normally blinks so rapidly as to be barely visible. If continuously illuminated, it indicates that the control has not returned from the interrupt processing routine, a "hung up" condition.                                                                                                                                                         |  |  |

<sup>\*</sup>Label refers to switch position. See description for function PL name.

Table 3-3. GA-16/220 Controls and Indicators (Sheet 4 of 7)

| Кеу            | Label | Description and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (B)<br>(CPU-1) | ISE   | Interrupt system enabled indicator is illuminated when the ISE flip-flop is set; which means that the inhibitable interrupt system is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| (CPU-1)        | OMA   | This indicator (also referred to as the OMA stall indicator) is illuminated when the operator's monitor alarm (OMA) has timed out. The OMA must have been initially turned on by a PMA instruction. When the OMA indicator illuminated, the RUN indicator (21) is extinguished and the CPU is in an idle state. To recover from an OMA, the operator must press an idle state. To recover from an OMA, the operator must press the RESET button (16).                                                                                                                                                                                                       |

| (CPU-1)        | FGND  | Foreground indicator is illuminated when the foreground registers are used, and extinguished when background registers are used. Refer to instructions BMS and FMS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (CFU-1)        | RUN   | The RUN indicator is illuminated when the CPU is in the run mode. If the WAIT indicator (22) is also illuminated, the CPU is in a wait condition as a result of executing a WAIT instruction. If MPP indicators (27) through (30) are illuminated, memory parity error has caused the stall. In order for an MPP stall to occur, the STALL switch (31) must be in the stall position. To recover, the user must RESET the system. If the run indicator is extinguished, the system is in idle.  NOTE: If 18-bit memories are installed without installation of MPP module, a stall condition may occur if the parity override switch (36) is not set. Refer |

|                |       | to description of 36, 37, and 38 in this table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (CPU-1)        | WAIT  | Wait indicator illuminates when a WAIT instruction has been executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 3-3. GA-16/220 Controls and Indicators (Sheet 5 of 7)

| Key         | Label | Description and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (GPU-1)     | -     | In the 31D02573A board, this unlabeled 2-position battery backup switch faces to the rear of CPU-1 module; it is located between coordinate D1 and E1. In the backup power supply position (UP), +5VB refresh power for the memories (including the pigyback RAM) originates in the backup power supply or from batteries (when AC power is disconnected). When switch is not in backup position, the refresh power is obtained from the main power supply. When backup power supply is not installed, a memory service module must be installed in the J18 or J21 rear connector (Figures 3-1 and 3-2) to obtain power from the main power supply for the RAM memories. On CPU-1 boards other than 31D02573A (early models) the battery backup switch is on the board front edge; and the backup power supply position is DOWN. |

| (MPP)       | DPT   | The DMA write protect indicator, when illuminated, indicates that an attempt has been made by DMA or DMT port 1 to write into a memory area (via the high-speed data channel) which has been DMA-protected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (MPP)       | ME    | Multiple error indicator illuminates when a second error occurs before software can process a previous error. Other indicators also may be illuminated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 26<br>(MPP) | PPT   | Program write protector indicator, illuminates when a program has attempted to write data in a memory area which has been program-protected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| (MPP)       | LPB   | Lower parity bit indicator shows the contents of parity bit for the lower byte of a memory word (illuminated = 1). Content of bit must be compared with the lower byte to determine if error has occurred; even parity is error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 28<br>(MPP) | UPB   | Upper parity bit indicator shows contents of the parity bit for the upper byte of a memory word (illuminated = 1). Content of bit must be compared with the upper byte to determine if error has occurred; even parity is error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 29<br>(MPP) | DPY   | DMA parity indicator illuminates when a parity error is detected during a DMA transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 3-3. GA-16/220 Controls and Indicators (Sheet 6 of 7)

| Key            | Label                | Description and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (MPP)          | PPY                  | Program parity indicator illuminates when a parity error is detected when a program reads a memory location (data or instruction fetch).  NOTE: Indicators 24 through 30 remain illuminated until MPP status is reset under software control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (MPP)          | STALL                | The 2-position switch faces to the rear of the MPP module and is preset prior to operation. This switch determines CPU action when a DMT, DMA or CPU parity error occurs. When switch is in STALL position, the memory bus is forced to a busy state, thereby, halting the CPU. When not in the STALL position, control is passed to a routine, via non-inhibitable interrupt vector X'42'. (All non-parity errors pass control, via X'42', regardless of the setting of STALL switch. The routine must determine type of error.)                                                                                                                                                                                                                                                                                                                                                                                                              |

| 99<br>99<br>99 | 15<br>14<br>13<br>12 | 2-position switches on the memory modules set the memory module address boundaries as described in Section 2.1.3 and Figure 2-11. The number of switches present depend on the memory module capacity (8K boards are shown in Figures 3-2 and 3-3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (MEM)          | PAR<br>O VRD         | The 2-position switch is installed only on 18-bit memories. This switch is effective only if MPP module is not installed; it enables parity override, which disables parity error detection, when in DOWN position. When in UP position, parity error detection occurs. Action upon a parity error depends on whether or not an MPP module is installed.  1. When MPP module is not installed and switch is in the UP position, a parity error will cause a CPU STALL condition on data fetches. The DERR and IERR indicators will identify the error.  2. When an MPP module is installed, switch may be in either position and parity errors will be identified by the LPB, UPB, DPY, and PPY indicators (27) through (30) on the MPP module. Detection is enabled by a programmed I/O instruction to the MPP module. Action taken upon parity error detection then is determined by the setting of the stall switch (31) on the MPP module. |

Table 3-3. GA-16/220 Controls and Indicators (Sheet 7 of 7)

| Key           | Label    | Description and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| (37)<br>(MEM) | DERR     | The data error indicator illuminates (in 18-bit memories) when a parity error occurs on a data fetch. The data comes out as X'0000'. This condition is cleared by a system reset or by a break reset (see description of 16 and 12).                                                                                                                                                                                                                                                                                             |  |  |

| 33            | IERR     | This instruction error indicator (in 18-bit memories) illuminates when a parity error occurs on an instruction fetch. The instruction comes out as X'0000' (WAIT). This condition is cleared by a system reset or by a break reset.  NOTE: If the Memory Parity Protect (MPP) option is included in a system, neither the IERR nor DERR indicators will illuminate unless there is a high failure rate, assuming the MPP is managing the memory under program control.                                                           |  |  |

| (BAT)         | -        | Unlabeled indicator illuminates when power (either from AC line or from batteries) is applied to the memory modules. Light is extinguished when manual cut-off button (38) is pressed, (or if batteries are exhausted), provided AC power is disconnected from the auxiliary power supply.                                                                                                                                                                                                                                       |  |  |

| (BAT)         | -        | Unlabeled pushbutton provides manual cut-off of battery power to memory modules. Pressing this button will have no effect unless AC power is disconnected from auxiliary power supply. If AC power is disconnected, pressing this button will cut off power to memories. Power will not be restored to memories until AC power is reconnected.  NOTE: Application of power to auxiliary power supply is independent of built-in main power supply switch (1), or other means of controlling power to external main power supply. |  |  |

| (BAT)         | BAT CHG* | This control is used to adjust the charge voltage to the battery pack to maintain a 0.4 ampere rate (maximum).                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| (BAT)         | 5VB      | This control is used to adjust the +5 volt regulator. (Specification 82S00629A.)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| (3AT)         | VDD      | This control is used to adjust the +12 volt regulator. (Specification 82S00629A).                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

<sup>\*</sup>Refer to Specification 82S00629A for adjustment procedure.

Table 3-4. IPL Selector Switch on SCI Module (GA-16/220)

| Position   | Device                                       |  |  |

|------------|----------------------------------------------|--|--|

| 0          | Teletype (Load and Go)                       |  |  |

| 1          | High-Speed Paper Tape Reader (Load and Go)   |  |  |

| 2          | Card Reader (Load and Go)                    |  |  |

| . <b>3</b> | 3347 Disk (Load and Go)                      |  |  |

| 4          | 3346 Removable Disk (Load and Go)            |  |  |

| 5          | 3349 Floppy Disk (Load and Go)               |  |  |

| 6          | 3343 Disk (Load and Go)                      |  |  |

| 7          | 3346 Fixed Disk (Load and Go)                |  |  |

| 8          | 3342 Disk (Load and Go)                      |  |  |

| 9          | 3341 Disk (Load and Go)                      |  |  |

| A          | Teletype (Load and Stop)                     |  |  |

| В          | High-Speed Paper Tape Reader (Load and Stop) |  |  |

| С          | Card Reader (Load and Stop)                  |  |  |

| D          | Option                                       |  |  |

| E          | Option                                       |  |  |

| F          | Option                                       |  |  |

NOTE: Refer to description of IPL SEL switch (14) in Table 3-3.

#### 3.2.2 INITIAL SWITCH SETTINGS

- 1. BAUD RATE SELECTOR 2: This switch should be set to the 110 baud position for a TTY, or to the baud rate required for a CRT or alternate serial I/O device.

- 2. Memory Address Switches 32, 33, 34, 35: Set these switches to provide contiguous memory addressing as explained in Section 2.1.3.

- 3. PAR OVRD (36): Set this switch in the UP position. A parity error will stall the machine if no MPP is installed, otherwise, the resulting action is a function of the MPP board. (Refer to explanation of PAR OVRD switch in Table 3-3.)

- 4. Unlabeled (2): This switch has two positions: backup power supply and main power supply. The switch MUST be set in the backup power supply position if a battery backup power supply is installed. If a battery backup unit is not installed, this switch must be in the main power supply position.

On the 31D02573A CPU-1 board, the backup power supply position is UP. On other, early model CPU-1 boards, the backup power supply position is DOWN. Refer to item (23) in Table 3-3.

#### CAUTION

If AC power is off with this switch in the main power supply position (non-backup) and the battery backup unit is installed, the battery will attempt to drive the main +5V CPU circuit, and will, therefore, discharge rapidly. The +5V battery output is not capable of driving the +5V logic for both CPU and memories, since it is only intended for memory backup power. In addition to a discharged battery, this situation may also result in damage to the backplane etch.

#### 3.3 INITIAL POWER-UP

- If a battery backup unit is installed in the system, AC primary power should be applied to it first. The unlabeled indicator (39), will light indicating the backup unit is functioning.

- 2. Apply primary AC power to the system supply. If the Reset Selector (15), Break Disable (11) and Break Mode (12) switches are set as:

RESET SELECTOR (5): Console Position ('UP")

BREAK DISABLE (11): Enable Position ("UP")

BREAK MODE ("DOWN")

The TTY or CRT should output a CR/LF when power is applied. The "FGND" 20 and "RUN" 21 indicators should be lit at this time.

3. Pushing "RESET" (6) will cause the TTY or CRT to output a CR/LF. The same will occur if the AC power is switched off and then back on again.

## 3.4 EXECUTING THE CPU T&V

The user should now refer to the CPU T&V listing (Model 5T10A) for loading and executing procedures for the GA Series-16 processor T&V. The T&V listing contains all the remaining necessary information to load and execute the CPU T&V.

## additional documentation 4

#### 4.1 ADDITIONAL T&VS AND UTILITY PROGRAMS

#### 4.1.1 CPU RELATED T&VS

The following CPU related T&Vs may also be loaded and executed in a similar manner to the CPU T&V if desired:

- MPP T&V 5T110A

- TTY T&V 5T100A

- Memory T&V 5T14A

#### 4.1.2 PERIPHERAL T&V

The standard SPC-16 peripheral T&Vs have been updated to be applicable to GA-Series computers. To facilitate loading and operating these programs a peripheral T&V Reference Manual (94A01519A) is provided. This manual should be used in conjunction with the particular peripheral T&V manual and listing for full understanding of the operation.

A list of the applicable peripheral T&Vs is provided in Appendix B.

#### 4.2 STAND-ALONE UTILITIES

A description of the GA-16/220/330 Stand-Alone Utility programs is provided in Document Number 94A01531A, GA-16/220/330 Stand-Alone Utilities Manual.

#### 4.3 BECOMING AN EXPERIENCED 220 USER

After successfully loading and executing the CPU T&V (Section 3), the user should now become intimately familiar with the System Reference Manual, GA Document Number 88A00508A. Once this is achieved, the user may then become familiar with the additional documentation pertinent to the particular system.

# early GA-16/220 configuration A

Figure A-1 shows the configuration of the compact chassis, built prior to November, 1976. The major changes, made in currently shipped units, provide additional space between CPU-1 and CPU-2 modules to accommodate a redesigned SCI module. (See Section 3, Figure 3-2, System Reference Manual.) Table A-1 shows connector assignments for early compact chassis.

Figure A-2 shows the configuration of jumbo chassis built prior to October, 1976. To provide more space between CPU-1 and CPU-2 modules to accommodate redesigned SCI module (see Section 3, Figure 3-4, System Reference Manual), an I/O slot has been eliminated in currently shipped units. Table A-2 shows connector assignments for early jumbo chassis.

The circled numbers are keyed to Table 3-3, Section 3, for descriptions of controls and indicators.

Figure A-3 shows the priority interrupt chain wiring for early compact and jumbo chassis.

Figure GA-16/220 System ij Compact Chassis (No MPP)

Table A-2. Connector Assignments for Jumbo Chassis, GA-16/220 Computer System

| Front/Module (220)                                                                                                                                                                    | Rear/Interface (220)                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|