# GENERAL® AUTOMATION

GA-16/220/230/240 addendum

### NOTICE

The information contained in this document is subject to change without notice.

General Automation makes no warranty or representation with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. General Automation shall not be liable for errors contained herein.

General Automation assumes no responsibility for the use or reliability of its software on equipment that is not furnished by General Automation.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another program language without the prior written consent of General Automation.

# GA-16/220/230/240 addendum

# **GENERAL AUTOMATION**

1055 South East Street Anaheim, California 92805 (714) 778-4800 TWX 910-591-1695

© 1980, General Automation, Inc.

Prepared on GA Econotext system

# **RECORD OF REVISIONS**

Title: GA-16/220/230/240 Addendum

Document Number:

88A00654A

| DATE   | ISSUE          |

|--------|----------------|

| Sep 80 | Original Issue |

| ·      |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

|        |                |

### FOR EWORD

The purpose of this GA-16/220/230/240 Addendum is to supplement the current issues of the following GA publications:

| Document No. | <u>Title</u>                          |

|--------------|---------------------------------------|

| 88A00508A    | GA-16/110/220 System Reference Manual |

| 88A00509A    | GA-16/110/220 Maintenance Manual      |

| 88A 00 52 5A | How To Use Your GA-16/220             |

This addendum describes the differences between the GA-16/220 microcomputer and the GA-16/230/240 microcomputer. The major part of the information supplied in the 110/220 manuals specified above is applicable to the GA-16/230/240 and need not be repeated in this document.

# TABLE OF CONTENTS

| Section | Title                                        | Page                            |

|---------|----------------------------------------------|---------------------------------|

| 1       | INTRODUCTION  1.1 GA-16/220 VS GA-16/230/240 | 1-1<br>1-1<br>1-2<br>1-2<br>1-2 |

| 2       | HYPAK MEMORY WITH ECC                        |                                 |

| 2       | 2.1 HYPAK MEMORY                             | 2-1<br>2-1                      |

|         | 2.1.1 MEMORY BOARD CONFIGURATIONS            | 2-1                             |

|         | 2.1.2 MODULE ADDRESS SWITCH S1               |                                 |

|         | 2.1.3 DEPOPULATED MEMORY SWITCH S2           | 2 <b>-</b> 2                    |

|         | 2.1.4 ECC STATUS PRIORITY                    |                                 |

|         |                                              | 2-3                             |

|         |                                              | 2-3                             |

|         | 2.1.5.1 Read                                 | 2-3                             |

|         |                                              | 2-4                             |

|         |                                              | 2-4                             |

|         |                                              | 2-4                             |

|         |                                              | 2-7.                            |

|         | 2.1.6.1 Memory Module to Data Bus and MMS    | 2-7                             |

|         | 2.1.6.2 ECC to Memory Interface              | 2-7                             |

|         | 2.1.7 MEMORY POWER                           | 2-7                             |

|         |                                              | 2-12                            |

|         | 2.2.1 OPERATING MODES                        | 2-12                            |

|         | 2.2.1.1 Error Correction Mode OFF (Mode 0)   | 2-13                            |

|         | 2.2.1.2 Normal 1 Mode                        | 2-13                            |

|         | 2.2.1.3 Normal 2 Mode                        | 2-13                            |

|         | 2.2.1.4 Write Data Only Mode (Mode 4)        | 2-13                            |

|         | 2.2.1.5 Input Status Mode (Mode 3)           | 2-14                            |

|         | 2.2.2 ECC MODULE STATUS INDICATORS           | 2-16                            |

|         | 2.2.3 ERROR CORRECTION INTERRUPTS            | 2-16                            |

|         | 2.2.3.1 Correctable Error Interrupt          | 2-16                            |

|         | 2.2.3.2 Non-Correctable Error Interrupt      | 2-16                            |

|         | 2.2.4 STATUS WORDS                           | 2-17                            |

|         | 2.2.4.1 MMS Status Word                      | 2-17                            |

|         | 2.2.4.2 MPP Status Word                      | 2-17                            |

| 3       | MEMORY MANAGEMENT SYSTEM                     | 3-1                             |

| -       | 3.1 INTRODUCTION                             | 3-1                             |

|         | 3.2 MMS INTERFACE                            | 3-2                             |

|         | 3.3 MMS FUNDAMENTALS                         | 3-4                             |

|         | 3.4 MEMORY MAPPING                           | 3-11                            |

|         | 3.4.1 MAP CELL FORMAT                        | 3-13                            |

|         | 3.4.2 MAP DATA WRITING                       |                                 |

|         | 3.4.3 MMS MAP PAGES O AND 63                 | 3-14                            |

|         | JOTO J PINI PART FAGED U RIN D               | 3-1 3                           |

| Section |      | Title                                     | Page |

|---------|------|-------------------------------------------|------|

|         | 3.5  | MMS INSTRUCTIONS                          | 3-16 |

|         |      | 3.5.1 MAP LOADING                         | 3-16 |

|         |      | 3.5.1.1 Map Reading                       | 3-16 |

|         |      | 3.5.1.2 Status                            | 3-18 |

|         |      | 3.5.1.3 Status Reading                    | 3-22 |

|         |      | 3.5.2 SET COMMAND VALUE                   | 3-23 |

|         |      | 3.5.2.1 T State/Ml State (I)              | 3-26 |

|         |      | 3.5.2.2 MSTAL (NI)                        | 3-26 |

|         |      | 3.5.2.3 Enable DMA Mapping and            |      |

|         |      | Page Fault (DPF)                          | 3-27 |

| •       |      | 3.5.2.4 DMA Write Protection (DPP)        | 3-27 |

|         |      | 3.5.2.5 DMA Memory Error Detection (DME)  | 3-27 |

|         |      | 3.5.2.6 Parity Error Simulation (GU, GL)  | 3-28 |

|         |      | 3.5, 2.7 Change State                     | 3-28 |

|         |      | 3.5.2.8 Enable Program Mapping and        |      |

|         |      | Page Fault Detection (PF)                 | 3-28 |

|         |      | 3.5.2.9 Enable Program Protect (PP)       | 3-29 |

|         |      | 3.5.2.10 Select Program Protect Map (MAP) | 3-29 |

|         |      | 3.5.2.11 Enable Program Memory Error      |      |

|         |      | Detection (PME)                           | 3-29 |

|         |      | 3.5.2.12 Enable Program Timeout           | 3-29 |

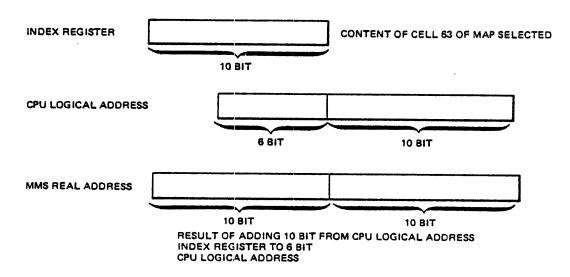

|         |      | 3.5.3 INDEXED, REAL MEMORY ADDRESSING     | 3-30 |

|         |      | 3.5.4 SINGLE-CYCLE INSTRUCTIONS           | 3-31 |

|         |      | 3.5.5 CLEAR MMS INSTRUCTION               | 3-31 |

|         |      | 3.5.6 ECC MODE SELECTION                  | 3-31 |

|         | 3.6  | MMS INTERRUPTS                            | 3-32 |

|         |      | 3.6.1 T STATE                             | 3-32 |

|         |      | 3.6.2 M STATE                             | 3-32 |

|         |      | 3.6.3 MSTAL                               | 3-32 |

|         |      | 3.6.4 MMS NON-INHIBITABLE (NI) INTERRUPT  | 3-33 |

|         |      | 3.6.4.1 General                           | 3-33 |

|         |      | 3.6.4.2 Recovery Considerations           | 3-34 |

|         |      | 3.6.5 NI INTERRUPT PROGRAM OPTIONS        |      |

|         |      | 3.6.5.1 Program Timeout (PTO)             | 3-35 |

|         |      | 3.6.5.2 Page Fault Interrupts (PFF or PF) | 3-36 |

|         |      |                                           | 3-36 |

|         |      | 3.6.5.4 Memory Error (ME)                 | 3-36 |

|         | 3.7  | MEMORY PROTECT                            | 3-37 |

|         | 3.8  | DMA CONSIDERATIONS                        | 3-37 |

|         | 3.9  | PAGE-TO-MEMORY ADDRESS CONVERSION         | 3-38 |

|         | 3-10 | STIMMARY OF MMS COMMANDS                  | 2 20 |

# LIST OF ILLUSTRATIONS

| Number     | Title                                     | Page |

|------------|-------------------------------------------|------|

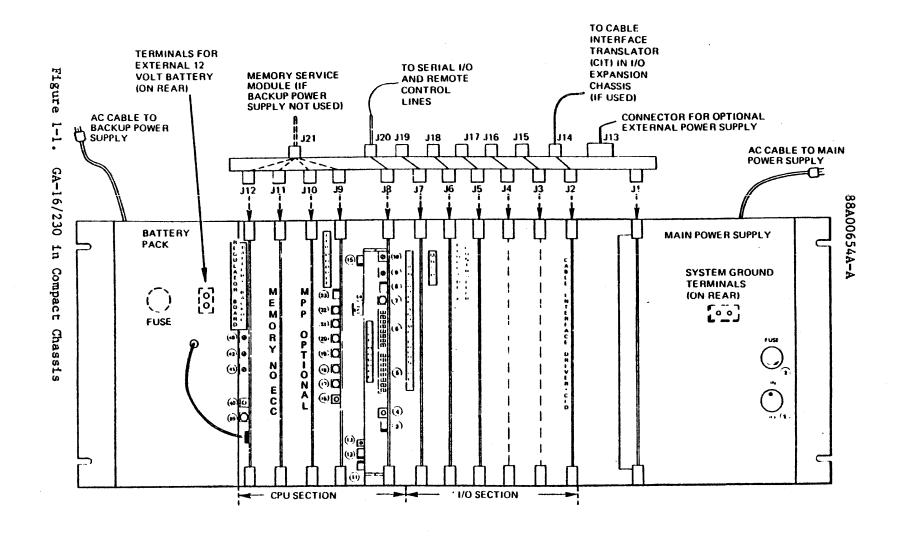

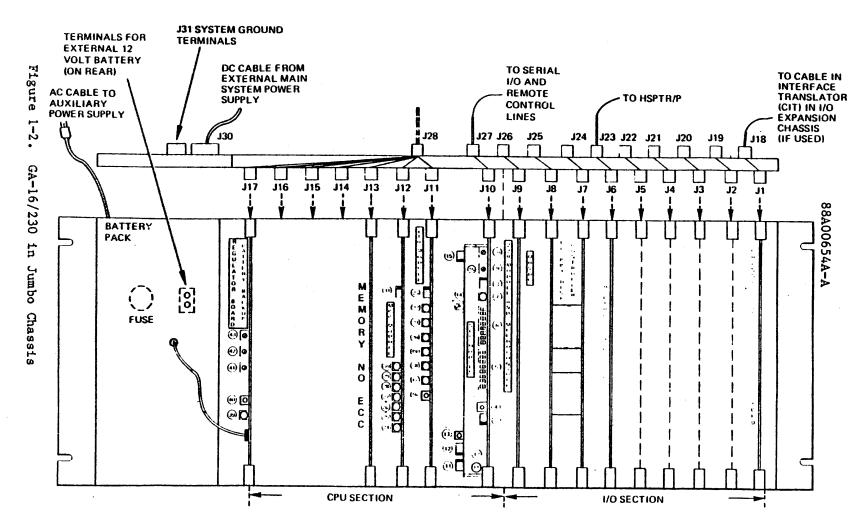

| 1-1<br>1-2 | GA-16/230 in Compact Chassis              | 1-3  |

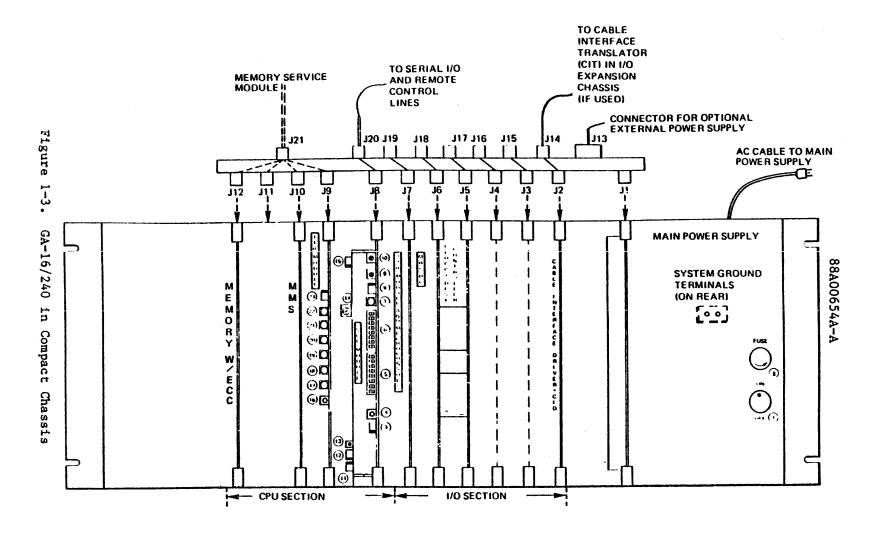

| 1 –3       | GA-16/240 in Compact Chassis              | 1-5  |

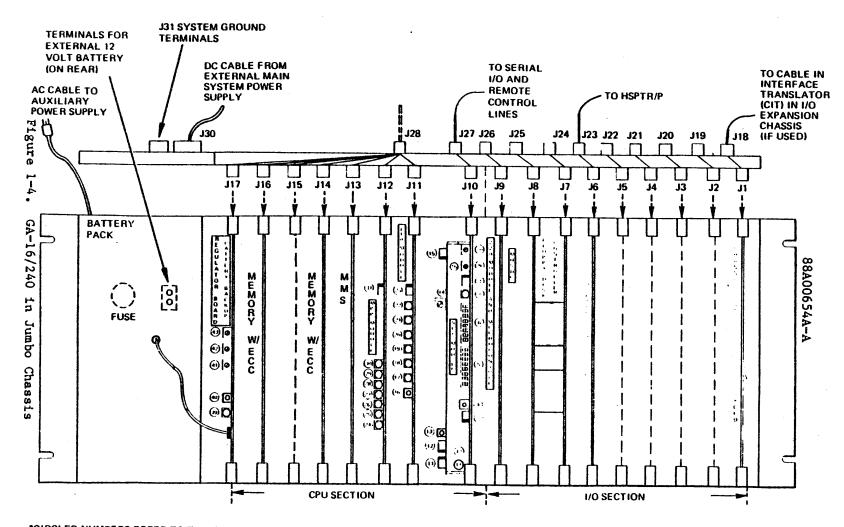

| 1-4        | GA-15/240 in Jumbo Chassis                | 1-6  |

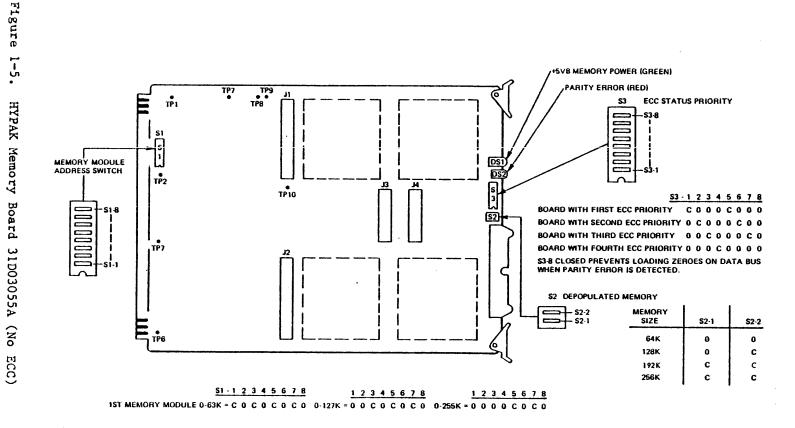

| 1 –5       | HYPAK Memory Board 31D03055A (No ECC)     | 1-7  |

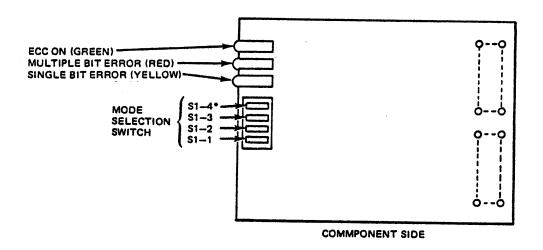

| 1-6        | 1/2MB ECC Board, 31D03061A                | 1-8  |

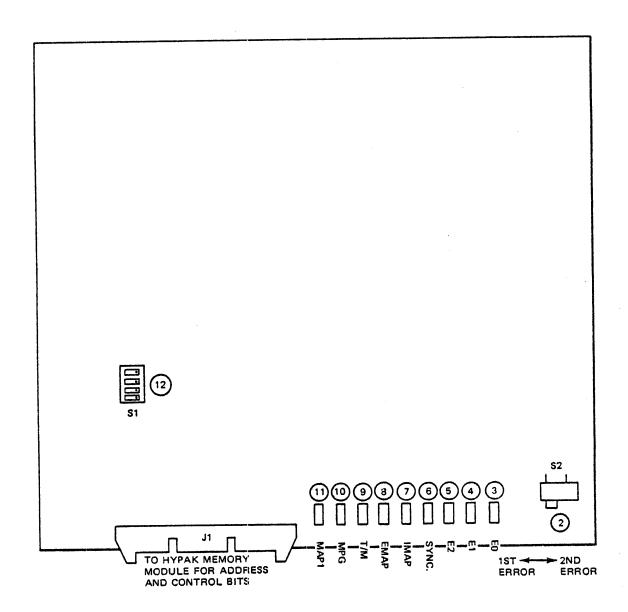

| 1-7        | MMS Module, 31D03076A                     | 1-9  |

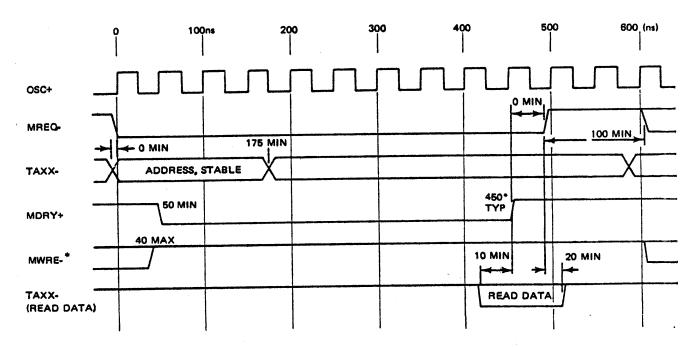

| 2-1        | Read Cycle                                | 2-5  |

| 2-2        | Write Cycle                               | 2-5  |

| 2-3        | Read-Modify-Write Cycle                   | 2-6  |

| 2-4        | MMS Interrupt Status, Word O              | 2-19 |

| 2-5        | MPP Status Word                           | 2-19 |

| 3-1        | Memory Management System Architecture     | 3-3  |

| 3-2        | Transparent Mode                          | 3-4  |

| 3-3        | Maximum Memory Size                       | 3-6  |

| 3-4        | Simplified Memory and Operating System    | 3-7  |

| 3-5        | Simplified Map Function                   | 3-9  |

| 3-6        | MMS Dynamic Address Translation (Mapping) | 3-12 |

| 3-7        | Map Cell Format                           | 3-13 |

| 3-8        | Map Loading.                              | 3-14 |

| 3-9        | Indexed Real Memory Address Computation   | 3-15 |

| 3-10       | MMS Status Word                           | 3-19 |

| 3-11       | MMS Interrupt Status, Word 0              | 3-20 |

| 3-12       | Status Word 4                             | 3-22 |

| 3-13       | MMS Command Value                         | 3-24 |

| 3-14       | Jumper For PTO Timing.                    | 3-36 |

| 3-15       | MMS Command Summary                       | 3-39 |

|            |                                           | J-77 |

# LIST OF TABLES

| Number | Title                                                    | Page |

|--------|----------------------------------------------------------|------|

| 1-1    | GA-16/230/240 Configurations                             | 1-10 |

| 1 –2   | Switches and Indicators for Memory, ECC and MMS Modules  |      |

| 2-1    | Data Bus Pin Assignments (P1)                            | 2-8  |

| 2-2    | MMS Pin Assignments (J5)                                 |      |

| 2-3    | GA-16/230/240 256K x 18 x 22 (31D03055A, 31D03061A)      | 2-11 |

| 2-4    | ECC Status Word Decode                                   | 2-15 |

| 3-1    | Instruction Summary for MMS                              |      |

| 3-2    | Further Interrupt Status Word O Interpretation When Page | •    |

|        | Fault, Program Protect, or Memory Error Occurs           | 3-21 |

| 3-3    | Command Value Description                                | 3-24 |

| 3-4    | MMS NI Interrupt Summary                                 |      |

| 3-5    | Page-To-Memory Address Conversion                        |      |

introduction

### 1.1 GA-16/220 VS GA-16/230/240

This addendum contains the information necessary for installation and operation of the GA-16/230/240 microcomputer. The GA-16/230/240 is based on the same hardware and software features as the GA-16/220. Major differences are related to the semiconductor memories and are identified below.

The GA-16/220 uses conventional 16K semiconductor memory modules with a total memory capacity of 64K words. MPP is available as an option. HYPAK memory is not available for the GA-16/220.

The GA-16/230 uses the 64K (128K bytes) HYPAK memory. The memory parity and write protect (MPP) option is available separately. A full complement of HYPAK modules on the single memory circuit board provides 128K bytes of 18-bit memory with parity.

The GA-16/240 uses a single memory board with at least 128K bytes; error checking and correction (ECC) and the extended instruction set are included. (Memory parity and write protect are incorporated in ECC.) By inserting HYPAK memory modules into DIP sockets, the memory board capacity can be expanded to 512K bytes in 128K byte increments. A memory management system (MMS) is contained on a single circuit board (31D03076A) that may be installed in a GA-16/240 with 128KB memory; MMS is a prerequisite for a GA-16/240 with any memory larger than 128KB. The memory parity and write protect (MPP) option is available separately for memory up to 128KB.

A GA-16/230/240 can be packaged in a compact or jumbo chassis (nucleus), just as the GA-16/220. In essence, the major difference between the compact and jumbo chassis in a GA-16/230 or GA-16/240 is the power supply and chassis size. The jumbo power supply accepts a range of four AC input voltages; and the larger jumbo chassis provides more I/O slots. Regarding the difference between a GA-16/230 and GA-16/240, the GA-16/240 has ECC in all configurations and increased memory with MMS in most configurations. These differences are demonstrated in the configuration listings, Table 1-1.

Table 1-1, GA-16/230/240 Configurations, specifies the GA-16/230/240 configurations for each chassis and the available expansion kits and options, and identifies a part or assembly number (engineering drawing) for each constituent component.

In summary, this addendum describes the General Automation HYPAK with ECC and the memory management system as used with the GA-16/230/240. The memory parity and write protect feature used with the GA-16/230/240 is described in the GA-16/220 publications.

### 1.2 EXTENDED INSTRUCTION SET

A GA-16/240 contains a CPU-1 board that has a smaller circuit board attached in a piggyback fashion. This attached piggyback contains the extended instruction set for the CPU-1 board; it enhances CPU operation when the GA-16/240 is used with GA-16/440 software. Although the basic GA-16/230/240 or GA-16/220 operates successfully with 440 software, overhead penalties reduce system efficiency. The extended instruction set ensures optimum performance.

### 1.3 INSTALLATION AND SET-UP BOARD CONFIGURATION

Installation and set-up procedures for a GA-16/230/240 are essentially the same as described in the GA-16/220 publications. However, circuit board configurations in the compact or jumbo chassis differ for the GA-16/220 and the GA-16/230/240. Figures 1-1 and 1-2 show typical GA-16/230 configurations. Memory module addressing is determined by switches mounted on the module and is independent of module position (slot). There is, however, one constraint relative to slot position for the GA-16/240 memory board(s): Due to the piggyback ECC module, a GA-16/240 memory board requires two slot spaces, hence the adjacent lower number slot must be unoccupied. For example, the GA-16/240 memory board in Figure 1-4 must be installed in slot J15 or J16 rather than J14. The MMS board can be installed in any unoccupied memory slot (CPU section of card cage).

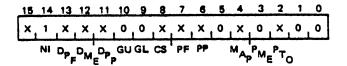

### 1.4 MEMORY CONFIGURATION SWITCHES

The switches and indicators on the memory board (31D03055A), the piggyback ECC board (31D03061A), and the MMS board (31D03076A) are shown in Figures 1-5, 1-6 and 1-7; and are defined in Table 1-2. All switches on these boards relate to the memory configuration board; namely the memory board (module) address, the memory board ECC priority, and the size of the memory. These memory configuration switches must be set as described in Table 1-2, prior to the start of system operation. A more detailed explanation of the memory configuration switches is provided in the Section 2 and Section 3 text.

With one exception, there are no strapping requirements for setting operating variables on the HYPAK, ECC or MMS boards. The sole strapping requirement relates to the program timeout interval on the MMS board and is explained in Section 3.6.5.1.

\*CIRCLED NUMBERS REFER TO TABLES 2-5.

IF MMS IS INSTALLED IN J12, THE MEMORY BOARD WILL BE IN J11.

\*CIRCLED NUMBERS REFER TO TABLES 2-5.

# 1/2MB Piggyback ECC Memory

\*S1-4 is not used.

Manual Mode Selection Switch Settings

| ECC Mode | Function          | s1 <b>-</b> 3 | Switch<br>S1-2 | S 1-1 |

|----------|-------------------|---------------|----------------|-------|

| 0        | OFF               | 0             | 0              | 0     |

| 1        | MODE 1            | 0             | 0              | С     |

| 2        | MODE 2            | 0             | С              | 0     |

| 3        | INPUT STATUS MODE | 0             | С              | С     |

| 4        | WRITE DATA ONLY   | С             | 0              | o     |

Figure 1-6. 1/2MB ECC Board, 31D03061A

See Table 1-2 for explanation of MMS controls and indicators.

Figure 1-7. MMS Module, 31D03076A

Table 1-1. GA-16/230/240 Configurations (Sheet 1 of 3)

| Model Number              | Nomenclature                           | Drawing                                                                                   |

|---------------------------|----------------------------------------|-------------------------------------------------------------------------------------------|

| GA-16/230 Compact Chassis |                                        |                                                                                           |

| 1623-1030                 | GA-16/230 CPU (115V)                   | 01P0275A                                                                                  |

|                           | Compact chassis and power supply       | 51D 000 85A<br>51P 000 85A<br>90C 02 470A                                                 |

|                           | System console interface with IPL      | 31D 02 405A<br>31P 02 405A<br>90C 02 405A<br>or<br>31D 03116A<br>31P 03116A<br>90C 03116A |

|                           | RS232/current loop (TTY) adapter       | 31C 02 486A                                                                               |

|                           | Memory service module                  | 31D 02 301A<br>31P 02 301A<br>90C 02 301A                                                 |

|                           | 128KB HYPAK memory;<br>18-bit, non ECC | 31D 03055A<br>31P 03055A<br>90C 03055A                                                    |

| 1623-0050                 | Memory Parity Protect option           | 31D 02 531A<br>31P 02 531A<br>90C 02 531A                                                 |

| GA-16/230 Jumbo Chassis   |                                        |                                                                                           |

| 162 3 <b>–</b> X040       | GA-16/230 CPU                          | 01P02075A0Z                                                                               |

|                           | Jumbo chassis and power supply         | 51D 000 93A<br>51P 000 93A<br>90C 02 088A                                                 |

<sup>&</sup>lt;sup>1</sup>Except for the changes specified below, the model-assembly-drawing listings for a GA-16/230 with jumbo chassis are the same as shown for a GA-16/230 with compact chassis.

Table 1-1. GA-16/230/240 Configurations (Sheet 2 of 3)

| Model Number                         | Nomenclature                           | Drawing                                                                                         |

|--------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------|

| GA-16/240 Compact Chassis            |                                        |                                                                                                 |

| 1624-1031                            | GA-16/240 CPU (115V)                   | 01P02074                                                                                        |

|                                      | Compact chassis and power supply       | 51D00085A<br>51P00085A<br>90C02470A                                                             |

|                                      | System console interface with IPL      | 31D 02 40 5A<br>31P 02 40 5A<br>90C 02 40 5A<br>or<br>31D 0311 6A<br>31P 0311 6A<br>90C 0311 6A |

|                                      | RS232/current loop (TTY) adapter       | 31C02486                                                                                        |

|                                      | Memory service module                  | 31D02301A<br>31P02301A<br>90C02301A                                                             |

|                                      | 128KB HYPAK Memory;<br>22 bit with ECC | 31D 03055A<br>31P 03055A<br>90C03055A<br>or<br>31D 03061A<br>31P 03061A                         |

| GA-16/240 Jumbo Chassis <sup>2</sup> |                                        | 90C 03 0 61 A                                                                                   |

| 1624 <b>-</b> X041                   | GA-16/240 CPU                          | 01P02074A1Z                                                                                     |

|                                      | Jumbo chassis and power supply         | 51D 00093A<br>51P 00093A<br>90C 02 088A                                                         |

$<sup>^2</sup>$ Except for changes specified below, the model-assembly-drawing listings for a GA-16/240 with jumbo chassis are the same as shown for a GA-16/240 with compact chassis.

Table 1-1. GA-16/230/240 Configurations (Sheet 3 of 3)

| Model Number                                         | Nomenclature                               | Drawing                                      |  |

|------------------------------------------------------|--------------------------------------------|----------------------------------------------|--|

| Conversion Kit: GA-16/230                            | to GA-16/240 <sup>3</sup>                  |                                              |  |

| 1624-0724                                            | Conversion kit 16/230 - 16/240             | 01P02074A                                    |  |

|                                                      | 128KB, ECC piggyback memory module (64Kx4) | 31D03061A<br>31P03061A<br>90C03061A          |  |

|                                                      | Extended instruction set                   | 31D 03 00 5A<br>31P 03 00 5A<br>90C 03 00 5A |  |

| 1624-0893 Memory Expander                            | for GA-16/240 <sup>4</sup>                 |                                              |  |

| 1624-0893                                            | Memory expander for GA-16/240              | 01P02074A                                    |  |

|                                                      | Memory management system                   | 31D 03076A<br>31P 03076A<br>90C 03076A       |  |

|                                                      | 128KB, 22-bit HYPAK chips with ECC         | 01D 02 081A                                  |  |

| 1624-0823 Memory Expander For GA-16/240 <sup>5</sup> |                                            |                                              |  |

| 1 62 4-0 82 3                                        | 128KB, 22-bit HYPAK chips (11) with ECC    | 01P02074A<br>01D02081A                       |  |

$<sup>^3</sup>$  The 1624-0724 conversion kit provides a memory piggyback board with two HYPAK chips to convert 128kB of non ECC memory to ECC HYPAK memory. It also provides an extended instruction set that is installed on the CPU-1 board. The kit converts a compact GA-16/230 (1623-1030) to a compact GA-16/240 (1624-1031) or converts a jumbo GA-16/230 (1023-X040) to a jumbo GA-16/240 (1624-X041). ECC is added to memory, but memory size remains the same.

This memory expander consists of a set of 11 HYPAK chips (128KB memory) with ECC and an MMS board.

$<sup>^{5}</sup>$ This expansion kit is applicable to a GA-16/240 if the current memory is 256KB or higher. The kit provides 11 chips comprising 128K bytes with ECC.

Table 1-2. Switches and Indicators for Memory, ECC and MMS Modules (Sheet 1 of 3)

| Switch/<br>Indicator  | Function                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Board 31D0     | 03055A                                                                                                                                                                                                                                                                                                                                                         |

| DS 1-LED<br>IND (11D) | Power-on. Green power-on indicator turns on if +5V is received from the power supply.                                                                                                                                                                                                                                                                          |

| DS 2-LED<br>IND (11E) | Parity error. Red memory parity error indicator turns on if ECC board detects parity error.                                                                                                                                                                                                                                                                    |

| S1-DIP<br>SW (1D)     | Module address. Slassigns the module address as shown in Figure 1-5.                                                                                                                                                                                                                                                                                           |

| S2-DIP<br>SW (11J)    | Depopulated memory. S2 should be set as shown in Figure 1-5.                                                                                                                                                                                                                                                                                                   |

| S3-DIP<br>SW (11G)    | ECC status priority. If more than one memory board is installed, S3 selects the response priority when the memory (ECC) boards are interrogated for ECC status. If only one HYPAK memory board is installed, that board should be considered the "first" memory board and should be assigned the highest ECC priority. S3 positions are defined in Figure 1-5. |

| ECC Board 31D030      | <br>61A                                                                                                                                                                                                                                                                                                                                                        |

| DS 1-LED<br>IND (1A)  | ECC mode select. Green indicator turns on if ECC mode is selected by S1.                                                                                                                                                                                                                                                                                       |

| DS 2-LED<br>IND (1B)  | Multiple parity error. Red indicator turns on if multiple parity error is detected by ECC.                                                                                                                                                                                                                                                                     |

| DS 3-LED<br>IND (1C)  | Single parity error. Yellow indicator turns on if single parity error is detected by ECC.                                                                                                                                                                                                                                                                      |

| S1-DIP<br>SW (1E)     | Manual/ECC mode select. Sl positions are defined in Figure 1-6. Mode definitions are provided in Section 2.                                                                                                                                                                                                                                                    |

Table 1-2. Switches and Indicators for Memory, ECC and MMS Modules (Sheet 2 of 3)

| Switch/  |   |

|----------|---|

| Indicato | C |

|          |   |

### Function

### MMS Board 31D03076A

Switch S2

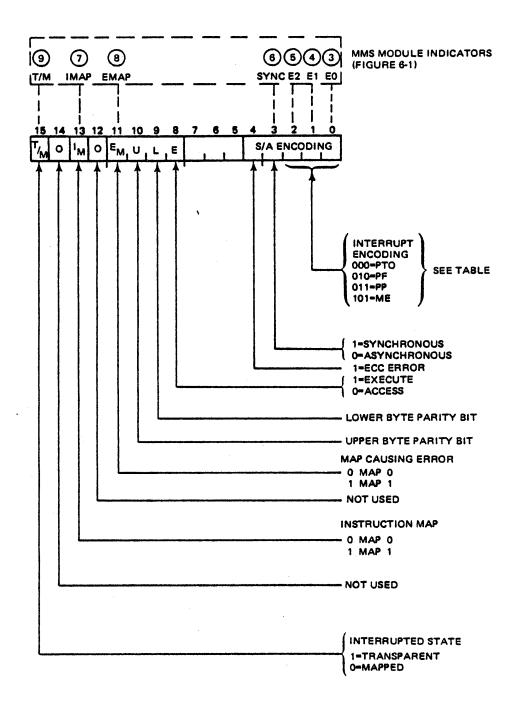

2-position switch in LEFT position, the indicators 3, 4, 5, 6, 7, and 8 are illuminated by an error which caused an NI interrupt (first error). In the RIGHT position the indicators are illuminated by a second error which can cause a MSTAL condition (refer to Section 3.5.2.2).

EO, E1, E2 LED IND Indicators are decoded to determine type of interrupt condition which occurred as follows (illuminated = 1):

| E2 | El  | EO | Condition                                     |

|----|-----|----|-----------------------------------------------|

| 0  | 0   | 0  | Program Timeout (PTO)                         |

| 0  | 1   | 0  | Page Fault (check sync lamp also) (PF)        |

| 0  | . 1 | 1  | Program Protect (PP) (check sync lamp 6 also) |

| 1  | 0   | 1  | Memory Error (ME) (check sync lamp 6 also)    |

These lamps are equivalent to bits 0, 1 and 2 in status word 0 (Section 3.5.1.2).

SYNC LED IND

Synchronous fault indicator. If illuminated concurrently decode of E2, E1, E0 as PF or PP indicates a fault. If not illuminated with PF or PP indicates a DMA/DMT fault. This indicator corresponds with the S/A bit in status word 0. (If illuminated with ME, it indicates an unconnectable program error.)

I MAP LED IND Error instruction map indicator to determine the instruction map used at the time the interrupt condition was created. only valid if indicator (9) is off.

1 = MAP 1

0 = MAP 0

This indicator corresponds with the IM bit in status word 0 (Section 3.5.1.2).

Table 1-2. Switches and Indicators for Memory, ECC and MMS Modules (Sheet 3 of 3)

Switch/ Indicator

### Function

### MMS Board 31D03076A

E MAP LED IND

Error execute map indicator to determine the MAP being used at the time the interrupt condition was created. Only valid if indicator (9) is off.

1 = MAP 10 = MAP 0

This indicator corresponds with the EM bit in status word 0 (Section 3.5.1.2).

T/M LED IND 9

If illuminated indicates MMS in transparent mode when interrupt occurred. This indicator corresponds with the T/M bit of status word 0.

MPG LED IND Mapping mode indicator. If illuminated indicates that either the CPU or DMA/DMT mapping is enabled.

MAP 1 LED IND MAP 1 indicator, when lit with (10) indicates MMS is in MAP 1. When off with (10) indicates MAP 0.

Memory Size

Set to indicate maximum memory size so that an overflow condition during indexed/real memory addressing is detected.

| Switch<br>Closed | Value | Address Range |  |  |

|------------------|-------|---------------|--|--|

| 1                | 7     | 1024K         |  |  |

| 2,3,4            | 8     | 896K          |  |  |

| 2,3              | 9     | 768K          |  |  |

| 2,4              | A     | 640K          |  |  |

| 2                | В     | 512K          |  |  |

| 3,4              | С     | 384K          |  |  |

| 3                | D     | 256K          |  |  |

| 4                | E     | 128K          |  |  |

| All Open         | F     | oĸ            |  |  |

# HYPAK memory with ECC 2

The GA-16/230/240 are the enhanced version of the GA-16/220, with the exception of the memory related features noted in Section 1. This section describes two of the three GA-16/230/240 memory related features that are not incorporated in the GA-16/220; namely, the HYPAK memory and error checking and correction (ECC). (The third feature, the memory management system, is described in Section 3.)

### 2.1 HYPAK MEMORY

The standard GA-16/230/240 HYPAK memory module is a single printed circuit board (31D03055A) containing 128, 256, 384, or 512 kilobytes of random access memory. Four connectors are provided on the circuit board for connection to the piggyback ECC module. A memory board can be used with or without an ECC module up to 128KB. Memory is added to the basic 128KB configuration in increments of 128KB by inserting HYPAK memory chips in DIP sockets.

### 2.1.1 MEMORY BOARD CONFIGURATIONS

The 31D03055A memory board and the 31D03061A ECC board come in four versions, as shown:

| Memory Board              | 64K x 18              | 31D 03055A21                 |

|---------------------------|-----------------------|------------------------------|

| ECC Board                 | 64K x 4               | 31D03061A24                  |

| Memory Board<br>ECC Board | 128K x 18<br>128K x 4 | 31D 03055A41<br>31D 03061A44 |

| Memory Board              | 192K x 18             | 31D 03055A51                 |

| ECC Board                 | 192K x 4              | 31D03061A54                  |

| Memory Board              | 256K x 18             | 31D03055A61                  |

| ECC Board                 | $2.56K \times 4$      | 31D03061A64                  |

The memory board and the ECC board both use the General Automation 70A00780A HYPAK memory module in a 28-pin DIP which contains  $65,536 \times 2$  bits of memory. The HYPAK module incorporates eight  $16K \times 1$  memory chips which are interconnected and used as a  $64K \times 2$  bit configuration. The memory chips used in the HYPAK memory modules are  $16K \times 1$  bit type TMS 4116 or MB 8216 chips. (Refer to GA specification 61A00016A for electrical parameters and test procedure.)

Refresh circuitry for the semiconductor memory is incorporated on the memory board and provides an internal refresh cycle issued every 16 usec. A refresh cycle has priority over a memory cycle. This guarantees that each of the 128 row addresses will be refreshed every 2 msec.

When the ECC board is not plugged in, the memory operates as a 16-bit data word plus 2 parity bits, one for each byte. During a write cycle, two parity bits are generated from the data present on the data bus and then stored in the memory. During a read cycle, two parity bits are generated from the data read from memory and compared with the two parity bits stored in the memory during the write cycle. If any of the parity bits do not match, a parity error is then detected. When a parity error is detected, (no MPP), the data bus is disabled (all zeros) until the error is cleared with system reset.

### 2.1.2 MODULE ADDRESS SWITCH S1

Address assignments for the memory module are shown in Figure 1-5 (Section 1). Logic drawing 90C03055A, sheet 4, shows how memory module address switch S1 generates an active MSEL memory select signal when an S1 setting corresponds to the address on MA16- through MA19- of the memory address bus. MSEL enables the read or write select gating and addressing logic for the memory chips, enabling the addressed memory module to respond to an MREQ memory request from the CPU.

### 2.1.3 DEPOPULATED MEMORY SWITCH S2

Depopulated memory board switch S2 is set to conform to the memory board capacity (chip population) as shown in Figure 1-5. If S2 conforms to the memory size, address lines MA16- and MA17- can develop row address strobes RASO- through RAS15- to initiate memory access (refer to 90C03055A, sheet 7).

### 2.1.4 ECC STATUS PRIORITY

If the ECC board is operating in the Input Status Mode, the CPU can execute a read at memory address 0 and thereby read the ECC status word from each ECC board (memory module with piggyback ECC). The ECC status words, one per board, are consecutively read in a priority sequence established by ECC status priority switch S3. Figure 1-5 shows how S3 is set to establish 1st, 2nd, 3rd or 4th priority for the associated board.

### NOTE

Only applicable if all memories have an error. Refer to Section 2.2.1.5.

Drawing 90C03055A, sheet 14, shows S3 and the priority selection lines. Priority lines PRL1-, PRL2- and PRL3- are on the MMS address line that connects all memory boards. With contacts 1 and 5 closed (first priority board) an active MPSI- is sent to the piggyback ECC board on J1-50. MPSI- enables the ECC board to place its status word and address on the In-Bus to the CPU. When the In-Bus data has been read, the ECC board sends an active MPSO- term to the memory module on J1-48. This signal is routed through S3-5; the resulting PRL1- is sent to the other memory boards. The second priority module has S3-2 and S3-6 closed to generate MPSI- and MPSO- with the results described for the first board.

### 2.1.5 MEMORY TIMING

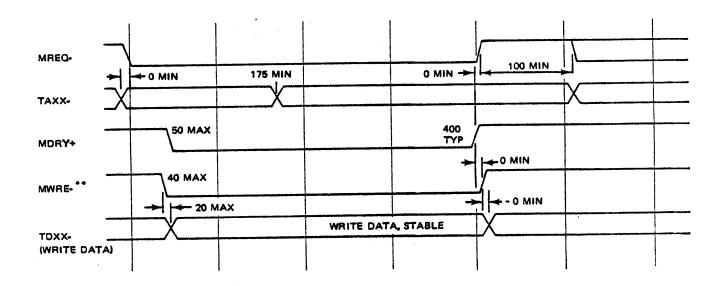

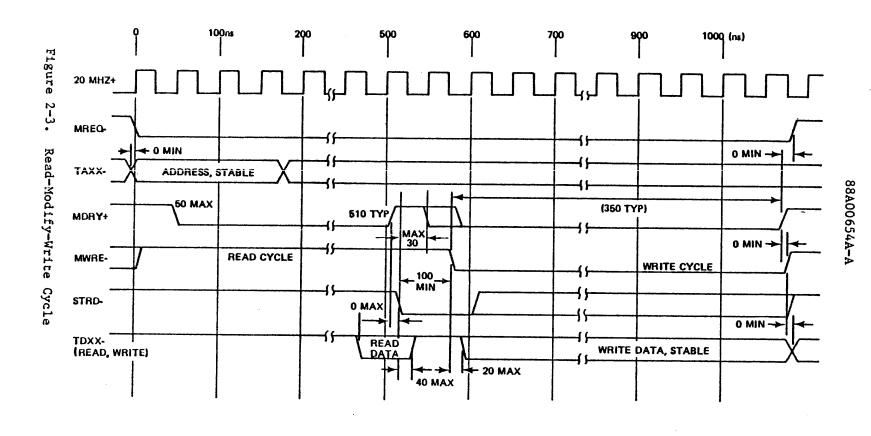

Figures 2-1, 2-2 and 2-3 contain timing diagrams for the memory read, write, and read-modify-write cycles.

### 2.1.5.1 Read

Memory request signal (MREQ-) from the CPU must remain low (active) until memory ready signal (MRDY+) is returned high (inactive) or within 1.6usec, and must remain off for 100ns minimum.

All address lines (ADXX-) must be valid for a minimum of 20ns on the address bus before the leading edge of memory request (MREQ-) and remain valid for 175ns minimum on the bus.

Data on the data bus (TDXX-) must be valid at the leading edge of memory data ready signal (MRDY+) and remain valid until memory request signal (MREQ-) goes high.

### 2.1.5.2 Write

Memory request signal (MREQ-) and address lines requirements are the same as for the read timing.

Memory write signal (MWRE-) not using Stop Read (STRD-), must go low within 40nsec maximum after memory request signal (MREQ-) goes low and go high when MREQ- goes high.

Data from the memory is inhibited from the data bus during the write cycle by means of a tri-state bus drivers disabled with memory write signal (MWRE-) activated (low).

### 2.1.5.3 Read-Modify-Write

Memory request signal (MREQ-) must remain low until memory data ready signal (MDRY+) is returned high after the write portion of the cycle.

Stop read signal (STRD-) may go low after memory data ready (MDRY+) is returned high and remain low until memory write signal (MWRE-) goes low. Refer to Figure 2-3.

Memory write signal (MWRE-) may go low 100nsec minimum after stop read signal (STRD-) and should go high when memory request signal (MREQ-) goes high.

The data on the data bus (TDXX) must be valid between the trailing edge of memory data ready signal (MDRY+) (low to high transition) and the leading edge of stop read signal (STRD-).

The complete Read-Modify cycle must be terminated within 2 usec maximum from the time of memory request signal (MREQ-) is activated.

### 2.1.5.4 Refresh Timing

The refresh circuit provides a lousec refresh timer. If the timer becomes active during a memory cycle, the refresh is enabled at the end of the memory cycle.

If a memory request signal (MREQ-) is activated during a refresh cycle, the cycle will be delayed until the refresh cycle is completed. Each refresh cycle refreshes each of the 128 row addresses at least once every 2msec.

Figure 2-1. Read Cycle

- 530 TYP. FOR CYCLE HAVING CORRECTED DATA.

- \*\* STOP READ, STRD IS HIGH DURING READ OR WRITE CYCLE.

Figure 2-2. Write Cycle

1

### 2.1.6 INTERFACE PIN ASSIGNMENTS

### 2.1.6.1 Memory Module to Data Bus and MMS

Table 2-1 gives pin assignments and term definitions for the P1 edge connector that connects the memory module to the CPU data (I/O) bus. Table 2-2 gives pin assignments for the J5 connector that connects the memory module to the MMS board (on the GA-16/240).

### 2.1.6.2 ECC to Memory Interface

The error correction board assembly 31D02061A is interfaced with the memory board assembly 31D03055A via four connectors, J1 through J4. J1 and J2 are 50 pins and J3 and J4 are 12 pin connectors.

The ECC board assembly plugs in the back of the memory board non-components side. The unique lines which were not listed in Tables 2-1 and 2-2 are identified below:

| ERROR CLOCK                                | J1 <b>-</b> 34 | ECM-   | ECM- (Error Correction Mode) generates an extra clock to strobe corrected data into data register.                                   |

|--------------------------------------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| CORRECTABLE or<br>NON-CORRECTABLE<br>ERROR | J4 <b>-</b> 9  | ECCER+ | Error flag used only when no MPP or MMS is used. Forces the tri-state data bus to all zeros. Cleared with system reset (SYRT-) only. |

| DATA CORRECTION BITS                       | ERB 00 -       | ERB 15 | Single bit error correction bits.                                                                                                    |

| WRITE ECC BITS                             | WECC-          | J1-33  | Read/write line for the ECC bits.  During a write data only mode,  WECC- line disable write into  ECC bits.                          |

### 2.1.7 MEMORY POWER

Table 2-3 defines power requirements for all configurations of a GA-16/230/240 memory board.

Table 2-1. Data Bus Pin Assignments (P1) (Sheet 1 of 2)

| POWER PINS:     | 1,140<br>71<br>81<br>82<br>3,4,137,1 | 38    | +5V Supply<br>+5VB Battery Back-Up<br>+12V Supply<br>-5V Supply<br>Ground |

|-----------------|--------------------------------------|-------|---------------------------------------------------------------------------|

| DATA BUS:       | 94                                   | TD00- |                                                                           |

|                 | 95                                   | TD01- |                                                                           |

|                 | 96                                   | TD02- |                                                                           |

|                 | 97                                   | TD03- |                                                                           |

|                 | 98                                   | TD04- |                                                                           |

|                 | 100                                  | TD06- |                                                                           |

|                 | 101                                  | TD07- |                                                                           |

|                 | 102                                  | TD08- |                                                                           |

|                 | 103                                  | TD09- |                                                                           |

|                 | 104                                  | TD10- |                                                                           |

|                 | 105                                  | TD11- |                                                                           |

|                 | 106                                  | TD12- |                                                                           |

|                 | 107                                  | TD13- |                                                                           |

|                 | 108                                  | TD14- |                                                                           |

|                 | 109                                  | TD15- |                                                                           |

|                 | 74                                   | TD16- | Parity Bit Byte O                                                         |

|                 | 76                                   | TD17- | Parity Bit Byte 1                                                         |

|                 |                                      |       | , , , , , , , , , , , , , , , , , , ,                                     |

| ADDRESS BUS:    | 110                                  | TA00- | Least Significant Bit                                                     |

|                 | 111                                  | TA01- | 3                                                                         |

|                 | 112                                  | TA02- |                                                                           |

|                 | 113                                  | TA03- |                                                                           |

|                 | 114                                  | TA04- |                                                                           |

|                 | 115                                  | TA05- |                                                                           |

|                 | 116                                  | TA06- |                                                                           |

|                 | 117                                  | TA07- |                                                                           |

|                 | 118                                  | TA08- |                                                                           |

|                 | 119                                  | TA09- |                                                                           |

|                 | 120                                  | TA10- |                                                                           |

| •               | 121                                  | TA11- |                                                                           |

|                 | 122                                  | TA12- | 4K Select                                                                 |

|                 | 123                                  | TA13- | 8K Select                                                                 |

|                 | 124                                  | TA14  | 16K Select                                                                |

|                 | 125                                  | TA15  | 32K Select                                                                |

| MEMORY REQUEST: | 126                                  | MREQ  | Initiates the memory cycle.                                               |

Table 2-1. Data Bus Pin Assignments (P1) (Sheet 2 of 2)

|                                  |                |                            | •                                                                                                                        |

|----------------------------------|----------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------|

| MEMORY PROTECT                   | 45             | MEMPR-                     | Inhibits Memory Cycle                                                                                                    |

| MEMORY WRITE                     | 127            | MWRE-                      | Low for a write cycle.                                                                                                   |

| STOP READ                        | 128            | STRD-                      | Aborts read cycle.                                                                                                       |

| MEMORY DATA READY                | 129            | MDRY+                      | Indicates data valid for read and memory response for write.                                                             |

| OSCILLATOR                       | 69             | osc+                       | 20 MHz processor clock                                                                                                   |

| MEMORY PARITY<br>AND PROTECT     | 63             | MPP-                       | Low (ground) when memory protect option is used.                                                                         |

| SYSTEM RESET                     | 46             | SYRT-                      | System resets when low. Used for power up/down sequence.                                                                 |

| NON-INH IB ITABLE<br>INTERRUPT 1 | 77             | NIIR1-                     | When low, resets parity error latches.                                                                                   |

| DATA PARITY<br>ERROR BUS         | 50             | MEMPY-                     | Low indicates data parity error. It also disables data from the data bus. Used only when no MMS or MPP is in the system. |

| FORCE PARITY<br>ERROR LOW BYTE   | 68             | FPBL-                      | Low causes wrong parity to be written byte 0.                                                                            |

| FORCE PARITY<br>ERROR HIGH BYTE  | 70             | f PB U-                    | Low causes wrong parity to be written byte 1.                                                                            |

| NON-CORRECTABLE<br>ERROR         | 83             | NC ERR -                   | Used with ECC only. Causes error interrupt with non-correctable error.                                                   |

| CORRECTABLE<br>ERROR             | 84             | COERR-                     | Used with ECC only. Causes error interrupt with correctable errors and ECC mode selection.                               |

| ECC MODE<br>CONTROL LINES        | 25<br>26<br>27 | ECMDO-<br>ECMD1-<br>ECMD2- | Select one of five ECC modes.                                                                                            |

| ECC MODE CLOCK                   | 52             | WCE-                       | Used to clock in ECMDO - ECMD2 into mode register.                                                                       |

Table 2-2. MMS Pin Assignments (J5)

| MEMORY MANAGEMENT<br>UNIT                               | J5 <b>-</b> 3                                      | MMS-                                               | Low (ground) when memory management option is used.                                                                |

|---------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| PRIORITY LINES                                          | J5-5<br>J5-7<br>J5-9                               | PRI.1-<br>PRI.2-<br>PRI.3-                         | Priority lines, used with memory management option, to sequentially propagate error status through memory modules. |

| ADDRESS ZERO                                            | J5 <b>-</b> 1                                      | ADZ S-                                             | Low (active) when addresses A00-A15 are zero and ECC error status mode is activated.                               |

| MEMORY WRITE                                            | J5 <b>-</b> 37                                     | MMWRE-                                             | Low for a write command from the MMS.                                                                              |

| EXTENDED MEMORY<br>ADDRESS LINES                        | J5-11<br>J5-13<br>J5-19<br>J5-21                   | MA16-<br>MA17-<br>MA18-<br>MA19-                   | 64K Select<br>128K Select<br>256K Select<br>512K Select                                                            |

| ERROR CORRECTION<br>ENABLED                             | J5 <b>-</b> 2                                      | ECC EN-                                            | Low (ground) when ECC unit is plugged in.                                                                          |

| MEMORY REQUEST                                          | J5-35                                              | MMREQ-                                             | Low for initiating a memory cycle from the MMS.                                                                    |

| ADDRESS LINES FROM<br>MMS (MEMORY<br>MANAGEMENT OPTION) | J5-29<br>J5-23<br>J5-25<br>J5-27<br>J5-31<br>J5-37 | MA10-<br>MA11-<br>MA12-<br>MA13-<br>MA14-<br>MA15- | Used for the ECC status word.                                                                                      |

Table 2-3. GA-16/230/240 256K x 18 x 22 (31D03055A, 31D03061A) Memory System at Room Temperature (25 $^{\circ}$ C)

| VERSIONS:                                  | +5V  | 'C    | i    | +5VB  |            |       | +12VB |            |      | -5VB  |            |

|--------------------------------------------|------|-------|------|-------|------------|-------|-------|------------|------|-------|------------|

| 18 BIT = PARITY 22 BIT = ECC               | OP   | STDBY | OP   | STDBY | BATT<br>OP | OP    | STDBY | BATT<br>OP | OP.  | STDBY | BATT<br>OP |

| 64K x 18 BITS                              | 1.3A | 1.2A  | .76A | .72A  | .75A       | . 27A | .08A  | .08A       | 1 ma | .6 ma | .6 ma      |

| 64K x 22 BITS                              | 2.4A | 2.3A  | .89A | .81A  | .85A       | .34A  | . 1A  | . 1A       | l ma | .6 ma | .6 ma      |

| 128K x 18 BITS                             | 1.3A | 1.2A  | .76A | .72A  | .75A       | .36A  | .17A  | .17A       | l ma | .6 ma | .6 ma      |

| 128K x 22 BITS                             | 2.4A | 2.3A  | .89A | .81A  | .85A       | .43A  | . 2A  | . 2A       | l ma | .6 ma | .6 ma      |

| 192K x 18 BITS                             | 1.3A | 1.2A  | .76A | .72A  | .75A       | .44A  | .25A  | . 25A      | l ma | .6 ma | .6 ma      |

| 192K x 22 BITS                             | 2.4A | 2.3A  | .89A | .81A  | .85A       | .53A  | . 3A  | . 3A       | l ma | .6 ma | .6 ma      |

| 256K x 18 BITS                             | 1.3A | 1.2A  | .76A | .72A  | .75A       | .52A  | .33A  | .33A       | l ma | .6 ma | .6 ma      |

| 256K x 22 BITS                             | 2.4A | 2.3A  | .89A | .81A  | .85A       | .63A  | .4A   | .4A        | l ma | .6 ma | .6 ma      |

|                                            |      |       |      |       |            |       |       |            |      |       |            |

|                                            |      |       |      |       |            | •     |       |            |      |       |            |

| REFERENCE:<br>16K x 18 BITS<br>(31D02578A) | .83A | .83A  | .42A | .42A  | .42A       | .93A  | .06A  | .06A       | 4 ma | .4 ma | .4 ma      |

# 2.2 ERROR CHECKING AND CORRECTION

The GA-16/230/240 ECC feature provides single-bit error correction and multiple-bit error detection. The ECC module is a single printed circuit board which plugs into four connectors on a 64Kx18 bit memory module. To accomplish error detection and/or correction, the ECC module generates and stores six "check bits" per data word during a write operation. During a read operation, these check bits are exclusive-ORed with the new check bits (generated during the read). If the result is zero, all data was read correctly. A single bit error results in a non-zero result, with the bit position in error specified by the decode of the result. A multiple bit error also generates a non-zero result, however the decode does not represent a valid bit position.

### NOTE

Upon initial power-up, all ECC bits are incorrect. All memory locations must be initialized by a store operation before the ECC is enabled. Failure to do so will cause false error indications.

### 2.2.1 OPERATING MODES

The error correction board operates in five different modes. The modes are selected by executing a DTOR/M to the MMS (or MPP) with the appropriate mode coded in bits 4, 5 and 6 of the output data words. In addition, manual switches on the ECC boards provide manual selection of the five operating modes. (Manual selection should aid in testing or troubleshooting the system.) Mode selection is received by the ECC board via the ECMDO - ECMD2 control lines. Coding is as follows:

| ECMDO | ECMD1 | ECMD2 | MODES                                                                                            |

|-------|-------|-------|--------------------------------------------------------------------------------------------------|

| L     | L     | L     | ECC OFF  NORMAL 1 MODE  NORMAL 2 MODE  INPUT STATUS MODE (MODE 3)  WRITE DATA ONLY MODE (MODE 4) |

| L     | L     | H     |                                                                                                  |

| L     | H     | L     |                                                                                                  |

| L     | H     | H     |                                                                                                  |

Figure 1-6 (Section 1) explains the manual mode selection.

### 2.2.1.1 Error Correction Mode OFF (Mode 0)

This mode, when selected, disables the error correction capability. System reset will select the OFF mode.

#### 2.2.1.2 Normal 1 Mode

This mode, when selected, enables the error correction circuitry to generate an interrupt on both correctable (single-bit) and non-correctable (multiple-bit) errors. The applicable indicator on the ECC board turns on if an error is detected (Figure 1-6).

#### 2.2.1.3 Normal 2 Mode

This mode, when selected, allows the error correction circuitry to generate an interrupt on non-correctable errors only; single-bit errors are corrected. The applicable indicator on the ECC board turns on if an error is detected (Figure 1-6).

#### 2.2.1.4 Write Data Only Mode (Mode 4)

This mode is restricted to diagnostic and test purposes. When selected, new check bits are generated, but not stored in memory. The original check bits remain in the memory.

# 2.2.1.5 Input Status Mode (Mode 3)

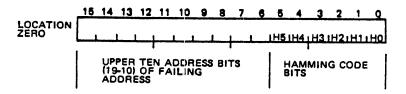

When the input status mode is selected (by the program), each ECC board will generate a status word if it has detected a single or multiple bit error on the associated memory board. The input status mode causes a status priority signal from the CPU to be propagated through each error correction board. The first board with an error will trap the status priority signal. If the CPU executes a read for memory location zero while input status mode is selected, the ECC board that trapped the status priority signal will place the following status word on the data bus:

Following the read execution, the status priority signal is propagated to the next lower priority ECC board. Each ECC board with a detected error blocks propagation of the priority status signal and responds to a CPU read of location zero, just as described for the first board to trap the priority signal. After transmitting the status priority signal, the CPU continues to read location zero until a status word with all zeros is received, indicating there are no more ECC boards with error status.

Table 2-4 defines the ECC status word bits, and shows the decode of hamming bits 0-5 to identify the error type (single or multiple bit), and the identity of the erroneous bit for a single bit error.

#### NOTE

A single bit failure of hamming bit 5 occurring in the first lK of memory will result in a status word of X'0000', rather than a status word with an address and a hamming code. Therefore, status should be checked twice if X'0000' is received on the first status read. (The MSS/MPP status can also be read in the conventional manner to identify an error condition in a memory board with ECC.)

Table 2-4. ECC Status Word Decode

ECC STATUS DECODE FOR 240 CPU

BITS 15----6 IDENTIFY A 1K BLOCK OF MEMORY WHERE AN EC ERROR HAS OCCURED.

BITS 5----O IDENTIFY THE TYPE OF ERROR, MULTI OR SINGLE,,

AND SPECIFY THE ERRONEOUS BIT FOR SINGLE-BIT ERRORS.

In the following tabulation for hamming bits 5-0:

"B" IDENTIFIES A DATA WORD BIT

"H" IDENTIFIES A HAMMING CHECK BIT

"MULTI" IDENTIFIES A MULTIPLE-BIT ERROR CODE

|     | В | ITS | 5- | 0 |   |           |     | В | ITS | 5- | 0 |   |       |

|-----|---|-----|----|---|---|-----------|-----|---|-----|----|---|---|-------|

| 5   | 4 | 3   | 2  | 1 | 0 |           | 5.  | 4 | 3   | 2  | 1 | 0 |       |

| 0   | 0 | 0   | 0  | 0 | 0 | Н5        | 0   | 1 | 0   | 0  | 0 | 0 | н4    |

| 0   | 0 | 0   | 0  | 0 | 1 | HO        | 0   | 1 | 0   | 0  | 0 | 1 | в8    |

| 0   | 0 | 0   | 0  | 1 | 0 | H1        | 0   | 1 | 0   | 0  | 1 | 0 | В9    |

| 0   | 0 | 0   | 0  | 1 | 1 | во        | 0   | 1 | 0   | 0  | 1 | 1 | B10   |

| 0   | 0 | 0   | 1  | 0 | 0 | H2        | 0   | 1 | 0   | 1  | 0 | 0 | B11   |

| 0   | 0 | 0   | 1  | 0 | 1 | B1        | 1/0 | 1 | 0   | 1  | 0 | 1 | MULTI |

| 0   | 0 | 0   | 1  | 1 | 0 | <b>B2</b> | 0   | 1 | 0   | 1  | 1 | 0 | B12   |

| 0   | 0 | 0   | 1  | 1 | 1 | в3        | 1/0 | 1 | 0   | 1  | 1 | 1 | MULTI |

| 0   | 0 | 1   | 0  | 0 | 0 | H3        | 0   | 1 | 1   | 0  | 0 | 0 | B13   |

| 0   | 0 | 1   | 0  | 0 | 1 | <b>B4</b> | 0   | 1 | 1   | 0  | 0 | 1 | B14   |

| 0   | 0 | 1   | 0  | 1 | 0 | B5        | 1/0 | 1 | 1   | 0  | 1 | 0 | MULTI |

| 1/0 | 0 | 1   | 0  | 1 | 1 | MULTI     | 1/0 | 1 | 1   | 0  | 1 | 1 | MULTI |

| 0   | 0 | 1   | 1  | 0 | 0 | <b>B6</b> | 1/0 | 1 | 1   | 1  | 0 | 0 | MULTI |

| 0   | 0 | 1   | 1  | 0 | 1 | В7        | 1/0 | 1 | 1   | 1  | 0 | 1 | MULTI |

| 1/0 | 0 | 1   | 1  | 1 | 0 | MULTI     | 0   | 1 | 1   | 1  | 1 | 0 | B15   |

| 1/0 | 0 | 1   | 1  | 1 | 1 | MULTI     | 1/0 | 1 | 1   | 1  | 1 | 1 | MULTI |

For example, the fourth tabulation in the left-hand column contains a l in hamming bits 0 and 1, and 0s in bits 2, 3, 4 and 5. This hamming code specifies an error in data bit 0 (BO).

# 2.2.2 ECC MODULE STATUS INDICATORS

The ECC module contains three indicators which indicate the presence of the ECC module and error status. The yellow indicator is illuminated when a correctable error has occurred. The red indicator is illuminated when a non-correctable error has occurred.

#### NOTE

When a non-correctable error occurs, the yellow indicator may or may not be illuminated.

The green indicator is illuminated when the ECC is on. Figure 1-6 shows the location of these indicators.

# 2.2.3 ERROR CORRECTION INTERRUPTS

The following interrupts are generated by the error correction board:

- Correctable Error Interrupt

- Non-Correctable Error Interrupt

# 2.2.3.1 Correctable Error Interrupt

An error correction from an ECC board will cause the MMS/MPP to generate a noninhibitable interrupt.

# 2.2.3.2 Non-Correctable Error Interrupt

The ECC board will generate incorrect byte parity on the erroneous word to signify a non-correctable error. Response to this depends on whether the GA-16/440 is equipped with MMS or MPP. The MMS will respond by generating a non-inhibitable interrupt with a CPU reset. The MPP will generate a non-inhibitable interrupt without a CPU reset.

#### 2.2.4 STATUS WORDS

The occurrence of both non-correctable and correctable interrupts may be distinguished by examining the MPP or MMS status word.

#### 2.2.4.1 MMS Status Word

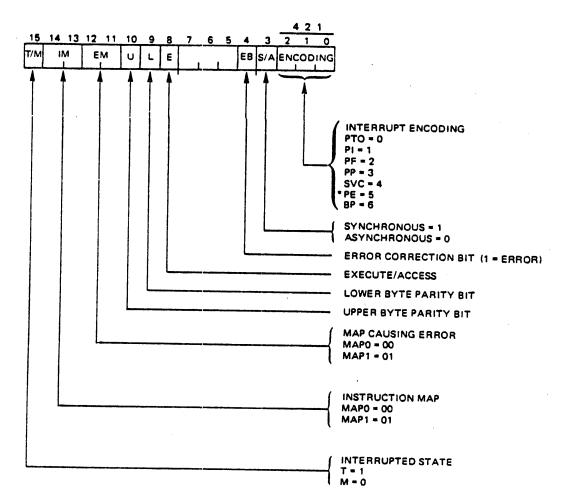

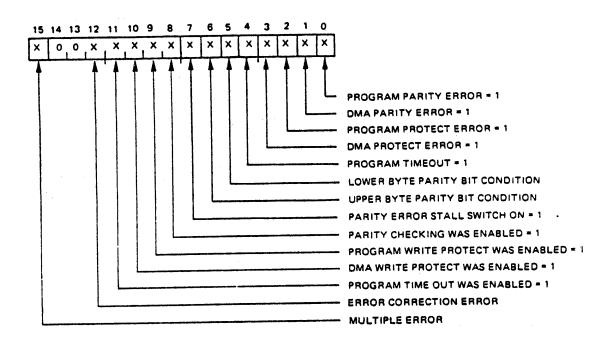

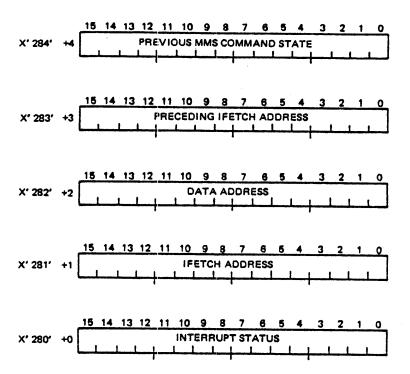

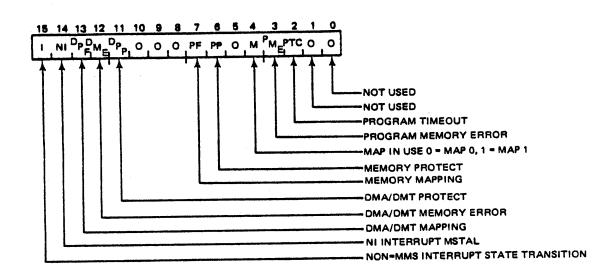

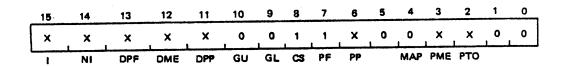

Error correction status may be determined by examining bit 4 and bits 0, 1 and 2 of MMS status word zero. Figure 2-4 illustrates the MMS status word zero format used with the GA-16/230/240.

Bits 0, 1 and 2 of MMS status word zero are binary weighted for error indication. Correctable errors are indicated by a decode of these bits being equal to zero, and bit 4 equal to a one. A non-correctable error is indicated when bits 0, 1 and 2 decode to five and bit 4 is equal to a one.

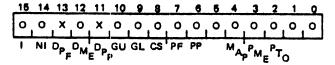

#### 2.2.4.2 MPP Status Word

If MMS is not installed, error correction may be determined by examing the MPP status word. A correctable error is indicated by bit 12 of the MPP status word being on. Non-correctable errors are indicated by the error correction bit (bit 12) and the parity error bit (bit 0) being on. Figure 2-5 shows the MPP status word coding.

\*NON CORRECTABLE ERRORS CAUSE ECC BOARD TO GENERATE ODD PARITY, HENCE PE IS INDICATED

Figure 2-4. MMS Interrupt Status, Word O

Figure 2-5. MPP Status Word

# memory management system 3

#### 3.1 INTRODUCTION

The Memory Management System (MMS) provides an operating environment external to the CPU which permits the implementation of a protected, multi-programmed, memory management operating system. The application of this option is directed toward multi-user and multi-process real-time systems. In providing an environment for multi-programming, MMS protects user programs from one another and protects the operating system from user programs. Many users can have access to the CPU, but the interaction between the various user programs can be rigidly controlled by the operating system. Additionally, the operating system or executive program can be protected from user programs.

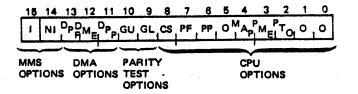

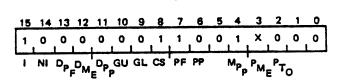

The memory mapping scheme that is implemented in MMS is very flexible and efficient in reconfiguring logical to physical memory. Very little overhead time is required by the operating system to consolidate programs. The features of MMS that provide these capabilities are:

- Memory Expansion to 2048 Kilobytes (KB) of physical memory

- Mapping of physical memory (2048KB) into 128KB blocks of logical memory

- Two MAP system capable of separate DMA/DMT I/O mapping

- Memory write protection

- DMA/DMT write protection

- Mapping page fault protection

- Program timeout protection

- Instruction execution protection

- Indexed real memory addressing capability

The MMS is mechanized in a single circuit board, 31D03076A. The MMS board controls and indicators are identified in Figure 1-7 and defined in Table 1-2.

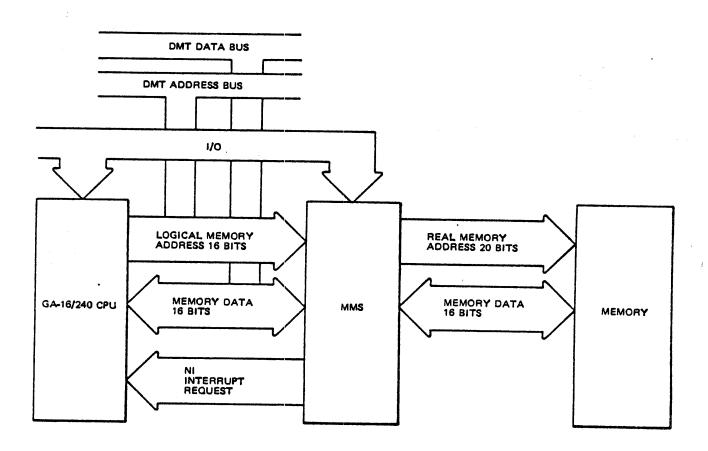

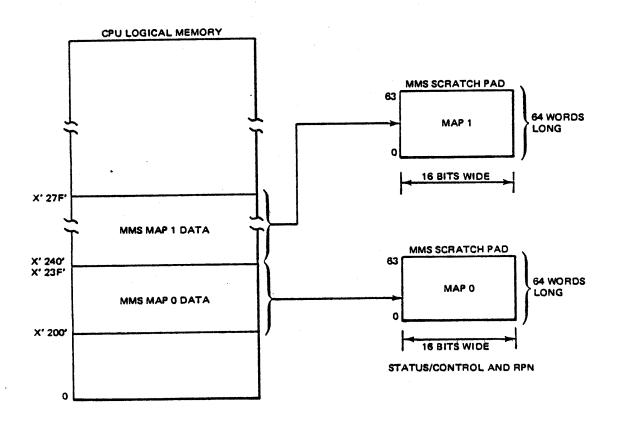

#### 3.2 MMS INTERFACE

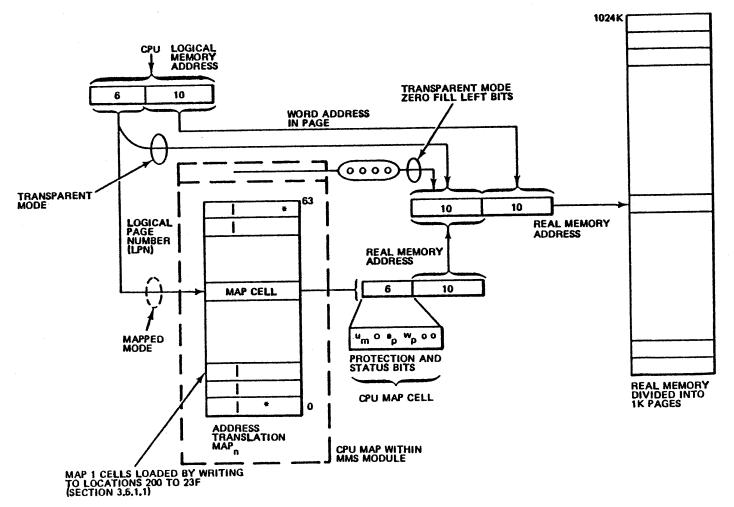

MMS interfaces the GA-16/240 with its memory subsystem (Figure 3-1). It monitors CPU activity on the I/O and memory buses to provide an environment for protected multi-programming of non-cooperating, contentious programs. By monitoring and controlling the memory bus, MMS provides a mapping mechanism to expand usable real memory from the GA-16/240's inherent architectural limit of 128KB to 2048KB.

Although only 128KB of real memory may be employed at any instant of time, MMS mapping commands may reconfigure whatever part of the real 2048KB of memory will be accessed by the CPU. MMS does this by transforming or translating the GA-16/240's logical addresses to the appropriate real addresses through its mapping functions. By routing memory control through MMS, program or DMA/DMT write protection is possible.

Finally, MMS monitors and controls some CPU activity. For example, if ISE is turned off too long (program timeout), the operating system may lose control of the machine. In this case, and for other error conditions, an NI interrupt will be generated to signal abnormal user program activity. This NI interrupt causes the CPU map to operate in transparent mode; that is, it enables the operating system to regain control.

The next few parts of this section will cover a general description of memory mapping which will lead to specific descriptions of MMS capabilities and commands. When references are made to DMA maps or options, it is to be understood that DMT is also implied.

Figure 3-1. Memory Management System Architecture

#### 3.3 MMS FUNDAMENTALS

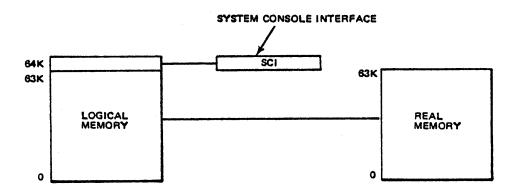

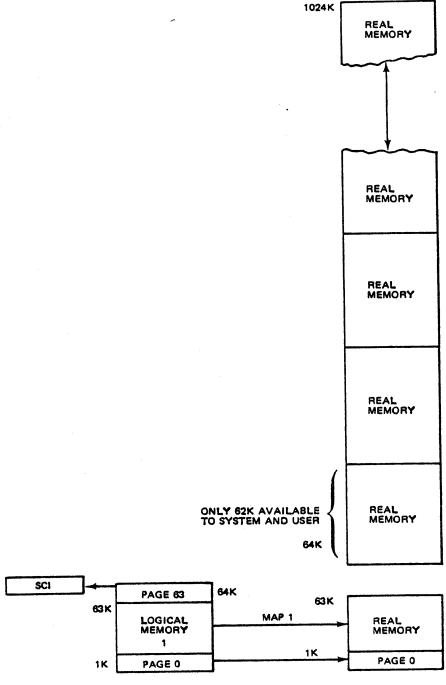

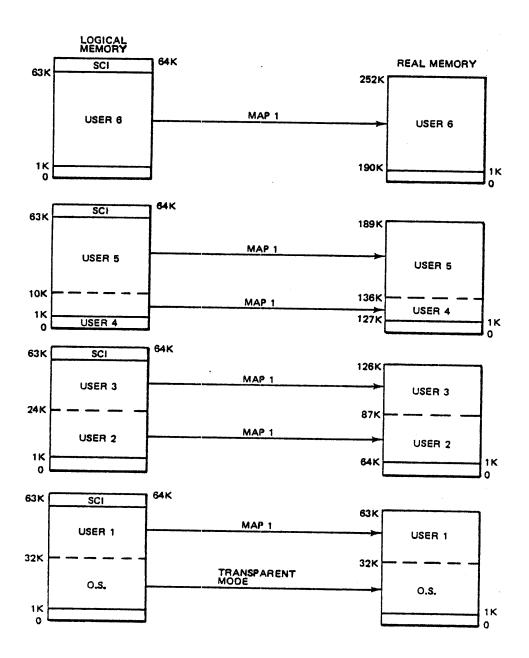

The basic function performed by MMS is the translation, through its mapping feature, of logical addresses to real addresses. Memory mapping is accomplished by making a "logical-to-real" address translation. Address translation is necessary to address locations greater than 64K because the program counter (register P) is only 16 bits long (X'FFFF' = 64K). This P counter limit of memory addressing or address space is called the "logical" address of the machine. With MMS installed, the physical memory size may be increased to 1024KW or 2048KB. This physical memory will be referred to as "real" memory with "real" address. The logical and real address will correspond if MMS is installed but mapping is not enabled. This is called the "transparent" mode (Figure 3-2).

Real memory can contain 64K logical memory spaces. MMS contains two maps, each map can translate the logical memory space address to a real memory space address. The logical memory spaces will be shown as contiguous blocks of memory for ease of grasping the basic concepts. Actually, each mapped space is made up of sixty-four lK pages, of which sixty-two may be "scattered" throughout memory as required.

It should be noted that page zero (0) will always address real memory, and page sixty-three (63) will always address the System Console Interface (SCI) if present. That is to say, page 0 will always address locations X'0000-X'03FF of real memory and page 63, address locations X'FC00-X'FFFF will always reference the SCI. If the SCI is not present real memory will be addressed.

Figure 3-2. Transparent Mode

In Figure 3-3, real memories 5 through 16 could be thought of as containing different logical memories. However, only one logical-to-real translation can be mapped.

Real memories 2 to 16 could be accessed by changing map 1 data. In other words, if programs that resided in real memory 2 had been executed to completion, map 1 data could be changed to effect a different address translation to access a different part of real memory.

The above representation implies that only one user can be mapped at any one time, that each user could access 64K, and that each user would operate as if he were the only user. In reality, it would be highly unlikely for each user program to require exactly 64K of memory space; most likely, a software operating system would be incorporated to effect executive control over the various programs. Also, there might be some routines that different user programs need to share. Lastly, MMS must incorporate some protective features to stop user programs from destroying each other.

A supervisory operating system (OS) can reside in memory space. However, the part of the OS which controls MMS functions would typically be placed in lower memory, since any error condition sensed by MMS invokes an NI interrupt and the transparent mode (logical = real address). This allows easy access to the operating system's control. Some of the controls performed by the operating system are:

- Allocating blocks of memory for users

- Loading user programs in memory

- Monitoring users' action

- Setting priorities for execution of programs

- Error recovery

A simplified organization of memory running under control of an operating system might appear as represented in Figure 3-4.

NOTE: 0-63K ALSO ACCESSED IN TRANSPARENT MODE PAGE 63 ALWAYS REFERENCES THE SCI

Figure 3-3. Maximum Memory Size

Figure 3-4. Simplified Memory and Operating System

In Figure 3-4, not every program occupies 64K. In fact, MMS can allocate memory in blocks as small as lK. Suppose that the operating system ordered user programs to execute in numerical sequence. As soon as user I had been serviced for its allocated time period, the operating system could redefine MAP I for user 5, then transfer control to user 5. When user 5 was finished, MAP I could be redefined to allocate memory for user 6, and so on down the line.

A typical way for control to be transferred from a user program to the operating system would incorporate the real-time clock (RTC). The operating system could determine the time intervals allocated for each user. The RTC interrupt routine can be designed to force the transparent state and, thereby, transfer control back to the operating system. Thus, the user would execute its program until the RTC interrupted and transferred control back to the operating system. The operating system would count the intervals and either return to the original user or select the next user for its time period.

If an error occurs during user execution, an NI interrupt will be generated. It forces the transparent state and returns to the operating system.

The example shown in Figure 3-4 is not completely representative of MMS capability. First, it only shows a maximum of 252K of memory, and more important, it does not show the interleaving possible between logical and real memory. The use of MAP 0 is not shown and it falsely implies that mapping is done only in contiguous blocks. If that were the case, a lot of operating system overhead time would be taken up by moving various user routines into contiguous spaces. Also some users may share some routines. For a more representative picture of mapping, see Figure 3-5.

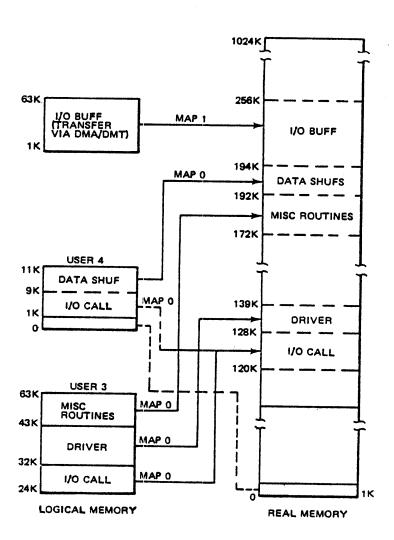

In Figure 3-5 both user 3 and 4 share, through their respective maps, a part of real memory from 120K to 128K for an I/O call routine. Note that neither user 3 nor user 4 has completely contiguous blocks in real memory. However, as far as the CPU is concerned, it sees only logical memory; therefore, program execution is maintained in an orderly fashion so long as the operating system does its map bookkeeping orderly.

MAP 1 could be considered as the 'system MAP' in that portions of the operating system and all DMA/DMT operations reside in real memory space controlled by MAP 1. Map 0 should be considered as the 'user's MAP' on a multiple map operating system. The user programs will reside in the portion of real memory controlled by MAP 0.

Figure 3-5. Simplified Map Function

In Figure 3-5, both user 3 and 4 share a routine in real memory labeled I/O call. If the first user on the line started some DMA activity with I/O CALL, the other user would have to wait until the first user was finished before he could use I/O CALL for his DMA requirements. If the associated DMA operation entailed a large block transfer, the wait time would be prohibitive. To circumvent this, MMS allows DMA to use MAP I and the user to user MAP O. DMA operations are always mapped through MAPI when DMA mapping is enabled. That is, DMA activity from one user may be overlapped with program execution of another.

If the map interleaving of Figure 3-5 is combined with the transparent mode of Figure 3-4, and again combined to show 1024K of memory as in Figure 3-3 for a dozen or more users, we would finally show a representative total picture of MMS capability. Unfortunately, the various mapping lines would be so numerous as to obliterate all meaning. However, the mapping concept involved should be also.

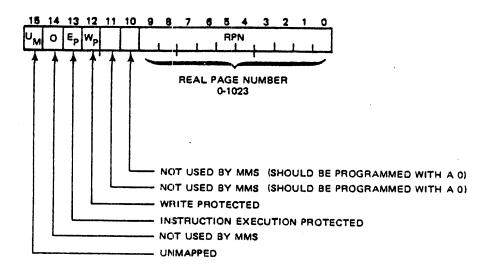

MMS employs two maps and a transparent (T) mode. If DMA mapping is enabled, it always employs MAP 1. If DMA mapping is not enabled, it will use transparent mode even if one of the other MAPs is selected for use.