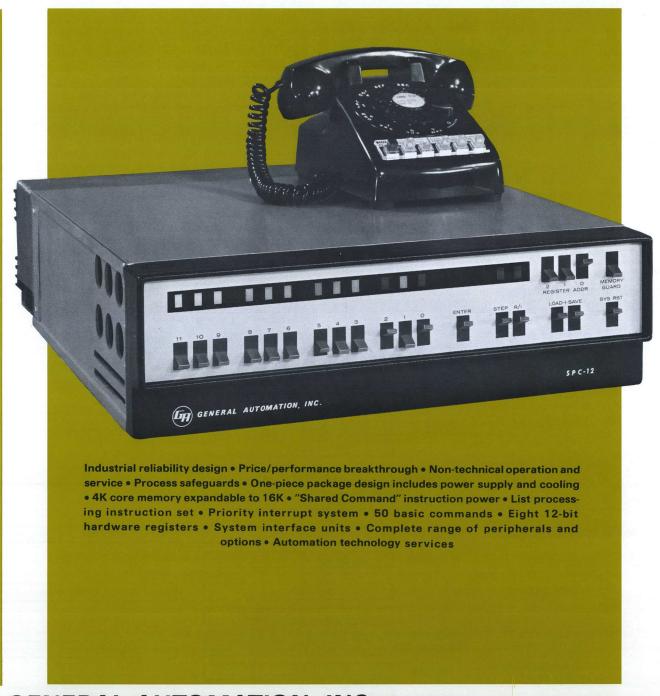

# SPC-12 automation computer

GENERAL AUTOMATION, INC. Automation Products Division

# The industrial automation computer

The SPC-12 Automation Computer is a new kind of digital computer—designed to work in an industrial climate, unattended and around the clock. Industrial reliability is assured by the SPC-12's worst case design, its wire-free construction, its use of integrated circuits, its wide-temperature (Lithium) memories, and its exhaustive environmental testing and factory burn-in procedures. It can be operated and maintained by non-technical personnel.

The SPC-12 instruction repertoire has six classes of instructions and a powerful new technique for sharing the command fields of four of them. The shared command technique minimizes the memory locations required for SPC-12 programs. Assigned to each of these four classes is a sector of 16 words of memory. When an instruction of

this type is taken from memory for execution, the

The full product scope of the SPC-12 includes the computer, system interfacing units, and control software. In combination they produce a general-purpose industrial computer subsystem for automation projects with significant advances in technology, price/performance, reliability, and maintainability.

All functional facilities required for control applications are standard. The basic SPC-12 includes a 4,096 by 8-bit word memory (expandable to 16,384 words), with a full cycle time of 2  $\mu$ sec. It provides a parallel adder—six addressing modes—eight 12-bit hardware registers, including an accumulator, an index, and two index/accumulator registers—50 basic commands—a priority interrupt system—a relative-time clock—a console lock—and a teletypewriter interface.

Nearly every functional organization can produce many applications where the SPC-12 will provide a substantial return on investment, such as: place stored intelligence into industrial machinery. collect and process data in hospitals and medical laboratories; concentrate, store, forward, switch, and separate data in communications systems; receive and generate data in display systems; count and control traffic; automate production and testing processes; and scan, log, and alarm data in process control.

## **Instructions and Shared commands**

SPC-12 control unit recognizes that a memory access from the shared sector is required to completely assemble the instruction. With this "shared command" concept, only one in-line 8-bit word of memory is required to specify an instruction. Any instruction that has the capability of using shared locations may instead use the next location in the "immediate" format.

| Load B, Store B, Jump                                                 |             | 7 6 5 4 3 2 1 0  Op Code X Address (M) | 7 6 5 4 3 2 1 0<br>Address (L) |

|-----------------------------------------------------------------------|-------------|----------------------------------------|--------------------------------|

| Skip                                                                  |             | Op Code Condition N                    |                                |

| Arithmetic, Logical                                                   | (immediate) | Operation Code                         | Operator B,Lit Register        |

|                                                                       | (shared)    | Op Code K                              |                                |

| Register Transfer                                                     | (immediate) | Operation Code                         | Mode Register d Register s     |

|                                                                       | (shared)    | Op Code K                              |                                |

| Control, Shift, I/O                                                   | (immediate) | Operation Code                         | Mode Shift, Control Reg, I/O   |

|                                                                       | (shared)    | Op Code K                              |                                |

| List Processing<br>Instruction Set,<br>Augmented Memory<br>Addressing | (immediate) | Operation Code N                       | Index D/I Operator Register    |

|                                                                       | (shared)    | Op Code K N                            |                                |

|                                                                       | (indirect)  | Index a Memory                         | Address                        |

# SPC-12 I/O Systems

The SPC-12 provides both parallel and serial I/O systems, each operating independently of the other. Included is a priority interrupt system to permit asynchronous events to interrupt the normal sequencing of a program to demand service.

The parallel I/O system provides flexibility through a single set of data and control lines to interface readily to a wide variety of external equipments. The 12-bit data bus of the I/O permits efficient handling of 8,12,16, and 24 bit data transfers. New peripherals or interfaces can be added in the field without modifying the SPC-12. New devices are added by simply connecting the I/O bus from the last to the new device.

The serial input/output system is a unique data transfer channel for serial data, operating indepen-

dently of the parallel I/O system. Typically connected to a teletypewriter, it permits operation up to 2000 feet away. Two instructions of the SPC-12 provide complete control of the serial I/O system.

The priority interrupt system services signals from external equipment, automatic restart, and the real-time clock on a priority basis. It permits asynchronous events to interrupt the SPC-12 normal sequencing of a program to request service. Hardware interrupt priorities can be implemented by the addition of interrupt expander units, each of which contains eight priority interrupt lines, interrupt servicing addresses, and enable/disable facilities. When an interrupt is acknowledged, the contents of the program counter are saved, and program control is transferred to a unique, dedicated location.

## **Software**

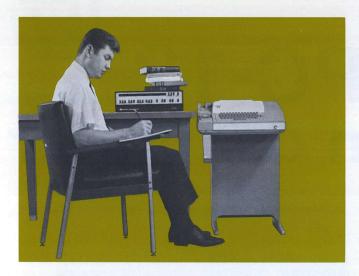

Standard program systems provided with the computer comprise the Conversational Assembly System, the Basic Utility System, and a subroutine library.

The Conversation Assembly System is a symbolic assembly program that minimizes the time required for assembling a program. It permits the programmer to recover from errors on-line without having to restart the assembly process. With this system the programmer can insert corrections from the keyboard during assembly. The assembler also provides the programmer with a means of entering linkage, mapping, and common data. With the system, instructions, data, memory addresses, and address modifiers can be coded and entered in symbolic notation. The assembler provides 11 pseudo-operation codes. A single pass of the input source program is sufficient to completely assemble the program.

The Basic Utility System enables the programmer to trace through his program to correct errors, to enter and execute test cases, and to verify results. The system operates on-line with a teletypewriter. Data can be input, instructions can be changed, and small programs can be executed using the keyboard for input.

The subroutine library includes a package of often used utility programs, I/O programs, mathematical subroutines, and a hardware maintenance and verification subsystem. The utility package contains routines for loading, punching, and listing programs, as well as aids for debugging and updating programs. I/O routines are available for such peripheral equipment as the Teletype Model 33 and 35, send/receive sets, standard communication modem interfaces, discrete digital inputs and outputs, contact closure and sensing units, analog-to-digital

and digital-to-analog conversion subsystems, and other standard peripheral devices. Also provided is a library of mathematical subroutines, including multiple precision fixed-point addition, subtraction, multiplication, and division routines.

In addition to the standard software package, total solutions or services in software applications are available to SPC-12 users from the process analysis programming staff of the Automation Sciences Division of General Automation, Inc. A substantial library of real-time monitors, executive control systems, process control functional programs, utility routines, and I/O drivers are operational and maintained for application to SPC-12 user projects.

# Reliability and Maintainability

SPC-12 computers are designed and manufactured to operate unattended and around the clock with the highest level of reliability. Reliability design features include: no-wire construction; integrated circuits; exceptional margins for timing, temperature, power, and noise; minimal number of components; and worst-case design. In addition, 100% preassembly testing is performed on all components and subsystems, and every assembled SPC-12 undergoes operation in an environmental test chamber and burn-in before shipment.

No computer maintenance training is required to service the SPC-12. The computer contains only three types of printed circuit boards—master inter-connect, memory, and processor—any one of which can be replaced within five minutes. The proper operation of each board can be verified by running the test and verify program.

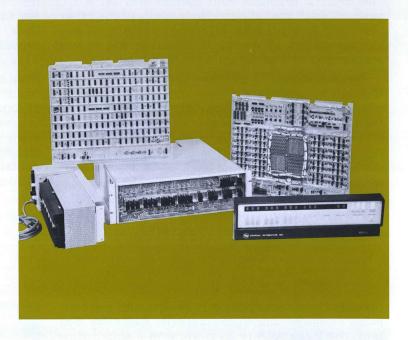

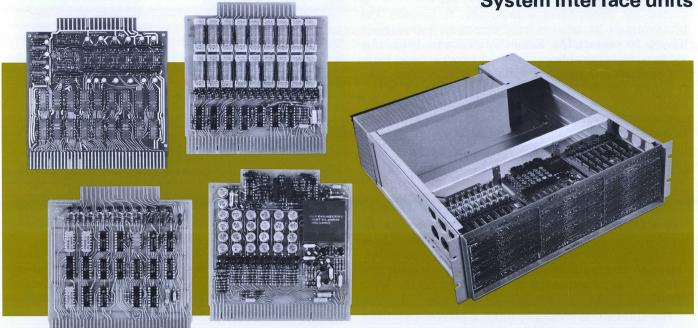

# SPC-12 System interface units

The SPC-12 is designed to combine multiple technologies into one computer subsystem economically and easily through use of a complete family of interface and controller system units. Each system interface unit is a functional entity which eliminates redundant and superfluous electronics. This approach

provides a new level of ease for system configuring, servicing, field expansion, and module economy. Up to 21 system interface units can be accommodated in one enclosure, and as many as eight more can be installed via an optional internal mounting assembly.

# SPC-12 Organization

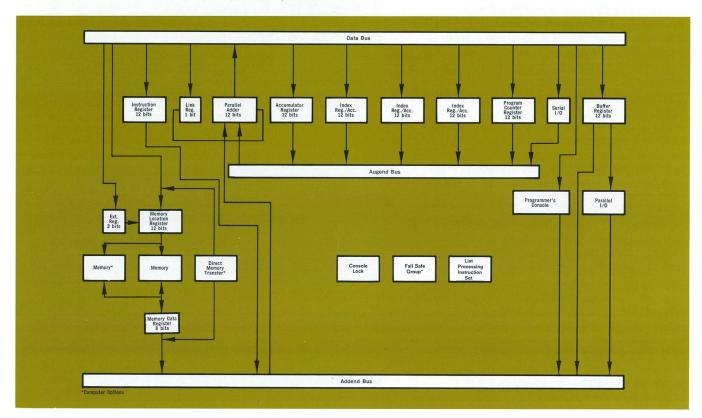

The dual-purposed registers and common bus organization of the SPC-12 are designed to process realtime control data efficiently and easily. The 12-bit organization efficiently processes data for direct, indirect, and indexed addressing to 4,096 words of memory, and is equally effective with 8-bit byte data. Thus, when generating addresses, the SPC-12 functions as a 12-bit parallel processor. When processing data, the SPC-12 operates as an 8-bit parallel processor.

# Instruction repertoire

| Mnemonic                                             |                                  | Description                                                                                                                                          | Cycles            |

|------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Load                                                 | B, Sto                           | ore B, Jump Class                                                                                                                                    |                   |

| LDB<br>LDB<br>STB<br>STB<br>ELB<br>JMP               | m<br>m, X<br>m<br>m, X<br>m<br>m | Load B register<br>Load B register, indexed<br>Store B register<br>Store B register, indexed<br>Extend Load B register<br>Jump to m                  | 3 3 3 4 2         |

| Skip (                                               | Class                            |                                                                                                                                                      |                   |

| SKC<br>SKR<br>SKP<br>SKM<br>SKZ<br>SKN<br>SKF<br>SKT | N<br>N<br>N                      | Skip if Link Set<br>Skip if Link Reset<br>Skip if Plus<br>Skip if Minus<br>Skip if Zero<br>Skip if Not Zero<br>Skip if I/O False<br>Skip if I/O True | 1 1 1 1 1 1 1 1 1 |

| X = indexed<br>B = B  Register<br>r = A, X, Y, Z, P  or  B  registers<br>v = literal value<br>N = 0, 2, 4,  or  6 |

|-------------------------------------------------------------------------------------------------------------------|

| t = X, Y, Z<br>a = auto-increment index tag<br>I = indirect address                                               |

| Mnemonic                                                                  |                      | Description                                                                                                                                                                                                                  | Cycles                                                                                           |  |

|---------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| Arithmetic, Logical Class                                                 |                      |                                                                                                                                                                                                                              |                                                                                                  |  |

| AAD<br>AAD<br>ASU<br>ALD<br>ALD<br>AZE<br>AND<br>AND<br>AOR<br>AOR<br>AXR | r, v<br>r, B<br>r, v | Add B to r Add v to r Subtract B from r Subtract v from r Load v into r Zero r Logical AND B with r Logical AND v with r Logical OR B with r Logical OR v with r Logical Exclusive OR B with r Logical Exclusive OR v with r | 2<br>3<br>2<br>3<br>3<br>2<br>2<br>3<br>2<br>3<br>2<br>3<br>2<br>3<br>2<br>3<br>2<br>3<br>2<br>3 |  |

| Regis                                                                     | ter T                | ransfer Class                                                                                                                                                                                                                |                                                                                                  |  |

| RTR<br>RIC                                                                | r, r<br>r, r         | Transfer r to r<br>Transfer & Increment<br>r to r                                                                                                                                                                            | 2 2                                                                                              |  |

| RDC                                                                       | r, r                 | Transfer & Decrement                                                                                                                                                                                                         | 2                                                                                                |  |

| RLK                                                                       | r, r                 | Transfer & Add Link,                                                                                                                                                                                                         | 2                                                                                                |  |

| Mnemonic |       | Description                           | Cycles              |

|----------|-------|---------------------------------------|---------------------|

| Contro   | ol, S | Shift, I/O Class                      |                     |

| PLR      |       | Pulse Link Reset                      | 2                   |

| PLS      |       | Pulse Link Set                        | 2 2 2 2 2 2 2 2 2 2 |

| TBB      |       | Transfer BB to B                      | 2                   |

| TBE      |       | Transfer B to E register              | 2                   |

| SHR      | r     | Shift Right r                         | 2                   |

| SHC      | r     | Shift Circular r                      | 2                   |

| SHL      | r     | Shift Circular Link r                 | 2                   |

| SHI      | r     | Shift Serial In r                     | 2                   |

| SHRO     | r     | Shift Right & Serial Out r            | 2                   |

| SHCO     | r     | Shift Circular & Serial<br>Out r      | 2                   |

| SHLO     | r     | Shift Circular Link &<br>Serial Out r | 2                   |

| SHIO     | r     | Shift Serial In & Out r               | 2                   |

| FOB      |       | Function Out from B register          | 2 2                 |

| DOB      |       | Data Out from B register              | 2                   |

| DIB      |       | Data In to B register                 | 2<br>2<br>3         |

| TOI      |       | Transfer on Interrupt                 | 3                   |

| Augme    | nte   | d Memory Addressin                    | g Class             |

| GNL r,   |       | Load r                                | 3                   |

| GNAr,    |       | Add to r                              | 3<br>3<br>3         |

| GNS r,   |       | Store from r                          | 3                   |

| CNIZ     | +     | Ctore and alees                       | 0                   |

Store and clear r Indirect address word

(+2)

GNZ r, t, I

# **Peripherals and Options**

Since many features of the SPC-12 Automation Computer would be extracost options if available on other computers, the standard SPC-12 requires far less than usual to implement it into a complete inter-technology system. The ease with which the SPC-12 combines multiple technologies into one computer subsystem is one of the important reasons for its performance-versus-price advantage.

Basic to this advantage are the SPC-12's family of interface and controller system units. Each of these units is designed to perform a complete function in interfacing or controlling, eliminating redundant electronics and custom engineering. The family consists of six sets, totalling more than 30 units, for interfacing and controlling communication data sets, instruments, sensors, computer peripherals, mechanisms, devices, displays, and keyboards.

Also, a choice of processor options can expand the power and utility of the SPC-12 to optimize the computer for a wide variety of system requirements, including additional core memories (up to 16,384 words), direct memory transfer, power failure detection and automatic restart, and enclosure and mounting assemblies.

# Automation Technology Services

The SPC-12 is another General Automation, Inc., total product line. This complete line comprises the computer, computer options, system interface units, peripheral controllers, peripherals, programming aids, and automation technology services. Automation technology services include application analysis, applied programming, development engineering, systems engineering, and installation service. Any combination of these products and services can be selected and applied to accomplish a complete computer based automation project.

# **SPC-12 Specifications**

#### **TYPE**

A digital, automation computer. Single address, parallel processor.

#### **MEMORY**

Random access. Wide temperature ferrite magnetic core memory storage. 4,096 8-bit bytes (expandable to 16,384 bytes). Memory cycle time of 2.16  $\mu$ sec; access time, 600 nsec.

#### **ADDRESSING**

Six modes. Direct addressing to 4,096 bytes. Literal addressing. Indexing. Indirect. Auto Index incrementing. Extended addressing.

#### ARITHMETIC

Parallel. Binary, fixed point, twos complement.

#### **INSTRUCTIONS**

Single and double word instructions. 50 basic instructions within six classes: Load B, Store B, Jump; Skip; Arithmetic, Logical; Register Transfer; Control, Shift, I/O; List Processing Instruction Set.

#### SPEED

Instruction Execute Times

| Add/subtract registers       | 4.32 μsec |

|------------------------------|-----------|

| Load/store from/to memory    | 6.48 μsec |

| Add/subtract memory          | 6.48 μsec |

| Input I/O bus to B register  | 4.32 μsec |

| Output B register to I/O bus | 4.32 μsec |

#### INPUT/OUTPUT

12-bit parallel I/O bus. Serial I/O bus. Automatic priority interrupt, relative-time clock; optional fail safe group and direct memory transfer.

#### PANEL

Programmer's console. Includes 12 data switches and indicators. Register selection switches. Six control switches. Console lock.

#### SOFTWARE

Software includes: conversational assembly system, basic utility system, subroutine library, hardware test and verify programs, and optional generalized real-time monitors and applied programming services.

#### **OPTIONS**

Expansion to 16K memory. Read-only memory. Fail safe group, with power fail detection, automatic restart, and stall alarm. Direct memory transfer channel and control unit. Priority interrupt expander unit. Over thirty system interface units. Mounting hardware. Battery power adapter (24 vdc input). Teletypewriter. Peripheral equipment. Real-time monitors. Application, programming and engineering services. Hardware optimization engineering for minimum recurring cost systems.

**DIMENSIONS**, including power supply and cooling Height 51/4 inches. Width 171/2 inches. Depth 20 inches.

WEIGHT, including power supply and cooling

**TEMPERATURE,** Operable 0 to 50° C.

**HUMIDITY,** Operable 90% relative.

#### POWER

115 volts ac  $\pm 10\%.$  Single phase. Frequency of 47 to 63 hz. 24 vdc power supply optional.

#### **INSTALLATION**

One piece packaging includes enclosure, power supply and cooling, permitting table top or standard 19" rack mounting.