Operation and Maintenance

ASN-24 COMPUTER

and Associated Test Equipment

# TABLE OF CONTENTS

| Purpose of Manual                                                                                                                                                                                          | 1-1<br>1-1                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose of Equipment                                                                                                                                                                                       | 1-1<br>1-1<br>1-1                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                            | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Weight and Valuma                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Magnetic Memory Drum                                                                                                                                                                                       | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TRICAL DESCRIPTION                                                                                                                                                                                         | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Write Amplifiers                                                                                                                                                                                           | 3-1<br>3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-4<br>3-4<br>3-6<br>3-6<br>3-7<br>3-7<br>3-7                                                                                                                                                                                                                                                                                                                                                            |

| RY OF OPERATION                                                                                                                                                                                            | 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| General  Basic Logical Elements  4-3. AND Gate  4-4. OR Gate  4-5. Flip-Flop  4-6. Emitter Follower  4-7. Read Flip-Flop  4-8. Write Amplifier  Memory Section  4-10. Memory Drum  4-11. Read/Record Heads | 4-1<br>4-2<br>4-2<br>4-2<br>4-4<br>4-4<br>4-5<br>4-5<br>4-5<br>4-5<br>4-6                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                            | Components  3-3. Resistors  3-4. Semiconductors  3-5. Magnetics  3-6. Capacitors  Clock Amplifier  Flip-Flops  Diode Gates  Emitter Followers  Write Amplifiers  Preamplifiers  Head-Switching Matrix  Read Amplifiers (Read Flip-Flops)  Drum  AY OF OPERATION  General  Basic Logical Elements  4-3. AND Gate  4-4. OR Gate  4-5. Flip-Flop  4-6. Emitter Follower  4-7. Read Flip-Flop  4-8. Write Amplifier  Memory Section  4-10. Memory Drum |

| Section |          |                                                                                                                           | Page         |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------|--------------|

| IV (Co  | nt.)     |                                                                                                                           |              |

|         | <u> </u> | 4-13. Clock Track                                                                                                         | 4-6          |

|         |          | 4-14. Sector Address Track                                                                                                | 4-8<br>4-8   |

|         |          | 4-16. Permanent Storage Tracks                                                                                            | 4-8          |

|         |          | 4-17. Temporary Storage Tracks                                                                                            | 4-9          |

|         |          | 4-18. Head Selecting Matrix                                                                                               | 4-10         |

|         |          | 4-19. Instruction Register                                                                                                | 4-10         |

|         |          | 4-20. Accumulator Register                                                                                                | 4-10         |

|         |          | 4-21. Multiplicand-Divisor Register                                                                                       | 4-11<br>4-11 |

|         |          | 4-22. Multiplier-Quotient Register                                                                                        | 4-11         |

|         |          | 4-24. Sigmator Short Line                                                                                                 | 4-12         |

|         | 4-25.    | Control                                                                                                                   | 4-13         |

|         |          | 4-26. Pulse Time Indicator                                                                                                | 4-14         |

|         |          | 4-27. Initial Synchronization                                                                                             | 4-14         |

|         |          | 4-28. Sigmator Program Delay                                                                                              | 4-18         |

|         |          | 4-29. Order Register                                                                                                      | 4-18         |

|         |          | 4-30. Track Selection Register                                                                                            | 4-21         |

|         |          | 4-31. Input-Output Selection Register                                                                                     | 4-23         |

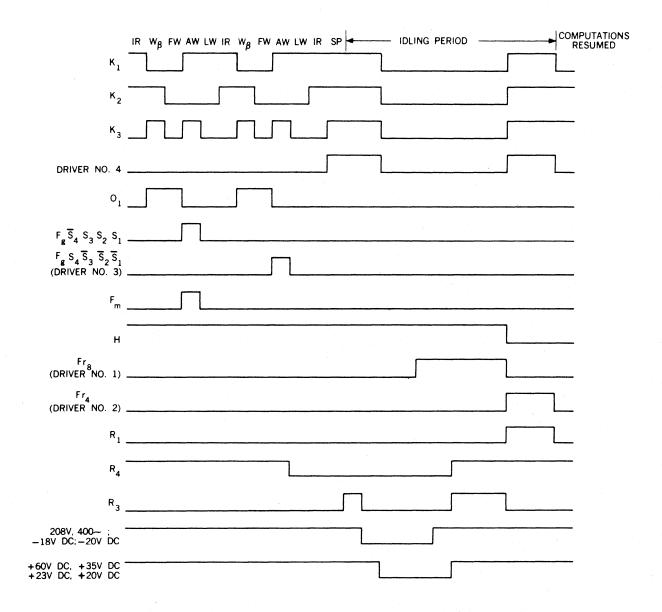

|         |          | 4-32. Phase Sequencing                                                                                                    | 4-26         |

|         |          | 4-33. Wait Alpha Phase (W) $K_1 K_2 K_3 \dots$                                                                            | 4-28         |

|         |          | 4-34. Instruction Read-In Phase                                                                                           | 4-28         |

|         |          | (IR) $K_1 K_2 \overline{K}_3 \dots$                                                                                       |              |

|         |          | 4-35. Wait Beta Phase $(W\beta) \overline{K}_1 K_2 K_3 \dots$                                                             | 4-31         |

|         |          | 4-36. First Word Phase (FW)                                                                                               | 1 22         |

|         |          | $\overline{K}_1$ $\overline{K}_2$ $(K_3 \text{ or } \overline{K}_3)$                                                      | 4-32         |

|         |          | 4-37. Additional Words Phase (AW)                                                                                         |              |

|         |          | $K_1 K_2 K_3 \dots \dots$                                                                                                 | 4-32         |

|         |          | 4-38. Last Word Phase (LW) $K_1 \overline{K}_2 \overline{K}_3 \dots$                                                      | 4-32         |

|         |          | 4-39. Stop Phase (SP) $K_1 K_2 K_3 \dots$                                                                                 | 4-33         |

|         | 4-40.    | Serial Adder                                                                                                              | 4-33         |

|         | 4-41.    | Input-Output Operations                                                                                                   | 4-37         |

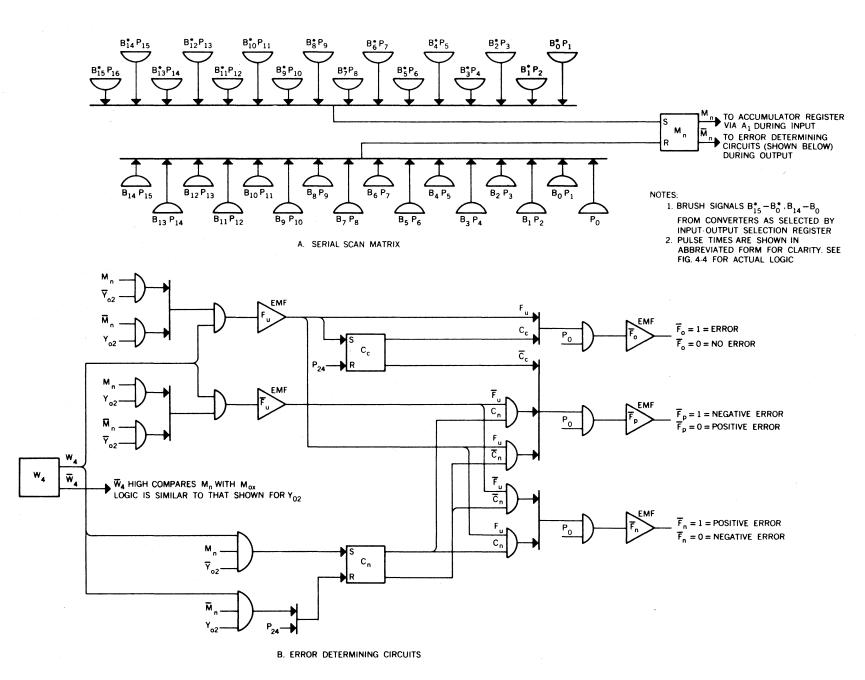

|         |          | 4-42. Scan Matrix                                                                                                         | 4-37         |

|         |          | 4-43. Error Determining Circuits                                                                                          | 4-39         |

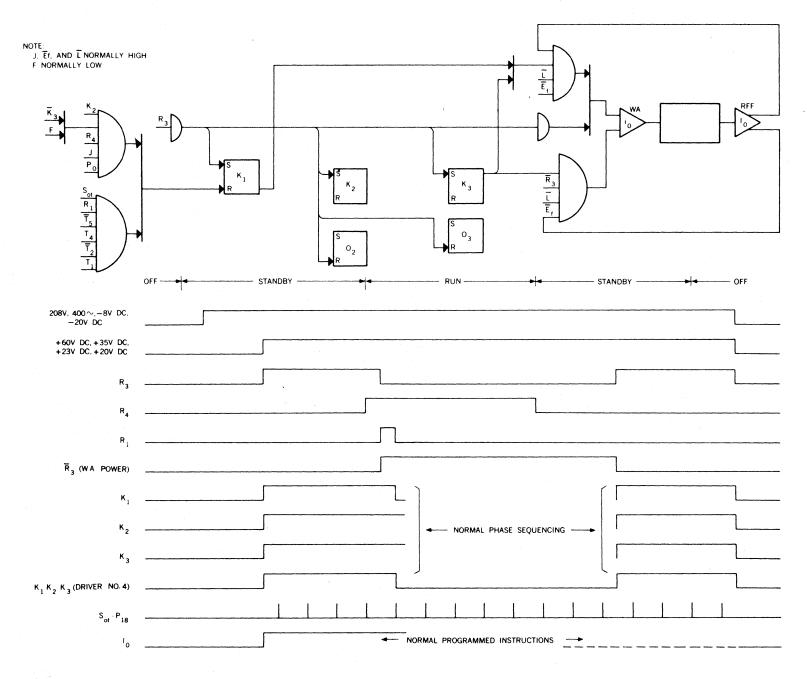

|         | 4-44.    | Starting Sequence                                                                                                         | 4-41         |

|         |          | 4-45. External Control                                                                                                    | 4-42         |

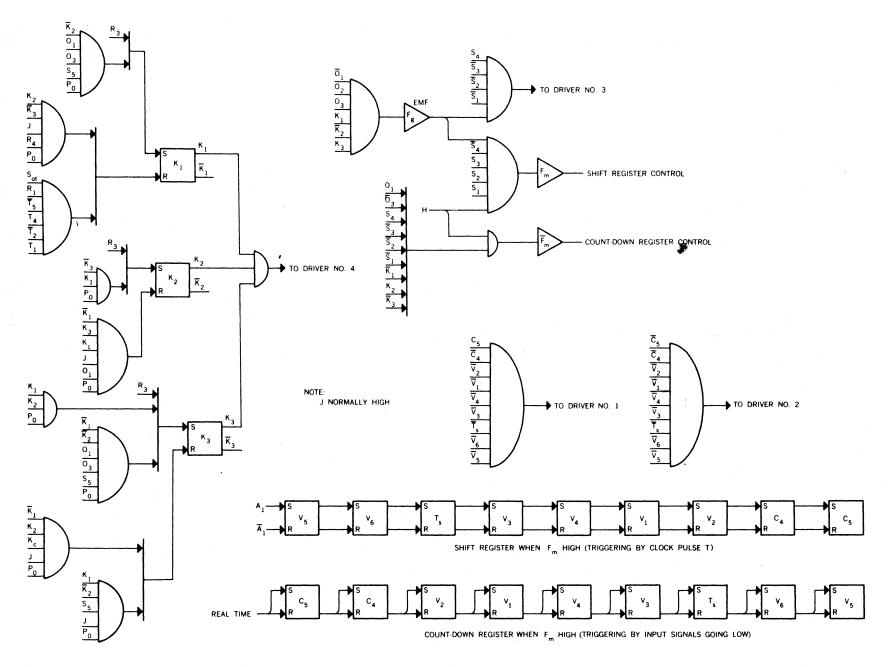

|         |          | 4-46. Internal Control                                                                                                    | 4-44         |

|         |          | 4-47. Instruction Read-In (IR) $K_1 K_2 \overline{K}_3 \dots$ 4-48. Wait Beta (W $\beta$ ) $\overline{K}_1 K_2 K_3 \dots$ | 4-45         |

|         |          |                                                                                                                           | 4-45         |

|         |          | 4-49. First Word (FW) $\overline{K}_1$ $\overline{K}_2$                                                                   | 4-45         |

|         |          | 4-50. Additional Words (AW) $K_1 \overline{K}_2 K_3 \dots$                                                                | 4-45         |

|         |          | 4-51. Last Word (LW) $K_1 \overline{K}_2 \overline{K}_3 \dots \dots$                                                      | 4-47         |

| Sect | ion     |                                                                                                                                    | Page         |

|------|---------|------------------------------------------------------------------------------------------------------------------------------------|--------------|

| IV   | (Cont.) |                                                                                                                                    |              |

|      |         | 4-52. Instruction Read-In (IR) $\overline{K}_1 \overline{K}_2 K_3 \dots$                                                           | 4-47         |

|      |         | 4-53. Wait Beta $(W\beta)$ $\overline{K}_1$ $K_2$ $K_3$                                                                            | 4-47         |

|      |         | 4-54. First Word (FW) $\frac{1}{K_1}$ $\frac{1}{K_2}$                                                                              | 4-47         |

|      |         | 4-55. Additional Words (AW) $K_1 \overline{K}_2 K_3 \dots$                                                                         | 4-49         |

|      |         | 4-56. Last Word (LW) $K_1 \overline{K}_2 \overline{K}_3 \dots \dots$                                                               | 4-49         |

|      |         | 4-57. Instruction Read-In (IR) $K_1 K_2 \overline{K}_3$ .                                                                          | 4-49         |

|      |         | 4-58. Stop (SP) K <sub>1</sub> K <sub>2</sub> K <sub>3</sub>                                                                       | 4-49         |

|      |         | 4-59. Idling Period and Idle to Run                                                                                                | 4-49         |

|      | 4-60.   | Clear and Add Order (At) $\overline{0}_1$ $\overline{0}_2$ $\overline{0}_3$ Add Order (Ad) $0_1$ $\overline{0}_2$ $\overline{0}_3$ | 4-50         |

|      | 4-61.   | Add Order (Ad) $0_1 0_2 0_3 \dots \dots \dots \dots$                                                                               | 4-52         |

|      | 4-62.   | Subtract Order (Su) $0_1 0_2 \overline{0}_3 \dots \dots \dots \dots$                                                               | 4-54         |

|      | 4-63.   | Extract Order (Ex) $\overline{0}_1$ $\overline{0}_2$ $0_3$                                                                         | 4-56         |

|      | 4-64.   | Conditional Transfer Order (Tc) $\overline{0}_1$ $0_2$ $0_3$                                                                       | 4-56         |

|      | 4-65.   | Normal Store Orders (Sr) $0_1 0_2 0_3 \overline{S}_5 \overline{S}_4 \dots$                                                         | 4-59         |

|      | 4-66.   | Modified Store Orders $0_1 0_2 0_3 \overline{S}_5 S_4 \dots \dots$                                                                 | 4-60         |

|      | 4-67.   | Multiply Order (Mu) $\overline{0}_1$ $0_2$ $\overline{0}_3$                                                                        | 4-64         |

|      | 4-68.   | Divide Order (Dv) $0_1 \overline{0}_2 0_3 \dots \dots \dots \dots$                                                                 | 4-73         |

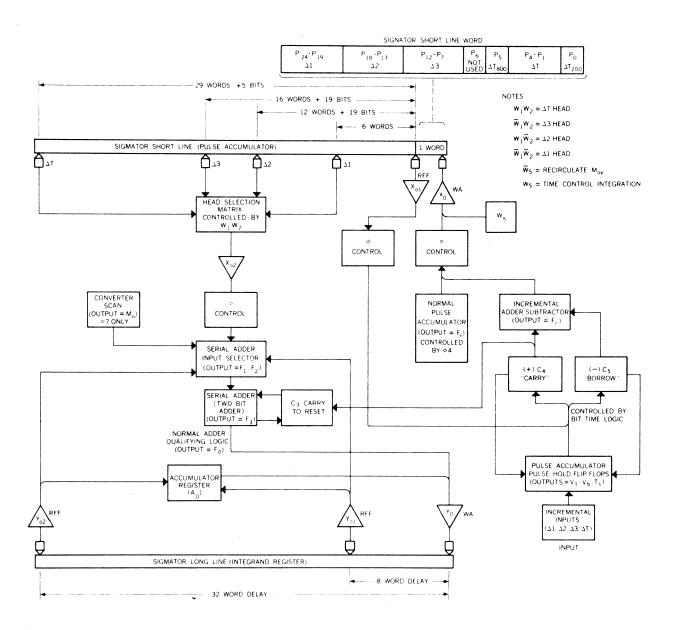

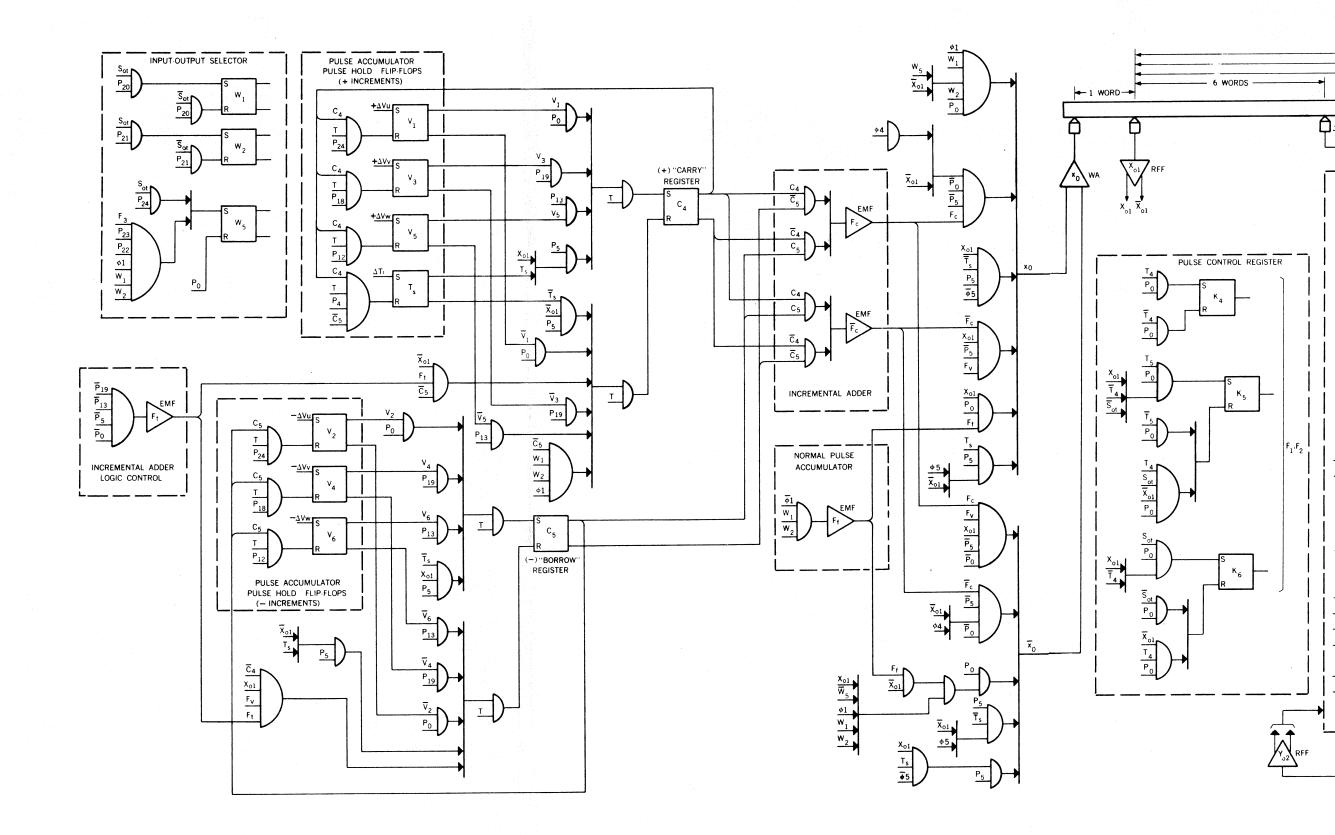

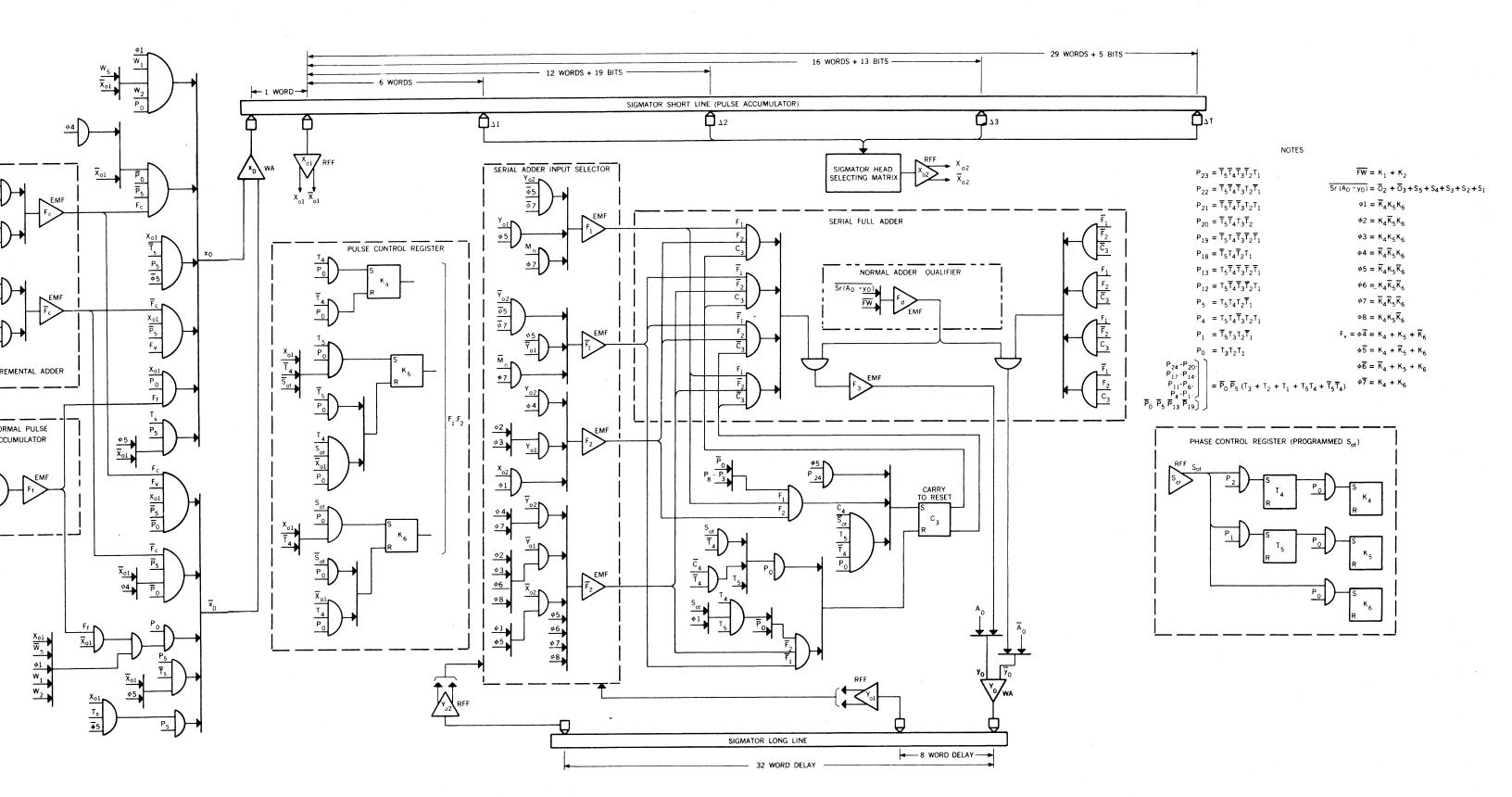

|      | 4-69.   | Sigmator                                                                                                                           | 4-82         |

|      |         | 4-70. Major Portions of the Sigmator                                                                                               | 4-83         |

|      |         | Flip-Flops                                                                                                                         | 4-83         |

|      |         | 4-72. Incremental Adder (One-Bit                                                                                                   |              |

|      |         | Adder-Subtractor)                                                                                                                  | 4-83         |

|      |         | 4-73. Pulse Accumulator (Sigmator Short Line)                                                                                      | 4-83         |

|      |         | 4-74. Serial Adder Input Selector                                                                                                  | 4-83         |

|      |         | 4-75. Phase Control Register                                                                                                       | 4-86         |

|      |         | 4-76. Serial Full Adder (Two-Input Adder).                                                                                         | 4-86         |

|      |         | 4-77. Integrand Register (Sigmator                                                                                                 | 4 0/         |

|      |         | Long Line)                                                                                                                         | 4-86<br>4-86 |

|      |         | 4-78. Input-Output Selector                                                                                                        | 4-86         |

|      |         | 4-79. Functional Cycle                                                                                                             | 4-88         |

|      |         | 4-81. Phase 1                                                                                                                      | 4-88         |

|      |         | 4-82. Phase 2                                                                                                                      | 4-88         |

|      |         | 4-83. Phase 3                                                                                                                      | 4-88         |

|      |         | 4-84. Phase 4                                                                                                                      | 4-89         |

|      |         | 4-85. Phase 5                                                                                                                      | 4-89         |

|      |         | 4-86. Phase 6                                                                                                                      | 4-89         |

| Section |                                                                      |                                                                                                                                                                                          | Page                                                               |

|---------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| IV (C   | ont.)                                                                |                                                                                                                                                                                          |                                                                    |

|         |                                                                      | 4-87. Phase 7                                                                                                                                                                            | 4-89<br>4-89<br>4-91<br>4-105                                      |

| v       | PROG                                                                 | RAMMING                                                                                                                                                                                  | 5-1                                                                |

|         | 5-1.<br>5-2.<br>5-3.<br>5-4.<br>5-5.<br>5-6.<br>5-7.<br>5-8.<br>5-9. | Introduction Main Memory Control States Variations of States Instruction Word Format Data Word Format Order Format Computation Time Store Orders 5-10. Normal Store 5-11. Modified Store | 5-1<br>5-1<br>5-3<br>5-4<br>5-4<br>5-7<br>5-8<br>5-8               |

|         | 5-13.<br>5-17.                                                       | 5-12. Discrete Orders  Data  5-14. Binary Numbers  5-15. Conversion  5-16. Positive and Negative Numbers  Sample Program                                                                 | 5-8<br>5-8<br>5-8<br>5-12<br>5-12                                  |

| VI      |                                                                      | TENANCE                                                                                                                                                                                  | 6-1                                                                |

|         | 6-1.<br>6-2.                                                         | General                                                                                                                                                                                  | 6-1<br>6-1                                                         |

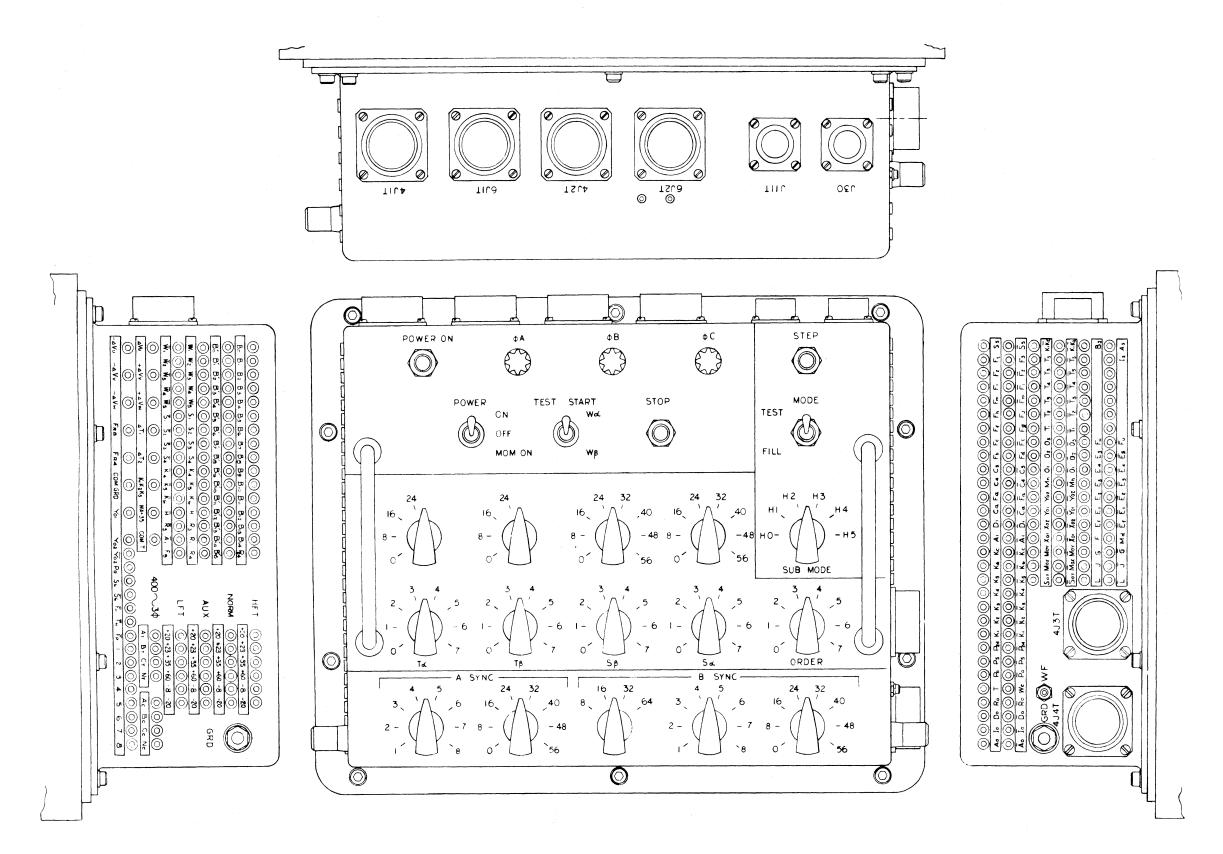

| VII     |                                                                      | Description                                                                                                                                                                              | 7-1 7-1 7-1 7-2 7-2 7-2 7-4 7-8 7-13 7-13 7-16 7-16 7-16 7-17 7-17 |

| Section | n<br>-         |                                 | Page |

|---------|----------------|---------------------------------|------|

| VII (   | Cont.)         |                                 |      |

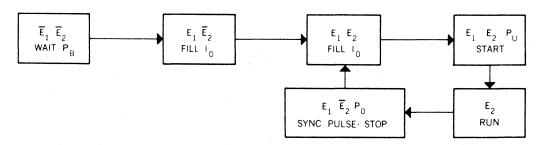

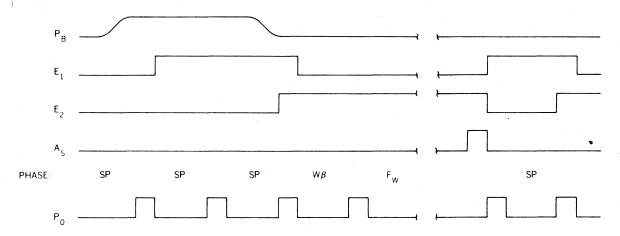

|         | 7-17.<br>7-18. | Fill and Test Logic             | 7-24 |

|         |                | Control of Computer             | 7-25 |

|         | 7-19.          | Operating Procedures            | 7-26 |

|         |                | 7-20. Equipment Necessary       | 7-26 |

|         |                | 7-21. Test Preparation          | 7-26 |

|         |                | 7-22. Tape Fill Procedure       | 7-27 |

|         |                | 7-23. Tape Check Procedure      | 7-28 |

|         |                | 7-24. Word Fill Procedure       | 7-28 |

|         | <b>5</b> 2/    | 7-25. Word Fill Check Procedure | 7-29 |

|         | 7-26.          | Definition of Symbols           | 7-30 |

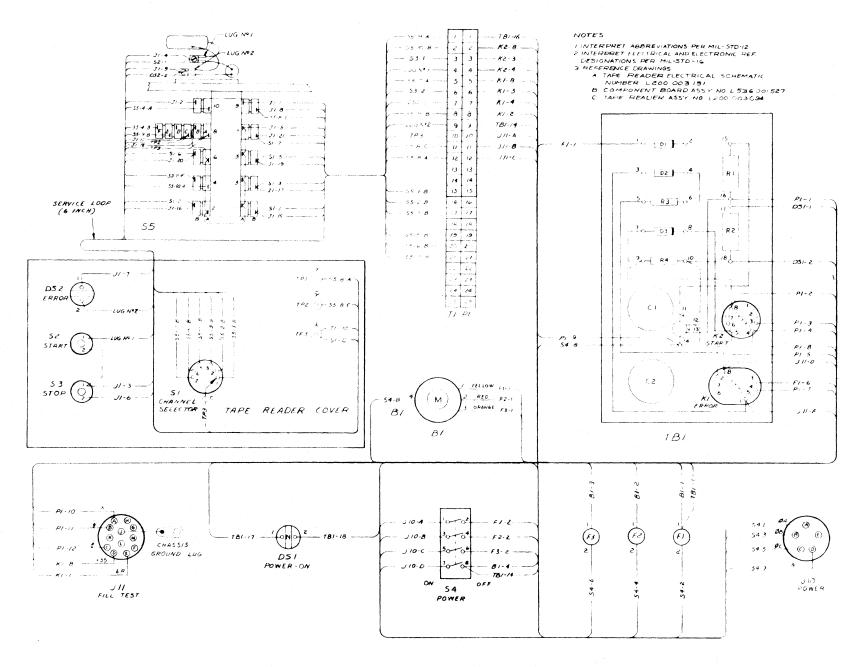

| VIII    | TAPE           | READER                          | 8-1  |

|         | 8 - 1.         | Description                     | 8-1  |

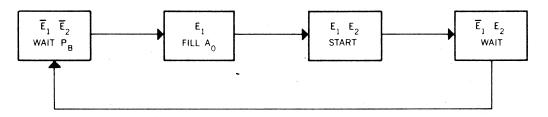

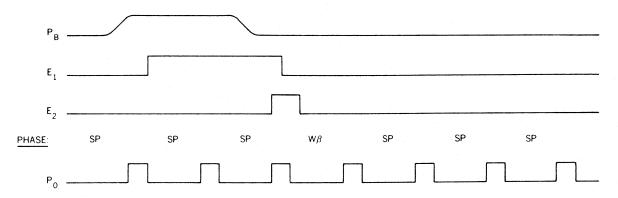

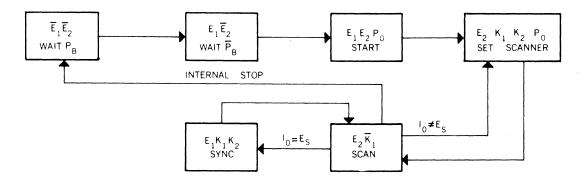

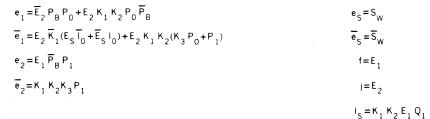

|         | 8-2.           | Theory of Operation             | 8-1  |

|         |                | 8-3. General                    | 8-1  |

|         |                | 8-4. Start                      | 8-3  |

|         |                | 8-5. Reading Cycle              | 8-4  |

|         |                | 8-6. Stop                       | 8-4  |

|         |                | 8-7. Check                      | 8-5  |

|         |                | 8-8. Controls                   | 8-5  |

|         |                | 8-9. Operation                  | 8-5  |

|         | 8-10.          | Maintenance                     | 8-6  |

| IX      | CARD           | CHECKER                         | 9-1  |

|         | 9-1.           | Description                     | 9-1  |

|         | 9-2.           | Theory of Operation             | 9-1  |

|         | ,              | 9-3. Logic Gates                | 9-2  |

|         |                | 9-4. Flip-Flops                 | 9-2  |

|         |                | 9-5. Emitter Followers          | 9-2  |

|         |                | 9-6. Read Flip-Flops            | 9-2  |

|         |                | 9-7. Write Amplifiers           | 9-4  |

|         |                | 9-8. Clock Generators           | 9-4  |

|         |                | 9-9. Head Selection Cards       | 9-4  |

| APPEN   | DIX A -        | WIRING TABLES                   | A-1  |

| APPEN   | DIX B -        | ADDITIONAL ILLUSTRATIONS        | B-1  |

# LIST OF TABLES

| Table |                                       | Page |

|-------|---------------------------------------|------|

| 4-1   | Input-Output Selection Register Codes | 4-25 |

| 4-2   | Error Determining Truth Table         |      |

| 5-l   | Instruction Word Format               |      |

| 5-2   | Data Word Format                      |      |

| 5-3   | Order Coding                          |      |

| 5-4   | Computation and Word Times            | 5-7  |

| 5-5   | Store Order Coding                    |      |

| 5-6   | Discrete Order Coding                 |      |

| 5-7   | Binary and Decimal Equivalents        |      |

| 5-8   | The Powers of 2                       |      |

| 5-9   | Positive Coded Operand                | 5-12 |

| 5-10  | Negative Coded Operand                | 5-12 |

| 5-11  | Programmed and Coded Problem          |      |

# LIST OF ILLUSTRATIONS

| Figure |                                                    |    | Page  |

|--------|----------------------------------------------------|----|-------|

| 2-1    | Computer Component Location                        | •  | 2-3   |

| 3 - 1  | Clock Amplifier, Schematic Diagram                 |    | 3 - 3 |

| 3-2    | Flip-Flop, Schematic Diagram                       |    | 3-5   |

| 3-3    | Emitter Follower, Schematic Diagram                |    | 3 - 7 |

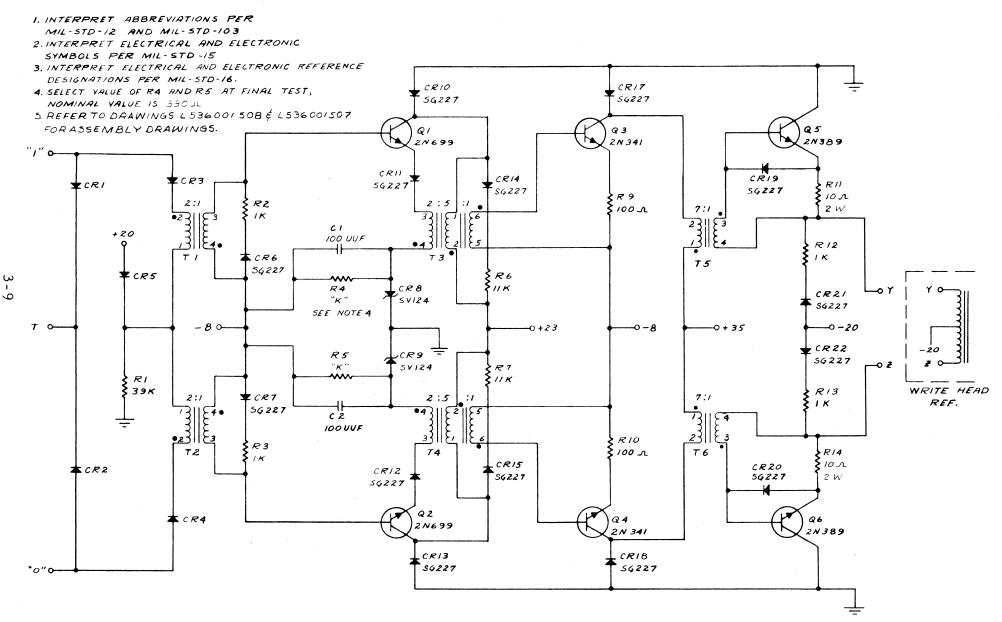

| 3-4    | Write Amplifier, Schematic Diagram                 |    | 3-9   |

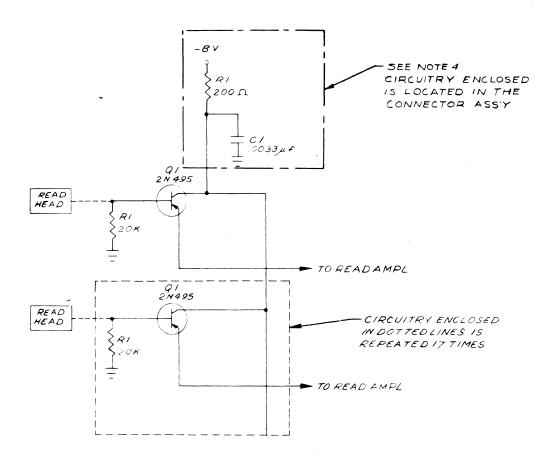

| 3-5    | Preamplifier, Schematic Diagram                    |    | 3-10  |

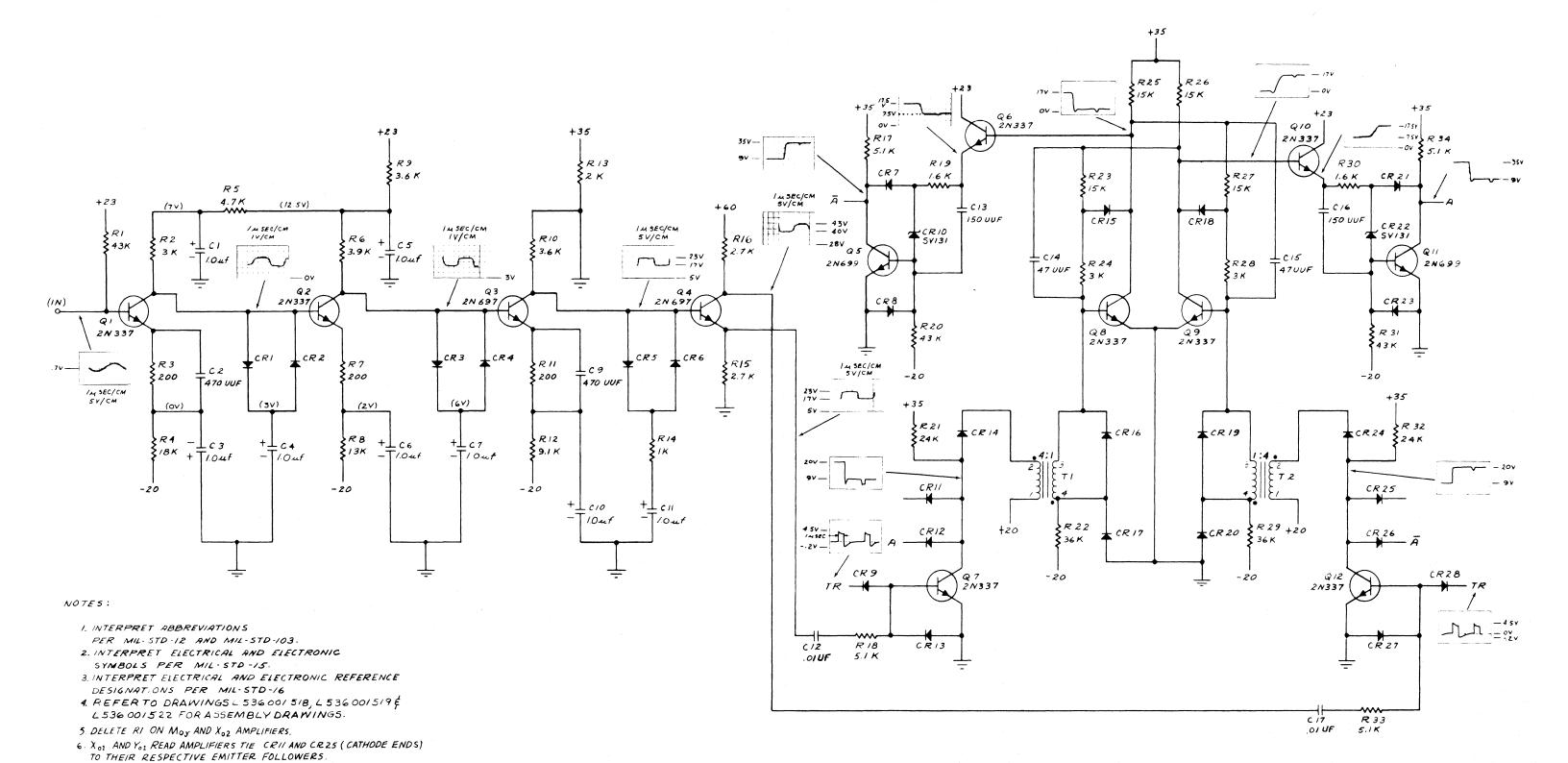

| 3-6    | Read Amplifier, Schematic Diagram                  |    | 3-11  |

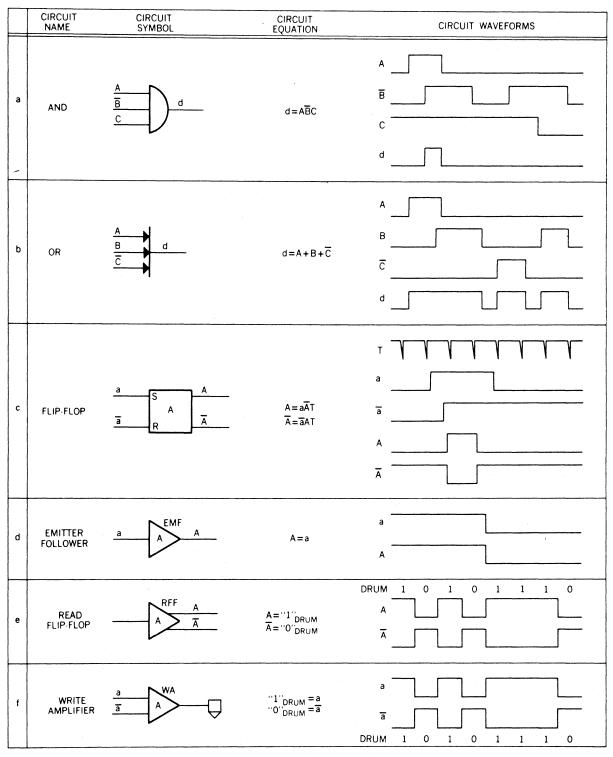

| 4-1    | Circuit Symbology                                  | •  | 4-3   |

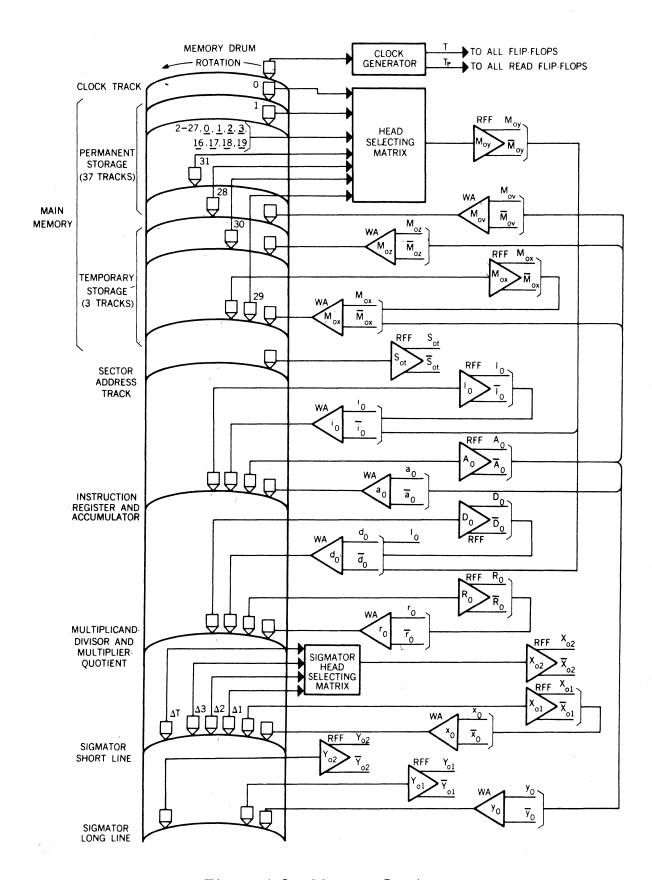

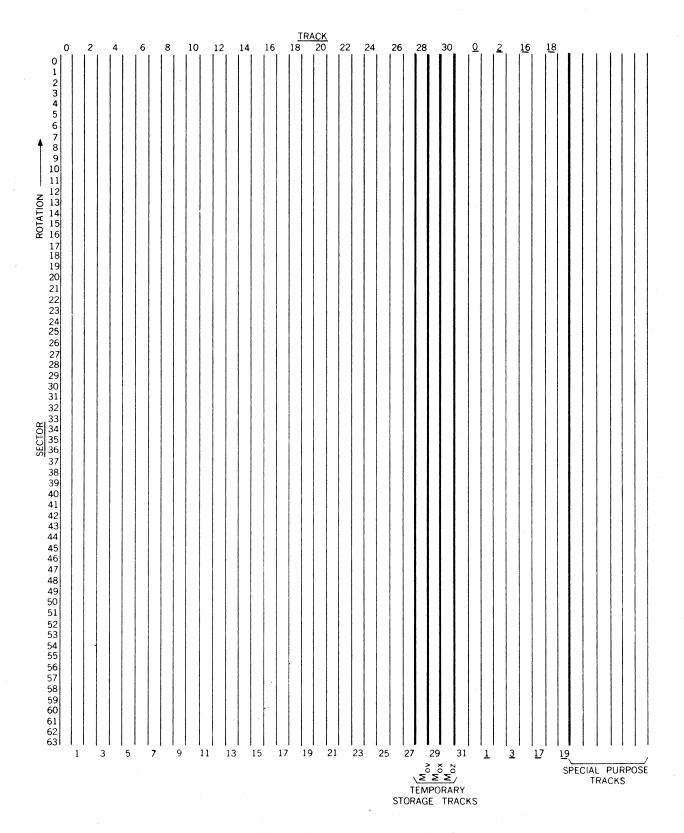

| 4-2    | Memory Section                                     |    |       |

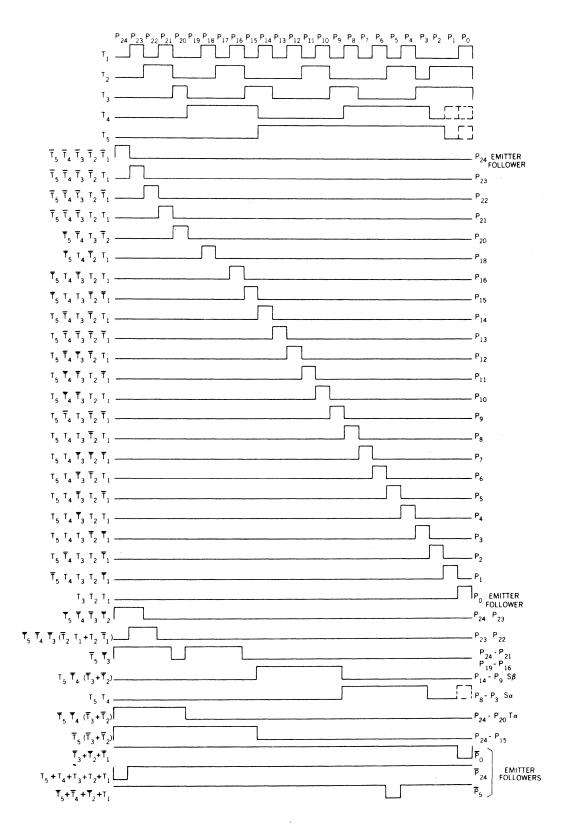

| 4-3    | Basic Timing Diagram                               | •, | 4-15  |

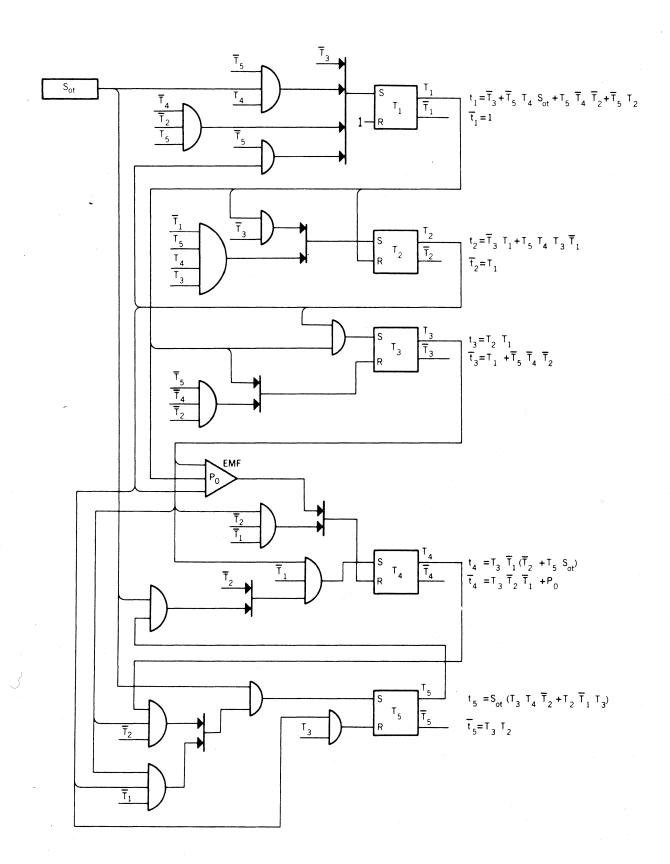

| 4-4    | Pulse Time Indicator, Logic Diagram                |    | 4-16  |

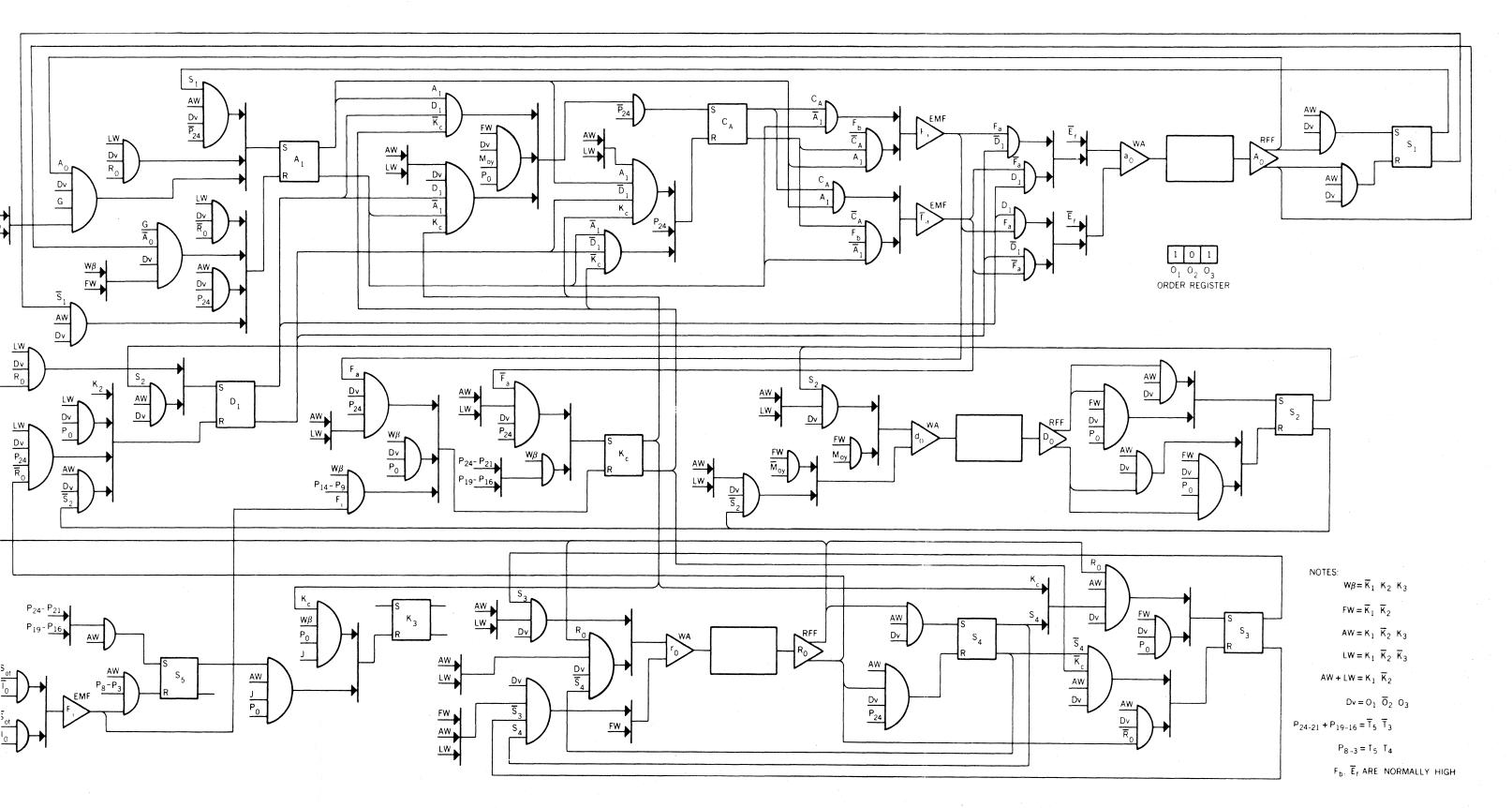

| 4-5    | Order Register, Logic and Timing Diagram           | •  | 4-20  |

| 4-6    | Track Selection Register, Logic and Timing Diagram | •  | 4-22  |

| 4-7    | Input-Output Selection Register, Logic and         |    |       |

|        | Timing Diagram                                     |    | 4-24  |

| 4-8    | Phase Sequencing Diagram                           |    | 4-27  |

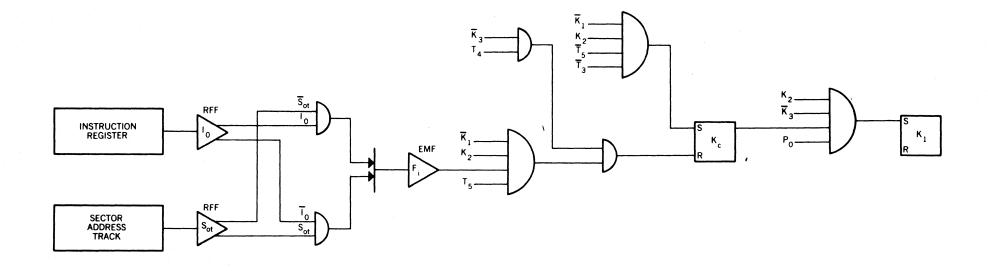

| 4-9    | Wait Alpha, Logic and Timing Diagram               |    | 4-29  |

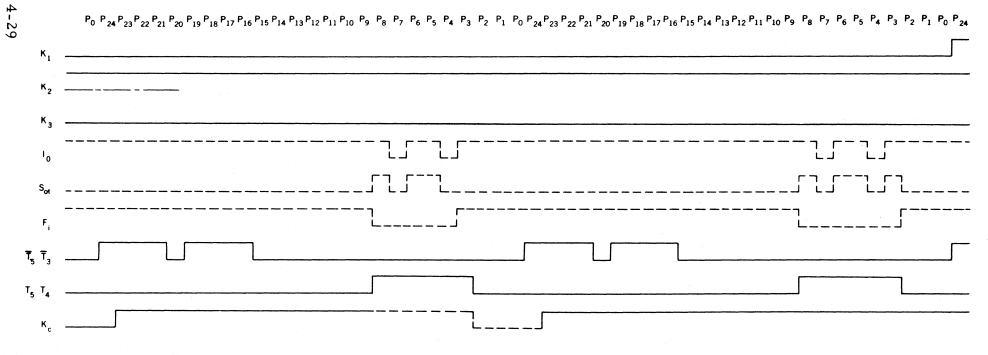

| 4-10   | Instruction Read-In, Logic Diagram                 |    | 4-30  |

| 4-11   | Serial Adder, Logic Diagram                        |    | 4-35  |

| 4-12   | Input and Output Operations, Logic Diagram         |    | 4-38  |

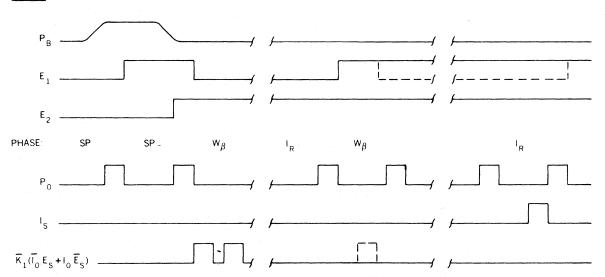

| 4-13   | External Control, Logic and Timing Diagram         |    | 4-43  |

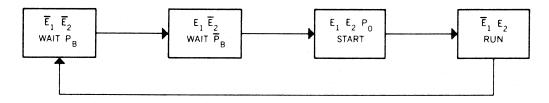

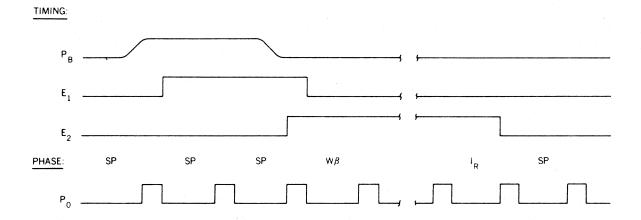

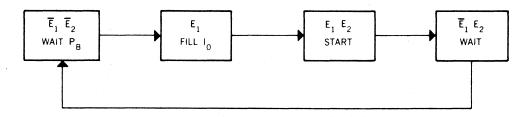

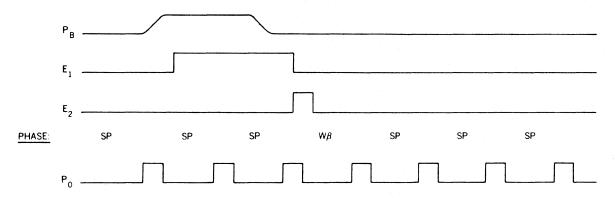

| 4-14   | Internal Idling Control, Logic Diagram             |    | 4-46  |

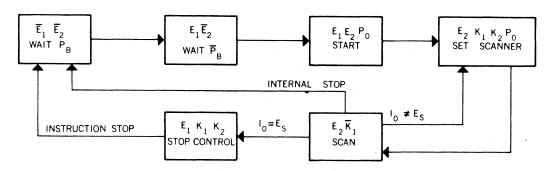

| 4-15   | Internal Idling Control, Timing Diagram            |    | 4-48  |

| 4-16   | Clear and Add Order, Logic and Timing Diagram      |    | 4-51  |

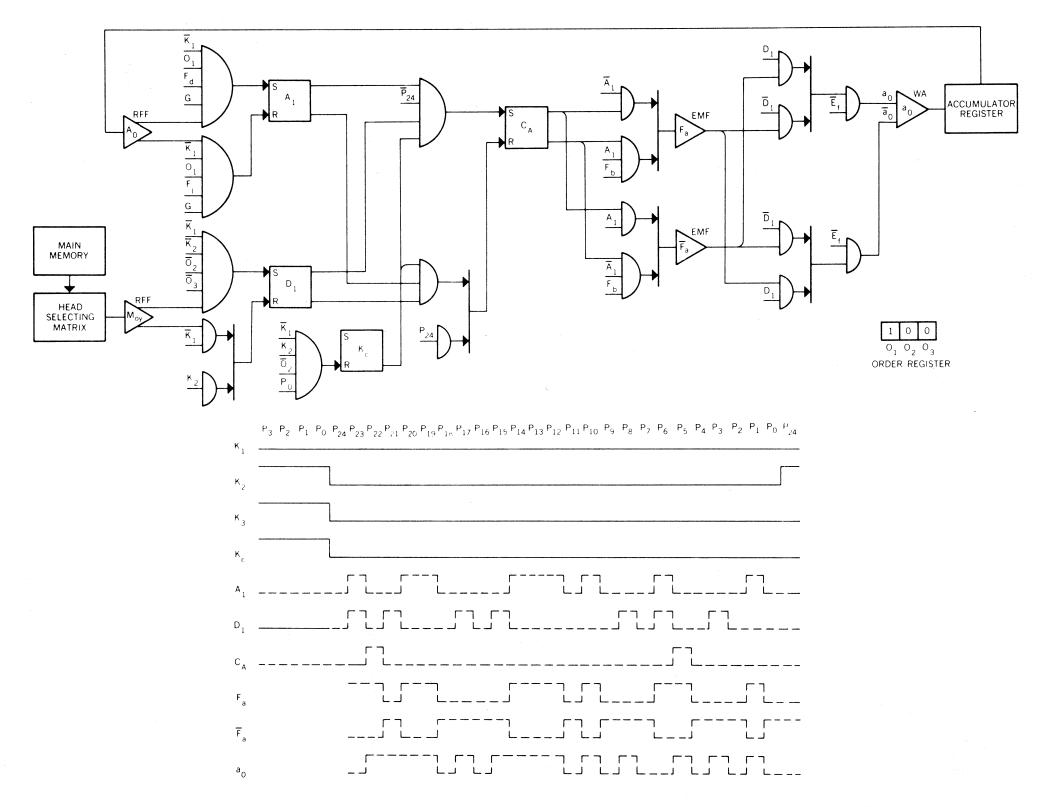

| 4-17   | Add Order, Logic and Timing Diagram                |    | 4-53  |

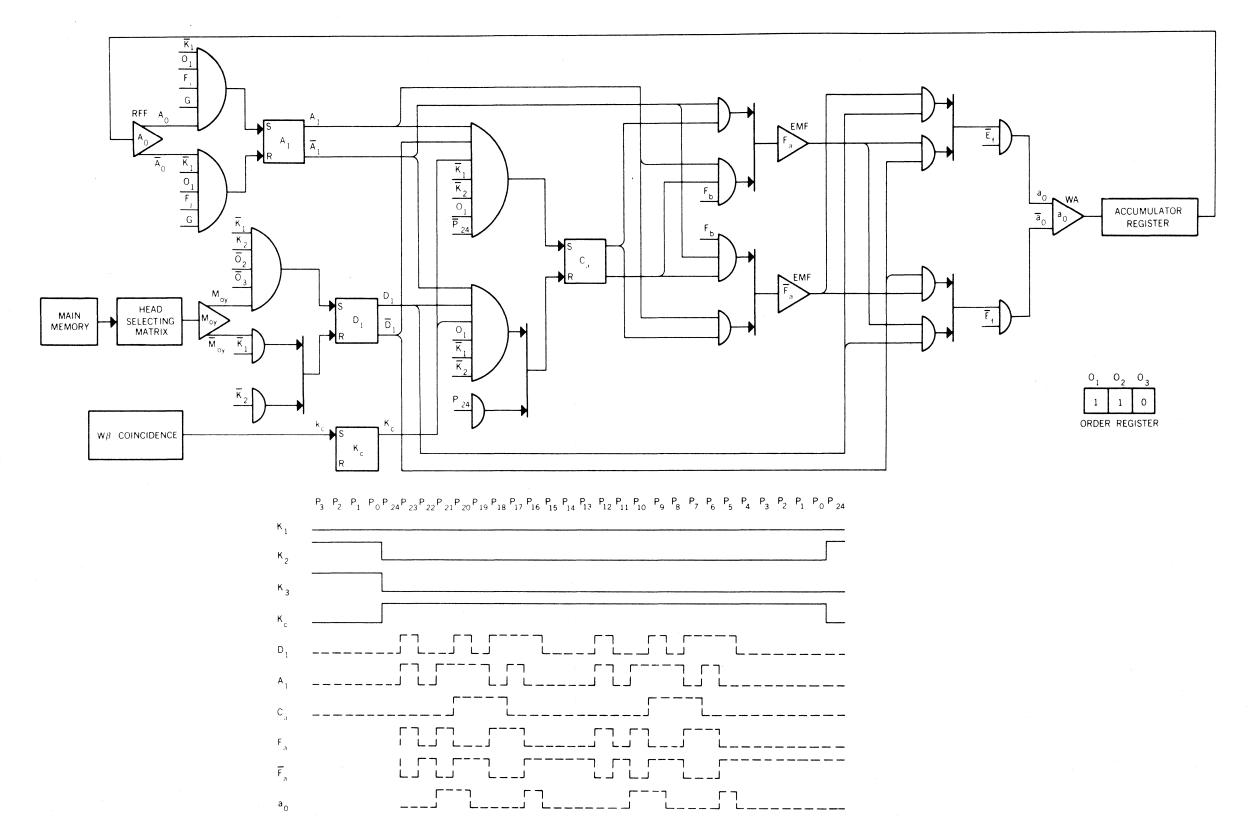

| 4-18   | Subtract Order, Logic and Timing Diagram           |    | 4-55  |

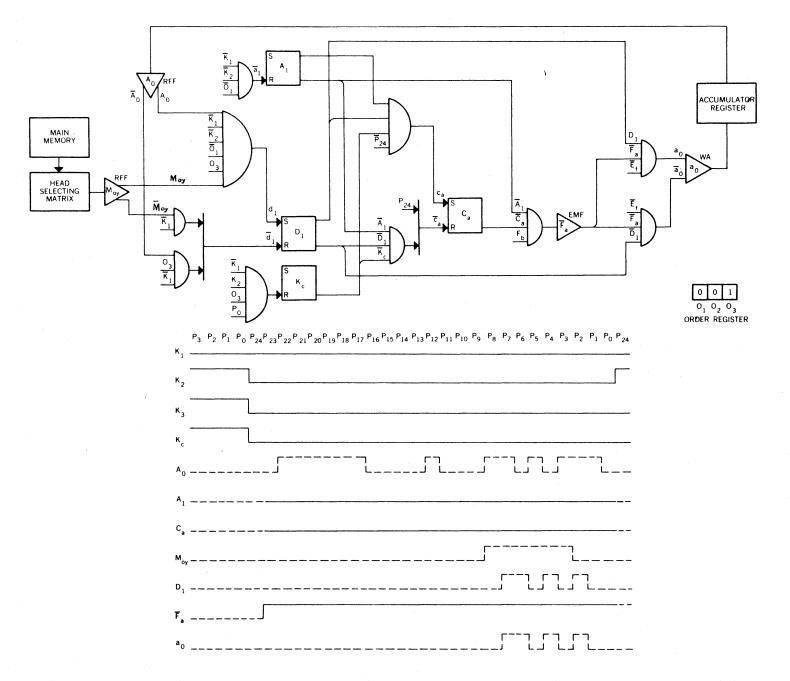

| 4-19   | Extract Order, Logic and Timing Diagram            |    | 4-57  |

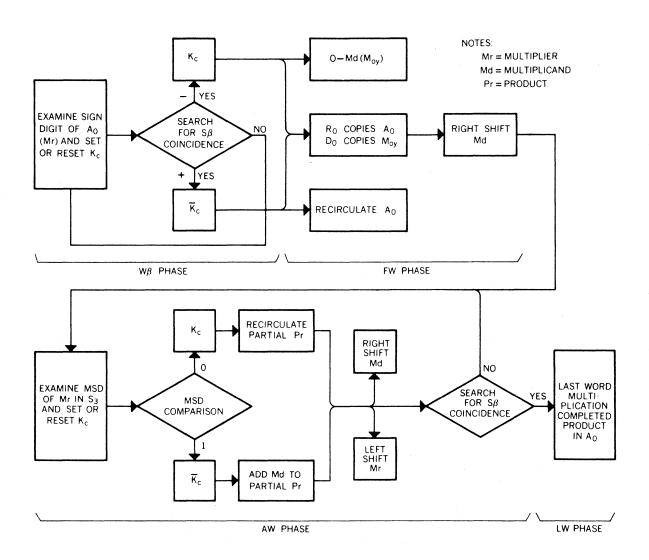

| 4-20   | Multiply Order, Flow Diagram                       | •  | 4-65  |

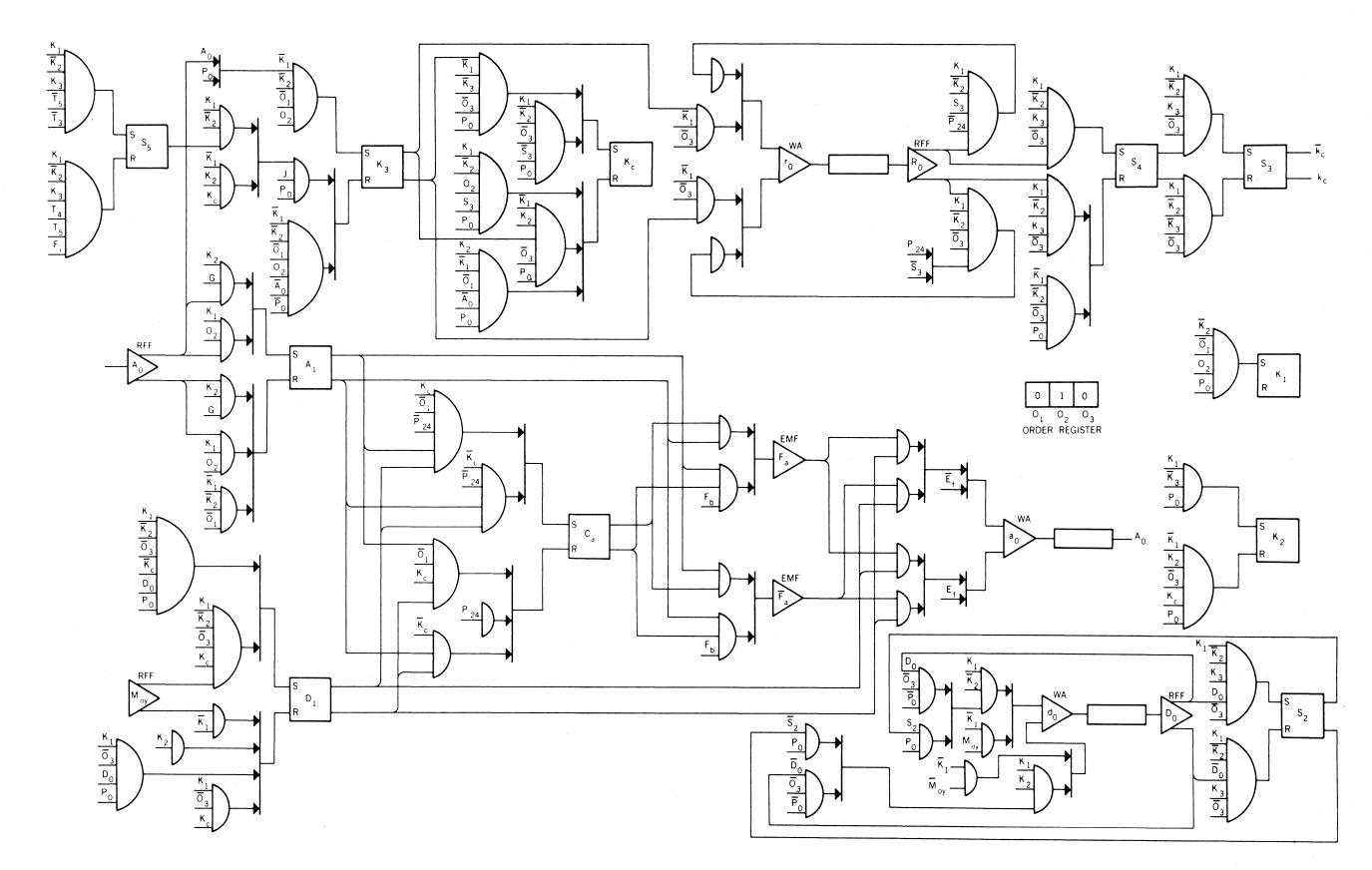

| 4-21   | Multiply Order, Logic Diagram                      | •  | 4-67  |

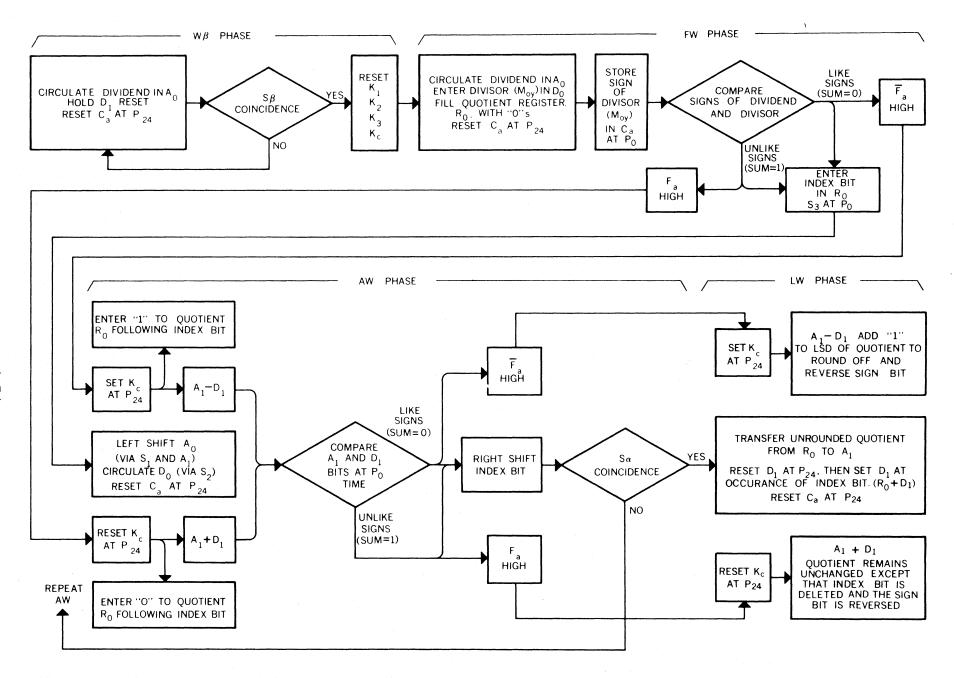

| 4-22   | Divide Order Flow Diagram                          | •  |       |

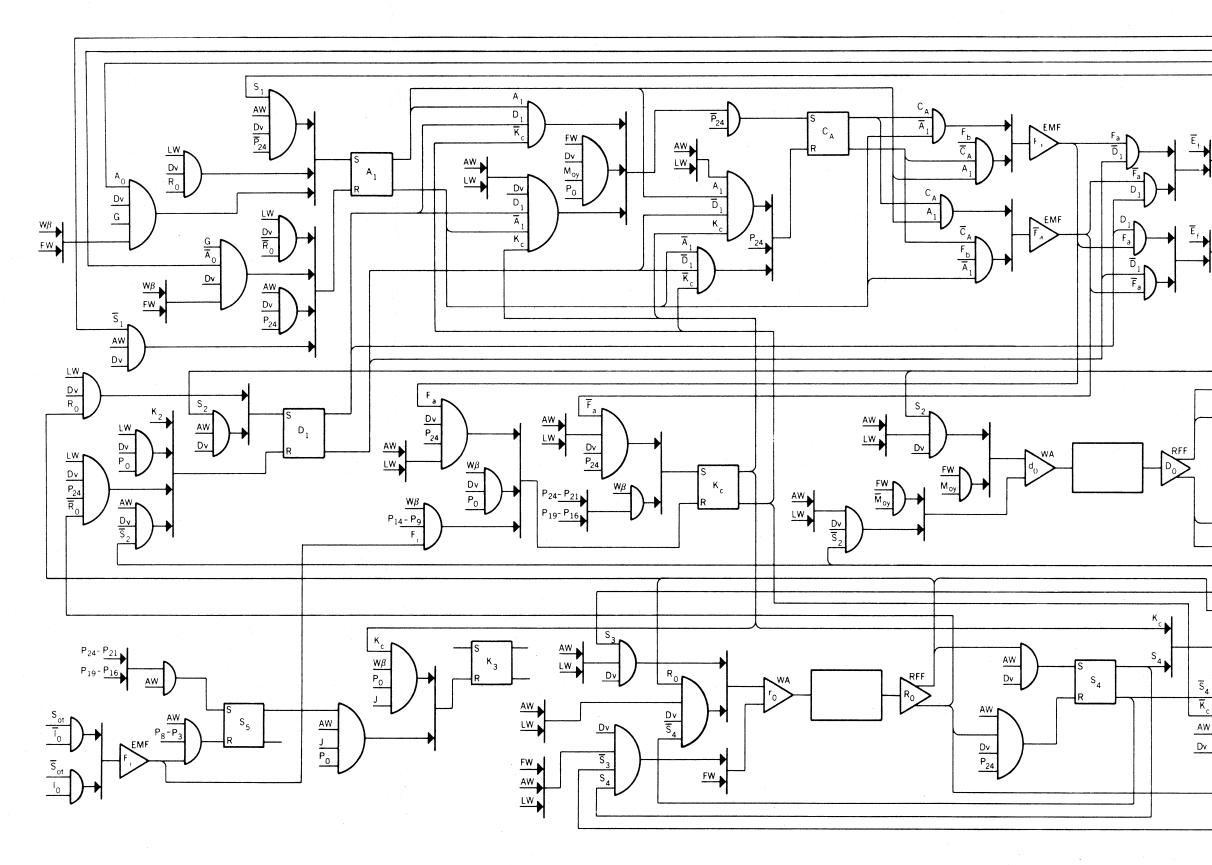

| 4-23   | Divide Order, Flow Diagram                         | •  | 1 75  |

| 4-23   | Divide Order, Logic Diagram                        | •  | 1 01  |

| 4-24   | Sigmator, Flow Diagram                             | •  | 4-04  |

| 5-1    | Sigmator, Logic Diagram                            | •  | 4-00  |

| 7-1    | Main Memory Layout                                 | •  | 7-3   |

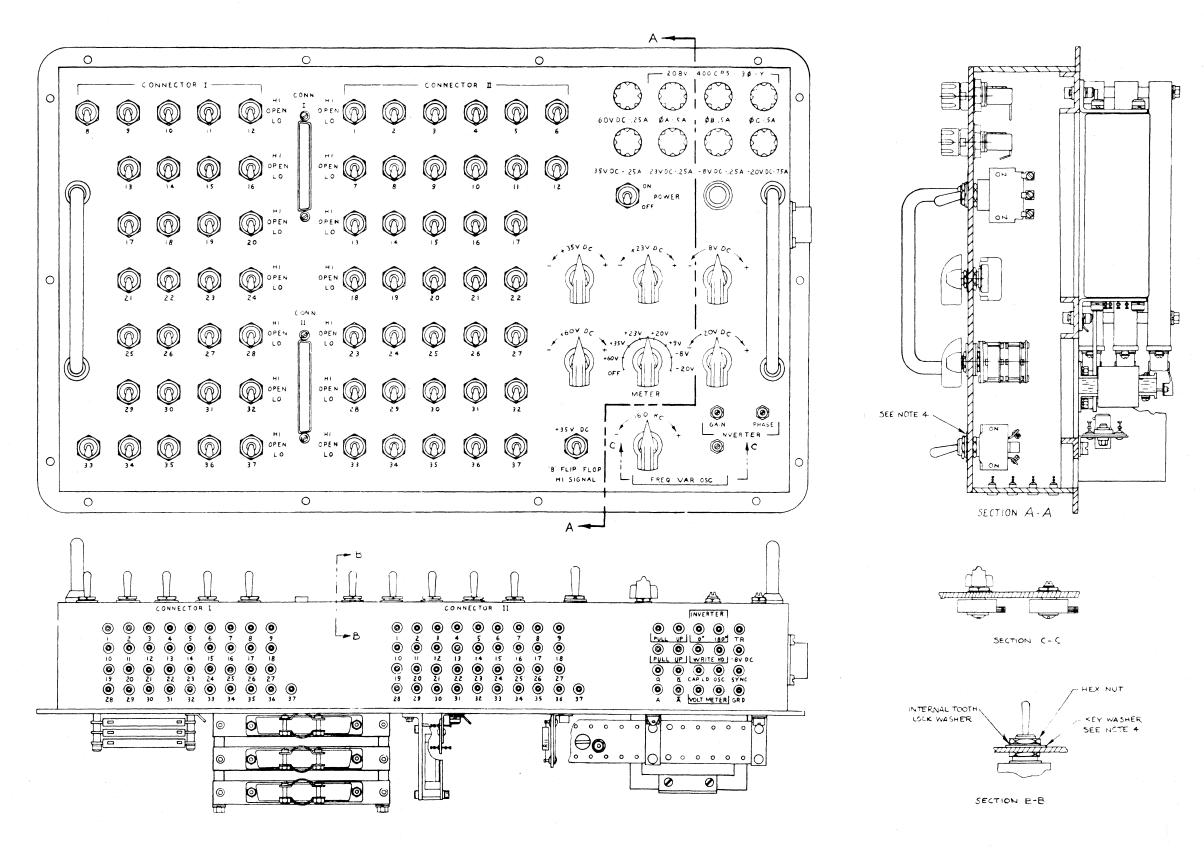

| 7-2    | Fill-Test Control Panel                            | •  |       |

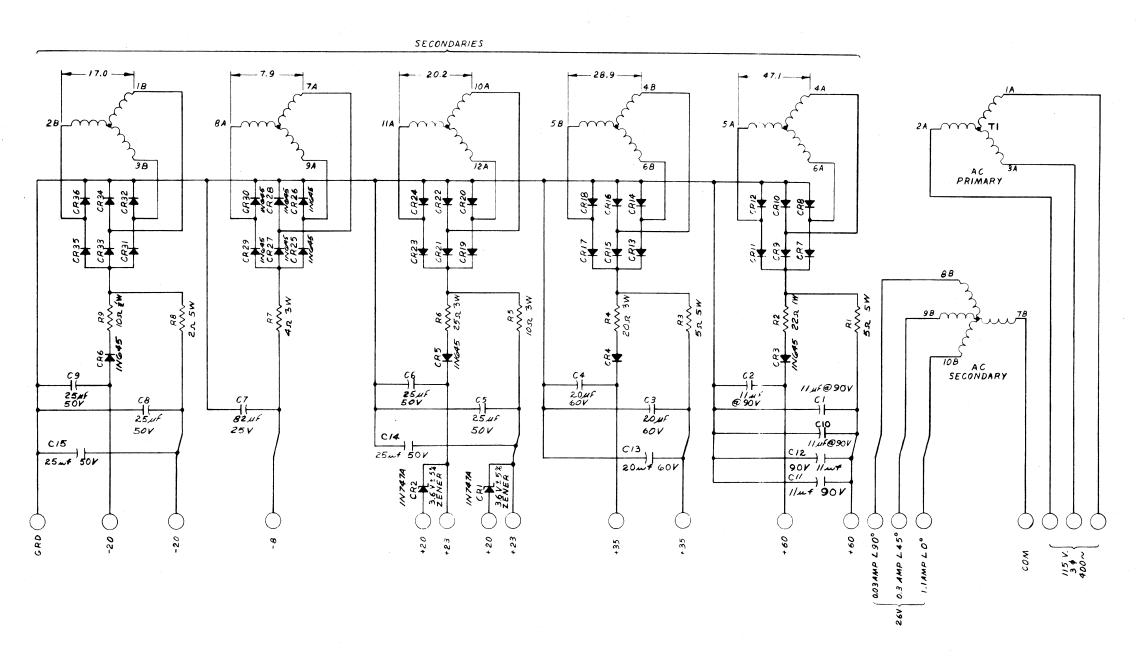

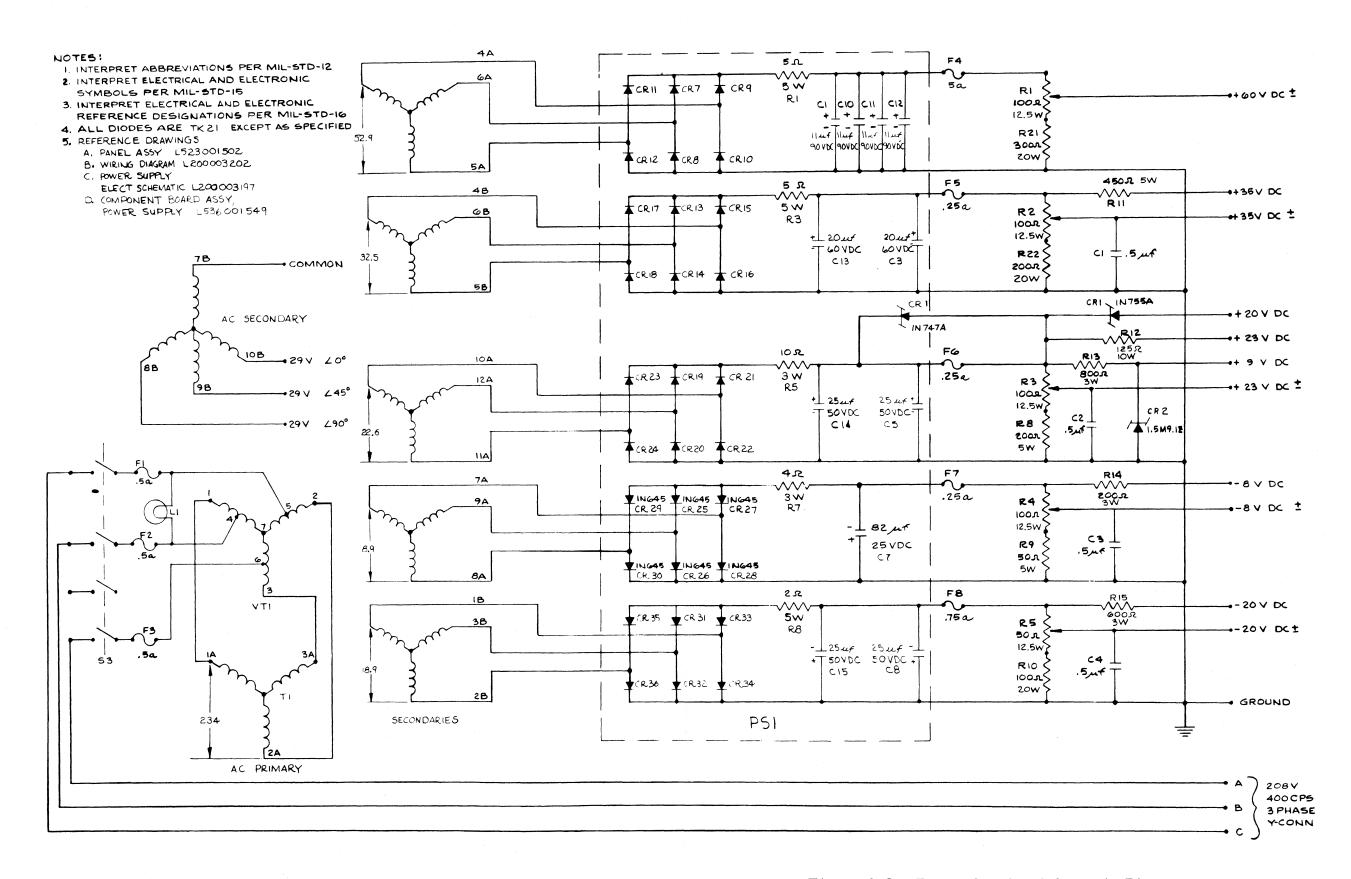

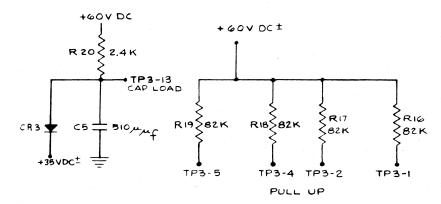

| 7-3    | Power Supply, Schematic Diagram                    |    | 7-5   |

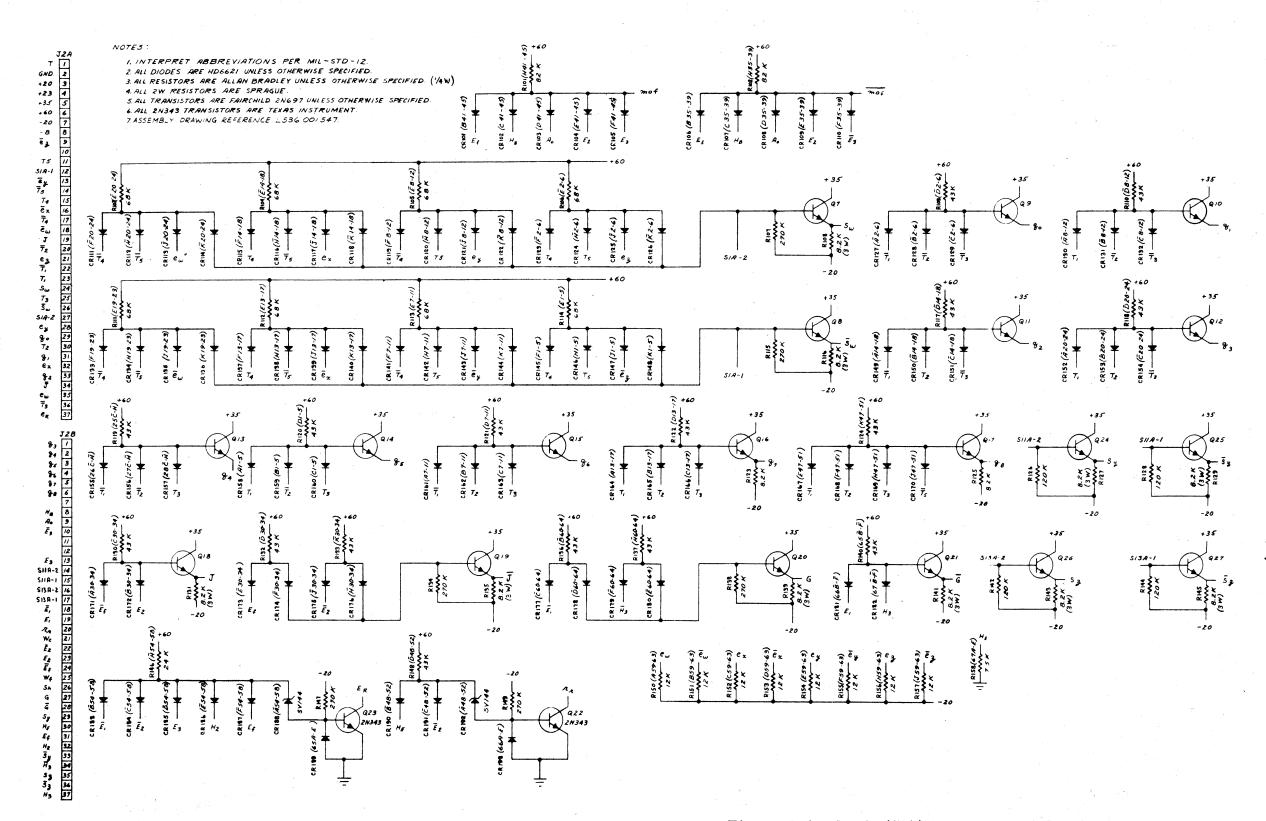

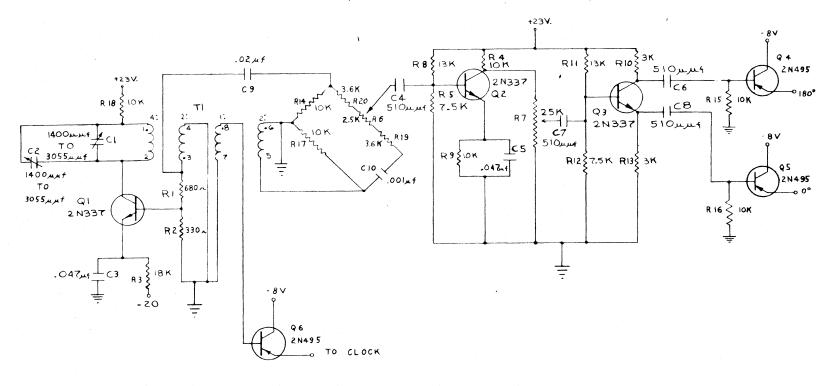

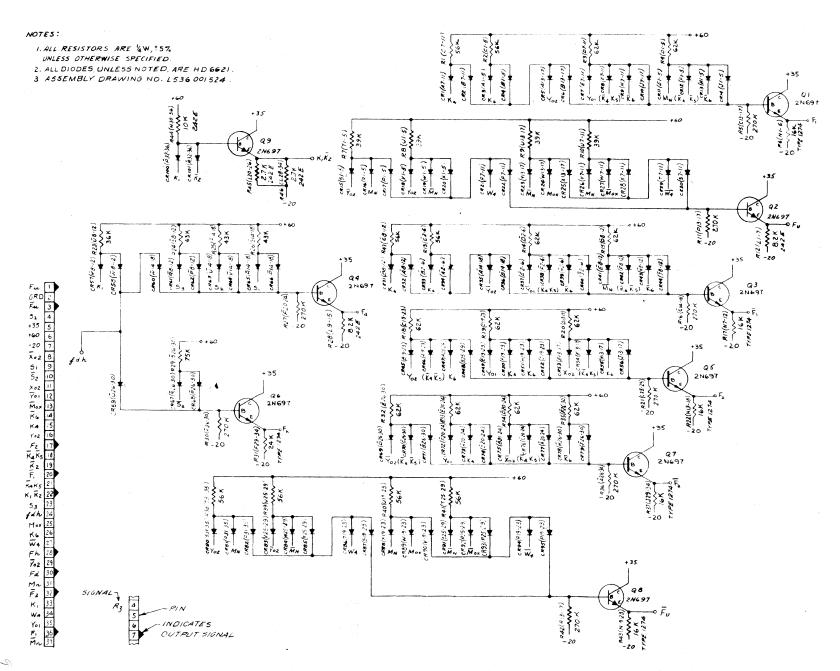

|        | Logic (FF), Schematic Diagram                      |    | 7-6   |

| 7-4    | Logic (WA), Schematic Diagram                      |    | 7-7   |

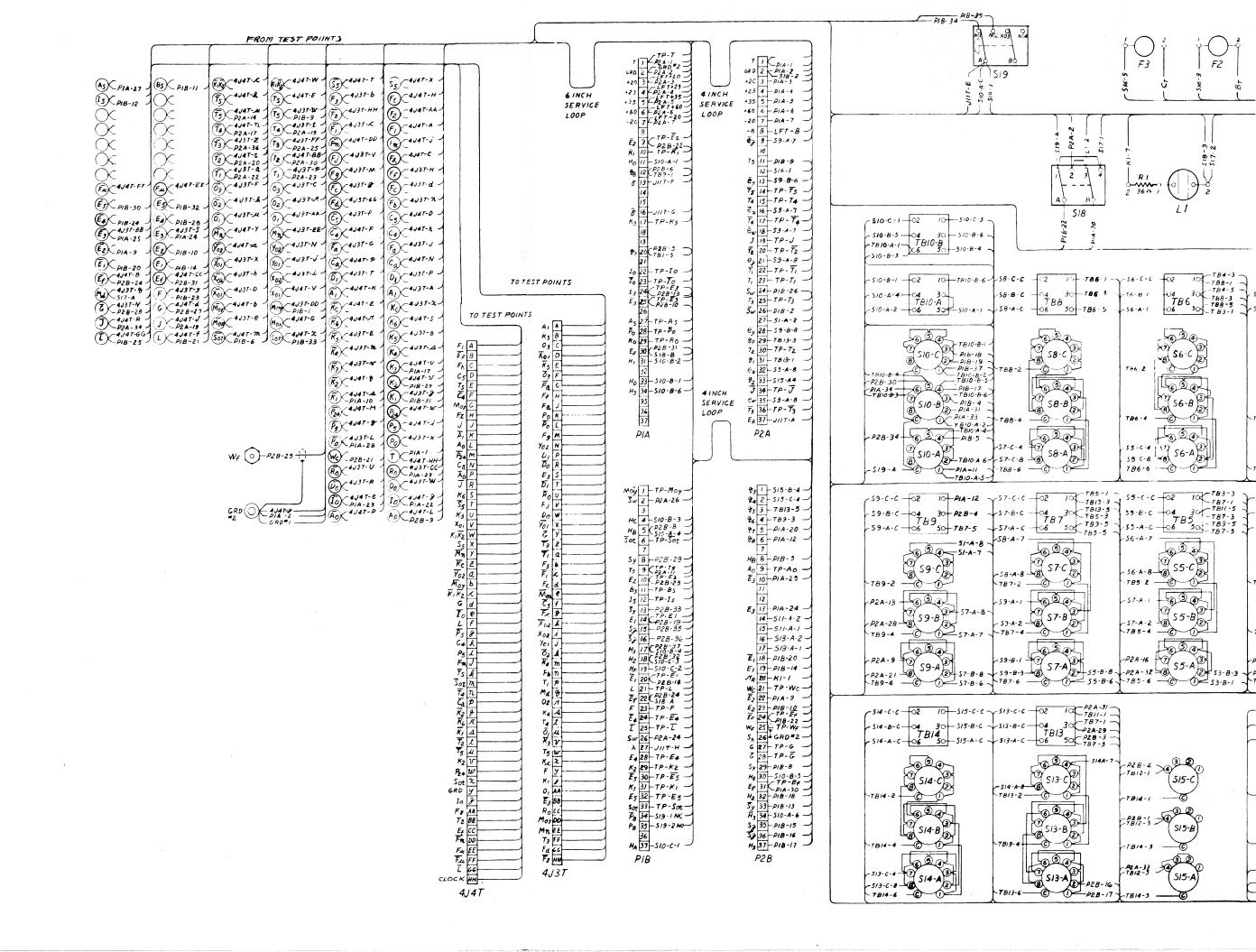

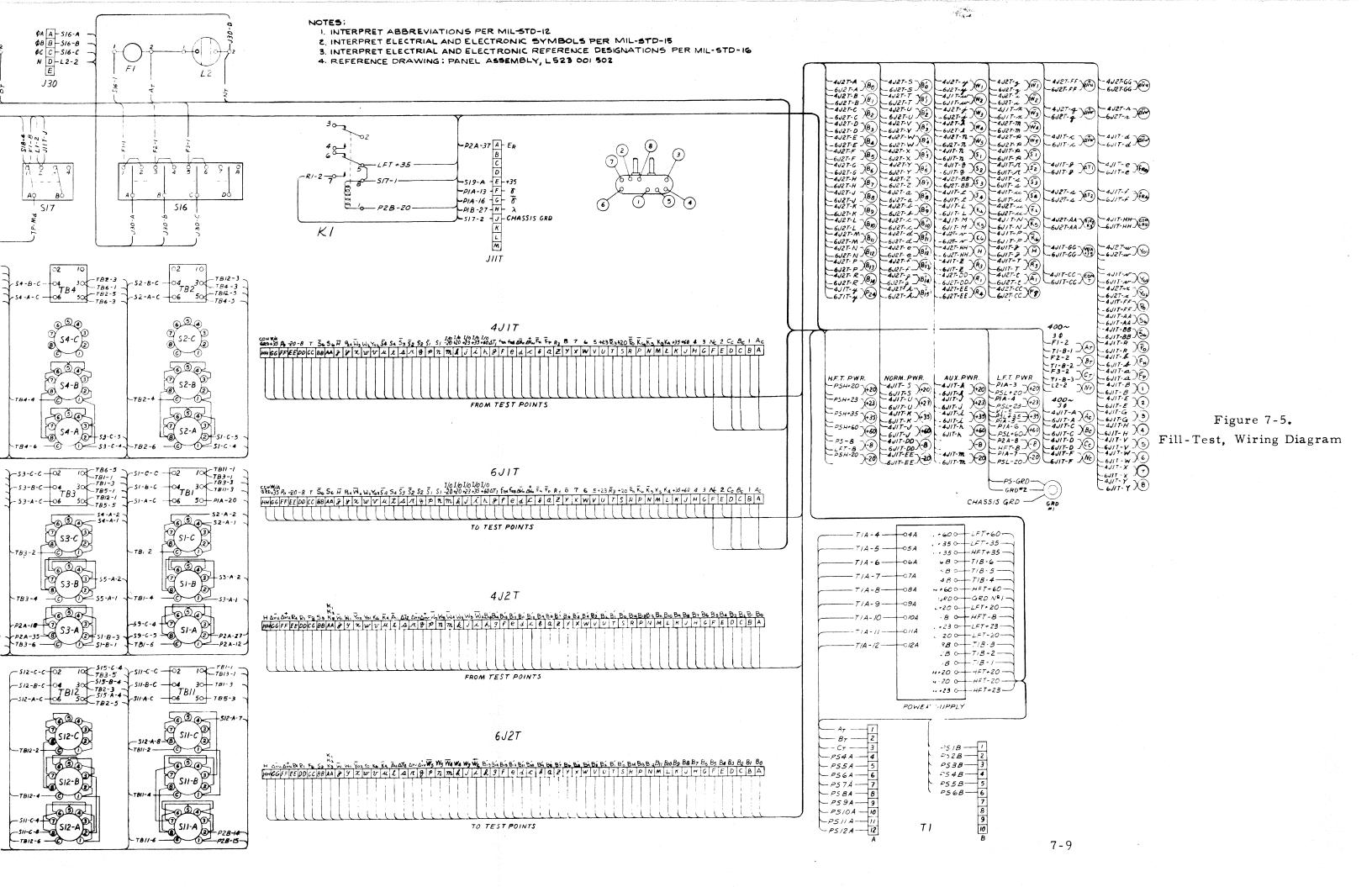

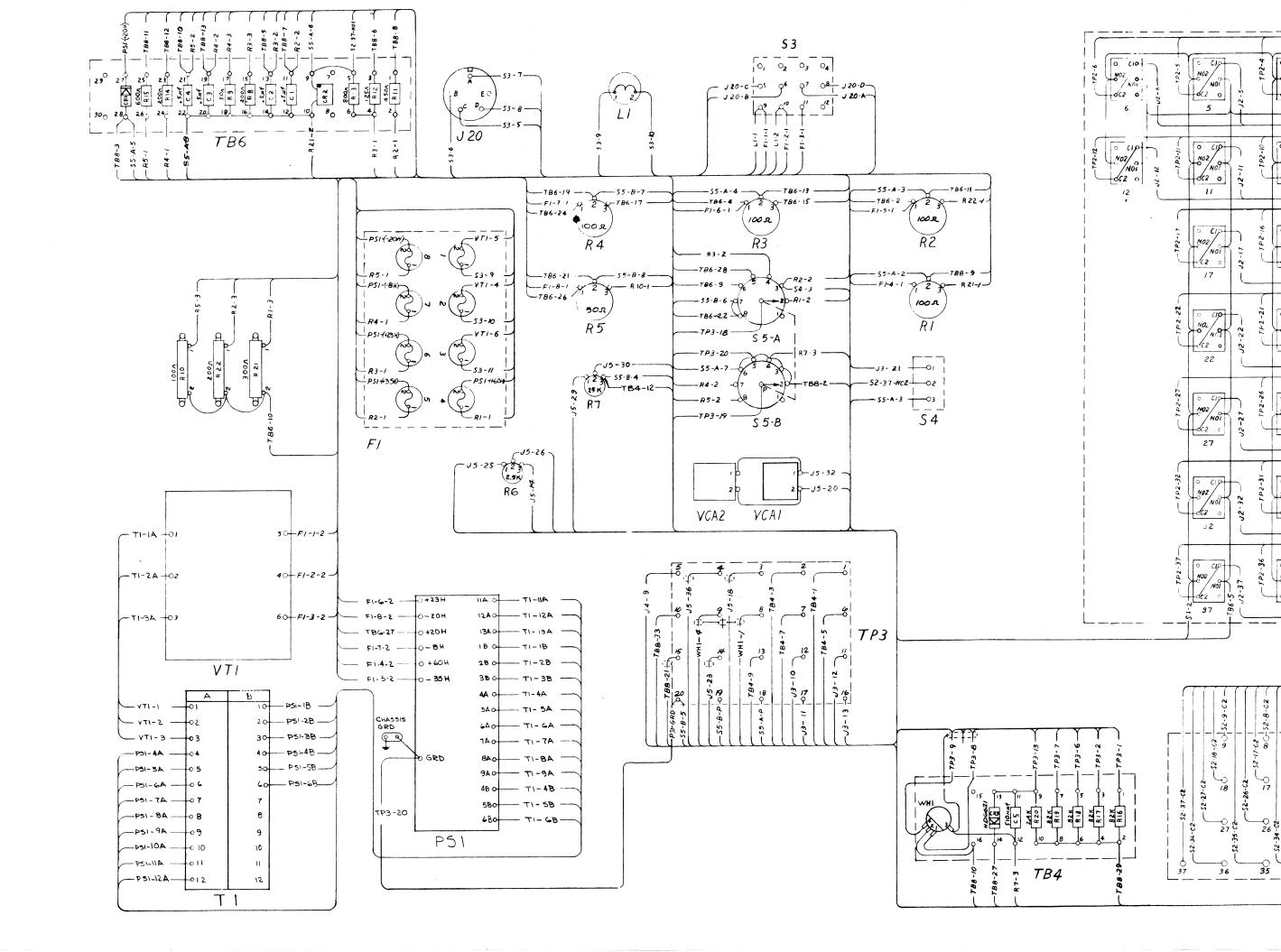

| 7-5    | Fill-Test, Wiring Diagram                          | •  | 7-9   |

| 7-6    | Test Mode, Loop Sub-mode                           |    | 7-10  |

| 7-7    | Test Mode, One Step Sub-mode                       |    | 7-11  |

| 7-8    | Test Mode, Instruction Fill Sub-mode               |    | 7-12  |

| 7-9    | Test Mode, Accumulator Fill Sub-mode               |    | 7-14  |

| 7-10   | Test Mode, Instruction Sync Sub-mode               |    | 7-15  |

| 7-11   | Test Mode, Instruction Stop Sub-mode               |    | 7-17  |

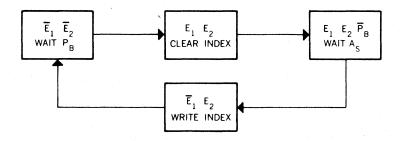

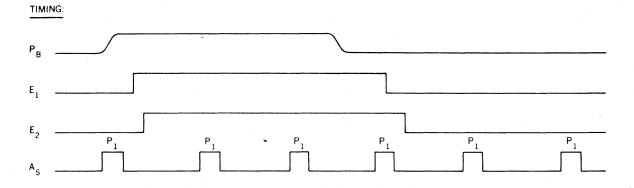

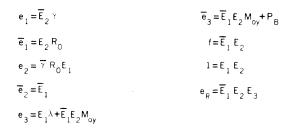

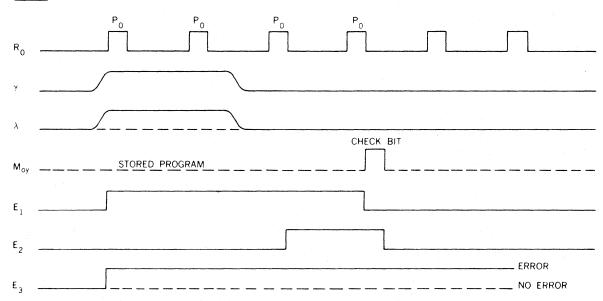

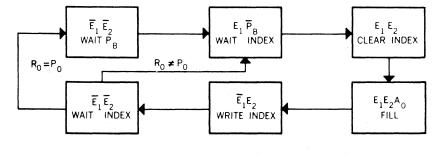

| 7-12   | Fill Mode, Build Index Sub-mode                    |    | 7-18  |

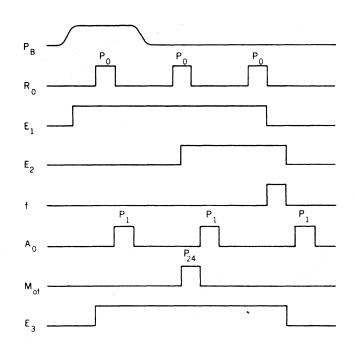

| 7-13   | Fill Mode, Tape Fill Sub-mode                      | •  | 7-20  |

| 7-14   | Fill Mode, Check Sub-mode                          |    | 7-22  |

| 7-15   | Fill Mode, Word Fill Sub-mode                      |    | 7-23  |

# LIST OF ILLUSTRATIONS (Cont.)

| Figure |                                                       | Page |

|--------|-------------------------------------------------------|------|

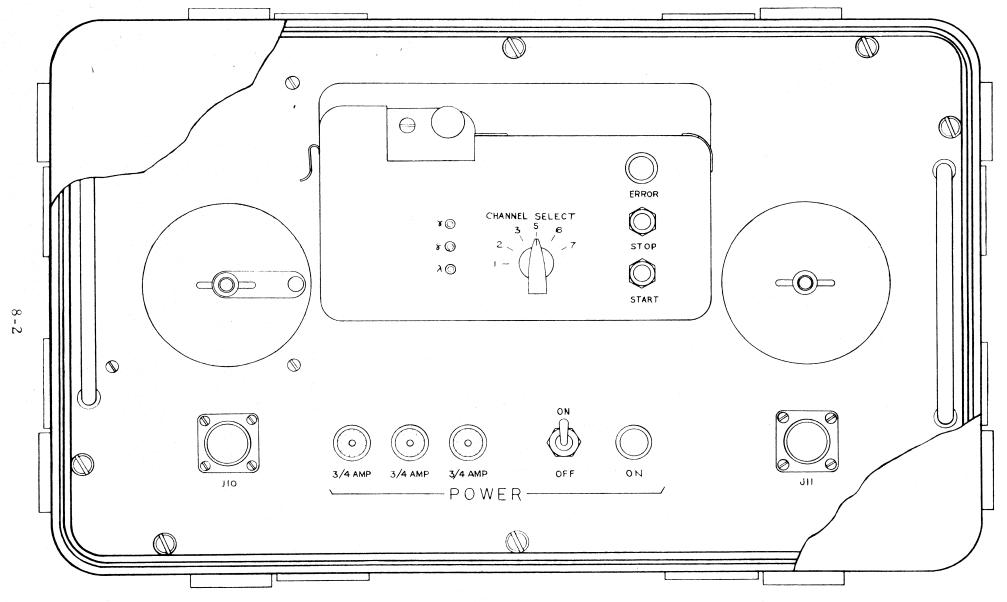

| 8-1    | Tape Reader Control Panel                             | 8-2  |

| 8-2    | Tape Reader, Schematic Diagram                        |      |

| 8-3    | Tape Reader, Wiring Diagram                           |      |

| 9-1    | Card Checker Control Panel                            | 9-3  |

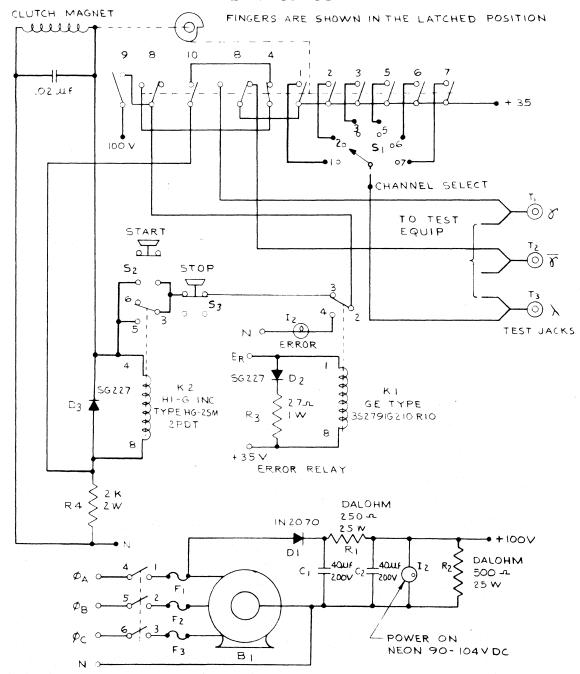

| 9-2    | Power Supply, Schematic Diagram                       |      |

| 9-3    | Inverter Oscillator, Schematic Diagram                |      |

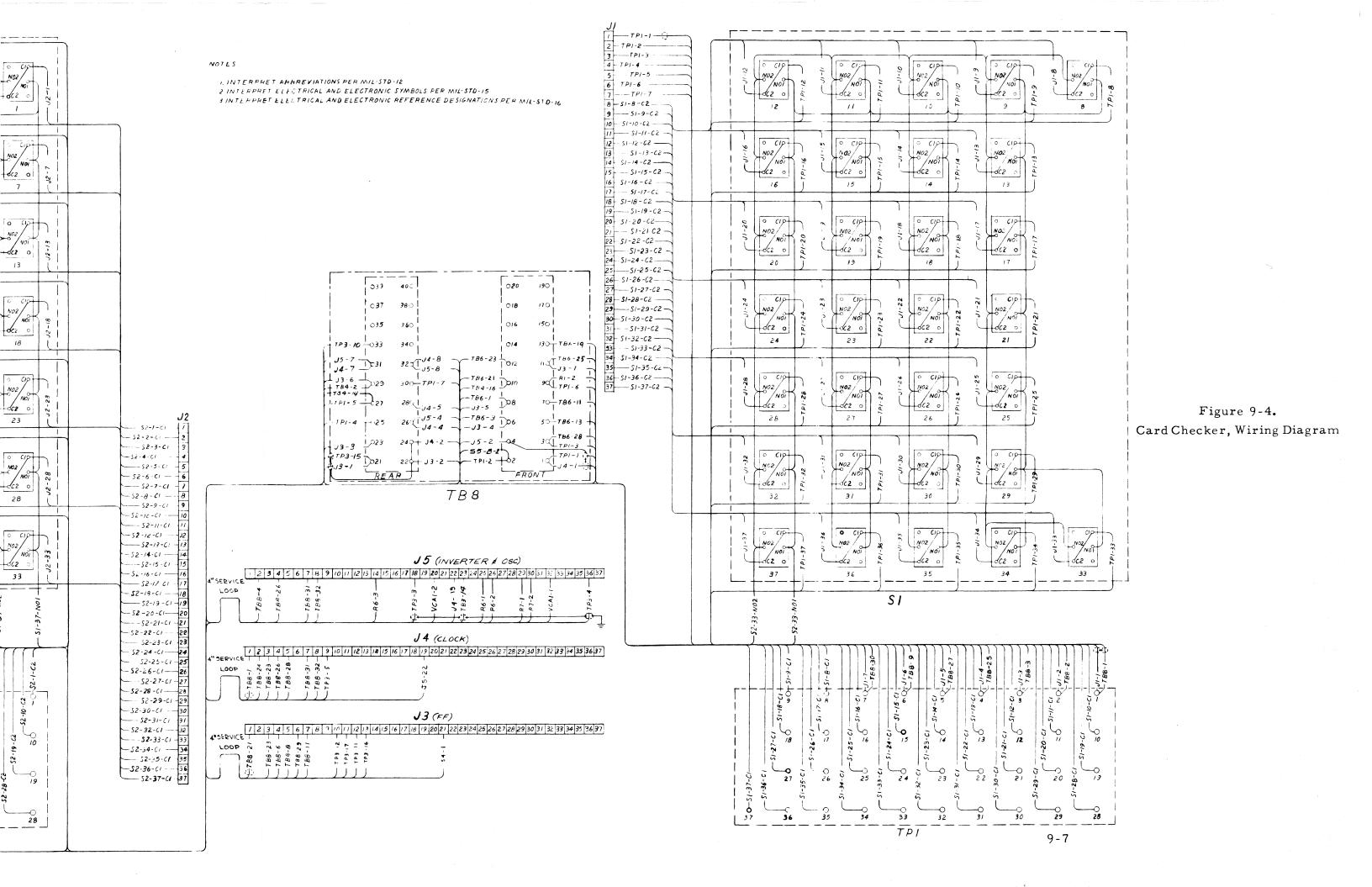

| 9-4    | Card Checker, Wiring Diagram                          |      |

| 9-5    | Test Circuits (FF), Schematic Diagram                 |      |

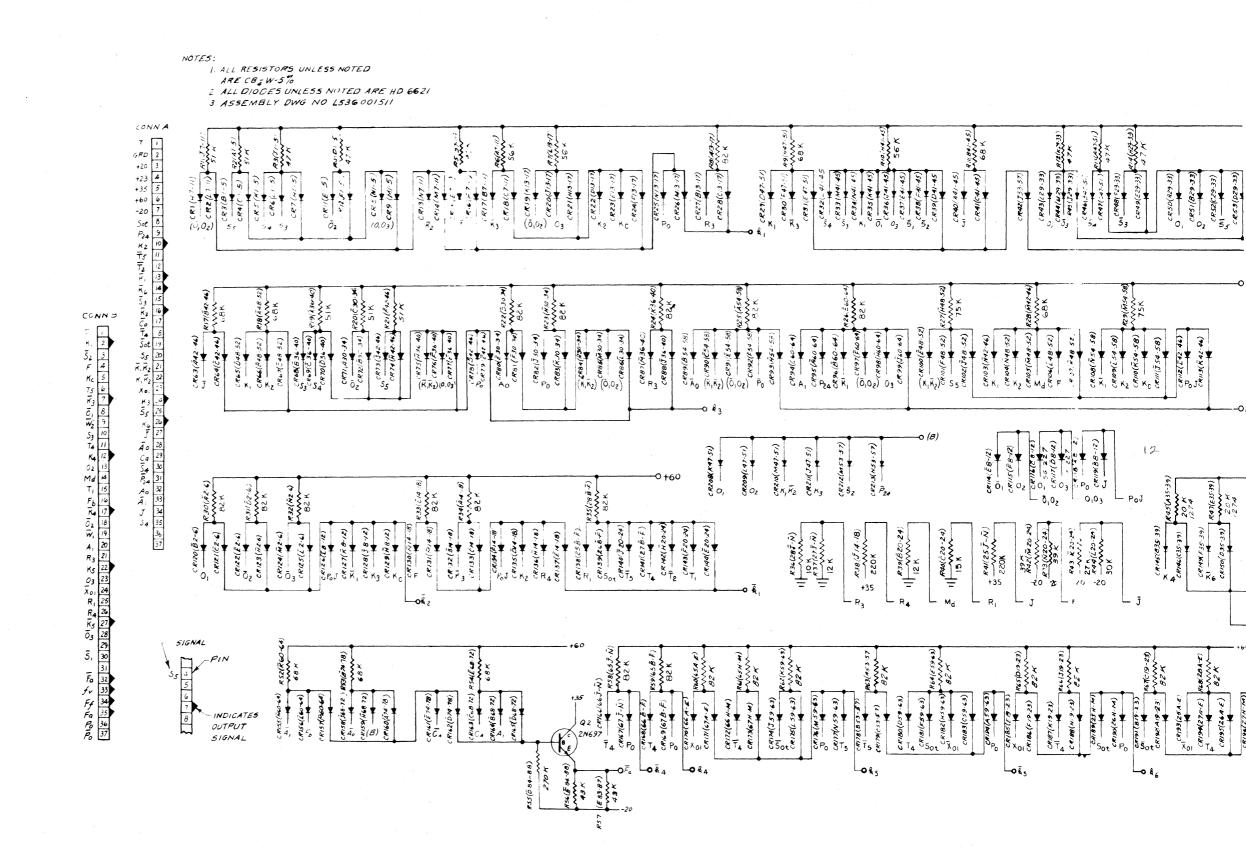

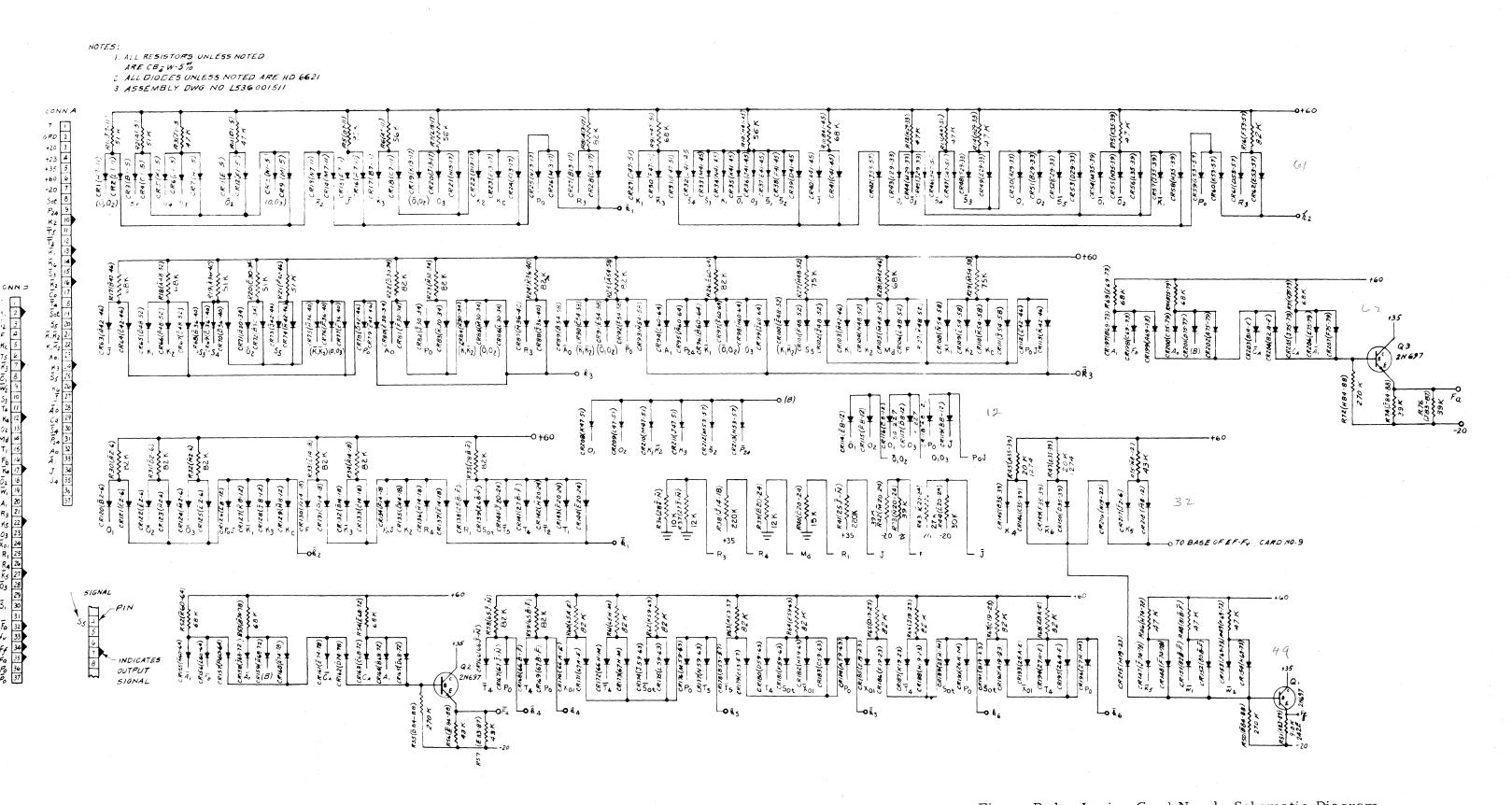

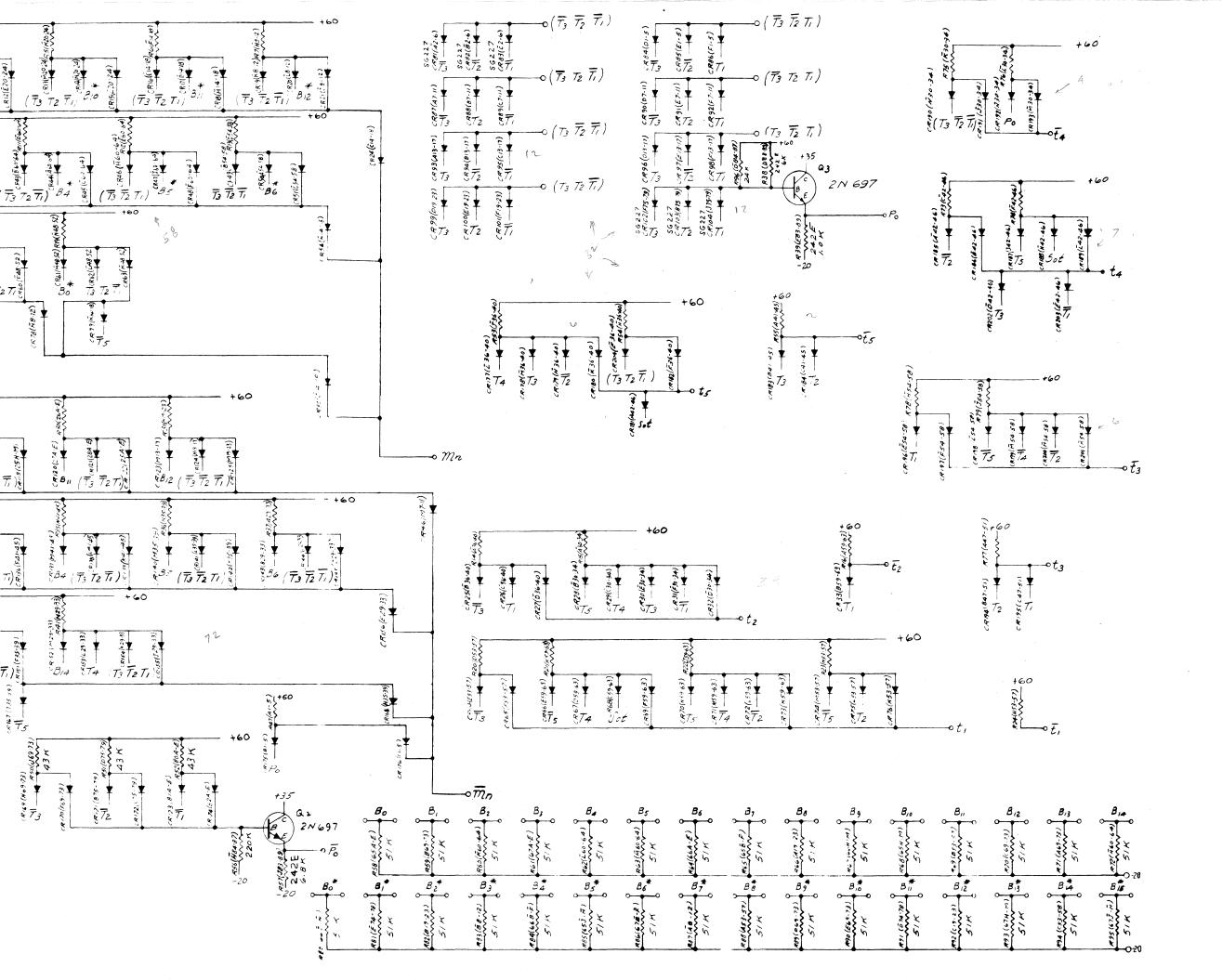

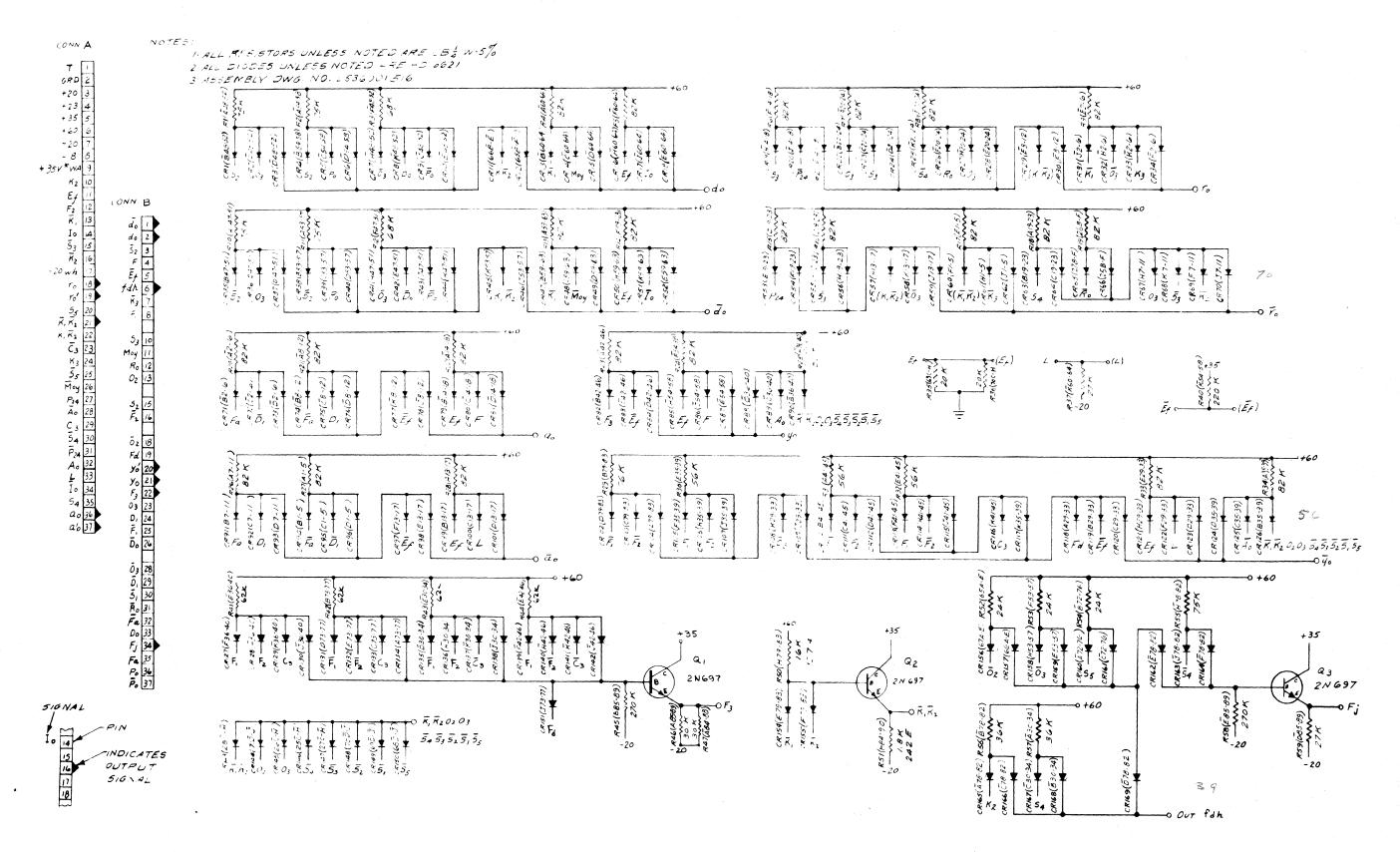

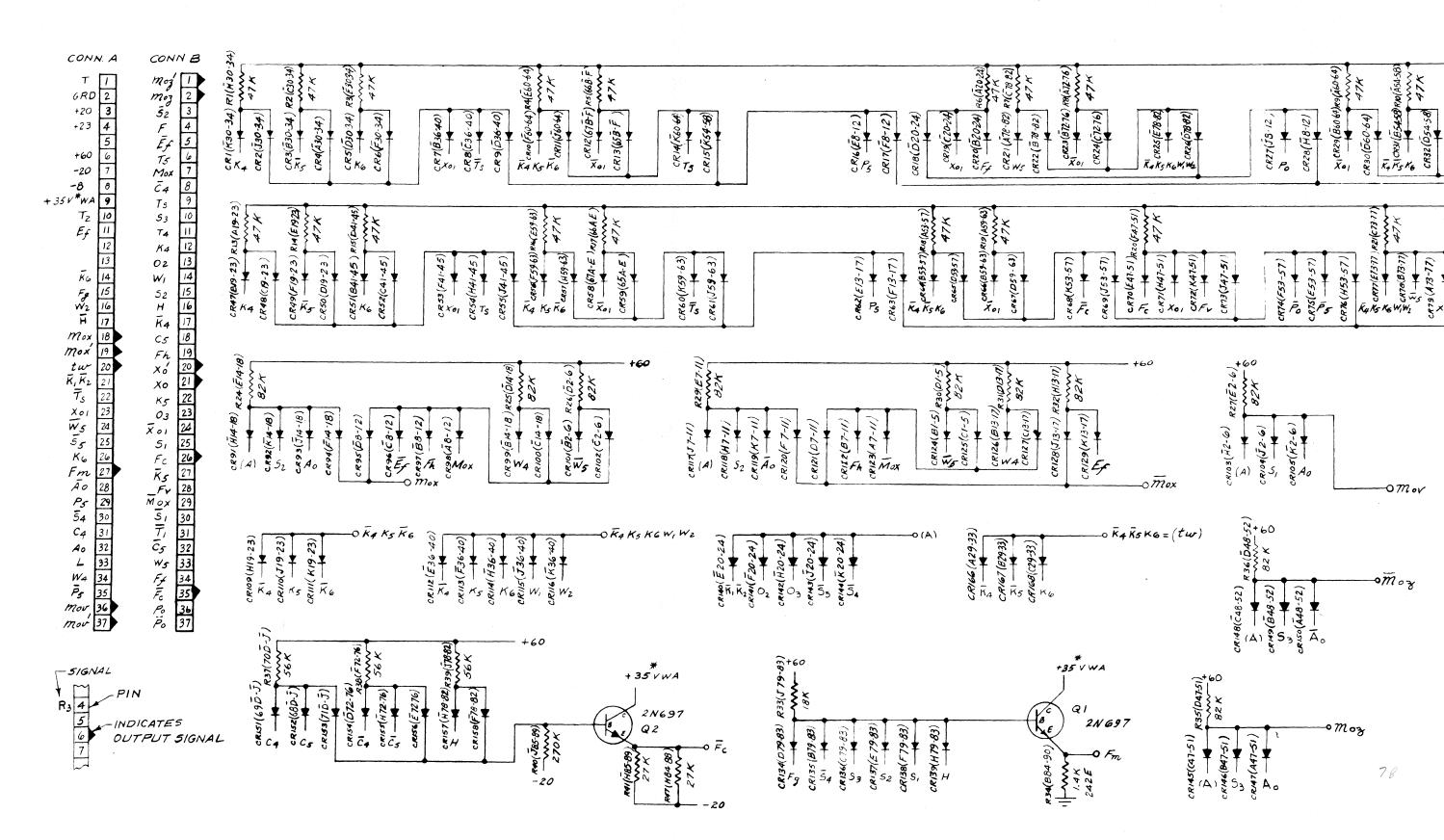

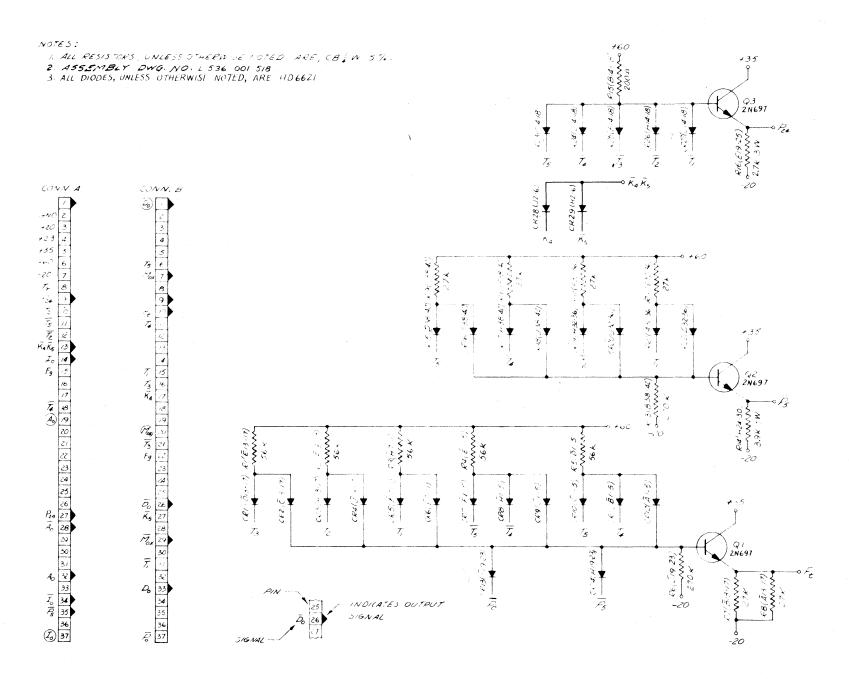

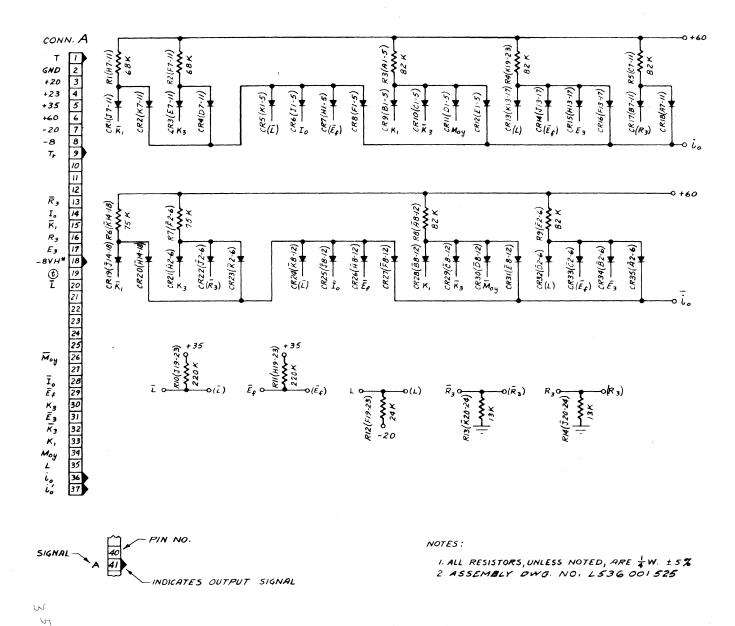

| B-1    | Logic, Card No. 1, Schematic Diagram                  |      |

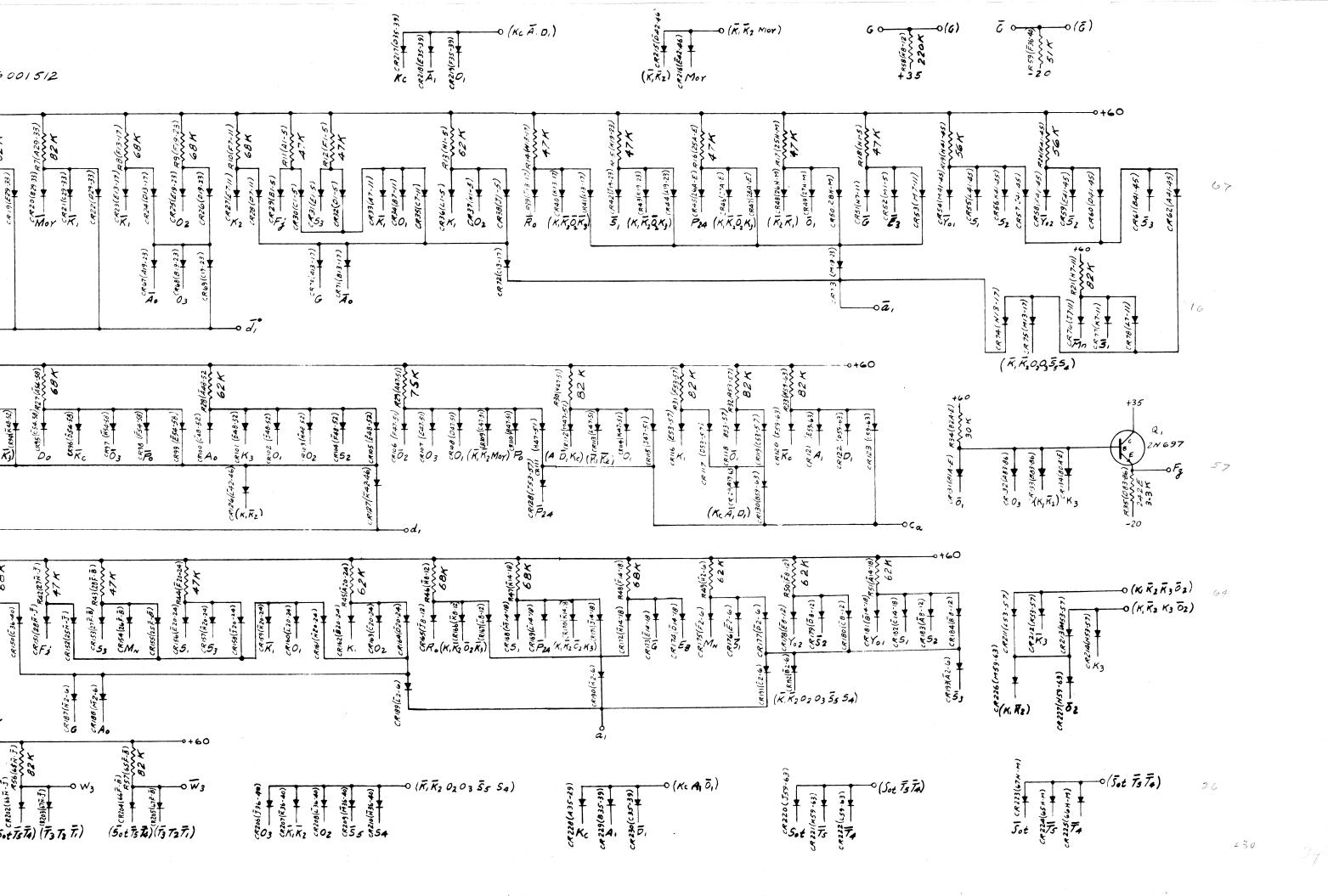

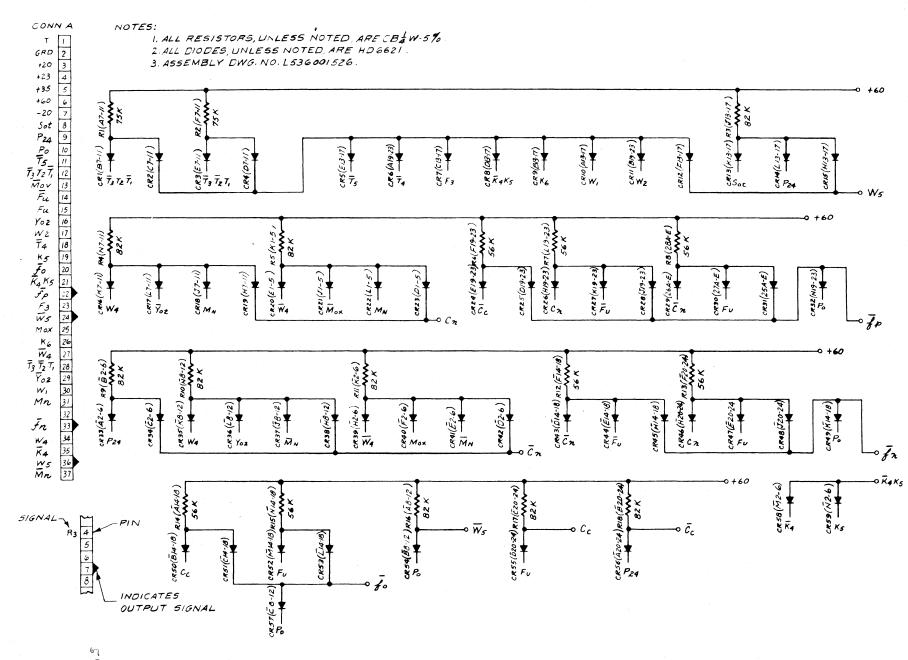

| B-2    | Logic, Card No. 2, Schematic Diagram                  |      |

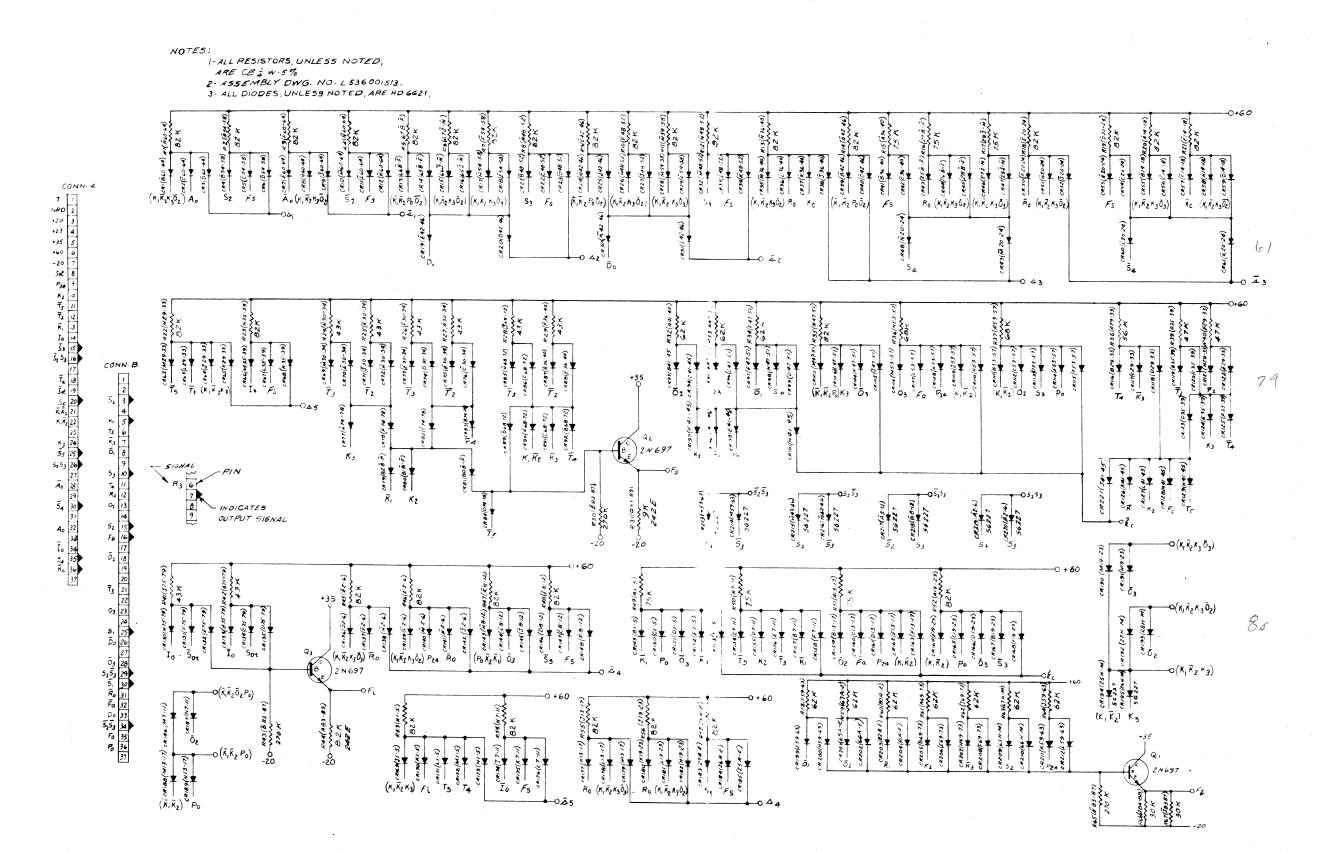

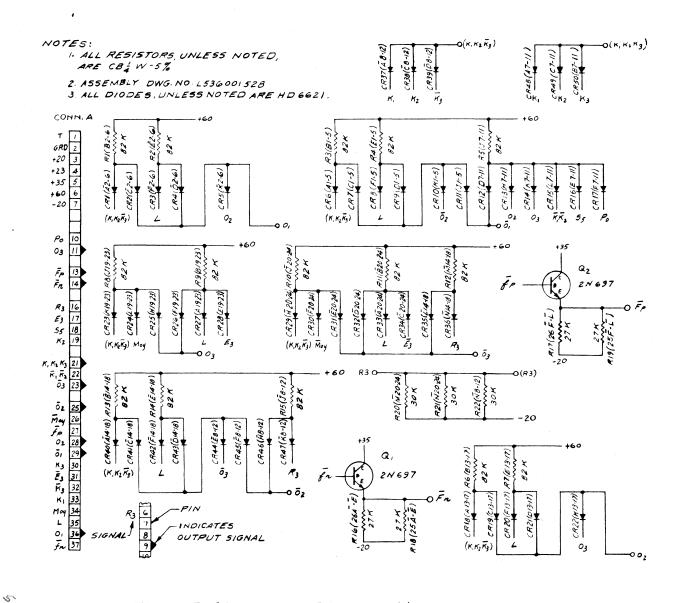

| B-3    | Logic, Card No. 3, Schematic Diagram                  |      |

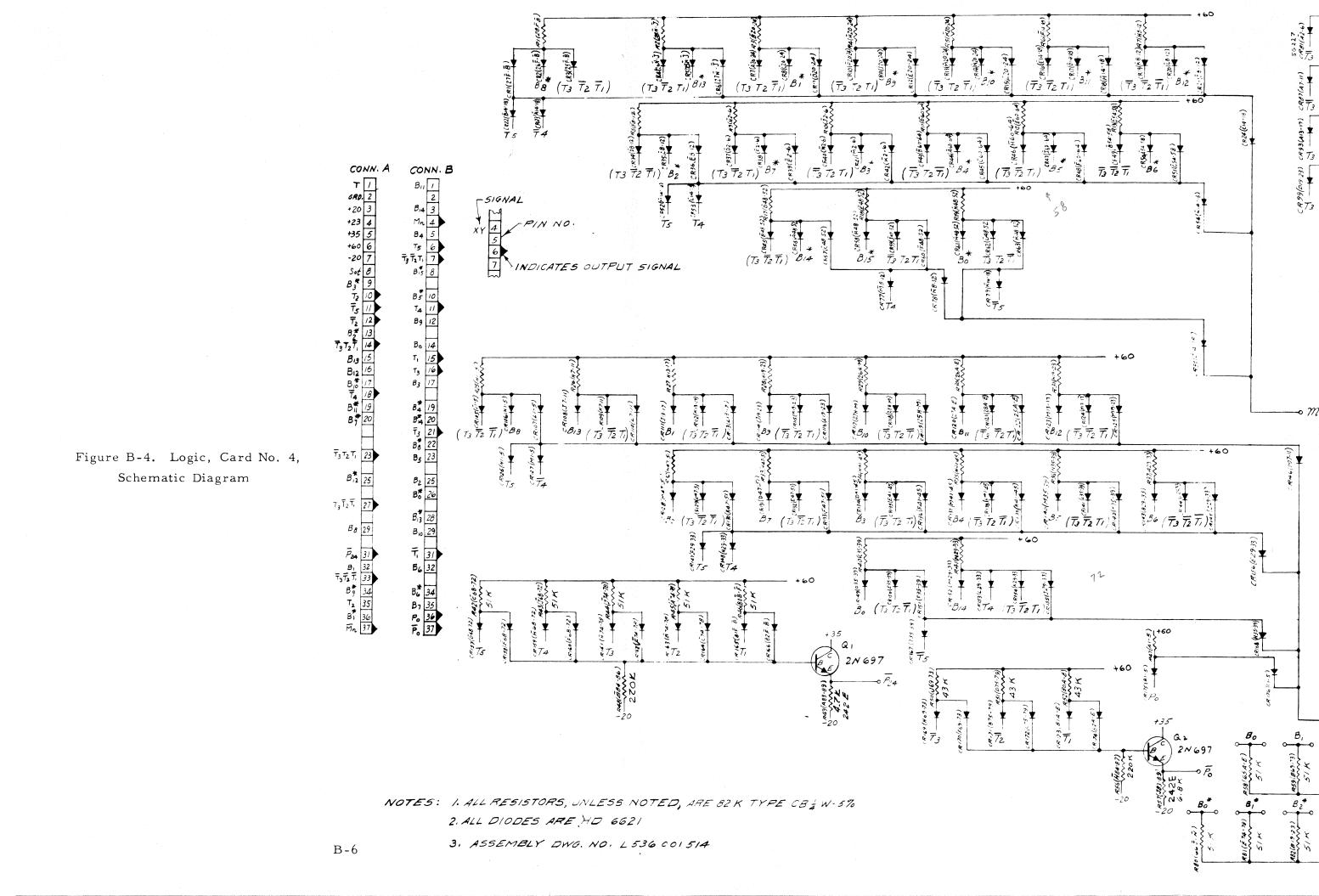

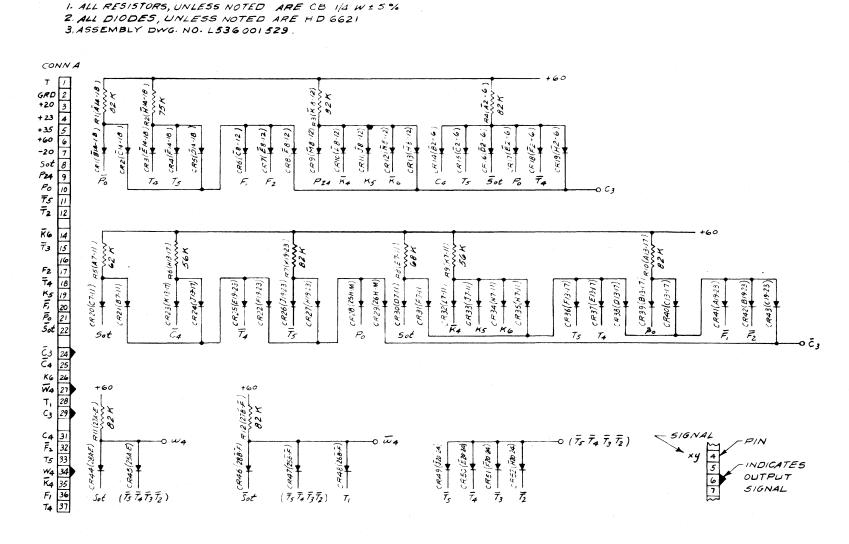

| B-4    | Logic, Card No. 4, Schematic Diagram                  | B-6  |

| B-5    | Logic, Card No. 5, Schematic Diagram                  | B-7  |

| B-6    | Logic, Card No. 6, Schematic Diagram                  |      |

| B-7    | Logic, Card No. 7, Schematic Diagram                  | B-9  |

| B-8    | Logic, Card No. 8, Schematic Diagram                  | B-10 |

| B-9    | Logic, Card No. 9, Schematic Diagram                  |      |

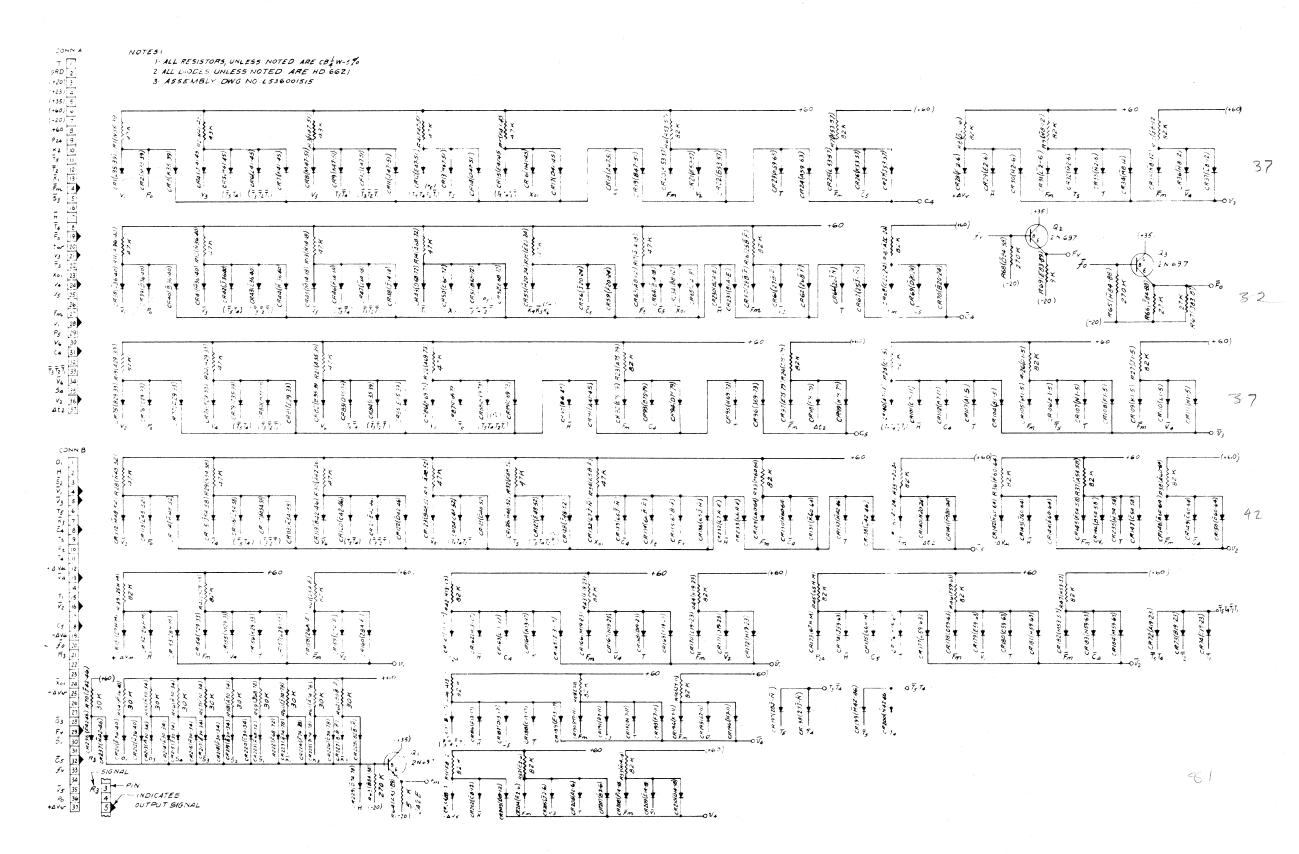

| B-10   | Logic, Card No. 13, Schematic Diagram                 | B-13 |

| B-11   | Logic, Card No. 14, Schematic Diagram                 | B-14 |

| B-12   | Logic, Card No. 15, Schematic Diagram                 | B-15 |

| B-13   | Logic, Card No. 16, Schematic Diagram                 | B-16 |

| B-14   | Logic, Card No. 17, Schematic Diagram                 | B-17 |

| B-15   | Logic, Card No. 19, Schematic Diagram                 | B-18 |

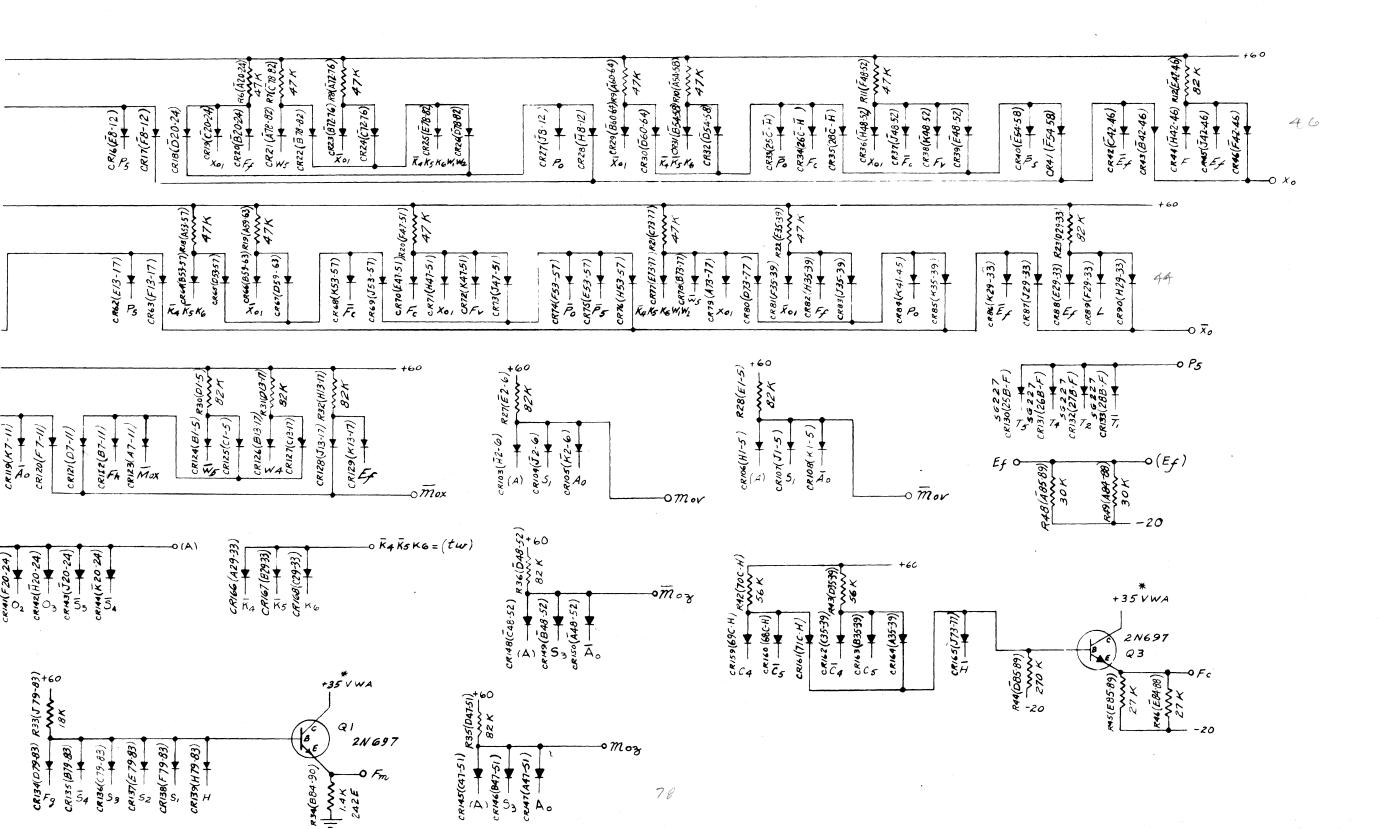

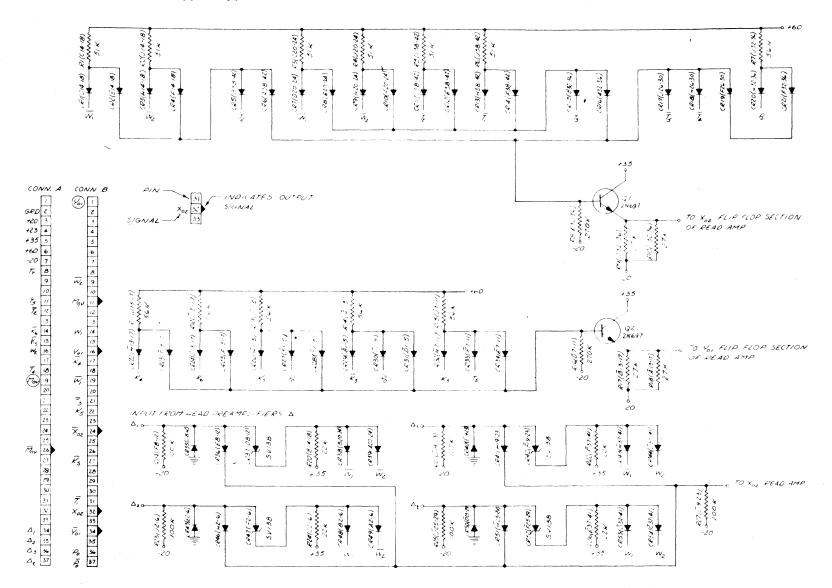

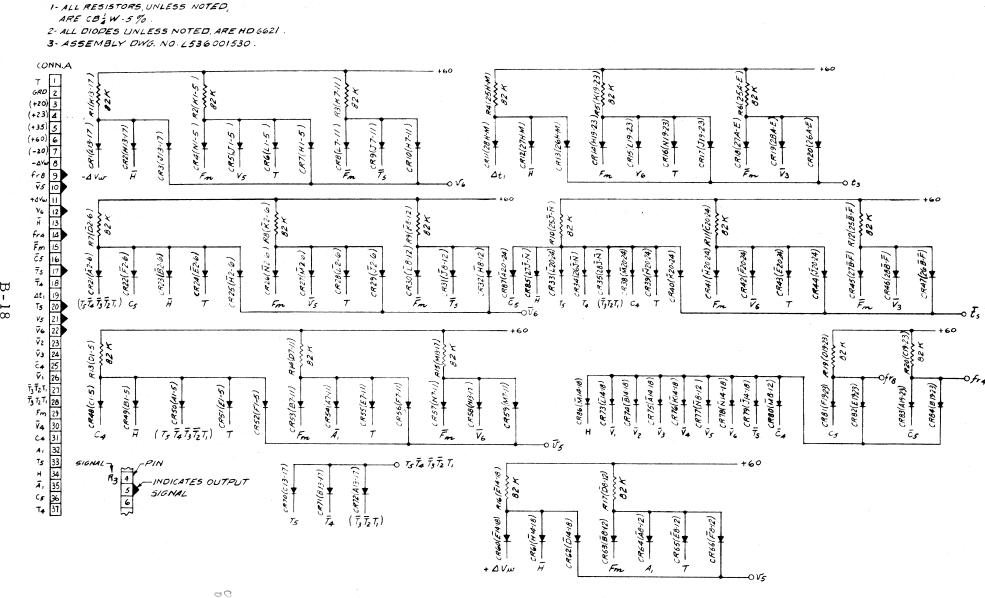

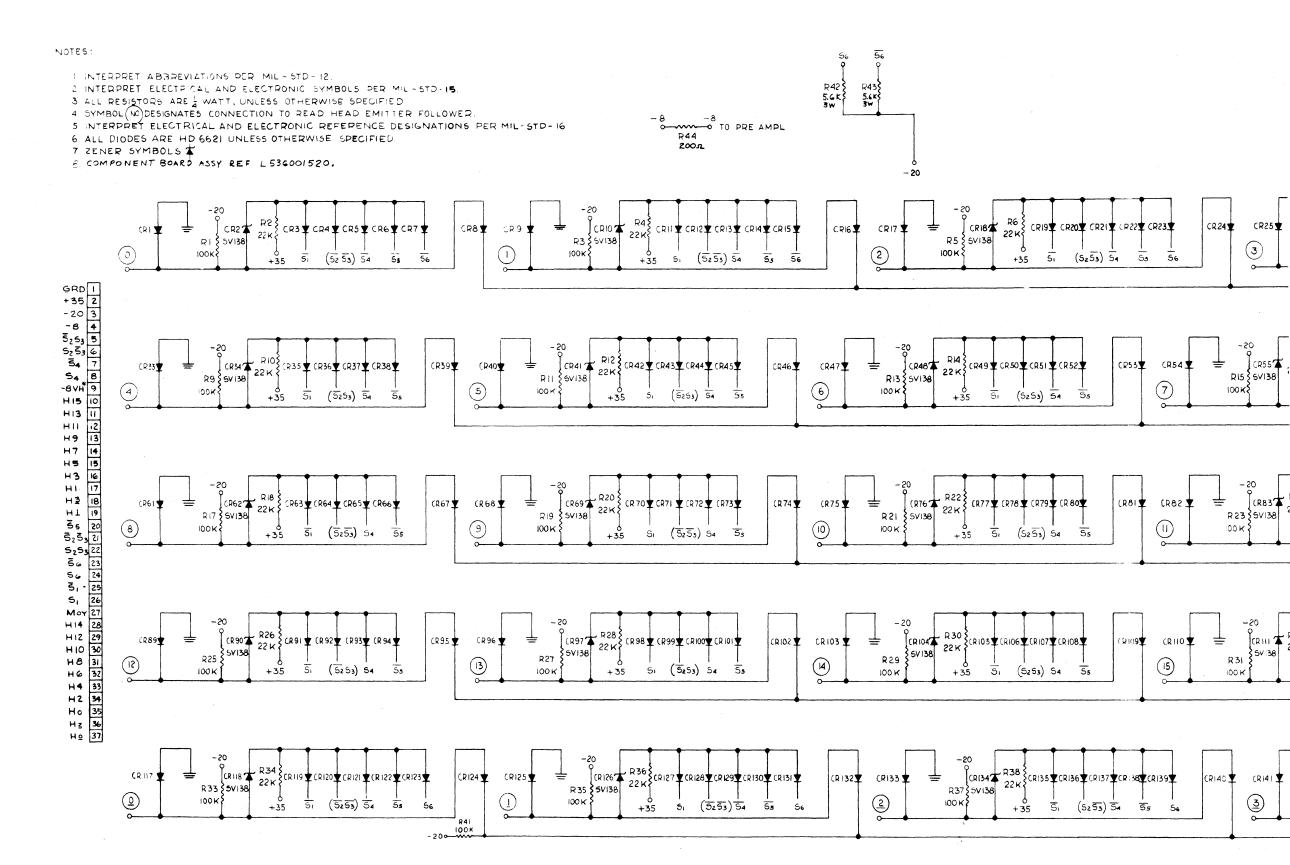

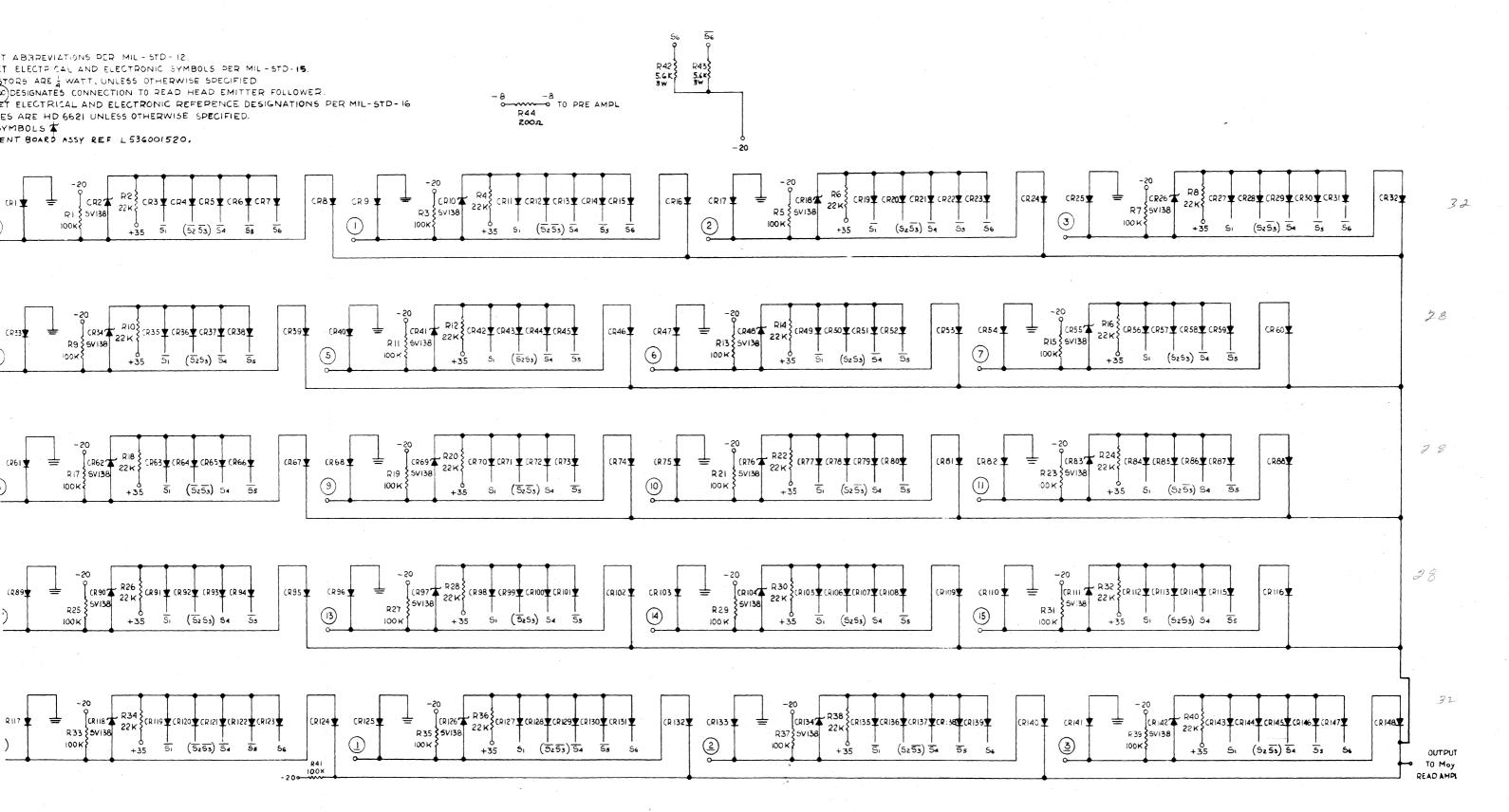

| B-16   | Head Selecting Matrix, Card No. 10, Schematic Diagram | B-19 |

| B-17   | Head Selecting Matrix, Card No. 18, Schematic Diagram | B-20 |

# Section I INTRODUCTION

#### 1-1. PURPOSE OF MANUAL

This manual contains operation and maintenance instructions for the ASN-24 Computer and associated test equipment, designed and manufactured by Librascope Division, General Precision, Inc., and is written to the level of field engineers and technicians who are skilled in the handling of digital computers.

# 1-2. PURPOSE OF EQUIPMENT

The ASN-24 Computer is a versatile, general-purpose, electronic digital computer which, by virtue of its non-fixed internally-stored program, is easily adaptable for many commercial, scientific, and military uses. In addition, the computer's small size and weight and its low power requirements make it well suited for application in compact systems.

#### 1-3. DESCRIPTION

The computer occupies 0.55 cubic feet of space, weighs 31 pounds including its magnetic memory drum, and has a memory capacity of 2560 words. An input-output unit, expressly designed for the specific computer application, is used with the ASN-24.

## 1-4. POWER REQUIREMENTS

The computer requires the following DC power:

| Voltages | Watts |

|----------|-------|

| +60      | 31.7  |

| +35      | 22.3  |

| +23      | 6.1   |

| +20      | . 7   |

| -8       | 2.0   |

| -20      | 17.4  |

The computer also requires 30 watts of 115V AC, 400 cycles, 3 phase, assuming a power factor of 50 percent. A total of 110 watts of AC and DC power are required.

# Section II PHYSICAL DESCRIPTION

#### 2-1. WEIGHT AND VOLUME

The computer weighs 31 pounds and is 0.55 cubic feet in volume.

#### 2-2. MAGNETIC MEMORY DRUM

The magnetic memory drum has a 4-1/2-inch diameter, is 3-1/2 inches long, and is driven by a 400-cycle, three-phase, hysteretic synchronous motor at 6000 rpm. The drum surface has 1600 equidistant grooves along its full length. The grooves are filled with magnetic material to a depth of 0.0015-inch. Sixty-three magnetic heads are mounted 0.001 inch from the surface of the drum. Each head can magnetize the material in the grooves to a 0.050-inch wide channel or track. The heads are spaced to provide for 47 separate channels (some have more than one monitoring head). Channels are subdivided into 25-bit words, 64 words per channel. Two of the main design features of the drum are:

- a. The bearings, housing, drum, and associated structure are designed to ensure a change in read-record head-to-drum spacing of less than 0.0001 inch in an airborne environment.

- b. The motor is designed as an integral part of the drum, producing a lighter and more compact assembly.

### 2-3. READ-RECORD HEADS

- a. Size: case, 0.4-in. diameter by 0.75-in. long; core, 0.3-in. long by 0.25-in. wide with 0.05-in. square cross-section.

- b. Material: case, aluminum; core, ferramic H.

- c. Core gap: 0.001 in. with silver shim filling gap.

- d. Turns: read, 600; write, 100 center tap.

- e. Shielding: 0.04-in. thick Mu metal.

- f. Inductance: read, 16 millihenries; write, 0.06 millihenries for half-head.

The core is secured to the case as close to the gap as possible so that temperature variations will result in small absolute variations in drum surface-to-head spacing. The cores are mechanically mounted in the case and are entirely enclosed (except for pole pieces), thereby preventing entrance of foreign particles.

#### 2-4. CIRCUIT CARDS

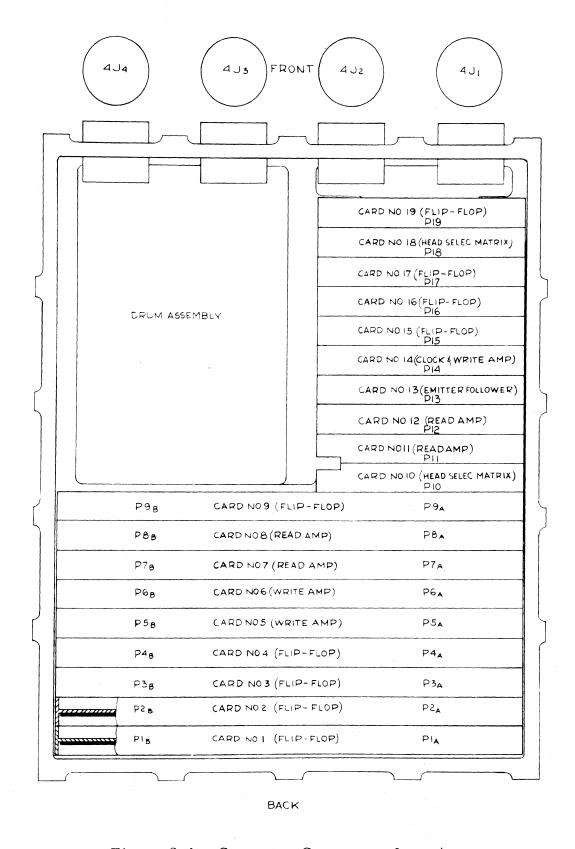

The computer has 19 circuit cards. Nine are large,  $9-1/2 \times 6$  in., and ten are small,  $4 \times 6$  in. (see figure 2-1). Each large one has two 37-pin connector sections; each small one has one 37-pin connector section. Listed below are each type of card and identification numbers.

- a. Five large flip-flop cards, numbers 1, 2, 3, 4, and 9.

- b. Two large write amplifier cards, numbers 5 and 6.

- c. Two large read amplifier cards, numbers 7 and 8.

- d. Four small flip-flop cards, numbers 15, 16, 17, and 19.

- e. Two small read amplifier cards, numbers 11 and 12.

- f. Two small head switching cards, numbers 10 and 18.

- g. One small emitter follower card, number 13.

- h. One small write amplifier and clock generator card, number 14.

Figure 2-1. Computer Component Location

# Section III ELECTRICAL DESCRIPTION

#### 3-1. GENERAL

All electronic circuits in the computer are designed to operate under severe environmental conditions and to tolerate large differences in individual component parameters and a wide variation in supply line voltage.

#### 3-2. COMPONENTS

#### 3-3. Resistors

The resistors are 1/4-watt, carbon composition-type, have low dielectric loss, high DC resistivity, and high thermal shock resistance.

#### 3-4. Semiconductors

The semiconductors in the ASN-24 Computer are silicon transistors and diodes with high back resistance and low leakage characteristics at high temperatures. The higher collector voltage ratings of silicon transistors permit larger logic swings. This reduces the susceptibility of the computer to noise disturbance.

## 3-5. Magnetics

The magnetic heads and flip-flop input transformers have ferrite cores. Although ferrites tend to change their magnetic characteristics over temperature extremes, the ferrites in the ASN-24 Computer have a comparatively flat permeability curve over the operating temperature

range and have a minimum decrease in saturation flux density with increasing temperature. Silicon steels and permalloy, which hold their magnetic characteristics over a large temperature range, are used in some transformers.

## 3-6. Capacitors

Most of the capacitors are a solid tantalum type, have high dielectric and insulation strength, and have no derating of voltage over a large temperature range. The very small capacitors are the subminiature ceramic type.

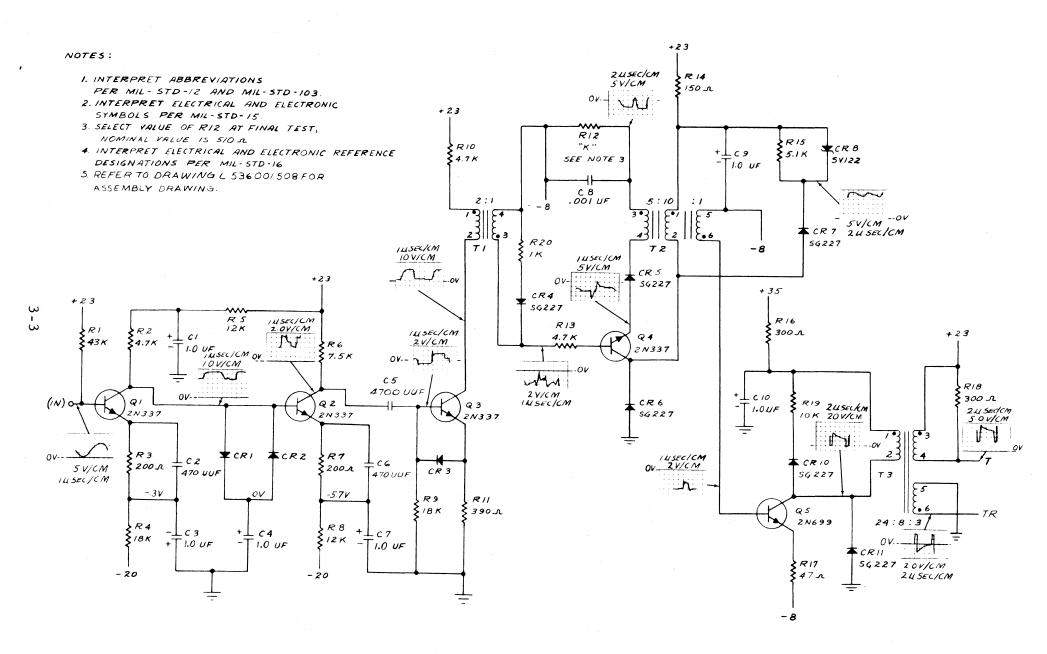

#### 3-7. CLOCK AMPLIFIER

- a. Type: DC preamplifier, trigger-shaping stage, blocking oscillator, power stage.

- b. Transistors: three 2N337, preamplifier; one 2N337, blocking oscillator; one 2N699, power stage.

- c. Input: 300 millivolts minimum into 5000 ohms.

- d. Output: 1.5 watts peak; 12-volt negative pulse and 5-volt positive pulse (read sync), each of 1  $\mu$ sec duration; rise time, 0.15  $\mu$ sec; and fall time, 0.4  $\mu$ sec (fully loaded).

- e. PRF: 100 to 200 kc.

- f. Total power dissipation: 900 milliwatts.

Because a pulse amplification-clipping technique is employed in the preamplifier section, there is no change in phase shift, output relative to input, as a function of input amplitude, frequency, or temperature. Stabilization in the regenerative feedback circuit of the blocking oscillator makes the pulse width independent of temperature and transistor parameters. A DC gain of less than one provides a high degree of stability in the DC preamplifier. See figure 3-1.

Figure 3-1. Clock Amplifier, Schematic Diagram

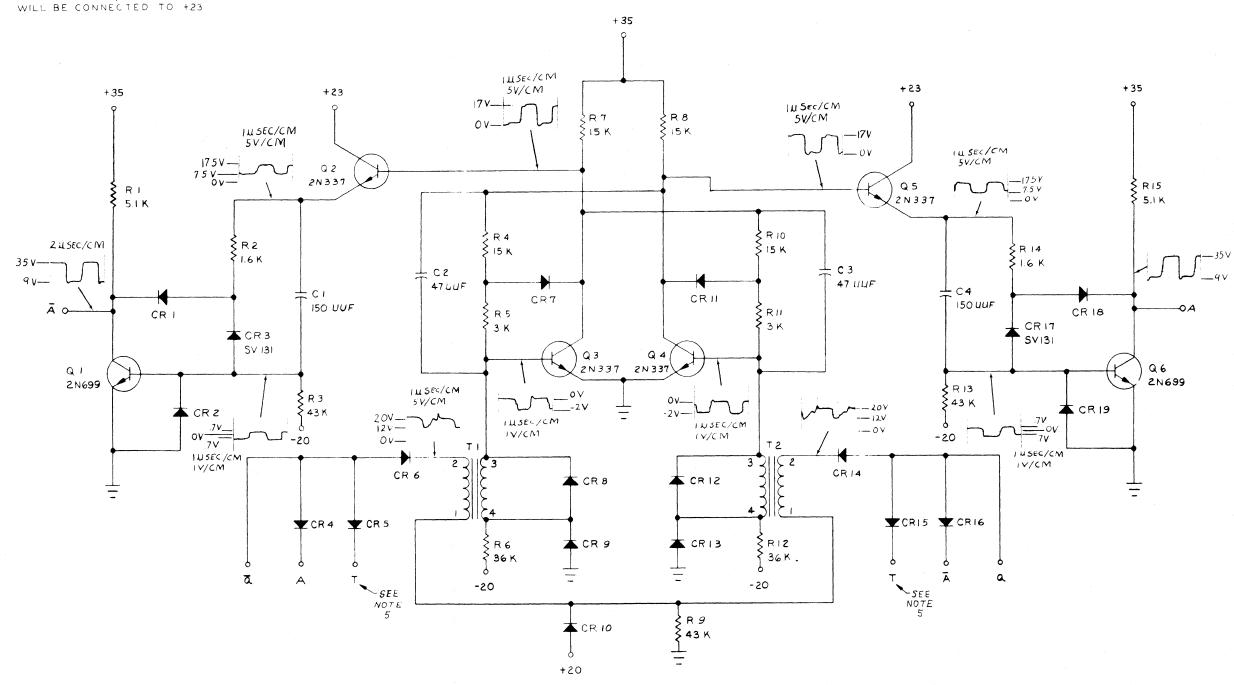

#### 3-8. FLIP-FLOPS

- a. Type: bi-stable Eccles-Jordan with output buffers and power gain stages. Logically a J-K type flip-flop (inherent cross-coupled feedback from the output of one side to the input of the other).

- b. Transistors: two 2N337, flip-flop; two 2N337, emitter follower buffers; and two 2N699, power gain stages.

- c. Input: clock pulse six volts minimum; l  $\mu$ sec duration and 5 milliwatts; transformer-coupled.

- d. Output: 26 volts (+9 to +35 volts); 1  $\mu$ sec rise time and 0.5  $\mu$ sec fall time; drive approximately 40 gates at 0.55 ma/gate.

- e. PRF: 0 to 200 kc.

- f. Total power dissipation: 300 milliwatts (fully loaded).

Collector saturation in all transistors is prevented by a technique which also compensates for transistors' gain variation. Compensation is provided for change in leakage currents. The lower level of output is regulated to ensure that an equal division of load current is supplied to a multiple input AND gate. See figure 3-2.

#### 3-9. DIODE GATES

- a. Type: AND-OR pyramid with a flip-flop input at apex.

- b. Diodes: HD6621.

- c. Input: +9 to +35 volts.

- d. Current transfer ratio: 0.8 maximum.

- e. PRF: 300 kc maximum.

- f. Power dissipation: 28 milliwatts per AND-OR gate.

The number of AND and OR inputs permitted in a single gate structure exceeds that required for instrumenting the logic.

#### NOTES :

- 1. INTERPRET ABBREVIATIONS PER MIL-STD-12

- 2. INTERPRET ELECTRICAL AND ELECTRONIC SYMBOLS PER MIL-STD-15.

- 3. INTERPRET ELECTRICAL AND ELECTRONIC REFERENCE DESIGNATIONS PER MIL-STD-16.

- 4. REFER TO DRAWINGS L536001504, L536001505 \$ L536001506 FOR ASSEMBLY DRAWINGS .

5. ON CARDS NO. 9 \$ NO. 19 (INCREMENTAL INPUT FLIP-FLOP) "T" DIODES CR5 \$ CR15

Figure 3-2. Flip-Flop, Schematic Diagram

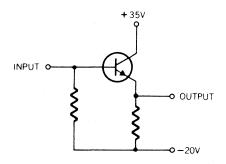

#### 3-10. EMITTER FOLLOWERS

- a. Type: standard.

- b. Transistors: one 2N697 per emitter follower.

- c. Input: direct drive from the logic (+9 to +35 volts).

- d. Output: direct drive from the emitter (+9 to +35 volts) with logic pull-down resistor.

- e. PRF: 0 to 500 kc.

Transistors are allowed to saturate as there is no minority carrier storage problem in this configuration. This permits minimum dissipation of power in transistors, maximum utilization of logic swing, and increased reliability due to reduction of components. See figure 3-3.

#### 3-11. WRITE AMPLIFIERS

- a. Type: push-pull pulse recording on milled tooth channels. For recording "one" or "zero" there is flip-flop type input, blocking oscillator, intermediate power stage, power output stage.

- b. Transistors: two 2N699, blocking oscillators; two 2N341, intermediate stages; two 2N389, output stages.

- c. Input: negative clock pulse, six volts minimum, 1  $\mbox{$\mu$sec}$  duration, transformer-coupled.

- d. Output: 300 ma current pulse of 2.5  $\mu$ sec duration into 50-turn magnetic record head represents 15 ampere turns of magnetic field strength required from write head for recording; 0.5  $\mu$ sec rise time and 0.7  $\mu$ sec fall time.

- e. PRF: 100 to 180 kc.

- f. Total power dissipation: 1 watt.

The input is logically a flip-flop input of set-reset type with additional capability of inhibiting recording of both "one" and "zero". By clamping collector and/or controlling emitter current, the transistors are not allowed to saturate. The pulse width, as determined by the blocking

Figure 3-3. Emitter Follower, Schematic Diagram

oscillator, is independent of transistor parameters. The stability factor for transistors ( $dI_{c}/dI_{co}$ ) is less than two in all stages. A current-limiting feature in the output power stage prevents power runaway. See figure 3-4.

#### 3-12. PREAMPLIFIERS

- a. Type: emitter follower.

- b. Transistors: one 2N495(PNP) each read head.

- c. Input: 0.5 volt peak-to-peak sinusoidal into 10K load.

- d. Output: 0.5 volt peak-to-peak.

- e. Amplifier response: 100 to 250 kc.

- f. Total power dissipation: 10 milliwatts.

The emitter follower preamplifiers are mounted close to each read head on the drum, permitting switching of heads and increased driving capabilities while reducing noise interference. See figure 3-5.

#### 3-13. HEAD-SWITCHING MATRIX

- a. Type: diode-gated.

- b. Transistors: included in preamplifiers.

- c. Input: Logic signals +9 to +35 volts.

- d. Output: head signal (0.5 volt peak-to-peak).

- e. Amplifier response: 100 to 250 kc.

- f. Total power dissipation: 850 milliwatts.

# 3-14. READ AMPLIFIERS (READ FLIP-FLOPS)

- a. Type: amplifier with modified flip-flop.

- b. Transistors: two 2N337 and to 2N697, amplifier; two 2N337, gating; four 2N337 and two 2N699, flip-flop.

Figure 3-4. Write Amplifier, Schematic Diagram

# NOTES:

- I. INTERPRET ABBREVIATIONS PER MIL-STD-12

- 2. INTERPRET ELECTRICAL É ELECTRONIC SYMBOLS PER MIL-STD-15. 3. INTERPRET ELECTRICAL É ELECTRONIC REFERENCE DESIGNATIONS PER MIL -STD-16.

- 4. REFERENCE DRAWINGS; L 520 002 005, \$ L200 003 049, PREAMPLIFIER ASSEMBLY. CONNECTOR ASSEMBLY PRE-AMP

Figure 3-5. Preamplifier, Schematic Diagram

Figure 3-6. Read Amplifier, Schematic Diagram

- c. Input: 300 millivolts minimum into 5000 ohms.

- d. Output: standard flip-flop.

- e. Amplifier response: 100 to 250 kc.

- f. Total power dissipation: 850 milliwatts.

A DC gain of less than one in the amplifier provides a high degree of stability. Collector saturation is prevented in all stages. The signal is symmetrically clipped and shaped independently of changes in the operating point and parameters of the transistors. To eliminate noise and feedback through the power supply, collectors of transistors in the amplifier stages are decoupled. See figure 3-6.

#### 3-15. DRUM

- a. Type: milled; hysteretic synchronous motor, 400 cycles, 3 phase.

- b. Tracks: 47.

- c. Bits per track: 1600.

- d. Bit rate: 160 kc at 6000 rpm.

- e. Input: magnetic field from write head.

- f. Output: read by read head (non-destructive read-out).

- g. Total power dissipation: 30 watts AC (steady state).

# Section IV THEORY OF OPERATION

#### 4-1. GENERAL

The ASN-24 Computer performs arithmetic and logical operations called orders. These orders include such operations as add, subtract, multiply, divide, extract, and conditional transfer. An order is a part of an instruction; other parts of an instruction define the address of the operand on which the order is to be performed and the address of the next instruction to be performed. Instructions are sequentially arranged to form a program which enables the computer to solve mathematical operations of various complexities. A program, when internally stored on the computer's memory drum, governs over-all computer operation, whereas a system of internally-fixed logic and control patterns governs the method by which the computer performs each type of instruction. It is essentially the built-in logic and control system, and not a specific program, that is the concern of this section on theory of operation.

Information stored in the computer is of two general types: control data and numerical data. Control data governs machine operation; numerical data is processed under specific control conditions. All information in the computer is represented by electrical pulses within the circuitry and by magnetic polarities on the memory drum. Two voltage levels, or magnetic polarities, are significant: a high voltage level (+35 volts) or magnetic polarization in the north direction represents the presence of a condition, or "1" state; a low voltage level (+9 volts) or magnetic polarization in the south direction represents the absence of a condition, or "0" state. Slight amplitude variations are meaningless. The significance of the conditions thus represented is dependent on the point and time at which they occur. Thus, a high and low voltage, respectively, may signify at various points and times any of the following: the binary

digits 1 and 0 to some power of the base 2, the arithmetic signs - and +, or simply the presence or absence of some specific control condition. Information is stored magnetically over extended periods of time on an oxide-coated, rotating drum. During brief intervals, when information is being processed, it is stored in flip-flop circuits.

## 4-2. BASIC LOGICAL ELEMENTS

Any presentation of the theory of operation of the ASN-24 computer must employ logical equations and equivalent pictorial symbols to represent the electronic circuitry. Through use of these symbols, all unnecessary repetition of standard electronic details can be avoided. At the same time, all pertinent information can be presented concisely. The basic electronic elements are described in section III.

Although the basic electronic circuits used in the computer are relatively simple, the computer as a whole is a complex machine. This complexity arises from the fact that the computer is essentially an elaborate switching network with many switching configurations. A knowledge of configurations which define the theory of operation is necessary for successful diagnosis of machine malfunctions.

The symbology used to represent the basic elements is shown in figure 4-1 and the logical functions of these elements are described in the following paragraphs.

#### 4-3. AND Gate

An AND gate is a logical device whose output follows its lowest input level. When all inputs are high, the output is high. When any or all inputs are low, the output is low. An AND gate is represented in row a of figure 4-1.

#### 4-4. OR Gate

An OR gate is a logical device whose output follows its highest input level. When any or all inputs are high, the output is high. When all inputs are low, the output is low. An OR gate is represented in row b of figure 4-1.

NOTE:

DESIGNATIONS AND WAVEFORMS

ARE ARBITRARY AND DO NOT

DEFINE ANY ACTUAL CIRCUITS

Figure 4-1. Circuit Symbology

#### 4-5. Flip-Flop

A flip-flop is a bi-stable device having complementary outputs. It is used as a temporary storage medium. The two states which a flip-flop may assume are referred to as its set and reset states. A flip-flop is in the set state (also called true or 1 state) when its non-barred output is high and its barred output is low; it is in the reset state (also called false or 0 state) when its non-barred output is low and its barred output is high. A flip-flop sets, as shown in row c of figure 4-1, when its set input (designated by a non-barred lower case letter) is high, its barred output is high, and a clock pulse T occurs. Conversely, a flip-flop resets when its reset input (designated by a barred lower case letter) is high, its non-barred output is high, and a clock pulse T occurs. A flip-flop's cross-coupling and clock triggering logic terms are not represented symbolically in either the pictorials or the logic equations because this logic is internal to a flip-flop. Because of clock pulse triggering of flip-flops, a one-bit delay is created between the time a flip-flop changes state and the time its outputs have effect upon other flip-flops.

#### 4-6. Emitter Follower

An emitter follower is a device whose output follows its input. There is no significant time delay between input and output signal levels. Emitter followers have no inherent logical function; they are used to provide power gain for heavily loaded signals. An emitter follower is shown in row d of figure 4-1.

### 4-7. Read Flip-Flop

A read flip-flop (also called read amplifier) is a device which receives its input from an associated read head and generates two complementary outputs. When an associated read head senses a "1" on the drum, the read flip-flop produces a high A output and a low  $\overline{A}$  output; when the read head senses a "0" on the drum, the read flip-flop produces a low A output and a high  $\overline{A}$  output. A read flip-flop is shown in row e of figure 4-1.

## 4-8. Write Amplifier

A write amplifier is a device which receives complementary inputs from a flip-flop and generates high current pulses to an associated write head. When the write amplifier receives a high "a" input, a "l" is written on the drum; when it receives a high "a" input, a "0" is written on the drum. A write amplifier is shown in row f of figure 4-1.

#### 4-9. MEMORY SECTION

The memory section is the major information storage medium in the computer. It comprises the memory drum, its associated read/record heads and their respective read flip-flops or write amplifiers, preamplifiers, and the head selecting matrix.

## 4-10. Memory Drum

The memory drum is a cylindrical, motor-driven unit which is rotated at a nominal speed of 100 revolutions per second. On the periphery of the drum and running parallel to its rotational axis are 1600 magnetic oxide-filled grooves. These grooves are evenly spaced around the drum. Encasing the drum is an aluminum shroud on which read/record heads are installed. A read/record head thus defines a particular line around the drum which intersects each of the 1600 grooves during one drum revolution. These 1600 bit paths are called tracks. A track may have one or more read/record heads, depending on its function.

#### 4-11. Read/Record Heads

The read/record heads are similar; however, the function of each head is determined by its wiring to either a read flip-flop or to a write amplifier. Each read/record head is wired either to one or the other of these circuits, never to both. A read/record head wired to a write amplifier continuously records information onto its associated track; a read/record head wired to a read flip-flop continuously reads information from its

associated track. A read/record head wired to a read flip-flop will subsequently be referred to as a read head; a read/record head wired to a write amplifier will be referred to as a write head. The process of writing information erases automatically any previously recorded information. No special erase process is necessary.

#### 4-12. Tracks

The drum shroud contains 63 read/record heads which define 47 tracks on the memory drum. These tracks and their associated heads and read flip-flops or write amplifiers are shown in figure 4-2 and are defined in the following paragraphs.

#### 4-13. Clock Track

The clock track is prerecorded with each of its 1600 grooves polarized in the same direction. The clock track has one associated read head which feeds amplification and wave-shaping circuits located in the clock amplifier (see figure 4-2). The clock amplifier generates spiked pulses at a frequency of approximately 160 kilocycles (1600 pulses per drum revolution at 100 revolutions per second). These spiked pulses, called clock pulses, provide a 12-volt negative-going pulse, T, which is used to trigger all flip-flops in the computer with the exception of the read flip-flops which are triggered by a 5-volt positive-going pulse, T. The clock pulses are used to synchronize the computer circuitry with the memory drum. This synchronization is accomplished by triggering all flip-flops with clock pulses, thereby preventing change of state of flipflops during the intervals between clock pulses. Since the computer circuitry is synchronized from the memory drum, slight variations in the rotational speed of the drum cannot adversely affect computer operation. Setting and resetting of flip-flops is accomplished only at clock pulse time, as shown in row c of figure 4-1.

Figure 4-2. Memory Section

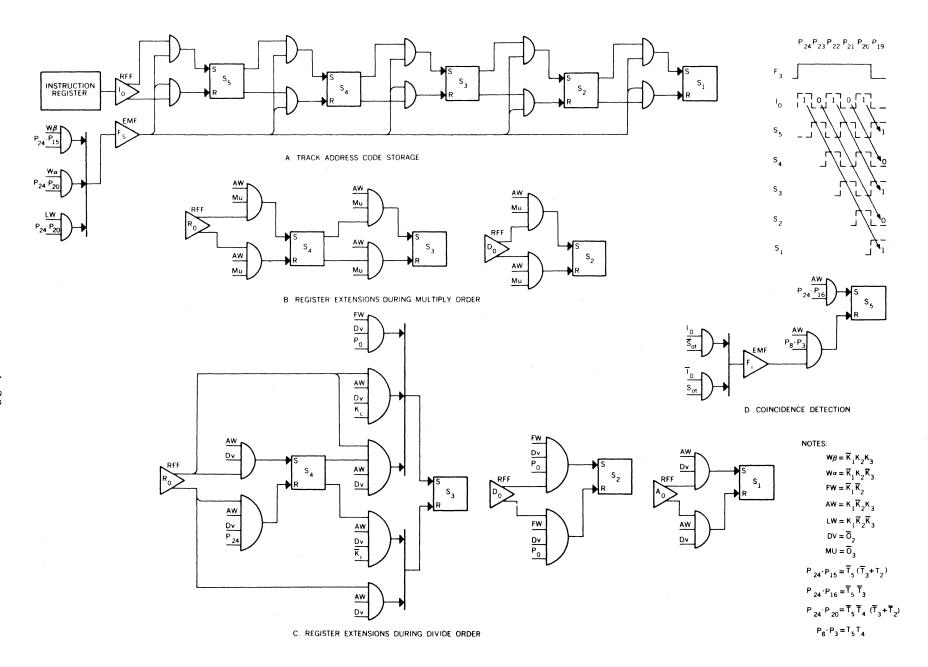

#### 4-14. Sector Address Track

The sector address track contains permanently-recorded control information which is continuously read by the S<sub>ot</sub> read flip-flop via its associated read head (see figure 4-2). The primary function of the sector address track is to define each of the 64 sectors of the main memory tracks to enable location of particular words for computing purposes. A sector is a 25-bit, one-word, storage segment. The sector address track also provides synchronization pulses which are used to initially enter, and then maintain, the pulse time indicator in synchronism with the drum. In addition, the sector address track furnishes control codes used for setting the input-output selection register and the sigmator program.

The  $S_{\rm ot}$  signals occur at the following pulse times of each word: sector address codes occur at  $P_{14}$  through  $P_9$  time (s $\beta$ ) and are repeated at  $P_8$  through  $P_3$  time (s $\alpha$ ); a "1" occurs at every  $P_{15}$  time for synchronization of the pulse time indicator; the input-output selection register control codes occur at  $P_{24}$  through  $P_{20}$  time; and sigmator program information occurs at  $P_2$  and  $P_1$  time. For detailed explanation on locating the sector address of a word, refer to paragraphs 4-30 and 4-33; for pulse time indicator synchronization, refer to paragraph 4-27; for input-output selection register control, refer to paragraph 4-31; and for sigmator program control, refer to paragraph 4-69.

## 4-15. Main Memory

Main memory comprises 40 tracks on the memory drum — 37 permanent storage tracks and 3 temporary storage tracks. Associated with main memory is the track selecting matrix and the time-shared, main memory read flip-flop, M<sub>oy</sub>. The permanent storage tracks are described in paragraph 4-16, the temporary storage tracks are described in paragraph 4-17, and the head selecting matrix is described in paragraph 4-18.

4-16. Permanent Storage Tracks. The permanent storage tracks comprise 37 of the 40 main memory tracks (see figure 4-2). These 37 tracks store the program which consists of both instruction and operand words.

Each track has one associated read head numbered 0 through 27, 31,  $\underline{0}$ ,  $\underline{1}$ ,  $\underline{2}$ ,  $\underline{3}$ ,  $\underline{16}$ ,  $\underline{17}$ ,  $\underline{18}$ , and  $\underline{19}$ . The outputs of all 37 read heads are routed to the head switching matrix which, under control signals from the track selection register, selects the track of a desired word, then passes the word to the commonly shared main memory read flip-flop,  $M_{oy}$ . The output of  $M_{oy}$  may be routed to the instruction register, the order register, the multiplicand-divisor register, and to the serial adder via flip-flop  $D_1$ . These registers accept the  $M_{oy}$  information under specified control conditions. Normally, instruction words are routed to the instruction register. Operand words are routed to the multiplicand-divisor register and the serial adder.

4-17. Temporary Storage Tracks. The temporary storage tracks comprise 3 of the 40 main memory tracks (see figure 4-2). These three tracks store data temporarily while it is still required in the computation. Normally, the data consists of intermediate solutions such as a sum or a product which is needed for larger scale problem solutions defined by the program, or to temporarily store input-output data. The three tracks have one read head each, numbered 28, 29, and 30 which are wired to the head switching matrix. Upon selection of a read head the respective signal passes to the M<sub>OY</sub> read flip-flop. Each track also has a write head and associated write amplifier. The write amplifiers, m<sub>OY</sub>, m<sub>OX</sub>, and m<sub>OZ</sub>, receive information from the accumulator register under specified control conditions. The spacing of the write heads with relation to the read heads is such that a word written on m<sub>OZ</sub> is available at M<sub>OY</sub> four word-times later, a word written on m<sub>OZ</sub> is available at M<sub>OY</sub> 60 word times later.

Track  $M_{\rm ox}$  contains a second read head and associated read flip-flop. The output of the read flip-flop may be routed to the  $m_{\rm ox}$  write amplifier to permit recirculation of the information, if required. The output of the  $M_{\rm ox}$  read flip-flop is also routed to the error determining circuits where it is used for output operations, refer to paragraph 4-43. Separation between the read and write heads is equivalent to eight word times. This recirculation line, or loop, permits more rapid access to desired words contained on the  $M_{\rm ox}$  track.

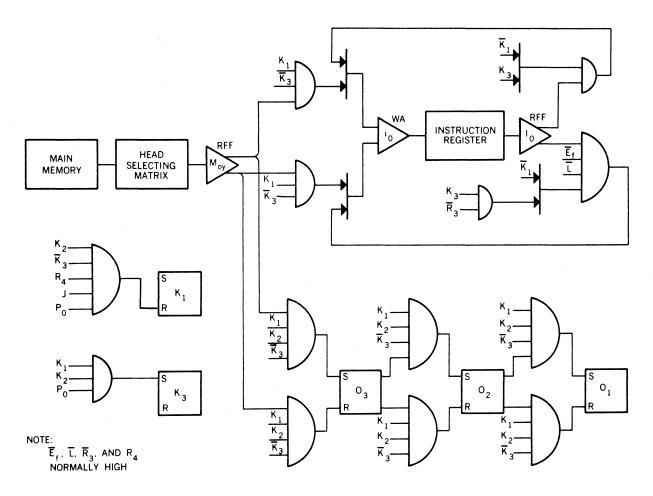

4-18. Head Selecting Matrix. The head selecting matrix is used to select any one of the 40 main memory tracks for read-out via read flip-flop  $M_{oy}$ . The head selecting matrix comprises 40 gating circuits, one for each main memory track. See figures B-16 and B-17. Each AND gate of the matrix has a unique gating code derived from various configurations of the track selection register flip-flops  $(S_1, S_2, S_3, S_4, S_5)$  and the externally located relay  $S_6$ . Refer to paragraph 4-30 for particulars on the track selection register.

When a specific code is generated by the track selection register and the  $S_6$  relay, it is decoded by its associated gate in the matrix to electrically connect the desired main memory read head via a preamplification stage to read flip-flop  $M_{oy}$ . It may be noted that there is always an  $M_{oy}$  output i.e.,  $M_{oy}$  is always copying the contents of some main memory track. However, the computer circuits only accept  $M_{oy}$  information at specific control times.

# 4.19 Instruction Register

The instruction register is a 25-bit recirculating register on the drum used for storing instruction words, see figure 4-2. The instruction register contains one write head and associated write amplifier  $i_0$ , and one read head and associated read flip-flop  $I_0$ . The write and read heads are spaced to provide a 25 bit delay to make the instruction word in the register available every word time.

An instruction word is routed into the instruction register from main memory via the M<sub>oy</sub> read flip-flop during the instruction read-in phase. At this time recirculation of the register is blocked. During all other phases, except last word phase, the instruction recirculates.

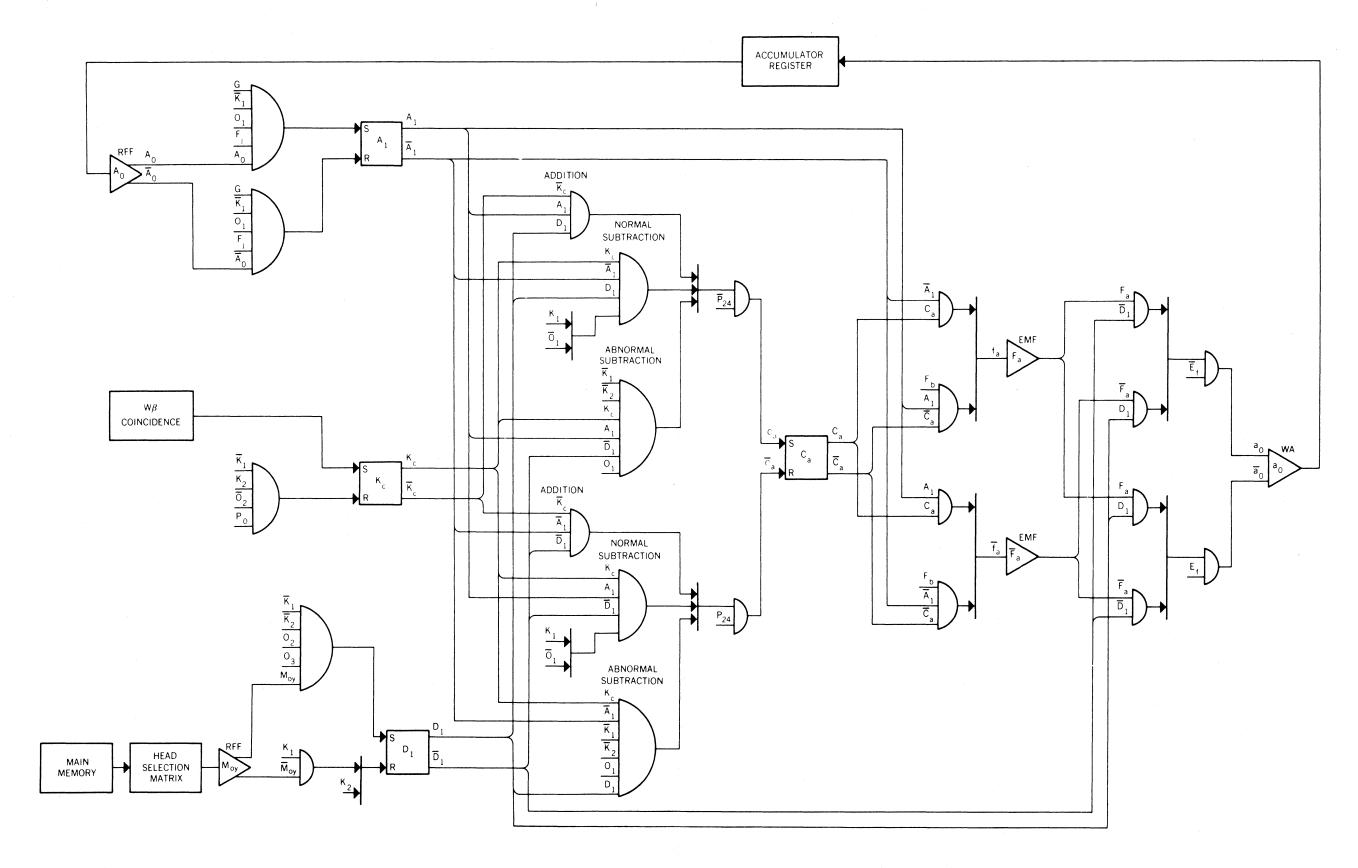

## 4.20 Accumulator Register

The accumulator register is a 24-bit recirculating register used for storing operand words during computation, see figure 4-2. The accumulator

register contains one write head and one read head and their respective write amplifier  $a_0$  and read flip-flop  $A_0$ . Between the read flip-flop  $A_0$  and write amplifier  $a_0$  is a serial adder which, in addition to other control logic, controls information flow into the accumulator register. The serial adder is discussed in paragraph 4-40.

The accumulator register normally receives operand words from main memory read flip-flop  $M_{oy}$  via the serial adder. While the  $M_{oy}$  operand is passing through the adder to the register, the operand stored in the register may be added or subtracted from it thus entering the sum or difference into the accumulator register. Other types of arithmetic operation may also be performed. At the time that the  $M_{oy}$  operand is passing through the adder, recirculation of the accumulator may also be blocked to permit the accumulator register to simply copy  $M_{oy}$ . The contents of the accumulator may only be altered during first word phase FW, additional words phase AW, or last word phase LW phase; during all other phases the contents of the accumulator is permitted to recirculate.

The operand word in the accumulator register may be routed to any of the three working storage registers  $M_{ox}$ ,  $M_{oy}$ , or  $M_{oz}$ , or to  $\Sigma$  long line  $Y_{o}$ , in addition to being recirculated in the accumulator.

# 4-21. Multiplicand-Divisor Register

The multiplicand-divisor register is a 24-bit recirculating register used for storing the multiplicand during a multiplication order or the divisor during a divide order, see figure 4-2. The multiplicand-divisor register contains one write and one read head and their resepctive write amplifier do and read flip-flop Do.

For detailed descriptions of how the multiplicand-divisor register is used refer to multiplication order, paragraph 4-67; divide order, paragraph 4-68; and extract order, paragraph 4-63.

### 4-22. Multiplier-Quotient Register

The multiplier-quotient register is a 24-bit recirculating register used for storing the multiplier during a multiplication order or the quotient during a division order, see figure 4-2. The multiplier-quotient register contains one write and one read head and their respective write amplifier  $r_0$  and read flip-flop  $R_0$ .

For detailed descriptions of how the multiplier-quotient register is used refer to multiply order, paragraph 4-67; and divide order, paragraph 4-68.

# 4-23. Sigmator Long Line

The sigmator long line is used as an integrand register in the sigmator section of the computer. The sigmator long line contains one write head and associated write amplifier  $y_0$ , and two read heads and their associated read flip-flops  $Y_{o1}$  and  $Y_{o2}$ . Head spacing provides an 8-word delay between input  $y_0$  and output  $Y_{o1}$ , and a 32-word delay between input  $y_0$  and output  $Y_{o2}$ .

Information may be received by input  $y_0$  from the accumulator register  $A_0$  during FW of a normal store order  $(0_3\ 0_2\ 0_1\ \overline{S}_5\ \overline{S}_4\ \overline{S}_3\ \overline{S}_2\ \overline{S}_1)$  or from the output of the sigmator two-input adder. Outputs  $Y_{o1}$  or  $Y_{o2}$  may be transferred to the accumulator register during modified store orders  $0_3\ 0_2\ 0_1$   $\overline{S}_5\ S_4\ \overline{S}_3\ S_2\ S_1$  and  $0_3\ 0_2\ 0_1\ \overline{S}_5\ S_4\ \overline{S}_3\ \overline{S}_2\ S_1$ , respectively. Output  $Y_{o2}$  is also sent to the error determining circuits during output operations, refer to paragraph 4-43.

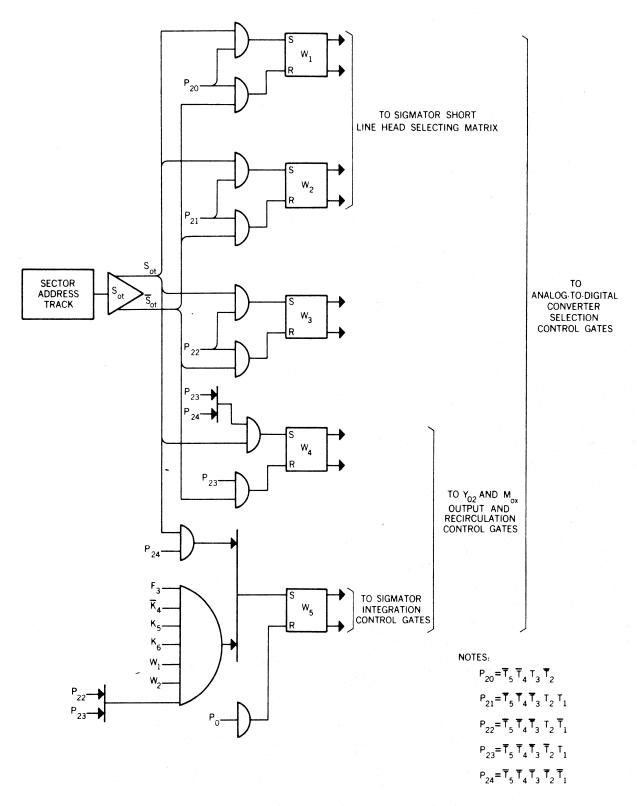

## 4-24. Sigmator Short Line

The sigmator short line is used as an increment accumulation register in the sigmator section of the computer. The sigmator short line contains one write head and associated write amplifier  $\mathbf{x}_0$ , and five read heads to provide increased availability of information. One read head is associated with read flip-flop  $\mathbf{X}_{01}$  and provide a word delay between  $\mathbf{x}_0$  and  $\mathbf{X}_{01}$ . The other four read heads ( $\Delta 1$ ,  $\Delta 2$ ,  $\Delta 3$ , and  $\Delta T$ ) time share read flip-flop  $\mathbf{X}_{02}$ . Head selection is accomplished by a head selecting matrix which is program

controlled via flip-flops  $W_1$  and  $W_2$  of the input-output selection register, refer to paragraph 4-31. Head spacing provides the following delays with respect to  $X_{01}$ : head  $\Delta 1$  - 6 words, head  $\Delta 2$  - 12 words plus 19 bits, head  $\Delta 3$  - 16 words plus 13 bits, head  $\Delta T$  - 29 words plus 5 bits.

Incremental information is received by input  $\mathbf{x}_0$  from the output of the sigmator one-increment adder-subtractor. Output  $\mathbf{X}_{01}$  is used as an input to the one-increment adder-subtracter, and output  $\mathbf{X}_{02}$  is used as an input via the sigmator two-input adder to the sigmator long line.

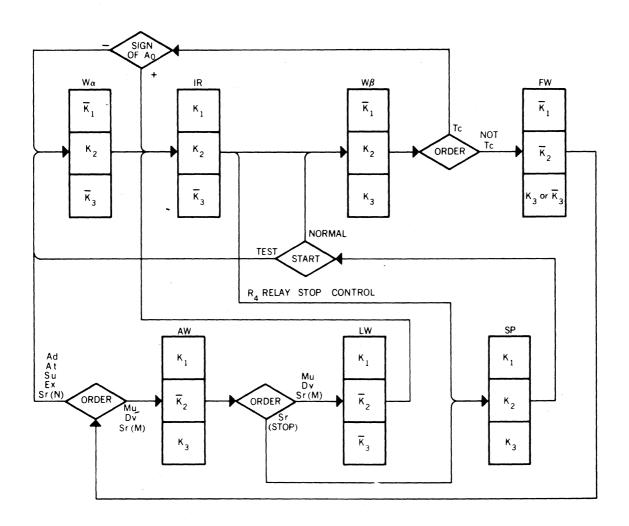

### 4-25. CONTROL

The major over-all control governing computer operation is the stored program on the memory drum. Important subsidiary controls which enable the computer to follow the program include (1) the pulse time indicator, (2) the phase sequencing control, (3) the order register, (4) the track selection register, and (5) the input-output selection register.

The pulse time indicator enables designation of each pulse time of a computer word to afford precise timing of all operations. The phase sequencing control provides over-all sequential control of operations. During a particular phase, for example, only certain types of computer operation are permitted. When these operations are completed, another phase is entered thereby allowing other types of operation to be performed. The various phases normally follow one another in a limited number of fixed sequential patterns. The order, track selection, and input-output selection registers receive coded program information from the drum during specified control phases. The registers store the codes until phase control permits the codes to be sampled and acted upon.

The order register stores the order part of an instruction word, the track selection register normally stores the code of a desired track in main memory, and the input-output selection register normally stores the code of a desired converter in the input-output equipment.

The following paragraphs provide detailed descriptions of these controls which are essential to the general purpose section of the computer. Controls peculiar to the sigmator section are separately discussed in paragraph 4-69.

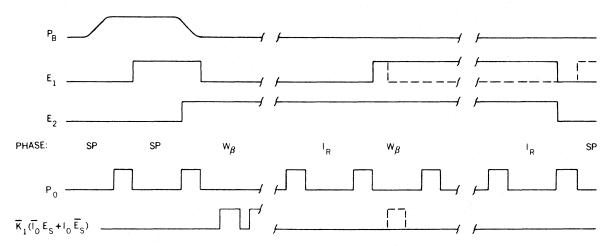

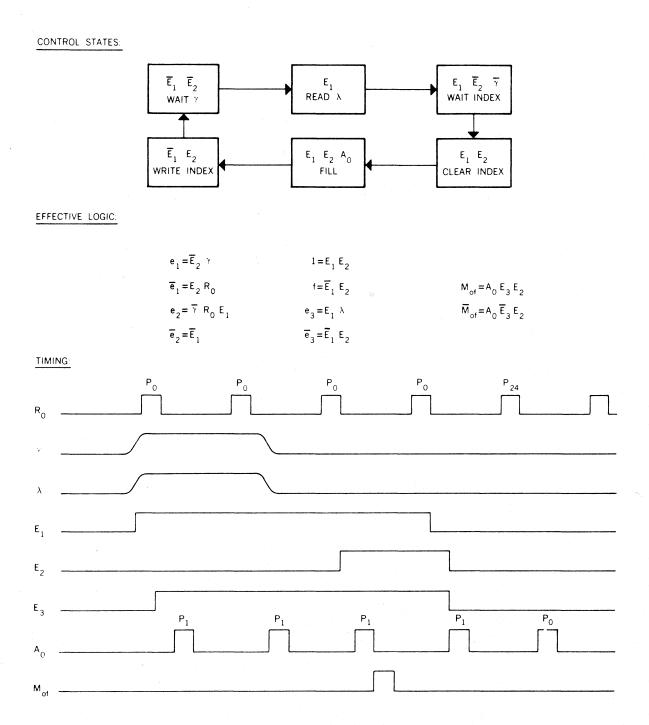

#### 4-26. Pulse Time Indicator

The pulse time indicator consists of five flip-flops and their interconnecting logic. These flip-flops,  $T_1$  through  $T_5$ , are used to define each bit of a "computer word". The configuration of the pulse time indicator changes at each clock time. One computer word is composed of 25 bits which are termed  $P_{24}$  through  $P_0$ . The  $P_{24}$  bit occurs first, the  $P_0$  bit last. Each of the pulse time indicator flip-flops has a distinct output. The output waveforms of these flip-flops and logical derivations of these outputs with respect to their pulse times are illustrated in figure 4-3. The pulse time indicator normally recycles every word time. The pulse time indicator logical diagram, figure 4-4 illustrates the logic for the pulse time indicator together with its logical equations.

4-27. Initial Synchronization. Synchronization of the pulse time indicator is accomplished in less than two drum revolutions at computer start. This initial synchronization is accomplished by a "1" that is contained in all 64 words on the sector address track ( $S_{ot}$ ) at pulse time 15 only. When the T flip-flops come on, they may or may not be defining the correct time. That is, the pulse time defined by the indicator may not be the same as the true pulse time at any read flip-flop. Whether or not the indicator is defining the correct pulse time, it will count down in a normal sequence until the  $P_{15}$  pulse is defined. At this time the indicator will sample  $S_{ot}$ . The condition of  $S_{ot}$  determines whether the indicator continues in a normal manner, or precesses to the  $P_{20}$  state. This operation is described in the following paragraphs.

At  $\mathbf{P}_{15}$  time the pulse time indicator flip-flops assume the following states.

Figure 4-3. Basic Timing Diagram

Figure 4-4. Pulse Time Indicator, Logic Diagram

In order to define  $P_{14}$ , the indicator flip-flops must assume the following new states.

$${f T}_5 \ {f T}_4 \ {f T}_3 \ {f T}_2 \ {f T}_1$$

${f P}_{14} \ {f 1} \ {f 0} \ {f 1} \ {f 0} \ {f 1}$

The  $T_3$  and  $T_2$  flip-flops do not require a change of state. However, the state of  $T_5$ ,  $T_4$ , and  $T_1$  must change.

To change the state of  $T_4$ , the following logic is required:  $\overline{t}_4 = T_3 \overline{T}_2 \overline{T}_1 + P_0$ . This equation is satisfied at  $P_{15}$  time by the  $T_1$ ,  $T_2$  and  $T_3$  flipflops.  $T_1$  and  $T_2$  are low, and  $T_3$  is high; i.e.,  $T_3 \overline{T}_2 \overline{T}_1$ . Therefore,  $T_4$  changes state.

To turn on  $T_1$ , the following logic is required:

$$t_1 = \overline{T}_3 + \overline{T}_5 T_4 S_{ot} + T_5 \overline{T}_4 \overline{T}_2 + \overline{T}_5 T_2$$

The state of the pulse time indicator flip-flops at  $P_{15}$  allow only the  $\overline{T}_5$   $T_4$   $S_{ot}$  portion of the OR gate to satisfy the equation. The  $T_1$  flip-flop is now dependent on the condition of the sector address track ( $S_{ot}$ ).

To turn on  $T_5$ , the following logic is required:  $S_{ot} T_3 T_4 \overline{T}_2$ . The condition of the pulse time indicator flip-flops indicator time  $P_{15}$  is such that the  $T_3 T_4 \overline{T}_2$  portion of the OR circuit is satisfied. However, the  $T_5$  flip-flop is dependent on the condition of  $S_{ot}$ .

The condition of  $S_{ot}$  will now dictate the pulse time defined by the indicator. Where a 1 appears in all 64 words of  $S_{ot}$  at indicator time  $P_{15}$ , the  $T_{1}$  and  $T_{5}$  flip-flops will turn on and the indicator condition will be as follows:

The pulse time indicator is then defining P<sub>14</sub>, and the normal count will continue.

However, where a 0 appears in any word of the  $S_{ot}$  track at indicator time  $P_{15}$ , the  $T_1$  and  $T_5$  flip-flops will remain off and the condition of the pulse time indicator will be as follows:

This condition defines the  $P_{20}$  pulse time. The indicator will now count down from  $P_{20}$  through  $P_{15}$ , where the condition of  $S_{ot}$  will again decide whether the pulse time indicator will continue the count in a normal manner or reset to  $P_{20}$  and attempt to sync once more.

The possibility of a "false sync" exists due to the fact that the data on the  $S_{\rm ot}$  track, except for  $P_{15}$  time, is random with respect to the sync operation. This "false sync" condition is compensated for by the fact that every time  $P_{15}$  is defined by the indicator, a l on the sector address track is required to continue the count. The true  $P_{15}$  time is the only time that  $S_{\rm ot}$  will contain a l in all 64 words of the track every time it is defined.

4-28. Sigmator Program Delay. Another function of the pulse time indicator is to delay part of the sigmator program from S<sub>ot</sub> into the sigmator control flip-flops. This is defined by the following logic:

$$t_5 = S_{ot} T_2 \overline{T}_1 T_3$$

$$t_4 = S_{ot} T_5 \overline{T}_1 T_3.$$

This function is described in paragraph 4-69.

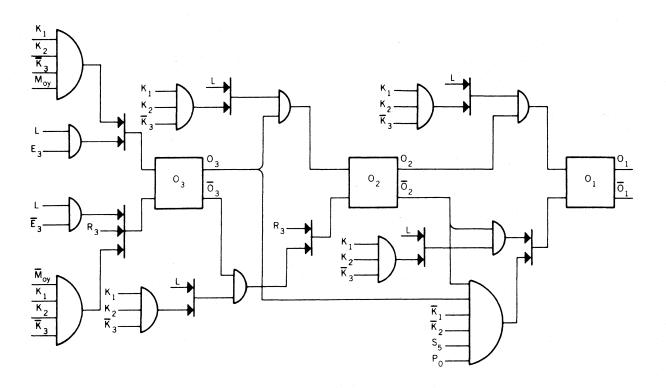

# 4-29. Order Register

The order register is comprised of three flip-flops, 0<sub>1</sub>, 0<sub>2</sub>, and 0<sub>3</sub>, which allow for eight basic orders. Thirty-two additional operations are provided by time sharing the output of the track selection register flip-flops,

S<sub>1</sub> through S<sub>5</sub>, with a store order (Sr) to define unique kinds of store orders. This provides a total of 39 operations, of which, 38 are used to provide 13 different commands. Store order codes are listed in section 5 of this manual. Listed below are the eight basic commands.

|                        | 0 1 | 02 | 03  | ORDERS               |

|------------------------|-----|----|-----|----------------------|

| At                     | 0   | 0  | 0   | Clear and Add        |

| $\mathbf{E}\mathbf{x}$ | 0   | 0  | 1 1 | Extract              |

| Mu                     | 0   | 1  | 0   | Multiply             |

| Тс                     | 0   | 1  | 1   | Conditional Transfer |

| Ad                     | 1   | 0  | 0 , | Add                  |

| Dv                     | 1   | 0  | 1   | Divide               |

| Su                     | 1   | 1  | 0   | Subtract             |

| Sr                     | 1   | 1  | 1   | Store (Normal)       |

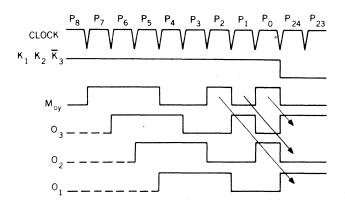

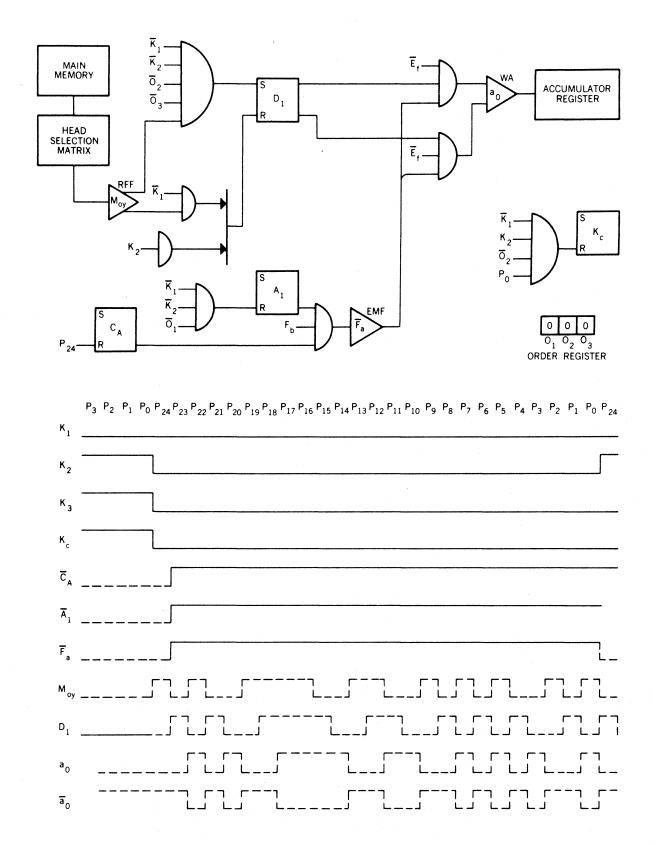

The order is read from the instruction in the main memory during the IR phase and is stored in the order flip-flops until the next order is read in except for certain modified store orders. The order is read in to  $0_3$  and shifted through to  $0_2$  and  $0_1$ , so that the bit at  $P_2$  ends up in  $0_1$ , the bit at  $P_1$  ends up in  $0_2$ , and the bit at  $P_0$  remains in  $0_3$ . Figure 4-5 shows the wave forms of the order register flip-flops as the order is shifted through to its final configuration. The order from the main memory  $(M_0)$  is read in to the order register during the IR phase  $(K_1 \ K_2 \ \overline{K}_3)$ . The arrows indicate where each bit is stored. The order illustrated by the figure is the divide order.

Figure 4-5 illustrates the logic network for the order register. Logic for the order register flip-flops is listed below.

$$o_{1} = (K_{1} \ K_{2} \ \overline{K}_{3} + L) \ 0_{2}$$

$$\overline{o}_{1} = (K_{1} \ K_{2} \ \overline{K}_{3} + L) \ \overline{o}_{2} + o_{2} \ o_{3} \ \overline{K}_{1} \ \overline{K}_{2} \ S_{5} \ P_{0}$$

$$o_{2} = (K_{1} \ K_{2} \ \overline{K}_{3} + L) \ 0_{3}$$

$$\overline{o}_{2} = (K_{1} \ K_{2} \ \overline{K}_{3} + L) \ \overline{o}_{3} + R_{3}$$

Figure 4-5. Order Register, Logic and Timing Diagram

$$o_3 = K_1 K_2 \overline{K}_3 M_{oy} + L E_3$$

$$\overline{o_3} = K_1 K_2 \overline{K}_3 \overline{M}_{oy} + L \overline{E}_3 + R_3$$