# GENERAL PRECISION | LIBRASCOPE GROUP

L

l

L

Ľ

L

l

1

## 808 WESTERN AVENUE, GLENDALE 1, CALIFORNIA

Technical Description L-1192 CONTROLLER PROCESSOR

# **Technical Description**

# L-1192 CONTROLLER PROCESSOR

.

# CONTENTS

| Section |      |                                                     | Page               |

|---------|------|-----------------------------------------------------|--------------------|

| 1.0     | INTI | RODUCTION                                           | 1 - 1              |

| 2.0     | SUM  | MARY OF APPROACH                                    | 2 - 1              |

|         | 2.1  | Word Format                                         | 2 - 1              |

|         | 2.2  | Instruction Efficiency                              | 2 - 1              |

|         | 2.3  | Communication Interface                             | 2 - 1              |

|         | 2.4  | Code/Format Flexibility                             | 2 - 1              |

|         | 2.5  | I/O Stations                                        | 2-2                |

|         | 2.6  | Communication Processing                            | 2 - 2              |

|         | 2.7  | I/O Interface                                       | 2-2                |

|         | 2.8  | Support Software                                    | 2-2                |

|         | 2.9  | AUTODIN Processing                                  | 2-3                |

| 3.0     | EQU  | IPMENT DESCRIPTION AND OPERATION                    | 3 - 1              |

|         | 3.1  | Core Memory                                         | 3 - 1              |

|         | 3.2  | L-1192 Controller-Processor                         | 3 - 1              |

|         |      | <ul><li>3.2.1 Arithmetic and Logical Unit</li></ul> | 3 - 1<br>3 - 7     |

|         |      | Card/Print I/O                                      | 3-9                |

|         |      | 3.2.4 I/O Interface                                 | 3 - 1 0<br>3 - 1 0 |

|         |      | 3.2.6 L-1192 Interval Timer                         | 3-14               |

| 4.0     | L-1] | 192 INSTRUCTIONS                                    | 4 - 1              |

|         | 4.1  | Fixed Length Character Operations                   | 4 - 1              |

|         | 4.2  | Variable Field Operations                           | 4-8                |

|         | 4.3  | Full Word Operations                                | 4-12               |

|         | 4.4  | Program Control Operations                          | 4-14               |

|         | 4.5  | Internal Condition Operations                       | 4-15               |

|         | 4.6  | Communication Interface Operations                  | 4-1ó               |

|         | 4.7  | Input/Output Operations                             | 4-18               |

•

•

# CONTENTS - Continued

| Section |     |                                                                                                                         | Page                                   |

|---------|-----|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 5.0     | PER | IPHERAL EQUIPMENT                                                                                                       | 5-1                                    |

|         | 5.1 | Line Unit Console                                                                                                       | 5 - 1                                  |

|         | 5.2 | Model 2250 Systematics Card/Printer Input/<br>Output Stations                                                           | 5-2                                    |

|         |     | 5.2.1 Operating Modes5.2.2 Operating Speed5.2.3 Station Devices                                                         | 5-2<br>5-3<br>5-3                      |

|         | 5.3 | Magnetic Tape Console                                                                                                   | 5-5                                    |

|         |     | <ul> <li>5.3.1 Tape Transport On-Line Read</li></ul>                                                                    | 5-6<br>5-8<br>5-8                      |

|         | 5.4 | Card Reader/Punch Console                                                                                               | 5-9                                    |

|         |     | 5.4.1 Card Reader                                                                                                       | 5-9<br>5-11                            |

|         | 5.5 | High-Speed Printer Console                                                                                              | 5-11                                   |

|         | 5.6 | Master Disc File Console                                                                                                | 5-13                                   |

| 6.0     |     | PORT SOFTWARE AND PROGRAMMING                                                                                           | 6 - 1                                  |

|         | 6.1 | LAP-1192 Assembler                                                                                                      | 6 - 1                                  |

|         |     | ó.1.1Purposeó.1.2Equipment Requiredó.1.3Input Mediaó.1.4Output Mediaó.1.5Featuresó.1.6Input Formató.1.7Pseudo-Operation | 6-1<br>6-1<br>6-1<br>6-2<br>6-3<br>6-3 |

|         | 6.2 | System Loader                                                                                                           | 6 <b>-</b> 6                           |

|         | 6.3 | Core and Disc Dump                                                                                                      | 6 <b>-</b> 7                           |

|         | б.4 | Acceptance Tests                                                                                                        | 6-7                                    |

| 7.0     | AUT | ODIN PROCESSING                                                                                                         | 7 - 1                                  |

|         | 7.1 | Input Processing                                                                                                        | 7 - 1                                  |

|         |     | 7.1.1Character Frame7.1.2System States                                                                                  | 7 - 1<br>7 - 4                         |

# CONTENTS - Continued

# Section

Page

| 7.1.4          | Data Characters                                                                          | 7 - 4<br>7 - 5<br>7 - 5                                                                         |

|----------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Output         | Processing                                                                               | 7-6                                                                                             |

| 7.2.2<br>7.2.3 | Start of Block Processing                                                                | 7 -6<br>7 -6<br>7 -8<br>7 -8                                                                    |

| Channe         | el Coordination                                                                          | 7 - 8                                                                                           |

| 7.3.2          | Processing of RM and DM                                                                  | 7 - 10<br>7 - 11<br>7 - 14                                                                      |

|                | 7.1.4<br>7.1.5<br>Output<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>Channe<br>7.3.1<br>7.3.2 | <ul><li>7.3.2 Processing of RM and DM</li><li>7.3.3 Establishment of Acknowledge Sync</li></ul> |

# ILLUSTRATIONS

# Figure

•.

i

.

١

# Page

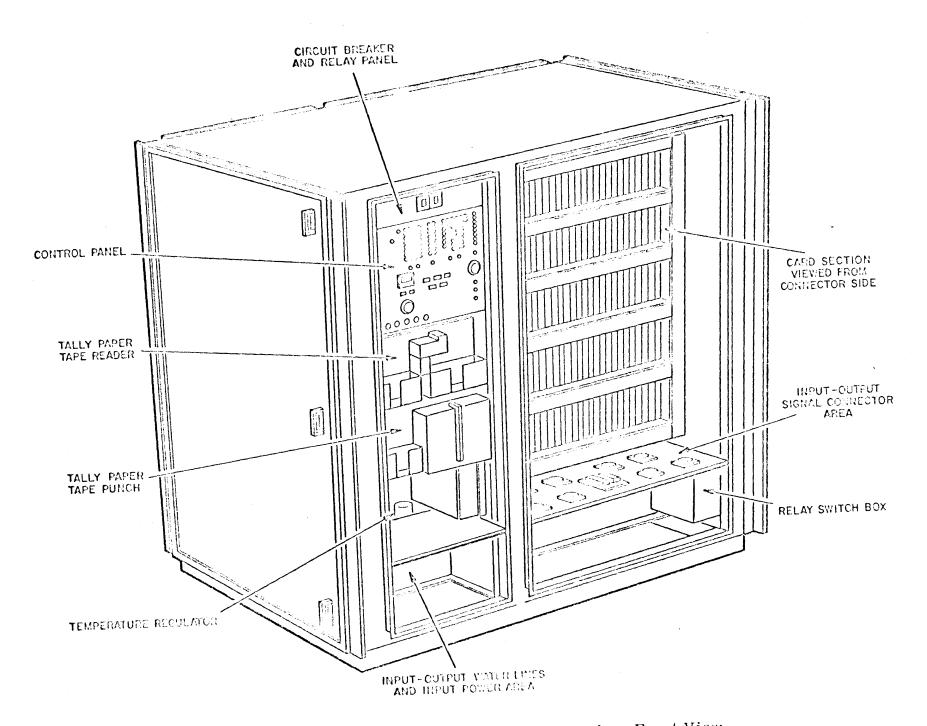

| 3 - 1 | L-1192 Buffer Processor Console - Front View             | 3-2          |

|-------|----------------------------------------------------------|--------------|

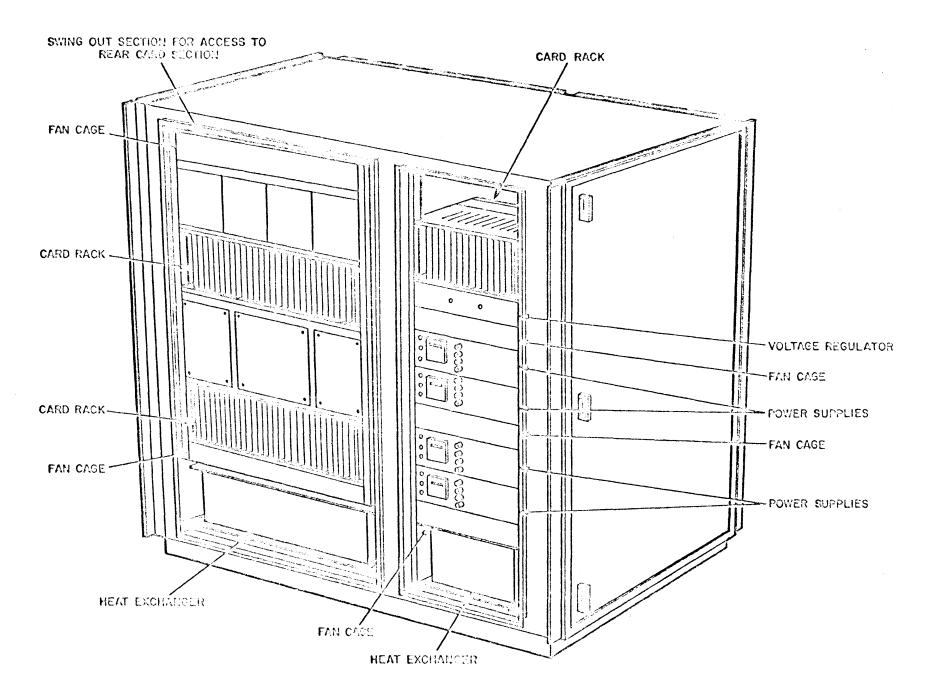

| 3 - 2 | L-1192 Buffer Processor Console - Rear View              | 3 - 3        |

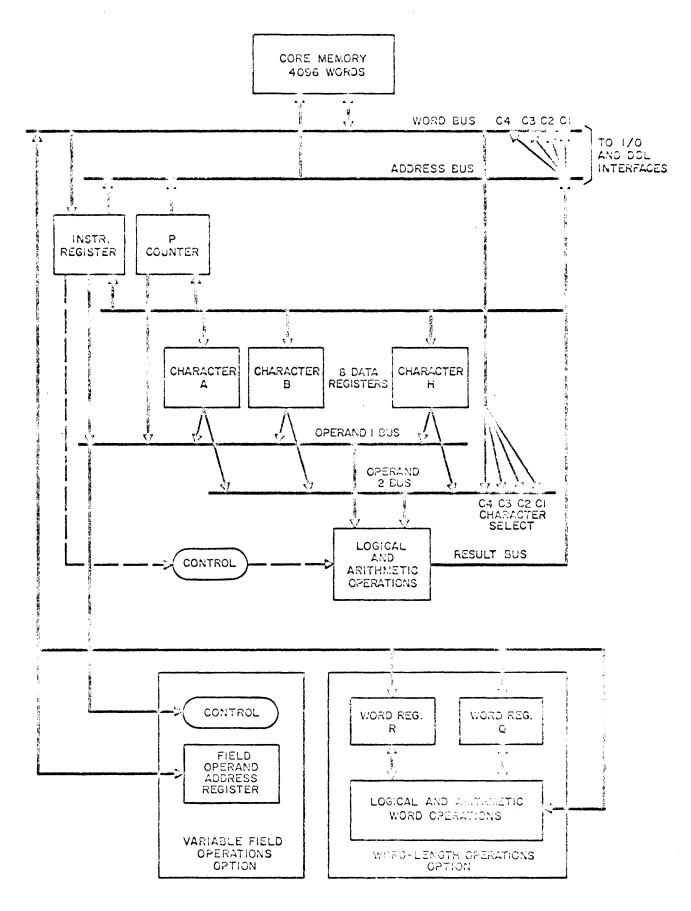

| 3 - 3 | L-1192 Buffer Processor, Block Diagram                   | 3 - 5        |

| 3-4   | L-1192 Maintenance Panel                                 | 3 - 1 1      |

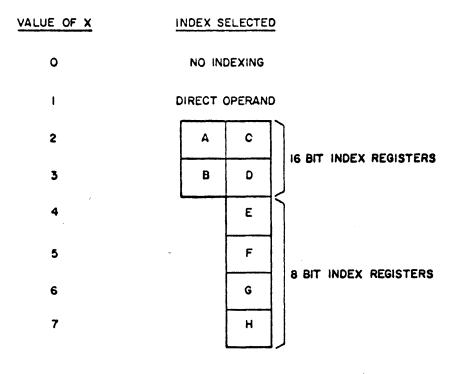

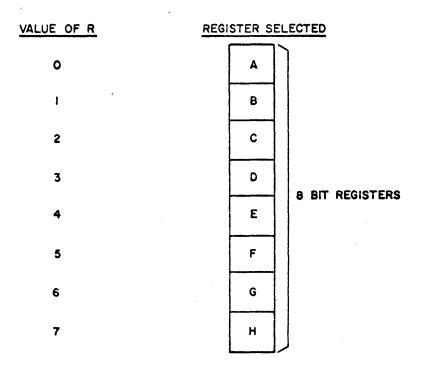

| 4 - 1 | Register Selection                                       | 4 - 1        |

| 5-1   | Magnetic Tape Console Control Panel                      | 5-7          |

| 5-2   | Card Reader/Punch Console                                | 5-10         |

| 5-3   | High-Speed Printer Console                               | 5-12         |

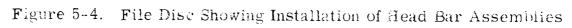

| 5-4   | File Disc Showing Installation of Hear Bar<br>Assemblies | 5-14         |

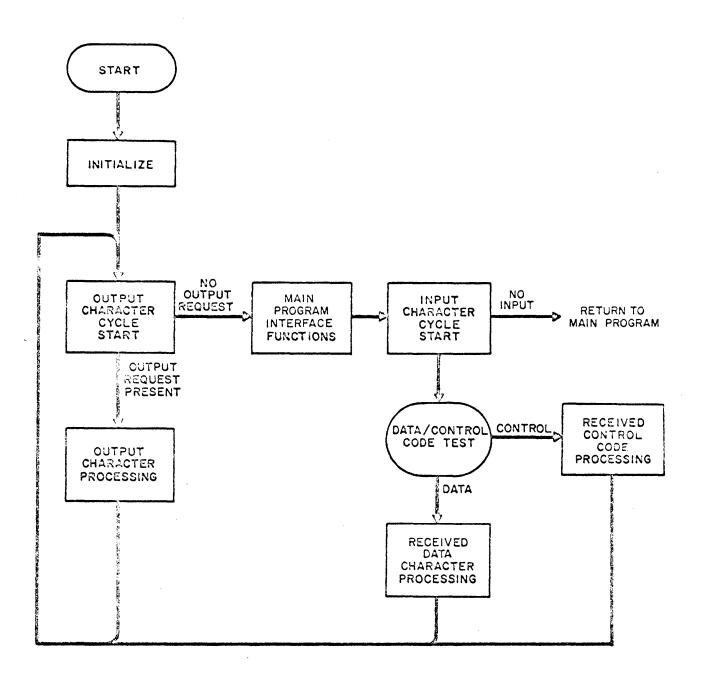

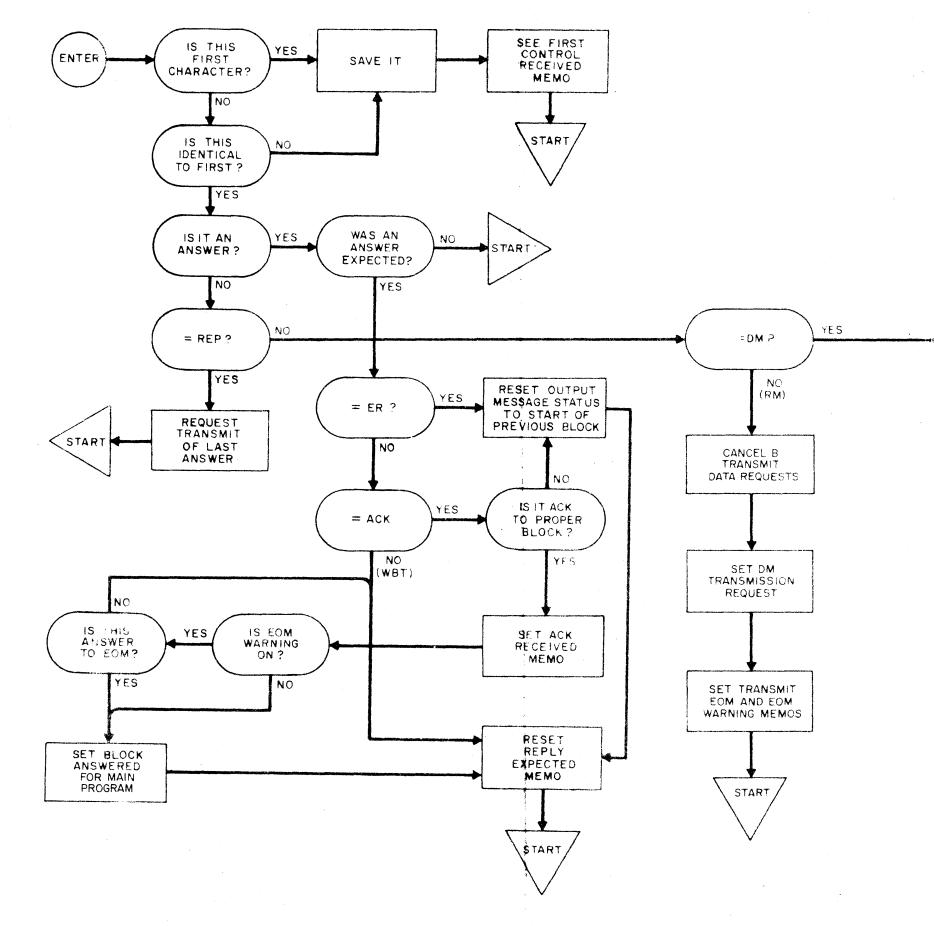

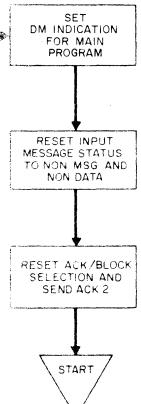

| 7 - 1 | AUTODIN Program - Overall Flowchart                      | 7-2          |

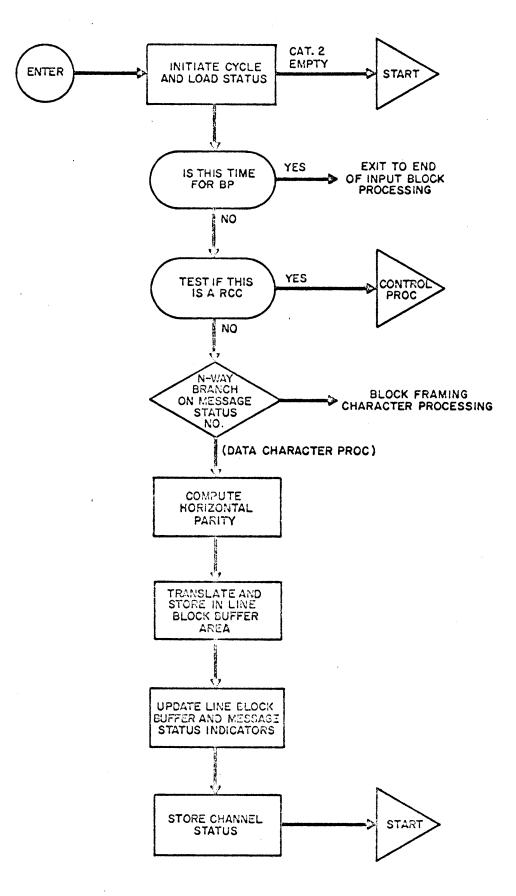

| 7-2   | Input Character Processing                               | 7 <b>-</b> 3 |

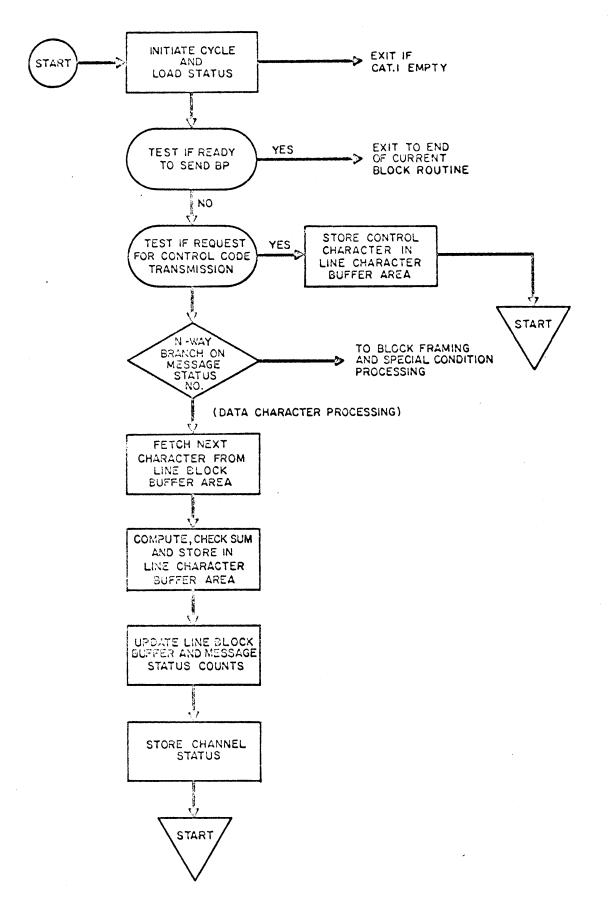

| 7-3   | Output Character Processing                              | 7-7          |

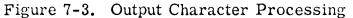

| 7-4   | Channel Coordination Processing                          | 7-9          |

### Section 1

#### INTRODUCTION

This document presents a technical description of the L-1192 Controller-Processor system. The Librascope design approach is based primarily on experience gained from their L-3055 data processing system. This equipment was developed and installed in the Pentagon as the AN/FYQ-11 data processing elements of Command and Control System 473-L. Extensive effort was expended to structure and create a system which will function reliably and continuously without loss of service.

The L-1192 system provides a stored-program binary computer, with both an AUTODIN communication interface and general purpose processing capability. It will operate as a communication buffer to the L-3155 Central Processor in the 473-L system, and can also provide this function for other available processing systems. The L-1192 Controller-Processor may also be utilized as a general-purpose computer on its own. It will interface with a variety of communication channels, input-output stations, and peripheral devices. These include asynchronous and synchronous lines, paper tape/card/typewirter I/O stations, magnetic tape transports, card reader/punches, disc files, and high speed line printers.

A description of the L-3155 Central Processor, which provides eight 7-bit alphanumeric characters per computer word, is provided under separate cover.

1-1

#### Section 2

### SUMMARY OF APPROACH

The L-1192 Controller Processor is a general purpose computer system, with special emphasis on the efficient processing of input-output and communication data.

## 2.1. WORD FORMAT

The L-1192 provides 2 microsecond cycle cone memory in modules of 4096 words, with a maximum capacity of 65,536 words. The 33-bits per word includes 32 data bits, providing four 8-bit characters, plus one parity bit. This word length permits an instruction format well suited to character processing and addressing.

### 2.2 INSTRUCTION EFFICIENCY

The L-1192 offers three categories of processor instructions: single characted operations, variable-length field operations, and full-word operations. The single character instructions utilize a group of eight arithmetic registers, which eliminates the bottleneck normally encountered in processing multiple input-output data.

### 2.3 COMMUNICATION INTERFACE

The L-1192 Console can communicate with up to four duplex communication channels, by the addition of the proper interface modules. This capability can be expanded to 64 duplex channels by means of an optional Line Unit Console. Any mix of asynchronous and synchronous lines is permissible. Asynchronous lines operate up to 150 bits/sec, and synchronous lines at up to 4800 bits/sec.

## 2.4 CODE/FORMAT FLEXIBILITY

The L-1192 has been designed to efficiently process AUTODIN communication requirements. Care has been exercised to permit flexibility of operation through program modification. Desired character codes, formats, and channel coordination procedures are under control of the stored program.

## 2.5 I/O STATIONS

The Standard Communication Interface will also communicate with up to eight input/output stations, which may be located at remote positions. One station is utilized by the 300 char/sec paper tape reader, 60 char/sec paper tape punch, and 15 char/sec electric typewriter at the Operator/ Maintenance Panel. The other seven stations may each provide a 20 char/ sec card read/punch and a 40 char/sec print station, or other desired I/O character device.

The number of I/O stations may be expanded in groups of 8 to a total of 32.

### 2.6 COMMUNICATION PROCESSING

Input characters and output requests for the communication channels and the I/O Stations automatically enter cyclic Channel Activity Tables reserved in core memory. These entries do not interrupt the system, and are accessible to the computer program for further processing.

## 2.7 I/O INTERFACE

One I/O Interface is provided with the L-1192 Controller Processor, and up to sixteen interfaces may be utilized. Each interface may communicate with up to sixteen standard Librascope peripheral devices. These include magnetic tape, card reader/punch, high-speed line printer, and disc file equipment.

## 2.8 SUPPORT SOFTWARE

The support software offered with the L-1192 system includes an Assembler, a System Loader, Core and Disc Dump, and Acceptance Test.

# 2.9 AUTODIN PROCESSING

Librascope has had extensive experience in processing communication data, and will be available to assist in meeting AUTODIN requirements. An operational approach developed for the L-1192 system is presented in this proposal.

#### Section 3

#### EQUIPMENT DESCRIPTION AND OPERATION

This section discusses the design and operation of each item of equipment available with the L-1192 Controller-Processor system.

### 3.1 CORE MEMORY

Core memory for the L-1192 Controller-Processor system is provided in modules of 4096 words. The L-1192 may address up to a maximum of sixteen modules, for a total of 65,536 words of memory. A word contains 32 data bits plus an additional bit to maintain odd parity. Each data word provides four 8-bit characters, which may be individually addressed by L-1192 instructions. Transfers to and from core memory are in word parallel, and these are parity checked. The core memory modules offer a readwrite cycle time of 2.0 microseconds. The transfers between core memory and the central processor arithmetic/logical unit, the communication interface, and the input-output interface all overlap on a cycle stealing basis.

### 3.2 L-1192 CONTROLLER-PROCESSOR

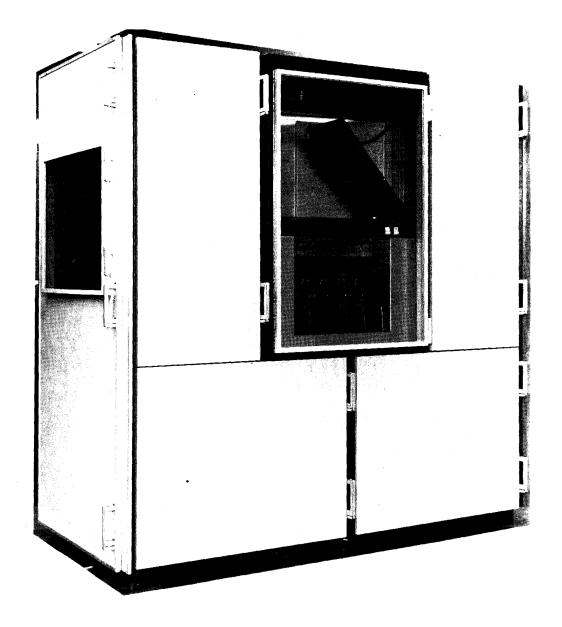

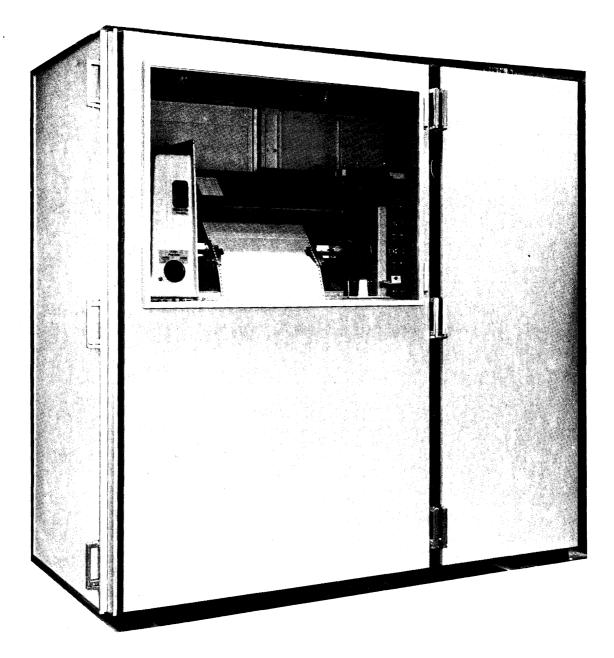

The L-1192 Controller-Processor consists of an Arithmetic and Logical Unit, a Communication Interface, Paper Tape Reader/Punch and Electric Typewriter, an I/O Interface, and the Maintenance Panel, and an Interval Timer. The L-1192 Console is presented in Figures 3-1 and 3-2.

#### 3.2.1 Arithmetic and Logical Unit

The L-1192 ALU includes the instruction register and instruction decode logic, individually addressable character-length data registers, a Field Operand Address Register, and two full-word arithmetic registers.

The simple yet flexible organization of the L-1192 is apparent from the block diagram of the processor organization, presented in Figure 3-3 any operations which involve two operands can be obtained in any combination from the data or word registers and memory by general bus logic. The

Figure 3-1. L-1192 Buffer Processor Console - Front View

3-2

Figure 3-2. L-1192 Buffer Processor Console - Rear View

ເມ |-ເປ function of address modification is also performed by this technique. Communication with the core memory is by an address and word bus which is time shared with the Communications Interface and with the I/O Interface.

3.2.1.1 <u>Data Format.</u> Each L-1192 word consists of 32 data bits plus one parity bit. Four 8-bit data characters are contained in a word, and these characters may be individually selected by the L-1192 instruction.

| _ | 8              | 8              | 8              | 8              | 1 |

|---|----------------|----------------|----------------|----------------|---|

|   | Character<br>4 | Character<br>3 | Character<br>2 | Character<br>l | Р |

3.2.1.2 Instruction Format. Instructions are one word in length, and permit register selection in addition to memory word addressing. Special features of the instruction set include direct character selection, word and character indexing, indirect addressing for both memory and registers, and the inclusion of specialized instructions.

3.2.1.3 <u>Memory Addressing</u>. The address field of an instruction provides for direct reference to any one of 65,536 words of core memory. In addition, 2 bits appended to the low order end of the address field permit the selection of an individual character within the word. This feature provides full-character addressing.

3.2.1.4 <u>Processor Instructions</u>. The L-1192 offers three categories of processor instructions. Fixed length character instructions primarily provide single-character transfer, arithmetic, and logical operations. These facilitate the processing of data from multiple communication lines and direct-coupled paper tape, punched card, and typewriter/printer de-vices. A set of variable field (up to 16 character) instructions provide added formatting and editing capability for both communication and input-output devices. Word-length operations are also provided to meet higher speed processing requirements.

3-4

Figure 3-3. L-1192 Buffer Processor, Block Diagram

3.2.1.5 <u>Specialized Instructions.</u> Several of the L-1192 instructions have been specialized in order to enhance speed-cost effectiveness in communication and input-output processing. The inclusion of these instructions combine the advantages of wired logic with the flexibility of stored program control. An Initiate Character Cycle instruction, for example, will efficiently locate and access the next input character or output request to be processed. These were automatically stored in core memory Channel Activity Tables (CAT) by the L-1192 hardware.

3.2.1.6 <u>Character Data Registers.</u> The L-1192 is provided with a set of 8 character-length static registers, which are basic to its list of powerful character processing instructions and capabilities. Any of the 8 registers may be utilized in arithmetic, data, or logical operations. Most operations involve a single register and a location in core memory. Operations may also be specified which involve only a pair of registers, or a register and an operand or mask contained in the instruction word itself. These features serve to reduce the amount of time normally consumed by computers in the access and storing of operands in core memory. The unusually high character processing efficiency of the L-1192 is attained by making up to 8 separate data items immediately available to the arithmetic unit.

The data registers may also function as index registers. When used as index registers, four of the 8-bit data registers operate independently. Each can provide a total modification of 256 character or 64-word addresses. The remaining four are paired to provide two 16-bit index registers, each with an addressing capacity of 65, 536 characters. Indirect addressing is also a feature of the L-1192, and may extend over any number of levels. Indexing is effective at each indirect level.

3.2.1.7 <u>Additional Registers</u>. The variable field instructions provide memory to memory operations. One operand address and field length is normally specified by the instruction word. The second operand address and field length must first be loaded into a Field Operand Address Register (FOAR). The full-word instructions utilize two independent word

3-6

arithmetic registers (R and Q). The variable field instructions and the full-word instructions also utilize the character data registers as index registers. They are available as arithmetic registers only to the fixed length character instructions.

3.2.1.8 Error Checks. To insure message protection, the L-1192 employs several internal error checks. These include an automatic test of word parity when a word is transferred from core memory, and parity checks on transfer operations between the L-1192 and the I/O peripheral devices. Program testing is normally utilized to parity check characters received from the communication lines.

3.2.1.9 <u>Interrupts</u>. To permit efficient servicing of the Input-Output and Communication Interfaces, a number of interrupts have been provided. The conditions which can cause an interrupt include: Interval Timer elapsed, I/O operation ended, service requests from the peripheral devices, and internal or input-output parity error.

When an interrupt occurs, the content of the P counter and a bit indicating the cause of the interrupt are stored in core memory location  $\emptyset$ , and the next instruction is taken from location 1. All other interrupts are then prevented from occurring. They may be enabled by use of the ESI or PSI instructions.

## 3.2.2 Communication Interface

The Communication Interface is contained in the L-1192 Controller-Processor Console. It controls the transfers of data between core memory and on-line communication channels or devices.

The basic system can accommodate four input and four output communication channels, by the addition of optional Line Interface Modules. Modules may be specified for asynchronous or for synchronous transmission at rates up to 4800 baud. The communication interface capability can be expanded by the addition of an optional Line Unit Console, which can accommodate up to 64 input and 64 output communication interface modules and channels. 3.2.2.1 <u>Core Buffering</u>. Character buffering is provided by the interface modules, while message blocks are accumulated in core memory. This approach results in significant saving in system cost, and permits the program to operate asynchronously with line rates.

The core buffering operation is performed in a unique and efficient manner. Two cyclic table areas, named Channel Activity Tables, are reserved in core memory. These are automatically loaded by the Communication Interface with the input characters or with requests for output characters, each with a line identity number. Channel Activity Table 1 (CAT 1) is reserved for character requests made by high speed output lines. Channel Activity Table 2 (CAT 2) is used to buffer all other lower priority output requests and all input traffic. CAT 1 may contain 128 entries or words in memory, while CAT 2 has a capacity of 256 entries.

3.2.2.2 <u>Communication Line Servicing</u>. The Communication Interface makes use of two cyclic load address registers designated Ll and L2, for CAT 1 and CAT 2 control respectively. Each time an entry is to be stored in either table, the appropriate load counter provides the required core loading address and is then stepped. CAT 1 and CAT 2 are unloaded and processed by means of two other cyclic address counters, named Ul and U2. A more detailed discussion of the procedure for unloading of CAT 1 and CAT 2 is contained in the discussion of the Initiate Character Cycle instruction, found in Section 4.6.

The output characters transmitted in response to output requests are automatically obtained from another table, named the Line Character Buffer Table. The LCBT contains one assigned character address in core memory for each output line implemented. These output locations are loaded by the program with the next output character for the corresponding line number. When an output interface module has completely transmitted an output character it initiates an interface available signal, which will be detected by and halt the scanners in both the Line Unit Console and in Communication Interface. The two scanner positions will generate the proper character memory address in the LCBT, and the character at this position

3-8

will transfer to the waiting output line interface module. The Communication Interface will then load an output request, including the line identification number, into CAT 2 (for high speed lines) or into CAT 1 (for slow speed lines). The L1 or L2 load point is stepped, and the scanners are released to continue searching for other input or output traffic. Input traffic is handled in a somewhat similar manner by the Communication Interface. When a complete character has been accumulated by an input line interface module, it sets a signal causing the scanners to stop. Memory access is obtained, and the character plus the associated line number is automatically transferred to the next available word location in CAT 2. The L2 load point is stepped, and the scanners are then released to continue looking for traffic. The input character will be processed by the L-1192 program, whose instructions can efficiently access the next input character or output request from the two Channel Activity Tables.

3.2.2.3 <u>Channel Activity Table Formats</u>. The following information provides the word formats loaded into the Channel Activity Tables (CAT) for the input characters and the output requests.

|                   | 8        | 8 |   | 8                      |              |

|-------------------|----------|---|---|------------------------|--------------|

| Input<br>Entry    | Not Used |   | 0 | Line/Device<br>Address | Input Char.  |

| Output<br>Request | Not Used |   | 1 | Line/Device<br>Address | Alway's Zero |

## 3.2.3 Paper Tape, Typewriter, and Card/Print I/O

The basic Communication Interface also communicates with up to eight direct-connected input-output stations, which may be located at remote sites. The number of such stations accessible to the communication interface may be optionally increased in groups of eight up to a total capacity of 32 such stations. The paper tape reader, punch, and IBM keyboard/ typewriter at the computer console provide one station position. A Kleinschmidt keyboard/printer, and a card reader/punch may be located at each of the other seven station positions. These stations will, however, accept other input-output devices which contain the proper interface. Transfers to or from these devices are character-serial, with up to 8 bits/char.

## 3.2.4 I/O Interface

The I/O Interface provides for data transfers to and from the standard line of Librascope magnetic tape, card reader/punch, line printer, and disc file equipment. These peripheral devices are presently utilized in the Librascope AN/FYQ-11 Data Processor Set for the Headquarters U.S. Air Force 437-L Command and Control System. All data transfer to and from these devices occur on an asynchronous basis, with the I/O interface obtaining memory access priority as needed. The I/O interface will independently execute interface block transfers, and overlap central processor operations.

3.2.4.1 <u>Description.</u> The I/O interface contains a Device Command Register, a Block Control Register, an Interface Data Register, a Command Address Register, and associated control and bus logic. Once the interface has been placed in operation, it will access a device Command Word and a Block Control Word from core memory. The Command Word specifies the device and command operation. The Block Control word designates the memory starting address and the required number of characters. Data is shifted into or out of the Interface Data Register in a character-serial fashion on a device demand basis. As data is transferred, the Block Control Register counts characters and memory locations. When the Block Control word is satisfied, the operation is terminated and the main processor program is interrupted.

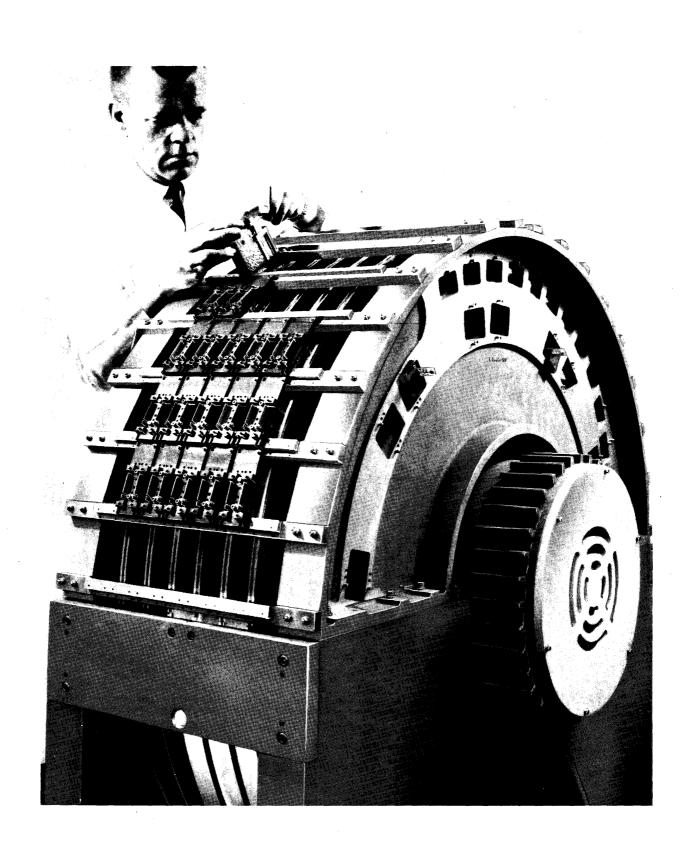

## 3.2.5 L-1192 Maintenance Panel

The maintenance panel, presented in Figure 3-4, contains the necessary controls and indicators for performing preventive or corrective maintenance on the L-1192 Controller-Processor and its interfaces. By means of these controls and indicators, the various internal registers are displayed and their contents may be altered. In addition, L-1192 error

Figure 3-4. L-1192 Maintenance Panel

indicators may be reset from this panel. The output voltages of the various power supplies may be measured, and their outputs biased to assist in detecting machine malfunctions. The following paragraphs describe in detail the functions of the various controls and indicators on the maintenance panel.

3.2.5.1 <u>Word Register Display and Switches.</u> An array of 33 pushbutton indicator/switches displays the content of the specified word register. Selection of the Memory Access Register (M), the Field Operand Access Registers (F), or the word arthmetic R and Q Registers is by means of a "Word Register" select switch. The display is arranged into 4 characters of eight bits each and the parity bit. An associated error indicator is illuminated when the memory register is selected and contains a parity fault condition (even number of bits). Direct manual memory entry is performed using the Clear and Load pushbutton switches. The Clear pushbutton clears the selected register to binary zeros, except for the parity bit which is a binary one to maintain required odd parity. The desired word is then set by pushing appropriate register pushbuttons. Pushing the parity pushbutton will set the correct parity bit and reset the error indicator.

Pressing the STORE pushbutton stores the contents of the selected register into the address specified by the W portion of the Instruction Register. W is then incremented by one. The content of the memory location specified by W may be displayed by pressing the DISPLAY button, which also causes W to increment by one.

3.2.5.2 <u>Program Counter Display and Controls.</u> An array of pushbutton indicators displays the content of the program counter. The "PROGRAM COUNTER" display can be set to zero by the associated "CLEAR" pushbutton and new content set in manually.

3.2.5.3 Instruction Register Display and Controls. An array of pushbutton indicators displays by fields the content of the instruction register. The "INST REG" display can be cleared by the associated "CLEAR" pushbutton and new content set in manually. The currently contained instruction can be executed in stop mode by pushing the "EXECUTE" button, permitting instruction processing without counting up the program counter or leaving the stop mode.

3.2.5.4 <u>Operand Registers Display and Controls</u>. The "OPERAND REGISTERS" display pushbutton indicators may be used to observe the content of any of the 8 Data Registers, or the content of the two Load and Unload Counters associated with the communication interface. Selection of register or counter to be displayed is controlled by a rotary "DATA REGISTER" switch below the "OPERAND REGISTERS" indicators. The register currently displayed may have its content cleared to zero by means of the "CLEAR" pushbutton and a new content manually entered.

3.2.5.5 <u>Error Indicators.</u> The three error indicators in the lower righthand section of the panel display detail errors detected by the L-1192 hardware. The "INTERNAL PARITY ERROR" indicator will light whenever the L-1192 hardware detects a word parity error on transfers to or from core memory.

The "INTERFACE ERROR" indicator will light whenever the L-1192 interface logic detects a character parity error on input-output data transfers. The "TIMER ERROR" indicator will light whenever the INTERVAL TIMER counts down to zero.

3.2.5.6 <u>Operating Controls.</u> The ON and OFF buttons control the application of power. Pressing the RUN button will cause the L-1192 to locate and execute instructions at normal operating speed until either a HALT command is decoded, the STOP button is pressed, or an internal error is detected. The STEP button will cause a single instruction to be executed each time the button is pressed. Operation of the ERROR CLEAR will reset all error toggles. 3.2.5.7 Error Controls. The "ERROR CLEAR" pushbutton resets all error indicators.

The "IGNORE ERROR" pushbutton disables the halt on instruction parity error and may be used while operating diagnostic or maintenance programs.

3.2.5.8 <u>Power Supply Monitor and Controls.</u> By means of the associated selector switch, output voltages of the various power supplies in the L-1192 may be displayed on the meter on the lower left-hand portion of the main-tenance panel. Toggle switches are provided to control increase or de-crease of power supply voltages in the diagnosis of machine malfunctions.

### 3.2.6 L-1192 Interval Timer

The L-1192 Interval Timer is an electronic counter operated by the master logic clock. It is composed of 32 bits (one word). It counts down by one during each clock period. It can be pre-set under program control via the I/O interface, and its current value can similarly be stored in core.

The maximum pre-set value is equivalent to approximately one hour. Resolution is approximately ten times greater than the instruction execution rate.

#### Section 4

#### L-1192 INSTRUCTIONS

The detailed descriptions of L-1192 instructions have been grouped under the following general categories:

- 1. Fixed Length Character Operations

- 2. Variable Field Operations

- 3. Full Word Operations

- 4. Program Control Operations

- 5. Internal Condition Operations

- 6. Communication Interface Operations

- 7. Input/Output Operations

The timing provided with each instruction includes instruction and operand access, and is given in memory cycles (each 2 microseconds). If indirect addressing is employed, one cycle must be added for each indirect level. Indexing does not increase the instruction time.

#### 4.1 FIXED LENGTH CHARACTER OPERATIONS

These instructions provide for moving, comparing, modifying or performing arithmetic operations on single-character or fixed-length multiple character fields. These instructions are primarily used for performing character buffering functions. Most of them permit the selection of one of eight single character data registers in which the operation is to be performed. Those operations which address core memory also may specify indirect addressing, as well as indexing by one of six groups of character registers. If indirect addressing is designated, each indirect level may be independently indexed. Indexing does not normally increase the execution time, but each indirect level adds one memory cycle. The table shown below shows the general format for L-1192 fixed length character instructions. Where an individual instruction deviates from this format, the change is described in detail.

|        | 6                                                                |                                                              | 1                                                       | 3            | 1   | 3    | 16                             | 2             |  |  |  |

|--------|------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------|--------------|-----|------|--------------------------------|---------------|--|--|--|

|        | Op Code                                                          |                                                              | U                                                       | R            | I   | Х    | W                              | С             |  |  |  |

| •••••• | U Functions as described for individual instruction, or not used |                                                              |                                                         |              |     |      |                                |               |  |  |  |

|        | R                                                                | OF                                                           | perar                                                   | nd l         | sou | rce. | R = 0, 1,, 7: use one of the e | eigh <b>t</b> |  |  |  |

|        |                                                                  | da                                                           | data registers A, B,, H directly.                       |              |     |      |                                |               |  |  |  |

|        | I                                                                | OF                                                           | Operand 2 indirect bit. I = 0: direct. I = 1: indirect. |              |     |      |                                |               |  |  |  |

|        | x                                                                | х                                                            | = 0:                                                    | No indexing. |     |      |                                |               |  |  |  |

|        |                                                                  | X = 1: Use the right-most bits of $W/C$ as a direct operand. |                                                         |              |     |      |                                |               |  |  |  |

|        |                                                                  | X = 2, 3: Use 16-bit index registers A, C and B, D.          |                                                         |              |     |      |                                |               |  |  |  |

|        | X = 4-7: Use 8-bit index registers E, F, G, H.                   |                                                              |                                                         |              |     |      |                                |               |  |  |  |

|        |                                                                  |                                                              |                                                         |              |     |      |                                |               |  |  |  |

W/C Operand 2 source. Obtain operand 2 from core memory word location W and character position C, indexed as specified by X.

Note: Operand 2 is usually referred to as "the specified character in memory."

#### 1. Character Transfer

The following instructions permit single characters of data to be transferred between the specified data register and the specified character position in core memory.

BBR Bring to R

Bring the specified character in memory to register R. Timing: 2 IF  $X \neq 1$ , 1 IF X = 1

BRM Bring to R through Mask

Bring the specified character in memory to register R through the mask in Register E. Zeros in E inhibit

#### CODING OF THE X FIELD

CODING OF THE R FIELD

í

Figure 4-1. Register Selection

information transfer to the corresponding bits of R. Timing: 2 IF X  $\neq$  1, 1 IF X = 1

STR Store R

Store the character in register R into the specified memory location.

Timing: 2

STM Store R through Mask

Store the character in register R into the specified memory location through the mask in register E. Zeroes in E inhibit change in the corresponding bits of the memory location.

Timing: 2

#### 2. Multiple-Character Transfer

- The following instructions permit the simultaneous transfer of multiple-character groups between certain data registers. They are useful for rapidly loading or unloading a group of registers. The R field of these commands is utilized as an extension of the Op Code.

- BRL Bring to Low Registers

Bring fields Cl, C2, C3 and C4 of the specified word in memory to the low registers A, B, C and D respectively. Timing: 2

BRH Bring to High Registers

Bring fields Cl, C2, C3 and C4 of the specified word in memory to the high registers, E, F, G and H respectively. Timing: 2

STL Store Low Registers

Store the characters in the low registers A, B, C and D into the specified word in memory in fields Cl, C2, C3 and C4 respectively. Timing: 2

4-4

STH Store High Registers

Store the characters in the high registers E, F, G and H into the specified word in memory in fields Cl, C2, C3 and C4 respectively. Timing: 2

BXA Bring the right-most 16 bits of the specified word in memory to the data register pair A, C designated as index register 2.

Timing: 2 IF  $X \neq 1$ , 1 IF X = 1

- BXB Bring the right-most 16 bits of the specified word in memory to the data register pair B, D designated as index register 3. Timing: 2 IF X  $\neq$  1, 1 IF X = 1

- <u>SXA</u> Store the data register pair A, C designated as index register 2 in the right-most portion of the specified word in memory. Timing: 2

- SXB Store the data register pair B, D designated as index register 3 in the right-most portion of the specified word in memory. Timing: 2

#### 3. Character Arithmetic and Compare

These instructions will perform unsigned arithmetic operations on a single 8-bit field, or will compare the contents of one of the data registers with a specified character in core memory. All characters are considered to be magnitudes, and subtraction underflow will yield a difference in complement form.

ADD Add

Add the specified character in memory to register R and put the result in register R. Overflow sets the overflow memo.

Timing:  $2 \text{ IF } X \neq 1$ , 1 IF X = 1

#### SUB Subtract

Subtract the character in memory from register R and put the result in register R. Underflow sets the over-flow memo.

Timing:  $2 \text{ IF } X \neq 1$ , 1 IF X = 1

CCM Compare Character to Memory

The character in register R is compared to the specified character in memory. If the register contents are greater than memory, the next sequential instruction is executed. If the two characters are equal, one instruction is skipped. If the register contents are less, two instructions will be skipped.

Timing: 2 IF  $X \neq 1$ , 1 IF X = 1 (add one if skip occurs)

4. Logical

The L-1192 logical operations enable setting and testing any combination of bits held in any of the data registers.

EOR Exclusive Or

Replace the specified character in memory with its bitby-bit exclusive-or with the contents of register R. Timing: 2

SCH Set Character

Set all selected bits of register R to one (U = 1) or zero (U = 0). Selected bits are those which are masked by corresponding ones in W. (I is not used.) Timing: 1

TSC Test Character

Test all selected bits of register R for values of one (U = 1) or zero (U = 0). Selected bits are those which are masked by corresponding ones in W. A skip occurs if (1) I = 1 and all selected bits match U, or if (2) I = 0 and a mismatch exists.

Timing: 1 (add one if skip occurs)

TSP Test Parity

Test all selected bits of register R for parity. Selected bits are those which are masked by corresponding ones in W. A skip occurs if (1) I = 1 and parity is odd, or (2) I = 0 and parity is even. (U is not used.) Timing: 1 (add 1 if skip occurs)

5. Shift

Single characters may be shifted within any of the data registers. Shifting may be open or cyclic as specified. The number of places shifted may be modified by an index register. The shift count (N) is contained in the right-most bits of the instruction. A maximum of 8 shifts will be made.

#### SCL Shift Character Left

The contents on register R are shifted left the number of places specified by N. Bits shifted past the high order end of the register are lost, and zeros replace those shifted away from the low order positions. Timing:  $(N \div 4) + 1$

RCL Rotate Character Left

The contents of register R are shifted left the number of places specified by N in a cyclic manner. Bits leaving the high order end of the register are shifted into the low order end.

Timing:  $(N \div 4) + 1$

6. Index Modify

#### DXR

Decrement Index Register

The contents of the instruction R field  $(U = \emptyset)$ , or the contents of the register specified by the R field is

subtracted from the index register as specified by X. If  $I = \emptyset$ , the next sequential instruction will always be executed. If I = 1, the result of the decrement will be tested. If the decrement did not cause the index register contents to pass through zero, the next instruction is taken from the location specified by W. If the index register did pass through zero, the next sequential instruction is executed. Timing: 1

IXR Increment Index Register

The contents of the R field or the register specified by R, according to the setting of U, is added to the index register specified by X. If  $I = \emptyset$ , the next sequential will be executed. If I = 1, the results of the increment will be compared to W/C of the instruction. If the index is greater, or if it overflowed as a result of the increment, the next sequential instruction will be executed. Otherwise one instruction will be skipped. Timing: 1

## 4.2 VARIABLE FIELD OPERATIONS

These instructions facilitate the processing of variable length character fields as required, for example, by message formatting and editing. This capability is important in those applications providing message switching on a mix of both synchronous and asynchronous communication channels. It is also useful in formatting messages for magnetic tape, disc file, and/or display equipment.

Variable field instruction execution permits each of two operand addresses to specify independent field locations and lengths, up to a maximum of 16 characters. The addresses of both operands are subject to normal modification through indexing and indirect addressing. A separate register, designated the Field Operand Address Register (FOAR), is provided to hold the address and length of the first operand. The timing for the execution of most field instructions is a function of the number of characters in each operand field ( $F_1$  and  $F_2$ ), and to some extent the locations of word boundaries within these fields. If a recomplement cycle is required, additional time is required.

Variable field arithmetic operations may be performed on both binary and decimal operands. The sign of each operand is carried in the least significant character field. These arithmetic operations are algebraic and are executed in the following manner:

#### Decimal:

The four least significant bits of each character field contain the decimal digit. Bit 6 of the least significant character of each operand field contains the sign. The remaining bits will be ignored. The address and field length of operand 1 is in the Field Operand Address Register. Operand 1 is added to or subtracted from operand 2, whose length and address is carried in the instruction word. The result of the operation is stored in place of operand 2. The result of the operation is in true sign and magnitude form. If the result passes through zero, the ten's complement (recomplementing) of the result is taken. To yield meaningful results, in the event the operand lengths are not the same, operand 2 must have the greater length.

#### Binary:

The least significant bit of the least significant character of each operand is considered to be the operand sign. Processing is similar to that described for decimal operands above, and operand 2 must always have the greater length.

The instruction format for variable-field operations is similar to that described for the standard single character commands. U and R in the instruction word, however, specify a field length of up to 16 characters. The following instructions comprise the list of variable field operations. Timing is given in memory cycles.

## IFO Initialize Field Operation

This instruction sets up the Field Operand Address Register (FOAR). U and R are transferred directly to the FOAR. The W/C field remains in the instruction register until the specified address modification has been completed, at which time W/C is transferred to the FOAR. Except for the special case of the Compare Fields Equal instruction described below, the FOAR must be initialized each time before another variable field operation is performed. Timing: 1

## SFA Store Field Address

The contents of the FOAR are stored in U, R, and W/C of the specified memory location. The R field of the instruction is a part of the operation code. Timing: 2

### AFB Add Field Binary

The two binary operands whose addresses are specified by the FOAR (operand 1) and W/C of the instruction (operand 2) are added algebraically. The results of the addition occupies the position of the second operand. The result will carry true sign and magnitude. Overflow will set the overflow memo.

Timing: (a) No recomplement cycle:  $3.25 + .75 F_2$ (b) Recomplement cycle:  $4 + F_2$

## SFB Subtract Field Binary

The two binary operands whose addresses are specified by FOAR (operand 1) and W/C of the instruction (operand 2) are subtracted algebraically. The results of the subtraction occupies the position of the second operand. The result will carry true sign and magnitude. Underflow will cause the overflow memo to be set.

Timing: (a) No recomplement cycle:  $3.25 + .75 F_2$

(b) Recomplement cycle:  $4 + F_2$

## AFD Add Field Decimal

The two decimal operands whose addresses are specified by FOAR and W/C of the instruction are added algebraically. The sum is stored in the location of the second operand, and carries true sign and magnitude. Overflow will set the over-flow memo.

Timing: (a) No recomplement cycle: 3.25 + .75 F<sub>2</sub>

(b) Recomplement cycle: 4 + F<sub>2</sub>

### SFD Subtract Field Decimal

The two decimal operands whose addresses are specified by FOAR and W/C of the instruction are subtracted algebraically. The difference in stored in the location of the second operand, and carries true sign and magnitude. Underflow will set the overflow memo.

Timing: (a) No recomplement cycle:  $3.25 + .75 F_2$

- (b) Recomplement cycle:  $4 + F_2$

- CFE Compare Fields Equal

This instruction compares the two fields whose addresses are specified by FOAR and W/C of the instruction. The field lengths are assumed to be identical and the length count in FOAR will be ignored. Comparison is on a bit-bybit basis. Equal comparison causes the next sequential instruction to be executed. Unequal comparison will cause one instruction to be skipped. Since FOAR need not be initialized before each execution of CFE, automatic indexing through a table of contiguous entries may be achieved without the use of index registers.

Timing: (a) No skip:  $2.5 + 5 F_2$

(b) Skip:  $3.5 + .5 F_2$

## CFM Compare Field Magnitudes

The operands whose addresses are specified by FOAR and W/C of the instruction are compared arithmetically with

signs treated as part of the magnitude. If the operand addressed by FOAR is greater than or equal to the operand specified by W/C of the instruction, the next sequential instruction will be executed. If not, one instruction will be skipped. The two operands used with CFM need not have identical lengths.

Timing: (a) No skip:  $2.5 + .5 F_2$ (b) Skip:  $3.5 + .5 F_2$

MFM Move Field in Memory

The field whose address is specified by FOAR is moved to the address specified by W/C of the instruction starting in lower memory. Reaching the end of the shorter field will terminate the operation.

Timing:  $2.5 + .5 (F_1, F_2) min$ .

4.3 FULL WORD OPERATIONS

ţ

The word instructions provide full-word (32 bit) transfer, arithmetic, and logical operations.

The format for most of these instructions is as follows:

|    | 6    | 1 | 3 | 1 | 3 | 16 | 2 |

|----|------|---|---|---|---|----|---|

| OF | CODE | U |   | I | x | W  |   |

The eight character registers A, B, ...., H are not modified by word arithmetic. Fields I, X and W are still employed to specify the location of the second operand. Load and Store word instructions use the one-bit U field to specify one of two one-word registers, R and Q. A third but non-addressable register also participates in word operations. Word operands are 32 bit numbers, with negative numbers represented in 2's complement form. The timing for the following word instructions is given in memory cycles.

#### WAD Word Add

Add the specified word in memory to R and put the result in memory. Overflow sets the overflow memo. Q is unchanged.

Timing: 2

WSB Word Subtract

Subtract the specified word in memory from R and put the result in memory. Underflow sets the overflow memo. Q is unchanged.

Timing: 2

## WMP Word Multiply

Multiply the specified word in memory by R, and put the most significant half of the product in R and the least significant half of the product in Q. The sign of the least significant half is made the same as that of the most significant half.

Timing: 6.25

WDV Word Divide

Divide the specified word in memory into R & Q and put the quotient in Q. The remainder is placed in R in twos complement form.

Timing: 10.5

WCM Word Compare

The word in R is compared to the specified word in memory. If the register contents are algebraically greater than the word in memory the next sequential instruction is executed. If the two words are equal, one instruction is skipped. If the register contents are less than the word in memory, two instructions are skipped.

Timing: (a) No skip: 2

(b) Skip: 3

### WBR Word Bring

Bring the specified word in memory to register R ( $U = \emptyset$ ) or register Q (U = 1). Timing: 2

WST Word Store

Store the word in register R  $(U = \emptyset)$  or register Q (U = 1) into the specified memory location. Timing: 2

WCD Word Complement

Two's complement the contents of the R register. Timing: 1

WSF Word Shift

Shift the word in register R ( $U = \emptyset$ ) or register Q (U = 1) right (I =  $\emptyset$ ) or left (I = 1), the number of places specified by the rightmost five bits of the instruction. Signs are not included, overflow digits are discarded. Indexing of the number of places shifted may be modified by indexing. Timing: 1.5 + .25N

WSL Word Shift Long

Shift the combined words in register R and Q right  $(I = \emptyset)$ or left (I = 1), the number of places specified by the rightmost six bits of the instruction. Signs are not included, overflow digits are discarded. The number of places shifted may be modified by indexing. Timing: 1.5 + .25N

## 4.4 PROGRAM CONTROL OPERATIONS

NOP No-Operation

Proceed with next instruction. (Op code field used only.) Timing: 1

#### JMP Jump

Take the next instruction from memory location W as modified by X and I. (R and U are not used.) Timing: 1

JSL Jump and Store Location

The location of this instruction plus one are stored in the memory location specified by W. The next instruction is taken from location W + 1. Only the word address in location W is affected. Remaining positions are left unchanged. Timing: 2

HLT Halt

Execution of this instruction halts the computer program by removing the RUN condition. Depressing the PROGRAM START pushbutton on the operators console restarts the program with the instruction specified by the program counter. (Op code field used only.) Timing: 1

## 4.5 INTERNAL CONDITION OPERATIONS

The L-1192 has a number of internal condition indicators, which may be tested and modified.

#### Interrupts

The interrupts are enabled through the use of a mask, which may be stored anywhere in core memory. The bits within this mask correspond to the various interrupt conditions. By enabling interrupts from this mask, only the desired interrupts may be used.

ESI Enable System Interrupts

The word at location W is used as a mask to enable interrupt operation for the I/O Interface specified by R, U. For every position which contains a one, the corresponding interrupt will be enabled. For every position which contains a zero, the corresponding interrupt will be disabled. Timing: 2

### System Conditions

÷

System conditions may be set or reset, and tested for on or off condition. The available instructions utilize the W/C field to select the memo or condition to be set or tested. This memo or condition is therefore subject to index register modification.

SSC Set System Condition

For those conditions which can be switched by program, this instruction will cause the state of the addressed device to be equal to the status of the U bit. Thus, if the U bit is zero, the device will be reset. If U is one, the device will be set. If this instruction is addressed to a device which is not program settable, it will execute as NOP. Timing: 1

TCC Test Control Condition

The condition of the specified memo or switch is compared to the U bit. If the condition and the bit are equal, the next sequential instruction will be executed. If not equal, one instruction will be skipped. Timing: 1

#### 4.6 COMMUNICATION INTERFACE OPERATIONS

Input-output character transfers for the communication channels and the slow-speed on line devices (paper tape, punched card, and typewriter/ printer) provide interlaced core memory access to permit simultaneous operation.

Due to frequency of servicing the DDL interface, instructions are provided which greatly reduce the processing load when removing data from the low and high priority channel activity tables (CAT 1, CAT 2). In a single instruction are combined the functions of testing for the presence of data in CAT 1 or CAT 2, bringing the next entry to be processed to the data registers if data is waiting to be processed, and moving hardware bookkeeping markers to the next entry to be processed.

When either ICH or ICL is executed, the relative positions of the load and unload markers are tested. If the same, indicating the tested table is empty, the instruction terminates and the next sequential instruction is executed. If the markers are not the same, the entry at the location of the unload marker (Ul, U2) is brought into the data registers as shown:

| Character        | E Register |

|------------------|------------|

| Channel Identity | F Register |

| I/O Indicator    | G Register |

The unload marker is then stepped cyclicly to the next entry position in the table. The next sequential instruction is skipped and this instruction is terminated.

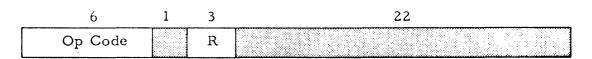

The format for the ICH and the ICL instructions is:

| 6     |                                                      | 24                                                              |  |  |  |  |  |

|-------|------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|

| Op Co | ode                                                  |                                                                 |  |  |  |  |  |

| ICH   | Initiate High Priority Chara                         | acter Cycle                                                     |  |  |  |  |  |

|       |                                                      | l and Ul are tested. If equal, ninates and the next instruction |  |  |  |  |  |

|       | in sequence is executed. If                          | not identical, the next entry                                   |  |  |  |  |  |

|       | in CAT 1 is obtained from t                          | the location specified by Ul.                                   |  |  |  |  |  |

| ĩ     | The next sequential instruction is skipped and Ul is |                                                                 |  |  |  |  |  |

| ţ     | automatically stepped.                               |                                                                 |  |  |  |  |  |

|       | Timing: 1 IF L1 = U1, 2 II                           | F L1 ≠ U1                                                       |  |  |  |  |  |

| ICL   | Initiate Low Priority Chara                          | cter Cycle                                                      |  |  |  |  |  |

|       | The relative positions of L                          | 2 and U2 are tested. If equal,                                  |  |  |  |  |  |

|       | the current instruction terr                         | ninates and the next sequential                                 |  |  |  |  |  |

|       | instruction is executed. If                          | unequal, the next entry is                                      |  |  |  |  |  |

accessed from CAT 2 at the location specified by U2. U2 is stepped, the following instruction is skipped, and the current instruction is terminated. Timing: 1 IF L2 = U2, 2 IF L2  $\neq$  U2

The ECH and the DCH instructions control the operation of the DDL interface module scanner. The instruction format is:

ECH Enable Channel

The interface module attached to scanner position R (one of eight positions) is placed in operation. Characters will be automatically input or output under control of the Line Unit Interface module or Low Speed I/O device. Timing: 1

#### DCH Disable Channel

The interface module attached to scanner position R (one of eight positions) is taken out of operation. Any fragment of a character in transmission will be lost. Timing: 1

#### 4.7 INPUT/OUTPUT OPERATIONS

The L-1192 Controller Processor may interface with up to sixteen I/O Channels. Each channel added to the system contains the required control logic plus a Command Register and a Block Control Register, and can communicate with up to 16 peripheral devices.

For the purpose of the following discussion, the term "instruction" refers to those operations which are decoded and executed in the instruction register. The term "command" designates those operations which are executed in the I/O interface. To activate most input/output operations, it is necessary for the L-1192 program to initiate an IIO instruction, which selects one of sixteen interface channels and specifies the location of a Command Word. If the designated interface is busy, the Program Counter moves to the next instruction in sequence following the IIO. If the interface is not busy, the Command Word and a following Block Control Word are transferred to the selected I/O Interface. The Command Word, which specifies one of several available I/O commands and selects an I/O device, is transferred to the interface Command Register. The Command Word in core memory must be followed by a Block Control Word. It specifies the data transfer starting memory address and the required character count, which are loaded into the interface Block Control Register. Input/output operation then proceeds and overlaps computer instruction access and execution. The Program Counter returns the internal program to the address of the IIO instruction plus 2. A flag is set when the I/O transfer is completed, which will provide a program interrupt unless the indicator is masked.

A single interface transfer can proceed at one time on any I/O Channel. Multiple and simultaneous input-output operations therefore require more than one channel.

The parameters contained in the interface registers may be accessed by means of a Save I/O Register instruction. A Halt I/O instruction also permits the program to immediately terminate any I/O transfer operation when required. These two instructions need not be preceded or activated by an IIO instruction.

The following paragraphs provide a description and present the formats for the I/O instructions and commands.

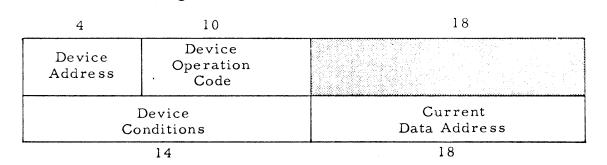

IIO Initiate I/O Operation

| 6       | 4    | 1 | 3 | 16 | 2 |

|---------|------|---|---|----|---|

| Op Code | U, R | I | x | W  |   |

U, R These

These 4 bits select one of 16 Interfaces (I/O Channels) to be placed in operation, unless already busy.

I Indirect Bit

X Index specification. X = 1 has no meaning

W This address, modified by I and X specifies the core memory location of the Command Word.

Command Word Format

0

|         | 2 | 4  | 10 | 16 |

|---------|---|----|----|----|

| <b></b> |   | DS | 0  |    |

DS Device Selection. This field specifies one of sixteen devices on the selected interface.

Device Operation Code. This field specifies the input/output command to be executed. The translation between the device operation code and the actual device function controls will be largely done by the device adapter.

#### Block Control Word Format

| 2 | 12           | 18                 |

|---|--------------|--------------------|

|   | Block Length | Starting Address · |

1. Starting address can be any character position in memory.

2. Block length can be as great as 4096 characters.

SIO Save I/O Registers

Two words, as described below, are transferred from the interface specified by R, U to core memory at the location specified by W/C. Timing: 3

### HIO

# Halt I/O Operation

The execution of this instruction will cause the interface specified by R, U to terminate operations immediately. The contents of the interface Block Control Register and the interface Command Register will be destroyed by this instruction.

Timing: 1

### Section 5

## PERIPHERAL EQUIPMENT

The L-1192 Controller Processor system has available a wide range of peripheral input - output equipment. Devices such as the Line Unit Console and the Card/Printer Input/Output Stations connect to the Communication Interface. The Magnetic Tape, Card Reader/Punch, Line Printer and Disc File Consoles normally attach to an I/O Interface Channel.

## 5.1 LINE UNIT CONSOLE

The L-1192 Controller Processor Console, by the addition of line interface modules, may interface with up to eight simplex communication lines. The optional Line Unit Console provides the circuits for expanding this interface to as many as 64 duplex communication lines. Each group of eight input and eight output line interfaces are packaged into a Line Group Module, and up to eight such Line Groups may be contained in a Line Unit Console. A Line Group module provides its own power supplies and line interface module scanner, and is plug-in rack mounted. This method of packaging increases system performance by insuring that a power supply failure will affect a limited number of communication lines.

A Line Group may contain up to eight input and eight output interface modules, each providing up to one character of input or output buffering for a communication line. There are four types of interface modules available for use in a Line Unit Console: to receive data on a synchronous line; to transmit data on a synchronous line; to receive data on an asynchronous line; and to transmit data on an aynchronous line.

A simplex communication line will require either an input (receive) or an output (transmit) interface module, while a half-duplex or full-duplex line utilizes an input-output pair within a Line Group. The synchronous line interface modules provide the character framing for the high speed lines, and will operate at up to 4800 bits per second. The asynchronous interface for slower speed lines accumulates standard TTY or other required

codes, and will operate on up to 150 bits per second. The line interface modules transmit the input data or the output request to the Controller-Processor, along with the line interface identification number. A slow speed asynchronous channel position in the Line Unit can be converted to a high speed synchronous line terminal by simply replacing the interface plug-in module.

The number and type of interface modules actually provided with the Line Unit Console is dependent on the number of simplex, half-duplex, and fullduplex operational lines and the number of spare units required by the communication system.

## 5.2 MODEL 2250 SYSTEMATICS CARD/PRINTER INPUT/OUTPUT STATION

The 2250 Input/Output Station provides communication to and from the computer through the media of punched cards, page copy, and keyboard entries. The station consists of a page printer, an alphanumeric keyboard, a card read/punch, and a control module. Connections between the computer and the station I/O devices are controlled by switches on the control module. Indicator lights show the status of each device -- on or off -- and in some cases, whether the device is conditioned for input or output.

### 5.2.1 Operating Modes

By setting switches on the control module, the operator conditions the 2250 in any of the following nine operating modes:

| Device Function                  |   | Station Operating Mode |   |   |   |   |   |   |   |

|----------------------------------|---|------------------------|---|---|---|---|---|---|---|

|                                  | 1 | 2                      | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| Read Cards                       | X | X                      | X |   |   |   |   |   |   |

| Accept Keyboard Entries          |   |                        |   | X | X | X |   |   |   |

| Present Input Data to Computer   | X |                        | X |   |   | X |   |   |   |

| Accept Output Data from Computer |   |                        |   |   |   |   | X | X | Х |

| Punch Cards                      |   |                        |   |   | X |   |   | X | X |

| Print                            |   | X                      | X | X | X | X | Х |   | Х |

Keyboard and printer communication with the computer is bi-directional when the card read and punch functions are switched off. The console operator may then make keyboard entries to the computer and receive printed replies without changing the setting of the mode switches. The 2250 exchanges data with the computer in bit-parallel character serial.

The control module transfers data to and from the computer and among the station devices on a character-for-character basis. Every character accepted as computer output is reproduced by all active station devices. Every character read from card or entered on the keyboard is transferred to all active station devices, and to the computer if it has also been selected. Other than making necessary code conversions, the station does not edit or modify data presented to it.

### 5.2.2 Operating Speed

The station will operate at up to 40 characters per second, input and output, when the card read and punch functions are inactive. When either card function is active, maximum speed of all station devices is 20 characters per second.

The station cannot accept output from the computer during the brief intervals when the print hammer is returning to the left margin or when the card unit is going through a feed cycle. During these intervals the station control module will present a busy signal to the computer.

## 5.2.3 Station Devices

1. Printer

Type:

40 character per second serial input. Printing is produced by striking a print hammer against ribbon, paper, and a rotating type drum, in that order.

80 characters @ 10 character per inch.

Line Length:

| Paper Handling:            | Friction feed, fanfold or continuous<br>roll paper. The machine produces<br>an original and three tissue copies.                        |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Printable Characters:      | Letters A through Z<br><u>Digits</u> 0 through 9<br><u>Space</u> (blank)<br><u>Special Characters</u> -<br>\$ ! " - ' ? ; : & , . / ( ) |

| Type Style:                | Murray (standard teletypewriter<br>type face); capital letters only;<br>black printing only.                                            |

| Line Feed/Carriage Return: | The print hammer is returned to<br>the left margin by a Carriage<br>Return code; the paper is spaced<br>to the next line by a Line Feed |

code. Both codes must be keyed by the operator or presented by the computer to terminate each line of printing.

## 2. Alpha Numeric Keyboard

The keyboard is mounted on the front of the printer, but is not mechanically linked to the printer. Depressing a typing key produces a parallel-wire electrical output which is then routed to the printer, other active station devices, and the computer. The keyboard is locked when the printer is not selected or when the computer or card punch shows a busy signal.

Keys are provided for all printing codes and for the Line Feed and Carriage Return functions.

## 3. Card Read/Punch

The 2250 uses a standard IBM 24 Card Punch for card input and output. The unit operates as a punch or as a reader but not both simultaneously. When the card punch is not selected for

either reading or punching, it may be operated off-line for manual keypunching.

The card unit reads and punches 20 characters per second. Pre-determined card columns or groups of columns may be skipped at 80 characters per second. A card feed cycle requires one quarter of a second.

The card feed hopper and the card stacker each hold approximately 500 cards. If the machine runs out of cards when in punch mode, a busy signal is presented to all other active devices and to the computer. An alarm is also displayed on the 2250 control panel.

### 4. Control Module

The 2250 control module provides a common interface for the computer, printer, and card punch. Codes are translated as required. Compatibility of signal levels and duration is established. Data transfer among station devices and to or from the computer is enabled or inhibited as directed by switch settings on the 2250 control panel.

When the 2250 is in card read mode and the printer is enabled, a Carriage Return/Line Feed sequence is automatically generated by the control module after column 80 of each card has been read.

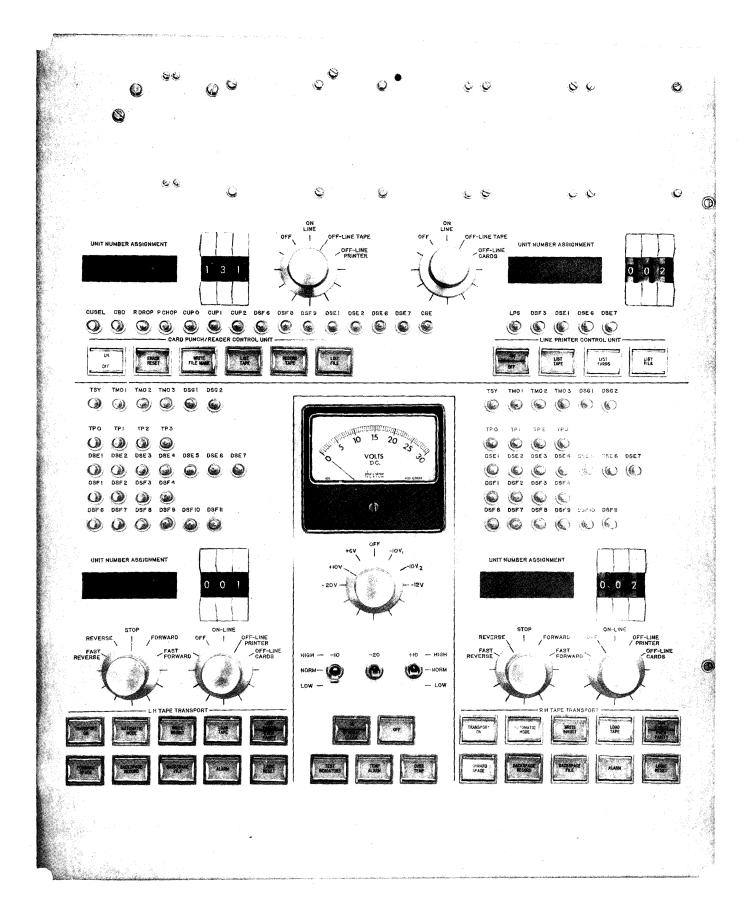

### 5.3 MAGNETIC TAPE CONSOLE

The Magnetic Tape Console contains two tape transports plus the necessary logic control and data circuits. Data is recorded at a density of 556 characters to the inch, operating at the rate of 90 inches per second. Records are separated by 3/4 inch inter-record gaps.

The end of file indication is a 3 inch gap followed by an end of file character. The 3/4 inch inter-record gap follows the end of file character. Tape can be read and recorded with either odd or even parity. Maximum tape start plus stop time is 7 milliseconds; minimum is 5 milliseconds. The unit is bi-directionally compatible with the IBM 729-IV transport.

Some degree of simultaneous operation is provided for any one I/O Interface Channel. A data transfer operation can be in process on one Tape Transport, overlapping non-data transfer operations on other Tape Transports; i.e., Rewind, Backspace Record, Backspace File, Skip Record, Skip File, Write File Mark. The use of more than one I/O channel and Tape Consoles also permits simultaneous I/O data transfers. Tape may be moved forward or backward; however, operations requiring data transfer can take place only while tape is moving forward. Forward is from left to right, over a split head. This split head has a write station and a read station. During recording the read station checks the parity of each character 3 milliseconds after it has been recorded.

After the tape start time of 3.5 milliseconds has passed, data is transferred at the rate of 50,000 characters per second. Maximum tape stop time is 3.5 milliseconds also. Tape normally moves at the rate of 90 inches per second. There are two rewind speeds: a hi-speed 270 inches per second, and a low-speed of 90 inches per second.

## 5.3.1 Tape Transport On-Line Read

On-line read operation may be under "normal input" or "controlled input," as specified in the Device Operation Code in the I/O Command Word. In either case, data is read character-serial into the selected I/O Interface Data Register. When a full word has been assembled, it is transmitted through the memory access register (M) into core memory. This transfer is under control of the Block Control Register, which specifies the starting memory address and is automatically incremented for each core access.

The "normal input" mode does not utilize a character count, and the input transfer continues until an inter-record gap is reached. The "controlled input" mode is monitored by the character count in the Block Control Register, which is decremented for each input character. The transfer halts when the count equals zero.

Figure 5-1. Magnetic Tape Console Control Panel

Vertical parity is checked as the tape is read into the tape console control section. At the end of each record, the horizontal check character is checked. The interface remains busy throughout the operation. When the operation is completed, the interface provide an interface not busy interrupts.

## 5.3.2 Tape Transport On-Line Write

The data to be written is transferred word parallel from core memory to the I/O Interface, and then is transferred character serial to the magnetic tape console for transfer onto tape. The Block Control Word specifies the starting memory location and the required character count, and the write operation continues until the count is zero. As soon as the last character is received by the magnetic tape console, the interface requests an interface not busy interrupt.