# FAST manual

GRI-909

FAST MANUAL

GRI Computer Corporation, 320 Needham Street, Newton, Massachusetts 02164

© November 1970 by the GRI Computer Corporation

## TABLE OF CONTENTS

| 1     | THE FAST ASSEMBLER                                       |

|-------|----------------------------------------------------------|

| 1.1   | Introduction                                             |

| 2     | FAST LANGUAGE ELEMENTS                                   |

| 2.1   | Character Set                                            |

| 2.2   | Symbols                                                  |

| 2.3   | Key Words                                                |

| 2.4   | Labels                                                   |

| 2.5   | Constants                                                |

| 2.6   | Expressions                                              |

| 2.7   | Comments                                                 |

| 2.8   | Statements                                               |

| 3     | MACHINE INSTRUCTIONS                                     |

| 3.1   | Register-to-Register Data Transmission Instructions. 3-3 |

| 3.2   | Memory Reference Data Transmission Instructions 3-11     |

| 3.2.1 | Direct Addressing Mode                                   |

| 3.2.2 | Deferred Addressing Mode                                 |

| 3.2.3 | Immediate Mode Addressing                                |

| 3.2.4 | Immediate-Deferred Addressing Mode                       |

| 3.3   | Data Testing Instructions                                |

| 3.4   | Function Output Instructions                             |

| 3.5   | Sense Function Instructions                              |

| 4     | ASSEMBLER INSTRUCTIONS                                   |

| 4 1   | Danamatan Dafdadadaa                                     |

| 4.2        | Radix Control                        |

|------------|--------------------------------------|

| 4.3        | Location Counter                     |

| 4.4        | Program Terminators                  |

| 4.5        | Data Definition                      |

| 4.5.1      | Word Values                          |

| 4.5.2      | Text                                 |

| 4.5.3      | Combined Text and Word Values 4-8    |

| 5          | DEFINITION OF NEW SYSTEM SYMBOLS     |

| 5.1        | Device and Device Related Codes 5-2  |

| 5.2        | Abbreviated Machine Instructions 5-6 |

| 5.3        | Local Pseudo-Instructions 5-8        |

| 6          | USAGE NOTES                          |

| 6.1        | System Linkage 6-1                   |

| 6.2        | Subroutine Linkage 6-2               |

| 6.3        | Some Fast Examples 6-5               |

| 6.3.1      | %TBO                                 |

| 6.3.2      | %TBI                                 |

| 6.3.3      | %TLO                                 |

| 6.3.4      | %TLI                                 |

| 6.3.5      | %TMO                                 |

| APPENDICES |                                      |

| A          | OPERATING INSTRUCTIONS               |

| В          | STANDARD SYMBOL TABLE                |

#### CHAPTER ONE

#### THE FAST ASSEMBLER

The FAST acronym stands for Functional Assembly System Technique. It is an aid in the preparation of programs for the GRI-909 computers.

#### 1.1 Introduction:

An assembler is an indispensible aid to the process of preparing programs to run on a computer. All of these programs to be

run on a computer are called object programs. They are often

prepared in a punched paper tape format where the holes or absence

of holes literally represent the 1's and 0's of the machine language

instructions. A program called a loader is then used to load this

object tape into the computer's memory where it can be executed by

the computer.

An assembler literally does what its name implies; it assembles object programs from symbols and expressions that have one for one correspondence to binary portions of an instruction word, or in some cases, have a binary word equivalent. The use of symbolic statements or expressions permits the programmer to relate the problem and its parameters more closely to the language he must write in order to produce an object tape. This simplifies the task of programming without degrading program efficiency. It differs from a compiler language in that each compiler instruction might generate many equivalent machine language instructions, decreasing program efficiency and making it difficult to relate to time based operations.

The assembler, then, is a translator of source material (called the SOURCE PROGRAM) into an OBJECT PROGRAM which can then be loaded into the computer's memory and run. The assembler also provides other useful functions for the programmer. It furnishes a listing which can be used to debug the object program once it is stored in memory. This listing is also used to correlate the object program as it resides in memory to the source program as it was originially prepared. The preparation of source programs is relegated to a program called the SOURCE TEXT EDITOR (%STE), Manual M44-3.

FAST is a functional assembly technique that is very much related to the basic organization of the GRI-909 computer. It is a symbolic assembly language that deals at a high functional level with the components of the system and the computer. It also provides all of the symbolic aids that are normally provided by an assembly language.

The basic organizational concept of the GRI-909 treats all components in a computer system as equal members of a data system that either produce or receive data. Furthermore, the control structure of the GRI-909 permits the basic instruction; move data from Source A to Destination B to be programmed by the user where the source and destination of data are any two system devices. When these system devices are internal parts of a computer, they also perform processing functions on the data they receive. Often these processing functions are independent parallel processing functions that are going on while other devices are in operation. Thus, an arithmetic unit independently performs its function on data received. It makes a result, which is some function of the data received, available to the system for transfer to some other system device or function.

The GRI-909 architecture also provides a bus modifier which permits simple modifications to the data while it is being transmitted from source to destination. These modifications are incrementing the data, shifting and complementing (the latter being performed prior to incrementing or shifting so that combined operations are permissible). Thus, the basic format of the instruction now becomes: SOURCE A (mod) to DESTINATION B.

The functional components of the system are assigned mnemonics, and the user describes the data transfers that take place between these components in concise, highly functional statements such as AX TO TTO. Memory locations may be referenced as symbolic entities in high level statements such as COUNT Pl. Other statements are provided for control purposes in the assembler itself. Statements such as \*END denote the end of a program. Statements like this are directives to the assembler itself and do not generate binary information for the object program.

The assembler interprets each such statement and either generates the appropriate binary object information or performs the implied assembler functions.

The programs are generally prepared on punched paper tape, although other media such as punched cards or magnetic tape may be used.

#### CHAPTER TWO

#### FAST LANGUAGE ELEMENTS

This chapter describes the various elements that are used to form FAST language source program statements. When learning the FAST language, a cursory reading of this chapter will suffice — the details contained herein may be referred to from time to time as the user gains experience with FAST programming. Throughout this manual, the following notational conventions will be employed when presenting general forms of language elements:

- [] Brackets used to contain an optional item. The language element may be written with or without the item -- generally, the meaning of the statement containing that language element is changed when such an item is omitted.

- Braces used to contain alternate items. These items will be arranged vertically within the braces -- the language element must include one, and only one, of the alternate items.

- ... Ellipses used to denote permissible repetition of the immediately preceding language element.

When braces are enclosed within brackets, then either the entire form in brackets is omitted or the form is included with the appropriate alternate item selected. Some examples of this notational usage are:

| Form                                                            | May be Written as |

|-----------------------------------------------------------------|-------------------|

| A [TO] B                                                        | A B               |

| (-)                                                             | A TO B            |

| $A  \left\{ \begin{array}{c} B \\ C \end{array} \right\}  D$    | A B D             |

| Fz. 37                                                          | A C D             |

| $A\left[\left\{\begin{matrix} B\\C \end{matrix}\right]\right]D$ | A D               |

|                                                                 | A B D             |

|                                                                 | A C D             |

| A [,A]                                                          | A                 |

|                                                                 | A,A               |

|                                                                 | A,A,A             |

|                                                                 | etc.              |

| A [B [C]]                                                       | A                 |

|                                                                 | A B               |

|                                                                 | АВС               |

## 2.1 Character Set:

The FAST assembler processes source program statements **com**posed of 8-bit ASCII characters and recognizes two distinct categories of characters: general usage characters and reserved characters.

General usage characters are used to form symbols (2.2) and simple numeric constants (2.5):

| Character    | <u>External</u> | <u>Internal</u> |

|--------------|-----------------|-----------------|

| Alphabetics  | A through Z     | 301 through 332 |

| Numerics     | 0 through 9     | 260 through 271 |

| Dollar Sign  | \$              | 244             |

| Percent Sign | %               | 245             |

| At Sign      | @               | 300             |

Reserved characters are used to impart special meanings to the assembler, to separate or delimit certain language elements, or  $t\circ$  enable error-recovery within source lines:

| Character       | External | Internal |                                                        |

|-----------------|----------|----------|--------------------------------------------------------|

| Colon           | :        | 272      | Delimits a label (2.4)                                 |

| Semi-colon      | ;        | 273      | Delimits a comment (2.7)                               |

| Equals          | =        | 275      | Used to define parameters (4.1)                        |

| Plus            | +        | 253      | Denotes addition in expressions (2.6)                  |

| Minus           | -        | 255      | Denotes subtraction in expressions (2.6)               |

| Comma           | ,        | 254      | Separates data definitions (4.5)                       |

| Ampersand       | &        | 246      | Denotes logical "AND" in expressions (2.6)             |

| Exclamation     | 1        | 241      | Denotes logical "OR" in expressions (2.6)              |

| Asterisk        | *        | 252      | Precedes certain assembler instructions (4.2-4.4)      |

| Period          | •        | 256      | Represents the assembler's LOCATION COUNTER            |

| Quote &         | •        | 247      | Delimits text definition (4.5.1)                       |

| Pound           | #        | 243      | Used to define new system symbols (5)                  |

| Carriage-return | (CR)     | 215      | Delimits source statements (2.8)                       |

| Line-feed       | (LF)     | 212      | Optionally follows CR at end of source statement (2.8) |

| Back-arrow      | -        | 337      | (1)                                                    |

| Rubout          | (RO)     | 377      | (1)                                                    |

| Block-mark      | (BL)     | 375      | (1)                                                    |

| Space           |          | 240      | Used to separate language elements                     |

(1) Back-arrow and rubout are used for error-recovery within a source line. Block-mark serves to delimit a source text block. See section 1.2, "SYSTEM CONVENTIONS" in the GRI-909 Manual M44-3, "SOURCE TEXT EDITOR".

NOTE: Although the FAST assembler recognizes only no-parity 8-bit ASCII characters internally, the characters punched onto a source tape may be 8-bit, even-parity, odd-parity, or no-parity codes since the text input routine logically OR's the high-order bit into each character read.

## 2.2 Symbols:

A FAST language symbol consists of one or more general usage characters (2.1), the first of which must <u>not</u> be numeric. Since only the first five characters are stored in the assembler's symbol table, symbols of greater length must be unique in the first five characters — the assembler ignores all characters in a symbol after the fifth.

The following character strings could validly be used as symbols:

START

LOOP

N23@

PARA11

PARA21

These character strings are invalid as symbols for the reason given:

8ABC First character numeric

GO\* Reserved character, \*

AB LE Embedded blank

PARAM1 Not unique in the first five characters

PARAM2

In FAST, as in any symbolic programming language, a symbol must ultimately represent some numeric value. Many commonly-used symbols are built into the assembler's standard symbol table (APPENDIX C). These, of course, already have numeric values associated with them. Other symbols are defined by the user in his source program — these have values assigned to them during the assembly process. User-defined symbols and their associated values are added to the assembler's symbol table — they reside there only during the assembly of a specific source program. As the assembler translates source statements into their binary or machine language equivalents, it merely replaces each symbol it encounters with its specific numeric value.

It is possible to use a symbol in a source program in such a fashion that the assembler cannot associate a numeric value with it. Symbols being defined by the user must appear in a symbol-defining context at least once in the source program. These symbol-defining contexts are described in detail in sections 2.4, 4.1, and 5 of this manual. If, by the end of the second pass of the assembly, there are still undefined symbols (i.e. symbols with no numeric values assigned), the assembler will flag each statement containing such a symbol with

the error code "U" as it generates the assembly listing.

Pre-defined symbols in the assembler's symbol table have mnemonic value -- for instance, AO represents the arithmetic operator, HSP represents the high speed punch, LTZ represents the data condition of less than zero, and CLIF represents a pulse code to clear an input flag. In order to enhance the overall utility of assembly listings, the user should attempt to compose his symbols with mnemonic value as well.

Symbols in the FAST language are of the following categories:

| Key Words      | (2.3) |

|----------------|-------|

| Labels         | (2.4) |

| Parameters     | (4.1) |

| System Symbols | (5)   |

Key words are pre-defined in the assembler's symbol table. These symbols comprise the framework of specific FAST language statements and enable the assembler to distinguish the various types of machine and assembler instructions.

The standard symbol table does not contain either labels or parameters — these are always defined by the user in his program. A label is prefixed to a FAST statement so that the associated instruction or data item may be referenced symbolically from other points in the same program. A parameter is used to represent constants that may be referred to many times in a program — a constant is often given a symbolic equivalent because it is more meaningful to the user than are octal or decimal numbers.

System symbols represent devices (registers), output pulse codes, status test codes, path codes for the GRI-909 Bus Modifier, data test codes, and pseudo-codes (5). The standard symbol table contains the more commonly used system symbols. Other system symbols may be defined by the user -- when doing so, the user is cautioned not to employ any symbols already in the standard table <u>unless</u> it is his specific intent to alter their standard meaning.

## 2.3 Key Words:

Key words are reserved character strings that have particular meanings to the FAST assembler. No key word may be redefined by the user nor may it be used in a context other than those shown in the general forms of FAST language instructions. Included in the FAST language key words are all the reserved characters — see section 2.1 for a tabulation of these characters and their functions. The other FAST key words are as follows:

| Symbol | <u>Function</u>                                                                                     |

|--------|-----------------------------------------------------------------------------------------------------|

| END    | Program terminator (4.4)                                                                            |

| EOT    | Program terminator (4.4)                                                                            |

| OCT    | Radix Control (4.2)                                                                                 |

| DEC    | Radix Control (4.2)                                                                                 |

| SKIP   | Indicates sense function instruction (3.5)                                                          |

| IF     | Indicates data test instruction (3.3)                                                               |

| то     | Used in data transmission $(3.1, 3.2)$ , data test $(3.3)$ and function output instructions $(3.4)$ |

| GO     | Combined with TO to indicate transfer of program control in data test instructions (3.3)            |

| С      | Indicates taking of one's complement in register-to-register data transmission instructions (3.1)   |

| I      | Indicates immediate addressing mode in memory reference data transmission instructions (3.2)        |

| Symbol Symbol | <u>Function</u>                                                                                       |

|---------------|-------------------------------------------------------------------------------------------------------|

| D             | Indicates deferred addressing mode in memory reference data transmission instructions (3.2)           |

| ID            | Indicates immediate-deferred addressing mode in memory reference data transmission instructions (3.2) |

## 2.4 <u>Labels</u>:

A FAST statement may be labeled or tagged by the use of the form

#### symbol:

(a symbol followed by the reserved character:) as the first element of the statement. The assembler assigns the current value of its LOCATION COUNTER (4.3) to this symbolic label — this will be the memory address of the first word assembled after the label is encountered. If, for instance, a label is prefixed to a statement which assembles as a two-word instruction, the label's value will be the memory address of the first word of the instruction. A label may also be associated with a statement which assembles as data.

A label, then, is a symbolic equivalent of the address of a specific machine instruction or data word in the user's program. The label may be used to symbolically reference the instruction or data word from other points in the same program. Therefore, each label must be unique. An attempt to use the same symbol more than once as a label will be flagged with the error code M (multiply-defined symbol) on the assembly listing.

When the assembler encounters a symbolic label in a context other than the one which defines it (above), the assigned numeric value is substituted for the symbol. Given the labeled statements:

LOOP: AO TO HSP (1-word instruction)

and TABLE: 1,10,100,1000 (4-word table)

then

GO TO LOOP transfers program control to the

instruction at LOOP,

and TABLE TO AX loads the first word of TABLE

(the value 1) into the register AX.

Addresses of machine words near these labeled may be accessed by forming a symbolic relative address in a FAST statement. Such an address expression (2.6) consists of a label plus or minus a constant (2.5). For instance,

GO TO LOOP+1 transfers control to the next instruction after the one at LOOP,

TABLE+2 TO AX loads the third word of TABLE

(the value 100) into the register AX.

These expressions result in addresses of words relative to labeled instructions or data. Note that if the instruction at LOOP were two words long, the expression pointing to the next instruction would be LOOP+2.

## 2.5 Constants:

and

A simple constant is represented by one or more successive numeric characters. The assembler converts the character string into its equivalent binary value — the digits are interpreted according to the setting of the assembler's RADIX (4.2). The user may write constants as either octal or decimal numbers provided he has specified the appropriate radix. The range of a constant, so as not to arithmetically overflow out of the fifteen magnitude bits of a signed machine word, is:

0 to +32767 decimal

or

0 to +77777 octal

A constant may be preceded with a minus sign (e.g. -20) and the assembler will form the two's complement value of the number (e.g. 177760). If the assembler's RADIX is set to octal, any single occurrence of the character 8 or 9 in a constant will be flagged with the error code D on the assembly listing and converted to octal. Multiple occurrences of 8 or 9 in a constant will result in an incorrect conversion to octal.

## 2.6 Expressions:

Compound addresses or data values may be formed by combining simple values in FAST language expressions. An expression consists of a numeric operand, or a series or operands separated by arithmetic and/or logical operators. The first operand in an expression may be preceded by a leading sign (arithmetic operator). Any given operand may be one of the following:

Label (2.4)

Parameter (4.1)

Constant (2.5)

represents the current value of the assembler's LOCATION COUNTER.

The permissible operators are:

+ denoting addition

denoting subtraction

& denoting logical AND

denoting logical OR

A general expression, e, is assembled into a 16-bit value. The resultant value may be positive or negative -- addresses, of course,

must be positive and result in a valid machine address. The general form of an expression e is:

$$\begin{bmatrix} \{+\} \\ - \} \end{bmatrix} \qquad \begin{cases} \text{Label} \\ \text{Parameter} \\ \text{Constant} \\ \cdot \end{cases} \qquad \begin{cases} + \\ - \\ \delta \\ ! \end{cases} \qquad \begin{cases} \text{Label} \\ \text{Parameter} \\ \text{Constant} \\ \cdot \end{cases} \qquad \cdots$$

An expression is evaluated by the assembler in a single left-to-right scan: no priorities are assigned to the operators. Some examples are:

#### 2.7 Comments:

Comments are used to augment the source program with documentation meaningful to the user. Such documentation often explains the use of a program or subroutine, describes the functions performed by a sequence of instructions, gives the reasons for various specific steps or statements, etc. A comment may be appended to a FAST statement by prefacing the comment with the reserved character semi-colon (;). Also, an entire statement may consist of only such a comment. When the assembler encounters the semi-colon, it ignores the rest of the statement until it reaches the carriage-return terminator (2.8). Comments are reproduced on the assembly listing — only as much of a comment as will fit on an assembly listing line will be printed,

however. Any printable ASCII character may be included in the body of a comment. Examples are:

;THIS ROUTINE PACKS CHARACTERS

IF AO LTZ GO TO ERR ;LIMIT EXCEEDED?

## 2.8 Statements:

A source program statement (line) is a meaningful arrangement of FAST language elements and is terminated by the reserved character carriage-return, which itself may optionally be followed by a line-feed character. This latter character is ignored by the assembler — it is usually included in a source tape so that it might be listed by an off-line device which requires the line-feed to advance the paper. A FAST statement may contain no more than 80 characters including spaces (blanks). The assembler will ignore all characters beyond the 80th.

The general forms for machine instructions and assembler instructions are presented in chapters 3 through 5 of this manual. Other than the rules given for specific instructions, there are no formatting requirements imposed upon a source statement. The major elements of a free-form source statement are label, instruction and comment — the assembler isolates these elements and arranges them in columns on the assembly listing.

The most basic elements, symbols and constants, must be separated or delimited from each other. Since these basic elements consist solely of general usage characters (2.1), an expression such as

V1+V2&V3!25

is easily understood by the assembler since the basic elements are

separated by reserved characters. Therefore, the rule to be observed when preparing source statements is:

When any two successive basic elements are not separated by a non-blank reserved character, then they must be separated by at least one blank (space).

#### CHAPTER THREE

#### MACHINE INSTRUCTIONS

The bulk of the FAST language statements written by a user assemble into GRI-909 machine instructions. A sequence of machine instructions, and their associated data, constitutes a program to perform a specific task on some GRI-909 machine configuration. All basic machine instructions are described by a single internal format:

| 15  | 10 9 | 6  | 5 0 |

|-----|------|----|-----|

| SDA | М    | OD | DDA |

where

SDA is the source device address,

MOD contains modifier, addressing mode, and function information, and

DDA is the destination device address.

The execution of any machine instruction causes, in effect, the transmission of information in the form of data or control signals from the source device specified by SDA to the destination device specified by DDA. The qualities of the transmission and/or the end result of the instruction is influenced by the specification of MOD. GRI-909 complete machine instructions are either one or two words in length. A machine instruction consists of either 1) a basic instruction in the above format or 2) a basic instruction followed by a word containing a memory address or data for the instruction.

Once an assembled program has been loaded and started, the GRI-909 control logic normally fetches and executes machine instructions from

sequential locations. The computer's sequence counter (SC) contains the memory address of the next instruction to be executed. As one or two-word machine instructions are executed sequentially, the SC is automatically updated by the GRI-909 control logic. During such normal flow of program control, the SC is analagous to the assembler's LOCATION COUNTER (4.3). Some instructions, however, cause this normal program flow to be altered. The sense function or SKIP instruction causes, under certain conditions, a skip over the <a href="next two memory locations">next two memory locations</a>. The data testing or GO TO instruction can cause an absolute jump to some new location. Also, since the SC can be modified by the user, a transmission of data to the SC causes an absolute jump to some new location. In any case, after any one of these instructions alters the program flow, the sequential execution of instructions begins anew.

FAST source program machine instructions are oriented to the functional organization of the GRI-909. The major element of a machine instruction statement, for the most part, corresponds to and is written in the same order as the SDA, MOD, and DDA components of the basic instruction itself. Specific key words (2.3) are used by the assembler to distinguish five major classes of machine instructions. In some cases, the class of instruction implies a standard SDA or DDA (or both), and these are not supplied by the user but are automatically filled in by the assembler.

In most of the FAST language examples in this chapter, the corresponding machine language instruction will be printed to the left of the statement as it would appear on an assembly listing. Comments to the right are intended to amplify the meaning of the example and are not part of the instruction itself.

#### 3.1 Register-to-Register Data Transmission Instructions:

A register is a storage place for data that has been produced by an input device, for data to be accepted by an output device, for data to be operated upon by a firmware device, or for data that is merely to be saved for temporary use. The data register associated with most input devices may only be used as a source of data.

Generally, all other registers in the system may be used as both sources of and destinations for data. In other words, given a GRI firmware device or user-developed device with a data register, the nature of the device determines that the register will be interfaced to the source bus, to the destination bus, or to both.

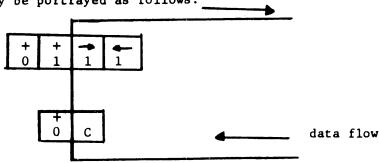

The GRI-909 architecture enables the transmission of data between any two registers in the system. This is accomplished via a direct connection between the source bus and the destination bus. For data transmission there is no distinction between internal registers, firmware device registers, and input/output device registers. In addition, the connection between the source bus and destination bus contains a special device called the Bus Modifier, which enables simple modifications to data during the transmission process. This Bus Modifier may be portrayed as follows:

The modification(s) to data as it passes from one register to another is specified by the MOD portion of the data transmission instruction. If no modification is selected (MOD = 0000), then data passes through the two +0 paths, which results in a direct 16-bit parallel transfer. The FAST key words (2.3) used to specify modifications to data are:

- C one's complement

- Pl plus one (increment)

- R1 shift right one bit

- Ll shift left one bit

If the one's complement is selected, it occurs before other modification, if any. Only one of the upper paths may be specified during a data transmission instruction. There are 2 X 4 or 8 possible paths through the Bus Modifier.

The increment (P1) path has a bus overflow indicator associated with it. When this path is selected, the overflow indicator will be set (true) if, and only if, the source data was equal to -1 (all one's). If such overflow did not occur, then the indicator will be cleared. This indicator, referenced as BOV, may be tested after a data transmission instruction with the appropriate Sense Function instruction (3.5).

The shifting paths (Rl or Ll) have a one-bit LINK register associated with them. Any shift, right or left, is performed circularly through this link (LNK). For instance, during a right shift, the entire word is displaced right one bit, and the low-order bit of the source word goes into the LNK. The previous contents of the LNK

goes into the high-order position of the data word as it is sent to its destination. After any shift the new state of the LNK may be tested with the appropriate Sense Function instruction (3.5). If it is desired to shift a zero (or a one) into the word being transmitted, the LNK is first cleared (or set) with the appropriate Function Output instruction (3.4).

A further feature of the GRI-909 is the bus address 00, referenced as ZERO, which is a source of a zero data word. This special source may be used to clear any data register. ZERO through the Pl path can be used to transmit plus one and ZERO through the complement path yields minus one. ZERO may be used as a destination for data. Then tests of the BOV (or LNK) can be done without affecting the source data itself.

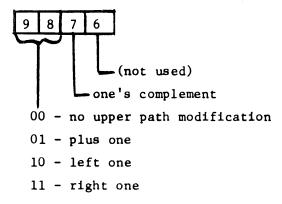

The MOD format for register-to-register data transmission instructions is:

These statements have the general form

If the transmission is between different registers, the source register is left unchanged and the contents of the destination register is replaced by the source data with the selected modifications. If the destination is omitted in this statement, then the operation is upon the contents of the source register — the assembler copies SDA into DDA when constructing the instruction word.

The statement

#### 77 0000 11 TTI TO AX

transmits the teletype input register to the arithmetic operator X-register. To transmit the incremented value of AX to AY, one writes.

### 11 0100 12 AX P1 TO AY

To send the one's complement of the high speed reader input to AX, we write

#### 76 0010 11 C HSR TO AX

The one's complement is formed by merely inverting all the bits in the data word. The two's complement is formed by following the one's complement with an increment. To transmit the two's complement in the above instruction, we would change it to

#### 76 0110 11 C HSR P1 TO AX

Keep in mind that the arithmetic operator assumes that negative numbers are in two's complement notation. Given two general purpose registers, GR1 and GR2, the following code computes their sum and difference and leaves the sum in GR1 and the difference in GR2 (of course, the original contents of GR1 and GR2 will be destroyed)

GR1 TO AX ;lst argument

GR2 TO AY ;2nd argument

ADD ;select add function (3.4)

AO TO GR1 ; store sum

C AY P1 TO AY ;negate 2nd argument

AO TO GR2 ;store difference

The initial values of the arguments need not have been positive — either one or both of them could have been negative (in two's complement notation). Note that to subtract argument 2 from argument 1, we add the two's complement of argument 2. The instruction that negated the data in AY could, of course, have been written

#### C AY P1

Some examples of the use of the special address ZERO are

| 00 0000 11 | ZERO TO AX     | ;CLEAR AX           |

|------------|----------------|---------------------|

| 00 0100 76 | ZERO P1 to HSP | ;PUNCH +1           |

| 00 0110 12 | C ZERO TO AY   | ;AY = -1            |

| 11 1000 00 | AX L1 TO ZERO  | COPY AX SIGN TO LNK |

This last example does not alter the contents of AX, but since the source word is sent through the Bus Modifier shifted left, the sign bit of AX is now also in the LNK.

An arithmetic right shift is often required in computer arithmetic. The arithmetic right shift displaces bits 0-14 each time it is performed and leaves the sign bit the same. Thus, if a word started with a 1 in the sign bit and were continually, arithmetically, shifted right, the word would eventually fill up with 1's from the left hand end.

During an arithmetic right shift, the sign of the argument being shifted is copied into the word as it is shifted right. Since the previous contents of the LNK is always shifted into the bit position vacated, the following two instructions perform an arithmetic right shift on the contents of AY

12 1000 00 AY L1 TO ZERO

12 1100 12 AY R1 ;AY/2

An arithmetic right shift is equivalent to dividing an argument by two. Similarly, a left shift is equivalent to multiplying an argument by two. In order to ensure that a zero is shifted into the low-order bit of the destination word, the LNK should be cleared before the shift. For example, the sequence

CLL ; LNK = 0

AX L1 ; AX\*2

shifts AX left one bit. It is not always necessary to set or clear the LNK before a shift. Sometimes it is only desired to examine a data word bit by bit. Such a data word might represent up to 16 switch settings. A device might be implemented such that each bit in its data register represented a contact setting or switch setting in some portion of the overall system. The GRI-909 console switch register continuously represents the settings of the 16 data switches. Since it is a source of data only, it must be transmitted to some other register before shifting its value. For example

As mentioned before, the LNK may be tested after each shift to see if the bit shifted out of the data word was a zero or a one.

The data is sent back to AX so that after each shift, the next bit to be examined moves to the low-order position.

Sometimes data is packed into a 16-bit machine word. The word may contain two or more pieces of information with one or more bits used to contain each item. For example, sometimes two ASCII characters are packed into a word, 8 bits each. Suppose we wish to isolate the high order three bits of AX by shifting AX left three places and storing the item in the low order bits of AY. We write

AX L1

ZERO L1 TO AY

AX L1

AY L1

AX L1

AY L1

Note that the second instruction in this sequence ensures that the 13 high order positions of AY will be zeros when the unpacking operation is complete.

As a final register-to-register data transmission example, suppose we wish to decrement (subtract one from) the contents of a register, say GR1. We can use the arithmetic operator for this purpose.

GR1 TO AX

C ZERO TO AY

;AY = -1

ADD

;SELECT ADD FUNCTION

AO TO GR1

;STORE RESULT

This code requires four machine words and ties up the arithmetic operator. The third instruction (ADD) could be left out if the AO were already in the required state. A better way to do this in the GRI-909 is:

C GR1 P1

C GR1

To demonstrate this, assume we have an 8-bit register containing the binary equivalent of 5.

00000101

$$(2^0 + 2^2 = 1 + 4 = 5)$$

taking the two's complement, we have

11111010

+ 00000001

11111011

following this with the one's complement, we have

$$00000100 (2^2 = 4)$$

## 3.2 Memory Reference Data Transmission Instructions:

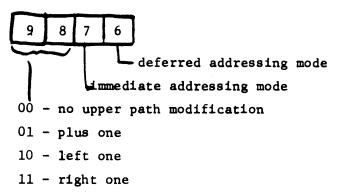

Main memory of the GRI-909 may contain from 1024 to 32,768 (decimal) locations. Any of these 16-bit words may be used as a source or destination in a data transmission instruction. These instructions are two words long — the first word is in the usual SDA MOD DDA format, and the second word is either an address of some other memory location or is data to be operated upon. The overall memory system is accessed whenever the bus address 06 (memory buffer) appears as either the SDA or the DDA (or both) of a machine instruction. The assembler infers memory referencing from the nature of the FAST statement and fills in SDA and/or DDA appropriately. Further information, which specifies the memory address of the particular location involved in the data transmission, is supplied by the combination of MOD and the second word of the instruction. The MOD format for these instructions is:

Note that only the modifications available in the upper portion of the Bus Modifier may be selected during memory reference data transmission -- bit 7 of the instruction word is here used to specify an addressing mode.

Data transmission statements involving main memory are of three types:

1) Register-to-memory - The contents of the hardware (non-memory) register at SDA is transmitted via the upper half of the Bus Modifier to the specified memory location. The assembler sets DDA = 06. This type has the general form:

[symbol:] register

$$\begin{bmatrix} P1 \\ L1 \\ R1 \end{bmatrix}$$

TO [I] [D] e [;comment]

2) Memory-to-register - The contents of the specified memory location is transmitted via the Bus Modifier to the hardware register at DDA. The assembler sets SDA = 06. This type has the general form:

3) Memory-to-self - The contents of the specified memory location is transmitted win the Bus Modifier back to the same memory location. Here, SDA = DDA = 06. This type has the general form:

In the foregoing general forms, e is a general FAST language expression (2.6) whose value assembles into the second word of the instruction. The key words (2.3) I and D are used to select the memory addressing mode.

The address of the particular memory location into which data is transmitted, or from which data is transmitted, is called the effective address. The effective address is determined differently for each of the memory addressing modes. Given the form [I] [D],

any one of the four GRI-909 addressing modes may be selected in a FAST memory reference statement.

| Form | Mod  | <u>Mode</u>                  |

|------|------|------------------------------|

|      | 0000 | Direct (3.2.1)               |

| D    | 0001 | Deferred (3.2.2)             |

| I    | 0010 | Immediate (3.2.3)            |

| ID   | 0011 | Immediate - deferred (3.2.4) |

## 3.2.1 Direct Addressing Mode

The direct mode is implied by the absence of both of the codes I and D in the FAST statement. In the direct addressing mode, the second word of the instruction contains the effective address — the GRI-909 control logic fetches this second word and uses its value to access the location involved in the data transmission. The statement

loads the contents of location 100 into the AX register. The statement

stores the incremented value of AY into location 1234. To increment or shift the data word labeled X1 (assume it is at location 501), we could write

06 0100 06 X1 P1 000501

or 06 1000 06 X1 L1 000501 or 06 1100 06 X1 R1

Note that unless the user of

000501

Note that, unless the user alters the second word during program execution, the same location is accessed every time a direct mode memory reference instruction is encountered.

# 3.2.2 Deferred Addressing Mode

The key word D selects the deferred mode in a FAST memory reference statement. In this mode, the second word of the instruction contains the address of another location whose incremented contents is the effective address. The second word of the instruction is fetched and its value is used to access another location whose contents is incremented and written back into the same location. The control logic then uses this incremented value as the effective address.

If location 5 contains the value 200, then

11 0001 06 AX TO D 5 000005

stores AX into location 201. Location 5 now contains the value 201. If we do not change the value in location 5 before executing the above (or an identical) instruction again, then AX will be stored into location 202 and location 5 will be left at 202.

The deferred mode is sometimes called "indirect with auto-indexing". "Indirect" means that the address in the memory reference instruction is not itself the effective address, but

is the address of the effective address. "Auto-indexing" means that the effective address is incremented before it is used in the data transmission.

The deferred mode (and the immediate-deferred mode, below) is ordinarily used to access the sequential words in a data table, work area, or buffer area. Assume location 5 is initialized to 200 before each of the following examples. Then,

06 0001 12 D 5 TO AY 000005

can be successively executed to load the contents of location 201, 202, 203, etc. into AY. Obviously, the data in AY will be processed by other instructions in the program before the next item is retrieved. The instruction

00 0001 06 ZERO TO D 5 000005

can be used to clear successive locations beginning at 201.

Also, the instruction

06 0101 06 D 5 P1 000005

can be used to increment these sequential locations.

Often the data entries in a table will consist of two or more words each. The first word of an entry is fetched and, depending on its value, a decision is then made either to fetch the rest of the entry or to skip over the current entry and retrieve the next entry. If our auto-indexing location (assume location 5 again) is labeled INDX, the instruction

06 0100 06 INDX P1 000005

executed n times will, in effect, skip over n words in the table in order to point us to the next entry.

# 3.2.3 <u>Immediate Mode Addressing</u>

The key word I selects the immediate mode in memory reference statements. "Immediate" implies that the instruction itself provides or receives the data being transmitted. Therefore, the effective address in this mode is merely the address of the second word of the instruction itself.

To load the constant 14 into AX, one writes

06 0010 11 I 14 TO AX 000014

Note that the data to be transmitted has been assembled into the second word of the instruction. To initialize an auto-indexing location (INDX) so that successive entries of a table (TABLE) may be retrieved using a deferred mode, we could write

I TABLE-1 TO TRP

TRP TO INDX

Sometimes counting of events, like the number of times through a given program loop, is done with an immediate mode instruction. The statement

06 0110 06 I 0 P1 000000

causes the second word of the instruction to be incremented. The statement could be written with other than 0 as the value for the second word -- in any case, before entering a loop containing this counter, the second word of the instruction must be set to some appropriate initial value.

When an interrupt is detected, some portion of the interrupt-handling routine usually saves the contents of crucial registers in the system. This is often done with a sequence of immediate mode instructions.

03 0010 06 SAVE: TRP TO I 000000

17 0010 06 MSR TO I

000000

11 0010 06 AX TO I

000000

12 0010 06 AY TO I

000000

etc.

When the interrupt has been processed, the following direct mode statements could be used to restore the saved registers

SAVE+1 TO TRP

SAVE+3 TO MSR

SAVE+5 TO AX

SAVE+7 TO AY

etc.

# 3.2.4 Immediate-Deferred Addressing Mode

The key word ID selects the immediate-deferred mode in memory reference statements. This mode combines the immediate and deferred features. "Immediate" here implies that the address of the auto-indexing location is merely the address of the second word of the instruction itself. The GRI-909 control logic fetches the second word of the memory reference instruction, increments it, and writes the incremented value back into the second word. This incremented value is then used as the effective address in the data transmission. The statement

11 0011 06 AX TO ID 200 000200

can be used to store AX into locations 201, 202, 203, etc. It is the second word of the instruction itself which is auto-indexed. Of course, this second word must be re-initialized before a new set of AX values can be stored into the same locations. The statement

GET: ID TBL-1 TO AY

loads AY with the word labeled TBL the first time it is executed. The next n times, without being re-initialized, it loads the words at TBL+1, TBL+2, TBL+3, ..., TBL+n. This instruction at GET would probably be the first instruction in a program loop which processes the entries in the data table, TBL. Before entering the loop, the instruction at GET could be initialized by writing

# I TBL-1 TO TRP TRP TO GET+1

where the expression GET+1 represents the address of the second word of the immediate-deferred instruction at GET. If each entry in TBL were two words long, then some other instruction in the loop, after the instruction at GET, might be used to load the second word of the entry into a register, say AX. The same auto-indexing location is used for this purpose. For example,

#### D GET+1 TO AX

loads the second word of the entry provided that the instruction at GET has already loaded the first entry word. If it is desired to bypass this second word and point to the next entry, then the auto-indexing location can be updated by the instruction represented by

#### GET+1 P1

#### 3.3 Data Testing Instructions:

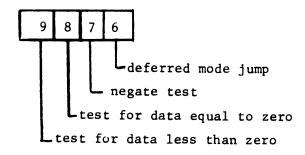

These instructions are used to test the data in a register relative to zero. The DDA is always the data tester and is filled in by the assembler. SDA refers to any non-memory data register, and MOD specifies the nature of the test and the addressing mode. The MOD format is:

If the test specified by MOD is not true, then the GRI-909 control logic procedes to the next sequential instruction in the program. If the test is true, the second word of the instruction is taken as a jump address or, in the deferred mode, as the address of the jump address. If a jump occurs (test is true), the address of the second word of the data test instruction is stored in the trap register (TRP), and the effective jump address replaces the contents of the computer's sequence counter (SC) (the TRP is used for subroutine linkage — see section 6.2). The FAST statement for data testing is an exact description of the action performed by the GRI-909, and has the general form

[symbol:] [IF register test] GO TO [D] e [;comment] where e is a general expression (2.6) whose value assembles into the second word of the instruction, and the word "test" in this context refers to a standard or user-defined symbolic data test code (6). The standard data test codes, their MOD values and associated meanings are:

| ETZ | 0100 | equal to zero                                                  |

|-----|------|----------------------------------------------------------------|

| LTZ | 1000 | less than zero                                                 |

| LEZ | 1100 | less than or equal to zero                                     |

| NEZ | 0110 | not equal to zero                                              |

| GEZ | 1010 | greater than or equal to zero (not less than zero)             |

| GTZ | 1110 | greater than zero (not less than <u>and</u> not equal to zero) |

In order to jump to location 100 if the AX register contains zero, one writes

11 0100 03 IF AX ETZ GO TO 100 000100

Note that the first word, as in all GRI-909 instructions, is a data transfer format telling the processor to connect device 11 (AX) to device 03 (data tester). The non-memory source and the 03 destination indicates the data test instruction to the processor. The MOD in this case has the meanings shown above. For the purpose of the example, we have used a constant as the jump address — the statement may be written with any meaningful expression to represent the jump address.

Because of the jump address, the data testing instruction is a form of memory reference instruction. The deferred mode jump operates similarly to the deferred mode memory reference data transmission instruction (3.2.3). If location 200 contains the value 543, then the statement

13 1001 03 IF AO LTZ GO TO D 200 000 200

causes a jump to location 544 if the arithmetic operator output (AO or device 13) is less than zero. The second word of the data test instruction is used by the processor to fetch the jump address at 200 -- this address is first incremented and the incremented value replaces the contents of location 200 before the jump address is transmitted to the SC. Normal program flow begins at location 544. Since location 200 now contains the value 544, the next jump affected by the foregoing data test instruction would cause a transfer of control to location 545 unless the user reinitialized location 200. The major use for the deferred mode jump is to return from subroutine (6.2).

In order to apply a data test to the contents of a memory location, it is first necessary to load it into some non-memory register. Suppose the data word X1 is at location 1234 and the instruction OVER is at location 157. In order to jump to OVER if X1 is greater than zero, we could write

06 0000 11 X1 TO AX 001234 11 1110 03 IF AX GTZ GO TO OVER 000157

If the AX register were being used for some other purpose and we did not wish to destroy its contents, the TRP register associated with the data tester could be used to contain the data for testing. We could accomplish the foregoing test by writing

Regarding this last example, we note the following: 1) since the TRP register has the same address as the data tester, it cannot be loaded with data from another non-memory register since this combination defines the data testing instruction, 2) the TRP can be loaded from memory (SDA=06) -- this is the only instance of DDA=03 that is not a data testing instruction, and 3) if the jump occurs, the data in TRP will be lost, since it is automatically loaded with the address of the second word of the data test instruction.

Other than the aforementioned restriction on the TRP, it can be used as a general purpose register. Its contents can be transmitted to another register or to some memory location. For example,

03 0000 12 TRP TO AY

03 0000 06 TRP TO 501

000501

03 0010 06 TRP TO I ; STORE IMMEDIATE

000000

This last example instruction is often used to save the contents of the trap upon entry to a subroutine (6.2).

Often we require an instruction which causes a jump every time it is encountered. This enables us to jump back to the beginning of a loop, to call or enter subroutines, etc. Since device ZERO is a source of a zero data word, we could always employ the following artifice to jump to some location, say 533

00 0100 03 IF ZERO ETZ GO TO 533 000533

The FAST language provides a short form for this particular instruction, a simple GO TO

The deferred mode jump may also be used with this short form jump instruction.

# 3.4 Function Output Instructions:

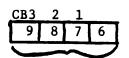

Function output instructions are used to deliver control or function pulses to those system devices which require them for mechanical or electrical control. A function output instruction always has the function generator as its SDA. Its code, 02, is supplied by the assembler. The DDA is some controllable system device, and the MOD specifies up to four pulses to be transmitted in parallel to the device at DDA. The MOD format is:

correspond to the four pulse output lines

The four pulses are transmitted in parallel. Therefore, up to 16 unique pulse patterns may be transmitted to a single device. Of course, the device must be interfaced so as to discriminate between the patterns. Simple devices usually associate a single line with a specific function. The general form of a function output statement is:

[symbol:] pulse [pulse] ... [TO] device ['comment]

The word "pulse" in this context refers to a standard or user-defined symbolic pulse code (5). The symbolic destination device code must be included unless the pulse code used has a destination built into it (5.1).

Standard pulse codes for operating devices such as teletype input/output, high speed reader, and high speed punch are

| Mnemonic | Definition         | Mod Code |

|----------|--------------------|----------|

| STRT     | -start             | 0001     |

| CLIF     | -clear input flag  | 1000     |

| CLOF     | -clear output flag | 0010     |

The STRT pulse causes a paper tape reader to advance and read the next frame of data.

| 02 0001 77 | STRT TO TTI | ;ADVANCE TTY READER |

|------------|-------------|---------------------|

| 02 0001 76 | STRT HSR    | ;ADVANCE HS READER  |

Note that the "TO" may optionally be omitted from the statement. It is possible to combine start and clear flag commands in one instruction.

| 02 | 1001 | 77 | STRT | CLIF | TO | TTI |

|----|------|----|------|------|----|-----|

| 02 | 1001 | 76 | CLIF | STRT | то | тто |

The ordering of multiple pulse codes is immaterial -- as each one is encountered, the assembler OR's its value into MOD. Depending upon how a device is being operated, the clear flag commands may be issued separately.

| 02 | 1000 | 77 | CLIF | то | TTI |

|----|------|----|------|----|-----|

| 02 | 0010 | 77 | CLOF | то | тто |

| 02 | 1000 | 76 | CLIF | то | HSR |

| 02 | 0010 | 76 | CLOF | TO | нѕр |

Standard pulse codes corresponding to internal functions of the GRI-909 have been defined so as to contain their destination. This means that the entire function output statement consists of merely the pulse code (5.1).

| 02 | 0100 | 00 | HLT | ;HALT MACHINE           |

|----|------|----|-----|-------------------------|

| 02 | 0010 | 00 | STL | ;SET LINK               |

| 02 | 0001 | 00 | CLL | ;CLEAR LINK             |

| 02 | 0011 | 00 | CML | ;COMPLEMENT LINK        |

| 02 | 0000 | 13 | ADD | ;SET AO TO ADD          |

| 02 | 0100 | 13 | AND |                         |

| 02 | 1000 | 13 | XOR |                         |

| 02 | 1100 | 13 | OR  |                         |

| 02 | 0010 | 04 | ICO | ;INTERRUPT CONTROL ON   |

| 02 | 0001 | 04 | ICF | ; INTERRUPT CONTROL OFF |

Note that the CML command is equivalent to

02 0011 00 STL CLL

The combined command is included in FAST as a convenience to the user.

#### 3.5 Sense Function Instructions:

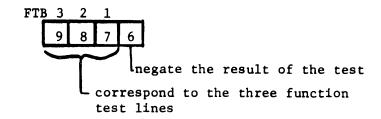

Sense function instructions are used to test the status or function signals of various types of devices. The device's status indicators are often used to represent such conditions as "ready", "busy", "overflow", "data error", etc. In a sense function instruction, the DDA is always the function tester, and its code (02) is filled in by the assembler. The SDA is any system device that has one or more status indicators associated with it. The MOD format is:

If the test specified by MOD is true, then the GRI-909 control logic causes a skip over the <a href="next two machine words">next two machine words</a>. Two words are skipped because a SKIP is usually followed by a jump (GO TO) instruction. The general form of a sense function is [symbol] SKIP [IF] [device] status [status] ... [;comment]

The word "status" in this context refers to a standard or user-defined status test code (5). The symbolic source device code must be used unless the status test code has a source built into it (5.1).

Standard status codes for testing devices such as teletype input/output, high speed reader, and high speed punch are:

| Mnemonic | <u>Definition</u> | Mod Code |

|----------|-------------------|----------|

| IRDY     | -input ready      | 1000     |

| ORDY     | -output ready     | 0010     |

#### For example:

77 1000 02 SKIP IF TTI IRDY ; CHARACTER READ? 76 0010 02 SKIP HSP ORDY ; READY TO PUNCH?

Note that the word "IF" may be omitted as desired. The standard status code NOT causes the low-order bit of MOD to be set.

76 1001 02 SKIP IF HSR NOT IRDY 77 0011 02 SKIP TTO NOT ORDY

If the status code NOT is included, then a skip occurs only if the <u>selected condition is not true</u>. Standard status codes corresponding to internal conditions of the GRI-909 have been defined so as to contain their sources. This means that the sense function instruction may be written without the source device.

| 13 ( | 0010 02 | SKIP IF AOV | ;ARITHMETIC OPERATOR OVERFLOW |

|------|---------|-------------|-------------------------------|

| 00 ( | 0010 02 | SKIP BOV    | ;BUS OVERFLOW                 |

| 00 ( | 0100 02 | SKIP LNK    | ;LINK SET                     |

| 00   | 1000 02 | SKIP POK    | ; POWER OK                    |

The code NOT may be included if it is desired to skip on the falsity of a given condition. Codes for status indicators residing on the same device may be combined in the same sense function instruction. For example,

00 0110 02 SKIP BOV LNK

skips if the <u>OR of the selected conditions is true</u>, that is, if <u>either</u> BOV or LNK is true. Setting the NOT bit complements this inclusive OR. Thus, the instruction

00 0111 02 SKIP NOT LNK BOV

skips only if BOV is not true and LNK is not true. Note that in neither of the foregoing instructions the setting of the POK indicator affected the tests in any way.

As a further clarification of sense function instructions, assume a device Q that has three status indicators X, Y, Z corresponding to bits 9, 8, 7 of MOD respectively. Further assume that we wish to test for unique combinations of the status indicators — given the three indicators, there are 8 unique combinations to test for. In the examples which follow, program control passes to YES if the desired combination test is true, and to NO if it is not true.

To test for the condition 000 (X, Y, Z all false), we write

SKIP Q NOT X Y Z

GO TO NO

YES: test true here ; NONE ON

To test for a single indicator on, such as 010, we could write

SKIP Q Y

GO TO NO

SKIP Q NOT X Z

GO TO NO

YES: test true here ;ONLY Y ON

To test for two indicators on, such as 110, we could write

SKIP Q NOT Z

GO TO NO

SKIP Q X

GO TO NO

SKIP Q X

GO TO NO

YES: test true here ; ONLY X and Y

To test for all three indicators on, we write

SKIP Q X

GO TO NO

SKIP Q Y

GO TO NO

SKIP Q Z

GO TO NO

YES: test true here ;ALL ON

Of course, the assumption we must make here is that the state of the device Q remains constant when testing for any unique combination.

#### CHAPTER FOUR

#### ASSEMBLER INSTRUCTIONS

Some FAST statements merely act as directives to the assembler during the assembly process and do not result in object code output.

Other assembler instructions enable the inclusion of numeric or textual data into the user's program. All of these so-called assembler instructions (pseudo-ups), with the exception of the one for defining new system symbols (Chapter 5), are presented in this chapter.

#### 4.1 Parameter Definition:

It is often desirable to establish a numeric value or constant and to be able to refer to it symbolically. For example, instead of using the constant 215 (the teletype carriage-return code), it might be more meaningful to use the symbol CR. Such a symbolic parameter can be defined by the statement:

CR = 215 ; CARRIAGE RETURN

We could then write: I CR TO TTO 06 0010 77 000215

The general form of a FAST parameter definition statement is:

symbol = e [;comment]

where e is a general expression (2.6). The value of the symbolic parameter will be the assembled value of the expression with which it is associated. A parameter is used to represent a numeric value — this parameter may be used as an operand in other expressions for address or data values. Note that no object code is generated by a

parameter definition statement -- the statement merely generates an entry in the assembler's symbol table.

DIFF = A - B

Examples:

TEN = 10 CRLF = 106612 ;CARRIAGE RETURN AND LINE FEED

A symbolic parameter may be redefined within the same program. If a parameter does take on more than one value, then its initial value must be defined in the source program before it is first used to reference a numeric value. Also, the expression e, used to specify the value of a parameter, must be fully resolvable by at least the end of pass 1 (so that it will have the correct value during passes 2 and 3). In other words, the value of any symbol in the expression must be established within at most one forward reference. For example, in the sequence

A = B + 5B = 22

the correct value of A is not established when the statement is first encountered during pass 1 since B is not yet defined (A will have the value 5 since undefined symbols are assigned the value 0). Nevertheless, when the definition of A is encountered during pass 2, it will be assigned the correct value, 27, since B is now defined.

Parameter definition statements are often used for the purpose of system linkage -- see section 6.1.

# 4.2 Radix Control:

FAST language constants (2.5) are converted to binary and are

interpreted according to the setting of an assembler variable called the RADIX. Constants may be written as either octal numbers or decimal numbers. The assembler's RADIX is set to octal at the beginning of <u>each</u> pass. In other words, the assembler assumes all constants to be in octal.

The user may switch the RADIX from one mode to another at will. The form of the RADIX control statement is:

If the user wishes to write constants in decimal notation, he precedes the first such constant with the statement:

\*DEC

All constants between this statement and the end of the program (or between this statement and a \*OCT command) will be interpreted as decimal numbers. The assembler's RADIX is like a switch -- once it is thrown to decimal it stays in that mode until the beginning of the next pass or until the assembler encounters the other RADIX command

\*OCT

causing the RADIX to be set back to octal. While in the octal mode, the assembler detects the usage of the decimal digits 8 and 9. If either of these digits occur in a statement while the assembler is in the octal mode, the assembly listing of that statement will be preceded by the error code D (decimal digit in octal field).

Remember that the assembler's RADIX is automatically set to octal at the beginning of each pass.

# 4.3 Location Counter:

The assembler maintains a variable called the LOCATION COUNTER. During the assembly process, the LOCATION COUNTER always reflects the address of the next memory location that object code may be assigned to by the assembler. As the assembler processes each statement that generates either a machine instruction or data, it automatically updates the LOCATION COUNTER by the length (number of machine words) of that statement's object code. At the beginning of each pass, the assembler sets its LOCATION COUNTER to 0. If the user does not change the LOCATION COUNTER, then his entire program will be assembled for sequential locations starting with location 0.

A statement to set the assembler's location counter is ordinarily used to specify the first location of a program being assembled. The set-LOCATION COUNTER statement has the form:

# \*e [;comment]

where e is an expression (2.6). A further restriction on this statement is that the expression <u>must not</u> contain any undefined symbols when it is first encountered by the assembler. Also, e is influenced by the current radix (4.2). The statement

# \*1000 ;START AT 1000 (8)

causes all subsequently encountered machine instructions or data words to be assembled for sequential locations starting at location 1000. More than one set-LOCATION COUNTER statement may be included in a given program -- if the user wishes to load various segments of his program into non-contiguous areas of memory, then a set-

LOCATION COUNTER statement at the beginning of each source program segment fixes its respective starting address.

Often it is desirable to reserve a block of memory locations to be used as a work area or input/output buffer when the object program is run. This is done by updating the LOCATION COUNTER relative to its current value. Thus, the statement

\*.+50 ;NOTE: 50 MAY BE OCTAL OR

causes the assembler to reserve (skip over) 50 sequential locations, the first of which will be at the address specified by the LOCATION COUNTER when the statement is read. This current value of the LOCATION COUNTER is denoted by the special character period (.). If the current value was 101, then the next object code generated will be assigned to location 151.

A block of memory thus reserved may be labeled. The statement

WORK: \*.+20

reserves 20 locations, the first of which may be symbolically referenced as WORK. Note that the label is encountered and processed before the set-LOCATION COUNTER command itself is processed.

#### 4.4 Program Terminators:

The user must indicate the physical end of a program to the assembler. The assembler can then finalize all processing for the current pass and come to a halt ready to procede to the next pass in the assembly process, if any. The assembler command

must be the last statement in the program. If a source program is made up of two or more segments of tape, then each segment but the last must have the command

\*EOT

as its last statement. This end-of-tape command causes the assembler to halt for the insertion of the next tape segment in the reader -- pressing CONT on the console starts the processing of the new tape as part of the same program.

#### 4.5 Data Definition:

Some of the data a program operates upon may be assembled into the program itself. Such items consist of numeric constants and/or textual data. Numeric constants could be upper and lower limits for checking against input values, tables of values used for code conversion or function interpolation, machine addresses of important tables or entry points in a program, etc. Of course, single-valued numeric constants are often assembled into immediate mode memory reference instructions (3.2.2). Textual data could consist of error messages to be output to an operator, or fixed heading information for printed reports.

#### 4.5.1 Word Values

Numeric constants can be assembled for consecutive locations of memory by using the general form

[symbol:] e [,e] ... [;comment]

where each e is a general expression (2.6). The expressions

representing values to be assembled for each location are separated from each other by commas (,). Each expression e results in a full 16-bit binary word in the object program. The first word assembled from this statement may optionally be labeled. Thus, the statement

PWR: 1750,144,12

causes the three consecutive octal numbers to be assembled for three consecutive memory locations, the first of which is labeled PWR. This statement is equivalent to the three statements:

PWR: 1750

144

12

Further examples are:

COUNT: 0

LNGTH: B - A + 1

Z!Q,ZQQ

2,15,.+5

Note: If the symbol . (representing the assembler's LOCATION COUNTER) is encountered in an expression in a comma-separated list of data word definitions, its value will be the address of the memory location for which that specific expression is being assembled.

# 4.5.2 <u>Text</u>

One or more characters of ASCII text may be assembled for consecutive words, packed two characters (8 bits each) per word. If the text contains an odd number of characters, the rightmost 8 bits of the last word assembled will be set to 0's. A textual data definition statement consists of the character single-quote ('), followed

by the body of the text, and is terminated by the same delimiting character that preceded the text. The general form for defining textual data is

'dc [c] ... d

where d is a delimiter chosen by the user, and the c's are the individual characters in the text. The delimiter must be chosen such that it does not occur within the body of the text. Examples are

'/LIMIT EXCEEDED/

MSG3: '.V1/V2 0.

Note that text may be labeled. The label (e.g. MSG3 above) is associated with the first packed word assembled from the text. As for word values, two or more text definitions may occur in the same source statement provided they are separated by commas.

The delimiters and text characters may be any of the printable ASCII characters, including those outside the FAST general usage and reserved character sets (2.1). Exceptions — the following characters have special meanings to the assembler and the Source Text Editor and may not be used as a delimiter or text character:

Carriage-return

Line-feed

Back-arrow

Rubout

Block-mark

#### 4.5.3 Combined Text and Word Values

Text and word value definitions may be freely combined in a

comma-separated list. In this, and in any statement, the 80-character statement length must not be exceeded. As an example of a reasonable such combination, consider the following

ERR4:7, '/TEMP. 4 HIGH/,106612

The address of this hypothetical message, represented by ERR4, is to be sent to a general output routine which will process the data assembled from the overall statement. The first word fetched by the output routine is the value 7 which tells it to unpack and type out the next 7 words (14 characters). The second list element assembles into 6 packed words, since there are 12 characters in the body of the text. The last list element, or 7th message word, represents the packed characters carriage-return and line-feed. This mechanism is necessary because they could not be made a part of the text definition itself (4.5.2).

#### CHAPTER FIVE

#### DEFINITION OF NEW SYSTEM SYMBOLS

The most useful function an assembler provides the user is the ability to give symbolic names to memory locations and word values. In addition to this, the FAST language also provides the user the ability to name new system entities beyond those defined in the assembler's permanent symbol table. This ability is extended to encompass not only the SDA and DDA portions of the instruction but also the MOD portion of the instruction.

The permanent symbol table contains definitions for standard IO devices such as TTI, TTO, HSP, and HSR. The user may desire to refer to an analog multiplexer as MUX, or an A/O converter as ADC. These symbols are added to the assembler's symbol table via a symbol definition statement.

Also included in the permanent symbol table are definitions of certain pulse patterns from the function output section as well as certain status codes utilized in sense function instructions. Examples are STRT, CLIF, BOV, ORDY, etc. The user again may wish to add his own unique codes to the symbol table, such as GRP1, STOP, LOAD, etc.

The user may also wish to develop his own pseudo code for commonly used instructions. The DEFINITION STATEMENT THAT DEFINES A NEW SYMBOL MUST PRECEDE ANY OTHER USE OF THE SYMBOL IN THE PROGRAM. (5.1)

It is strongly recommended that the user not re-define bus modifier symbols (P1, L1, R1, C) or data testing symbols (ETZ, LTZ, etc.). These are symbol type numbers 4 and 5. Symbol types 6 and 7 are more normally

defined as described in 2.4 and 4.1. They may, however, be defined by a definition statement.

The symbol definition statement may also be used to add pseudo-codes.

The general form for defining a new symbol is:

SYMBOL #t,n [;comment]

SYMBOL is the 5 character name being defined. #t is a type number that describes the type of definition being made (see table). n is the numeric value (in octal) that the assembler will use to replace the symbol when it is encountered during an assembly.

Note: ALL NUMERIC REFERENCES MUST BE OCTAL.

# SYMBOL DEFINITION TABLE

| #t | Type of Definition             |

|----|--------------------------------|

| 1  | Device Code                    |

| 2  | Output Pulse Code              |

| 3  | Status Test Code               |

| 4  | Path Code for Bus Modifier     |

| 5  | Data Test Code                 |

| 6  | Statement Label                |

| 7  | Parameter Symbol               |

| 10 | Register Reference Pseudo Code |

| 11 | Memory Reference Pseudo Code   |

# 5.1 Device and Device Related Codes:

New devices added to the system by the user will require the use of the definition statement if they are to be referred to symbolically in the users program. It is necessary that the user put these definitions at the front of the program, or perhaps on a separate tape terminated by an \*EOT (section 4.4). This

definition tape may be used in front of all program tapes the user wishes to assemble that refer to the same system devices. This definition tape need only be read during pass 1 of the assembly.

For example, if a new device named MUX were to be defined with an octal address 56 (maximum address is 77<sub>8</sub>), the definition statement is:

#### MUX#1,56

After this statement has been entered, the name MUX may be used just as any other device name in the assembler. If one wished to replace one of the existing assembler symbols with another address, the same procedure would be used. For example:

#### TTI#1,44

This associates the symbol TTI with the new address 44. It is useful to point out here that the values in the assembler's symbol table for type 1 symbols (devices) exist as right justified numbers. However, this is not the case when one specifies a MOD code (types 2-5). The MOD codes consist of four binary bits in the middle of a machine instruction, so defining a new pulse code will require that the octal value be located in the proper place (bits 9-6) of the octal "n" parameter.

Consider the following pulse code:

0110

Its name will be "QUIT", and it will be a type 2. It remains to define the octal "n" parameter.