# SW10 MAINTENANCE MANUAL

**General Terminal Corporation**

# SW10 MAINTENANCE MANUAL

GTC PN 970005-001

PRINTING: MAY 1982

#### COPYRIGHT 1981

# GENERAL TERMINAL CORPORATION 14831 FRANKLIN AVE. TUSTIN, CA. 92680-7282 (714) 730-0123 TWX 910-595-2428

All rights reserved. No part of this publication may be reproduced in any form without written permission from General Terminal Corporation.

The following related documents are available from GIC:

SW10 Users Manual

PN 970004-001

SW10 Reference Card

PN 970008-001

TV Monitor Manual

PN 05018-001

#### DISCLAIMER

The material in this manual is for information purposes only. The contents and the product it describes are subject to change without notice. General Terminal Corporation makes no representation or warranties with respect to this manual.

Printed in USA

| Page  | ii |  |

|-------|----|--|

| - 430 |    |  |

# TABLE OF CONTENTS

| Section        | I                                              | age          | Section    | n. <u>Page</u>                              |

|----------------|------------------------------------------------|--------------|------------|---------------------------------------------|

| 1.0            | INTRODUCTION                                   | -1           | 4.0        | DISASSEMBLY PROCEDURES4-1                   |

| 1.1            | GENERAL DESCRIPTION                            | . <b>-</b> 1 | 4.1        | Removing the Front Bezel4-1                 |

|                |                                                |              | 4.2        | Removing the Mounting Frame4-2              |

|                |                                                |              | 4.3        | Removing the Logic Control Bd.4-3           |

| 2.0            | TESTING & TEST AIDS                            | <u>:-1</u>   | 4.4        | Removing the CRT4-4                         |

| 2.1            | POWER-ON AUTOMATIC TESTS                       |              | 4.5        | Storing the CRT4-6                          |

| 2.2            | OFF LINE CONFIDENCE TESTS                      |              | 4.6        | Removing the Power Panel4-7                 |

| 2.3            | ON LINE INTERFACE TESTS                        |              | 4.7        | Removing the Monitor Ctrl.Bd4-8             |

| 2.4            | ALTERNATE TWO-WAY TEST                         |              | 4.8        | Disassembly of the Keyboard4-10             |

| 2.5            | FAULT ISOLATION                                |              | 4.0        | broubbally of the helpothers in             |

| 2.5.1          | Keyboard2                                      |              |            |                                             |

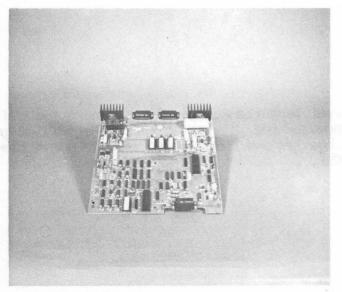

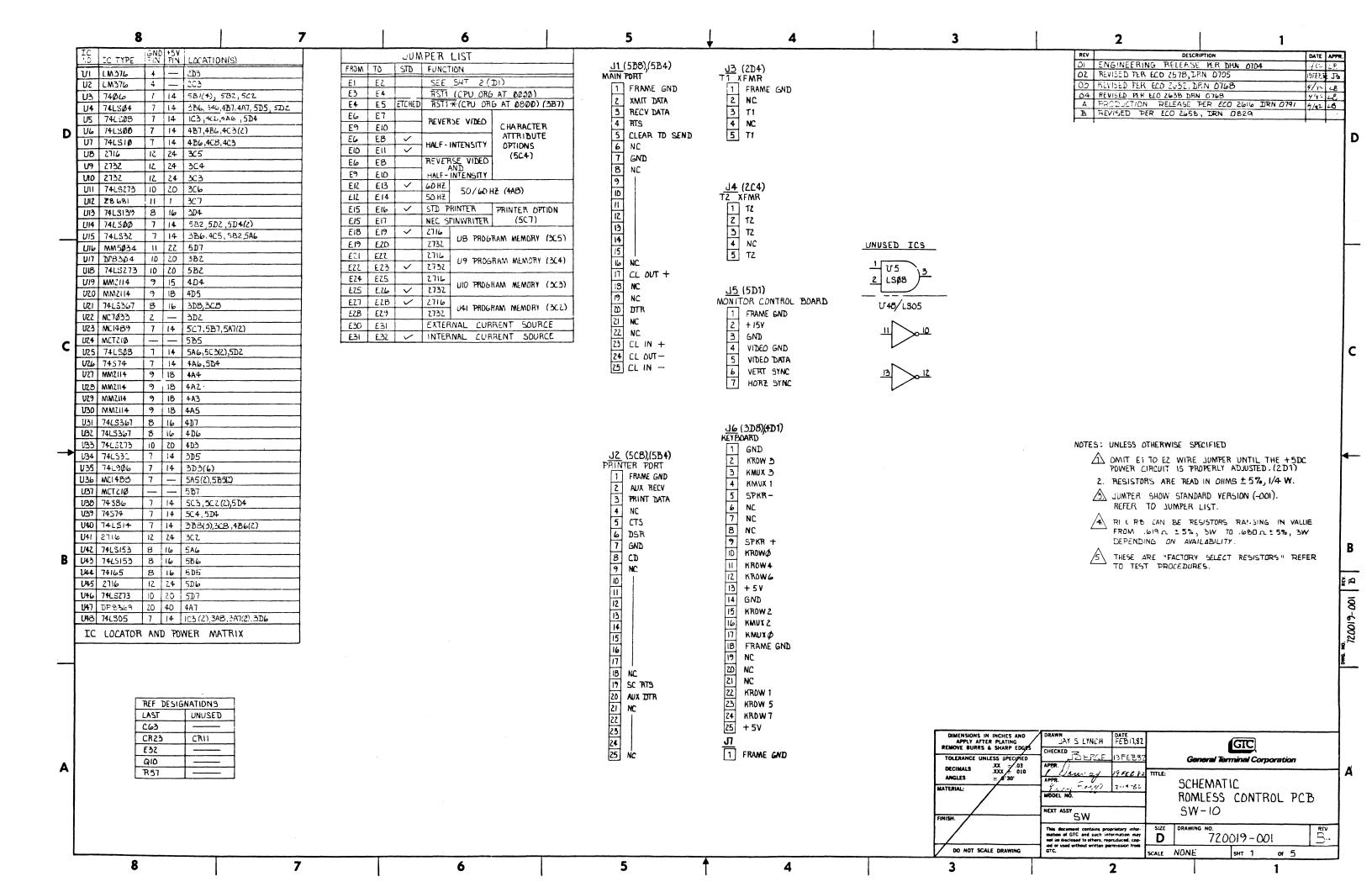

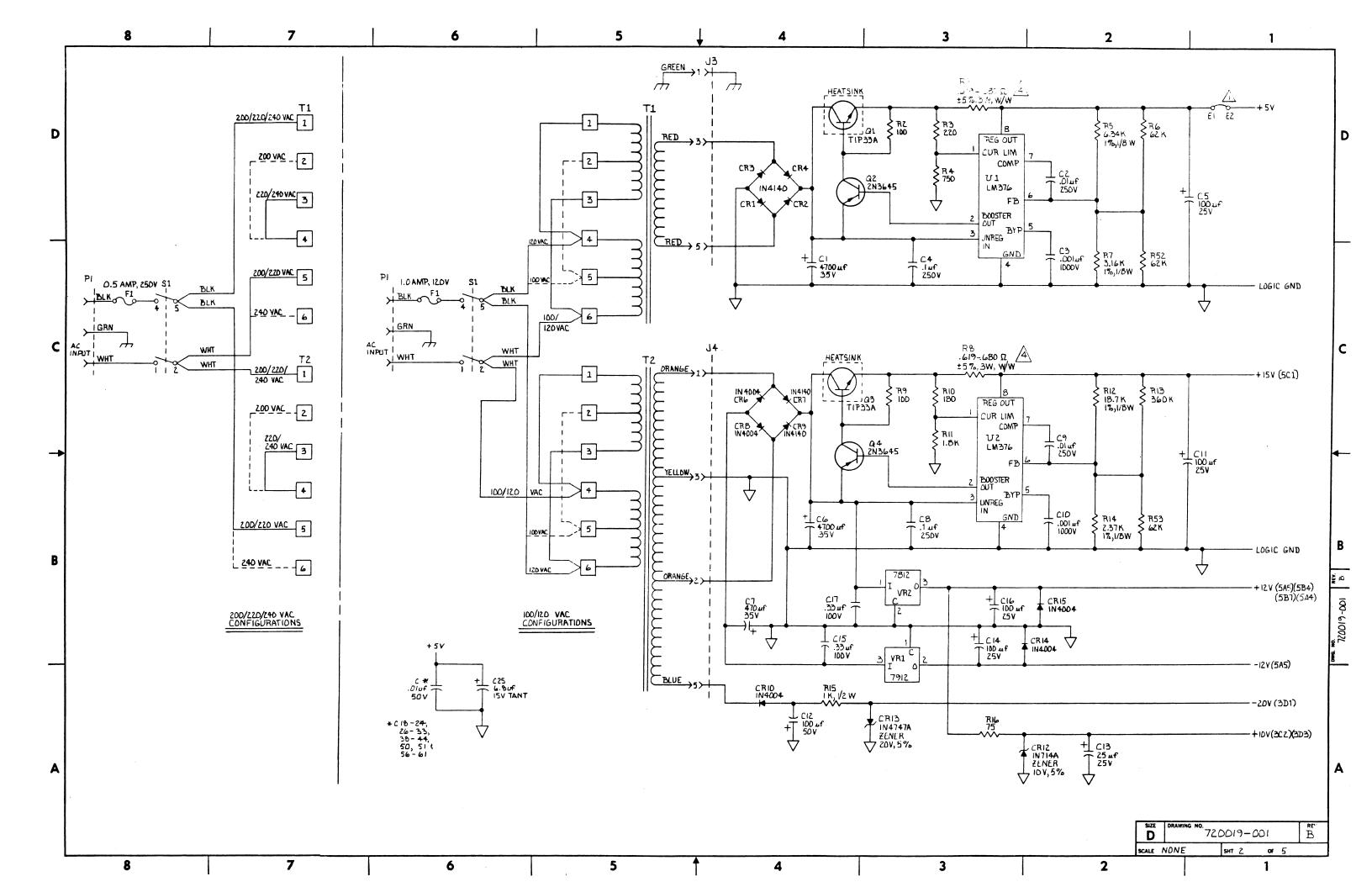

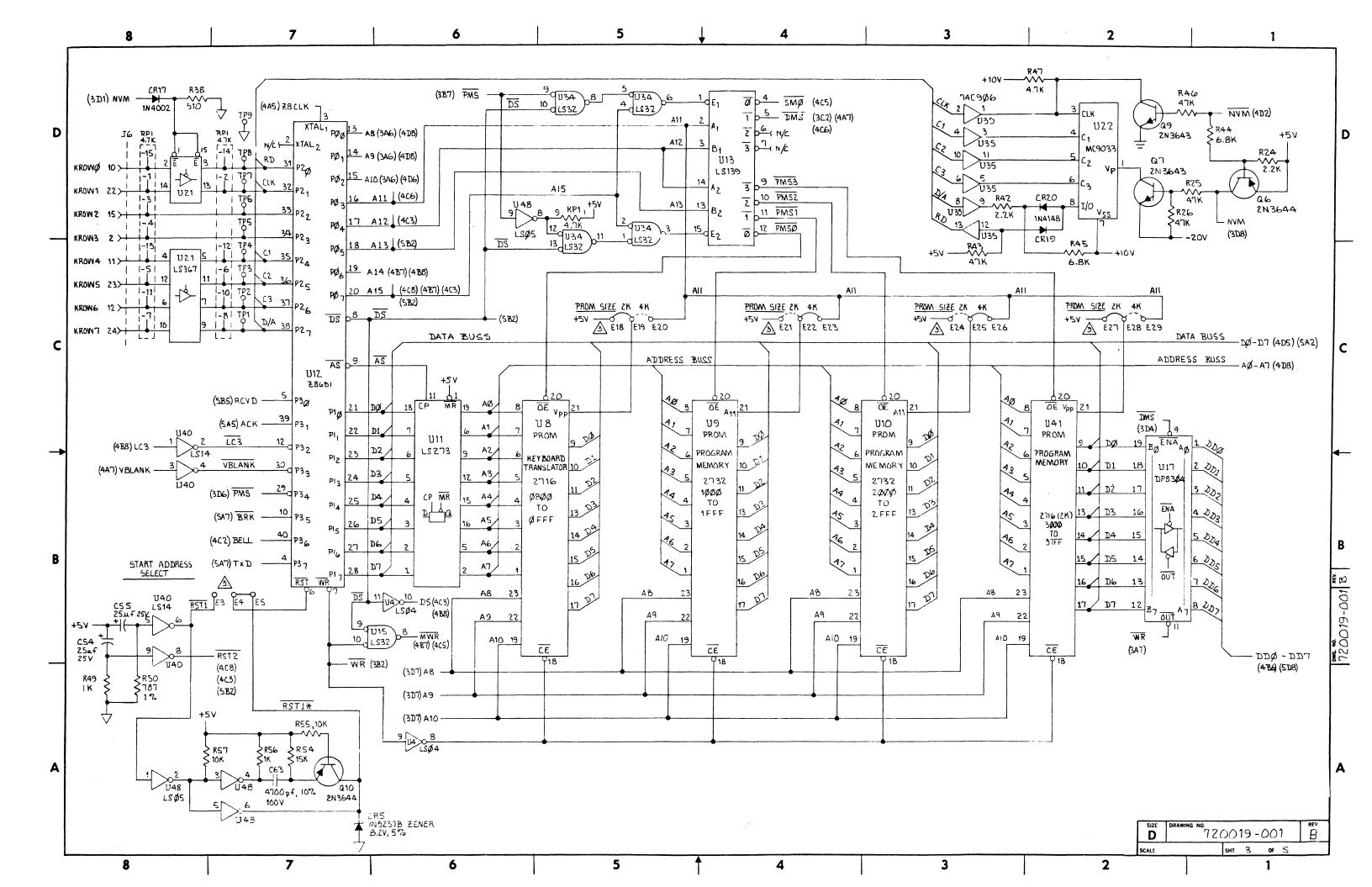

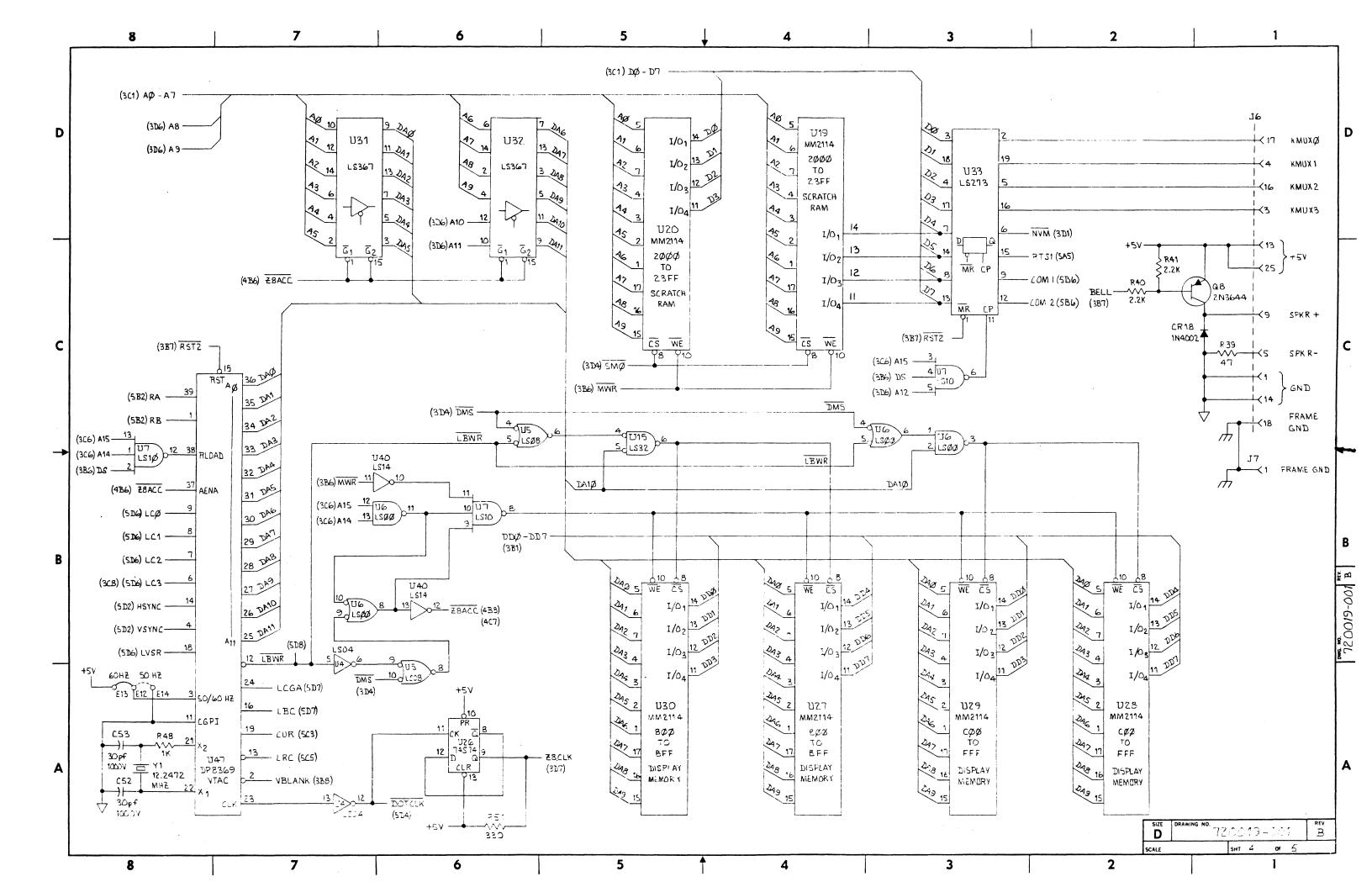

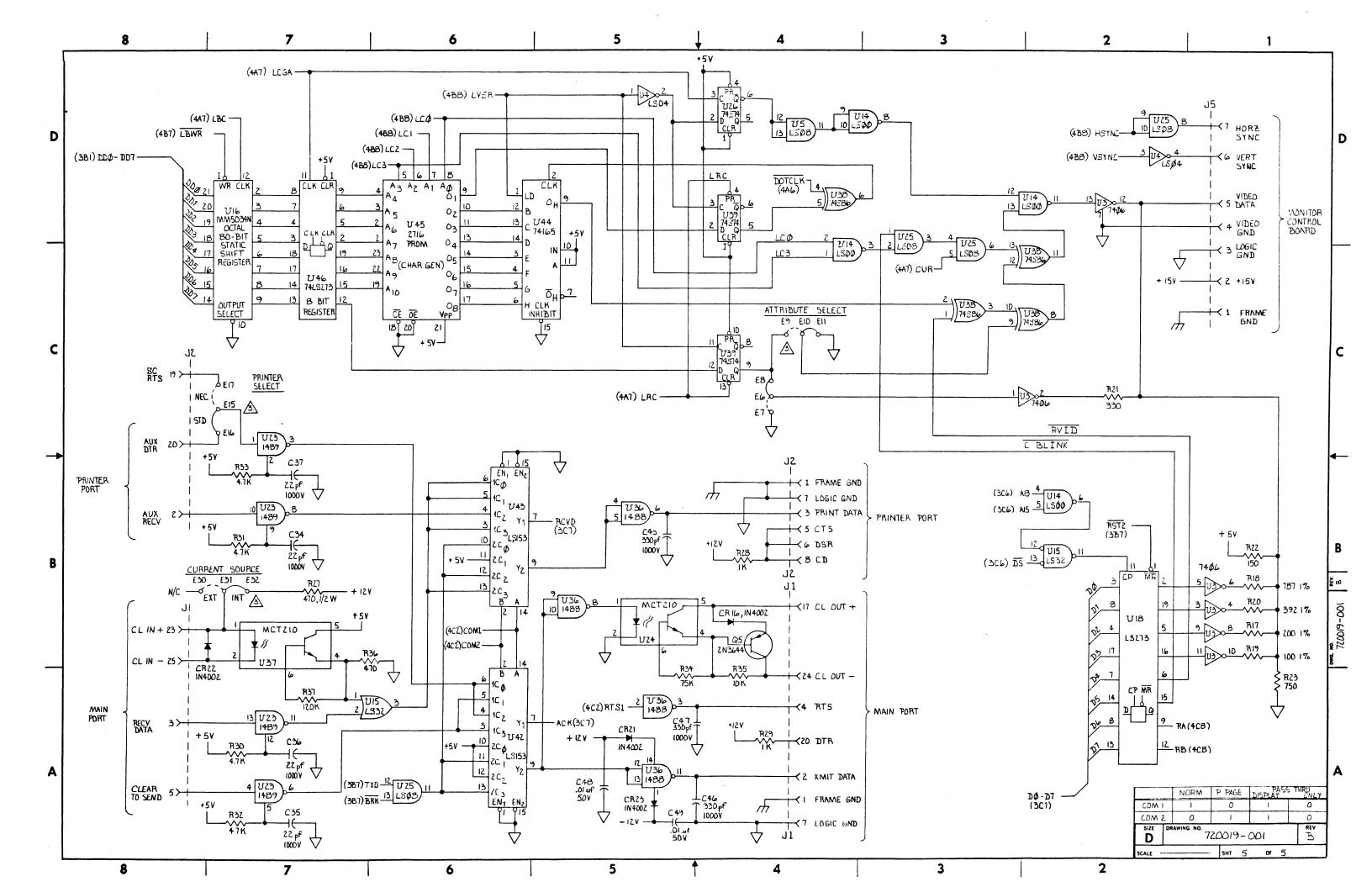

| 2.5.2          | Terminal Control Board                         |              | 5.0        | SCHEMATICS                                  |

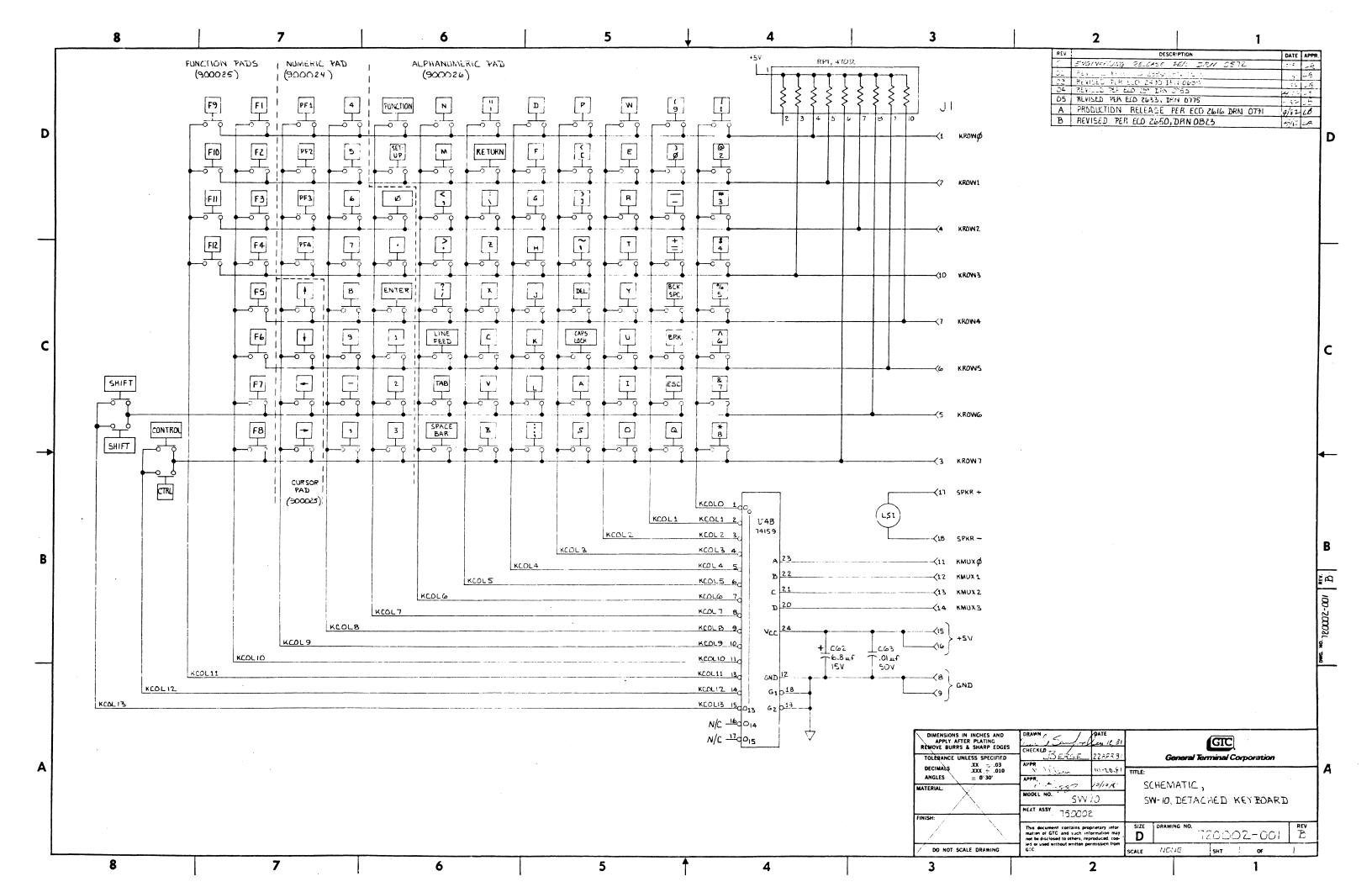

| _,,,,          | Taliffed Outer of Doubles 1888                 | . •          | J.D        | Keyboard 720002                             |

|                |                                                |              |            | Terminal Control Board5 sh                  |

| 3 <b>.</b> Ø   | THEORY OF OPERATIONS                           | _1           |            | Tenuncia Concior Deard                      |

| 3 <b>.</b> 1   | GENERAL                                        |              |            |                                             |

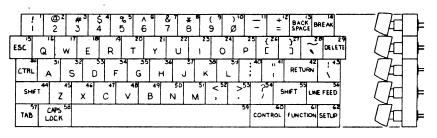

| 3 <b>.</b> 1.1 | Keyboard3                                      |              | 6.0        | CABLES AND CONNECTORS6-1                    |

| 3.1.2          | Terminal Control Board                         |              | 0.0        | CADLES AND CONNECTORS                       |

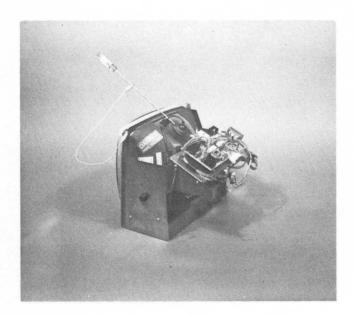

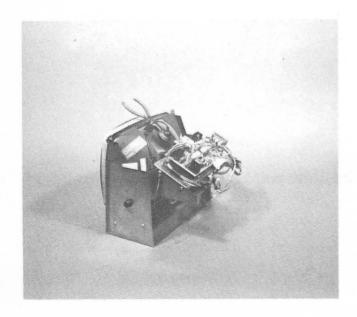

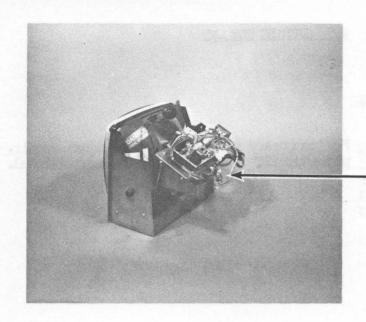

| 3 <b>.</b> 1.3 | Monitor Assembly                               |              |            |                                             |

| 3.1.4          | Power Transformers                             |              | 7.0        | ORDERING AND REPAIRS7-1                     |

| 3 <b>.</b> 2   | DETAILED THEORY OF OPERATIONS                  |              | 7.1        | Manual Ordering7-1                          |

| 3.2.1          | Keyboard Assembly                              |              | 7.2        |                                             |

| 3.2.2          | Terminal Control Board                         |              | 7.2<br>7.3 | Parts Ordering7-1                           |

| 3.2.2          | [1] Address Init Circuit3                      |              | 7.4        | Items Returned for Repair7-1 Parts Lists7-3 |

|                |                                                |              | 7.4        | raits hists/-3                              |

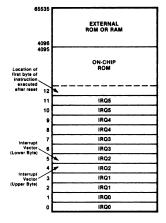

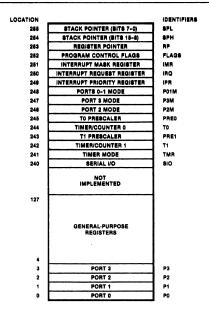

|                | [2] Microprocessor Circuits3 [3] Program PROM3 |              |            |                                             |

|                |                                                |              | 0 0        | ACCIDENT DISABILITING                       |

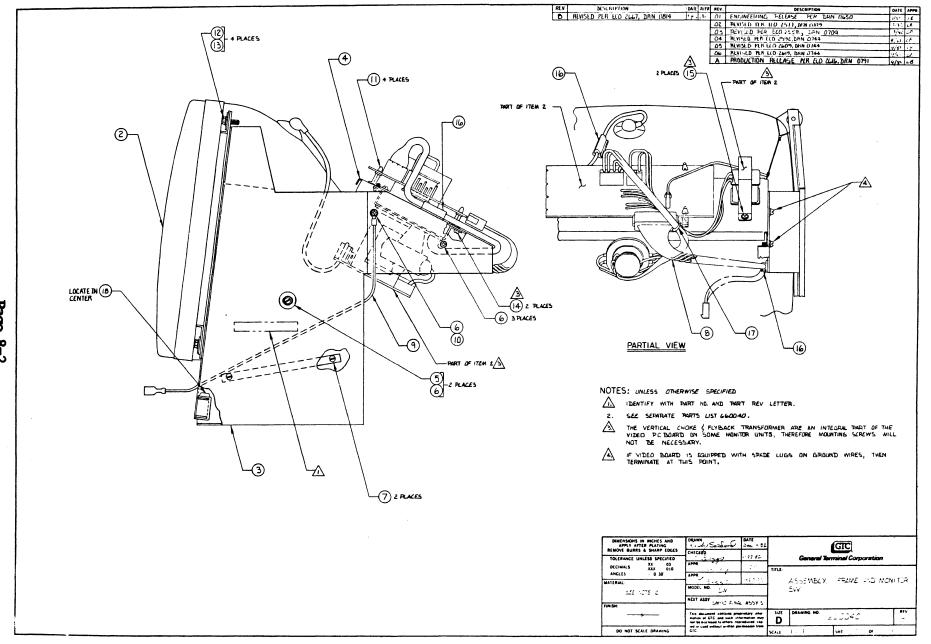

|                | [4] Scratch Pad RAM                            |              | 8.0        | ASSEMBLY DRAWINGS                           |

|                | [5] Display RAM                                |              |            |                                             |

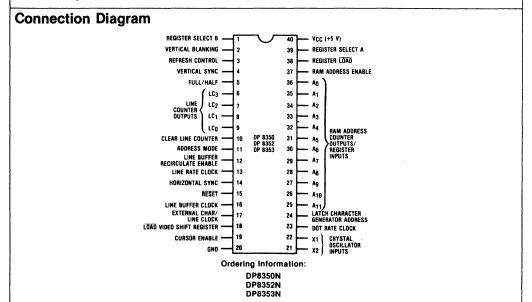

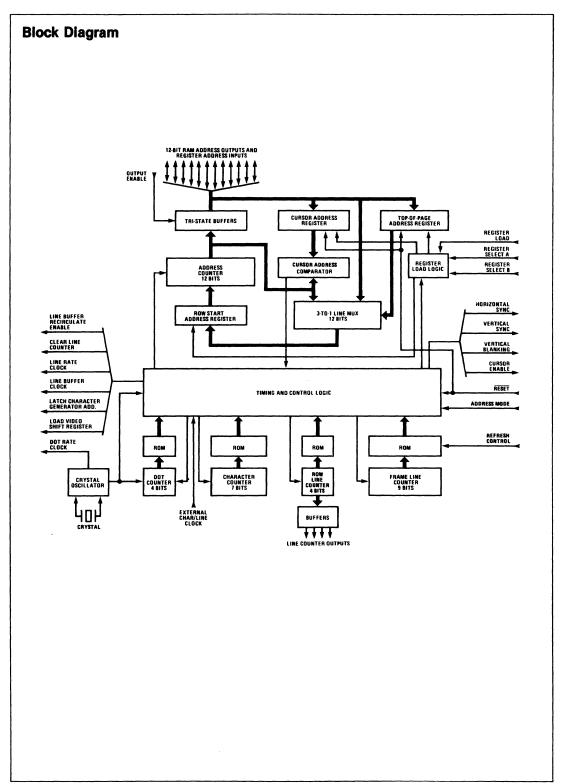

|                | [6] Video Timer & Controller (VIAC).3          |              | ATOTOTOTO  | NTV 3                                       |

|                | [7] System Clock                               |              |            | XIX AZ8 Product Spec                        |

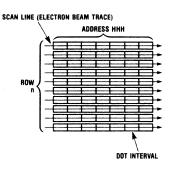

|                | [8] Row Buffer                                 |              |            | OIX BVTAC Product Spec                      |

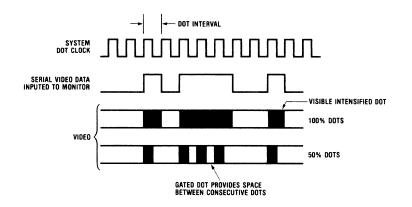

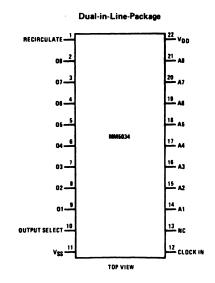

|                | [9] Video Generator                            |              |            | IX CRow Buffer Product Spec                 |

|                | [10] Function Decoder #23                      |              | APPENL     | OIX DNVM Product Spec                       |

|                | [11] Function Decoder #1                       |              |            |                                             |

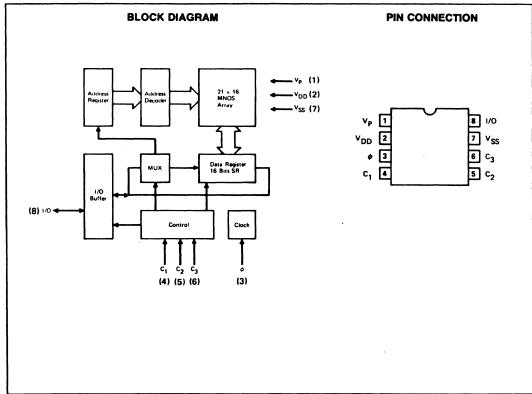

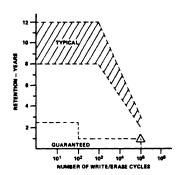

|                | [12] Non-Volatile Memory (NVM)3                |              |            |                                             |

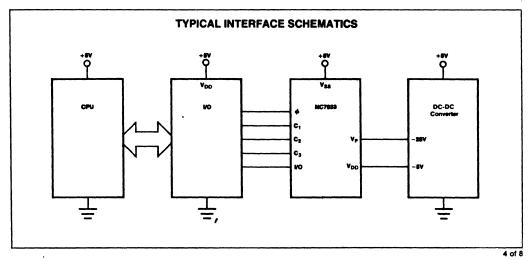

|                | [13] Interface Circuits3                       |              |            |                                             |

|                | [14] Bell Amp3                                 |              |            |                                             |

| 2 2 2          | [15] Power Supply                              |              |            |                                             |

| 3.2.3          | Monitor Assembly                               |              |            |                                             |

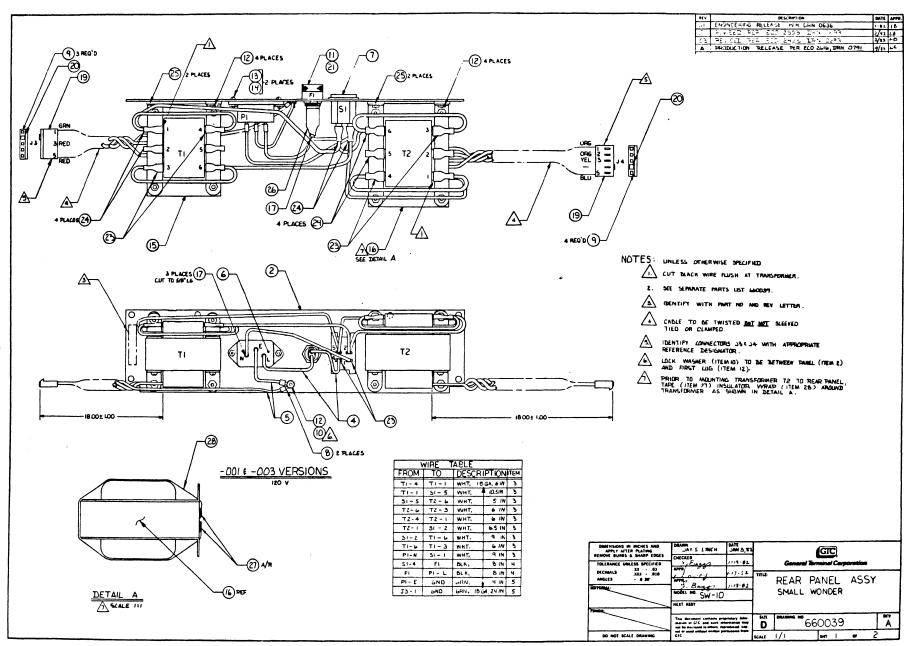

| 3.2.4          | Power Panel Assembly                           |              |            |                                             |

| 3.3            | MNEMONICS                                      | –נגר         |            |                                             |

## List of Figures

| Figure                                 | Page                            |

|----------------------------------------|---------------------------------|

| 1-1<br>1-2                             | SW10 Specifications             |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6 | Status Line Error Messages      |

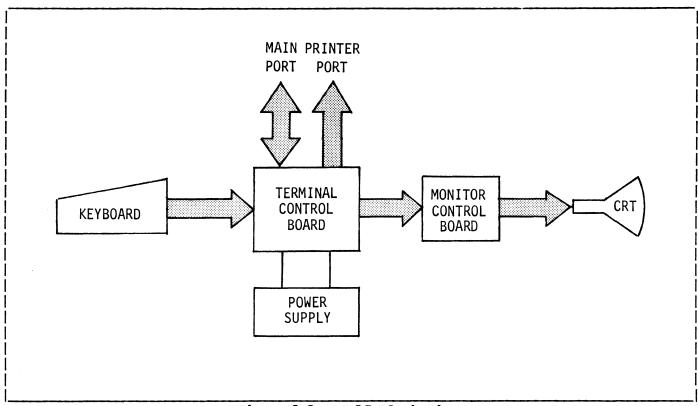

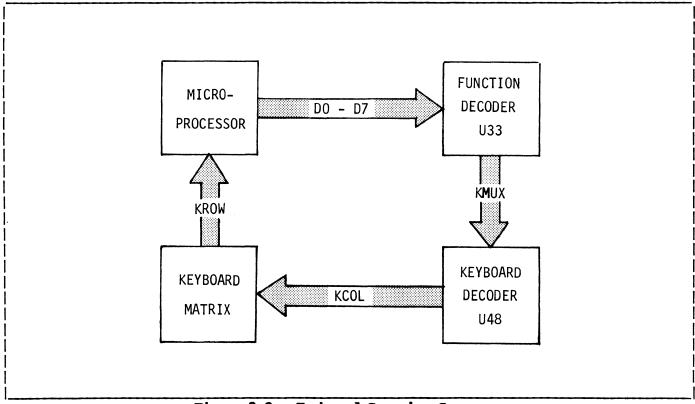

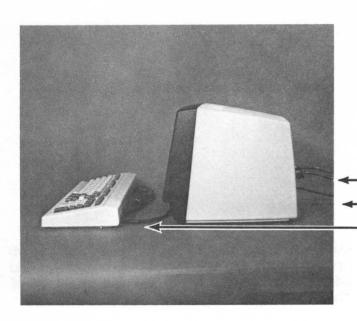

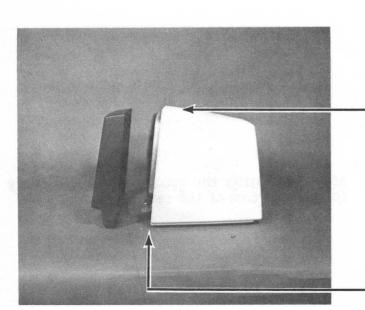

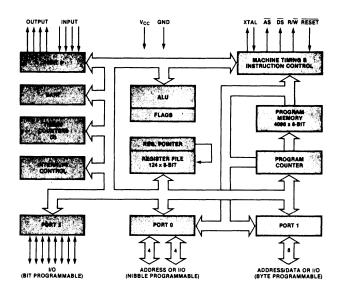

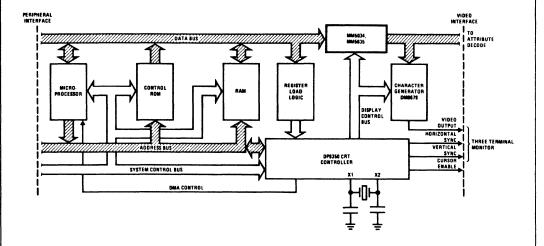

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5        | SW10 Block Diagram              |

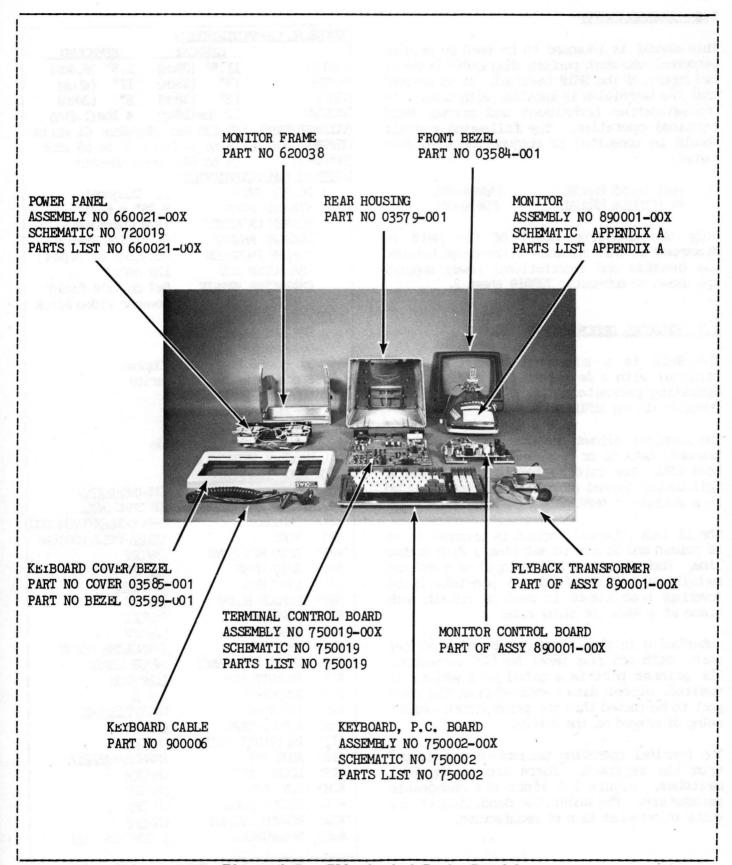

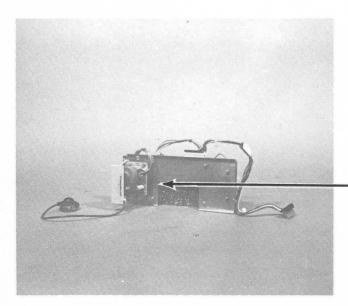

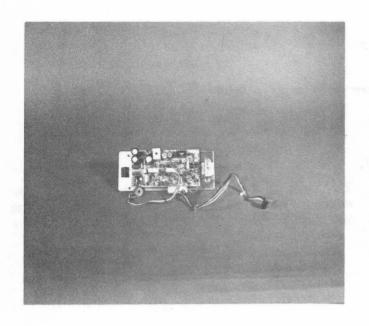

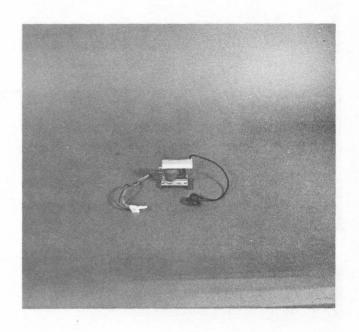

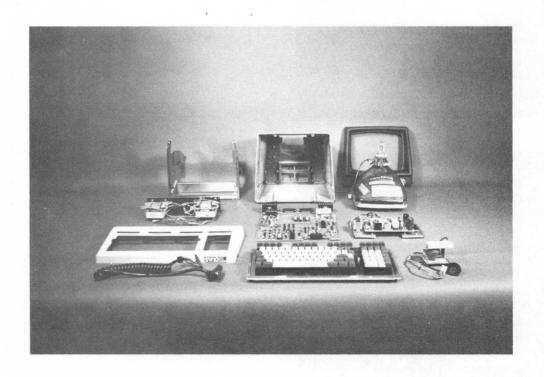

| 4-1                                    | Disassembly Procedures4-1       |

| 5–1                                    | Schematics5-1                   |

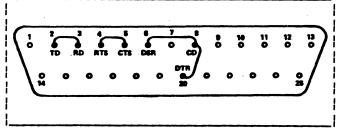

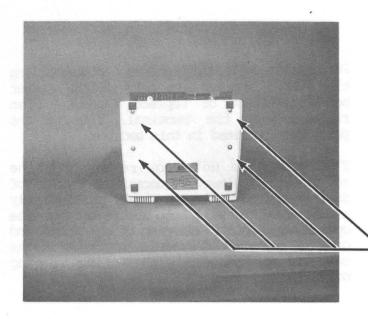

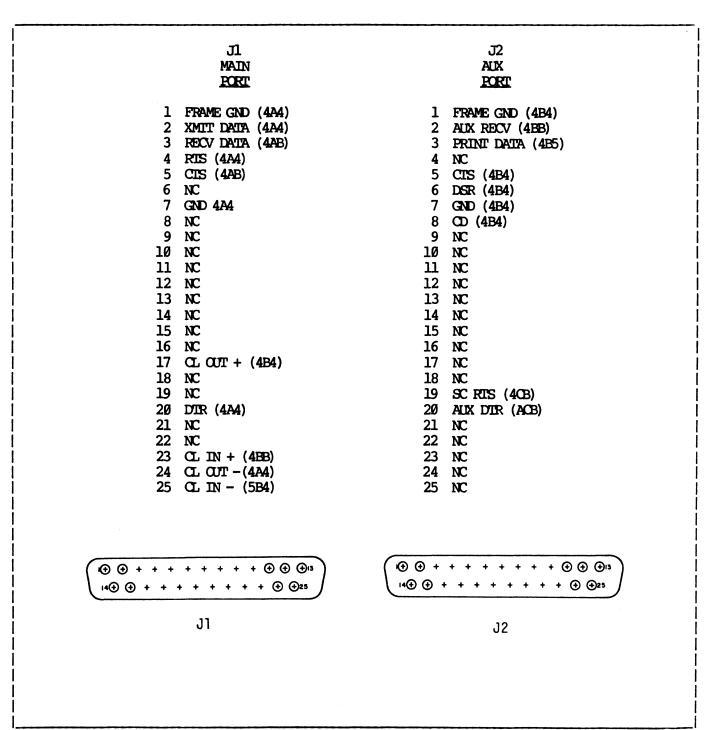

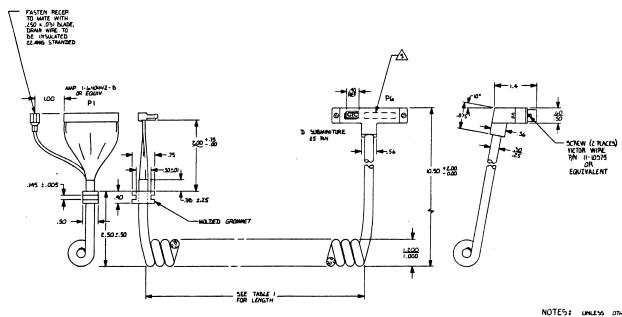

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5        | Communication Ports             |

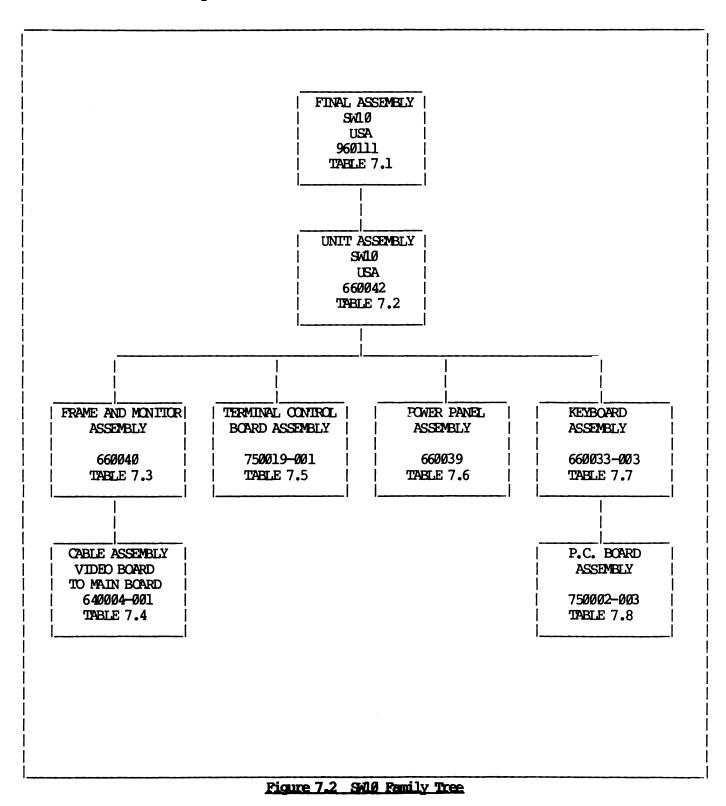

| 7–1<br>7–2                             | Warranty7-2 SWLØ Family Tree7-3 |

# List of Tables

| <u>Table</u> |                                 | Page                     |   |

|--------------|---------------------------------|--------------------------|---|

| 3.1          | PROM Enable                     | 3–5                      |   |

| 7.1          | SW10 FINAL ASSEMBLY             | 7-4                      |   |

| 7.2          | SWLØ UNIT ASSEMBLY              | <b></b> 7–5              |   |

| 7.3          | FRAME AND MONITOR ASSEMBLY      | <b></b> 7 <del>-</del> 6 |   |

| 7.4          | MONITIOR TO MAIN BOARD ASSEMBLY | 7–6                      |   |

| 7.5          | TERMINAL CONTROL BOARD          |                          |   |

| 7.6          | POWER PANEL ASSEMBLY            |                          |   |

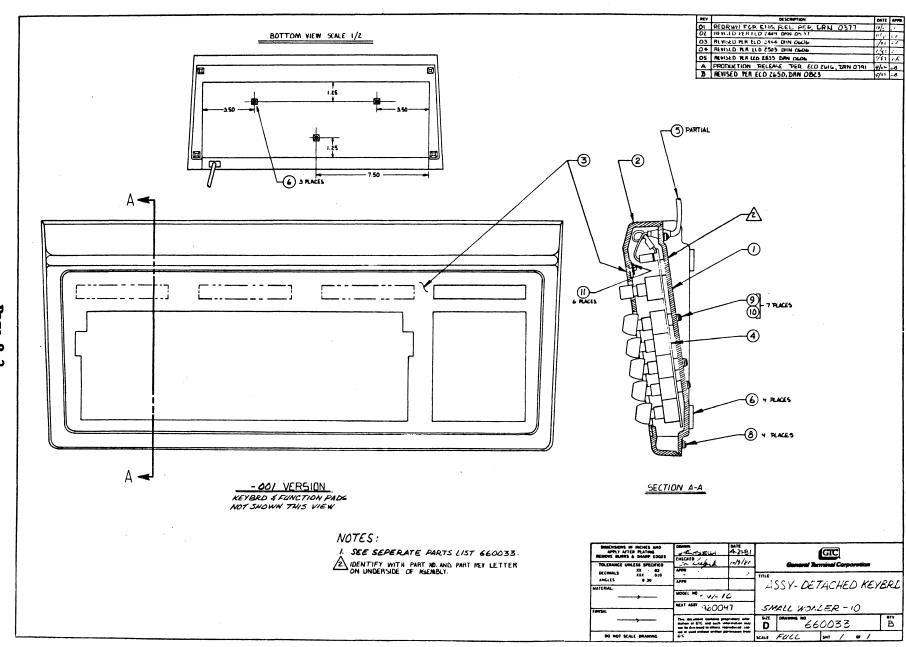

| 7.7          | KEYBOARD ASSEMBLY               |                          |   |

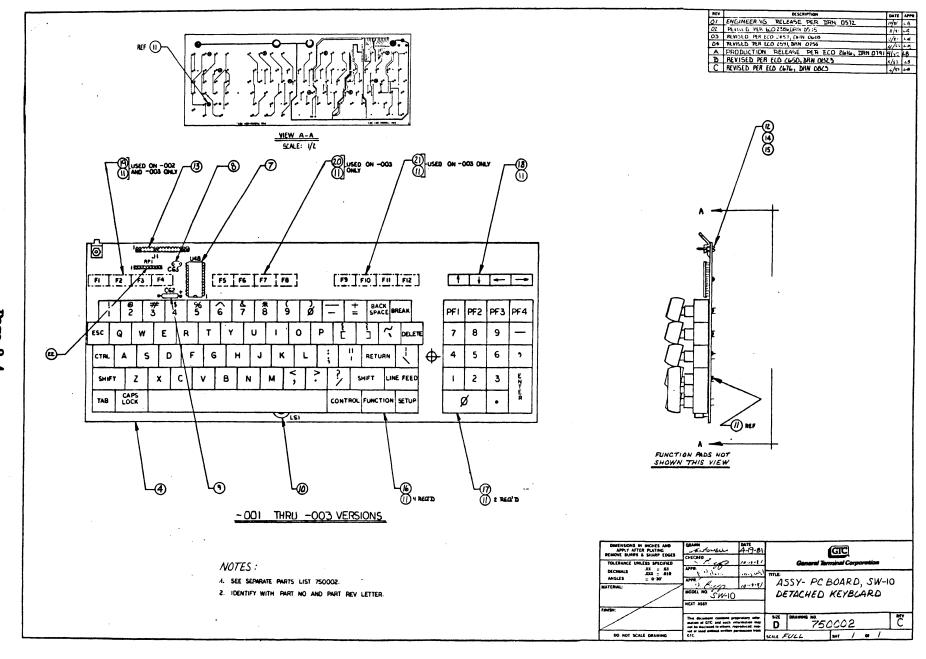

| 7.8          | KEYBOARD PC BOARD ASSEMBLY      |                          |   |

| 7.9          | OPTIONAL PARIS                  |                          | • |

| <br>         |                                 |                          |   |

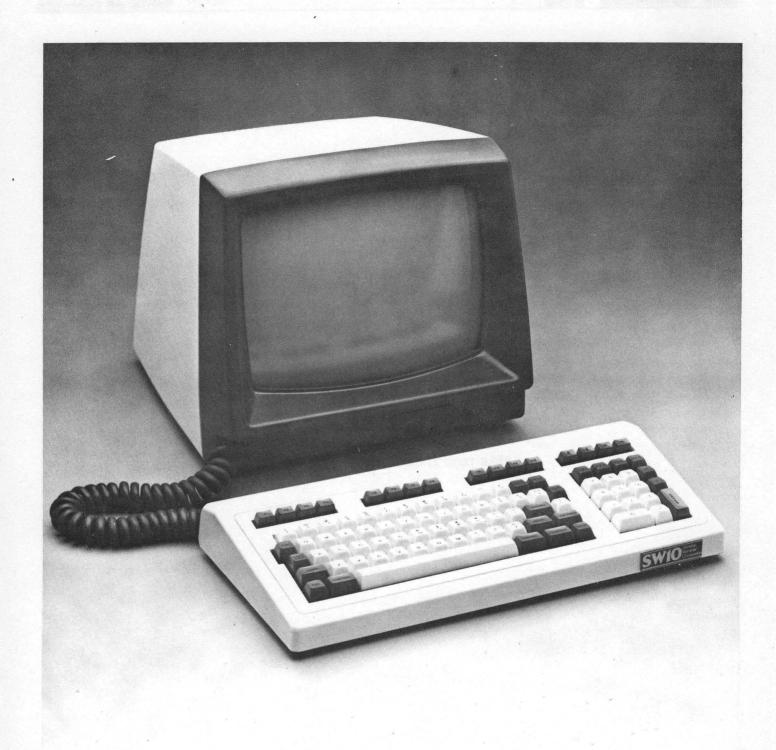

SW10 TERMINAL

| SWI A | Maintenance | Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |          |             |           | Table of    | Contents |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|-------------|-----------|-------------|----------|

|       |             | A SALES AND A SALE | <del></del> |          |             |           | <br>AWAG UL |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          | •           |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | mhi a an an |          | 17 1 -£4    | . bl onle |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | This page   | intentio | uality leru | DLank     |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |

|       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |          |             |           |             |          |